Page 1

Intel® 41210 Serial to Parallel PCI Bridge

Developer’s Manual

May 2005

Order Number: 278890-003US

Page 2

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. EXCEPT AS PROVIDED IN INTEL’S TERMS

AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHA TSO EVER, AND INTEL DISCLAIMS ANY EXP RESS

OR IMPLIED WARRANTY RELATING TO SALE AND/OR USE OF INTEL PRODUCTS, INCLUDING LIABILITY OR WARRANTIES RELATING TO

FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT, OR OTHER

INTELLECTUAL PROPERTY RIGHT.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the

presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by

estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

®

The Intel

published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calli ng

1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, i386, i486,

i960, iCOMP , InstantIP, Intel, Intel Centrino, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Create & Share, Intel GigaBlade,

Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel Play, Intel Play logo, Intel SingleDriver, Intel

SpeedStep, Intel StrataFlash, Intel TeamStation, Intel Xeon, Intel XScale, IPLink, Itanium, MCS, MMX, MMX logo, Optimizer logo, OverDrive,

Paragon, PC Dads, PC Parents, PDCharm, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, RemoteExpress, SmartDie,

Solutions960, Sound Mark, StorageExpress, The Computer Inside., The Journey Inside, TokenExpress, VoiceBrick, VTune, and Xircom are

trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

*Other names and brands may be claimed as the property of others.

Copyright © 2005, Intel Corporation

41210 Serial to Parallel PCI Bridge may contain design defects or errors known as errata which may cause the product to deviate from

2 Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual

Page 3

Contents

Contents

1 Introduction..................................................................................................................................11

1.1 PCI Express* Interface Features ........................................................................................11

1.2 PCI-X Interface Features....................................................................................................11

1.3 Power Management............................................................................................................12

1.4 SMBus Interface .................................................................................................................12

1.5 JTAG...................................................................................................................................12

2 Signal Description.......................................................................................................................13

2.1 On-Die Termination (ODT) .................................................................................................13

2.2 PCI Express* Interface .......................................................................................................15

2.3 PCI Bus Interface (Two Instances).....................................................................................16

2.4 PCI Bus Interface 64-Bit Extension (Two Interfaces) .........................................................18

2.5 PCI Bus Interface Clocks and, Reset and Power Management (Two Interfaces) ..............18

2.6 Interrupt Interface (Two Interfaces) ....................................................................................19

2.7 Reset Straps......................................................... ...... .............................................. ..........20

2.8 SMBus Interface .................................................................................................................21

2.9 Miscellaneous Pins......................................... ...... ....................................... ...... ....... ...... ....22

2.10 Voltage Pins........................................................................................................................23

3 PCI-X Interface.............................................................................................................................25

3.1 Initialization.........................................................................................................................25

3.2 Transactions Supported......................................................................................................26

3.2.1 PCI Mode...............................................................................................................26

3.2.2 PCI-X Mode ...........................................................................................................27

3.2.3 Read Transactions.................................................................................................27

3.2.4 Configuration Transactions....................................................................................28

3.2.5 LOCK Cycles .........................................................................................................29

3.2.6 Decoding................................................................................................................30

3.2.7 Transaction Termination ........................................................................................30

3.3 PCI-X Protocol Specifics.....................................................................................................34

3.3.1 Attributes................................................................................................................34

3.3.2 4 GB and 4 K Page Crossover ..............................................................................34

3.3.3 Wait States .................... ....... ...... ....... ...... ...... ....... ...... ....... ...... ....... ...... .................34

3.3.4 Split Transactions ..................................................................................................35

3.4 Arbitration ...........................................................................................................................35

4 Power Management.....................................................................................................................37

4.1 Hardware-Controlled Active State Power Management .....................................................37

4.2 Software-Driven PCI-PM 1.1–Compatible Power Management.........................................37

4.3 PCI Bus Power Management .............................................................................................37

4.4 Intel

4.5 Power-Management Event Signaling .................................................................................38

5 Addressing...................................................................................................................................41

5.1 Addressable Spaces within the Intel

5.2 Secondary PCI Devices......................................................................................................42

5.3 Configuration-Space Access ..............................................................................................42

®

41210 Serial to Parallel PCI Bridge Device Power Management .............................38

®

41210 Serial to Parallel PCI Bridge ........................41

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual 3

Page 4

Contents

5.3.1 PCI Express* Configuration Access ......................................................................42

5.3.2 Type 0 Configuration Access from PCI-X Interface...............................................44

5.3.3 SMBus Configuration Access................................................................................45

5.4 I/O Space Access Mechanism............................................................................................45

5.5 Memory Space Access Mechanism....................................................................................47

5.5.1 Memory-Mapped I/O Window................................................................................48

5.5.2 Prefetchable Memory Window...............................................................................49

5.5.3 Opaque Memory Window ......................................................................................49

5.6 VGA Addressing.................................................................................................................49

6 Transaction Ordering..................................................................................................................51

6.1 Upstream Transaction Ordering .........................................................................................51

6.2 Downstream Transaction Ordering.....................................................................................52

6.3 Relaxed Ordering/No-Snoop Support.................................................................................52

7 Interrupt Support.........................................................................................................................53

7.1 Legacy Interrupt Sharing ....................................................................................................53

7.2 Interrupt Routing for Devices behind a Bridge....................................................................54

8 System Management Bus Interface...........................................................................................55

8.1 SMBus Commands.............................................................................................................56

8.2 Initialization Sequence........................................................................................................57

8.2.1 Configuration ........................................................................................................57

8.2.2 Configuration Writes ...................... ....... ...... ...... .............................................. .......60

8.3 Error Handling.....................................................................................................................61

8.4 SMBus Interface Reset.......................................................................................................62

9 Local Initialization .......................................................................................................................63

10 Clock and Reset...........................................................................................................................65

10.1 Clocking..............................................................................................................................65

10.2 Device Reset ......................................................................................................................65

10.2.1 PERST# Reset Mechanism...................................................................................66

10.2.2 RSTIN# Reset Mechanism ....................................................................................66

10.2.3 PCI Express* Reset Mechanism............................................................................66

10.2.4 Software PCI Reset (SBR—Secondary Bus Reset)..............................................67

11 Error Handling .............................................................................................................................69

11.1 PCI Express* Errors............................................................................................................69

11.2 PCI Errors...........................................................................................................................69

11.2.1 Error Types............................................................................................................70

11.2.2 Termination of Completion Required Transactions ...............................................70

12 Register Description ...................................................................................................................73

12.1 Register Nomenclature and Access Attributes...................................................................73

12.2 Configuration Registers .............................. ....... ...... ...... ....... ...... ........................................74

12.2.1 Offset 00h: ID—Identifiers .....................................................................................78

12.2.2 Offset 04h: PCICMD—Command Register ...........................................................78

12.2.3 Offset 06h: PSTS—Primary Device Status............................................................79

12.2.4 Offset 08h: REVID—Revision ID...........................................................................80

12.2.5 Offset 09h: CC—Class Code.................................................................................81

4 Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual

Page 5

Contents

12.2.6 Offset 0Ch: CLS—Cache-Line Size.......................................................................81

12.2.7 Offset 0Dh: PMLT—Primary Master Latency Timer ..............................................81

12.2.8 Offset 0Eh: HEADTYP—Header Type...................................................................81

12.2.9 Offset 18h: BNUM—Bus Numbers ........................................................................82

12.2.10 Offset 1Bh: SMLT—Secondary Master Latency Timer..........................................82

12.2.11 Offset 1Ch: IOBL—I/O Base and Limit ..................................................................83

12.2.12 Offset 1Eh: SSTS—Secondary Status ..................................................................84

12.2.13 Offset 20h: MBL—Memory Base and Limit............................................................85

12.2.14 Offset 24h: PMBL—Prefetchable Memory Base and Limit....................................86

12.2.15 Offset 28h: PMBU32—Prefetchable Memory Base Upper 32 Bits........................86

12.2.16 Offset 2Ch: PMLU32—Prefetchable Memory Limit Upper 32 Bits.........................87

12.2.17 Offset 30h: IOBLU16—I/O Base and Limit Uppe r 16 Bit s........ ....... ...... .................87

12.2.18 Offset 34h: CAPP—Capabilities List Pointer .........................................................87

12.2.19 Offset 3Ch: INTR—Interrupt Information ...............................................................87

12.2.20 Offset 3Eh: BCTRL—Bridge Control......................................................................88

12.2.21 Offset 40h: BCNF—Bridge Configuration Register................................................90

12.2.22 Offset 42h: MTT—Multi-Transaction Timer............................................................91

12.2.23 Offset 43h: PCLKC—PCI Clock Control................................................................91

12.2.24 Offset 44h: EXP_CAPID—PCI Express* Capability Identifier................................91

12.2.25 Offset 45h: EXP_NXTP—Next Item Pointer..........................................................91

12.2.26 Offset 46h: EXP_CAP—PCI Express* Capability..................................................92

12.2.27 Offset 48h: EXP_DCAP—PCI Express* Device Capabilities Register ..................92

12.2.28 Offset 4Ch: EXP_DCTL—PCI Express* Device Control Register .........................93

12.2.29 Offset 4Eh: EXP_DSTS—PCI Express* Device Status Register...........................94

12.2.30 Offset 50h: EXP_LCAP—PCI Express* Link Capabilities Register .......................94

12.2.31 Offset 54h: EXP_LCTL—PCI Express* Link Control Register...............................95

12.2.32 Offset 56h: EXP_LSTS—PCI Express* Link Status Register................................96

12.2.33 Offset 5Ch: MSI_CAPID—PCI Express* MSI Capability Identifier ........................96

12.2.34 Offset 5Dh: MSI_NXTP—PCI Express* Next Item Pointer....................................96

12.2.35 Offset 5Eh: MSI_MC—PCI Express* MSI Message Control .................................97

12.2.36 Offset 60h: MSI_MA—PCI Express* MSI Message Address ................................97

12.2.37 Offset 68h: MSI_MD—PCI Express* MSI Message Data......................................97

12.2.38 Offset 6Ch: PM_CAPID—Power Management Capabilities Identifier ...................97

12.2.39 Offset 6Dh: PM_NXTP—Power Management Next Item Pointer ..........................98

12.2.40 Offset 6Eh: PM_PMC—Power Management Capabilities.....................................98

12.2.41 Offset 70h: PM_PMCSR—Power Management Control/Status Register..............99

12.2.42 Offset 72h: PM_BSE—Power Management Bridge

Support Extensions............................................................ ...... ....... ...... ....... ...... ....99

12.2.43 Offset 73h: PM_DATA—Power Management Data Field ......................................99

12.2.44 Offset D8h: PX_CAPID—PCI-X Capabilities Identifier ........................................100

12.2.45 Offset D9h: PX_NXTP—PCI-X Next Item Pointer ...............................................100

12.2.46 Offset DAh: PX_SSTS—PCI-X Secondary Status ..............................................101

12.2.47 Offset DCh: PX_BSTS—PCI-X Bridge Status .....................................................102

12.2.48 Offset E0h: PX_USTC—PCI-X Upstream Split Transaction Control...................102

12.2.49 Offset E4h: PX_DSTC—PCI-X Downstream Split Transaction Control...............103

12.2.50 Offset FCh: BINIT—Bridge Initialization Register................................................104

12.2.51 Offset 100h: EXPAERR_CAPID—PCI Express* Advanced

Error Capability Identifier .....................................................................................105

12.2.52 Offset 104h: ERRUNC_STS—PCI Express* Uncorrectable

Error Status Register ...........................................................................................105

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual 5

Page 6

Contents

12.2.53 Offset 108h: ERRUNC_MSK—PCI Express*

Uncorrectable Error Mask....................................................................................106

12.2.54 Offset 10Ch: ERRUNC_SEV—PCI Express* Uncorrectable

Error Severity.......................................................................................................107

12.2.55 Offset 110h: ERRCOR_STS—PCI Ex pres s*

Correctable Error Status......................................................................................108

12.2.56 Offset 114h: ERRCOR_MSK—PCI Express*

Correctable Error Mask........................................................................................109

12.2.57 Offset 118h: ADVERR_CTL—A dv anced Er ror Control

and Capability Register........................................................................................109

12.2.58 Offset 11C–12Bh: HDR_LOG—PCI Express*

Transaction Header Log ......................................................................................110

12.2.59 Offset 12Ch: PCIXERRUNC_STS—Un co rrectab le

PCI-X Status Register..........................................................................................111

12.2.60 Offset 130h: PCIXERRUNC_MSK —Uncorrec tabl e

PCI-X Error Mask Register ..................................................................................113

12.2.61 Offset 134h: PCIXERRUNC_SEV —Uncorrec tab le

PCI-X Error Severity Register..............................................................................115

12.2.62 Offset 138h: PCIXERRUNC_PTR— Uncorrec table

PCI-X Error Pointer..............................................................................................116

12.2.63 Offset 13C–14Bh: PCIXHDR_LOG— Uncorrec tabl e

PCI-X Error Transaction Header Log...................................................................117

12.2.64 Offset 16Ah: ARB_CNTRL—Internal Arbiter Control Register ............................117

12.2.65 Offset 170h: SSR—Strap Status Register...........................................................118

12.2.66 Offset 178h: PREFCTRL—Prefetch Control Register .........................................119

12.2.67 Offset 300h: PWRBGT_CAPID—Power Budgeting

Enhanced Capability Header...............................................................................120

12.2.68 Offset 304h: PWRBGT_DSEL—Power Budgeting

Data Select Register............................................................................................120

12.2.69 Offset 308h: PWRBGT_DATA—Power Budgeting Data Register.......................120

Figures

1 Internal Arbitration Scheme ........................................................................................................36

2 Type 1 to Type 0 Translation (PCI and PCI-X)...........................................................................44

3 Upstream Type 0 PCI-X Configuration Cycle Address Format ..................................................45

4 I/O Forwarding............................................................................................................................46

5 Memory Forwarding....................................................................................................................48

6 DWord Configuration Read Protocol (SMBus Block Write/Block Read, PEC Enabled) .............58

7 DWord Configuration Read Protocol (SMBus Word Write/Word Read, PEC Enabled) .............58

8 DWord Configuration Read Protocol (SMBus Block Write/Block Read, PEC Disabled) ............59

9 DWord Configuration Read Protocol (SMBus Word Write/Word Read, PEC Disabled).............59

10 DWord Configuration Write Protocol (SMBus Block Write, PEC Enabled).................................60

11 DWord Configuration Write Protocol (SMBus Byte Write, PEC Enabled) ..................................61

12 Intel

6 Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual

®

41210 Serial to Parallel PCI Bridge Capabilities...............................................................75

Page 7

Contents

Tables

1 ODT Signals ...............................................................................................................................14

2 PCI Express* Interface Pins .......................................................................................................15

3 PCI Interface Pins.......................................................................................................................16

4 PCI Interface Pins: 64-Bit Extensions.........................................................................................18

5 PCI Clock and Reset Pins ..........................................................................................................18

6 Interrupt Interface Pins ...............................................................................................................19

7 Reset Strap Pins.........................................................................................................................20

8 SMBus Interface Pins .................................................................................................................21

9 Miscellaneous Pins.....................................................................................................................22

10 Miscellaneous Pins.....................................................................................................................23

11 PCI Mode Pin/Strap Encoding....................................................................................................25

12 PCI-X Initialization Pattern..........................................................................................................25

13 PCI Transactions Supported.......................................................................................................26

14 PCI-X Transactions Supported...................................................................................................27

15 LOCK Transaction Handling in the Intel

16 Intel

17 Intel

®

41210 Serial to Parallel PCI Bridge Implementation of Requester Attribute Fields..........34

®

41210 Serial to Parallel PCI Bridge Implementation of Completer Attribute Fields..........35

18 Split Completion Abort Registers................................................................................................35

19 Addressable Spaces within the Intel

20 Secondary PCI Device Addressing.............................................................................................42

21 Upstream Transaction Ordering ............................. ...... ...... ....... ...... ....... ...... ....... ...... .................51

22 Downstream Transaction Ordering.............................................................................................52

23 INTx Routing Table.....................................................................................................................53

24 Interrupt Binding for Devices behind a Bridge ............................................................................54

25 SMBus Address Assignments ....................................................................................................55

26 SMBus Command Encoding.......................................................................................................56

27 SMBus Status Byte Encoding.....................................................................................................57

28 Clock Domains............................................................................................................................65

29 Completion-Status Translation for Immediate Terminations.......................................................70

30 Completion-Status Translation for PCI-X Split-Completion Terminations ..................................71

31 Completion-Status Translation for PCI Express* Split-Completion Terminations.......................72

32 Bit Attribute Definitions ...............................................................................................................73

33 Legacy Configuration Space.......................................................................................................76

34 PCI Express* Extended Configuration Space ............................................................................77

35 Offset 00h: ID—Identifiers ..........................................................................................................78

36 Offset 04h: PCICMD—Command Register ................................................................................78

37 Offset 06h: PSTS—Primary Device Status.................................................................................79

38 Offset 08h: REVID—Revision ID................................................................................................80

39 Offset 09h: CC—Class Code......................................................................................................81

40 Offset 0Ch: CLS—Cache Line Size............................................................................................81

41 Offset 0Dh: PMLT—Primary Master Latency Timer ...................................................................81

42 Offset 0Eh: HEADTYP—Header Type .......................................................................................81

43 Offset 18h: BNUM—Bus Numbers.............................................................................................82

44 Offset 1Bh: SMLT—Secondary Master Latency Timer...............................................................82

45 Offset 1Ch: IOBL—I/O Base and Limit.......................................................................................83

46 Offset 1Eh: SSTS—Secondary Status .......................................................................................84

47 Offset 20h: MBL—Memory Base and Limit ........................ ....... ...... ....... ...... ....... ...... ....... ...... ....85

48 Offset 24h: PMBL—Prefetchable Memory Base and Limit.........................................................86

49 Offset 28h: PMBU32—Prefetchable Memory Base Upper 32 Bits.............................................86

®

41210 Serial to Parallel PCI Bridge...........................29

®

41210 Serial to Parallel PCI Bridge................................41

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual 7

Page 8

Contents

50 Offset 2Ch: PMLU32—Prefetchable Memory Limit Upper 32 Bits .............................................87

51 Offset 30h: IOBLU16—I/O Base and Limit Upper 16 Bits ...................................... ...... ....... ...... .87

52 Offset 34h: CAPP—Capabilities List Pointer..............................................................................87

53 Offset 3Ch: INTR—Interrupt Information....................................................................................87

54 Offset 3Eh: BCTRL—Bridge Control ..........................................................................................88

55 Offset 40h: BCNF—Bridge Configuration Register ....................................................................90

56 Offset 42h: MTT—Multi-Transaction Timer ................................................................................91

57 Offset 43h: PCLKC—PCI Clock Control.....................................................................................91

58 Offset 44h: PCI Express*_CAPID—PCI Express* Capability Identifier......................................91

59 Offset 45h: PCI Express*_NXTP—Next Item Pointer.................................................................91

60 Offset 46h: EXP_CAP—PCI Express* Capability.......................................................................92

61 Offset 48h: EXP_DCAP—PCI Express* Device Capabilities Register.......................................92

62 Offset 4Ch: EXP_DCTL—PCI Express* Device Control Register..............................................93

63 Offset 4Eh: EXP_DSTS—PCI Express* Device Status Register ...............................................94

64 Offset 50h: EXP_LCAP—PCI Express* Link Capabilities Register............................................94

65 Offset 54h: EXP_LCTL—PCI Express* Link Control Register ...................................................95

66 Offset 56h: EXP_LSTS—PCI Express* Link Status Register.....................................................96

67 Offset 5Ch: MSI_CAPID—PCI Express* MSI Capability Identifier.............................................96

68 Offset 5Dh: MSI_NXTP—PCI Express* Next Item Pointer.........................................................96

69 Offset 5Eh: MSI_MC—PCI Express* MSI Message Control......................................................97

70 Offset 60h: MSI_MA—PCI Express* MSI Message Address.....................................................97

71 Offset 68h: MSI_MD—PCI Express* MSI Message Data ..........................................................97

72 Offset 6Ch: PM_CAPID—Power Management Capabilities Identifier........................................97

73 Offset 6Dh: PM_NXTP—Power Management Next Item Pointer...............................................98

74 Offset 6Eh: PM_PMC—Power Management Capabilities..........................................................98

75 Offset 70h: PM_PMCSR—Power Management Control/Status Register...................................99

76 Offset 72h: PM_BSE—Power Management Bridge Support Extensions...................................99

77 Offset 73h: PM_DATA—Power Management Data Field...........................................................99

78 Offset D8h: PX_CAPID—PCI-X Capabilities Identifier .............................................................100

79 Offset D9h: PX_NXTP—PCI-X Next Item Pointer....................................................................100

80 Offset DAh: PX_SSTS—PCI-X Secondary Status ...................................................................101

81 Offset DCh: PX_BSTS—PCI-X Bridge Status..........................................................................102

82 Offset E0h: PX_USTC—PCI-X Upstream Split Transaction Control........................................102

83 Offset E4h: PX_DSTC—PCI-X Downstream Split Transaction Control ...................................103

84 Offset FCh: BINIT—Bridge Initialization Register.....................................................................104

85 Offset 100h: EXPAERR_CAPID—PCI Express* Advanced Error Capability Identifier ............105

86 Offset 104h: ERRUNC_STS—PCI Express* Uncorrectable Error Status Register..................105

87 Offset 108h: ERRUNC_MSK—PCI Express* Uncorrectable Error Mask.................................106

88 Offset 10Ch: ERRUNC_SEV—PCI Express* Uncorrectable Error Severity ............................107

89 Offset 110h: ERRCOR_STS—PCI Express* Correctable Error Status....................................108

90 Offset 114h: ERRCOR_MSK—PCI Express* Correctable Error Mask ....................................109

91 Offset 118h: ADVERR_CTL—Advanced Error Control and Capability Register......................109

92 Offset 11C–12Bh: HDR_LOG—PCI Express* Transaction Header Log..................................110

93 Offset 12Ch: PCIXERRUNC_STS—Uncorrectable PCI-X Status Register .............................111

94 Offset 130h: PCIXERRUNC_MSK—Uncorrectable PCI-X Error Mask Register......................113

95 Offset 130h: PCIXERRUNC_SEV—Uncorrectable PCI-X Error Severity Register..................115

96 Offset 138h: PCIXERRUNC_PTR—Uncorrectable PCI-X Error Pointer Register....................116

97 Offset 13C–14Bh: PCIXHDR_LOG—Uncorrectable PCI-X Header Log..................................117

98 Offset 16Ah: ARB_CNTRL—Internal Arbiter Control Register.................................................117

99 Offset 170h: SSR—Strap Status Register................................................................................118

8 Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual

Page 9

Contents

100 Offset 178h: PREFCTRL—Prefetch Control Register ..............................................................119

101 Offset 300h: PWRBGT_HDR—Power Budgeting Enhanced Capability Header......................120

102 Offset 304h: PWRBGT_DSEL—Power Budgeting Data Select Register.................................120

103 Offset 308h: PWRBGT_DATA—Power Budgeting Data Register............................................120

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual 9

Page 10

Contents

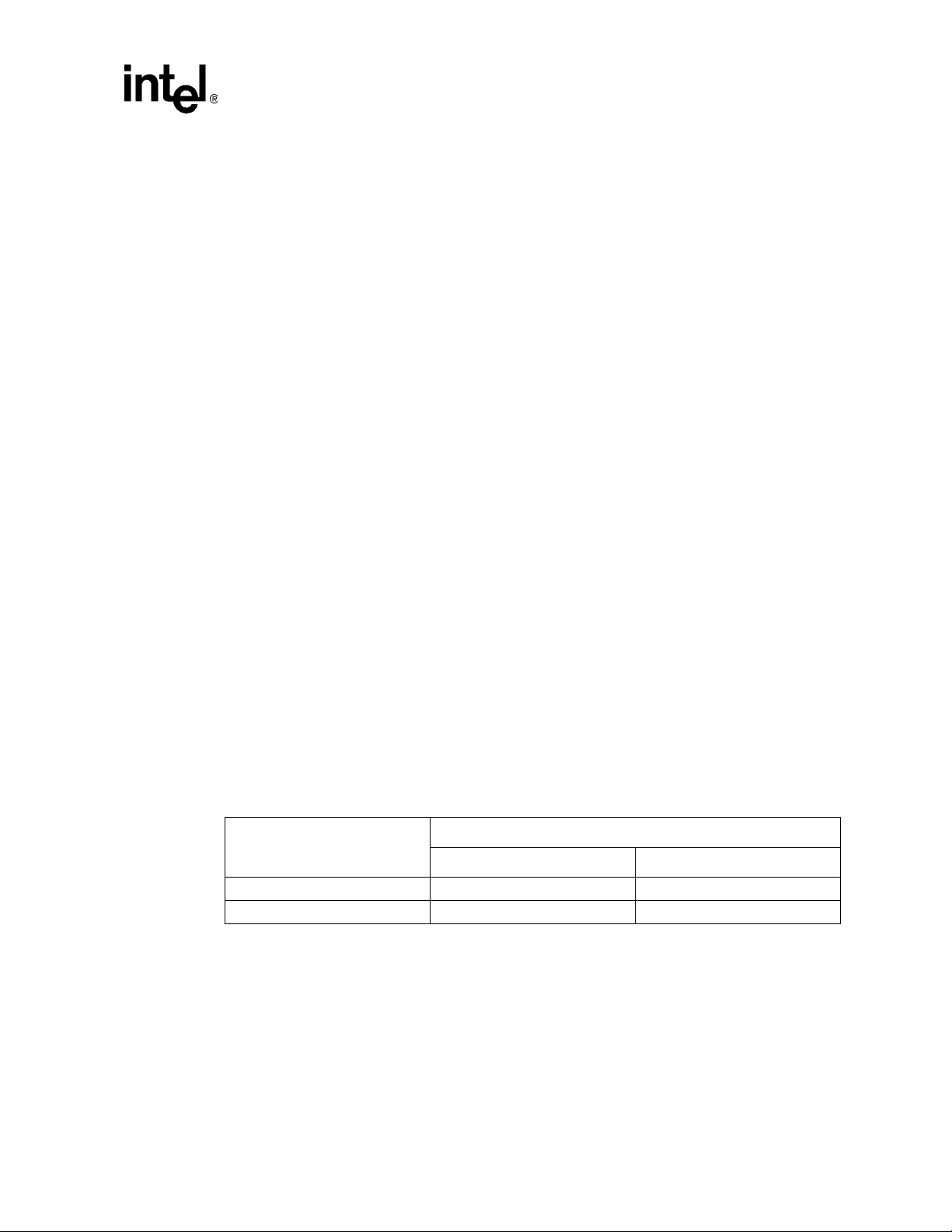

Revision History

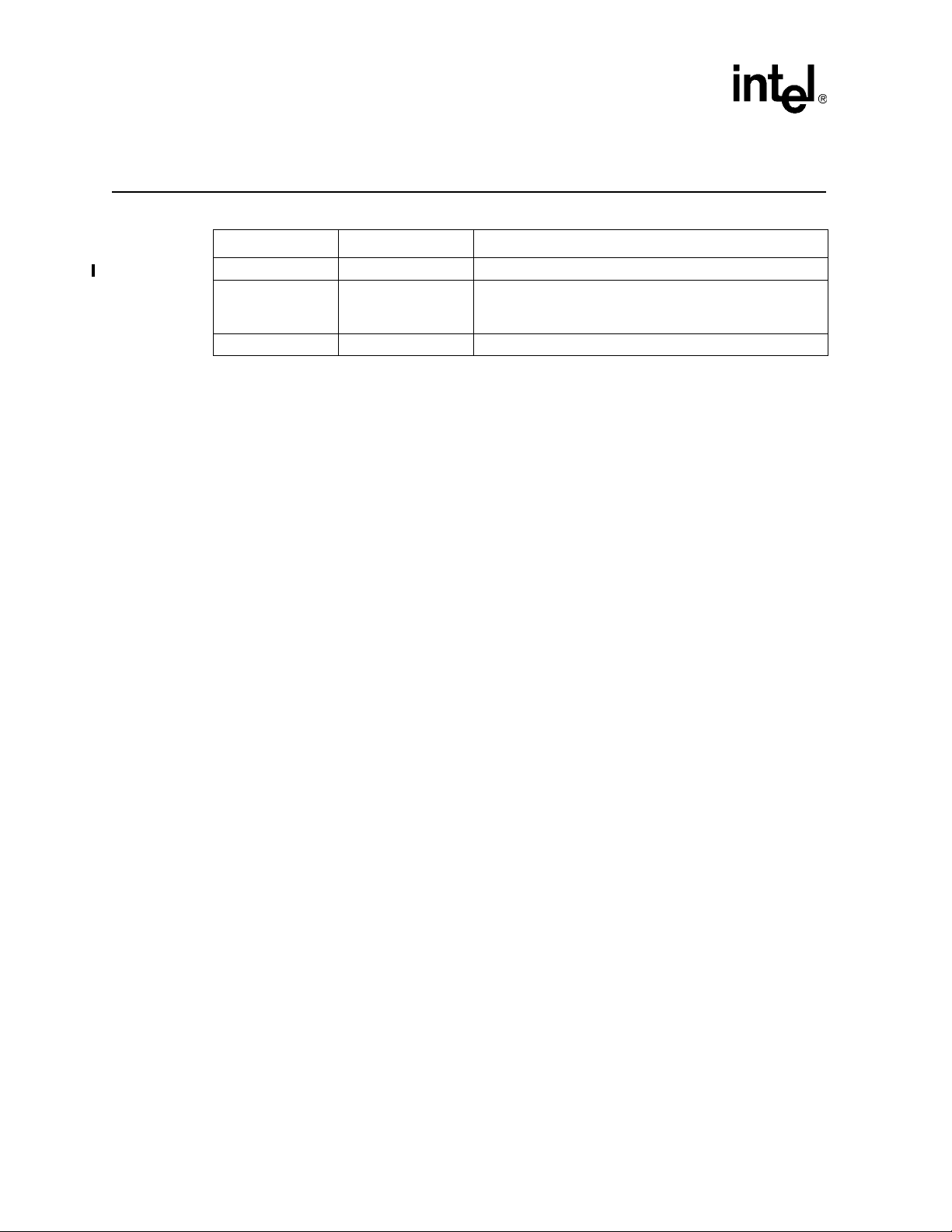

Date Revision Description

May 2005 003 Revised Table1 and Table 9

October 2004 002

March 2004 001 Initial release

Updated PCI Express operation information in Section 1.1 and

Table 2 inSection 2.2.

Removed L0s state information throughout manual.

10 Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual

Page 11

Introduction

Introduction 1

The Intel® 41210 Serial to Parallel PCI Bridge (also called the 41210 Bridge or the 41210)

integrates two PCI Express*-to-PCI/PCI-X bridges. Each bridge follows the PCI-to-PCI Bridge

programming model. The PCI Express* port is compatible with the PCI Express* Specification,

Revision 1.0a. The two PCI bus interfaces are comparable with the PCI Local Bus Specification,

Revision 2.3 and the PCI-X Addendum to the PCI Local Bus Specification, Revision 1.0b.

1.1 PCI Express* Interface Features

• PCI Express* Specification, Revision 1.0a

• Support for single ×8, single ×4 or single x1 PCI Express* operation

• 64-bit addressing support

• 32-bit CRC (cyclic redundancy checking) covering all transmitted data packets

• 16-bit CRC on all link message information

• Raw bit-rate on the data pins of 2.5 Gbit/s, resulting in a raw bandwidth per pin of 250 MB/s

• Maximum realized bandwidth on PCI Express* interface of 2 GB/s (in ×8 mode) in each

direction simultaneously, for an aggregate of 4 GB/s

1.2 PCI-X Interface Features

• PCI Local Bus Specification, Revision 2.3

• PCI-to-PCI Bridge Specification, Revision 1.1

• PCI-X Addendum to the PCI Local Bus Specification, Revision 1.0b

• 64-bit 66 MHz, 3.3 V, not 5 V tolerant

• On-Die Termination (ODT) with 8.3 KΩ pul l-up to 3.3 V for PCI signals

• Six external REQ/GNT pairs for internal arbiter on segment A and B respectively

• Programmable bus parking on either the last agent or always on Intel

PCI Bridge

• Two-level programmable round-robin internal arbiter with Multi-Transaction Timer (MTT)

• External PCI clock-feed support for asynchronous primary and secondary domain operation

• 64-bit addressing for upstream and downstream transactions

• Downstream LOCK# support

• No upstream LOCK# support

• PCI fast Back-to-Back capable as target

• Up to four active and four pending upstream memory read transactions

®

41210 Serial to Parallel

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual 11

Page 12

Introduction

• Up to two downstream delayed (memory read, I/O read/write and configuration read/write)

transactions

• Tunable inbound read prefetch algorithm for PCI MRM/MRL commands

• Device hiding support for secondary PCI devices

• Secondary bus private memory support via opaque memory region

• Local initialization via SMBus

• Secondary side initialization via Type 0 configuration cycles

• Full peer-to-peer read/write capability between the two secondary PCI segments

1.3 Power Management

• Support for PCI PM 1.1-compatible D0, D3hot and D3cold device power states

• Support for PME# event propagation on behalf of PCI devices

1.4 SMBus Interface

• Compatible with System Management Bus Specification, Revision 2.0

• Slave-mode operation only

• Full read/write access to all configuration registers

1.5 JTAG

• IEEE Standard Test Access Port and Boundary Scan Architecture 1149.1a

12 Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual

Page 13

Signal Description

Signal Description 2

The “#” symbol at the end of a signal name indicates that the active (asserted) state occurs when

the signal is at a low voltage level. When “#” is not present after the signal name, the signal is

asserted when at the high voltage level. The following notations are used to describe the signal

type:

I: Input pin

O: Output pin

OD: Open-drain Output pin

I/O: Bidirectional Input/Output pin

I/OD: Bidirectional Input/Open-drain Output pin

2.1 On-Die Termination (ODT)

The Intel® 41210 Serial to Parallel PCI Bridge (also called the 41210 Bridge or the 41210)

incorporates On-Die Termination (ODT) for most of the PCI interface signals. ODT eliminates the

need for the system designer to incorporate external pull-up resistors in the design.

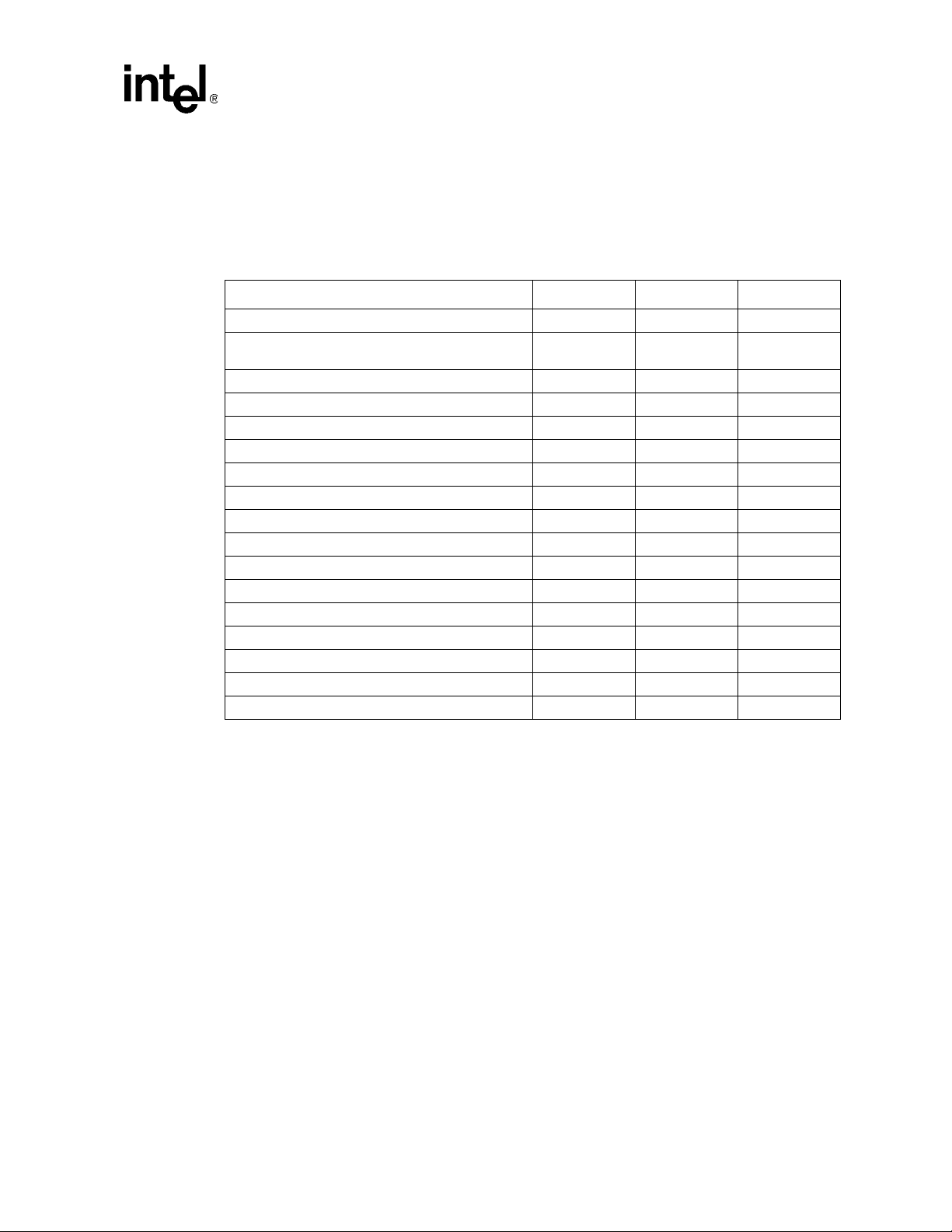

T a ble 1, “ODT Signals” on page 14 lists the signals that have an on-die termination of 8.33 KΩ @

40%.

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual 13

Page 14

Signal Description

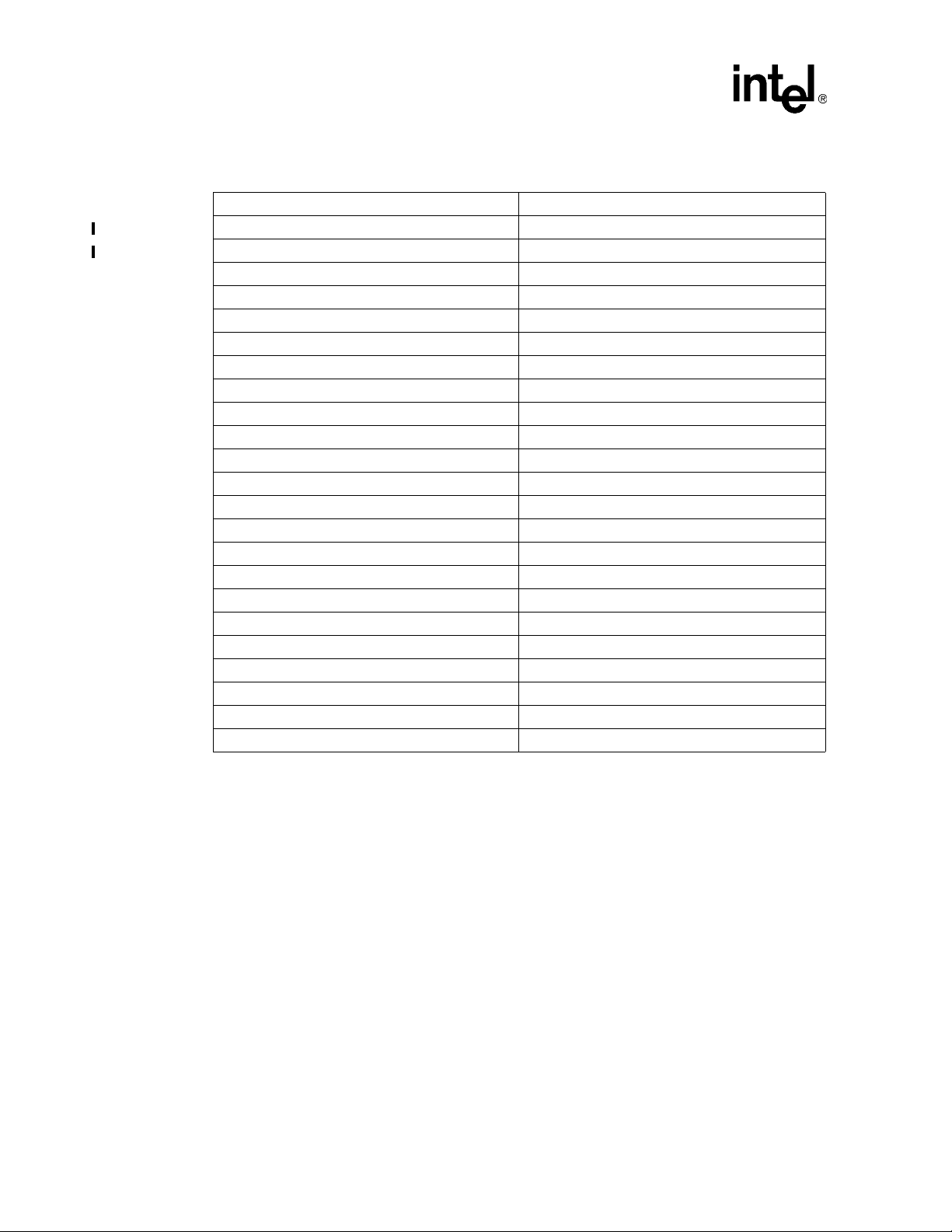

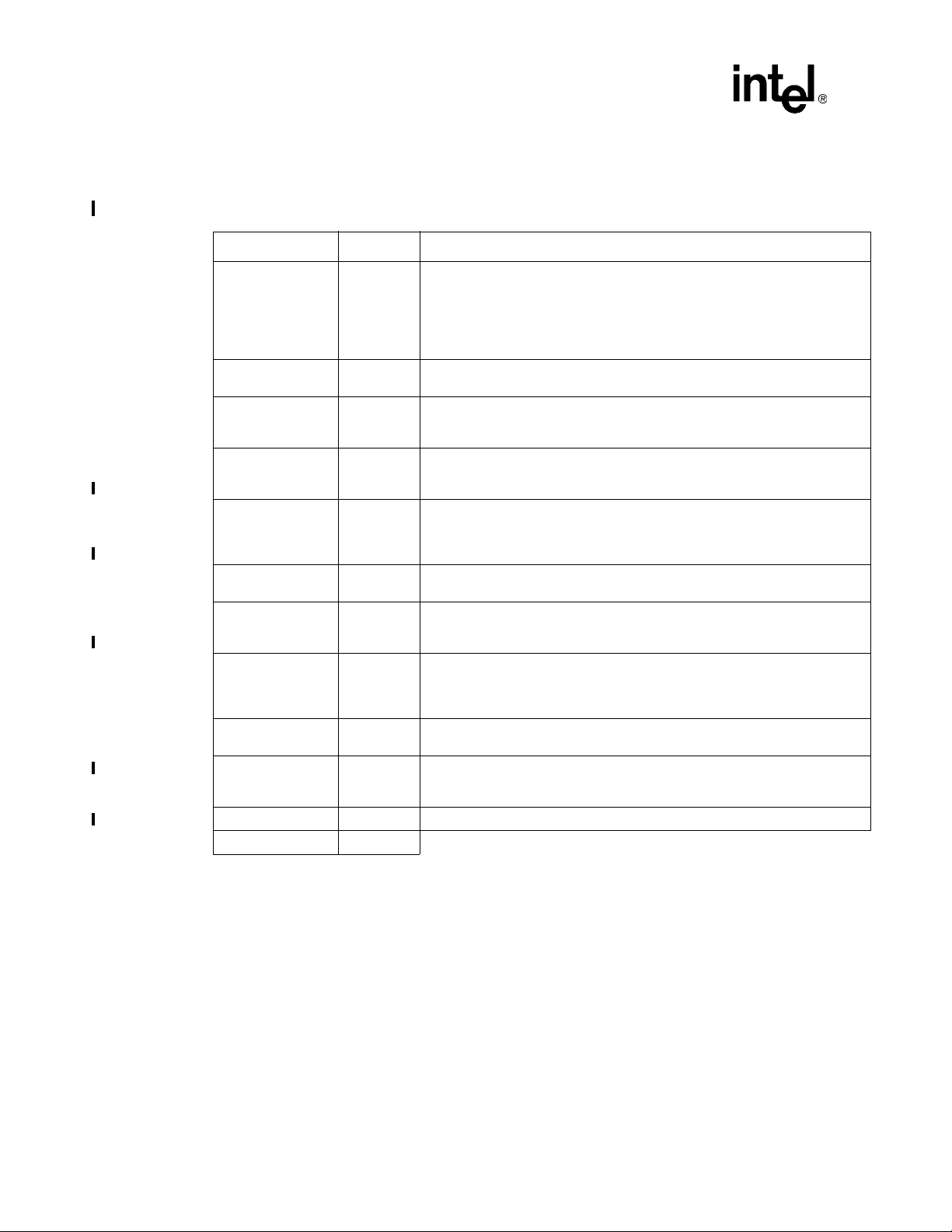

Table 1. ODT Signals

A_ACK64# B_ACK64#

A_AD[63:32] B_AD[63:32]

A_CBE#[7:4] B_CBE#[7:4]

A_DEVSEL# B_DEVSEL#

A_FRAME# B_FRAME#

A_GNT#[5:0] B_GNT#[5:0]

A_IRDY# B_IRDY#

A_PAR B_PAR

A_PAR64 B_PAR64

A_PERR# B_PERR#

A_LOCK# B_LOCK#

A_REQ#[5:0] B_REQ#[5:0]

A_REQ64# B_REQ64#

A_SERR# B_SERR#

A_STOP# B_STOP#

A_TRDY# B_TRDY#

A_INTA# B_INTA#

A_INTB# B_INTB#

A_INTC# B_INTC#

A_INTD# B_INTD#

TCK

TDI

TDO

TMS

14 Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual

Page 15

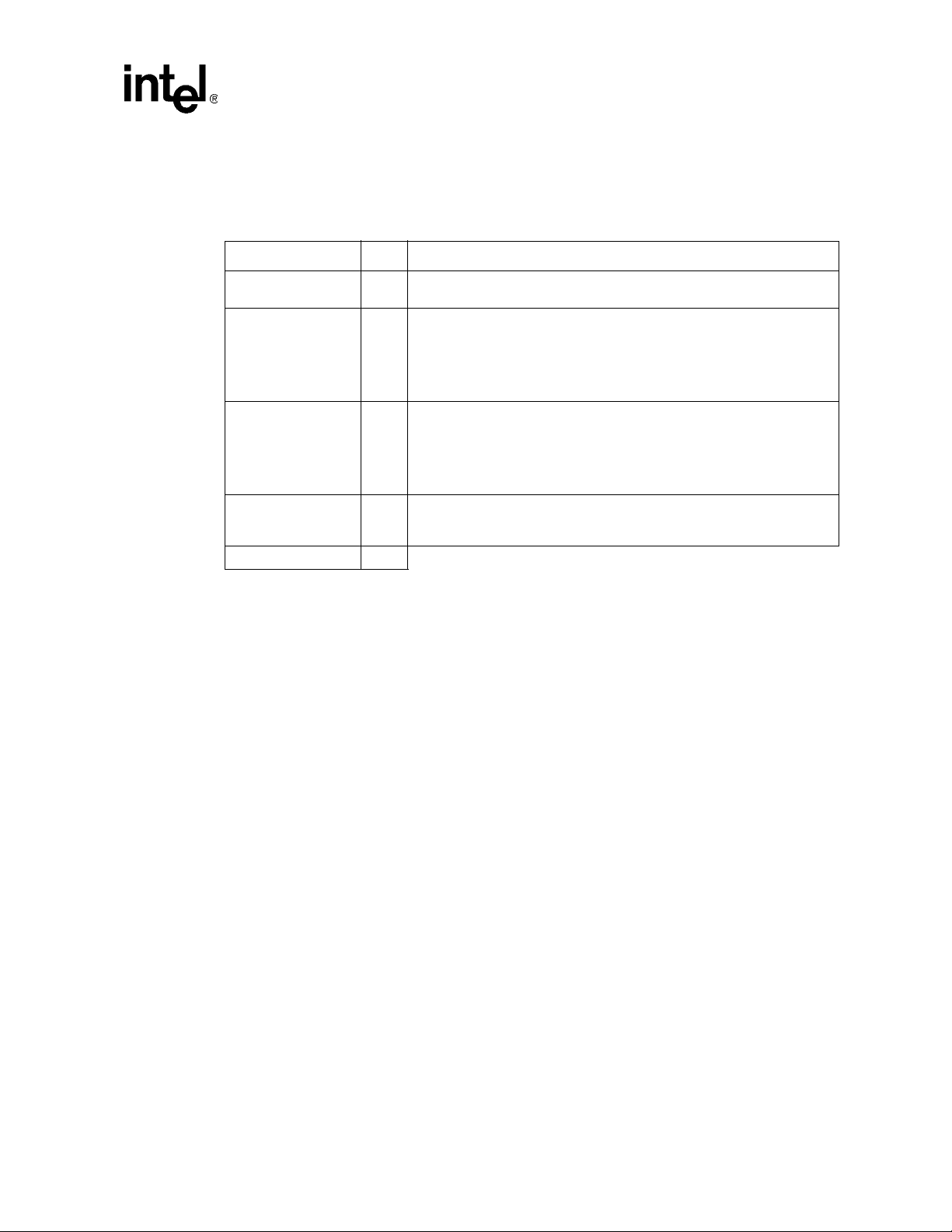

2.2 PCI Express* Interface

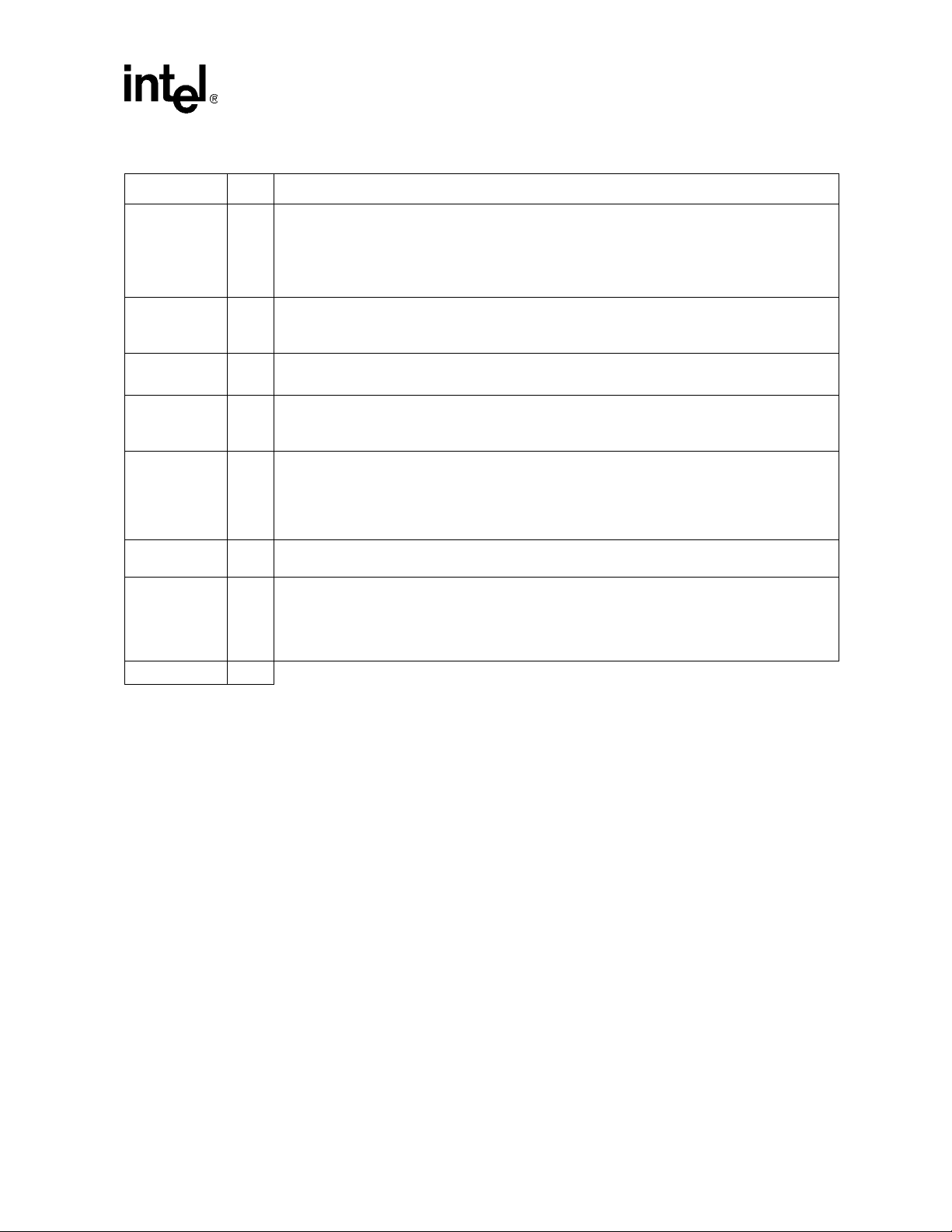

T able 2. PCI Express* Interface Pins

Signal I/O Description

Signal Description

REFCLKp/

REFCLKn

PETp[7:0]/

PETn[7:0]

PERp[7:0]/

PERn[7:0]

PE_RCOMP[1:0] I

Total 36

I PCI Express* Reference Clocks: 100 MHz differential clock pair

PCI Express* Serial Data Transmit: PCI Express* differential data transmit

signals

X8 Mode: All PETp[7:0]/PETn[7:0] are used.

O

X4 Mode: Only PETp[3:0]/PETn[3:0] are used.

X1 Mode: Either PETp[0]/PETn[0] is used or PETp[7]/PETn[7] is used.

PCI Express* Serial Data Receive: PCI Express* differential data receive

signals

X8 Mode: All PERp[7:0]/PERn[7:0] are used.

I

X4 Mode: Only PERp[3:0]/PERn[3:0] are used.

X1 Mode: Either PERp[0]/PERn[0] is used or PERp[7]/PERn[7] is used.

PCI Express* Compensation Inputs: Analog signals. Connect to a

24.9 Ω ±1% pull-up resistor to 1.5 V. A single resistor can be used for both

signals.

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual 15

Page 16

Signal Description

2.3 PCI Bus Interface (Two Instances)

Each interface is marked by either the letter “A” or “B” to signify the interface. For example,

A_AD refers to the AD bus on PCI bus A, and B_AD refers to the AD bus on PCI bus B. For pin

names described in the following sections, an “X” in the name indicates either A or B, for the PCI

bus A and PCI bus B sides, respectively. For example, “X_PAR” indicates A _PAR on the PCI bus

A and B_PAR on the PCI bus B.

Ta ble 3. PCI Interface Pins (Sheet 1 of 2)

Signal I/O Description

PCI Address/Data: These signals are a multiplexed address and data bus. During the address

A_AD[31:0]

B_AD[31:0]

A_C/BE#[3:0]

B_C/BE#[3:0]

A_PAR

B_PAR

A_DEVSEL#

B_DEVSEL#

A_FRAME#

B_FRAME#

A_IRDY#

B_IRDY#

A_TRDY#

B_TRDY#

A_STOP#

B_STOP#

phase or phases of a transaction, the initiator drives a physical address on X_AD[31:0]. During the

I/O

data phases of a transaction, the initiator drives write data, or the ta rget drives read data.

No external pull-up resistors are required on the system board for these signals.

Bus Command and Byte Enables: These signals are a multiplexed command field and byte enable

field. During the address phase or phases of a transaction, the initiator drives the transaction type on

C/BE#[3:0]. When there are two address phases, the first address phase carries the dual address

I/O

command and the second address phase carries the transaction type. For both read and write

transactions, the initiator drives byte enables on C/BE#[3:0] during the data phases.

No external pull-up resistors are required on the system board for these signals.

Parity: Even parity is calculated on 36 bits—AD[31:0] plus C/BE[3:0]#. It is calculated on all 36 bits

regardless of the valid byte enables. It is generated for address and data phases. It is driven

identically to the AD[31:0] lines, except it is delayed by exactly one PCI clock.

It is an output in the following cases:

• During the address phase for all transactions initiated by the Intel

I/O

I/O

I/O

I/O

I/O

I/O

Bridge

• During all data phases when the 41210 is the initiator of a PCI write transaction

• When the 41210 is the target of a read transaction

The 41210 checks parity when it is the initiator of PCI read transactions and when it is the target of

PCI write transactions.

No external pull-up resistors are required on the system board for these signals.

Device Select: The bridge asserts DEVSEL# to claim a PCI transaction. As a target, the 41210

asserts DEVSEL# when a PCI master peripheral attempts to access an address destined for PCI

Express*. As an initiator, DEVSEL# indicates the response to a transaction initiated by the 41210 on

the PCI bus. DEVSEL# is tristated from the leading edge of PCIRST#. DEVSEL# remains tristated by

the 41210 until driven as a target.

No external pull-up resistors are required on the system board for these signals.

Frame: FRAME# is driven by the initiator to indicate the beginning and duration of an access. While

FRAME# is asserted, data transfers continue. When FRAME# is deasserted the transaction is in the

final data phase.

No external pull-up resistors are required on the system board for these signals.

Initiator Ready: IRDY# indicates the ability of the initiator to complete the current data phase of the

transaction. A data phase is completed when both IRDY# and TRDY# are sampled asserted.

No external pull-up resistors are required on the system board for these signals.

Target Ready: TRDY# indicates the ability of the target to complete the current data phase of the

transaction. A data phase is completed when both TRDY# and IRDY# are sampled asserted. TRDY#

is tristated from the leading edge of RST#. TRDY# remains tristated by the 41210 until driven as a

target.

No external pull-up resistors are required on the system board for these signals.

Stop: This bit indicates that the target is requesting an initiator to stop the current transaction.

No external pull-up resistors are required on the system board for these signals.

®

41210 Serial to Parallel PCI

16 Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual

Page 17

T a ble 3. PCI Interface Pins (Sheet 2 of 2)

Signal I/O Description

Parity Error: PERR# is driven by an external PCI device when it receives data that has a parity error.

A_PERR#

B_PERR#

A_SERR#

B_SERR#

A_REQ#[5:0]

B_REQ#[5:0]

A_GNT#[5:0]

B_GNT#[5:0]

A_M66EN

B_M66EN

A_PCIXCAP

B_PCIXCAP

A_LOCK#

B_LOCK#

Total 118

PERR# is driven by the 41210 in the following cases:

• when the 41210, as an initiator, detects a parity error during a read transaction

I/O

• when the 41210, as a target, detects a parity error during a write transaction

No external pull-up resistors are required on the system board for these signals.

System Error: The 41210 samples SERR# as an input and conditionally forwards it to the PCI

Express*.

I

No external pull-up resistors are required on the system board for these signals.

PCI Requests: REQ# receives request inputs into the internal arbiter.

I

No external pull-up resistors are required on the system board for these signals.

PCI Grants: GNT# is the bus grant output corresponding to request input bits[5:0] from the internal

arbiter. GNT# indicates that an initiator can start a transaction on the PCI bus.

O

No external pull-up resistors are required on the system board for these signals.

66 MHz Enable: M66EN is an input signal from the PCI bus that indicates the speed of the PCI bus.

When it is high, the bus speed is 66 MHz. When it is low, the bus speed is 33 MHz. This signal is

used to generate an appropriate clock (33 or 66 MHz) on the PCI bus.

I/OD

To tie high: Use an approximately 8.2 KΩ resistor to pull to VCC33.

To tie low: Pull down to ground.

PCI-X Capable: PCIXCAP indicates whether all devices on the PCI bus are PCI-X devices, so that

I

the 41210 can switch into PCI-X mode. Use an approximately 8.2 KΩ resistor to pull to VCC33.

PCI Lock: LOCK# indicates an exclusive bus operation and may require multiple transactions to

complete. This signal is an output from the bridge when it is initiating exclusive transactions on PCI.

LOCK# is ignored when PCI masters are granted the bus. Locked transaction do not propagate

O

upstream.

No external pull-up resistors are required on the system board for these signals.

Signal Description

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual 17

Page 18

Signal Description

2.4 PCI Bus Interface 64-Bit Extension (Two Interfaces)

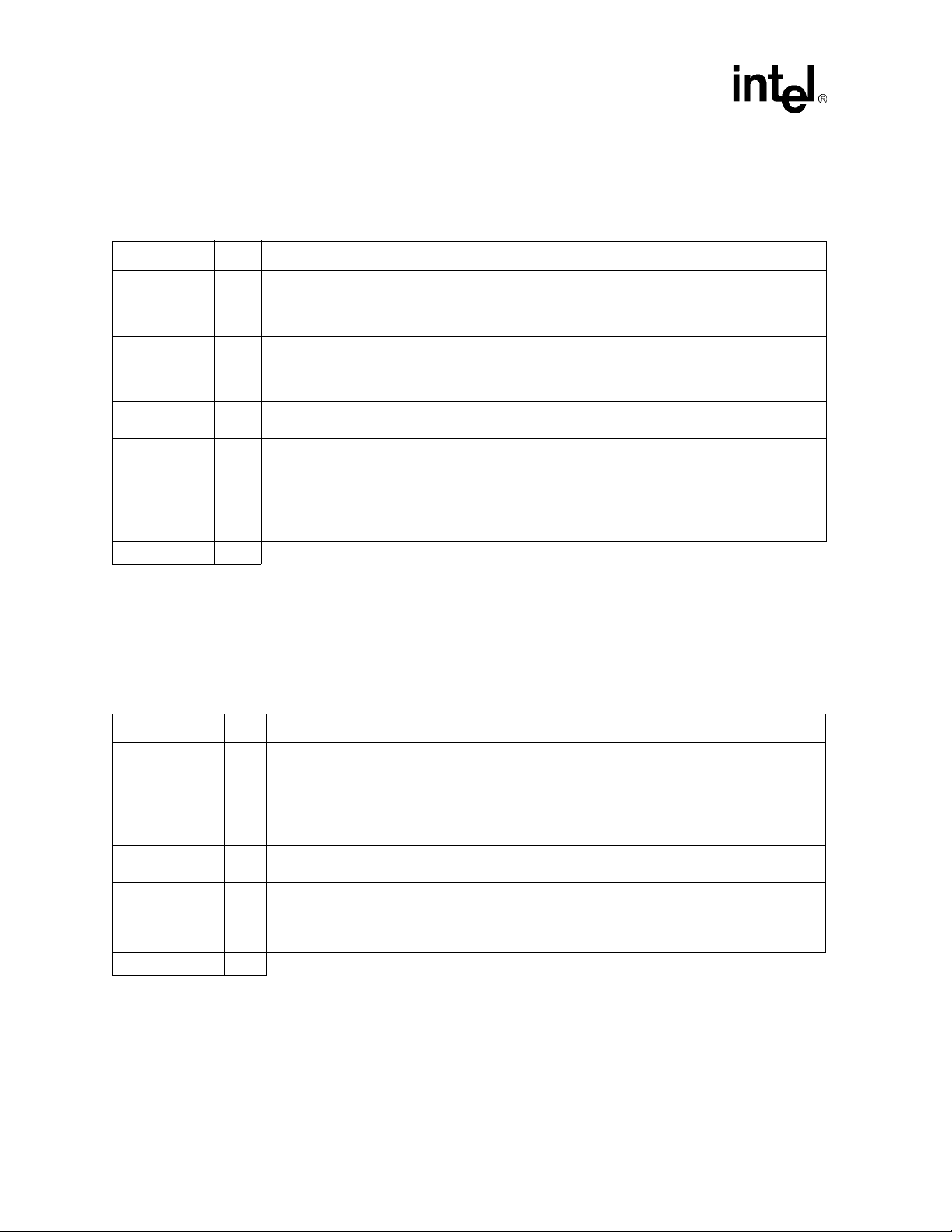

Table 4. PCI Interface Pins: 64-Bit Extensions

Signal I/O Description

A_AD[63:32]

B_AD[63:32]

A_C/BE#[7:4]

B_C/BE#[7:4]

A_PAR64

B_PAR64

A_REQ64#

B_REQ64#

A_ACK64#

B_ACK64#

PCI Address/Data: The AD signals are a multiplexed address and data bus. This bus provides an

additional 32 bits to the PCI bus. During the data phases of a transaction, the initiator drives the

I/O

upper 32 bits of 64-bit write data, or the target drives the upper 32 bits of 64-bit read data, when

REQ64# and ACK64# are both asserted.

Bus Command and Byte enables upper 4 bits: The C/BE# signals are a multiplexed command

field and byte enable field. For both reads and write transactions, the initiator drives byte enables for

I/O

the AD[63:32] data bits on C/BE[7:4] during the data phases when REQ64# and ACK64# are both

asserted.

PCI interface upper 32 bits parity: PAR64 carries the even parity of the 36 bits of AD[63:32] and

I/O

C/BE#[7:4] for both address and data phases.

PCI interface request 64-bit transfer: REQ64# is asserted by the initiator to indicate that the

I/O

initiator is requesting a 64-bit data transfer. REQ64# has the same timing as FRAME#. When the

41210 is the initiator, this signal is an output. When the 41210 is the target, this signal is an input.

PCI interface acknowledge 64-bit transfer: ACK64# is asserted by the target only when REQ64# is

I/O

asserted by the initiator, to indicate the target ability to transfer data using 64 bits. ACK64# has the

same timing as DEVSEL#.

Total 78

2.5 PCI Bus Interface Clocks and, Reset and Power Management (Two Interfaces)

T able 5. PCI Clock and Reset Pins

Signal I/O Description

A_CLKO[6:0]

B_CLKO[6:0]

A_CLKIN

B_CLKIN

A_RST#

B_RST#

A_PME#

B_PME#

PCI Clock Output: CLKO is the 33/66/100/133 MHz clock for a PCI device. X_CLK[6] must be

connected to the respective X_CLKIN input for feeding the PCI interface logic. Unused clock outputs

O

may be disabled via the “Offset 43h: PCLKC—PCI Clock Control” register and should be treated as

no connects on the board.

PCI Clock In : CLKIN is the PCI clock feedback input. CLKIN must be connected to the

I

corresponding X_CLKO[6] through a 22 Ω ± 1% series resistor.

O PCI Reset: The bridge asserts RST# to reset devices that reside on the secondary PCI bus.

PCI Power Management Event: PME# is the PCI bus power management event signal. PME# is a

shared open-drain input from all the PCI cards on the corresponding PCI bus segment. PME# is a

I

level-sensitive signal that is converted to a PME event on PCI Express*.

PME# does not have on-die 8.3 KΩ pull-up. This pull-up must be provided externally.

Total 20

18 Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual

Page 19

2.6 Interrupt Interface (Two Interfaces)

This section lists the interrupt interface signals. There are two sets of interrupt signals for the

standard INTA–INTD PCI signals.

T able 6. Interrupt Interface Pins

Signal I/O Description

A_INTA#

A_INTB#

A_INTC#

A_INTD#

B_INTA#

B_INTB#

B_INTC#

B_INTD#

Total 8

Interrupt Request Bu s: The interrupt lines from PCI interrupts INTA#–INTD# can be routed to

these interrupt lines.

I

Routing must be based on device number in accordance with the instructions given in Section 7,

“Interrupt Support” on page 53.

Signal Description

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual 19

Page 20

Signal Description

2.7 Reset Straps

The following signals are used for static configuration. These signals are all sampled on the rising

edge of PERST#.

Table 7. Reset Strap Pins

Signal I/O Description

PCI-X 133 MHz Enable: The 133EN pin, when high, allows the PCI-X segment to run at 133 MHz

A_133EN

B_133EN

A_STRAP[6:0]

B_STRAP[6:0]

when X_PCIXCAP is sampled high. When 133EN is low, the PCI-X segment runs only at 100MHz

when X_PCIXCAP is sampled high.

I

To tie high: Use an approximately 8.2 KΩ resistor to pull to VCC33.

To tie low: Pull down to ground.

Internal Test Modes: For normal operation, X_STRAP[6] and [2:0] must be pulled low and

X_STRAP[5:3] must be pulled high, as shown in the table below.

X_STRAP Logic Level

00

10

I

20

31

41

51

60

A_TEST[2:1]

B_TEST{2:1]

CFGRETRY I

Total

To tie high: Use approximately an 8.2 KΩ resistor to pull up to VCC33.

To tie low: Pull down to VSS.

Internal Test Modes: These straps must be pulled high to VCC33. Use an approximately 8.2 KΩ

I

resistor to pull up to VCC33.

Configuration Retry: This pin, when sampled high, sets the Configuration Cycle Retry Bit (bit 3) in

the Bridge Initialization Register (“Offset FCh: BINIT— Bridge Initialization Register” on page 104).

When no local initialization is needed, this pin must be pulled low to VSS.

See Section 9, “Local Initialization” for additional details.

19

20 Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual

Page 21

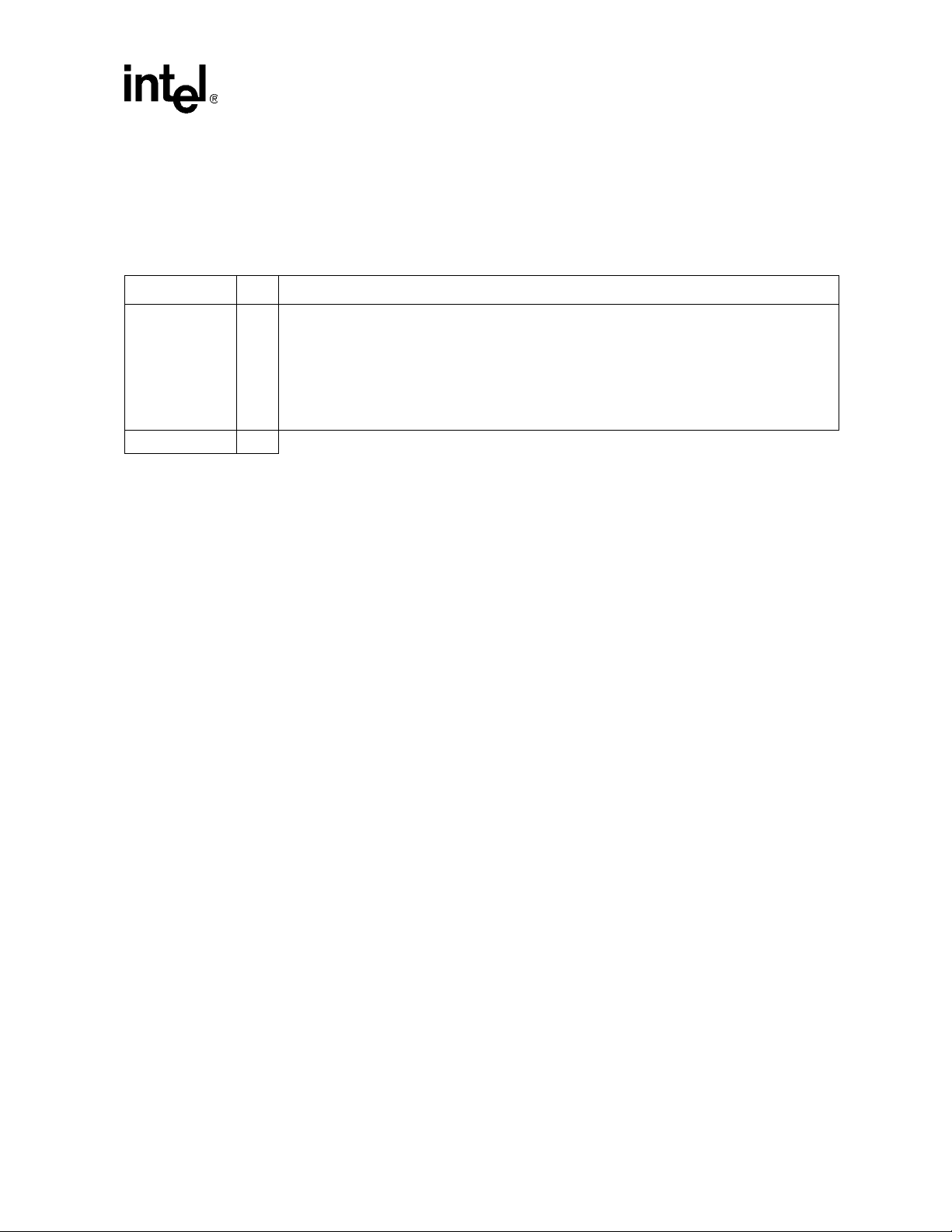

2.8 SMBus Interface

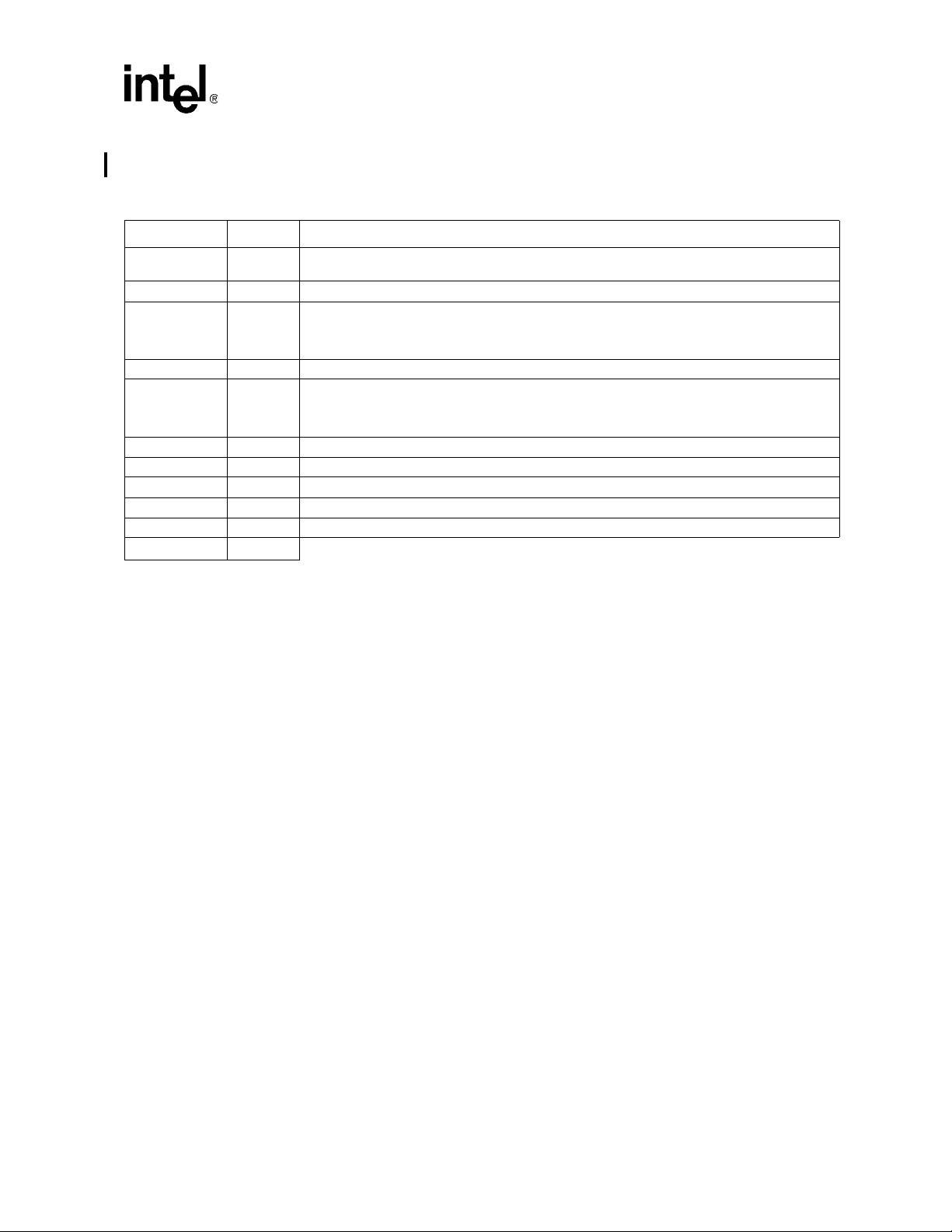

Ta ble 8. SMBus Interface Pins

Signal I/O Description

SMBCLK I/OD SMBus Clock: This signal must be pulled to 3.3 V through an 8.2 KΩ resistor.

SMBDAT I/OD SMBus Data: This signal must be pulled to 3.3 V through an 8.2 KΩ resistor.

SMBus Addressing Straps: These straps set the SMBus address for the 41210 Bridge. The address

is determined as indicated below:

•Bit[7]1

•Bit[6]1

SMBUS[5]

SMBUS[3:1]

Total

• Bit[5] SMBUS[5]

I

•Bit[4]0

• Bit[3] SMBUS[3]

• Bit[2] SMBUS[2]

• Bit[1] SMBUS[1]

These signals (bits[5], [3:1]) must be pulled up to 3.3 V or down to ground. Sampled at the rising edge

of PERST#.

6

Signal Description

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual 21

Page 22

Signal Description

2.9 Miscellaneous Pins

Table 9. Miscellaneous Pins

Signal I/O Description

Configuration Reset : This signal is asserted low when ever the bridge goes

through a fundemental reset (PERST#, RSTIN#, or PCI Express Reset). This

CFGRST# O

PERST# I

RSTIN# I

TCK I

TDI I

TDO O

TMS I

TRST# I

RESERVED[8:1] I

NC[19:18], NC[16:1]

A_NC[10:1]

B_NC[10:1]

NC[17] O This signal requires an external pull-up, 8.2K ohm to 3.3V

O No Connect: (39 pins) These output pins should be left floating

Total

signal should be used to indicate when the local initialization methods should be

executed.

Refer to the Intel® 41210 Serial to Parallel PCI Bridge Design Guide for more

information.

PCI Express Fundamental Reset: When low, asynchronously resets the

internal logic (including sticky bits).

Reset In: When Asserted, this signal asynchronously resets the internal logic

and asserts X_RST# output for both PCI interfaces. This signal should be pulled

high for adapter card usage.

TAP Clock In: This is the input clock to the JTAG TAP controller. Acceptable

frequency is 0-16MHz

If not utilizing JTAG, this signal can be left as a no connect.

Test Data In: Th is is the serial data input to the JTAG BSCAN shift register

chain and to the JT AG BSCAN control logic. This is latched in on the rising edge

of TCK.

If not utilizing JTAG, this signal can be left as a no connect.

Test Data Output: This is the serial data output from the JTAG BS CAN logic

If not utilizing JTAG, this signal can be left as a no connect.

Test Mode Select: This signal controls the T A P controller state machine to

move to different states and is sampled on the rising edge of TCK.

If not utilizing JTAG, this signal can be left as a no connect.

Test Reset In: This signal is used to asynchronously reset the JTAG BSCAN

logic.

If not utilizing JTAG, connect this signal to ground through a 1KΩ pull-down

resistor.

Reserved: (8 pins) These input pins should be pulled low

Use an approximately 8.2KΩ resistor to pull-down to ground.

57

22 Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual

Page 23

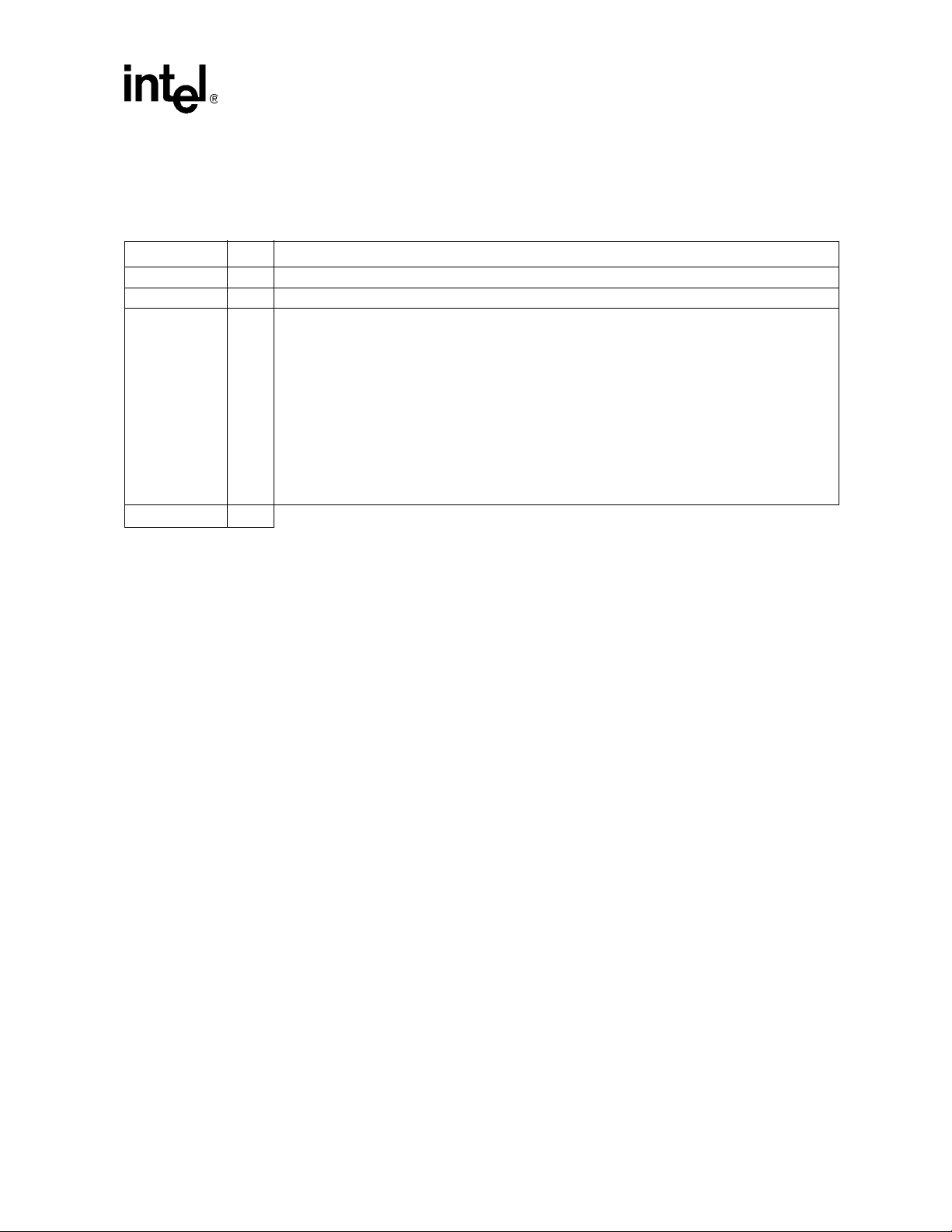

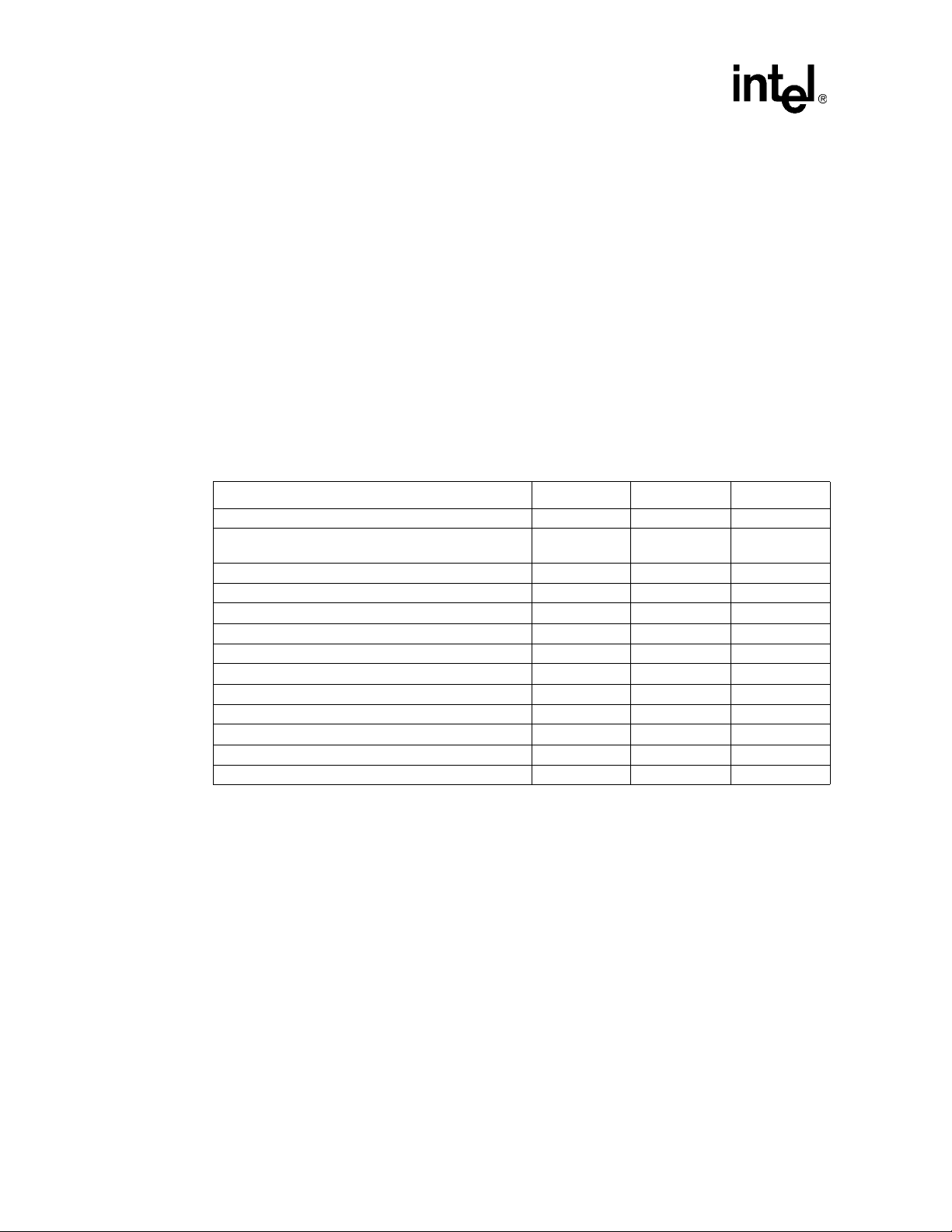

2.10 Voltage Pins

Table 10. Miscellaneous Pins

Signal Number Description

RCOMP 1

VCC 36 1.5 V Core Voltage: 1.5 V ± 5%.

VCCAPE 1

VCCAPCI[2:0] 3 Analog PCI Voltages: 1.5 V ±3%

VCCBGPE 1

VSSBGPE 1 Analog Band-gap Ground

VCCPE 9 1.5 V PCI Express* Voltage: 1.5 V ±3%

VCC33 30 3.3 V PCI I/O Voltage: 3. 3V ± 5%.

VSS 142 Ground: Ground for all voltage rails

VSSAPE 1 Analog PC I Express* Ground

Total

225

Analog Compensation Pin: RCOMP is the analog compensation pin for PCI. Pull down to

ground through a 100 Ω ±1% resistor.

Analog PCI Express* Voltage:

• DC: 1.5 V ± 3%

• AC: ±5 mV above 1 M Hz at package pin under DC load conditions

Analog Band-gap Voltage:

• DC: 2.5 V ±3%

• AC: ±10 mV above 1 MHz at package pin under DC load conditions

Signal Description

§ §

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual 23

Page 24

Signal Description

THIS PAGE INTENTIONALLY LEFT BLANK

24 Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual

Page 25

PCI-X Interface

PCI-X Interface 3

This section deals with the specifics of the operation and transaction flow details of the PCI

interfaces.

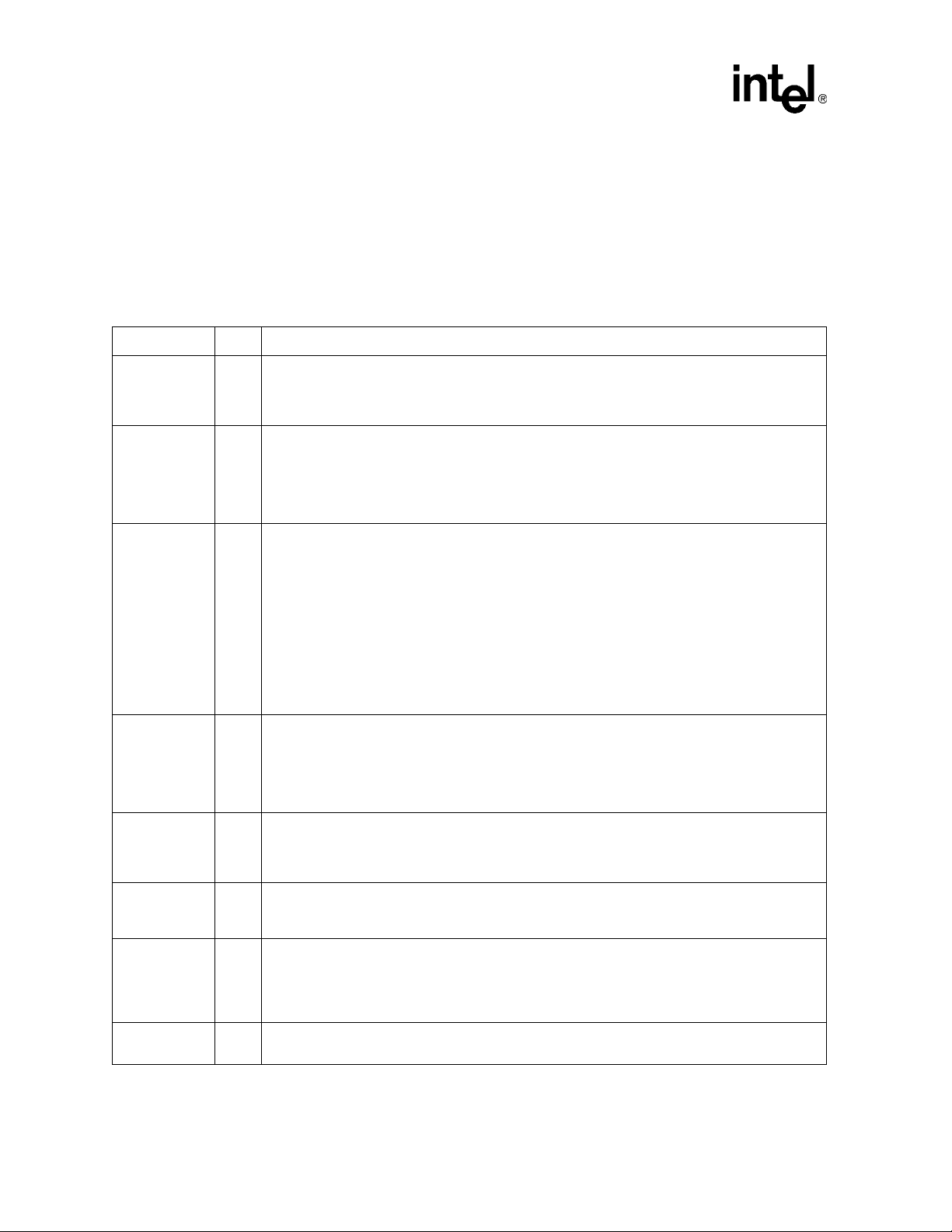

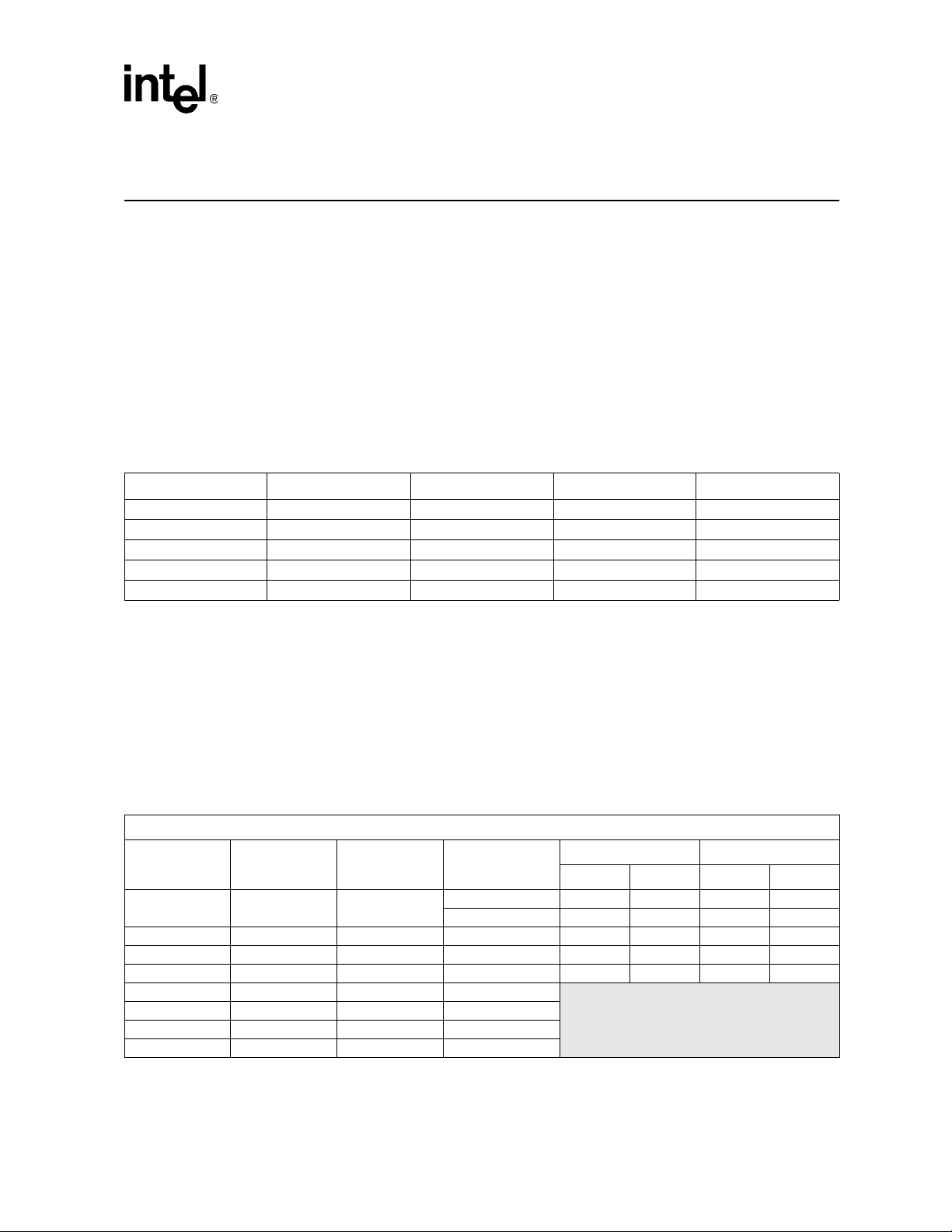

3.1 Initialization

The Intel® 41210 Serial to Parallel PCI Bridge (also called the 41210 Bridge or the 41210) is the

source bridge for the PCI bus and senses the X_M66EN, X_133EN, and X_PCIXCAP pins to

decide the mode and frequency of operation. Encoding on the M66EN and PCIXCAP pins along

with the PCI reset straps is shown below; these encodings identify the capabilities of the sy stem .

Table 11. PCI Mode Pin/Strap Encoding

X_133EN

Not connected – Not connected PCI-X 133 MHz

NOTE:

1. This pin is used by the board designer to run the PCI-X bus at 100 MHz even when all the PCI-X devices on the bus are

133 MHz capable, so as to accommodate the board routing limitation on frequency. Note that to accommodate running a

PCI-X bus at 66 MHz, when all cards are capable of 133 MHz, the motherboard has to drive the PCIXCAP pin to VCC33/2.

1

– Ground Ground PCI conventional 33 MHz

– Not connected Ground PCI conventional 66 MHz

– – Pull-down PCI-X 66 MHz

Ground – Not connected PCI-X 100 MHz

X_M66EN X_PCIXCAP PCI Bus Mode PCI Frequency

As soon as the 41210 identifies the capabilities of the PCI bus devices, it drives the initialization

pattern on the DEVSEL#, STOP#, TRDY#, FRAME#, and IRDY# pins as per Table 12 to initialize

the PCI bus devices to the proper mode and frequency. The patterns shown in Table 12 below are

stable on the rising edge of the A_RST# and B_RST# pins. Refer to the PCI-X Addendum to the

PCI Local Bus Specification, Revision 1.0b for details on the timing of these patterns with respect

to the A_RST# and B_RST# pins.

Table 12. PCI-X Initialization Pattern

FRAME# and IRDY# are Deasserted

DEVSEL# STOP# TRDY# Mode

Deasserted Deasserted Deas serted

Deasserted Deasserted Asserted PCI-X 15 20 50 66

Deasserted Asserted Deasserted PCI-X 10 15 66 100

Deasserted Asserted A sserted PCI-X 7.5 10 100 133

Asserted Deasserted Deasserted PCI-X

Asserted Deasserted Asserted PCI-X

Asserted Asserted Deasserted PCI-X

Asserted Asserted Asserted PC I-X

PCI 33 30 — 0 33

PCI 66 15 30 33 66

Clock Period (ns) Clock Freq. (MHz)

Minimum Maximum Minimum Maximum

Reserved

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual 25

Page 26

PCI-X Interface

In summary:

• A_RST# and B_RST# are outputs from the 41210.

• PCI clocks are actively driven out from the 41210.

• The 41210 drives X_AD[31:0], X_BE[3:0], and X_PAR low during PCI bus reset.

• The 41210 drives X_REQ64# low during reset.

3.2 Transactions Supported

3.2.1 PCI Mode

Table 13 lists all the transactions supported by the 41210 on the PCI bus. The 41210 supports full

64-bit addressing upstream and downstream and can both generate and accept dual address cycles.

Table 13. PCI Transactions Supported

Transaction Encoding

Interrupt acknowledge 0000 No No

Special cycle (PCI Express* Type1-t o-PC I Special

Cycle)

I/O read 0010 Yes Yes

I/O write 0011 Yes Yes

Memory read 0110 Yes Yes

Memory write 0111 Yes Yes

Configuration read 1010 Y es Y es

Configuration write 1011 Yes Yes

Memory read multiple 1100 No Yes

Dual address cycle 1101 Yes Yes

Memory read line 1110 No Yes

Memory write and invalidate 1111 No Yes

LOCK transaction – Yes No

NOTES:

1. PCI command encodings that are not shown in this table are ignored.

2. I/O transactions are forwarded from PCI to PCI Express* only when the inbound I/O enable bit is set in the

“Offset FCh: BINIT —Bridge Initialization Register” on page 104

3. Upstream Type 0 configuration cycles to the 41210 Bridge’s own configuration space are supported.

1

0001 Yes No

Master Target

2

3

26 Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual

Page 27

3.2.2 PCI-X Mode

Table 14 lists the transactions that the 41210 supports when the PCI interface is in the PCI-X mode.

As a master, the 41210 supports the memory write block command for writes that are multiples of

cache-line.

Table 14. PCI-X Transactions Supported

Transaction Encoding

Interrupt acknowledge 0000 No No

Special cycle

(PCI Express* Type1-to-PCI Special Cycle)

I/O read 0010 Yes Yes

I/O write 0011 Yes Yes

Reserved 0100 No No

Reserved 0101 No No

Memory read DWORD 0110 Yes Yes

Memory wri te 0111 Yes Y es

Alias to memory read block 1000 No Yes

Alias to memory write block 1001 No Yes

Configuration read 1010 Yes Y es

Configuration write 1011 Yes Yes

Split completion 1 100 Yes Yes

Dual address cycle 1101 Yes Yes

Memory read block 1110 Yes Yes

Memory write block 1111 Yes Yes

LOCK transaction – Yes No

NOTES:

1. PCI command encodings that are not detailed in this table are ignored.

2. Upstream Type 0 configuration cycles to the bridge’s own configuration space are supported.

PCI-X Interface

1

0001 Yes No

Master Target

2

3.2.3 Read Transactions

3.2.3.1 Prefetchable

Any memory read line or memory read multiple commands on PCI that are decoded by the 41210

are prefetched on the PCI Express* interface. The prefetchability of a given PCI read request is

determined by the prefetch policy (PP) bits[55:54] of the “Offset 178h: PREFCTRL—Prefetch

Control Register” on page 119. The amount of data prefetched depends on the clock frequency,

x_REQ64#, and the command type. The 41210 does not prefetch past a 4 KB page boundary.

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual 27

Page 28

PCI-X Interface

3.2.3.2 Delayed

All memory read transactions are delayed read transactions. When the 41210 accepts a delayed

read request, it samples the address, command, and address parity. This information is entered into

the delayed transaction queue. When the 41210 is in PCI-X mode, transactions follow the split

transaction model of PCI-X. Read data returned from PCI Express* for an active delayed

transaction entry is forwarded to the PCI-X master as a split completion.

3.2.3.3 Inbound Read Request Algorithm

In PCI mode:

• Each read stream always gets exactly 1 K buffer—no more or no less.

• A maximum of four requests can be outstanding per stream/buffer.

• A maximum of eight requests can be outstanding per PCI segment.

In PCI-X mode:

• Each read stream requests and gets buffer in 512 B chunks.

• There is no limit on how many 512 B chunks a read stream can occupy.

• A maximum of four requests can be outstanding per stream.

• A maximum of one request can be outstanding per 512 B buffer.

• A maximum of eight requests can be outstanding per PCI-X segment.

3.2.4 Configuration Transactions

Type 0 configuration transactions are issued when the intended target resides on the same PCI bus

as the initiator. A Type 0 configuration transaction is identified by the configuration command and

by the lowest two bits of the address being set to 00b.

Type 1 configuration transactions are issued when the intended target resides on another PCI bus,

or when a special cycle is to be generated on another PCI bus. A Type 1 configuration transaction

is identified by the configuration command and by the lowest two bits of the address being set to

01b.

The register number is found in both Type 0 and Type 1 formats and gives the Dword address of

the configuration register to be accessed. The function number is also included in both Type 0 and

Type 1 formats and indicates which function of a multifunction device is to be accessed. For singlefunction devices, this value is not decoded. Type 1 configuration transaction addresses also include

a five-bit field designating the device number that identifies the device on the target PCI bus that is

to be accessed. In addition, the bus number in Type 1 transactions specifies the PCI bus to which

the transaction is targeted.

28 Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual

Page 29

3.2.5 LOCK Cycles

A lock is established when all the following conditions are true:

• A PCI Express* device initiates a Memory Read Lock (MRdLk) request to read from a target

PCI device.

• LOCK# is asserted on the PCI bus.

• The target PCI device responds with a TRDY#.

The bus is unlocked when the Unlock Message is received on PCI Express*.

When the PCI bus is locked, all upstream mem ory transactions fr om that bus are retried. T he 41210

upstream read prefetch engine stops issuin g any mo re req uests o n the PCI Ex pres s* bus. However ,

note that the 41210 accepts read completions for upstream read requests that were issue d before the

lock was established on the PCI bus when they return on PCI Express*.

As soon as the bus is locked, any PCI Express* cycle to PCI is driven with the LOCK# pin

asserted, even when that particular cycle is not locked. This is not expected to occur, because under

lock, peer-to-peer accesses are internally blocked and the upstream component must not send any

non-locked transactions downstream.

When one PCI bus segment is locked, the other is still free to accept cycles (in other words, that

bus is not locked. However, these transactions are not allowed to proceed on PCI Express* or the

locked PCI segment). Therefore, as soon as the PCI bus is locked, additional cycles d o not pr oceed

onto PCI Express* from the non-locked PCI segment.

PCI-X Interface

During the LOCK sequence, when the initial locked read command results in a master or target abort

(either on the PCI bus or the internal switch interconnect), the 41210 does not esta blish lo ck, and i t

sends a completion packet on PCI Express* with an error status. In case of a subsequent memory read

or memory write receiving a target or master abort during a LOCK sequence, the 41210 unlocks only

after the unlock message is received on PCI Express*.

• Downstrea m LOCK is supported by th e 41210.

• Upstream LOCK transactions are treated with the LOCK signal ignored.

See Table 15 below for a summary of the 41210 responses to LOCK transactions.

Table 15. LOCK Transaction Handling in the Intel

End Point

PCI – Forward to PCI w/ LOCK#

PCI Express* Ignore

NOTE:

1. Transaction is treated as if it is a normal read or write transaction.

®

41210 Serial to Parallel PCI Bridge

Source

PCI PCI Express*

1

–

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual 29

Page 30

PCI-X Interface

3.2.6 Decoding

In the PCI mode, the 41210 supports only the linear i ncrement address mode for bursting memory

transfers (indicated when the lowest two address bits are equal to 0). When either of these address bits

is non-zero, the 41210 disconnects the transaction after the first data transfer. The 41210 decodes all

PCI cycles with medium DEVSEL# timing. In the PCI-X mode, 41210 always decodes as a Type A

target. Also, in PCI-X mode, the 41210 decodes split completions using the primary bus number

field.

Refer to Section 5, “Addressing” on page 41 for a general description of addressing and decoding.

3.2.7 Transaction Termination

3.2.7.1 PCI Mode Transaction Termination

• Normal Termination

As a PCI master, the 41210 uses normal termination when DEVSEL# is returned by the target

within five clock cycles of FRAME# assertion. It terminates a transaction when one of the

following conditions are met:

— All write data for a write transaction are transferred from the 41210 data buffers to the

target (the 41210 does not generate fast back-to-back transactions).

— All read data for a read transaction are transferred from the target to the 41210.

— The master latency timer expires and the bus grant of the 41210 is de-asserted.

• Master Abort

When the transaction initiated by the 41210 does not receive a DEVSEL# response within five

clocks of FRAME# assertion, the 41210 terminates the transaction with a master abort. The

41210 sets the received master abort bit in the secondary status register. Read requests

(configuration, I/O, memory) that receive master abort termination are sent back to PCI

Express*/peer PCI with a master abort status.

Note that when the 41210 performs a Type 1 to special cycle translation, a master abort is the

expected termination for the special cycle on the target bus. In this case, the master abort

received bit is not set, and the Type 1 configuration transaction is disconnected after the first

data phase.

• Tar g et Abort

When the 41210 receives a target abort, and the cycle requires completion on PCI Express*,

the bridge returns the target abort status to PCI Express*. The 41210 sets the received target

abort status bit in the secondary status register for all target aborts it receives on the PCI bus.

Tar get abort can occur dur ing any data phase of a PCI-X transaction. A read com pletion packet

to PCI Express*/peer PCI, incurring a target abort in the middle of the packet, returns valid

data to the point of target abort and a target abort completion status for the reminder.

• Disconnect and Retry

When the 41210 receives a disconnect response from a target, it re-initiates the transfer with

the remaining length. When the 41210 receives a retry , it waits at least two PCI clocks before it

retries the transaction. When the retried transaction is a write, the 41210 retries the write until

it completes normally or with a target or master abort. When the retried transaction is a

delayed read or delayed write transaction, the 41210 allows memory reads and writes to pass

the transaction. Refer to Section 6, “Transaction Orderin g” on page51 for details on the k i nds

30 Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual

Page 31

PCI-X Interface

of reordering allowed. Retry is not considered an error condition, so there is no error logging

or reporting done on a retry.

• The 41210 terminates a transaction with retry to an initiator when one of the following

conditions is met:

— The 41210 receives a new memory read transaction, and the 41210 delayed transaction

queue is full.

— The 41210 receives a memory read that has already been queued, but has not completed

on PCI Express*.

— The 41210 receives a memory read that has been queued and completed on PCI Expres s*,

but ordering rules require a downstream posted write to complete ahead of it.

— A LOCK transaction has been established from PCI Express*-to-PCI.

— The 41210 receives a memory write transaction, and the 41210 has no fr ee buf fer sp ace to

accept the write.

— A memory write transaction is from a master other than the master that was previously

retried (starvation prevention mechanis m).

• The 41210 disconnects an initiator when one of the following conditions is met:

— The 41210 cannot accept any more write data.

— The 41210 has no more read data to deliver.

— The memory address is non-linear.

— The inverse decode window ends.

• The 41210 returns a target abort to PCI when the following condition is met.

— The cycle master aborted, or the target aborted on PCI Express*/peer PCI.

Intel® 41210 Serial to Parallel PCI Bridge Developer’s Manual 31

Page 32

PCI-X Interface

3.2.7.2 PCI-X Mode Transaction Termination

• Initiator Disconnect or Satisfaction of Byte Count

As a PCI-X master, the 41210 uses normal termination (initiator disconnect or satisfaction of

byte count) if DEVSEL# is returned by the target within six clock cycles after address phase.

The 41210 terminates a transaction when one of the following conditions are met:

— Initiator disconnect occurs when all write data indicated in the byte count of the write

transaction is transferred from the 41210 data buffers to the target. The 41210 does not

perform an initiator disconnect on a write before the byte count size has been satisfied.

— Initiator disconnect at the next ADB on a split read completion because the 41210 data

buffer has run dry.

— Initiator disconnect occurs at the next ADB when the master latency timer expires and the

bus grant of the 41210 is de-asserted.

• Master Abort Termination

When a transaction initiated by the 41210 does not receive a DEVSEL# response within six

clocks after address phase, the 41210 terminates the transaction with a master abort. The

41210 sets the received master abort bit in the secondary status register. Read requests

(configuration, I/O, memory) that receive master abort termination are sent back to PCI

Express*/peer PCI with a master abort status. Delayed write requests that receive master abort

are sent back to PCI Express* with a master abort status.

Note: When the 41210 performs a Type 1 to special cycle translation, a master abort is the expected

termination for the special cycle on the target bus. In this case, the master abort received bit is not

set, and the Type 1 configuration transaction is disconnected after the first data phase.

• Tar g et Abort

When the 41210 receives a target abort, and the cycle requires completion on PCI Express*,