Page 1

Intel® 82575EB Gigabit Ethernet

Controller Software Developer’s

Manual and EEPROM Guide

LAN Access Division

324632-003

Revision: 2.1

January 2011

Page 2

Intel® 82575EB Gigabit Ethernet Controller — Legal

Legal

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED,

BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED

IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL

DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR

WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT,

COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life

sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that

relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any

license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property

rights.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel

reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future

changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family,

not across different processor families. See http://www.intel.com/products/processor_number for details.

Hyper-Threading Technology requires a computer system with an Intel

HT Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software

you use. See http://www.intel.com/products/ht/Hyperthreading_more.htm for additional information.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by

calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Intel and Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other

countries.

*Other names and brands may be claimed as the property of others.

Copyright © 2006,2007,2008,2010.2011; Intel Corporation. All Rights Reserved.

®

Pentium® 4 processor supporting HT Technology and a

Intel® 82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

2 January 2011

Page 3

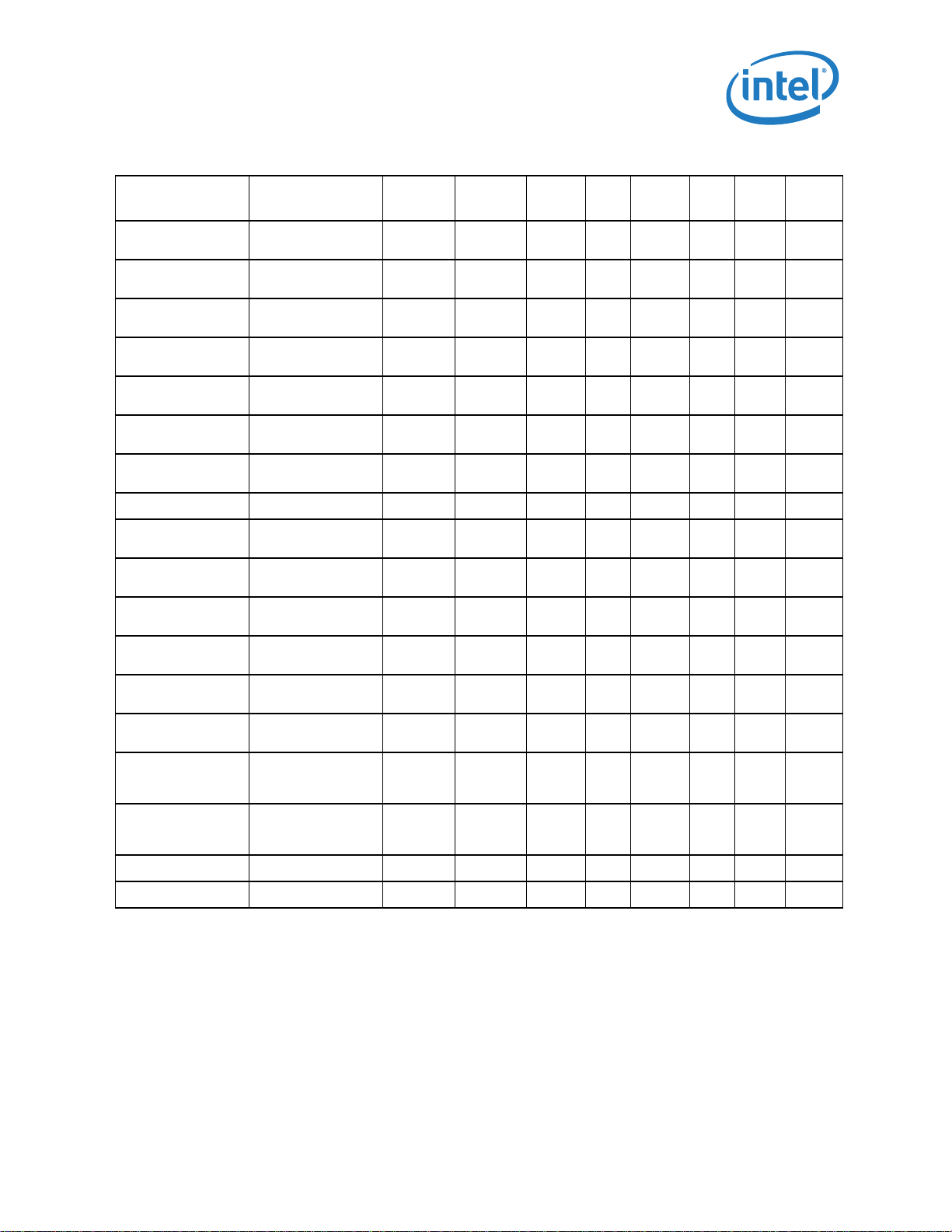

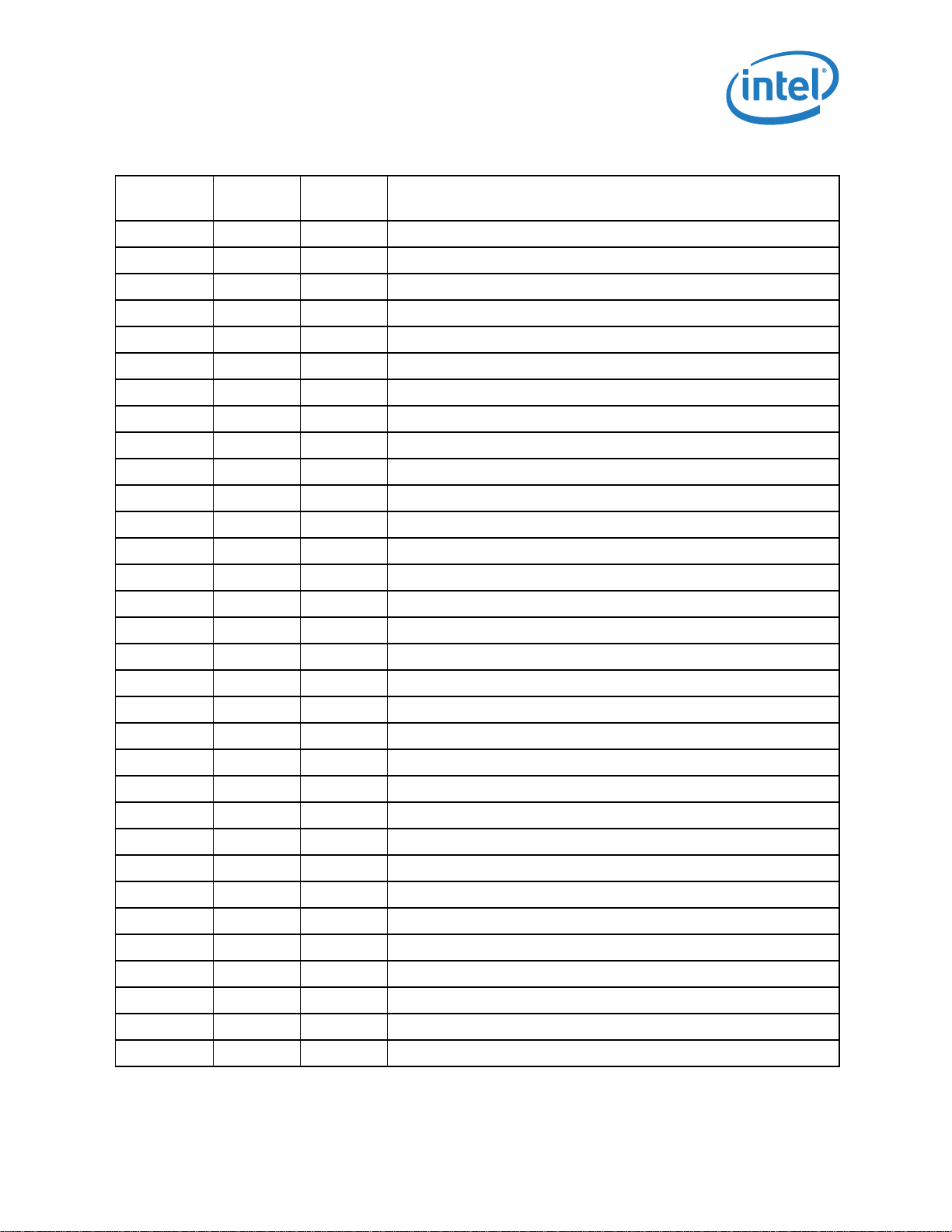

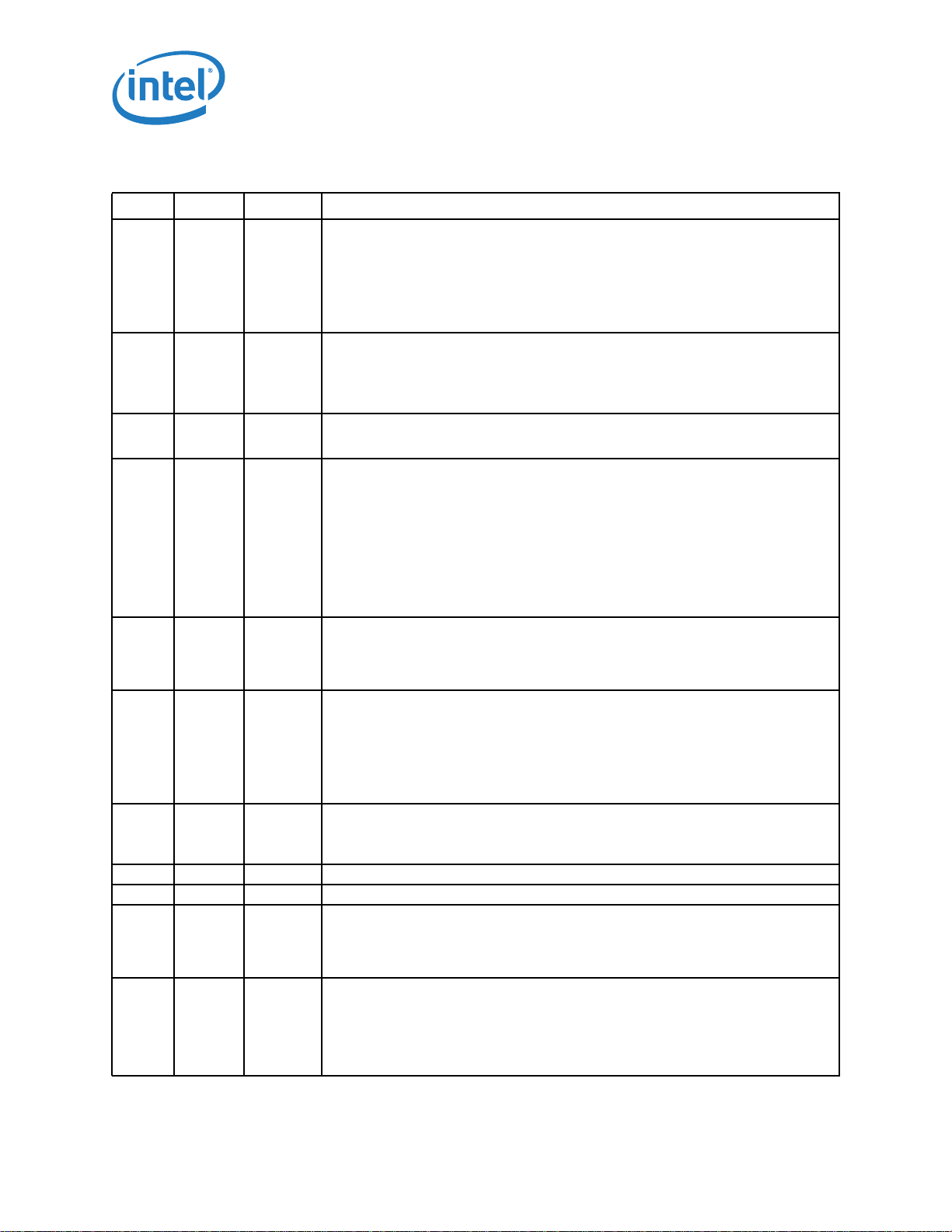

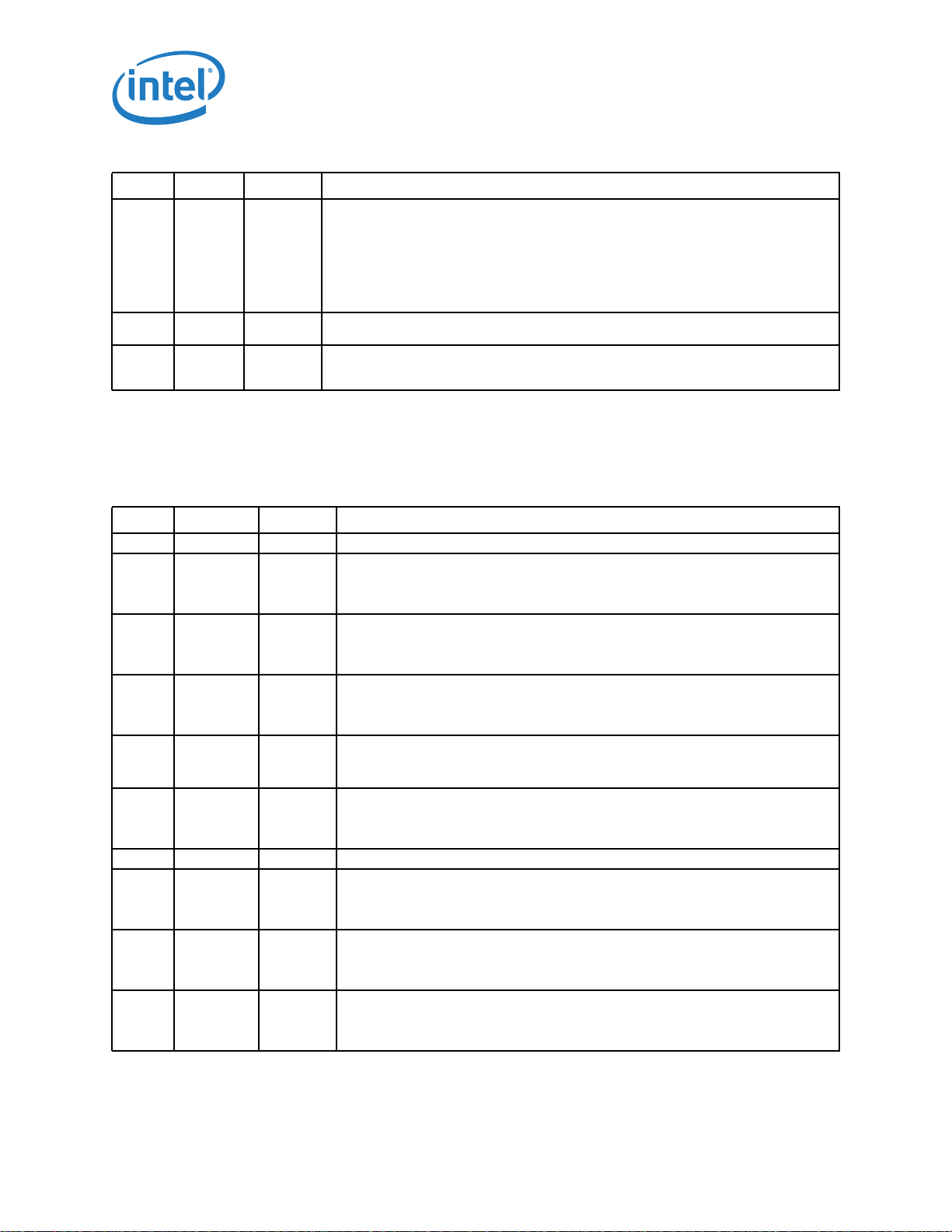

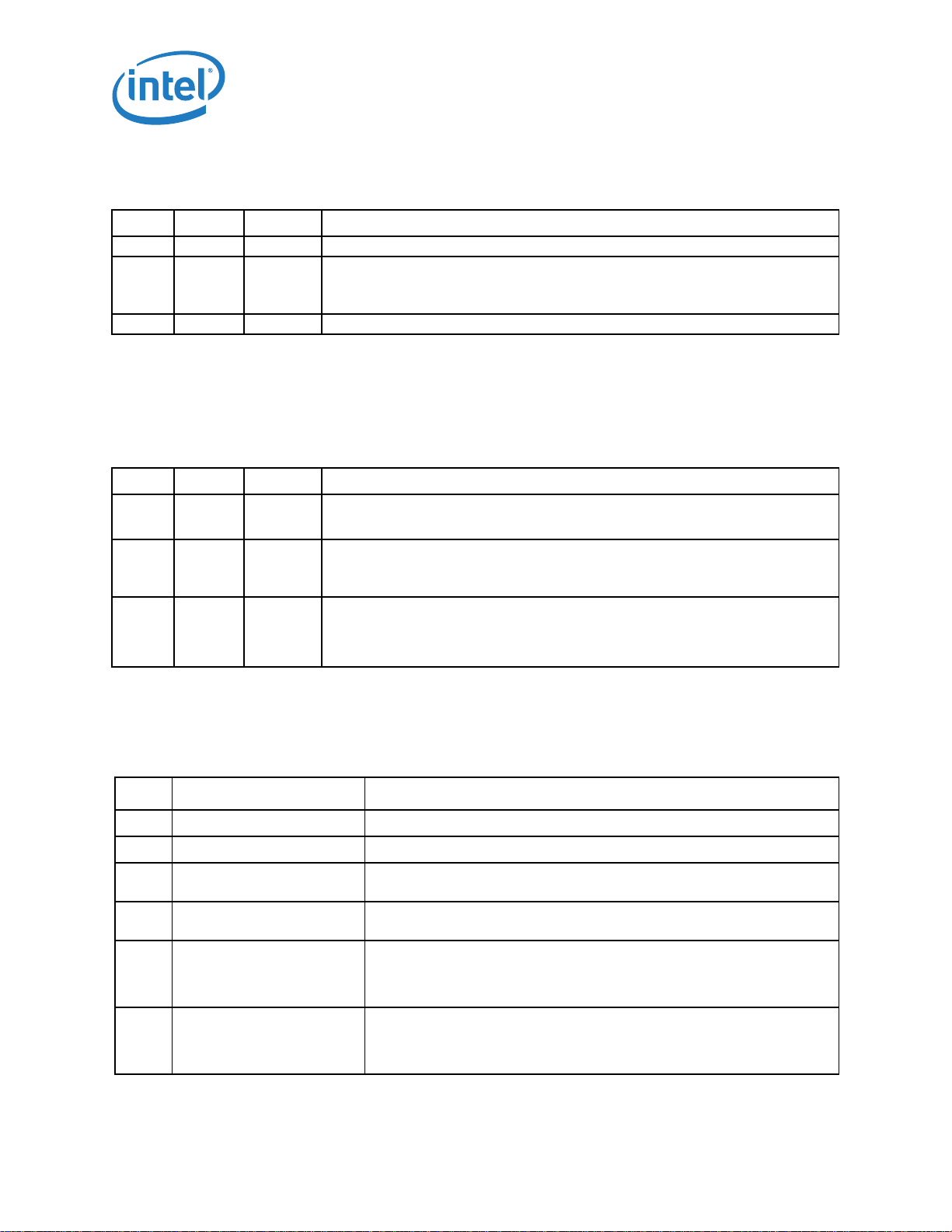

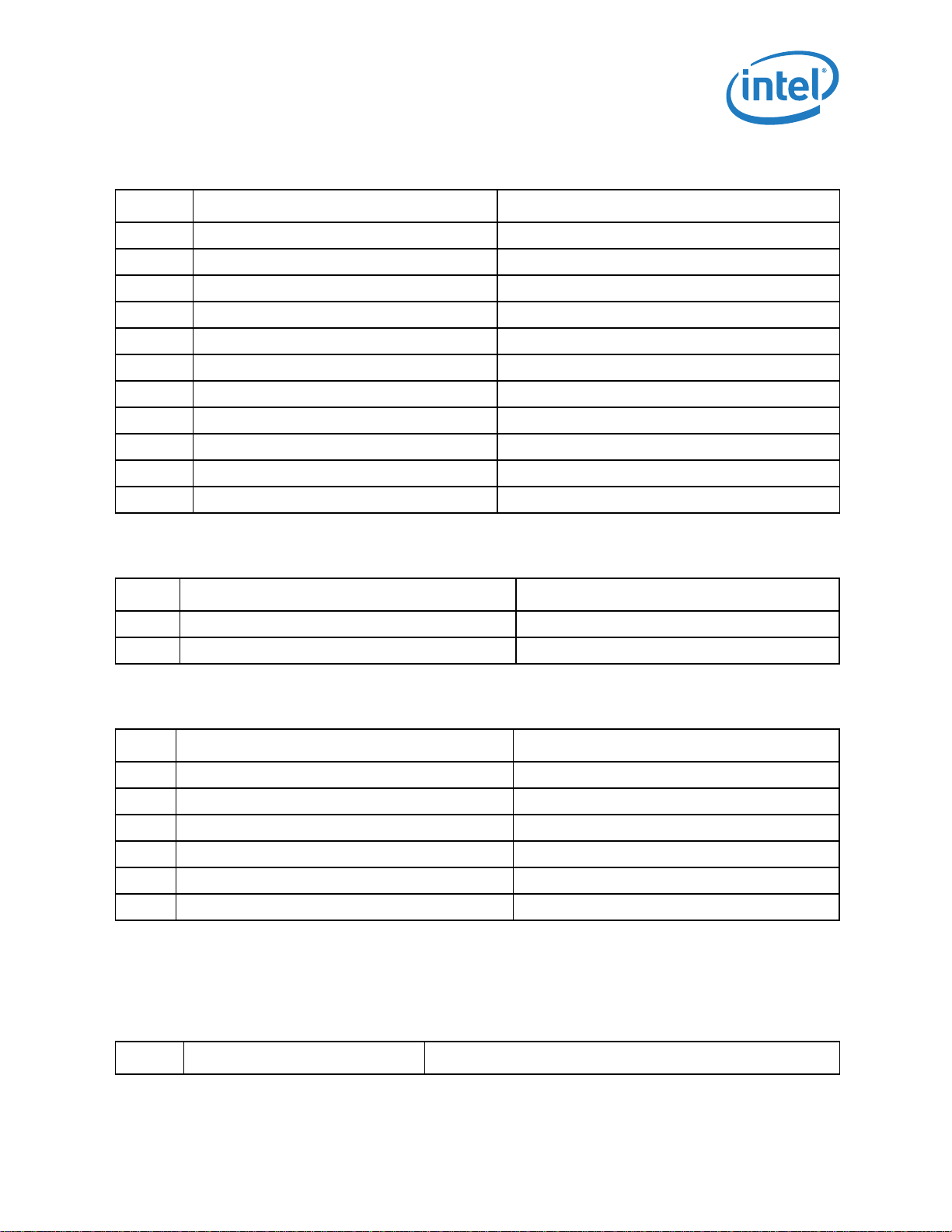

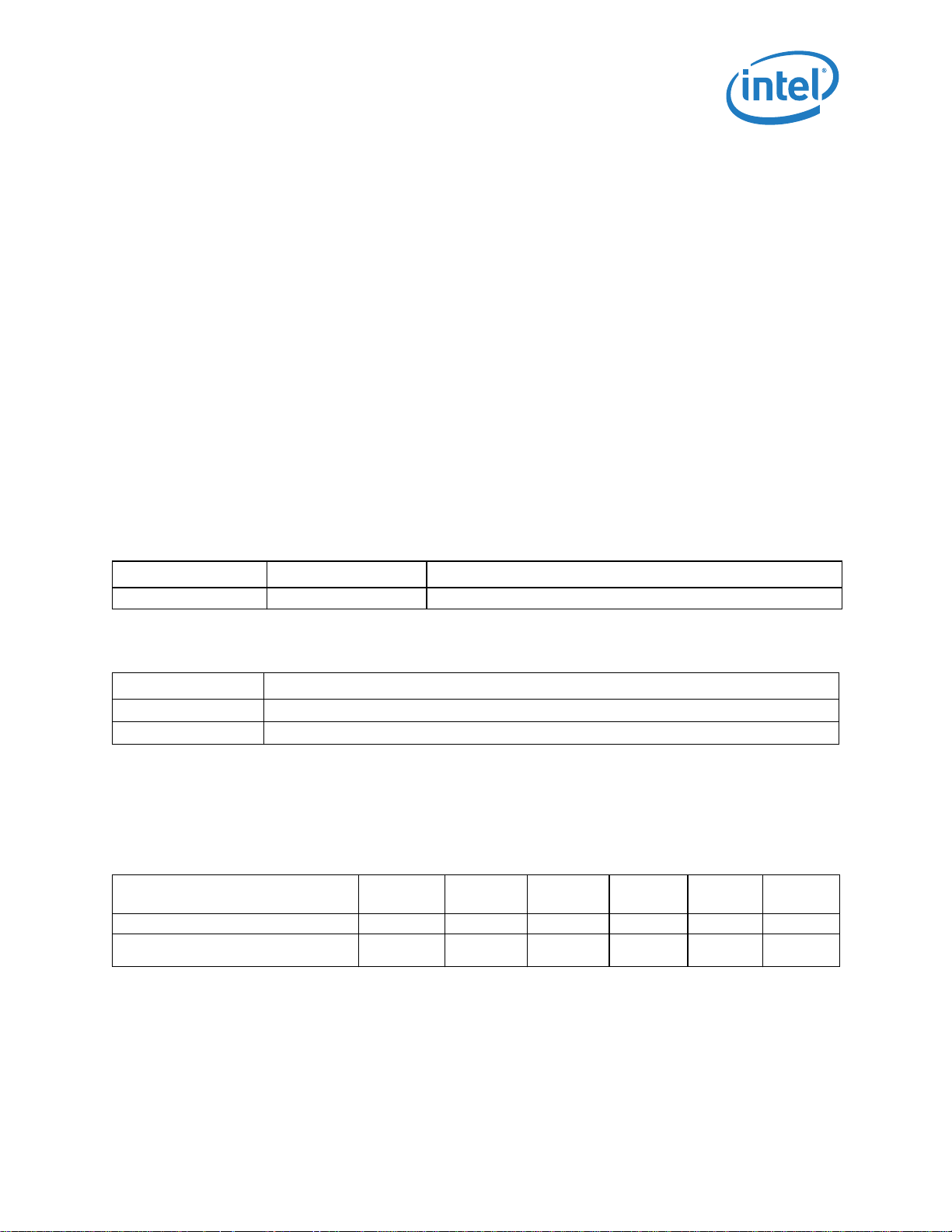

Revisions — Intel® 82575EB Gigabit Ethernet Controller

Revisions

Revision Date Description

.25 2/2006 Initial release (Intel Secret).

1.1 1/2008 • Updated Section 13.4.8.15 (bit 15 description).

• Updated Table 61 (bit 13 bit description).

.5 6/2006 Major revisions all sections.

1.0 6/2007 Final release (Intel Confidential).

1.2 6/2008 • Updated Section 5.6.1.5 (changed default device ID to 10A7h.

• Updated Section 5.6.1.1 (removed note concerning MAC

addresses).

• Removed table note from Sections 13.7.4 through 13.7.6.

• Updated Sections 13.4.65 and 14.7 concerning COLD field values.

• Updated Section 13.4.8.15 (revised bit 15 description).

• Updated Section 13.4.8.19 (removed statement that D0LPLU can

be loaded from the EEPROM.

• Updated Section 5.6.9 (added new PHY values).

.75 6/2006 Initial release (Intel Confidential).

1.3 9/2008 • Updated Section 13.4.2 (updated SPEED field description; bits

2.0 12/14/2010 • Section 4.1, EEPROM Device - EEPROM size data updated.

2.1 1/28/2011 • Updated brand strings. Updated title.

7:6).

• Replaced device ID table with note to refer to the spec update for

supported device IDs.

• Section 4.5.1.29, PXE Words (Words 30h:3Eh) - Section updated.

Specific field information exposed.

• Section 4.6.4, NC-SI Configuration Structure - Hardware default

values added.

• Section 4.7.2, PBA Number (Words 08h, 09h) - Section updated to

address new methodology.

• Section 5.4.1.3, Association through VLAN tag ID - Added.

• Section 5.4.1.4, Association through VLAN tag ID +RSS - Added.

• Section 10.2.1, Adding 802.1q Tags on Transmits - Section

updated.

• Section 14.3.34, Interrupt Cause Read Register - ICR (000C0H; R)

- Note located in OUTSYNC description updated.

• ASF references removed.

®

324632-003 Intel

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 3

82575EB Gigabit Ethernet Controller

Page 4

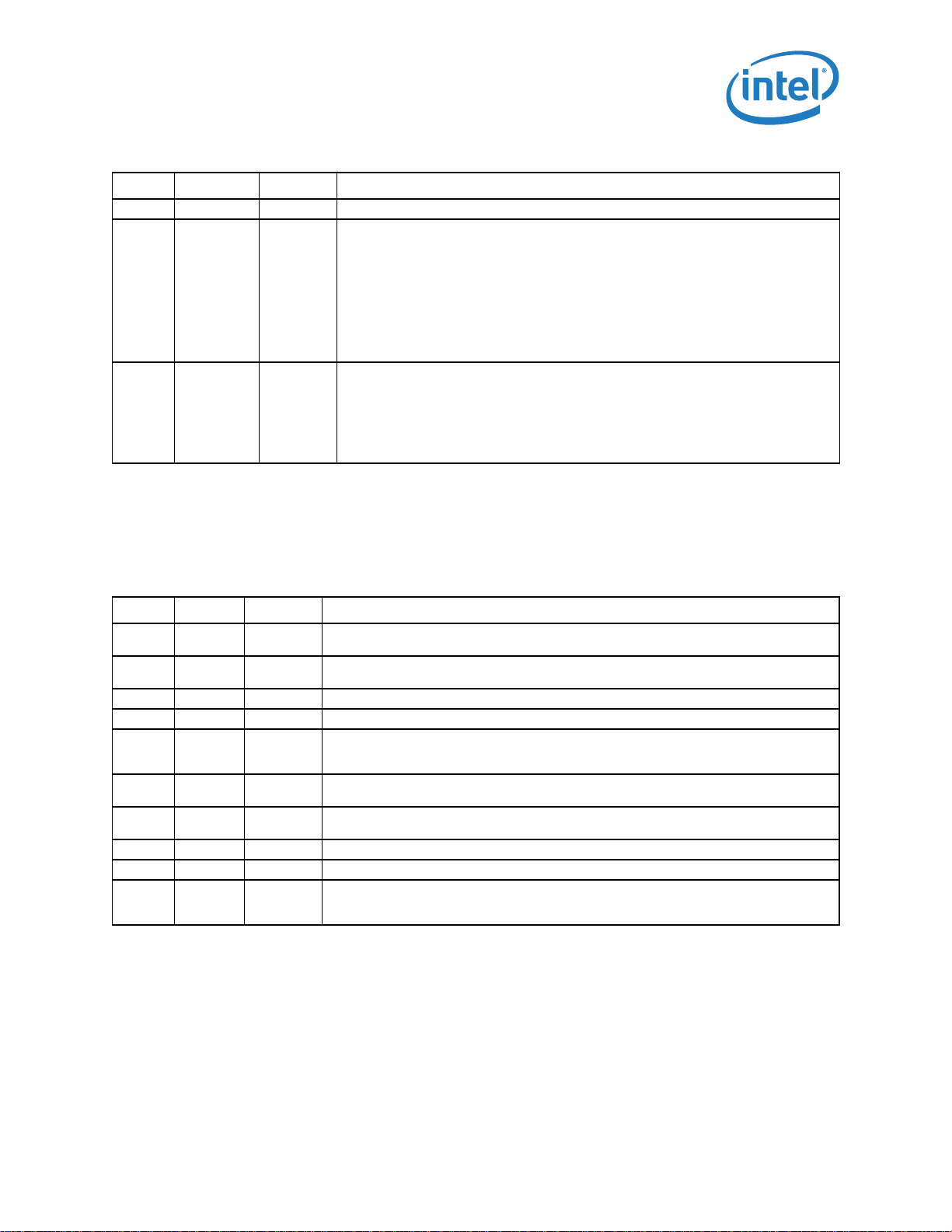

Intel® 82575EB Gigabit Ethernet Controller — Content

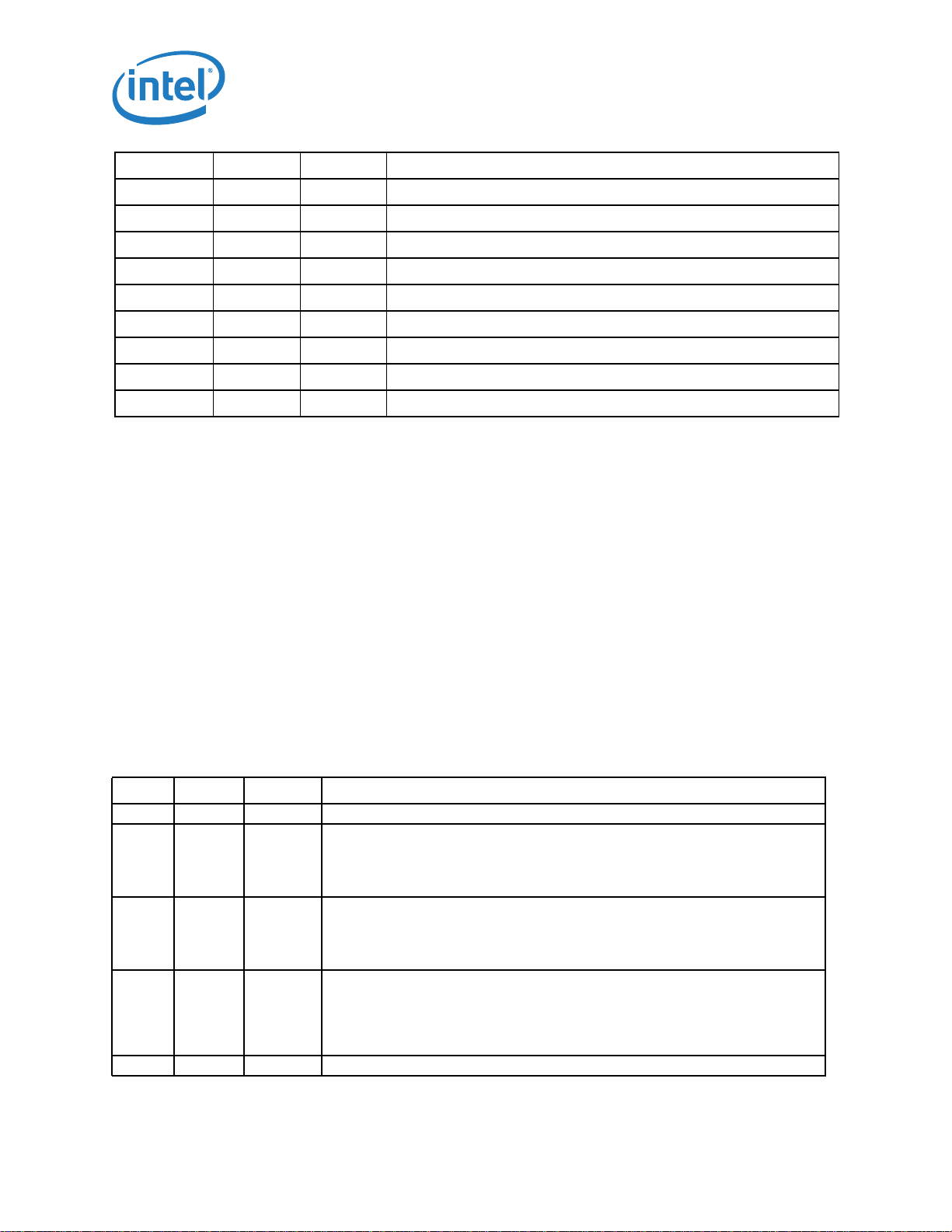

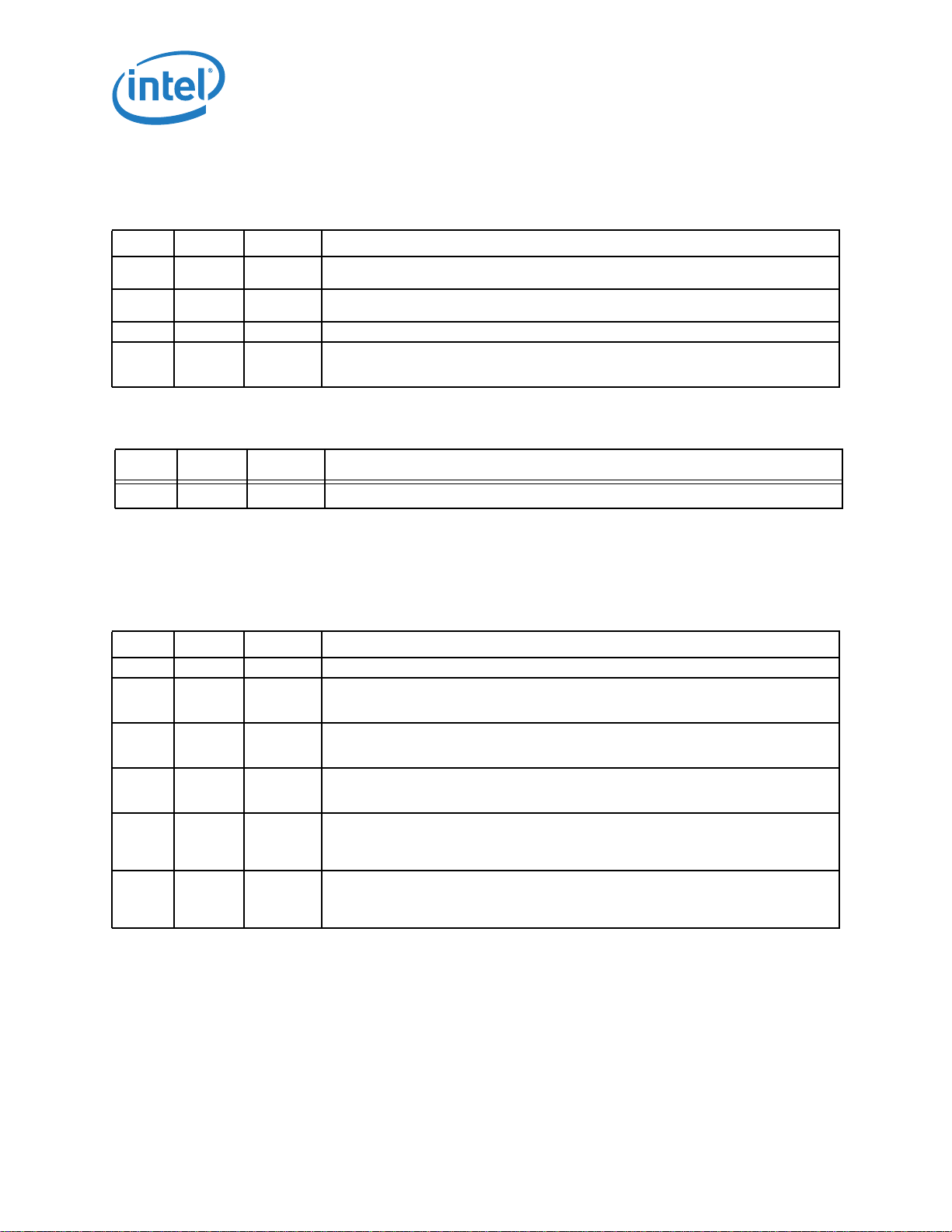

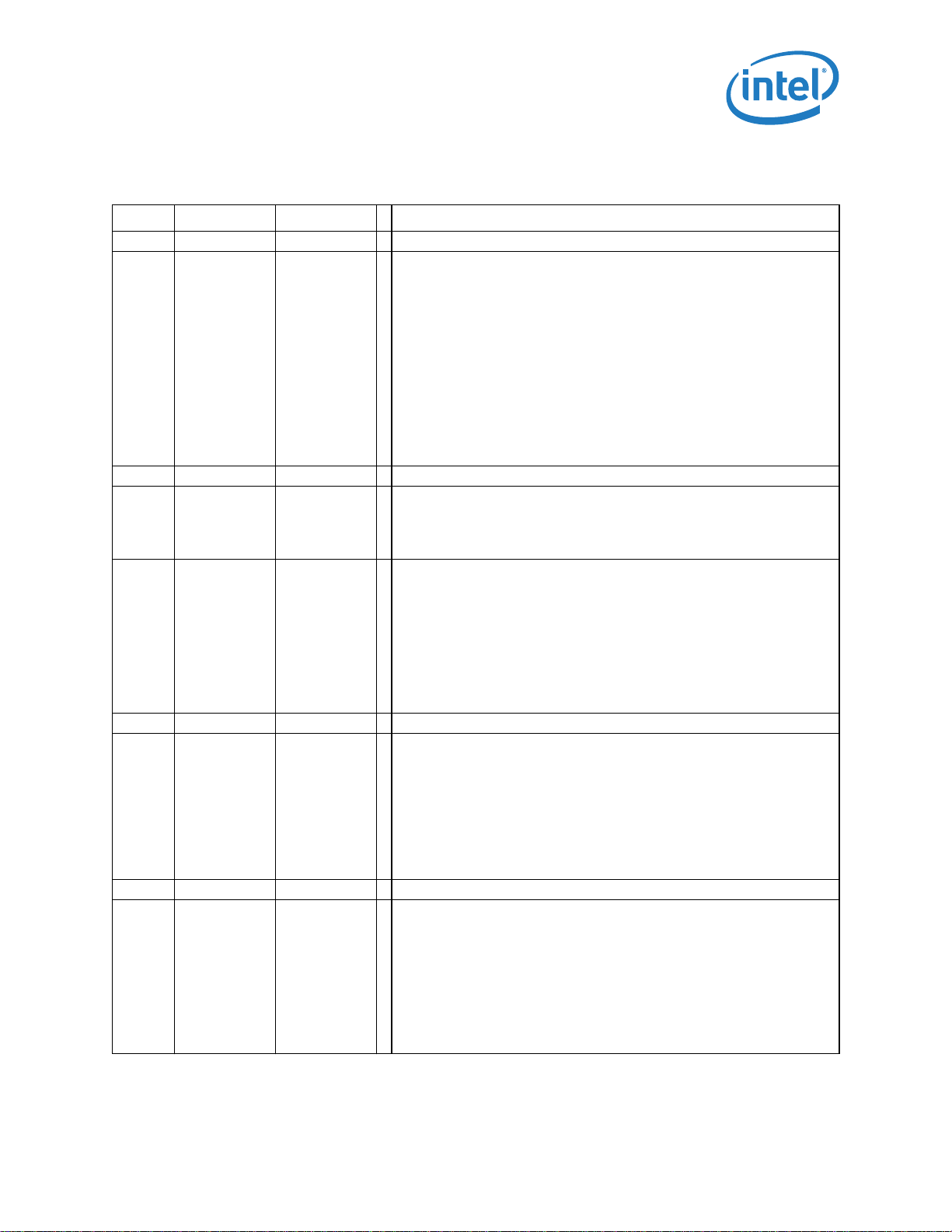

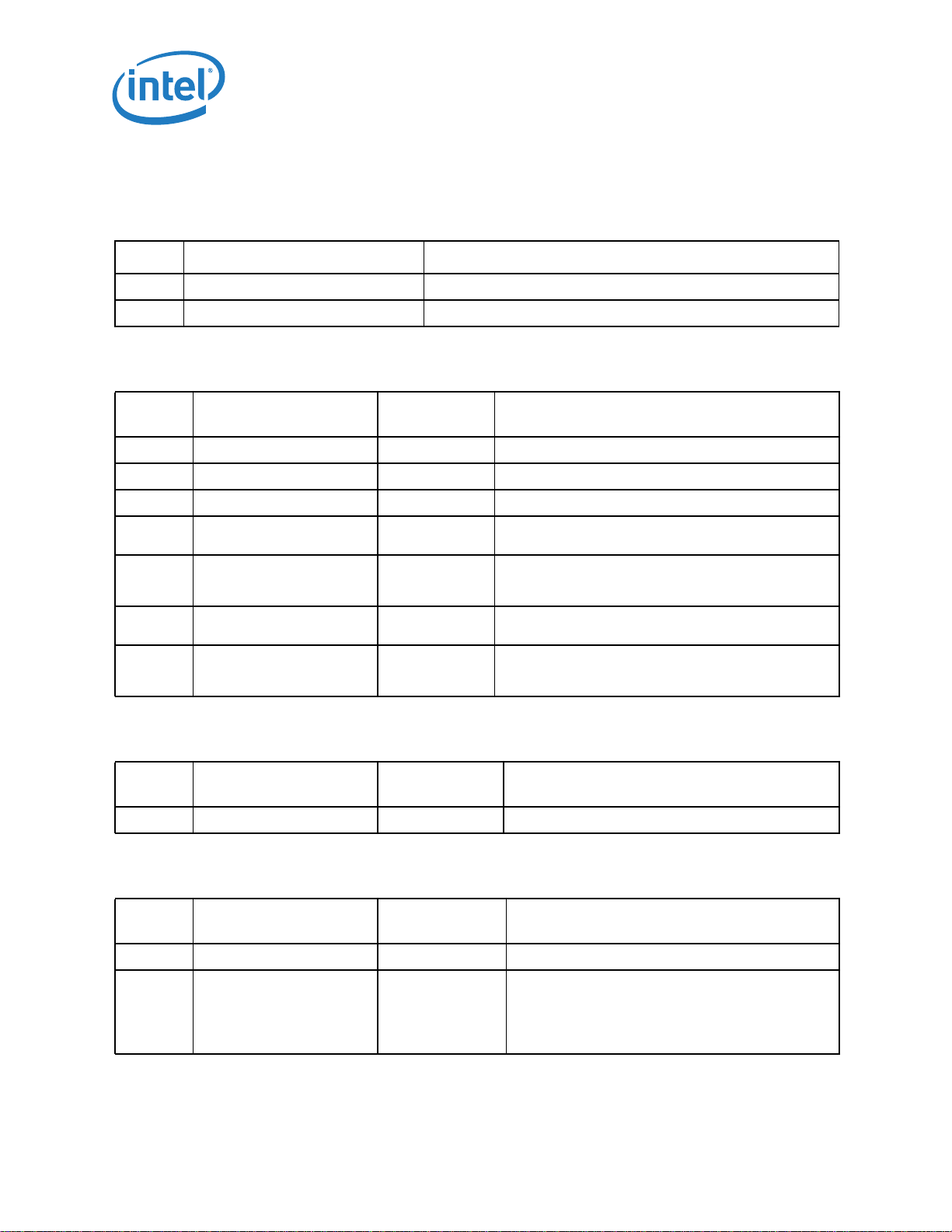

Content

1.0 Introduction ...........................................................................................................................19

1.1 Register and Bit References ........................................................................................................ 19

1.2 Byte and Bit Designations ........................................................................................................... 19

1.3 References ............................................................................................................................... 19

1.4 Memory Alignment Terminology .................................................................................................. 20

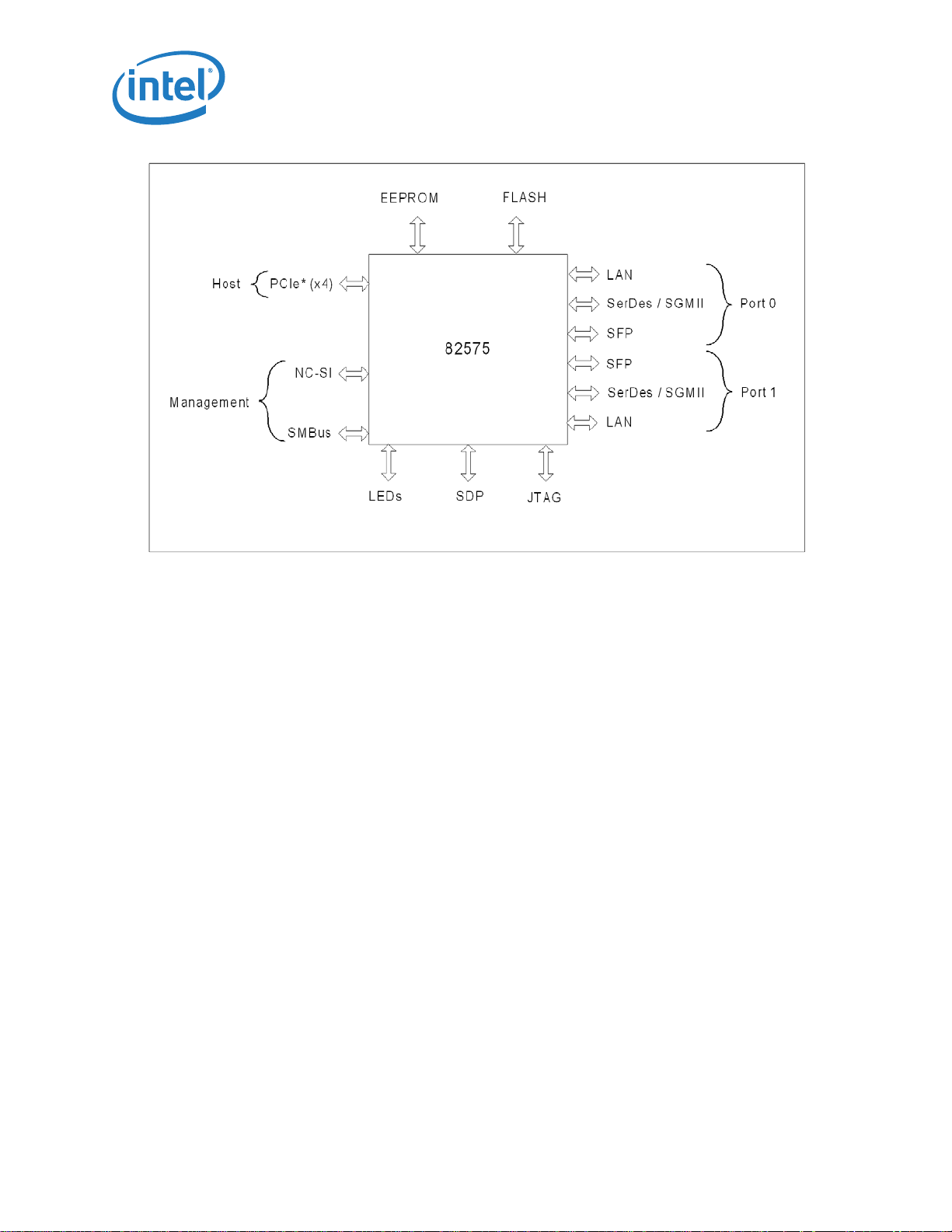

2.0 Architectural Overview ...........................................................................................................21

2.1 External Architecture ................................................................................................................. 21

2.1.1 Integrated 10/100/1000 Mb/s PHY......................................................................................... 22

2.1.2 System Interface................................................................................................................. 22

2.1.3 EEPROM Interface ............................................................................................................... 22

2.1.4 Flash Memory Interface........................................................................................................ 23

2.1.5 Management Interfaces........................................................................................................ 23

2.1.5.1 Software Watchdog ....................................................................................................... 23

2.1.6 General-Purpose I/O (Software-Definable Pins) ....................................................................... 23

2.1.7 LEDs.................................................................................................................................. 24

2.1.8 Network Interfaces .............................................................................................................. 24

2.2 DMA Addressing ........................................................................................................................ 24

2.3 Ethernet Addressing................................................................................................................... 25

2.4 Interrupt Control and Tuning....................................................................................................... 26

2.5 Hardware Acceleration Capability ................................................................................................. 26

2.5.1 Jumbo Frame Support.......................................................................................................... 27

2.5.2 Receive and Transmit Checksum Offloading ............................................................................ 27

2.5.3 TCP Segmentation ............................................................................................................... 27

2.5.4 Receive Fragmented UDP Checksum Offloading ....................................................................... 27

2.6 Buffer and Descriptor Structure ...................................................................................................27

2.7 Multiple Transmit Queues ........................................................................................................... 28

2.8 iSCSI Boot................................................................................................................................ 28

3.0 General Initialization and Reset Operation..............................................................................29

3.1 Power Up State ......................................................................................................................... 29

3.2 Initialization Sequence ............................................................................................................... 29

3.3 Interrupts During Initialization..................................................................................................... 29

3.4 Global Reset and General Configuration ........................................................................................ 30

3.5 Receive Initialization .................................................................................................................. 30

3.5.1 Initialize the Receive Control Register ....................................................................................31

3.5.2 Dynamic Queue Enabling and Disabling .................................................................................. 31

3.6 Transmit Initialization ................................................................................................................ 31

3.6.1 Dynamic Queue Enabling and Disabling .................................................................................. 32

3.7 Link Setup Mechanisms and Control/Status Bit Summary ................................................................ 32

3.7.1 PHY Initialization ................................................................................................................. 32

3.7.2 MAC/PHY Link Setup (CTRL_EXT.LINK_MODE = 00b) ............................................................... 32

3.7.3 MAC/SerDes Link Setup (CTRL_EXT.LINK_MODE = 11b)........................................................... 34

3.7.4 MAC/SGMII Link Setup (CTRL_EXT.LINK_MODE = 10b) ............................................................ 35

3.8 Reset Operation ........................................................................................................................ 37

3.8.1 PHY Behavior During a Manageability Session: ........................................................................ 41

3.9 Initialization of Statistics ............................................................................................................ 42

4.0 EEPROM and Flash Interface................................................................................................... 43

4.1 EEPROM Device ......................................................................................................................... 43

4.1.1 Software Accesses............................................................................................................... 43

4.1.2 Signature and CRC Fields ..................................................................................................... 44

4.1.3 EEPROM Recovery ............................................................................................................... 44

4.1.4 Protected EEPROM Space...................................................................................................... 45

4.1.5 Initial EEPROM Programming ................................................................................................ 45

4.1.6 Activating the Protection Mechanism ...................................................................................... 46

4.1.7 Non Permitted Accesses to Protected Areas in the EEPROM ....................................................... 46

4.1.8 EEPROM-Less Support.......................................................................................................... 46

Intel® 82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

4 January 2011

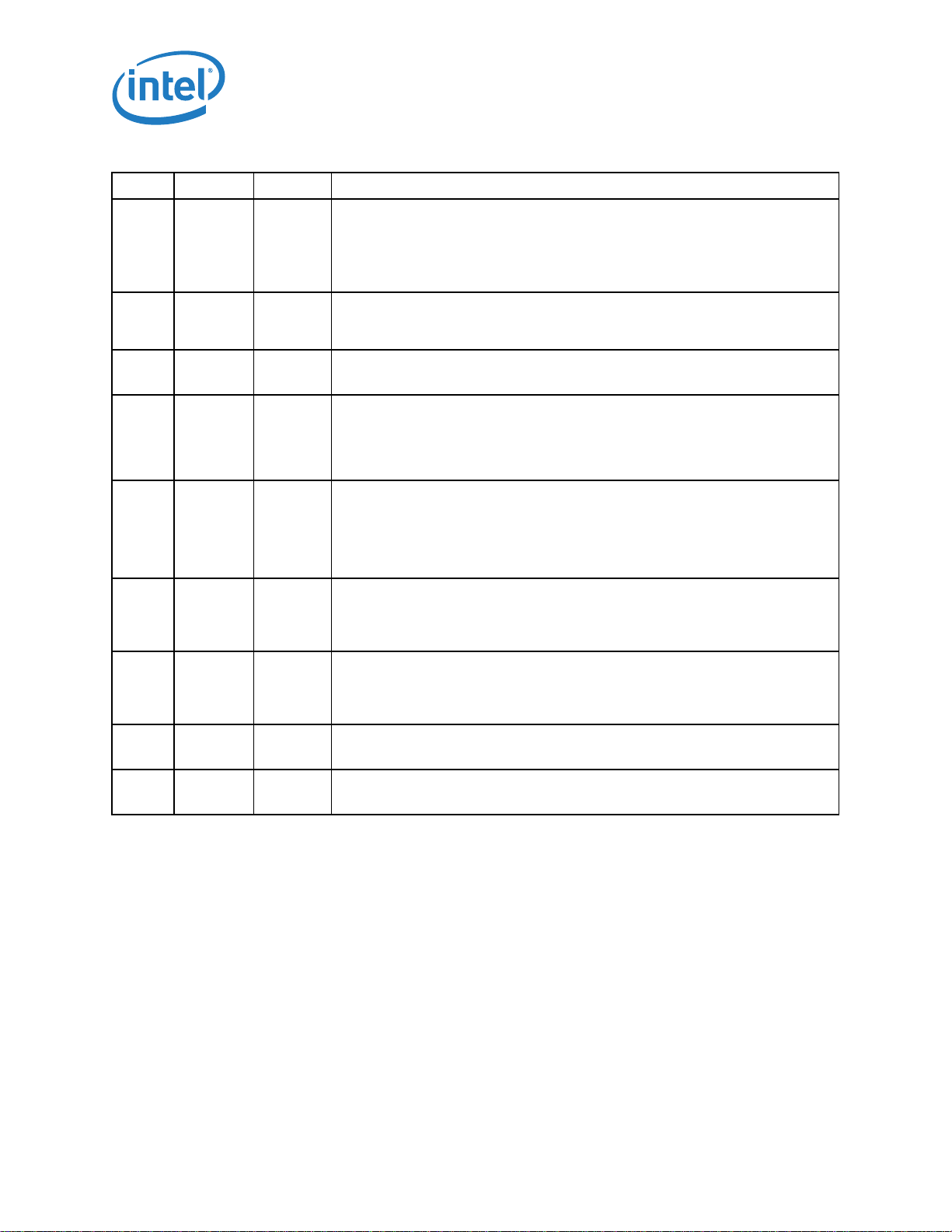

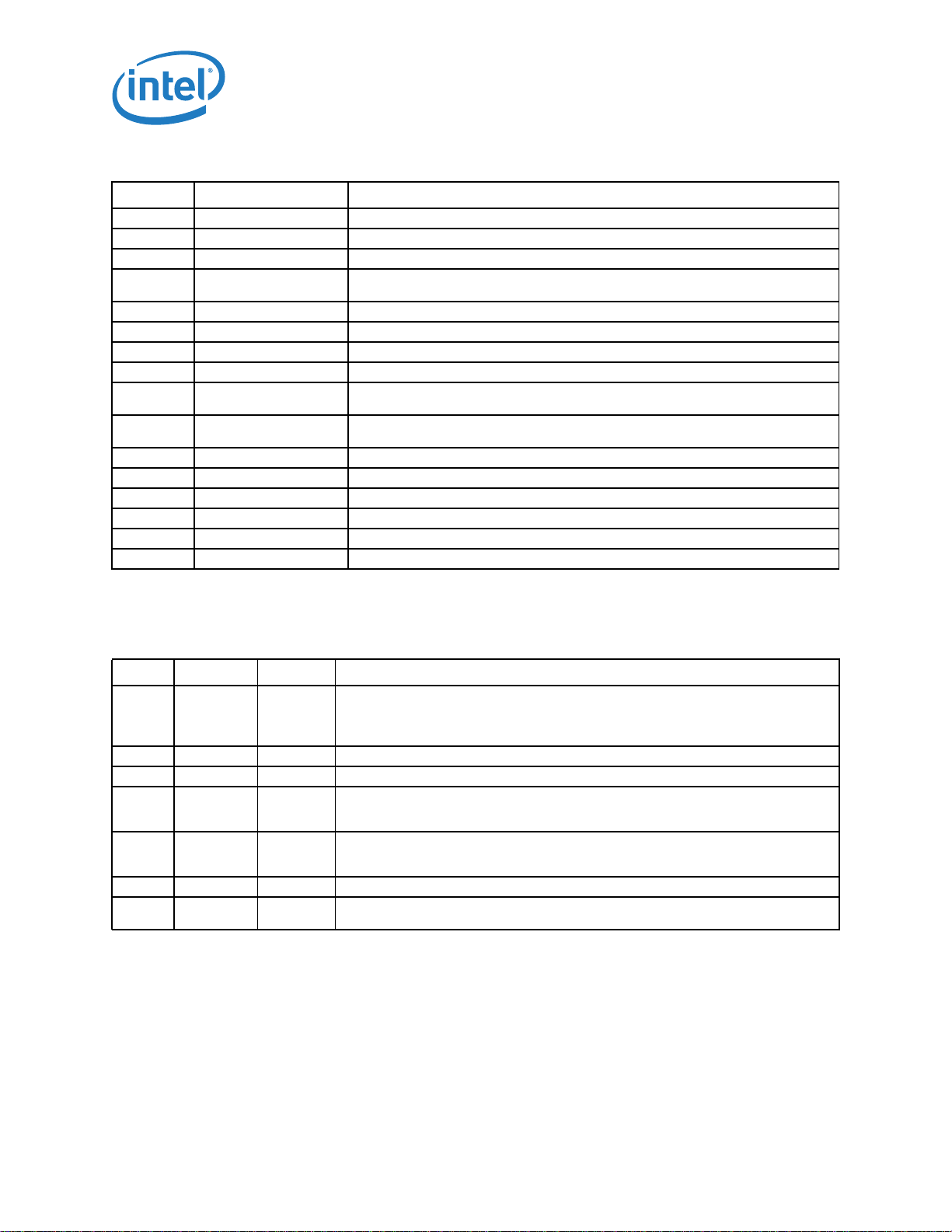

Page 5

Content — Intel® 82575EB Gigabit Ethernet Controller

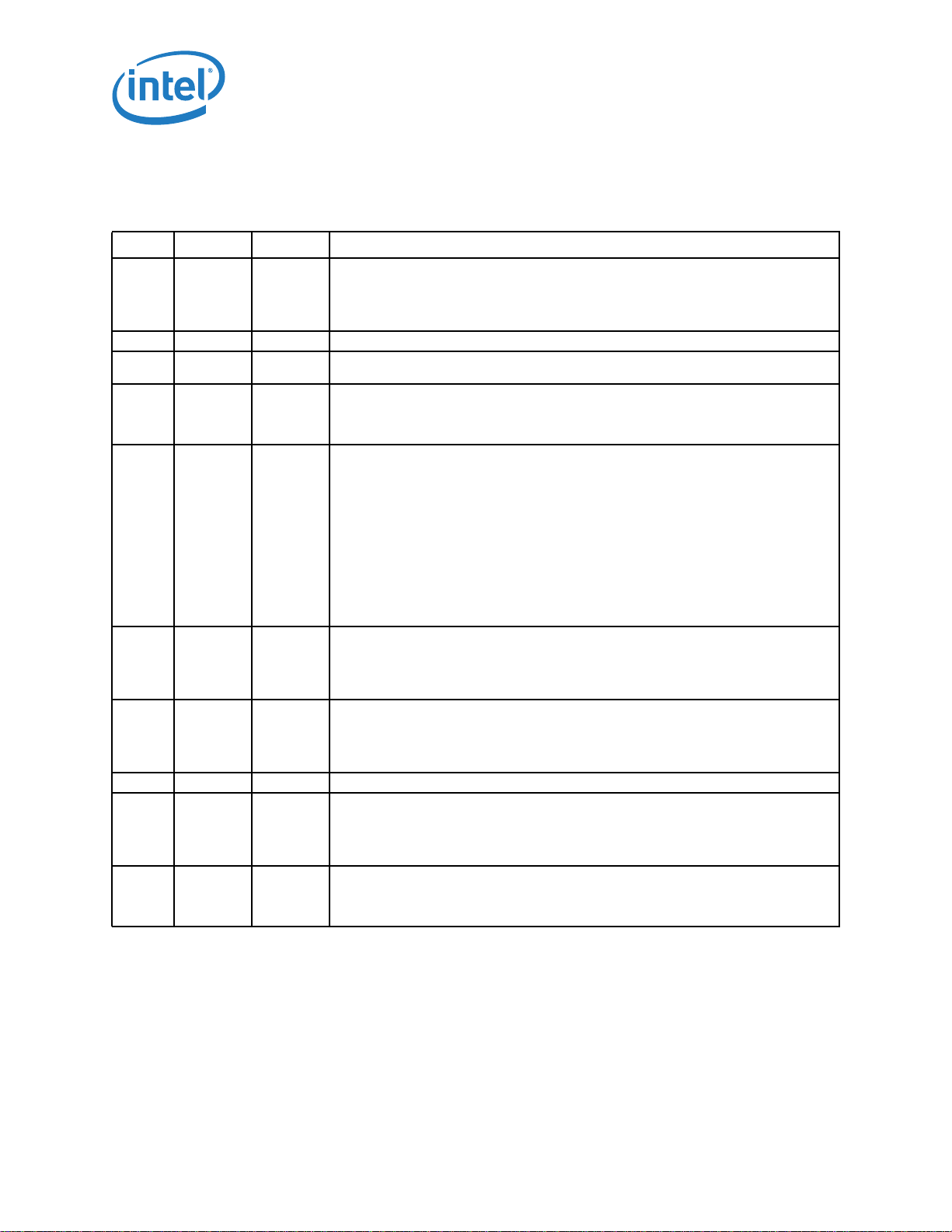

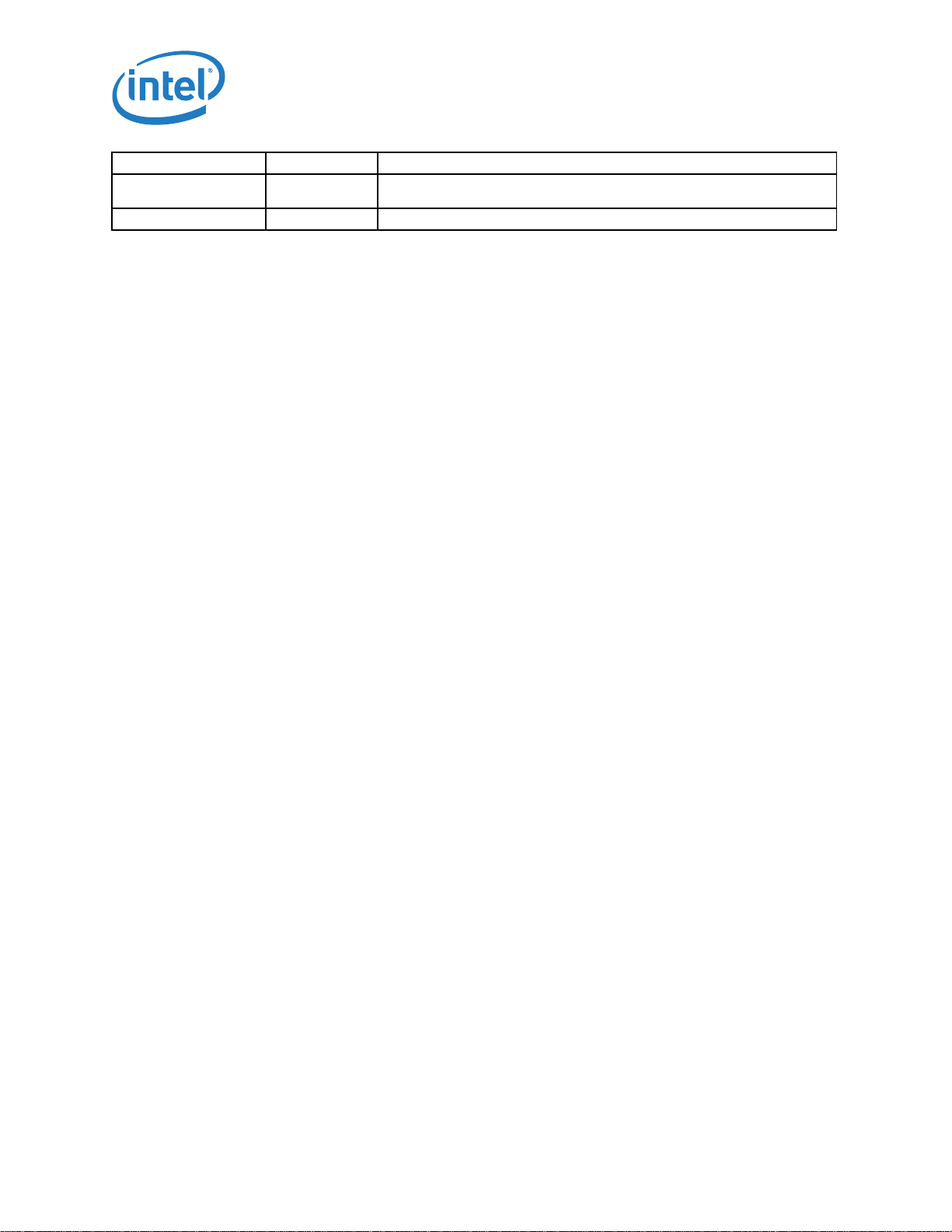

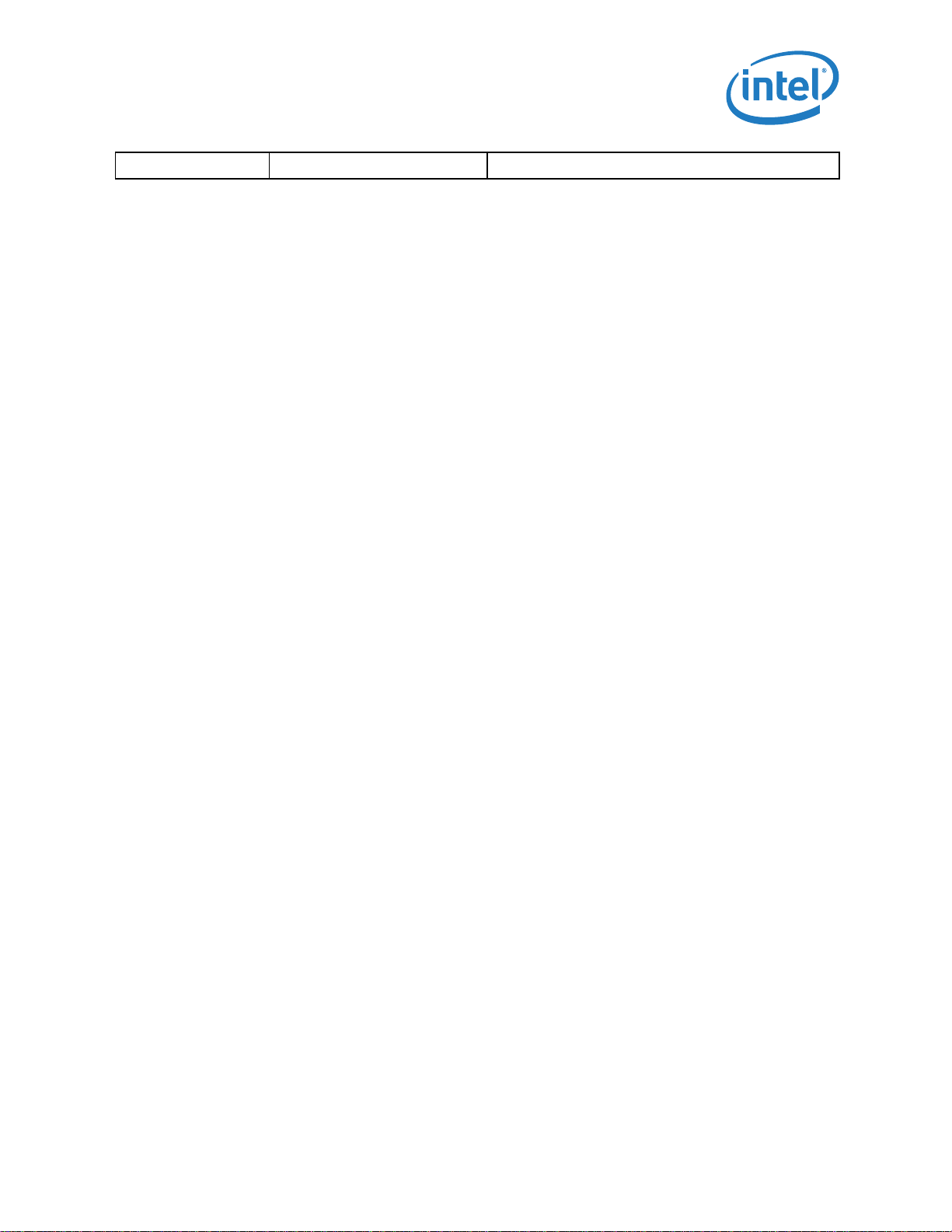

4.2 Flash Interface Operation ........................................................................................................... 49

4.2.1 Flash Write Control .............................................................................................................. 50

4.2.2 Flash Erase Control.............................................................................................................. 50

4.3 Shared EEPROM ........................................................................................................................ 50

4.3.1 EEPROM Deadlock Avoidance ................................................................................................ 50

4.3.2 EEPROM Map Shared Words.................................................................................................. 51

4.4 Shared FLASH........................................................................................................................... 51

4.4.1 Flash Access Contention ....................................................................................................... 52

4.4.2 Flash Deadlock Avoidance..................................................................................................... 52

4.5 EEPROM Map ............................................................................................................................ 52

4.5.1 Hardware Accessed Words....................................................................................................54

4.5.1.1 Ethernet Address (Words 00h – 02h) ............................................................................... 56

4.5.1.2 Initialization Control 1 (Word 0Ah) .................................................................................. 56

4.5.1.3 Subsystem ID (Word 0Bh) ............................................................................................. 57

4.5.1.4 Subsystem Vendor ID (Word 0Ch)................................................................................... 57

4.5.1.5 Device ID (Word 0Dh, 11h) ............................................................................................ 57

4.5.1.6 Dummy Device ID (Word 1Dh) ....................................................................................... 57

4.5.1.7 Initialization Control 2 (Word 0Fh)................................................................................... 57

4.5.1.8 Software Defined Pins Control (Word 10h)........................................................................ 59

4.5.1.9 EEPROM Sizing & Protected Fields (Word 12h) .................................................................. 60

4.5.1.10 Initialization Control 3 (Word 14h, 24h) ........................................................................... 61

4.5.1.11 NC-SI and PCIe* Completion Timeout Configuration (Word 15h) ......................................... 63

4.5.1.12 MSI-X Configuration (Word 16h) ..................................................................................... 64

4.5.1.13 PLL/Lane/PHY Initialization Pointer (Word 17h) ................................................................. 64

4.5.1.14 PCIe* Initialization Configuration 1 (Word 18h)................................................................. 64

4.5.1.15 PCIe* Initialization Configuration 2 (Word 19h)................................................................. 64

4.5.1.16 Software Defined Pins Control (Word 20h)........................................................................ 65

4.5.1.17 PCIe* Initialization Configuration 3 (Word 1Ah)................................................................. 66

4.5.1.18 PCIe* Control (Word 1Bh) .............................................................................................. 68

4.5.1.19 LED 1, 3 Configuration Defaults (Word 1Ch) ..................................................................... 69

4.5.1.20 Device Revision ID (Word 1Eh) ....................................................................................... 70

4.5.1.21 LED 0, 2 Configuration Defaults (Word 1Fh)...................................................................... 70

4.5.1.22 Functions Control (Word 21h) ......................................................................................... 72

4.5.1.23 LAN Power Consumption (Word 22h) ............................................................................... 72

4.5.1.24 Management Hardware Configuration Control (Word 23h) .................................................. 72

4.5.1.25 End of RO Area (Word 2Ch ............................................................................................. 74

4.5.1.26 Start of RO Area (Word 2Dh) .......................................................................................... 74

4.5.1.27 Watchdog Configuration (Word 2Eh) ................................................................................ 74

4.5.1.28 VPD Pointer (Word 2Fh) ................................................................................................. 74

4.5.1.29 PXE Words (Words 30h:3Eh) .......................................................................................... 74

4.5.1.29.1 Main Setup Options PCI Function 0 (Word 30h) .............................................................. 74

4.5.1.29.2 Configuration Customization Options PCI Function 0 (Word 31h) ...................................... 76

4.5.1.29.3 PXE Version (Word 32h)............................................................................................ 77

4.5.1.29.4 IBA Capabilities (Word 33h) ........................................................................................ 77

4.5.1.29.5 Setup Options PCI Function 1 (Word 34h) ..................................................................... 77

4.5.1.29.6 Configuration Customization Options PCI Function 1 (Word 35h) ...................................... 78

4.5.1.29.7 iSCSI Option ROM Version (Word 36h).......................................................................... 78

4.5.1.29.8 Alternate MAC Address Pointer (Word 37h).................................................................... 78

4.5.1.29.9 Setup Options PCI Function 2 (Word 38h) ..................................................................... 78

4.5.1.29.10 Configuration Customization Options PCI Function 2 (Word 39h) ...................................... 78

4.5.1.29.11 Setup Options PCI Function 3 (Word 3Ah) ..................................................................... 78

4.5.1.29.12 Configuration Customization Options PCI Function 3 (Word 3Bh) ...................................... 78

4.5.1.29.13 iSCSI Boot Configuration Offset (Word 3Dh) .................................................................. 78

4.5.1.29.13.1 iSCSI Module Structure ........................................................................................ 78

4.5.1.29.14 Checksum Word (Word 3Fh)........................................................................................ 80

4.6 Manageability Control Sections .................................................................................................... 81

4.6.1 Sideband Configuration Structure .......................................................................................... 81

4.6.1.1 Section Header - (0ffset 0h) ........................................................................................... 81

4.6.1.2 SMBus Max Fragment Size - (0ffset 01h).......................................................................... 81

4.6.1.3 SMBus Notification Timeout and Flags - (0ffset 02h) .......................................................... 81

®

324632-003 Intel

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 5

82575EB Gigabit Ethernet Controller

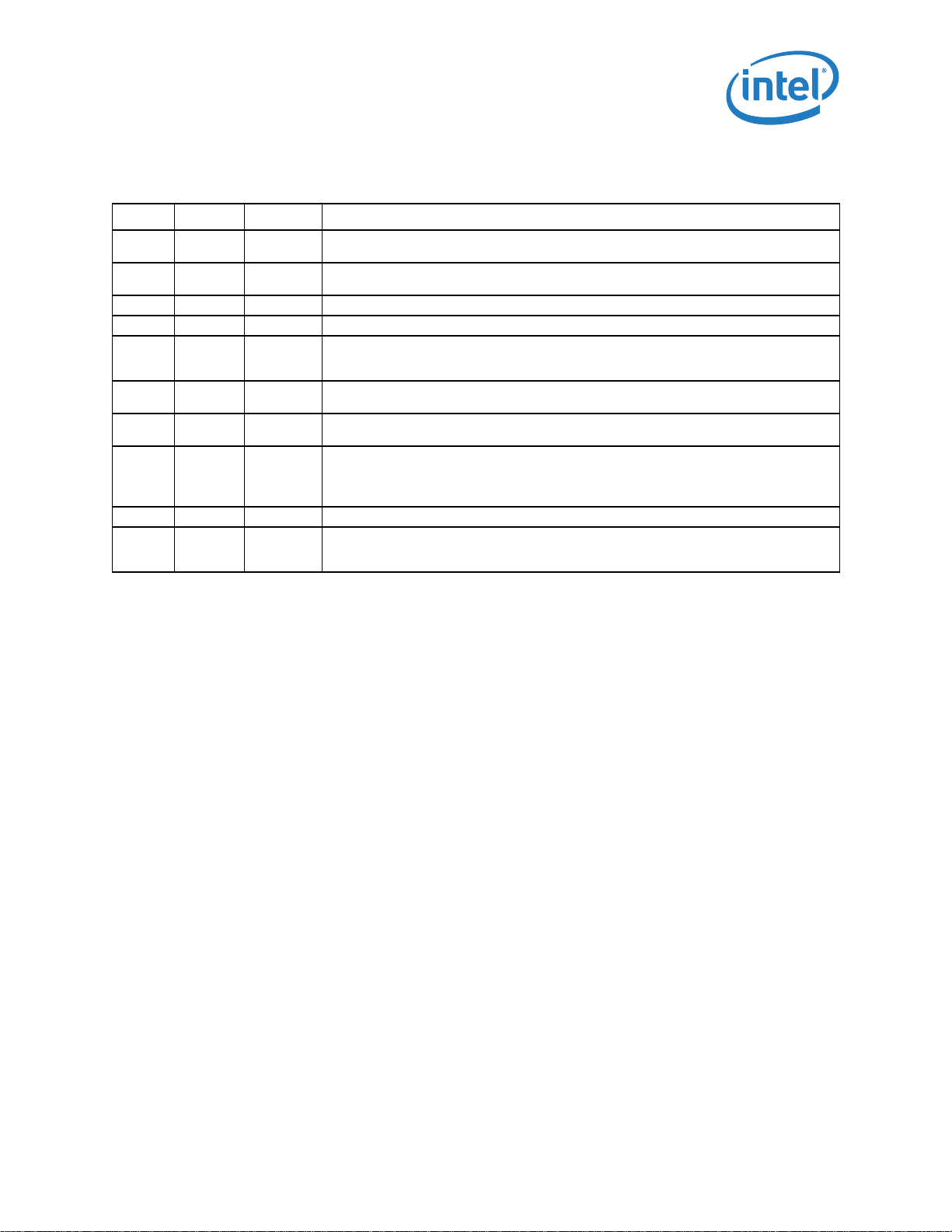

Page 6

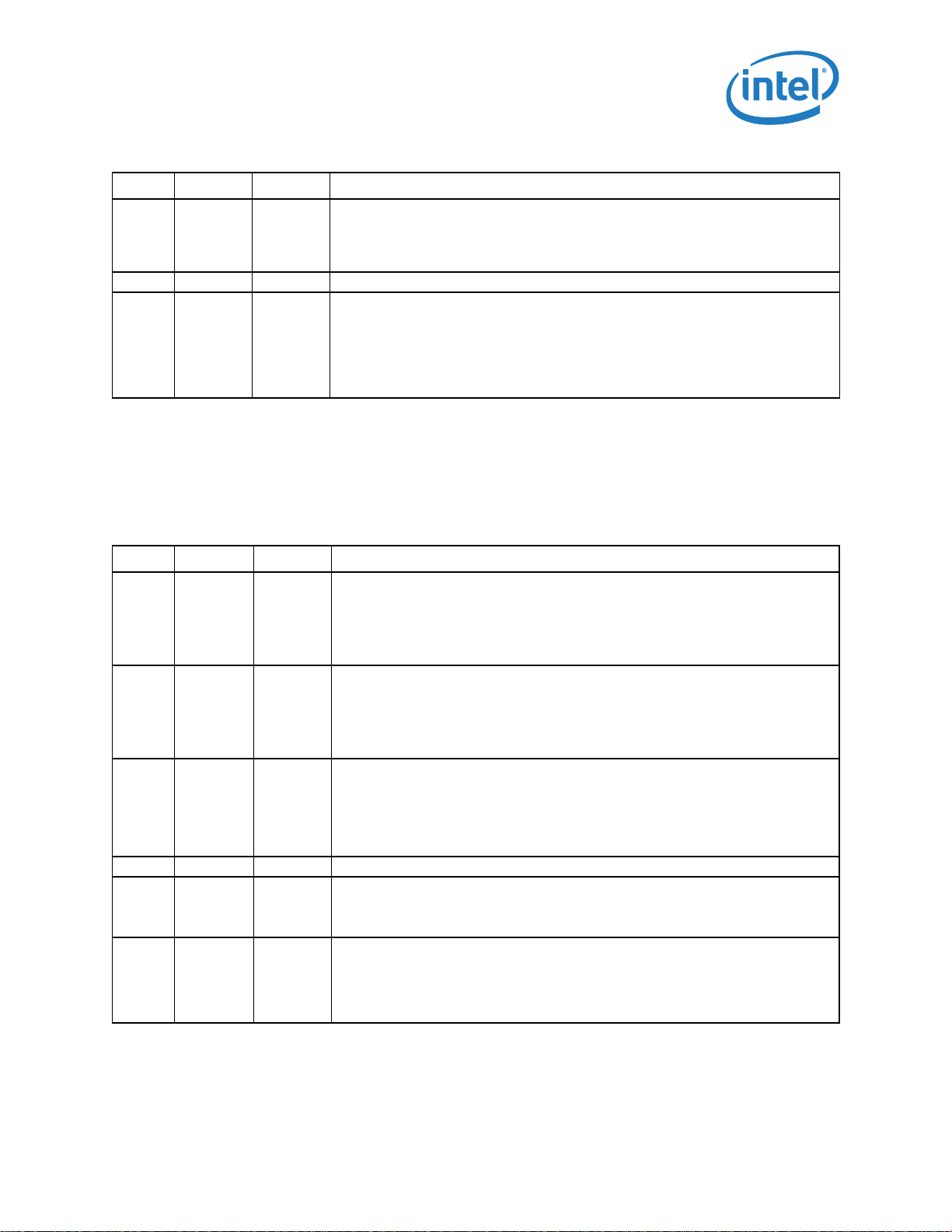

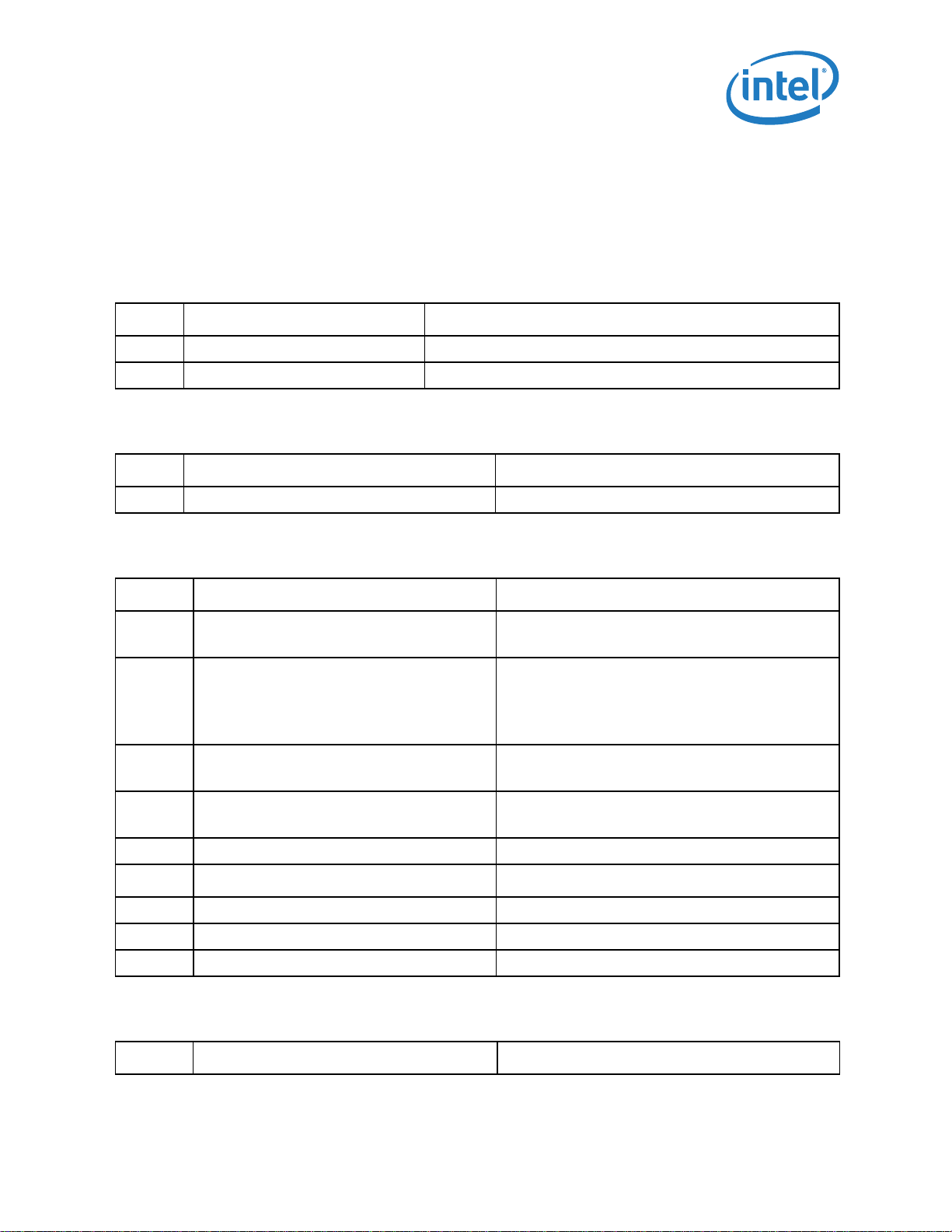

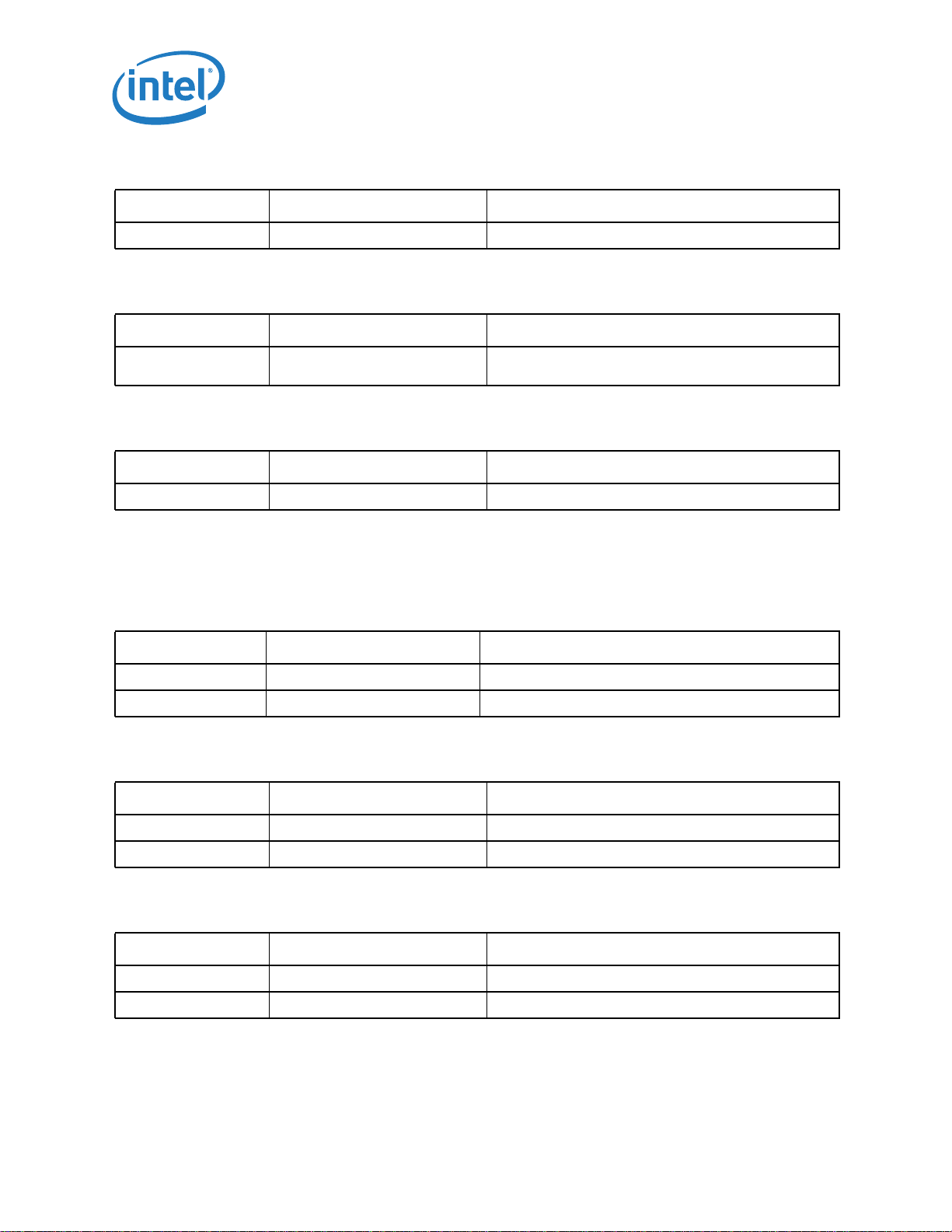

Intel® 82575EB Gigabit Ethernet Controller — Content

4.6.1.4 SMBus Slave Addresses - (0ffset 03h).............................................................................. 81

4.6.1.5 SMBus Fail-Over Register (Low Word) - (0ffset 04h) .......................................................... 83

4.6.1.6 SMBus Fail-Over Register (High Word) - (0ffset 05h) ......................................................... 83

4.6.1.7 NC-SI Configuration (0ffset 06h)..................................................................................... 83

4.6.2 Flex TCO Filter Configuration Structure................................................................................... 83

4.6.2.1 Section Header - (0ffset 0h) ........................................................................................... 83

4.6.2.2 Flex Filter Length and Control - (0ffset 01h) ..................................................................... 85

4.6.2.3 Flex Filter Enable Mask - (0ffset 02 - 09h) ........................................................................ 85

4.6.2.4 Flex Filter Data - (0ffset 0Ah - Block Length) .................................................................... 85

4.6.3 NC-SI Microcode Download Structure ..................................................................................... 85

4.6.3.1 Data Patch Size (Offset 0h) ............................................................................................ 85

4.6.3.2 Rx and Tx Code Size (Offset 1h) ..................................................................................... 85

4.6.3.3 Download Data (Offset 2h - Data Size)............................................................................. 85

4.6.4 NC-SI Configuration Structure............................................................................................... 86

4.6.4.1 Section Header - (0ffset 0h) ........................................................................................... 86

4.6.4.2 Rx Mode Control1 (RR_CTRL[15:0]) (Offset 01h)............................................................... 86

4.6.4.3 Rx Mode Control2 (RR_CTRL[31:16]) (Offset 02h)............................................................. 86

4.6.4.4 Tx Mode Control1 (RT_CTRL[15:0]) (Offset 03h) .............................................................. 86

4.6.4.5 Tx Mode Control2 (RT_CTRL[31:16]) (Offset 04h) ............................................................. 87

4.6.4.6 MAC Tx Control Reg1 (TxCntrlReg1 (15:0]) (Offset 05h) .................................................... 87

4.6.4.7 MAC Tx Control Reg2 (TxCntrlReg1 (31:16]) (Offset 06h) .................................................. 87

4.6.5 Common Firmware Pointer ................................................................................................... 87

4.6.5.1 Manageability Capability/Manageability Enable (Word 54h) ................................................. 88

4.6.6 Pass Through Pointers.......................................................................................................... 88

4.6.6.1 PT LAN0 Configuration Pointer (Word 56h) ....................................................................... 88

4.6.6.2 SMBus Configuration Pointer (Word 57h).......................................................................... 88

4.6.6.3 Flex TCO Filter Configuration Pointer (Word 58h)............................................................... 88

4.6.6.4 PT LAN1 Configuration Pointer (Word 59h) ....................................................................... 90

4.6.6.5 NC-SI Microcode Download Pointer (Word 5Ah)................................................................. 90

4.6.6.6 NC-SI Configuration Pointer (Word 5Bh)........................................................................... 90

4.6.7 PT LAN Configuration Structure .............................................................................................90

4.6.7.1 Section Header (Offset 0h) ............................................................................................. 90

4.6.7.2 LAN0 IPv4 Address 0 LSB, MIPAF0 (Offset 01h)................................................................. 90

4.6.7.3 LAN0 IPv4 Address 0 LSB, MIPAF0 (Offset 02h)................................................................. 90

4.6.7.4 LAN0 IPv4 Address 1; MIPAF1 (Offset 03h:04h) ................................................................ 90

4.6.7.5 LAN0 IPv4 Address 2; MIPAF2 (Offset 05h:06h) ................................................................ 91

4.6.7.6 LAN0 IPv4 Address 3; MIPAF3 (Offset 07h:08h) ................................................................ 91

4.6.7.7 LAN0 MAC Address 0 LSB, MMAL0 (Offset 09h) ................................................................. 91

4.6.7.8 LAN0 MAC Address 0 LSB, MMAL0 (Offset 0Ah) ................................................................. 91

4.6.7.9 LAN0 MAC Address 0 MSB, MMAH0 (Offset 0Bh)................................................................ 91

4.6.7.10 LAN0 MAC Address 1; MMAL/H1 (Offset 0Ch:0Eh) ............................................................. 91

4.6.7.11 LAN0 MAC Address 2; MMAL/H2 (Offset 0Fh:11h).............................................................. 91

4.6.7.12 LAN0 MAC Address 3; MMAL/H3 (Offset 12h:14h) ............................................................. 91

4.6.7.13 LAN0 UDP Flex Filter Ports 0:15; MFUTP Registers (Offset 15h:24h)..................................... 92

4.6.7.14 LAN0 VLAN Filter 0:7; MAVTV Registers (Offset 25h:2Ch)................................................... 92

4.6.7.15 LAN0 Manageability Filters Valid; MFVAL LSB (Offset 2Dh) .................................................. 92

4.6.7.16 LAN0 Manageability Filters Valid; MFVAL MSB (Offset 2Eh) ................................................. 92

4.6.7.17 LAN0 MAC Value MSB (Offset 2Fh) .................................................................................. 93

4.6.7.18 LAN0 MANC Value LSB (Offset 30h) ................................................................................. 93

4.6.7.19 LAN0 Receive Enable 1(Offset 31h) ................................................................................. 93

4.6.7.20 LAN0 Receive Enable 2 (Offset 32h) ................................................................................ 93

4.6.7.21 LAN0 MANC2H Value LSB (Offset 33h) ............................................................................. 95

4.6.7.22 LAN0 MANC2H Value MSB (Offset 34h) ............................................................................ 95

4.6.7.23 Manageability Decision Filters; MDEF0,1 (Offset 35h)......................................................... 95

4.6.7.24 Manageability Decision Filters; MDEF0, 2 (Offset 36h) ........................................................ 96

4.6.7.25 Manageability Decision Filters; MDEF1:6, 1:2 (Offset 37h:42h) ........................................... 96

4.6.7.26 ARP Response IPv4 Address 0 LSB (Offset 43h) ................................................................ 97

4.6.7.27 ARP Response IPv4 Address 0 MSB (Offset 44h)................................................................ 97

4.6.7.28 LAN0 IPv6 Address 0 LSB; MIPAF (Offset 45h) .................................................................. 97

4.6.7.29 LAN0 IPv6 Address 0 MSB; MIPAF (Offset 46h) ................................................................. 97

Intel® 82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

6 January 2011

Page 7

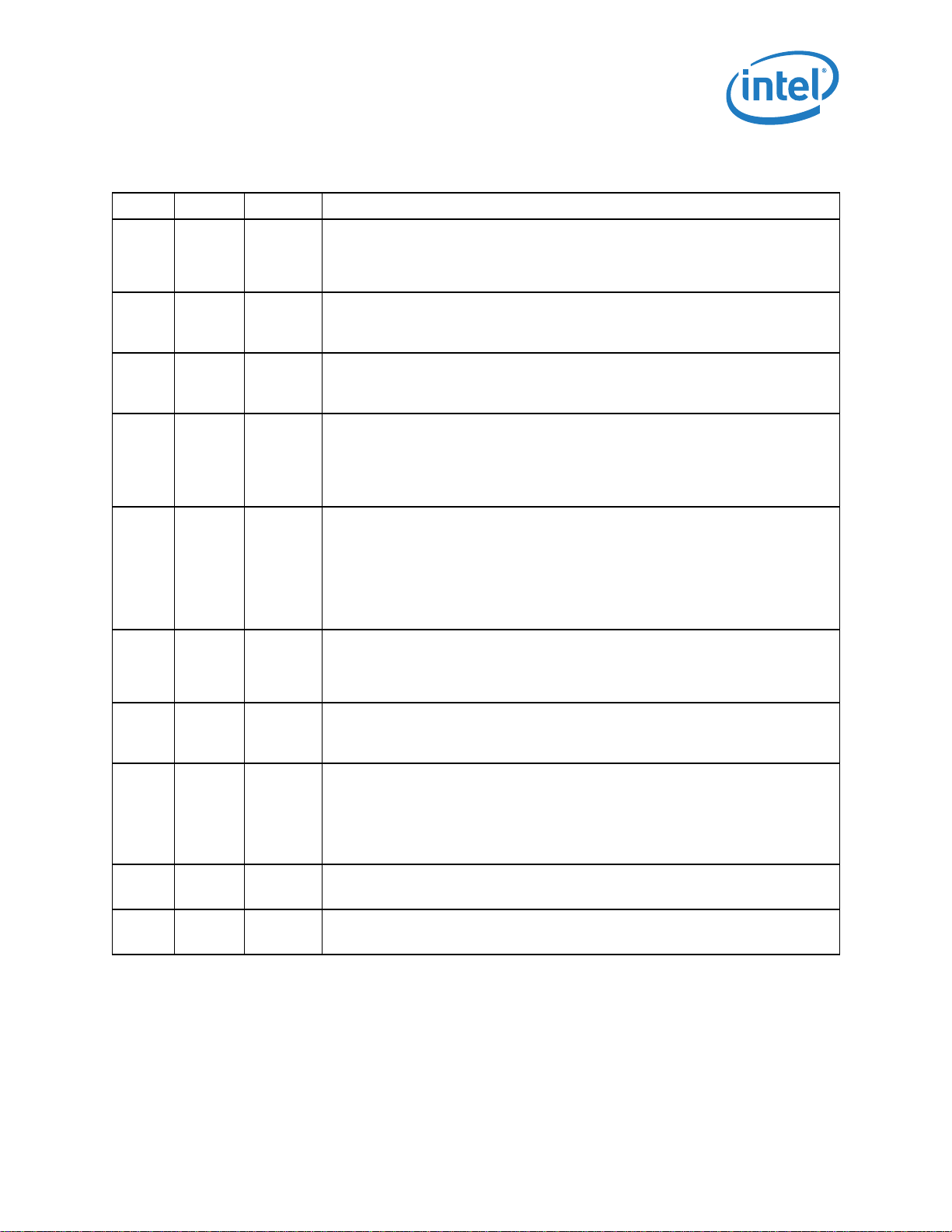

Content — Intel® 82575EB Gigabit Ethernet Controller

4.6.7.30 LAN0 IPv6 Address 0 LSB; MIPAF (Offset 47h) .................................................................. 97

4.6.7.31 LAN0 IPv6 Address 0 MSB; MIPAF (Offset 48h) ................................................................. 97

4.6.7.32 LAN0 IPv6 Address 0 LSB; MIPAF (Offset 49h) .................................................................. 98

4.6.7.33 LAN0 IPv6 Address 0 MSB; MIPAF (Offset 4Ah) ................................................................. 98

4.6.7.34 LAN0 IPv6 Address 0 LSB; MIPAF (Offset 4B).................................................................... 98

4.6.7.35 LAN0 IPv6 Address 0 MSB; MIPAF (Offset 4Ch) ................................................................. 98

4.6.7.36 LAN0 IPv6 Address 1; MIPAF (Offset 4Dh) ........................................................................ 98

4.6.7.37 LAN0 IPv6 Address 2; MIPAF (Offset 55h:5Ch).................................................................. 98

4.7 Software Owned EEPROM Words..................................................................................................98

4.7.1 Compatibility Fields (Word 03h:07h) ...................................................................................... 99

4.7.2 PBA Number (Words 08h, 09h) ............................................................................................. 99

5.0 Receive and Transmit Description......................................................................................... 101

5.1 82575 Data Flows.................................................................................................................... 101

5.1.1 Transmit Data Flow ............................................................................................................101

5.2 Receive Data Flow ................................................................................................................... 102

5.3 Receive Functionality ............................................................................................................... 102

5.3.1 Packet Address Filtering ......................................................................................................103

5.3.2 Receive Data Storage .........................................................................................................103

5.3.3 Legacy Receive Descriptor Format ........................................................................................104

5.3.3.1 Length Field ................................................................................................................104

5.3.3.2 Packet Checksum.........................................................................................................104

5.3.3.3 Receive Descriptor Status Field ...................................................................................... 105

5.3.3.4 Receive Descriptor Errors Field ......................................................................................107

5.3.3.5 VLAN Tag Field ............................................................................................................109

5.3.4 Advanced Receive Descriptors..............................................................................................109

5.3.4.1 Packet Buffer Address................................................................................................... 109

5.3.4.2 Header Buffer Address .................................................................................................. 109

5.3.4.3 Packet Type ................................................................................................................111

5.3.4.4 RSS Type.................................................................................................................... 111

5.3.4.5 Split Header ................................................................................................................ 111

5.3.4.6 Packet Checksum.........................................................................................................112

5.3.4.7 RSS Hash Value ...........................................................................................................113

5.3.4.8 Extended Status ..........................................................................................................113

5.3.4.9 Extended Errors...........................................................................................................114

5.3.4.10 Packet Buffer (Number of Bytes Exists in the Host Packet Buffer) .......................................115

5.3.4.11 VLAN Tag Field ............................................................................................................116

5.3.5 Receive UDP Fragmentation Checksum..................................................................................116

5.3.6 Receive Descriptor Fetching .................................................................................................116

5.3.7 Receive Descriptor Write-Back .............................................................................................117

5.3.7.1 Receive Descriptor Packing............................................................................................ 117

5.3.8 Receive Descriptor Ring Structure.........................................................................................117

5.4 Multiple Receive Queues ........................................................................................................... 119

5.4.1 Queuing for Virtual Machine Devices (VMDq)..........................................................................120

5.4.1.1 Association Through MAC Address ..................................................................................120

5.4.1.2 Association Through MAC Address + RSS ........................................................................121

5.4.1.3 Association through VLAN tag ID.................................................................................... 121

5.4.1.4 Association through VLAN tag ID +RSS ...........................................................................121

5.4.2 Multiple Receive Queues & Receive-Side Scaling (RSS) ............................................................122

5.4.2.1 RSS Hash Function.......................................................................................................122

5.4.2.1.1 Hash for IPv4 with TCP ..............................................................................................124

5.4.2.1.2 Hash for IPv4 with UDP.............................................................................................. 125

5.4.2.1.3 Hash for IPv4 without TCP.......................................................................................... 125

5.4.2.1.4 Hash for IPv6 with TCP ..............................................................................................125

5.4.2.1.5 Hash for IPv6 with UDP.............................................................................................. 125

5.4.2.1.6 Hash for IPv6 without TCP.......................................................................................... 125

5.4.2.2 Indirection Table.......................................................................................................... 125

5.4.2.3 Support for Multiple Processors ...................................................................................... 126

5.4.3 RSS Verification Suite .........................................................................................................126

5.4.3.1 IPv4...........................................................................................................................126

5.4.3.2 IPv6...........................................................................................................................126

®

324632-003 Intel

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 7

82575EB Gigabit Ethernet Controller

Page 8

Intel® 82575EB Gigabit Ethernet Controller — Content

5.5 Header Splitting and Replication ................................................................................................ 127

5.5.1 Receive Packet Checksum Offloading ................................................................................... 130

5.5.1.1 MAC Address Filter .......................................................................................................131

5.5.1.2 SNAP/VLAN Filter .........................................................................................................131

5.5.1.3 IPv4 Filter ...................................................................................................................131

5.5.1.4 IPv6 Filter ...................................................................................................................131

5.5.1.5 IPv6 Extension Headers ................................................................................................132

5.5.1.6 UDP/TCP Filter.............................................................................................................133

5.6 Packet Transmission ................................................................................................................ 133

5.6.1 Transmit Data Storage ....................................................................................................... 134

5.6.2 Transmit Contexts ............................................................................................................. 134

5.6.3 Transmit Descriptors.......................................................................................................... 135

5.6.4 Legacy Transmit Descriptor Format...................................................................................... 135

5.6.5 Transmit Descriptor Write Back Format ................................................................................ 136

5.6.5.1 Length........................................................................................................................136

5.6.5.2 Checksum Offset and Start (CSO and CSS)...................................................................... 136

5.6.5.3 Command Byte (CMD) .................................................................................................. 137

5.6.5.4 Transmit Descriptor Status Field Format.......................................................................... 139

5.6.6 Transmit Descriptor Special Field Format .............................................................................. 139

5.6.7 Advanced Transmit Context Descriptor ................................................................................. 140

5.6.7.1 Maximum Segment Size (MSS) Control ...........................................................................141

5.6.8 Advanced Transmit Data Descriptor ..................................................................................... 142

5.6.8.1 Address ......................................................................................................................142

5.6.8.2 DTALEN ......................................................................................................................142

5.6.8.3 DTYP ..........................................................................................................................142

5.6.8.4 DCMD.........................................................................................................................143

5.6.8.5 STA............................................................................................................................144

5.6.8.6 IDX ............................................................................................................................144

5.6.8.7 POPTS ........................................................................................................................ 144

5.6.8.8 PAYLEN.......................................................................................................................144

5.7 Transmit Descriptor Ring Structure ............................................................................................ 144

5.7.1 Transmit Descriptor Fetching .............................................................................................. 146

5.7.2 Transmit Descriptor Write-Back ........................................................................................... 146

5.8 TCP Segmentation ................................................................................................................... 147

5.8.1 Assumptions..................................................................................................................... 148

5.8.2 Transmission Process......................................................................................................... 148

5.8.2.1 TCP Segmentation Data Fetch Control............................................................................. 148

5.8.3 TCP Segmentation Performance .......................................................................................... 148

5.8.4 Packet Format .................................................................................................................. 149

5.8.5 TCP Segmentation Indication .............................................................................................. 149

5.8.6 IP and TCP/UDP Headers .................................................................................................... 151

5.8.7 IP/TCP/UDP Header Updating.............................................................................................. 156

5.8.7.1 TCP/IP/UDP Header for the First Frame ........................................................................... 157

5.8.7.2 TCP/IP/UDP Header for the Subsequent Frames ...............................................................157

5.8.7.3 TCP/IP/UDP Header for the Last Frame ...........................................................................158

5.9 IP/TCP/UDP Transmit Checksum Offloading ................................................................................. 158

5.10 IP/TCP/UDP Transmit Checksum Offloading in Non-Segmentation Mode .......................................... 159

5.10.1 IP Checksum .................................................................................................................... 159

5.10.2 TCP Checksum .................................................................................................................. 160

5.11 Multiple Transmit Queues ......................................................................................................... 160

5.12 Tx Completions Head Write-Back ............................................................................................... 161

5.13 Interrupts............................................................................................................................... 162

5.13.1 Interrupt Cause Register (ICR)............................................................................................ 162

5.13.2 Interrupt Cause Set Register (ICS) ...................................................................................... 163

5.13.3 Interrupt Mask Set/Read Register (IMS) ............................................................................... 163

5.13.4 Interrupt Mask Clear Register (IMC)..................................................................................... 163

5.13.5 Interrupt Acknowledge Auto-mask register (IAM)................................................................... 163

5.13.6 Extended Interrupt Cause Registers (EICR)........................................................................... 163

5.13.7 Extended Interrupt Cause Set Register (EICS)....................................................................... 164

Intel® 82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

8 January 2011

Page 9

Content — Intel® 82575EB Gigabit Ethernet Controller

5.13.8 Extended Interrupt Mask Set and Read Register (EIMS)/Extended Interrupt Mask Clear Register (EIMC)

164

5.13.9 Extended Interrupt Auto Clear Enable Register (EIAC).............................................................164

5.13.10 Extended Interrupt Auto Mask Enable Register (EIAM).............................................................164

5.13.11 Interrupt Modes Setting Bits ................................................................................................165

5.14 Interrupt Moderation................................................................................................................ 165

5.15 Clearing Interrupt Causes ......................................................................................................... 168

5.15.1 Auto-Clear.........................................................................................................................168

5.15.2 Write to Clear ....................................................................................................................169

5.15.3 Read to Clear.....................................................................................................................169

5.16 Dynamic Interrupt Moderation................................................................................................... 169

5.16.1 TCP Timer Interrupt............................................................................................................170

5.17 Memory Error Correction and Detection ...................................................................................... 170

6.0 PCIe* Local Bus Interface..................................................................................................... 173

6.1 General Functionality ............................................................................................................... 173

6.1.1 Message Handling (Receive Side) .........................................................................................173

6.1.2 Message Handling (Transmit Side)........................................................................................173

6.1.3 Data Alignment ..................................................................................................................174

6.1.3.1 4 KB Boundary ............................................................................................................174

6.1.4 Transaction Attributes.........................................................................................................174

6.1.4.1 Traffic Class and Virtual Channels................................................................................... 174

6.1.4.2 Relaxed Ordering ......................................................................................................... 175

6.1.4.3 Snoop Not Required .....................................................................................................175

6.1.4.3.1 No Snoop and Relaxed Ordering for LAN Traffic.............................................................175

6.1.4.3.2 No Snoop Option for Payload ......................................................................................175

6.2 Flow Control ........................................................................................................................... 176

6.2.1 Flow Control Rules..............................................................................................................176

6.2.2 Upstream Flow Control Tracking ...........................................................................................176

6.2.3 Flow Control Update Frequency ............................................................................................177

6.2.4 Flow Control Timeout Mechanism..........................................................................................177

6.2.5 Error Forwarding ................................................................................................................177

6.3 Host Interface......................................................................................................................... 177

6.3.1 Tag IDs.............................................................................................................................177

6.3.2 Completion Timeout Mechanism ...........................................................................................181

6.4 Error Events and Error Reporting ............................................................................................... 182

6.4.1 Error Events ......................................................................................................................182

6.4.2 Error Pollution....................................................................................................................184

6.4.3 Unsuccessful Completion Status ..........................................................................................184

6.4.4 Error Reporting Changes .....................................................................................................184

6.5 Link Layer .............................................................................................................................. 185

6.5.1 ACK/NAK Scheme...............................................................................................................185

6.5.2 Supported DLLPs................................................................................................................185

6.5.3 Transmit EDB Nullifying.......................................................................................................186

6.6 Physical Layer ......................................................................................................................... 186

6.6.1 Link Width.........................................................................................................................186

6.6.1.1 Polarity Inversion.........................................................................................................187

6.6.1.2 L0s Exit latency ...........................................................................................................187

6.6.1.3 Lane-to-Lane De-Skew .................................................................................................187

6.6.1.4 Lane Reversal.............................................................................................................. 187

6.6.1.5 Reset .........................................................................................................................188

6.6.1.6 Scrambler Disable ........................................................................................................188

6.6.2 Performance Monitoring ......................................................................................................188

6.6.3 Configuration Registers .......................................................................................................188

6.6.3.1 PCI Compatibility .........................................................................................................188

6.6.4 Mandatory PCI Configuration Registers.................................................................................. 189

6.6.5 PCI Power Management Registers.........................................................................................195

6.6.5.1 Message Signaled Interrupt (MSI) Configuration Registers .................................................197

6.6.5.2 MSI-X Configuration ..................................................................................................... 198

6.6.5.3 PCIe* Configuration Registers........................................................................................ 201

6.6.5.3.1 PCIe* Extended Configuration Space ...........................................................................210

®

324632-003 Intel

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 9

82575EB Gigabit Ethernet Controller

Page 10

Intel® 82575EB Gigabit Ethernet Controller — Content

6.6.5.3.2 Advanced Error Reporting Capability............................................................................211

6.6.5.3.3 Device Serial Number ................................................................................................211

7.0 Power Management .............................................................................................................. 215

7.1 Power States .......................................................................................................................... 215

7.2 Auxiliary Power ....................................................................................................................... 216

7.3 Form Factor Power Limits ......................................................................................................... 216

7.4 Power Management Interconnects ............................................................................................. 217

7.4.0.1 PCIe* Link Power Management ......................................................................................217

7.4.0.2 NC-SI Clock Control .....................................................................................................219

7.4.0.3 PHY Power Management ...............................................................................................219

7.4.0.3.1 Link Speed Control ....................................................................................................219

7.4.0.3.2 D0a State ................................................................................................................220

7.4.0.3.3 Non-D0a State..........................................................................................................221

7.4.0.3.4 Link Energy Detect ....................................................................................................221

7.4.0.3.5 PHY Power-Down State .............................................................................................. 221

7.4.0.3.6 SerDes/SGMII Power-Down State................................................................................222

7.4.1 Power States .................................................................................................................... 222

7.4.1.1 Dr State .....................................................................................................................222

7.4.1.1.1 Dr Disable Mode .......................................................................................................222

7.4.1.1.2 Entry to Dr State ......................................................................................................223

7.4.1.2 D0 Uninitialized State ...................................................................................................223

7.4.1.2.1 Entry to D0u State ....................................................................................................223

7.4.1.3 D0 Active State............................................................................................................224

7.4.1.3.1 Entry to D0a State ....................................................................................................224

7.4.1.4 D3 State .....................................................................................................................224

7.4.1.4.1 Entry to D3 State......................................................................................................224

7.4.1.4.2 Master Disable.......................................................................................................... 225

7.4.1.5 Link-Disconnect ...........................................................................................................225

7.4.2 Power-State Transitions Timing ........................................................................................... 226

7.4.2.1 Power Up (Off to Dup to D0u to D0a).............................................................................. 226

7.4.2.2 Transition from D0a to D3 and Back without PE_RST_N.....................................................227

7.4.2.3 Transition from D0a to D3 and Back with PE_RST_N .........................................................228

7.4.2.4 D0a to Dr and Back without Transition to D3 ...................................................................229

7.4.2.5 Timing Requirements.................................................................................................... 229

7.4.2.6 Timing Guarantees .......................................................................................................230

7.4.3 82575 and SerDes Power-Down State .................................................................................. 230

7.4.3.1 SerDes Power-Down State.............................................................................................230

7.4.3.2 82575 Power-Down State.............................................................................................. 231

7.5 Wake Up ................................................................................................................................ 231

7.5.1 Advanced Power Management Wakeup................................................................................. 231

7.5.2 PCIe Power Management Wakeup........................................................................................ 232

7.5.3 Wake-Up Packets .............................................................................................................. 233

7.5.3.1 Pre-Defined Filters .......................................................................................................233

7.5.3.1.1 Directed Exact Packet ................................................................................................ 233

7.5.3.1.2 Directed Multicast Packet ...........................................................................................233

7.5.3.1.3 Broadcast ................................................................................................................234

7.5.3.1.4 Magic Packet* ..........................................................................................................234

7.5.3.1.5 ARP/IPv4 Request Packet ........................................................................................... 235

7.5.3.1.6 Directed IPv4 Packet .................................................................................................235

7.5.3.1.7 Directed IPv6 Packet .................................................................................................236

7.5.3.2 Flexible Filter...............................................................................................................236

7.5.3.2.1 IPX Diagnostic Responder Request Packet ....................................................................237

7.5.3.2.2 Directed IPX Packet...................................................................................................237

7.5.3.2.3 IPv6 Neighbor Discovery Filter ....................................................................................238

7.5.3.3 Wake Up Packet Storage ............................................................................................... 238

8.0 DCA ...................................................................................................................................... 239

8.1 Implementation Details ............................................................................................................ 239

8.1.1 PCIe* Message Format for DCA (MWr Mode) ......................................................................... 239

Intel® 82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

10 January 2011

Page 11

Content — Intel® 82575EB Gigabit Ethernet Controller

9.0 Ethernet Interface ................................................................................................................ 241

9.1 Internal MAC/PHY 10/100/1000Base-T Interface.......................................................................... 242

9.1.1 MDIO/MDC ........................................................................................................................242

9.2 Duplex Operation for Copper PHY Operation ................................................................................ 243

9.2.1 Full Duplex ........................................................................................................................243

9.2.2 Half Duplex .......................................................................................................................244

9.2.3 Gigabit Physical Coding Sub-Layer (PCS) for SerDes ...............................................................244

9.2.3.1 8B10B Encoding/Decoding ............................................................................................244

9.2.3.2 Code Groups and Ordered Sets ...................................................................................... 245

9.2.4 SGMII Encoding in 10/100 Mb/s ...........................................................................................245

9.3 Auto-Negotiation and Link Setup ............................................................................................... 246

9.3.1 SerDes Link Configuration ...................................................................................................246

9.3.1.1 SerDes Mode Auto-Negotiation ......................................................................................246

9.3.1.2 PCS Hardware Auto-Negotiation ..................................................................................... 247

9.3.1.3 Forcing Link ................................................................................................................ 247

9.3.1.4 Hardware Detection of Non-Auto-Negotiation Partner........................................................248

9.3.1.5 SGMII Auto-Negotiation ................................................................................................ 248

9.3.2 Copper PHY Link Configuration .............................................................................................249

9.3.2.1 PHY Auto-Negotiation (Speed, Duplex, and Flow Control) ..................................................249

9.3.2.2 MAC Speed Resolution .................................................................................................. 249

9.3.2.2.1 Forcing MAC Speed ...................................................................................................249

9.3.2.2.2 Using Internal PHY Direct Link-Speed Indication............................................................250

9.3.2.3 MAC Full/Half Duplex Resolution ....................................................................................250

9.3.2.4 Using PHY Registers .....................................................................................................250

9.3.2.5 Comments Regarding Forcing Link.................................................................................. 251

9.3.3 Loss of Signal/Link Status Indication.....................................................................................251

9.3.4 Flow Control ......................................................................................................................251

9.3.4.1 MAC Control Frames and Reception of Flow Control Packets ............................................... 252

9.3.5 Discard PAUSE Frames and Pass MAC Control Frames .............................................................254

9.3.6 Transmission of PAUSE Frames ............................................................................................254

9.3.7 Software Initiated PAUSE Frame Transmission........................................................................255

9.4 Loopback Support.................................................................................................................... 255

9.4.1 MAC Loopback ...................................................................................................................256

9.4.1.1 Setting the 82575 to MAC Loopback Mode ....................................................................... 256

9.4.2 Internal PHY Loopback ........................................................................................................256

9.4.2.1 Setting the 82575 to Internal PHY Loopback Mode............................................................256

9.4.3 Internal SerDes Loopback....................................................................................................257

9.4.3.1 Setting Internal SerDes Loopback Mode ..........................................................................257

9.4.4 External PHY Loopback........................................................................................................257

9.4.4.1 Setting External PHY Loopback Mode ..............................................................................258

10.0 802.1q VLAN Support............................................................................................................ 259

10.1 802.1q VLAN Packet Format...................................................................................................... 259

10.1.1 802.1q Tagged Frames .......................................................................................................259

10.2 Transmitting and Receiving 802.1q Packets................................................................................. 260

10.2.1 Adding 802.1q Tags on Transmits.........................................................................................260

10.2.2 Stripping 802.1q Tags on Receives .......................................................................................261

10.3 802.1q VLAN Packet Filtering .................................................................................................... 261

10.4 Double VLAN Support............................................................................................................... 262

11.0 PHY Functionality and Features ............................................................................................ 263

11.1 Auto MDIO Register Initialization ............................................................................................... 263

11.1.1 General Register Initialization ..............................................................................................263

11.1.2 Visible Mirror Bit Initialization...............................................................................................263

11.2 Determining Link State............................................................................................................. 264

11.2.1 False Link..........................................................................................................................264

11.2.2 Forced Operation................................................................................................................265

11.2.3 Auto Negotiation ................................................................................................................265

11.2.4 Parallel Detection ...............................................................................................................266

11.2.5 Auto Cross-Over ................................................................................................................266

11.2.5.1 Support for Different Board Layouts ...............................................................................266

®

324632-003 Intel

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 11

82575EB Gigabit Ethernet Controller

Page 12

Intel® 82575EB Gigabit Ethernet Controller — Content

11.3 Link Criteria............................................................................................................................ 267

11.3.1 1000BASE-T ..................................................................................................................... 267

11.3.2 100BASE-TX..................................................................................................................... 267

11.3.3 10BASE-T......................................................................................................................... 267

11.4 Link Enhancements.................................................................................................................. 267

11.4.1 SmartSpeed ..................................................................................................................... 267

11.4.1.1 Using SmartSpeed .......................................................................................................268

11.4.2 Flow Control ..................................................................................................................... 268

11.5 Management Data Interface ...................................................................................................... 269

11.6 Low Power Operation ............................................................................................................... 269

11.7 Power Down via the PHY Register .............................................................................................. 269

11.8 1000 Mb/s Operation ............................................................................................................... 269

11.8.1 Transmit Functions ............................................................................................................ 270

11.8.1.1 Scrambler ................................................................................................................... 270

11.8.2 Transmit FIFO................................................................................................................... 271

11.8.2.1 Transmit Phase-Locked Loop PLL.................................................................................... 271

11.8.2.2 Trellis Encoder.............................................................................................................271

11.8.2.3 4DPAM5 Encoder..........................................................................................................271

11.8.2.4 Spectral Shaper ........................................................................................................... 271

11.8.2.5 Low-Pass Filter ............................................................................................................272

11.8.2.6 Line Driver ..................................................................................................................272

11.8.2.7 Transmit/Receive Flow..................................................................................................272

11.8.3 Receive Functions.............................................................................................................. 273

11.8.3.1 Hybrid ........................................................................................................................ 273

11.8.3.2 Automatic Gain Control .................................................................................................273

11.8.3.3 Timing Recovery ..........................................................................................................273

11.8.3.4 Analog-to-Digital Converter ........................................................................................... 273

11.8.3.5 Digital Signal Processor.................................................................................................273

11.8.3.6 Descrambler................................................................................................................ 273

11.8.3.7 Viterbi Decoder/Decision Feedback Equalizer (DFE)...........................................................274

11.8.3.8 4DPAM5 Decoder .........................................................................................................274

11.9 100 Mb/s Operation ................................................................................................................. 274

11.10 10 Mb/s Operation ................................................................................................................... 274

11.10.1 Link Test.......................................................................................................................... 274

11.10.2 10Base-T Link Failure Criteria and Override .......................................................................... 275

11.10.3 Jabber ............................................................................................................................. 275

11.10.4 Polarity Correction............................................................................................................. 275

11.10.5 Dribble Bits ...................................................................................................................... 275

12.0 Configurable LED Outputs..................................................................................................... 277

13.0 Dual Port Characteristics ...................................................................................................... 279

13.1 Features of Each MAC .............................................................................................................. 279

13.1.1 PCIe* Interface................................................................................................................. 279

13.1.2 MAC Configuration Register Space ....................................................................................... 281

13.1.3 SDP, LED, INT# Output...................................................................................................... 281

13.2 Shared EEPROM ...................................................................................................................... 281

13.3 Shared FLASH ......................................................................................................................... 281

13.3.1 FLASH Access Contention ................................................................................................... 281

13.4 Link Mode/Configuration........................................................................................................... 282

13.5 LAN Disable ............................................................................................................................ 282

13.5.1 Overview ......................................................................................................................... 282

13.5.2 Multi-Function Advertisement.............................................................................................. 283

13.5.3 Legacy Interrupt Use ......................................................................................................... 283

13.5.4 Power Reporting................................................................................................................ 283

13.6 Device Disable ........................................................................................................................ 283

13.6.1 BIOS Handling of Device Disable ......................................................................................... 284

13.7 Copper/Fiber Switch................................................................................................................. 284