5

www.schematic-x.blogspot.com

4

3

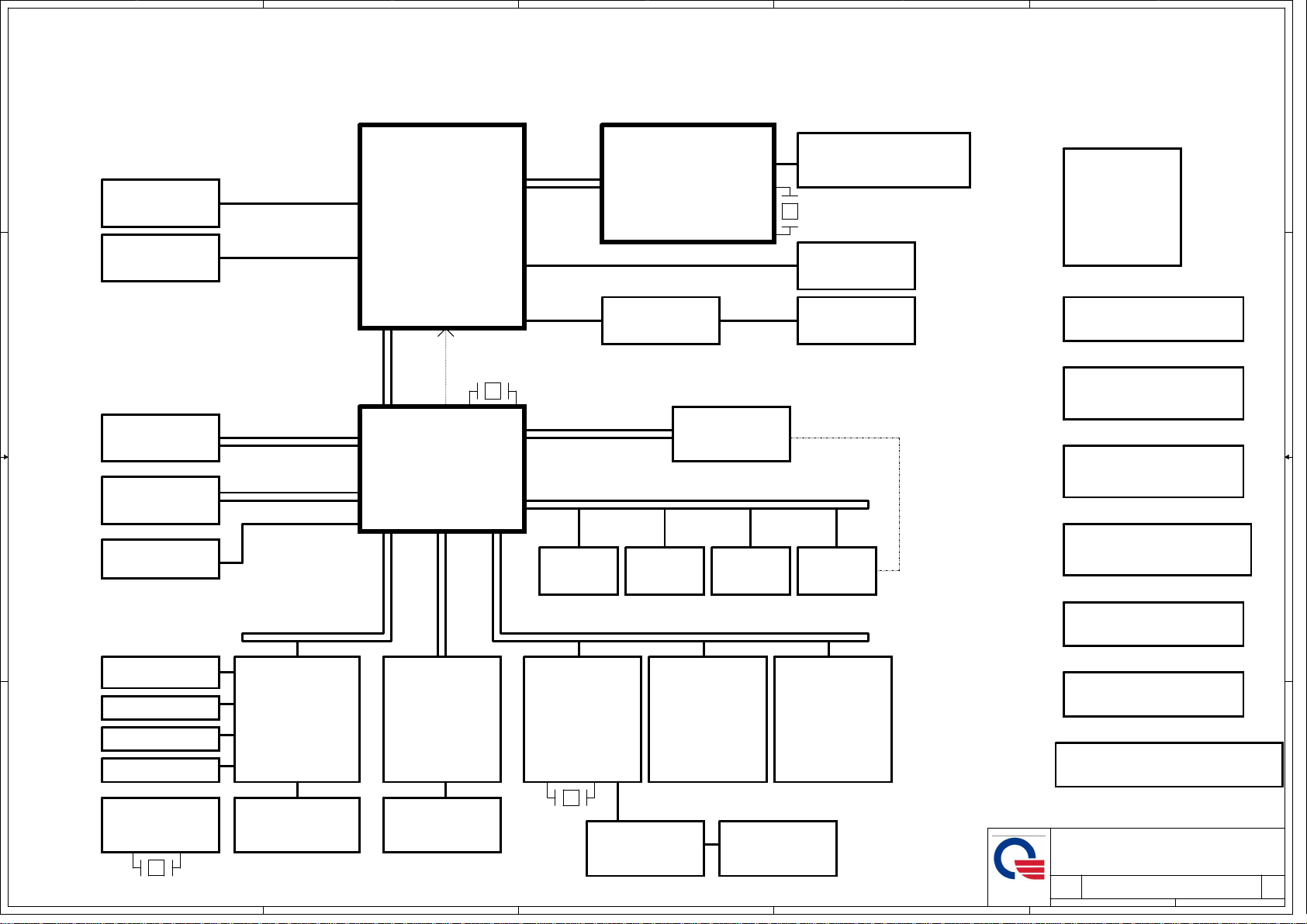

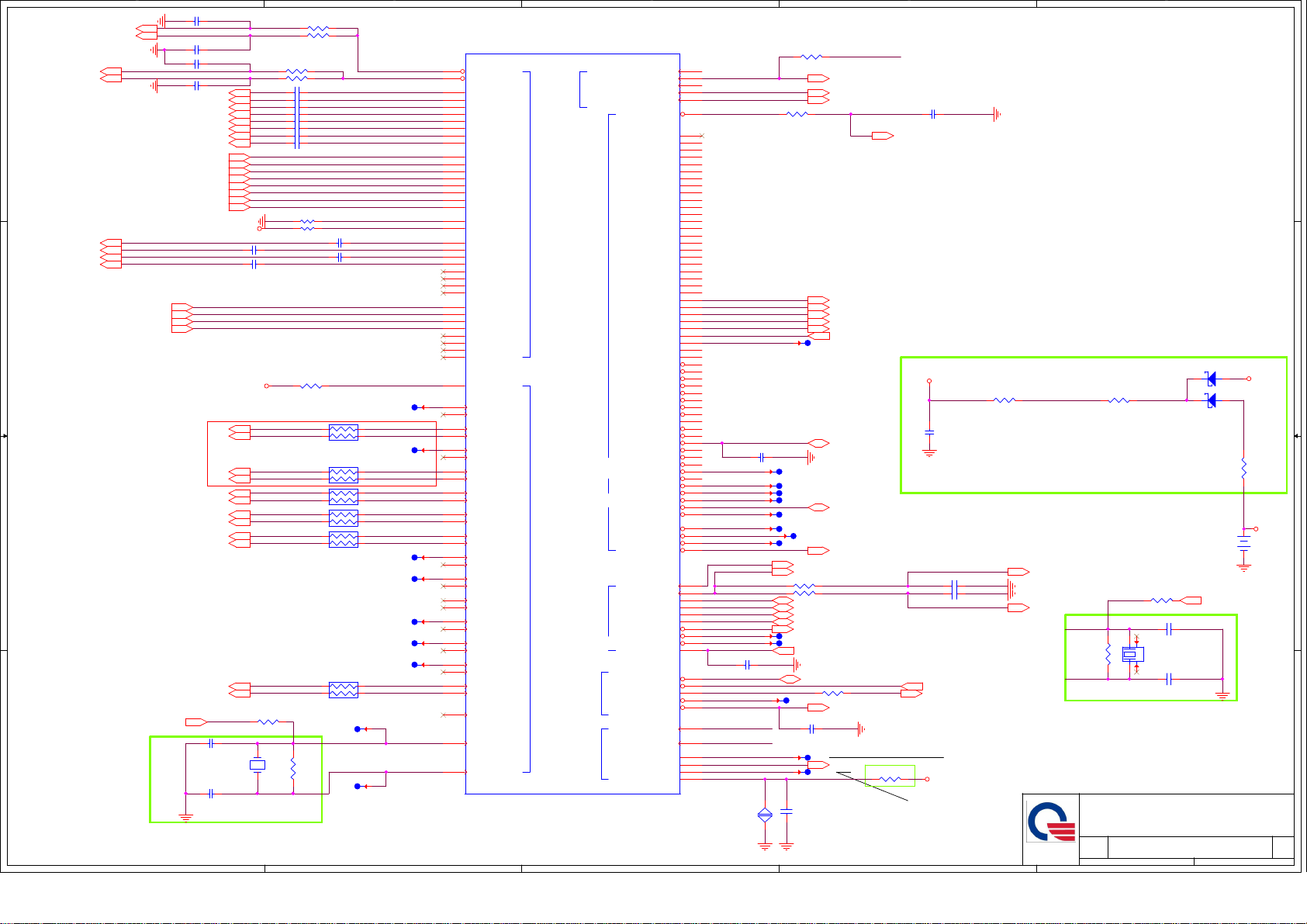

Volks_AMD Comal DIS/UMA (14")

2

Ultra/Slim

1

01

D D

AMD APU

PCI-E Gen3

x 8 Lane

DDR3 SODIMM1

Maxima 4GBs

DDR3 800 ~ 1600 MT/s

PAGE 12

DDR3 SO-DIMM2

Maxima 4GBs

DDR3 800 ~ 1600 MT/s

PAGE 13

C C

Processor : TRINITY Daul /

Quad Core

Power : 25 (Watt)

Package : FP2 827-PIN BGA

Size : 27 x 31 (mm)

IME

PAGE 02-05

Green CLK

UMI x 4

32.768KHz

PAGE 27

DP Port2

DP Port0

AIT Mars PRO

Power : 25 (Watt)

Package : M2

Size : 29 x 29 (mm)

RTD2132S

DP to LVDS

Translator

PAGE 11

PAGE 14-20

VRAM DDR3 x 8 (900 MHz)

128 x 16 x 8, 64 bit

Max 1GBs/2GBs

27MHz

PAGE 16

PAGE 21-22

HDMI Conn

PAGE 30

LCD Conn (15.6")

PAGE 30

BCLK133M

SATA - 1st HDD

Package : 9.5 (mm)

Power :

PAGE 28

mSATA

Package : 12.7 (mm)

Power :

PAGE 28

SATA0 6GB/s

SATA1 6GB/s

SPI Interface

AMD FCH

Hudson M3

Power : 4.7 Watt

Package : 656pin FCBGA

Size : 24.5 x 24.5 (mm)

PAGE 06-10

USB3.0 Interface

PORT0, 1

USB2.0 Interface

USB 2.0/3.0

Combo x 2

USB2.0 x 2

PAGE 26

System BIOS

B B

SPI ROM

PAGE 08

Azalia

Camera External USB BT USB2.0 x 2

8 10, 1120

PAGE 30 PAGE 23 PAGE 27 PAGE 26

PCIE Gen 1 x 1 LaneLPC Interface

PCB 6L STACK UP

LAYER 1 : TOP

LAYER 2 : SGND

LAYER 3 : IN1(High)

LAYER 4 : IN2(Low)

LAYER 5 : SVCC

LAYER 6 : BOT

Power Source

BQ24728

System Charge Power (+BATCHG)

G5934RZ1U

System Discharge Power

(+1.5V/+3V/+5V)

(+3VSUSV/+3VLANVCC/+1.1V)

Ricktek RT8223PZ

System Power (+3VPCU/+5VPCU/

+3VS5/+5VS5)

ISL6277/RT8228AZ/AP3407A/ISL6208BCRZ

Processor Power (+VCC_CORE/

+1.2V/+2.5V/+VDDNB_CORE)

Richtek RT8207L

System Memory Power (+1.5VSUS/

+0.75V_DDR_VTT)

80 Port (Debug)

PAGE 25

EC SPI ROM

Keyboard

Touch Pad

A A

PAGE 29

PAGE 26

PAGE 28

SLG3NB242

iTE IT8518E/HX

Embedded Controller

Power :

Package : LQPF128

Size : 14 x 14 (mm)

PAGE 29

FAN Controller

GreenCLK

PAGE 27

25MHz

5

PAGE 28

IDT 92HD99B

Audio Codec

Power :

Package : QFN-40

Size : 5 x 5 (mm)

PAGE 23

Daughterl/B CONN

Combo Jack

PAGE 23

4

Realtek RTL8105E

LAN Controller

Power :

Package : OFN48

Size : 6 x 6 (mm)

PAGE 24

25MHz

NS681684 RJ45 Conn

TRANSFORMER

Realtek RTS5229

Card Reader

Intel Rambo Peak

Halt Mini Card

WLAN / BT Combo

Power :

Package : LQPF24

Size : 4 x 4 (mm)

Power :

Package :

Size :

PAGE 25

PAGE 24 PAGE 24

3

PAGE 27

Richtek RT8228AZ

PCH Power (+1.1VS5)

RT8152E/G5193/G5193R41U/NB650

DGPU Power (+VGA_CORE/+1.0V_VGA/+3V_VGA/

+1.5V_VGA/+1.8V_VGA/+VDDCI)

PROJECT : VOLKS_Comal 14"

PROJECT : VOLKS_Comal 14"

PROJECT : VOLKS_Comal 14"

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Docu ment Numb er Rev

Size Docu ment Numb er Rev

Size Docu ment Numb er Rev

A3

A3

A3

Block Diagram

Block Diagram

NB5

NB5

2

NB5

Block Diagram

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

1 42Thursd ay, September 20, 2012

1 42Thursd ay, September 20, 2012

1 42Thursd ay, September 20, 2012

1A

1A

1A

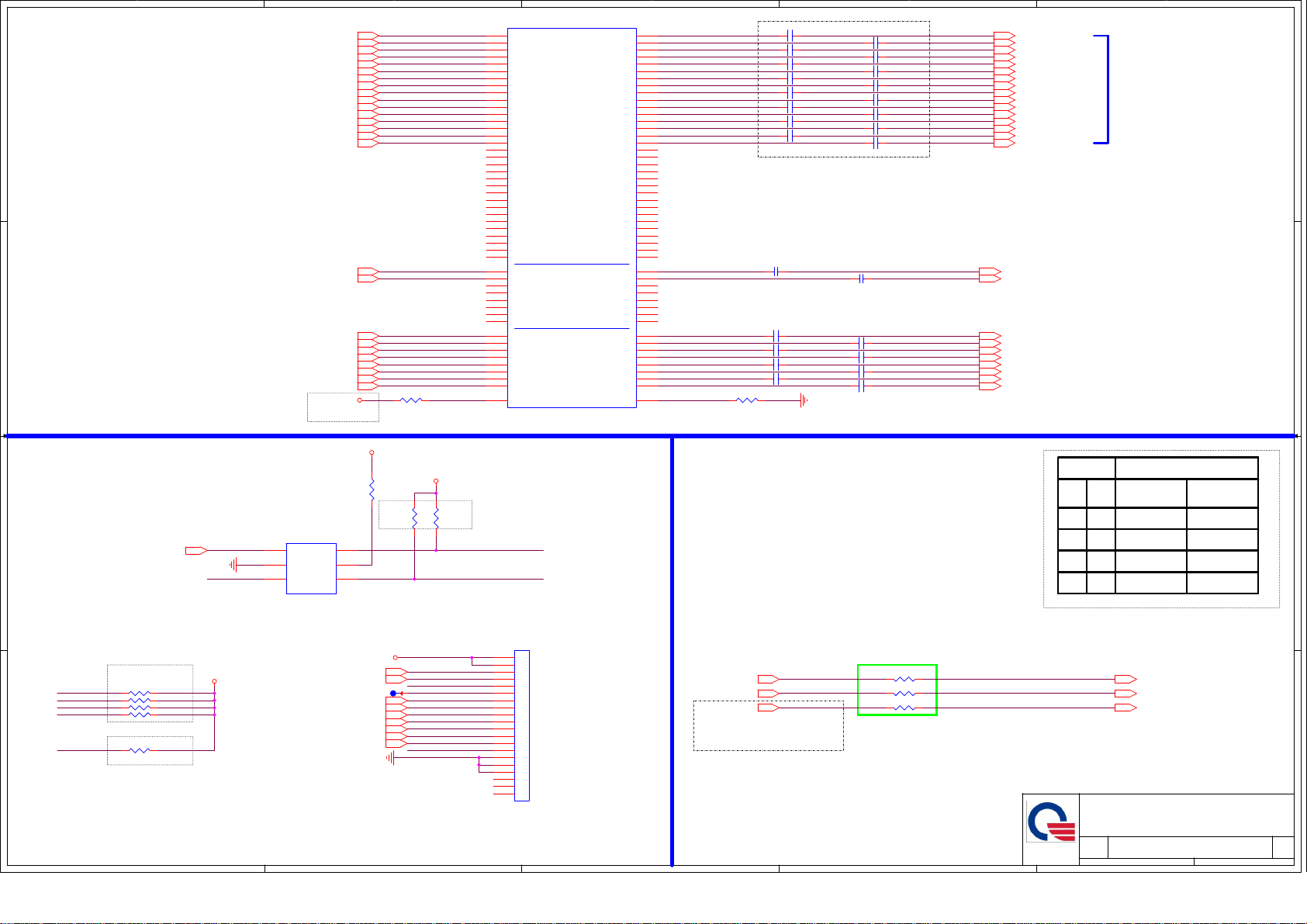

5

PEG_RXP 0[14]

PEG_RXN 0[14]

PEG_RXP 1[14]

PEG_RXN 1[14]

PEG_RXP 2[14]

PEG_RXN 2[14]

PEG_RXP 3[14]

PEG_RXN 3[14]

PEG_RXP 4[14]

PEG_RXN 4[14]

PEG_RXP 5[14]

PCIE_RX P0_WLAN[27]

PCIE_RX N0_WLAN[27]

PEG_RXN 5[14]

PEG_RXP 6[14]

PEG_RXN 6[14]

PEG_RXP 7[14]

PEG_RXN 7[14]

UMI_RX P0[7]

UMI_RX N0[7]

UMI_RX P1[7]

UMI_RX N1[7]

UMI_RX P2[7]

UMI_RX N2[7]

UMI_RX P3[7]

UMI_RX N3[7]

+1.2V_VD DP

D D

C C

4/19 For Comal.

4

PEG_RXP 0

PEG_RXN 0

PEG_RXP 1

PEG_RXN 1

PEG_RXP 2

PEG_RXN 2

PEG_RXP 3

PEG_RXN 3

PEG_RXP 4

PEG_RXN 4

PEG_RXP 5

PEG_RXN 5

PEG_RXP 6

PEG_RXN 6

PEG_RXP 7

PEG_RXN 7

PCIE_RX P0_WLAN

R422 196/F_6

U27A

AP1

P_GFX_ RXP[0]

AP2

P_GFX_ RXN[0]

AM1

P_GFX_ RXP[1]

AM2

P_GFX_ RXN[1]

AK3

P_GFX_ RXP[2]

AK4

P_GFX_ RXN[2]

AJ1

P_GFX_ RXP[3]

AJ2

P_GFX_ RXN[3]

AH4

P_GFX_ RXP[4]

AH3

P_GFX_ RXN[4]

AF2

P_GFX_ RXP[5]

AF1

P_GFX_ RXN[5]

AD1

P_GFX_ RXP[6]

AD2

P_GFX_ RXN[6]

AB3

P_GFX_ RXP[7]

AB4

P_GFX_ RXN[7]

AA1

P_GFX_ RXP[8]

AA2

P_GFX_ RXN[8]

Y4

P_GFX_ RXP[9]

Y3

P_GFX_ RXN[9]

V2

P_GFX_ RXP[10]

V1

P_GFX_ RXN[10]

T1

P_GFX_ RXP[11]

T2

P_GFX_ RXN[11]

P3

P_GFX_ RXP[12]

P4

P_GFX_ RXN[12]

N1

P_GFX_ RXP[13]

N2

P_GFX_ RXN[13]

M4

P_GFX_ RXP[14]

M3

P_GFX_ RXN[14]

K2

P_GFX_ RXP[15]

K1

P_GFX_ RXN[15]

AH5

P_GPP_ RXP[0]

AH6

P_GPP_ RXN[0]

AG5

P_GPP_ RXP[1]

AG6

P_GPP_ RXN[1]

AE6

P_GPP_ RXP[2]

AE5

P_GPP_ RXN[2]

AD6

P_GPP_ RXP[3]

AD5

P_GPP_ RXN[3]

AM10

P_UMI_R XP[0]

AN10

P_UMI_R XN[0]

AN8

P_UMI_R XP[1]

AM8

P_UMI_R XN[1]

AP8

P_UMI_R XP[2]

AR8

P_UMI_R XN[2]

AR7

P_UMI_R XP[3]

AP7

P_UMI_R XN[3]

AR11

P_ZVDD P

TRINITY-A8-S ERIES_BGA81 3

P_GFX_ TXP[0]

P_GFX_ TXN[0]

P_GFX_ TXP[1]

P_GFX_ TXN[1]

P_GFX_ TXP[2]

P_GFX_ TXN[2]

P_GFX_ TXP[3]

P_GFX_ TXN[3]

P_GFX_ TXP[4]

P_GFX_ TXN[4]

P_GFX_ TXP[5]

P_GFX_ TXN[5]

P_GFX_ TXP[6]

P_GFX_ TXN[6]

P_GFX_ TXP[7]

P_GFX_ TXN[7]

P_GFX_ TXP[8]

GRAPHICSGPPUMI

P_GFX_ TXN[8]

P_GFX_ TXP[9]

P_GFX_ TXN[9]

P_GFX_ TXP[10]

P_GFX_ TXN[10]

P_GFX_ TXP[11]

P_GFX_ TXN[11]

P_GFX_ TXP[12]

P_GFX_ TXN[12]

P_GFX_ TXP[13]

P_GFX_ TXN[13]

P_GFX_ TXP[14]

P_GFX_ TXN[14]

P_GFX_ TXP[15]

P_GFX_ TXN[15]

P_GPP_ TXP[0]

P_GPP_ TXN[0]

P_GPP_ TXP[1]

P_GPP_ TXN[1]

P_GPP_ TXP[2]

P_GPP_ TXN[2]

P_GPP_ TXP[3]

P_GPP_ TXN[3]

P_UMI_T XP[0]

P_UMI_T XN[0]

P_UMI_T XP[1]

P_UMI_T XN[1]

P_UMI_T XP[2]

P_UMI_T XN[2]

P_UMI_T XP[3]

P_UMI_T XN[3]

P_ZVSS

AN1

AN2

AM4

AM3

AK2

AK1

AH1

AH2

AF3

AF4

AE1

AE2

AD4

AD3

AB2

AB1

Y1

Y2

V3

V4

U1

U2

T4

T3

P2

P1

M1

M2

K3

K4

J1

J2

AG7

AG8

AE7

AE8

AD7

AD8

AB6

AB5

AN6

AM6

AP6

AR6

AP4

AR4

AP3

AR3

AP11

3

PEG_TXP 0_C

PEG_TXN 0_C

PEG_TXP 1_C

PEG_TXN 1_C

PEG_TXP 2_C

PEG_TXN 2_C

PEG_TXP 3_C

PEG_TXN 3_C

PEG_TXP 4_C

PEG_TXN 4_C

PEG_TXP 5_C

PEG_TXN 5_C

PEG_TXP 6_C

PEG_TXN 6_C

PEG_TXP 7_C

PEG_TXN 7_C

UMI_TXP 0_C

UMI_TXN 0_C

UMI_TXP 1_C

UMI_TXN 1_C

UMI_TXP 2_C

UMI_TXN 2_C

UMI_TXP 3_C

UMI_TXN 3_C

P_ZVSSP_ZVDD P

PCIE_TX P0_C

PCIE_TX N0_CPCIE_RX N0_WLAN

R421 196/F_6

C702 *0.1U/10V_4

C665 *0.1U/10V_4

C704 *0.1U/10V_4

C667 *0.1U/10V_4

C706 *0.1U/10V_4

C669 *0.1U/10V_4

C708 *0.1U/10V_4

C672 *0.1U/10V_4

UMA ca n remov e

C245 0.1U/10V_4

C282 0.1U/10V_4

C305 0.1U/10V_4

C274 0.1U/10V_4

C263 0.1U/10V_4

C703 *0.1U/10V_4

C666 *0.1U/10V_4

C705 *0.1U/10V_4

C668 *0.1U/10V_4

C707 *0.1U/10V_4

C670 *0.1U/10V_4

C709 *0.1U/10V_4

C671 *0.1U/10V_4

C251 0.1U/10V_4

C290 0.1U/10V_4

C315 0.1U/10V_4

C279 0.1U/10V_4

C267 0.1U/10V_4

2

PEG_TXP 0

PEG_TXN 0

PEG_TXP 1

PEG_TXN 1

PEG_TXP 2

PEG_TXN 2

PEG_TXP 3

PEG_TXN 3

PEG_TXP 4

PEG_TXN 4

PEG_TXP 5

PEG_TXN 5

PEG_TXP 6

PEG_TXN 6

PEG_TXP 7

PEG_TXN 7

UMI_TXP 0

UMI_TXN 0

UMI_TXP 1

UMI_TXN 1

UMI_TXP 2

UMI_TXN 2

UMI_TXP 3

UMI_TXN 3

PEG_TXP 0 [14]

PEG_TXN 0 [1 4]

PEG_TXP 1 [14]

PEG_TXN 1 [1 4]

PEG_TXP 2 [14]

PEG_TXN 2 [1 4]

PEG_TXP 3 [14]

PEG_TXN 3 [1 4]

PEG_TXP 4 [14]

PEG_TXN 4 [1 4]

PEG_TXP 5 [14]

PEG_TXN 5 [1 4]

PEG_TXP 6 [14]

PEG_TXN 6 [1 4]

PEG_TXP 7 [14]

PEG_TXN 7 [1 4]

PCIE_TX P0_WLAN [27]

PCIE_TX N0_WLAN [27]

UMI_TXP 0 [7]

UMI_TXN 0 [7]

UMI_TXP 1 [7]

UMI_TXN 1 [7]

UMI_TXP 2 [7]

UMI_TXN 2 [7]

UMI_TXP 3 [7]

UMI_TXN 3 [7]

1

02

PEG X 8

TO WLANTO WLAN

HDT+ Connector for Debug only

+3V

+1.5V

R184

*0_4/S

R183

1K/F_4

B B

APU_TD I

APU_TC K

APU_TM S

APU_TR ST#

A A

APU_DB REQ#

APU_RS T#[4,7]

close to H DT

debug HEAD ER

R186 1K/F_4

R188 1K/F_4

R187 1K/F_4

R185 1K/F_4

R189 1K/F_4

4/19 For Comal.

5

APU_RS T# APU_RS T_L_BUF

APU_PW RGD

+1.5VSUS

U7

1

A1

2

GND

3

A2

74LVC2G 07GW

VCC

6

Y1

5

4

Y2

+1.5VSUS

APU_TE ST18[4]

APU_TE ST19[4]

TP47

APU_DB REQ#[4]

APU_DB RDY[4]

APU_TC K[4]

APU_TM S[4]

APU_TD I[4]

APU_TR ST#[4]

APU_TD O[4]

4

4/19 For Comal.

R182

1K/F_4

APU_PW ROK_BUF

APU_TE ST18

APU_TE ST19

APU_RS T_L_BUF

CPU_LD T_RST_HTP A#

APU_DB REQ#

APU_DB RDY

APU_TC K

APU_TM S

APU_TD I

APU_TR ST#

APU_TD O

APU_PW ROK_BUF

J1

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

*HDT CON N

88511-200 1-20p-l

VID Override Circuit

SVC[4]

SVD[4]

APU_PW RGD[4,7]

APU_PWRGD have pu ll up 30 0ohm

to +1.5V on pag e 4

3

Note:

To ov erride VID, Remove Rd, Re, Rf , install Rc

set VID vi a SVC & S VD option RES .

SVC

SVD

APU_PW RGD

Rd

R158 *0_4/S

Re

R161 *0_4/S

Rf

R180 *0_4/S

PV1 Ch ange to short pad

2

SVC SVD

000

1

1

CPU_SV C

CPU_SV D

CPU_PW RGD_SVID _REG

PROJECT : VOLKS_Comal 14"

PROJECT : VOLKS_Comal 14"

PROJECT : VOLKS_Comal 14"

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

NB5

NB5

NB5

Date: Sheet of

Date: Sheet of

Date: Sheet of

BOOT VO LTAGE

VFIX_+V DD

=VCC/GN D

VFIX_+V DD

=OPEN

1.1 1.1

1

1.0 1.2

0

0.9 1.0

0.8 0.8

1

CPU_SV C [39]

CPU_SV D [39]

CPU_PW RGD_SVID _REG [39]

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Llano PCIE/UMI/GPP

Llano PCIE/UMI/GPP

Llano PCIE/UMI/GPP

1

2 42Thursday, September 20, 2012

2 42Thursday, September 20, 2012

2 42Thursday, September 20, 2012

1A

1A

1A

5

4

3

2

1

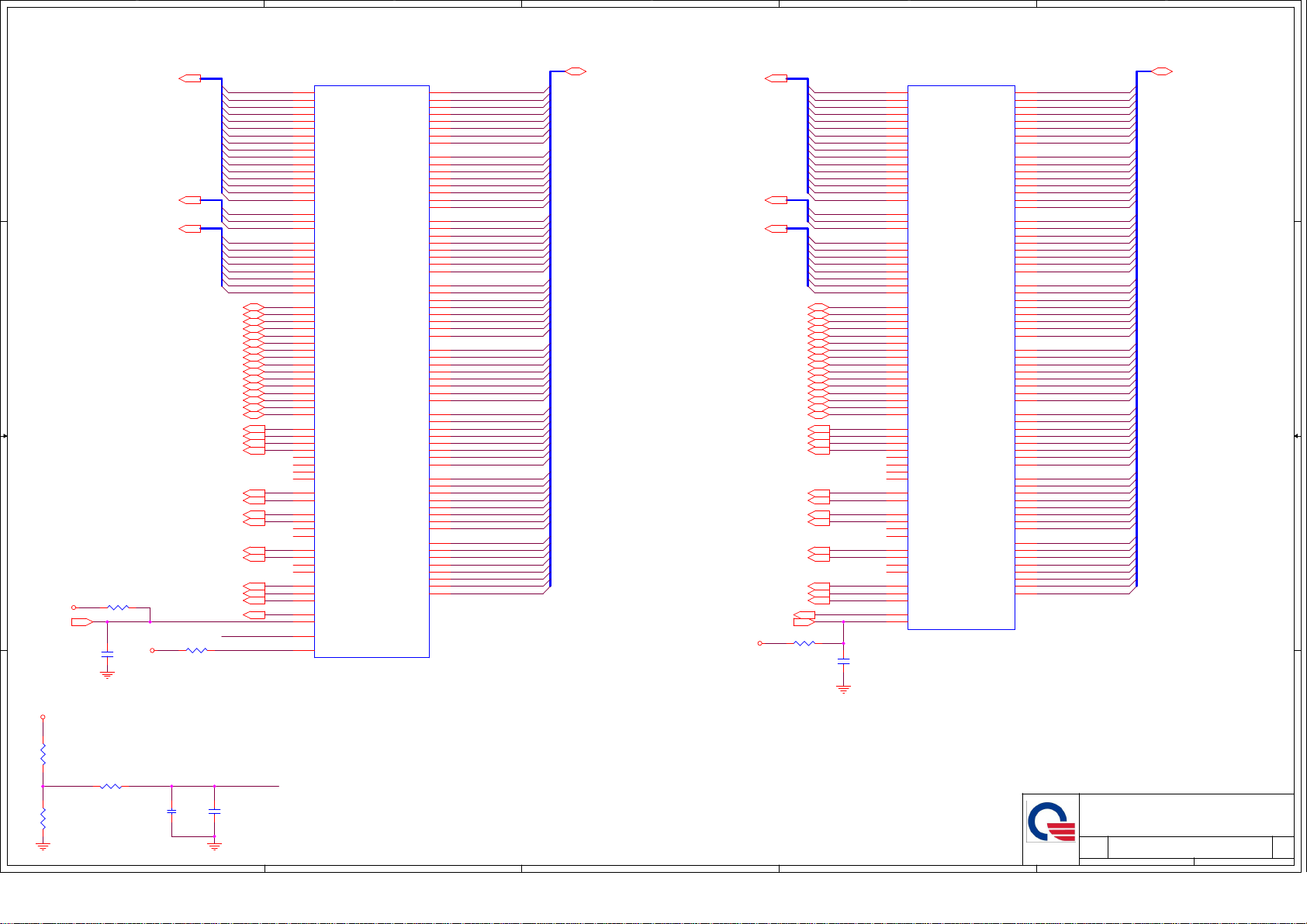

03

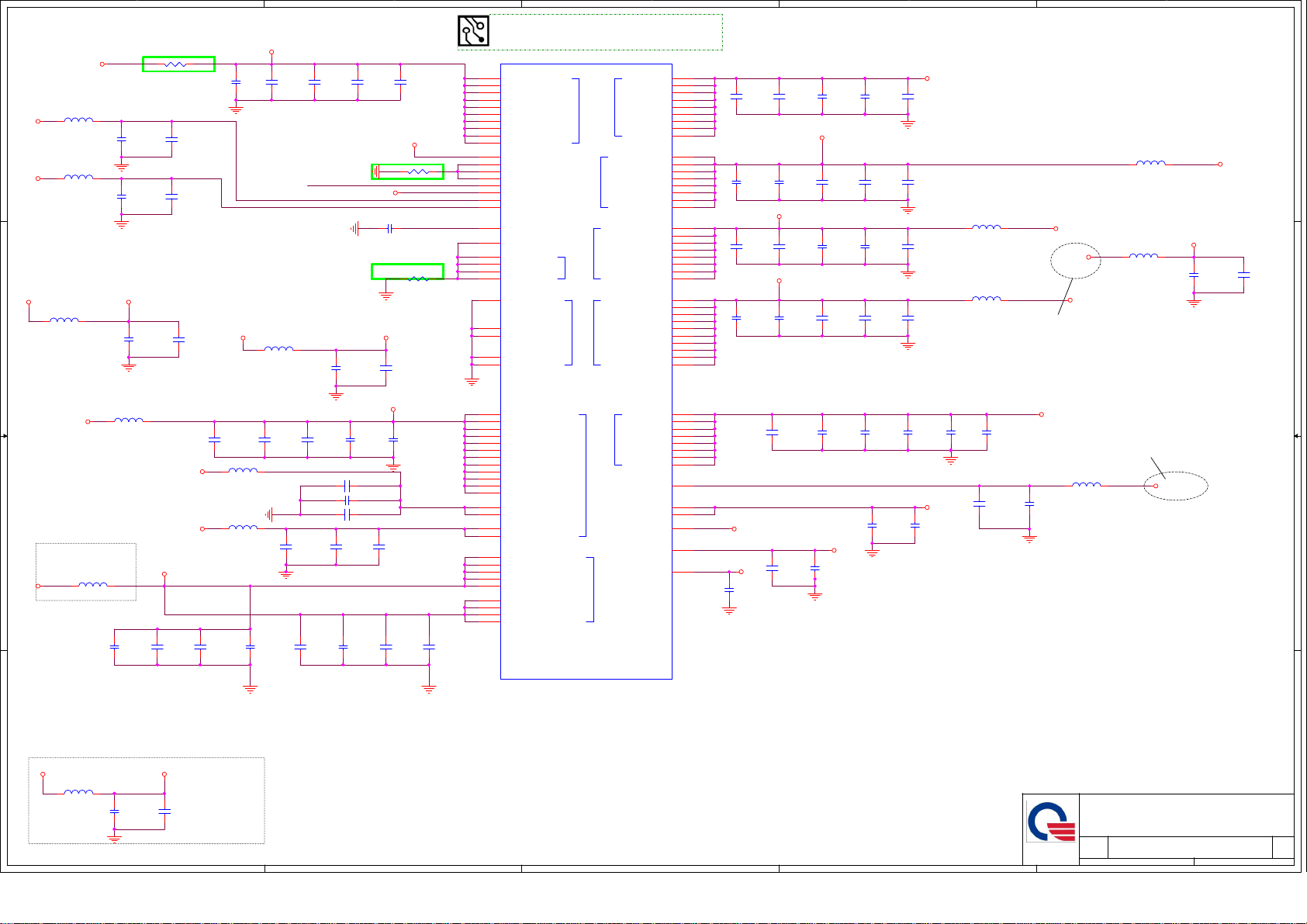

M_A_A[1 5:0][12] M_B_A[1 5:0][13]

D D

M_A_BS #[2..0][12]

M_A_DM [7..0][12]

C C

B B

+1.5VSUS

M_A_EV ENT#[12]

R222 1K/F_4

C388

220P/50V_4

+1.5VSUS

R220 39.2/F_4

Place clo se to APU w ithin 1"

M_A_DQ SP0[1 2]

M_A_DQ SN0[12]

M_A_DQ SP1[1 2]

M_A_DQ SN1[12]

M_A_DQ SP2[1 2]

M_A_DQ SN2[12]

M_A_DQ SP3[1 2]

M_A_DQ SN3[12]

M_A_DQ SP4[1 2]

M_A_DQ SN4[12]

M_A_DQ SP5[1 2]

M_A_DQ SN5[12]

M_A_DQ SP6[1 2]

M_A_DQ SN6[12]

M_A_DQ SP7[1 2]

M_A_DQ SN7[12]

M_A_CL KP0[12]

M_A_CL KN0[12]

M_A_CL KP1[12]

M_A_CL KN1[12]

M_A_CK E0[12]

M_A_CK E1[12]

M_A_OD T0[12]

M_A_OD T1[12]

M_A_CS #0[12 ]

M_A_CS #1[12 ]

M_A_RA S#[12]

M_A_CA S#[12]

M_A_W E#[12]

M_A_RS T#[12]

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A1 0

M_A_A1 1

M_A_A1 2

M_A_A1 3

M_A_A1 4

M_A_A1 5

M_A_BS #0

M_A_BS #1

M_A_BS #2

M_A_DM 0

M_A_DM 1

M_A_DM 2

M_A_DM 3

M_A_DM 4

M_A_DM 5

M_A_DM 6

M_A_DM 7

+MEMV REF_CPU

+M_ZVD DIO

U27B

AA28

MA_AD D[0]

R29

MA_AD D[1]

T30

MA_AD D[2]

R28

MA_AD D[3]

R26

MA_AD D[4]

P26

MA_AD D[5]

P27

MA_AD D[6]

P30

MA_AD D[7]

P29

MA_AD D[8]

M28

MA_AD D[9]

AB26

MA_AD D[10]

M26

MA_AD D[11]

M29

MA_AD D[12]

AE27

MA_AD D[13]

L26

MA_AD D[14]

L27

MA_AD D[15]

AB27

MA_BA NK[0]

AA29

MA_BA NK[1]

M30

MA_BA NK[2]

D16

MA_DM [0]

D20

MA_DM [1]

E25

MA_DM [2]

F30

MA_DM [3]

AK29

MA_DM [4]

AL25

MA_DM [5]

AM20

MA_DM [6]

AM16

MA_DM [7]

G17

MA_DQ S_H[0]

H17

MA_DQ S_L[0]

F22

MA_DQ S_H[1]

G22

MA_DQ S_L[1]

E26

MA_DQ S_H[2]

F26

MA_DQ S_L[2]

H30

MA_DQ S_H[3]

G30

MA_DQ S_L[3]

AL29

MA_DQ S_H[4]

AL30

MA_DQ S_L[4]

AH25

MA_DQ S_H[5]

AJ25

MA_DQ S_L[5]

AK20

MA_DQ S_H[6]

AL20

MA_DQ S_L[6]

AK15

MA_DQ S_H[7]

AL15

MA_DQ S_L[7]

W2 9

MA_CLK _H[0]

Y30

MA_CLK _L[0]

W2 6

MA_CLK _H[1]

W2 7

MA_CLK _L[1]

U29

MA_CLK _H[2]

V30

MA_CLK _L[2]

U26

MA_CLK _H[3]

U27

MA_CLK _L[3]

L29

MA_CK E[0]

K30

MA_CK E[1]

AD30

MA0_O DT[0]

AG28

MA0_O DT[1]

AE26

MA1_O DT[0]

AG29

MA1_O DT[1]

AD26

MA0_CS _L[0]

AE29

MA0_CS _L[1]

AB30

MA1_CS _L[0]

AF30

MA1_CS _L[1]

AB29

MA_RA S_L

AD29

MA_CA S_L

AD28

MA_W E_L

J28

MA_RE SET_L

AA26

MA_EV ENT_L

G32

M_VRE F

AJ32

M_ZVD DIO

TRINITY-A8-S ERIES_BGA81 3

MA_DA TA[0]

MA_DA TA[1]

MA_DA TA[2]

MA_DA TA[3]

MA_DA TA[4]

MA_DA TA[5]

MA_DA TA[6]

MA_DA TA[7]

MA_DA TA[8]

MA_DA TA[9]

MA_DA TA[10]

MA_DA TA[11]

MA_DA TA[12]

MA_DA TA[13]

MA_DA TA[14]

MA_DA TA[15]

MA_DA TA[16]

MA_DA TA[17]

MA_DA TA[18]

MA_DA TA[19]

MA_DA TA[20]

MA_DA TA[21]

MA_DA TA[22]

MA_DA TA[23]

MA_DA TA[24]

MA_DA TA[25]

MA_DA TA[26]

MA_DA TA[27]

MA_DA TA[28]

MA_DA TA[29]

MA_DA TA[30]

MA_DA TA[31]

MA_DA TA[32]

MA_DA TA[33]

MA_DA TA[34]

MA_DA TA[35]

MA_DA TA[36]

MA_DA TA[37]

MA_DA TA[38]

MA_DA TA[39]

MA_DA TA[40]

MA_DA TA[41]

MA_DA TA[42]

MA_DA TA[43]

MA_DA TA[44]

MA_DA TA[45]

MA_DA TA[46]

MA_DA TA[47]

MA_DA TA[48]

MA_DA TA[49]

MA_DA TA[50]

MA_DA TA[51]

MA_DA TA[52]

MA_DA TA[53]

MA_DA TA[54]

MA_DA TA[55]

MA_DA TA[56]

MA_DA TA[57]

MA_DA TA[58]

MA_DA TA[59]

MA_DA TA[60]

MA_DA TA[61]

MA_DA TA[62]

MA_DA TA[63]

F15

M_A_DQ 0

E15

M_A_DQ 1

H19

M_A_DQ 2

F19

M_A_DQ 3

E14

M_A_DQ 4

H15

M_A_DQ 5

E17

M_A_DQ 6

D18

M_A_DQ 7

G20

M_A_DQ 8

E20

M_A_DQ 9

H23

M_A_DQ 10

G23

M_A_DQ 11

E19

M_A_DQ 12

H20

M_A_DQ 13

E22

M_A_DQ 14

D22

M_A_DQ 15

H25

M_A_DQ 16

F25

M_A_DQ 17

D28

M_A_DQ 18

D29

M_A_DQ 19

E23

M_A_DQ 20

D24

M_A_DQ 21

D26

M_A_DQ 22

D27

M_A_DQ 23

G28

M_A_DQ 24

G29

M_A_DQ 25

H27

M_A_DQ 26

J29

M_A_DQ 27

E28

M_A_DQ 28

F27

M_A_DQ 29

H29

M_A_DQ 30

H28

M_A_DQ 31

AH29

M_A_DQ 32

AJ30

M_A_DQ 33

AM28

M_A_DQ 34

AM27

M_A_DQ 35

AH27

M_A_DQ 36

AH28

M_A_DQ 37

AJ29

M_A_DQ 38

AK27

M_A_DQ 39

AK26

M_A_DQ 40

AJ26

M_A_DQ 41

AK23

M_A_DQ 42

AJ23

M_A_DQ 43

AM26

M_A_DQ 44

AL26

M_A_DQ 45

AM24

M_A_DQ 46

AL23

M_A_DQ 47

AK22

M_A_DQ 48

AH22

M_A_DQ 49

AK19

M_A_DQ 50

AH19

M_A_DQ 51

AM22

M_A_DQ 52

AL22

M_A_DQ 53

AJ20

M_A_DQ 54

AL19

M_A_DQ 55

AK17

M_A_DQ 56

AJ17

M_A_DQ 57

AK14

M_A_DQ 58

AH14

M_A_DQ 59

AM18

M_A_DQ 60

AL17

M_A_DQ 61

AH15

M_A_DQ 62

AL14

M_A_DQ 63

Solderma sk openi ngs for all bott om side vias/TPs under FS1

M_A_DQ [0..63] [12 ] M_B_DQ [0..63] [13 ]

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A1 0

M_B_A1 1

M_B_A1 2

M_B_A1 3

M_B_A1 4

220P/50V_4

C389

M_B_A1 5

M_B_BS #0

M_B_BS #1

M_B_BS #2

M_B_DM 0

M_B_DM 1

M_B_DM 2

M_B_DM 3

M_B_DM 4

M_B_DM 5

M_B_DM 6

M_B_DM 7

M_B_BS #[2..0][13]

M_B_DM [7..0][13]

+1.5VSUS

M_B_DQ SP0[1 3]

M_B_DQ SN0[13]

M_B_DQ SP1[1 3]

M_B_DQ SN1[13]

M_B_DQ SP2[1 3]

M_B_DQ SN2[13]

M_B_DQ SP3[1 3]

M_B_DQ SN3[13]

M_B_DQ SP4[1 3]

M_B_DQ SN4[13]

M_B_DQ SP5[1 3]

M_B_DQ SN5[13]

M_B_DQ SP6[1 3]

M_B_DQ SN6[13]

M_B_DQ SP7[1 3]

M_B_DQ SN7[13]

M_B_CL KP0[13]

M_B_CL KN0[13]

M_B_CL KP1[13]

M_B_CL KN1[13]

M_B_CK E0[13]

M_B_CK E1[13]

M_B_OD T0[13]

M_B_OD T1[13]

M_B_CS #0[13]

M_B_CS #1[13]

M_B_RA S#[13]

M_B_CA S#[13]

M_B_W E#[13]

M_B_RS T#[13]

M_B_EV ENT#[13,27]

R223 1K/F_4

U27C

Y33

MB_AD D[0]

R32

MB_AD D[1]

T31

MB_AD D[2]

P33

MB_AD D[3]

P32

MB_AD D[4]

P31

MB_AD D[5]

N32

MB_AD D[6]

M33

MB_AD D[7]

M32

MB_AD D[8]

L32

MB_AD D[9]

AB31

MB_AD D[10]

M31

MB_AD D[11]

K32

MB_AD D[12]

AF33

MB_AD D[13]

K33

MB_AD D[14]

J32

MB_AD D[15]

AB33

MB_BA NK[0]

AA32

MB_BA NK[1]

K31

MB_BA NK[2]

C18

MB_DM [0]

B23

MB_DM [1]

C28

MB_DM [2]

D31

MB_DM [3]

AM31

MB_DM [4]

AN30

MB_DM [5]

AR24

MB_DM [6]

AN18

MB_DM [7]

B18

MB_DQ S_H[0]

A18

MB_DQ S_L[0]

B24

MB_DQ S_H[1]

A24

MB_DQ S_L[1]

B30

MB_DQ S_H[2]

B29

MB_DQ S_L[2]

D32

MB_DQ S_H[3]

D33

MB_DQ S_L[3]

AM32

MB_DQ S_H[4]

AM33

MB_DQ S_L[4]

AN28

MB_DQ S_H[5]

AP29

MB_DQ S_L[5]

AP23

MB_DQ S_H[6]

AP24

MB_DQ S_L[6]

AR18

MB_DQ S_H[7]

AP18

MB_DQ S_L[7]

W3 2

MB_CLK _H[0]

Y32

MB_CLK _L[0]

V33

MB_CLK _H[1]

V32

MB_CLK _L[1]

U32

MB_CLK _H[2]

V31

MB_CLK _L[2]

T33

MB_CLK _H[3]

T32

MB_CLK _L[3]

H32

MB_CK E[0]

H33

MB_CK E[1]

AF31

MB0_O DT[0]

AH31

MB0_O DT[1]

AE32

MB1_O DT[0]

AH33

MB1_O DT[1]

AD31

MB0_CS _L[0]

AF32

MB0_CS _L[1]

AC32

MB1_CS _L[0]

AG32

MB1_CS _L[1]

AB32

MB_RA S_L

AD32

MB_CA S_L

AD33

MB_W E_L

H31

MB_RE SET_L

Y31

MB_EV ENT_L

TRINITY-A8-S ERIES_BGA81 3

MB_DA TA[0]

MB_DA TA[1]

MB_DA TA[2]

MB_DA TA[3]

MB_DA TA[4]

MB_DA TA[5]

MB_DA TA[6]

MB_DA TA[7]

MB_DA TA[8]

MB_DA TA[9]

MB_DA TA[10]

MB_DA TA[11]

MB_DA TA[12]

MB_DA TA[13]

MB_DA TA[14]

MB_DA TA[15]

MB_DA TA[16]

MB_DA TA[17]

MB_DA TA[18]

MB_DA TA[19]

MB_DA TA[20]

MB_DA TA[21]

MB_DA TA[22]

MB_DA TA[23]

MB_DA TA[24]

MB_DA TA[25]

MB_DA TA[26]

MB_DA TA[27]

MB_DA TA[28]

MB_DA TA[29]

MB_DA TA[30]

MB_DA TA[31]

MB_DA TA[32]

MB_DA TA[33]

MB_DA TA[34]

MB_DA TA[35]

MB_DA TA[36]

MB_DA TA[37]

MB_DA TA[38]

MB_DA TA[39]

MB_DA TA[40]

MB_DA TA[41]

MB_DA TA[42]

MB_DA TA[43]

MB_DA TA[44]

MB_DA TA[45]

MB_DA TA[46]

MB_DA TA[47]

MB_DA TA[48]

MB_DA TA[49]

MB_DA TA[50]

MB_DA TA[51]

MB_DA TA[52]

MB_DA TA[53]

MB_DA TA[54]

MB_DA TA[55]

MB_DA TA[56]

MB_DA TA[57]

MB_DA TA[58]

MB_DA TA[59]

MB_DA TA[60]

MB_DA TA[61]

MB_DA TA[62]

MB_DA TA[63]

C16

B17

B20

C20

A16

B16

B19

A20

B22

C22

A26

B26

B21

A22

C24

B25

A28

B28

B31

A32

C26

B27

A30

C30

B33

C32

F33

F32

B32

C31

E32

F31

AK32

AL32

AP32

AN31

AK31

AK33

AN32

AP33

AP30

AR30

AP27

AN26

AR32

AP31

AR28

AP28

AP25

AN24

AR22

AP21

AP26

AR26

AN22

AP22

AR20

AP19

AP16

AR16

AN20

AP20

AP17

AN16

M_B_DQ 0

M_B_DQ 1

M_B_DQ 2

M_B_DQ 3

M_B_DQ 4

M_B_DQ 5

M_B_DQ 6

M_B_DQ 7

M_B_DQ 8

M_B_DQ 9

M_B_DQ 10

M_B_DQ 11

M_B_DQ 12

M_B_DQ 13

M_B_DQ 14

M_B_DQ 15

M_B_DQ 16

M_B_DQ 17

M_B_DQ 18

M_B_DQ 19

M_B_DQ 20

M_B_DQ 21

M_B_DQ 22

M_B_DQ 23

M_B_DQ 24

M_B_DQ 25

M_B_DQ 26

M_B_DQ 27

M_B_DQ 28

M_B_DQ 29

M_B_DQ 30

M_B_DQ 31

M_B_DQ 32

M_B_DQ 33

M_B_DQ 34

M_B_DQ 35

M_B_DQ 36

M_B_DQ 37

M_B_DQ 38

M_B_DQ 39

M_B_DQ 40

M_B_DQ 41

M_B_DQ 42

M_B_DQ 43

M_B_DQ 44

M_B_DQ 45

M_B_DQ 46

M_B_DQ 47

M_B_DQ 48

M_B_DQ 49

M_B_DQ 50

M_B_DQ 51

M_B_DQ 52

M_B_DQ 53

M_B_DQ 54

M_B_DQ 55

M_B_DQ 56

M_B_DQ 57

M_B_DQ 58

M_B_DQ 59

M_B_DQ 60

M_B_DQ 61

M_B_DQ 62

M_B_DQ 63

+1.5VSUS

Reserved for AMD suggest

A A

R212

1K/F_4

R224

1K/F_4

R218 *0_4/S

+MEMV REF_CPU

PROJECT : VOLKS_Comal 14"

PROJECT : VOLKS_Comal 14"

C386

C385

1000P/50V _4

0.1U/10V_ 4

NB5

NB5

5

4

3

2

NB5

PROJECT : VOLKS_Comal 14"

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Llano DDR3 MEM I/F

Llano DDR3 MEM I/F

Llano DDR3 MEM I/F

1

3 42Thursday, September 20, 2012

3 42Thursday, September 20, 2012

3 42Thursday, September 20, 2012

1A

1A

1A

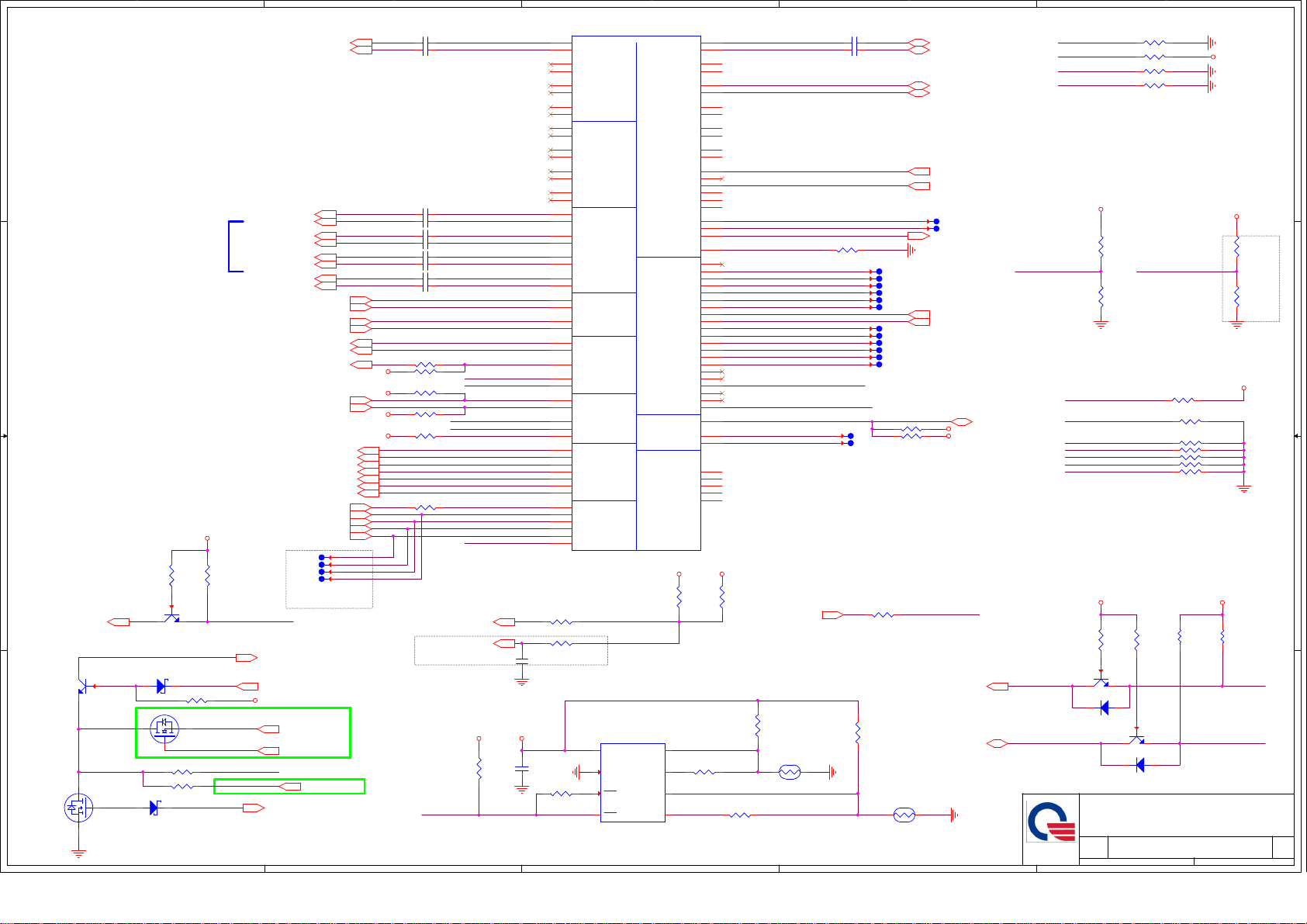

5

DP0 ou tput to

eDP to L VDS co nverter

INT_eDP_T XP0

INT_eDP_T XN0

Display p ort power 1.5V min 1.2v max : 1.65v

D D

IN_D2

4/19 HDMI change to DP2 fo r Comal.

DP2 output to

HDMI con nector

note --HD MI P&N can not swap

Note: CL K_APU_HCLKP /N is 100MHZ SSC

C C

Note: CL K_DP_NSSCP /N is 100MHZ no n-SSC

IN_D2#

IN_D1

IN_D1#

IN_D0

IN_D0#

IN_CLK

IN_CLK#

CLK_AP U_P

CLK_AP U_N

CLK_DP _P

CLK_DP _N

PV1 add fo r HW therm al protect

CPU_VD D0_RUN_FB _L

VDDP_F B_H

CPU_VD DNB_RUN_ FB_H

APU_TH ERMTRIP#

FCH_TH ERMTRIP#THERM TRIP#

HW_A LERT#

VDDIO_FB _H

CPU_VD D0_RUN_FB _H

TP82

TP33

TP84

TP49

3920_RS T#

ECPW ROK

PV1 change GPU therm al protect

+3V

DGPU_OV T#

DGPU_P WROK

HWPG

R420

10K/F_4

2

Q19

13

D11

BAS316/D G

R225 10K/F_4

Q29*2N7002E

2

R205 *0_4/S

R211 *0_4

+1.5VSUS

R418

1K/F_4

3920_RS T#

ECPW ROK

1

PV1 add fo r HW therm al protect

B B

Thermal

FCH_TH ERMTRIP#

A A

Q8

*ME2N70 02E

MMBT3 904-7-F

THERMT RIP# shutdow n temperature 125C

Q9

MMBT3 904-7-F

2

2 1

1 3

D9 *RB501V-40

2

3

2 1

SYS_SHDN -1#

3

1

IN_D2

IN_D2#

IN_D1

IN_D1#

IN_D0

IN_D0#

C_TXC_ HDMI+

C_TXC_ HDMI-

SVC

SVD

CPU_SV T

APU_RS T#

APU_PW RGD

APU_TD I

APU_TD O

APU_TC K

APU_TM S

APU_TR ST#

APU_DB RDY

APU_DB REQ#

4/19 For Comal,

close to APU.

HW_A LERT#

ADD VGA T EMP_ FAIL funct ion is active Hi

5

4

Place caps with APU < 1 inch

route PCI E as 85ohm +/- 10%

C739 0.1U/10V_4

C738 0.1U/10V_4

C740 0.1U/10V_4

C741 0.1U/10V_4

C742 0.1U/10V_4

C743 0.1U/10V_4

C744 0.1U/10V_4

C745 0.1U/10V_4

C746 0.1U/10V_4

C747 0.1U/10V_4

R157 *0_4/S

R156 *1K/F_4

+1.5V

R172 301/F_4

+1.5V

R181 301/F_4

+1.5V

+1.5VSUS

R417 1K/F_4

PV change to short -pad

R381 *0_4/S

FCH_PR OCHOT#

H_PROC HOT#

HW_A LERT#

over 120 degree C= Low

4

INT_eDP_T XP0_C

INT_eDP_T XN0_C

PEG_HD MI_TXDP2

PEG_HD MI_TXDN2

PEG_HD MI_TXDP1

PEG_HD MI_TXDN1

PEG_HD MI_TXDP0

PEG_HD MI_TXDN0

PEG_HD MI_TXCP

PEG_HD MI_TXCN

CLK_AP U_P

CLK_AP U_N

CLK_DP _P

CLK_DP _N

SVC

SVD

APU_SV T_R

APU_SIC

APU_SID

APU_RS T#

APU_PW RGD

APU_PR OCHOT#

APU_TH ERMTRIP#

APU_AL ERT

APU_TD I

APU_TD O

APU_TC K

APU_TM S

APU_TR ST#

APU_DB RDY

APU_DB REQ#

VSS_SE NSE

VDDP_F B_H

CPU_VD DNB_RUN_ FB_H

VDDIO_FB _H

CPU_VD D0_RUN_FB _H

VDDP_F B_H

R208

*10K/F_4

R198 *0_4/S

R200 *0_4/S

to EC rese rve only

C382

220P/50V_4

+5VPCU+3VPCU

C384

*1U/6.3V_4

1 2

R206 *0_4/S

3

U27D

H2

DP0_TX P[0]

H1

DP0_TX N[0]

H3

DP0_TX P[1]

H4

DP0_TX N[1]

F4

DP0_TX P[2]

F3

DP0_TX N[2]

F1

DP0_TX P[3]

F2

DP0_TX N[3]

E2

DP1_TX P[0]

E1

DP1_TX N[0]

D4

DP1_TX P[1]

D3

DP1_TX N[1]

D1

DP1_TX P[2]

D2

DP1_TX N[2]

C1

DP1_TX P[3]

C2

DP1_TX N[3]

B2

DP2_TX P[0]

A2

DP2_TX N[0]

B3

DP2_TX P[1]

A3

DP2_TX N[1]

B4

DP2_TX P[2]

A4

DP2_TX N[2]

B5

DP2_TX P[3]

A5

DP2_TX N[3]

AL9

CLKIN_H

AK9

CLKIN_L

AL7

DISP_CL KIN_H

AK7

DISP_CL KIN_L

E5

SVC

E6

SVD

D6

SVT

AJ11

SIC

AH11

SID

AK11

RESET_ L

AH9

PW ROK

AL12

PROCH OT_L

AK5

THERM TRIP_L

AR10

ALERT_ L

E11

TDI

G11

TDO

H12

TCK

F11

TMS

H11

TRST_L

E8

DBRDY

E7

DBREQ _L

G6

VSS_SE NSE

H6

VDDP_S ENSE

H5

VDDNB _SENSE

G7

VDDIO_ SENSE

G5

VDD_SE NSE

H7

VDDR_ SENSE

TRINITY-A8-S ERIES_BGA81 3

When 100K-NTC 100 C=6.164K

Thermal Trip = 120 C

APU_PR OCHOT#

U9

*G718

1

VCC

2

GND

3

OT1

4

OT2

DISPLAY P ORT 0DISPLAY P ORT 1DISPLAY P ORT 2CLKSER.CTRLJTAGSENSE

DISPLAY P ORT MISC.RSVD TEST

DP_VAR Y_BL

DP_AUX _ZVSS

DMAAC TIVE_L

TMSNS 1

RHYST 1

TMSNS 2

RHYST 2

3

M5

DP0_AU XP

M6

DP0_AU XN

L5

DP1_AU XP

L6

DP1_AU XN

J5

DP2_AU XP

J6

DP2_AU XN

P5

DP3_AU XP

P6

DP3_AU XN

R5

DP4_AU XP

R6

DP4_AU XN

U5

DP5_AU XP

U6

DP5_AU XN

M7

DP0_HP D

L7

DP1_HP D

J7

DP2_HP D

P7

DP3_HP D

R7

DP4_HP D

U7

DP5_HP D

C6

DP_BLO N

D7

DP_DIG ON

A6

B6

AL6

TEST6

Y23

TEST9

V23

TEST10

G9

TEST14

F9

TEST15

E9

TEST16

G8

TEST17

F12

TEST18

E12

TEST19

F14

TEST20

G12

TEST24

AJ8

TEST25_ H

AH8

TEST25_ L

G14

TEST28_ H

H14

TEST28_ L

V25

TEST30_ H

Y25

TEST30_ L

AH32

TEST31

R25

TEST32_ H

T25

TEST32_ L

AL5

TEST35

AP10

T23

TEST4

R23

TEST5

L8

RSVD

P8

RSVD

AH12

RSVD

AJ12

RSVD

AK12

RSVD

+1.5V +1.5VSUS

R197

*1K/F_4

8

7

R207 *8.87K/F_4

6

5

R217 *8.87K/F_4

INT_eDP_A UXP_C

INT_eDP_A UXN_C

FCH_LV DS_HPD

HDMI_H PD_Q

APU_BL EN

APU_DIG ON

DP_AUX _ZVSS

APU_TE ST9

APU_TE ST10

APU_TE ST14_BP0

APU_TE ST15_BP1

APU_TE ST16_BP2

APU_TE ST17_BP3

APU_TE ST18

APU_TE ST19

APU_TE ST20_SCANC LK2

APU_TE ST24_SCANC LK1

APU_TE ST25_H

APU_TE ST25_L

APU_TE ST28_H

APU_TE ST28_L

M_TEST

APU_TE ST35

DMAAC TIVE_L

CPU_TH ERMDA

CPU_TH ERMDC

R196

1K/F_4

R215

*11.5K/F_4

R204 *100K_6 NT C

C736 0.1U/10V_4

C737 0.1U/10V_4

R382 150/F_4

VRHOT

12

TP30

TP29

TP36

TP34

TP40

TP35

TP44

TP41

TP27

TP23

TP45

TP46

R410 *1K/F_4

R416 1K/F_4

TP32

TP42

R199 *0_4/S

R216

*11.5K/F_4

R210 *100K_6 NTC

2

FCH_LV DS_HPD

HDMI_H PD_Q

APU_TE ST18

APU_TE ST19

APU_PR OCHOT#

12

2

INT_eDP_A UXP

INT_eDP_A UXN

INT_HDM I_AUXP

INT_HDM I_AUXN

TP83

TP85

APU_BL PWM

To AMD HDT

DMAACTIVE _L controls

entry and exit from the

sleep and power states

DMAAC TIVE_L

+1.5V

+1.5VSUS

MBCLK 2

MBDAT A2

SI

MBCLK 2

MBDAT A2

INT_eDP_A UXP

INT_eDP_A UXN

INT_eDP_A UXP_C

INT_eDP_A UXN_C

APU_TE ST25_L

APU_TE ST9

APU_TE ST18

APU_TE ST19

APU_TE ST20_SCANC LK2

APU_TE ST24_SCANC LK1

APU_TE ST25_H

Q6

MMBT3 904-7-F

NB5

NB5

NB5

LVDS

HDMI

M_TEST CONNECTION T BD

1

R376 *100K/F_4

R377 *100K/F_4

R388 1.8K_4

R389 1.8K_4

+1.5VSUS

R221

*39.2/F_4

R213

39.2/F_4

R195

2K/F_4

2

13

Q7

MMBT3 904-7-F

PROJECT : VOLKS_Comal 14"

PROJECT : VOLKS_Comal 14"

PROJECT : VOLKS_Comal 14"

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Llano Display/Misc

Llano Display/Misc

Llano Display/Misc

Date: Sheet of

Date: Sheet of

Date: Sheet of

APU_TE ST35M_TEST

7/8 For C omal.

TEST35 P U FOR INTERN AL

TEST35 P D FOR CUSTOM ER

R160 510/F_4

R179 *0_4

R191 1K/F_4

R190 1K/F_4

R169 1K/F_4

R167 1K/F_4

R162 510/F_4

R209

2K/F_4

21

D8R B501V-40

2

13

21

D7R B501V-40

1

R214

1K/F_4

APU_SIC

APU_SID

+1.5VSUS+1.5VSUS

+3V

+1.5VSUS

4 42Thursday, September 20, 2012

4 42Thursday, September 20, 2012

4 42Thursday, September 20, 2012

04

R397

301/_4

R394

*301/_4

+1.2V

R201

1K/F_4

1A

1A

1A

5

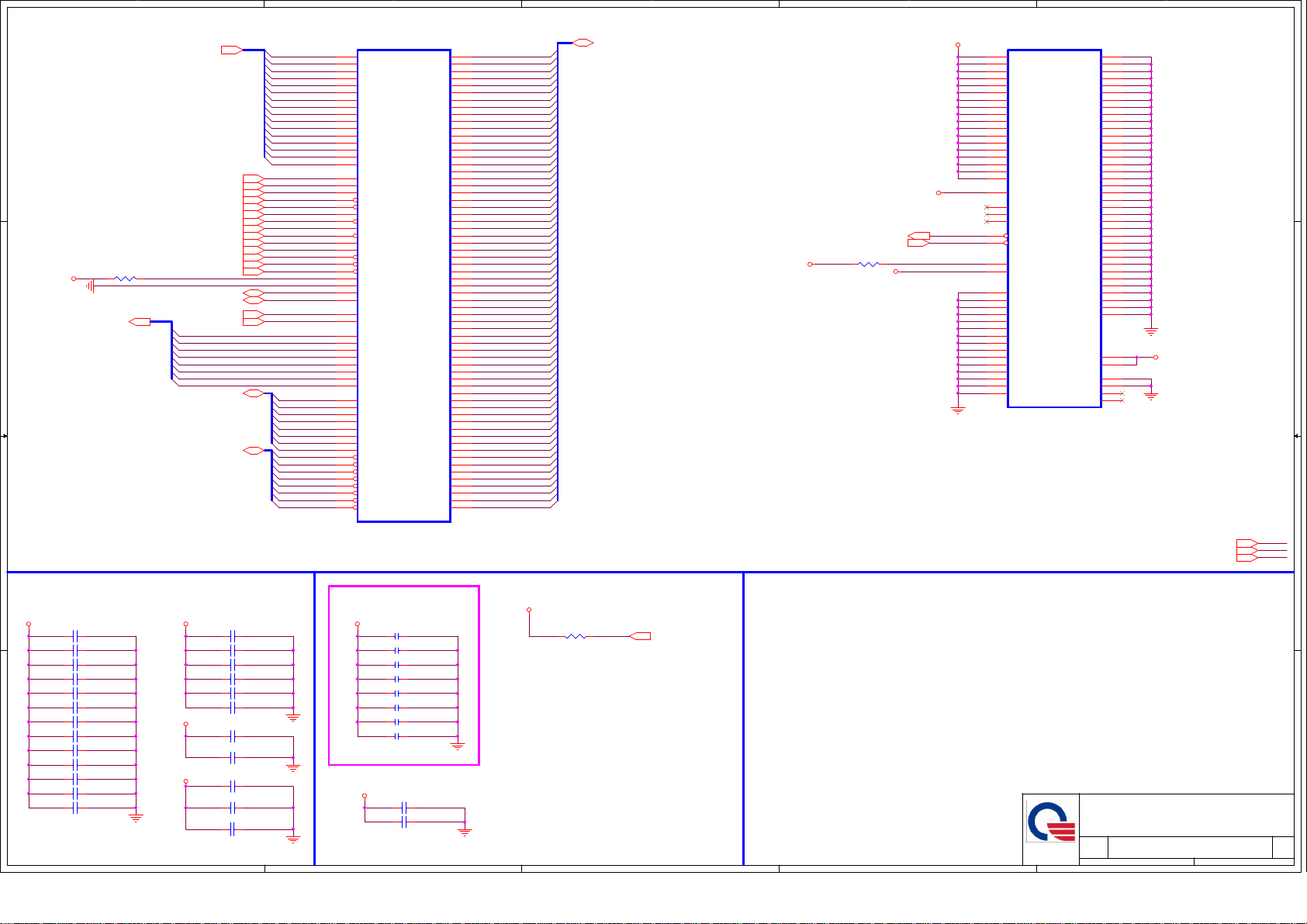

APU PO WER T ABLE

PIN NAM E

VDD

VDDNB

VDDIO

VDDR +1.2V

D D

VDDA

C C

B B

A A

NET NAM E

+VCC_C ORE

+VDDN B_CORE

+1.5VSUS

+1.2V_VD DP

+1.2V_VD DR

+2.5V_VD DA

C762

22U/6.3VS _8

C294

0.22U/10V _4

C300

22U/6.3VS _8

VOLTAG E

+1.1V

??

+1.5V

+1.2VVDDP

+2.5V

C788

22U/6.3VS _8

C295

0.22U/10V _4

C297

22U/6.3VS _8

C763

22U/6.3VS _8

C293

180P/50V_ 4

+VDDN B_CAP

C298

22U/6.3VS _8

+VDDP_ CAP

C301

22U/6.3VS _8

C302

*22U/6.3VS _8

2.8A Up to DDR3 -1333 @ 1.50V V DDIO

+1.2V_VD DP

C458

0.22U/10V _4

C481

180P/50V_ 4

VDDP = 5A

C770

22U/6.3VS _8

C774

180P/50V_ 4

+1.2V

+2.5V

C455

0.22U/10V _4

C432

180P/50V_ 4

R427 *0_8/S

PBY160808T -221Y-N(220,2A)

C425

0.22U/10V _4

C429

180P/50V_ 4

L21

5

C764

22U/6.3VS _8

C291

180P/50V_ 4

C299

22U/6.3VS _8

C438

0.22U/10V _4

C452

180P/50V_ 4

C772

0.22U/10V _4

C773

180P/50V_ 4

+VDDN B_CORE

C292

180P/50V_ 4

C289

180P/50V_ 4

0.22U/10V _4

+1.2V_VD DP

C771

0.22U/10V _4

C768

*22U/6.3VS _8

VDDA= 0.75A

+2.5V_VD DA

C353

4.7U/6.3V_6

+VDDN B_CORE +VDDN B_CORE

+1.5VSUS

C479

180P/50V_ 4

C373

C365

0.22U/10V _4

C769

22U/6.3VS _8

+VDDP_ CAP

TP43

C350

0.22U/10V _4

+VCC_C ORE

C351

3300P/50V _4

4

J12

J14

J15

J17

J19

J20

J22

M11

M12

M14

M15

M17

M19

M20

M22

R8

R9

R11

R12

R14

R15

R17

R19

R20

R22

U8

V9

V11

V12

V14

V15

A7

A8

A9

A10

A11

A12

A13

A14

A15

B7

B8

B9

B10

J33

K23

K25

L28

L30

L33

M27

N23

N25

N30

N33

P28

R27

R30

R33

U28

U30

U33

W2 8

W3 0

AM12

AN12

AP12

AP13

AR12

AR13

AA6

AA7

AM13

AM14

4

U27E

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP_C AP

VDDP_C AP

VDDA

VDDA

TRINITY-A8-S ERIES_BGA81 3

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB _CAP

VDDNB _CAP

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDR

VDDR

VDDR

VDDR

VDDR

V17

V19

V20

V22

W8

AA8

AA9

AA11

AA12

AA14

AA15

AA17

AA19

AA20

AA22

AD9

AD11

AD12

AD14

AD15

AD17

AD19

AD20

AD22

AG12

AG14

AG15

AG17

AG19

AG20

AG22

B11

B12

B13

B14

B15

C8

C10

C12

C14

D8

D10

D12

D14

M9

N9

W3 3

AA23

AA25

AA27

AA30

AA33

AB28

AC30

AC33

AD23

AD25

AD27

AE28

AE30

AE33

AG23

AG25

AG27

AG30

AG33

AN14

AP14

AP15

AR14

AR15

+VCC_C ORE

3

36A

Maximum IDDspike 50A

C338

22U/6.3VS _8

C334

22U/6.3VS _8

C321

0.22U/10V _4

C339

22U/6.3VS _8

C335

22U/6.3VS _8

C354

0.22U/10V _4

25A

Maximum IDDNBspike 33A

C348

22U/6.3VS _8

C311

22U/6.3VS _8

C336

180P/50V_ 4

DECOUPLING between PROCESSOR and DIMMs

+1.5VSUS

C420

+VDDN B_CAP

+1.5VSUS

C366

22U/6.3VS _8

4.7U/6.3V_6

C367

22U/6.3VS _8

VDDR = 3.3A ( Up to DD R3-1333 @ 1.5V )

+1.2V_VD DR_B+1.2V_VDDR_ B

C780

0.22U/10V _4

C778

0.22U/10V _4

3

Across VDDIO and VSS split

C511

4.7U/6.3V_6

If the VSS pla ne is c ut to c reate a VDDIO plane,

ceramic capacit ors are conne cted ac ross

the VD DIO and VSS p lane s plit as f ollows

C414

4.7U/6.3V_6

C777

1000P/50V _4

C363

22U/6.3VS _8

C288

*22U/6.3VS _8

C341

180P/50V_ 4

C368

4.7U/6.3V_6

C421

4.7U/6.3V_6

C779

180P/50V_ 4

C317

22U/6.3VS _8

C318

*22U/6.3VS _8

C362

180P/50V_ 4

C426

4.7U/6.3V_6

C415

4.7U/6.3V_6

C776

180P/50V_ 4

EMI suggest ion

C361

470P/50V_ 4

*470P/50V _4

C749

22U/6.3VS _8

C735

*22U/6.3VS _8

C364

0.01U/25V _4

C347

22U/6.3VS _8

C349

0.01U/25V _4

C377

0.22U/10V _4

C369

4.7U/6.3V_6

R429 *0_8/S

C325

*22U/6.3VS _8

0.22U/10V _4

C333

C378

2

2

+VCC_C ORE

C360

*470P/50V _4

C319

22U/6.3VS _8

C352

0.01U/25V _4

C800

0.22U/10V _4

+1.2V

C802

0.22U/10V _4

1

U27F

A17

VSS

A19

VSS

A21

VSS

A23

VSS

A25

VSS

A27

VSS

A29

VSS

A31

VSS

B1

VSS

C3

VSS

C4

VSS

C33

VSS

D5

VSS

D9

VSS

D11

VSS

D13

VSS

D15

VSS

D17

VSS

D19

VSS

D21

VSS

D23

VSS

D25

VSS

D30

VSS

E4

VSS

E27

VSS

E29

VSS

E30

VSS

E33

VSS

F5

VSS

F6

VSS

F7

VSS

F8

VSS

F17

VSS

F20

VSS

F23

VSS

F28

VSS

F29

VSS

G1

VSS

G2

VSS

G4

VSS

G15

VSS

G19

VSS

G25

VSS

G26

VSS

G27

VSS

G33

VSS

H8

VSS

H9

VSS

H22

VSS

H26

VSS

J4

VSS

J8

VSS

J9

VSS

J11

VSS

J23

VSS

J25

VSS

J26

VSS

J27

VSS

J30

VSS

K9

VSS

K11

VSS

K12

VSS

K14

VSS

K15

VSS

K17

VSS

K19

VSS

K20

VSS

K22

VSS

L1

VSS

L2

VSS

L4

VSS

M8

VSS

M23

VSS

M25

VSS

N4

VSS

N11

VSS

N12

VSS

N14

VSS

N15

VSS

N17

VSS

N19

VSS

N20

VSS

N22

VSS

R1

VSS

R2

VSS

R4

VSS

T9

VSS

T11

VSS

T12

VSS

T14

VSS

T15

VSS

T17

VSS

T19

VSS

T20

VSS

T22

VSS

U4

VSS

W1

VSS

W2

VSS

W4

VSS

W5

VSS

W6

VSS

W7

VSS

Y9

VSS

TRINITY-A8-S ERIES_BGA81 3

PROJECT : VOLKS_Comal 14"

PROJECT : VOLKS_Comal 14"

PROJECT : VOLKS_Comal 14"

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

NB5

NB5

NB5

Date: Sheet of

Date: Sheet of

Date: Sheet of

Y11

VSS

Y12

VSS

Y14

VSS

Y15

VSS

Y17

VSS

Y19

VSS

Y20

VSS

Y22

VSS

AA4

VSS

AA5

VSS

AB7

VSS

AB8

VSS

AC1

VSS

AC2

VSS

AC4

VSS

AC9

VSS

AC11

VSS

AC12

VSS

AC14

VSS

AC15

VSS

AC17

VSS

AC19

VSS

AC20

VSS

AC22

VSS

AC23

VSS

AC25

VSS

AE4

VSS

AF9

VSS

AF11

VSS

AF12

VSS

AF14

VSS

AF15

VSS

AF17

VSS

AF19

VSS

AF20

VSS

AF22

VSS

AF23

VSS

AF25

VSS

AG1

VSS

AG2

VSS

AG4

VSS

AG9

VSS

AG11

VSS

AG26

VSS

AH7

VSS

AH17

VSS

AH20

VSS

AH23

VSS

AH26

VSS

AH30

VSS

AJ4

VSS

AJ5

VSS

AJ6

VSS

AJ7

VSS

AJ9

VSS

AJ14

VSS

AJ15

VSS

AJ19

VSS

AJ22

VSS

AJ27

VSS

AJ28

VSS

AJ33

VSS

AK6

VSS

AK8

VSS

AK25

VSS

AK28

VSS

AK30

VSS

AL1

VSS

AL2

VSS

AL4

VSS

AL8

VSS

AL11

VSS

AL27

VSS

AL28

VSS

AL33

VSS

AM5

VSS

AM7

VSS

AM9

VSS

AM11

VSS

AM15

VSS

AM17

VSS

AM19

VSS

AM21

VSS

AM23

VSS

AM25

VSS

AM29

VSS

AM30

VSS

AN3

VSS

AN4

VSS

AN33

VSS

AP5

VSS

AP9

VSS

AR2

VSS

AR5

VSS

AR9

VSS

AR17

VSS

AR19

VSS

AR21

VSS

AR23

VSS

AR25

VSS

AR27

VSS

AR29

VSS

AR31

VSS

Llano POWER/GND

Llano POWER/GND

Llano POWER/GND

1

05

5 42Thursday, September 20, 2012

5 42Thursday, September 20, 2012

5 42Thursday, September 20, 2012

1A

1A

1A

5

+3VS5

NC,no i nstall b y default

R146 *2.2K_4

R153 *2.2K_4

R151 *2.2K_4

+3V

D D

R176 2.2K_4

R177 2.2K_4

+3VS5

R148 *1K/F_4

FCH_TE ST0

FCH_TE ST1

FCH_TE ST2

SMB_R UN_CLK

SMB_R UN_DAT

SYS_RST#

SYS_RST# in ternal

10K pull u p

to DDR3 SM BUS

GEVENT 0# internal pul l Hi 8.2K to +3V

GEVENT 1# internal pul l Hi 8.2K to +3V

GEVENT 23# internal pu ll Hi 8.2K to +3V

GEVENT 5# internal pul l Hi 8.2K to +3V S5

PCIE_WAKE# no need to pu ll

Hi resisto r from che ck list

CLK_REQ 2# interna l pull Hi 8.2K to +3V

+3VS5

R134 10K/F_4

R135 10K/F_4

R130 10K/F_4

R133 10K/F_4

C C

R142 2.2K_4

R141 2.2K_4

R143 *4.7K_4

C273 *0.01U/25V_4

R375 10K/F_4

SDA3

SCL2

SDA2

SCL1

SDA1

FCH_TH ERMTRIP#

DNBSW ON#

CLK_REQ 3# interna l pull Hi 8.2K to +3V

CLK_REQ 4# interna l pull Hi 8.2K to +3V

This pin i s used to

power down VGA DAC

regulators when CRT

no connect ed

GEVENT 16# internal pu ll Hi 8.2K to +3VS5

GEVENT 15# internal pu ll Hi 8.2K to +3VS5

To Azalia

ACZ_SD OUT_R

ACZ_SYNC _R

ACZ_BC LK_R

ACZ_RS T#_R

ACZ_SD IN0

B B

Pure UMA c an remove

VGA_REQ[37]

DGPU_P WROK

A A

R411 33_4

R412 33_4

R414 33_4

R425 33_4

C275

*33P/50V_ 4

D21 *RB501V-4 0

R440

10K/F_4

ACZ_SD OUT_AUDIO [23]

ACZ_SYNC _AUDIO [23 ]

BIT_CLK _AUDIO [23]

ACZ_RS T#_AUDIO [23]

ACZ_SD IN0 [23]

C280

33P/50V_4

CLK_REQ # already

internal pull up 8.2K

21

CLKREQ 1#

2

Q20

*MMBT3 904-7-F

1 3

4

DNBSW ON#[29]

FCH_PW RGD[10]

EC_A20G ATE[29]

EC_RCIN #[29]

SIO_EXT_ SMI#[29]

SIO_EXT_ SCI#[29]

PCIE_W AKE#[24 ,27]

FCH_TH ERMTRIP#[4]

RSMRS T#[29]

PCIE_CL KREQ_CR#[25]

PCIE_CL KREQ_LAN#[24]

SPKR[23]

SMB_R UN_CLK[12 ,13]

SMB_R UN_DAT[12,13]

SCL1[11,28]

SDA1[11,28]

PCIE_CL KREQ_WLA N#[27]

For Zero ODD

HD audio

interface is

+3V_S5 vol tage

SUSB#[29]

SUSC#[29]

RF_OFF1 #[27]

+3V

TP21

4/19 For Comal.

BT_COM BO_OFF#[27]

VGA_RST B[14]

VGA_ON_ SB[29]

TP100

TP92

TP20

TP18

R406 *0_4/S

C734 *100P/50V _4

R171 10K/F_4

PCIE_CL KREQ_CR#

PCIE_CL KREQ_LAN#

R432 *0_4/S

TP38

TP22

TP28

TP81

TP97

TP14

TP91

TP80

TP19

TP15

TP12

PCIE_CL KREQ_WLA N#

RF_OFF1 #

R415 *10K/F_4

R408 *10K/F_4

R403 *10K/F_4

R409 *10K/F_4

R402 *10K/F_4

PCIE_RS T2#

RI#

SUSB#

SUSC#

DNBSW ON#

FCH_PW RGD

FCH_TE ST0

FCH_TE ST1

FCH_TE ST2

EC_A20G ATE

EC_RCIN #

FCH_PM E#

SIO_EXT_ SMI#

GEVENT 5#

SYS_RST#

PCIE_W AKE#

FCH_TH ERMTRIP#

WD_P WRGD

RSMRS T#

FCH_GP IO66SCL3

SMB_R UN_CLK

SMB_R UN_DAT

SCL1

SDA1

CLKREQ 1#

SMART VOLT2

VGA_PD

GBE_LED 0

ODD_PLU GIN#

FCH_JT AG_TCK

FCH_JT AG_TDI

FCH_JT AG_RST#

ACZ_BC LK_R

ACZ_SD OUT_R

ACZ_SD IN0

ACZ_SD IN1

ACZ_SD IN2_R

ACZ_SD IN3_R

ACZ_SYNC _R

ACZ_RS T#_R

BT_COM BO_OFF#

VGA_RST B

VGA_ON_ SB

3

U25A

AB6

PCIE_RS T2#/GEVEN T4#

R2

RI#/GEV ENT22#

W7

SPI_CS3 #/GBE_STAT 1/GEVENT2 1#

T3

SLP_S3#

W2

SLP_S5#

J4

PW R_BTN#

N7

PW R_GOOD

T9

TEST0

T10

TEST1/ TMS

V9

TEST2

AE22

GA20IN/ GEVENT0#

AG19

KBRST# /GEVENT1#

R9

PME#/G EVENT3#

C26

LPC_SM I#/GEVENT2 3#

T5

LPC_PD #/GEVENT5 #

U4

SYS_RE SET#/GEVE NT19#

K1

WA KE#/GEVEN T8#

V7

IR_RX1/ GEVENT20#

R10

THRMT RIP#/SMBAL ERT#/GEVE NT2#

AF19

WD _PWRG D

U2

RSMRS T#

AG24

CLK_RE Q4#/SATA_IS 0#/GPIO64

AE24

CLK_RE Q3#/SATA_IS 1#/GPIO63

AE26

SMART VOLT1/SATA _IS2#/GPIO50

AF22

CLK_RE Q0#/SATA_IS 3#/GPIO60

AH17

SATA_IS 4#/FANOUT 3/GPIO55

AG18

SATA_IS 5#/FANIN3/G PIO59

AF24

SPKR/G PIO66

AD26

SCL0/G PIO43

AD25

SDA0/G PIO47

T7

SCL1/G PIO227

R7

SDA1/G PIO228

AG25

CLK_RE Q2#/FANIN4 /GPIO62

AG22

CLK_RE Q1#/FANOU T4/GPIO61

J2

IR_LED# /LLB#/GPIO1 84

AG26

SMART VOLT2/SHU TDOWN #/GPIO51

V8

DDR3_R ST#/GEVEN T7#/VGA_P D

W8

GBE_LE D0/GPIO183

Y6

SPI_HOL D#/GBE_LE D1/GEVENT 9#

V10

GBE_LE D2/GEVENT 10#

AA8

GBE_ST AT0/GEVEN T11#

AF25

CLK_RE QG#/GPIO6 5/OSCIN/IDLE EXIT#

M7

BLINK/U SB_OC7#/G EVENT18#

R8

USB_O C6#/IR_TX1/G EVENT6#

T1

USB_O C5#/IR_TX0/G EVENT17#

P6

USB_O C4#/IR_RX0/G EVENT16#

F5

USB_O C3#/AC_PRE S/TDO/GE VENT15#

P5

USB_O C2#/TCK/GE VENT14#

J7

USB_O C1#/TDI/GEV ENT13#

T8

USB_O C0#/SPI_TPM _CS#/TRST# /GEVENT12 #

AB3

AZ_BITC LK

AB1

AZ_SDO UT

AA2

AZ_SDIN 0/GPIO167

Y5

AZ_SDIN 1/GPIO168

Y3

AZ_SDIN 2/GPIO169

Y1

AZ_SDIN 3/GPIO170

AD6

AZ_SYN C

AE4

AZ_RST #

K19

PS2_DA T/SDA4/GP IO187

J19

PS2_CL K/CEC/SCL 4/GPIO188

J21

SPI_CS2 #/GBE_STAT 2/GPIO166

D21

PS2KB_ DAT/GPIO18 9

C20

PS2KB_ CLK/GPIO190

D23

PS2M_D AT/GPIO191

C22

PS2M_C LK/GPIO192

F21

KSO_0/ GPIO209

E20

KSO_1/ GPIO210

F20

KSO_2/ GPIO211

A22

KSO_3/ GPIO212

E18

KSO_4/ GPIO213

A20

KSO_5/ GPIO214

J18

KSO_6/ GPIO215

H18

KSO_7/ GPIO216

G18

KSO_8/ GPIO217

B21

KSO_9/ GPIO218

K18

KSO_10 /GPIO219

D19

KSO_11 /GPIO220

A18

KSO_12 /GPIO221

C18

KSO_13 /GPIO222

B19

KSO_14 /XDB0/GPIO 223

B17

KSO_15 /XDB1/GPIO 224

A24

KSO_16 /XDB2/GPIO 225

D17

KSO_17 /XDB3/GPIO 226

Hudson-M3-A 14

HUDSON-M3

Part 4 of 5

USBCLK /14M_25M_4 8M_OSC

USB

MISC

USB

1.1

ACPI / WAK E UP

EVENTS

USB

GPIO

USB

OC

HD

AUDIO

EC_PW M2/EC_ TIMER2/W OL_EN/G PIO199

EMBED DED

CTRL

USB

EC_PW M0/EC_ TIMER0/GPIO 197

EC_PW M1/EC_ TIMER1/GPIO 198

EC_PW M3/EC_ TIMER3/GPIO 200

USB_RC OMP

USB_FS D1P/GPIO18 6

USB_FS D1N

USB_FS D0P/GPIO18 5

USB_FS D0N

USB_HS D13P

USB_HS D13N

USB_HS D12P

USB_HS D12N

USB_HS D11P

USB_HS D11N

USB_HS D10P

USB_HS D10N

USB_HS D9P

USB_HS D9N

USB_HS D8P

USB_HS D8N

USB_HS D7P

USB_HS D7N

USB_HS D6P

USB_HS D6N

2.0

USB_HS D5P

USB_HS D5N

USB_HS D4P

USB_HS D4N

USB_HS D3P

USB_HS D3N

USB_HS D2P

USB_HS D2N

USB_HS D1P

USB_HS D1N

USB_HS D0P

USB_HS D0N

USBSS _CALRP

USBSS _CALRN

USB_SS _TX3P

USB_SS _TX3N

USB_SS _RX3P

USB_SS _RX3N

USB_SS _TX2P

USB_SS _TX2N

USB_SS _RX2P

USB_SS _RX2N

USB_SS _TX1P

3.0

USB_SS _TX1N

USB_SS _RX1P

USB_SS _RX1N

USB_SS _TX0P

USB_SS _TX0N

USB_SS _RX0P

USB_SS _RX0N

SCL2/G PIO193

SDA2/G PIO194

SCL3_LV /GPIO195

SDA3_L V/GPIO196

KSI_0/G PIO201

KSI_1/G PIO202

KSI_2/G PIO203

KSI_3/G PIO204

KSI_4/G PIO205

KSI_5/G PIO206

KSI_6/G PIO207

KSI_7/G PIO208

2

G8

B9

USB_RC OMP_SB

H1

H3

H6

H5

H10

G10

K10

J12

G12

USBP11 +

F12

USBP11 -

K12

USBP10 +

K13

USBP10 -

B11

D11

E10

USBP8+

F10

USBP8-

C10

A10

H9

G9

A8

C8

F8

E8

C6

A6

C5

A5

C1

C3

E1

E3

C16

USBSS_ CALRP

A16

USBSS_ CALRN

A14

C14

USB 3.0 N ot Impl emented: left unconnected.

C12

A12

D15

B15

E14

F14

F15

G15

H13

G13

J16

H16

J15

K15

H19

SCL2

G19

SDA2

G22

SCL3

G21

SDA3

E22

H22

J22

EC_PW M2

H21

No need for GPIO200

K21

K22

F22

F24

E24

B23

C24

F18

R365 11.8K/F_6

R366 1K/F_4

R358 1K/F_4

USBP11 + [26]

USBP11 - [26]

USBP10 + [26]

USBP10 - [26]

USBP8+ [30]

USBP8- [30]

USBP2+ [27]

USBP2- [27]

USBP0+ [23]

USBP0- [23]

USB30_T X1+ [2 6]

USB30_T X1- [26]

USB30_R X1+ [26]

USB30_R X1- [26]

USB30_T X0+ [2 6]

USB30_T X0- [26]

USB30_R X0+ [26]

USB30_R X0- [26]

EC_PW M2 [10]

1

USB Comb o 3. 0/2. 0.

USB Comb o 3. 0/2. 0.

CAMERA

WLAN Min -Car d

EXte rnal MIC

LEFT sid e US B 2. 0 Co nnec tor

+FCH_V DD_11_SSUS B_S

SCL3 of a TSI-capable APU's

thermal bus, Pulled up to

APU_VDD IO. Resistor value

verified in th e relevant A PU

design guid e.

06

PROJECT : VOLKS_Comal 14"

PROJECT : VOLKS_Comal 14"

PROJECT : VOLKS_Comal 14"

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Hudson-M3 GPIO/USB/AZ/RGMII

Hudson-M3 GPIO/USB/AZ/RGMII

NB5

NB5

5

4

3

2

NB5

Hudson-M3 GPIO/USB/AZ/RGMII

Date: Sheet of

Thursday, September 20, 2012 6 42

Date: Sheet of

Thursday, September 20, 2012 6 42

Date: Sheet of

Thursday, September 20, 2012 6 42

1

1A

1A

1A

5

CARD_P CIE_RST#[25]

MINI_PC IE_RST#[25,27]

LAN_PC IE_RST#[24]

GPU_RS T#[14]

Place these PICE AC

D D

coupling cap close to FCH

PCIE_TX P0_CARD[25]

PCIE_TX N0_CARD[25]

PCIE_TX P1_LAN[24]

PCIE_TX N1_LAN[24]

PCIE_RX P0_CARD[25 ]

PCIE_RX N0_CARD[25]

PCIE_RX P1_LAN[24]

C C

B B

PCIE_RX N1_LAN[24]

C784 150P/50V_ 4

C786 150P/50V_ 4

C787 150P/50V_ 4

C790 150P/50V_ 4

CLK_DP _P[4]

CLK_DP _N[4]

CLK_AP U_P[4]

CLK_AP U_N[4]

CLK_VGA _P[14]

CLK_VGA _N[14]

CLK_W LAN_P[27]

CLK_W LAN_N[27 ]

CLK_PC IE_CARD_P[25]

CLK_PC IE_CARD_N[25]

UMI_RX P0[2]

UMI_RX N0[2]

UMI_RX P1[2]

UMI_RX N1[2]

UMI_RX P2[2]

UMI_RX N2[2]

UMI_RX P3[2]

UMI_RX N3[2]

UMI_TXP 0[2]

UMI_TXN 0[2]

UMI_TXP 1[2]

UMI_TXN 1[2]

UMI_TXP 2[2]

UMI_TXN 2[2]

UMI_TXP 3[2]

UMI_TXN 3[2]

+1.1V_PC IE_VDDR

PCIE_RX P0_CARD

PCIE_RX N0_CARD

PCIE_RX P1_LAN

PCIE_RX N1_LAN

+1.1V_CK VDD

9/18 add RP7/RP8 f or CLK Sl ew Rate

R430 33_4

R431 33_4

R435 33_4

R437 33_4

C374 0.1U/10V _4

C370 0.1U/10V _4

C355 0.1U/10V _4

C359 0.1U/10V _4

C340 0.1U/10V _4

C346 0.1U/10V _4

C328 0.1U/10V _4

C332 0.1U/10V _4

R433 590/F_4

R434 2K/F_4

C7550.1U/10V_ 4

C7610.1U/10V_ 4

R131 2K/F_4

SI , ch ange to 22Ω & 47Ω

for Ris e/Fall t ime iss ue

4

2

RP7 0_4P2R_ 4

4

2

RP8 0_4P2R_ 4

4

2

RP3 0_4P2R_ 4

4

2

RP4 0_4P2R_ 4

4

2

RP5 0_4P2R_ 4

Note: CLK_ FCH_SRCP/N is 100MHZ SSC

Note: CLK_ PCIE_TRAVI SP/N is 10 0MHZ non-S SC

Note: CLK_ DP_NSSCP/N is 100MHZ non-SSC

Note: CLK_ APU_HCLKP/ N is 100MH Z SSC

Note: CLK_ PCIE_VGAP/ N is 100MH Z SSC

Note: GPP_ CLK(0:8)P/ N is 100MH Z SSC capa ble

CLK_PC IE_LANP[24]

CLK_PC IE_LANN[24]

PCH_XT AL25_IN[27]

C725

A A

C684

R369 0_4

*27P/50V_ 4

*27P/50V_ 4

Y3

*25MHZ

4

2

RP6 0_4P2R_ 4

TP78

R359

*1M/F_4

TP76

PV2 change to non-stuff for Green Clock soluti on

5

4

PCIE_RS T#

A_RST#

UMI_RX P0_C

UMI_RX N0_C

UMI_RX P1_C

UMI_RX N1_C

UMI_RX P2_C

UMI_RX N2_C

UMI_RX P3_C

UMI_RX N3_C

PCIE_CA LRP_FCH

PCIE_CA LRN_FCH

PCIE_TX P0_CARD_C

C7570.1U/10V_ 4

PCIE_TX N0_CARD_C

PCIE_TX P1_C

C7600.1U/10V_ 4

PCIE_TX N1_C

CLK_CA LRN_FCH

TP88

3

CLK_DP _P_FCH

1

CLK_DP _N_FCH

TP90

3

CLK_AP U_P_FCH

1

CLK_AP U_N_FCH

3

CLK_VGA _P_FCH

1

CLK_VGA _N_FCH

3

CLK_W LAN_P_FCH

1

CLK_W LAN_N_FCH

3

CLK_PC IE_CARD_P_ FCH

1

CLK_PC IE_CARD_N_ FCH

TP89

TP86

TP93

TP94

TP96

3

CLK_PC IE_LANP_FCH

1

CLK_PC IE_LANN_FCH

4

25M_X1

25M_X2

U25E

AE2

PCIE_RS T#

AD5

A_RST#

AE30

UMI_TX 0P

AE32

UMI_TX 0N

AD33

UMI_TX 1P

AD31

UMI_TX 1N

AD28

UMI_TX 2P

AD29

UMI_TX 2N

AC30

UMI_TX 3P

AC32

UMI_TX 3N

AB33

UMI_RX 0P

AB31

UMI_RX 0N

AB28

UMI_RX 1P

AB29

UMI_RX 1N

Y33

UMI_RX 2P

Y31

UMI_RX 2N

Y28

UMI_RX 3P

Y29

UMI_RX 3N

AF29

PCIE_CA LRP

AF31

PCIE_CA LRN

V33

GPP_TX 0P

V31

GPP_TX 0N

W3 0

GPP_TX 1P

W3 2

GPP_TX 1N

AB26

GPP_TX 2P

AB27

GPP_TX 2N

AA24

GPP_TX 3P

AA23

GPP_TX 3N

AA27

GPP_R X0P

AA26

GPP_R X0N

W2 7

GPP_R X1P

V27

GPP_R X1N

V26

GPP_R X2P

W2 6

GPP_R X2N

W2 4

GPP_R X3P

W2 3

GPP_R X3N

F27

CLK_CA LRN

G30

PCIE_RC LKP

G28

PCIE_RC LKN

R26

DISP_CL KP

T26

DISP_CL KN

H33

DISP2_C LKP

H31

DISP2_C LKN

T24

APU_CL KP

T23

APU_CL KN

J30

SLT_GF X_CLKP

K29

SLT_GF X_CLKN

H27

GPP_C LK0P

H28

GPP_C LK0N

J27

GPP_C LK1P

K26

GPP_C LK1N

F33

GPP_C LK2P

F31

GPP_C LK2N

E33

GPP_C LK3P

E31

GPP_C LK3N

M23

GPP_C LK4P

M24

GPP_C LK4N

M27

GPP_C LK5P

M26

GPP_C LK5N

N25

GPP_C LK6P

N26

GPP_C LK6N

R23

GPP_C LK7P

R24

GPP_C LK7N

N27

GPP_C LK8P

R27

GPP_C LK8N

J26

14M_25M _48M_OSC

C31

25M_X1

C33

25M_X2

Hudson-M3-A 14

HUDSON-M3

Part 1 of 5

PCICLK4 /14M_OSC/ GPO39

PCI

CLKS

PCI EXPR ESS

INTERFA CES

REQ2#/ CLK_REQ8# /GPIO41

REQ3#/ CLK_REQ5# /GPIO42

GNT3#/ CLK_REQ7#/ GPIO46

LDRQ1# /CLK_REQ6 #/GPIO49

CLOCK

GENERA TOR

S5

PCICLK1 /GPO36

PCICLK2 /GPO37

PCICLK3 /GPO38

AD0/GP IO0

AD1/GP IO1

AD2/GP IO2

AD3/GP IO3

AD4/GP IO4

AD5/GP IO5

AD6/GP IO6

AD7/GP IO7

AD8/GP IO8

AD9/GP IO9

AD10/G PIO10

AD11/G PIO11

AD12/G PIO12

AD13/G PIO13

AD14/G PIO14

AD15/G PIO15

AD16/G PIO16

AD17/G PIO17

AD18/G PIO18

AD19/G PIO19

AD20/G PIO20

AD21/G PIO21

AD22/G PIO22

AD23/G PIO23

AD24/G PIO24

AD25/G PIO25

AD26/G PIO26

AD27/G PIO27

AD28/G PIO28

AD29/G PIO29

AD30/G PIO30

AD31/G PIO31

PCI

INTERFA CE

REQ1#/ GPIO40

GNT1#/ GPO44

GNT2#/ SD_LED/GP O45

CLKRU N#

INTE#/G PIO32

INTF#/G PIO33

INTG#/G PIO34

INTH#/G PIO35

LPC

SERIRQ /GPIO48

DMA_A CTIVE#

PROCH OT#

APU

PLUS

LDT_ST P#

APU_RS T#

S5_COR E_EN

INTRUD ER_ALERT#

VDDBT _RTC_G

3

PCICLK0

PCIRST#

CBE0#

CBE1#

CBE2#

CBE3#

FRAME #

DEVSE L#

IRDY#

TRDY#

PAR

STOP#

PERR#

SERR#

REQ0#

GNT0#

LOCK#

LPCCLK 0

LPCCLK 1

LAD0

LAD1

LAD2

LAD3

LFRAM E#

LDRQ0#

APU_PG

32K_X1

32K_X2

RTCCLK

3

AF3

AF1

AF5

AG2

AF6

AB5

AJ3

AL5

AG4

AL6

AH3

AJ5

AL1

AN5

AN6

AJ1

AL8

AL3

AM7

AJ6

AK7

AN8

AG9

AM11

AJ10

AL12

AK11

AN12

AG12

AE12

AC12

AE13

AF13

AH13

AH14

AD15

AC15

AE16

AN3

AJ8

AN10

AD12

AG10

AK9

AL10

AF10

AE10

AH1

AM9

AH8

AG15

AG13

AF15

AM17

AD16

AD13

AD21

AK17

AD19

AH9

AF18

AE18

AC16

AD18

B25

D25

D27

C28

A26

A29

A31

B27

AE27

AE19

G25

E28

E26

G26

F26

G2

G4

H7

F1

F3

E6

*SHORT_ PAD1

PCI_CLK 1

PCI_CLK 3

PCI_CLK 4

PCIRST# _L

R419 33_4

PCI_AD2 3

PCI_AD2 4

PCI_AD2 5

PCI_AD2 6

PCI_AD2 7

HUDSON _MEMHOT#_ R

C789 100P/50V_4

CLKRUN #

TRAVIS_ EN#

ACCEL_ INTH#

LPC_CL K0

LPC_CL K1

LAD0

LAD1

LAD2

LAD3

LFRAME #

LDRQ#0

LDRQ#1

SERIRQ

C886 *100P/50V_ 4

DMAAC TIVE_L

FCH_PR OCHOT#

APU_PW RGD_R

APU_ST OP#

APU_RS T#

32K_X1

32K_X2

S5_CORE _EN

CLK_RT C

INTRUD ER_ALERT#

VDDBT_ RTC_G

20MIL

12

G1

R351 *33_4

TP31

TP112

TP109

TP37

TP110

TP101

TP114

TP105

TP25

LPC_CL K0 [10]

LPC_CL K1 [10]

R352 22_4

R353 33_4

LAD0 [27,29]

LAD1 [27,29]

LAD2 [27,29]

LAD3 [27,29]

LFRAME # [27,29]

TP10

TP24

SERIRQ [29]

DMAAC TIVE_L [4]

R370 *0_4/S

TP11

C358 0.022u/16V_4

TP17

TP16

C240

0.1U/10V_ 4

2

CLK_33M _DEBUG

PCI_CLK 1 [10]

PCI_CLK 3 [10]

PCI_CLK 4 [10]

KBC_RS T#

PCI_AD2 3 [10]

PCI_AD2 4 [10]

PCI_AD2 5 [10]

PCI_AD2 6 [10]

PCI_AD2 7 [10]

DGPU_P WROK [4,6,29,36,37,38 ]

C758 *150P/50V_4

KBC_RS T# [29 ]

+3V_RTC

20MIL

C812

PCI_SER R# [29]

CLKRUN # [29]

ACCEL_ INTH# [26 ]

FCH PRO CHOT#- -- (inpu t 0.8V threshold )

When it isasserted, it can generate SC I or

SMI to OS/BIOS

PV change to short -pad

APU_RS T# [2,4 ]

CLK_RT C [10 ]

LDT_ST P# let is NC from schematic recommen d

R139 150_4

INTRUDE R_ALERT# Left no t connected

(FCH has 50-kohm internal pull-u p to

VBAT).

1U/6.3V_4

PV2 change to non-stuff for Green Clock soluti on

Add G -sens or s ignal

C680 15P/50V _4

C657 15P/50V _4

FCH_PR OCHOT# [4]

APU_PW RGD [2,4]

+3V_RTC

2

R460 *499/F_4

+3VRTC _1 +3VRT C

CLK_33M _KBC [29]

CLK_33M _DEBUG [27]

R461 *10/F_4

32K_X1

R363

*20M_4

32K_X2

USE GROUN D GUARD F OR 32K_X1 AND 32K_ X2

20MIL20MIL

R356 0_4

C701 *18P/50V_4

23

Y4

*32.768KH Z

4 1

C723 *18P/50V_4

PV2 change to non-stuff for Green Clock soluti on

S5_CORE_EN is necess ary to con nect enabl e

pin of +3V PCU/+5VPCU regulator for S5+

mode imple mentation

X'tal Stuff 'R139 chang e to 0hm.

Green CLK S tuff'R139 ch ange to 510 ohm.

PROJECT : VOLKS_Comal 14"

PROJECT : VOLKS_Comal 14"

PROJECT : VOLKS_Comal 14"

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Hudson-M3 ACPI/PCI/CLOCK

Hudson-M3 ACPI/PCI/CLOCK

NB5

NB5

NB5

Hudson-M3 ACPI/PCI/CLOCK

Date: Sheet of

Thursday, September 20, 2012 7 42

Date: Sheet of

Thursday, September 20, 2012 7 42

Date: Sheet of

Thursday, September 20, 2012 7 42

1

1

D22

*RB500V -40

D23

*RB500V -40

20MIL

R457

*470/F_4

20MIL

CN15

BAT_CON N

CLKGEN _RTC_X1 [27]

07

21

+3VPCU

21

+VCCR TC_2

+BAT

+BAT

12

1A

1A

1A

HUDSON-M3

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSSAN _HWM

VSSXL

VSSPL_ SYS

000

1

00

1 1

0

1

1

1

0

1

1

5

Part 5 of 5

ID0ID1ID2ID3

0

0

0

0

0

0

0

0

GROUND

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSSPL_ DAC

VSSAN _DAC

VSSAN Q_DAC

VSSIO_D AC

EFUSE

UMA

SG / Muxle ss

T25

T27

U6

U14

U17

U20

U21

U30

U32

V11

V16

V18

W4

W6

W2 5

W2 8

Y14

Y16

Y18

AA6

AA12

AA13

AA14

AA16

AA17

AA25

AA28

AA30

AA32

AB25

AC6

AC18

AC28

AD27

AE6

AE15

AE21

AE28

AF8

AF12

AF16

AF33

AG30

AG32

AH5

AH11

AH18

AH19

AH21

AH23

AH25

AH27

AJ18

AJ28

AJ29

AK21

AK25

AL18

AM21

AM25

AN1

AN18

AN28

AN33

T21

L28

K33

N28

R6

SATA_LE D#[28]

GPIO52 internal pull Hi 8.2K to +3V

GPIO53 internal pull Hi 8.2K to +3V

GPIO54 internal pull Hi 8.2K to +3V

GPIO56 internal pull Hi 8.2K to +3V

GPIO57 internal pull Hi 8.2K to +3V

GPIO58 internal pull Hi 8.2K to +3V

U25D

A3

A33

B7

B13

D9

D13

E5

E12

E16

E29

D D

C C

B B

F7

F9

F11

F13

F16

F17

F19

F23

F25

F29

G6

G16

G32

H12

H15

H29

J6

J9

J10

J13

J28

J32

K7

K16

K27

K28

L6

L12

L13

L15

L16

L21

M13

M16

M21

M25

N6

N11

N13

N23

N24

P12

P18

P20

P21

P31

P33

R4

R11

R25

R28

T11

T16

T18

N8

K25

H25

Hudson-M3-A 14

ID4 CONFIG 31- Level BOM Item

0

0

0 0 1

0

0

0

1 1

0

1

0

0

1

A A

0

1

0 0 0 0 1

0 0 1 0 1

1

0

0 1

1

0

1

1

11

5

4

SATA HDD

MINISATA

R170 *0_4/S

+1.1V_AV DD_SATA

4/19 For Comal.

1

2

3

4

5

6

7

8

9

10

11

12

4

PLACE SAT A AC COUPLING

CAPS CLO SE TO HUDSON- M2/M3

SATA_T XP0[28]

SATA_T XN0[28]

SATA_R XN0[28]

SATA_R XP0[28]

SATA_T XP1[28]

SATA_T XN1[28]

SATA_R XN1[28]

SATA_R XP1[28]

SB_SAT A_LED#

PV , ch ange

to shor t pad

PLACE SATA_ CAL RES V ERY

CLOSE TO BALL OF

HUDSON-M2/M3

R163 1K/F_4

R159 931/F_4

R178 *220/F_6

+3V

Integrated Clock Mode:

Leave un connected .

RF_OFF#[27]

TP99

TP39

ACC_LE D#[28]

LCD_BK[30]

R137

R136

10K/F_4

10K/F_4

SATA_T XP0

SATA_T XN0

SATA_T XP1

SATA_T XN1

SATA_C ALRP

SATA_C ALRN

SB_SAT A_LED#

RF_OFF#

BT_OFF#

BT_COM BO_EN#

LCD_BK

R378

10K/F_4

TEMPIN 0

TEMPIN 1

TEMPIN 2

TEMPIN 3

R138

10K/F_4

SIDE_PORT_ ID2

0

0

0 0 NC

0

0

1

U25B

AK19

SATA_T X0P

AM19

SATA_T X0N

AL20

SATA_R X0N

AN20

SATA_R X0P

AN22

SATA_T X1P

AL22

SATA_T X1N

AH20

SATA_R X1N

AJ20

SATA_R X1P

AJ22

SATA_T X2P

AH22

SATA_T X2N

AM23

SATA_R X2N

AK23

SATA_R X2P

AH24

SATA_T X3P

AJ24

SATA_T X3N

AN24

SATA_R X3N

AL24

SATA_R X3P

AL26

SATA_T X4P

AN26

SATA_T X4N

AJ26

SATA_R X4N

AH26

SATA_R X4P

AN29

SATA_T X5P

AL28

SATA_T X5N

AK27

SATA_R X5N

AM27

SATA_R X5P

AL29

NC6

AN31

NC7

AL31

NC8

AL33

NC9

AH33

NC10

AH31

NC11

AJ33

NC12

AJ31

NC13

AF28

SATA_C ALRP

AF27

SATA_C ALRN

AD22

SATA_A CT#/GPIO67

AF21

SATA_X 1

AG21

SATA_X 2

AH16

FANOU T0/GPIO52

AM15

FANOU T1/GPIO53

AJ16

FANOU T2/GPIO54

AK15

FANIN0/ GPIO56

AN16

FANIN1/ GPIO57

AL16

FANIN2/ GPIO58

K6

TEMPIN 0/GPIO171

K5

TEMPIN 1/GPIO172

K3

TEMPIN 2/GPIO173

M6

TEMPIN 3/TALERT#/ GPIO174

Hudson-M3-A 14

TEMP( 0 - 3 )

Temp M onitor Not Imp lemented

10-KΩ 5% pull-u p to +3VS5

or 10-KΩ 5% pull- down

SIDE_PORT_ ID0SIDE_PORT_ ID1

0

1

0 1 1

3

HUDSON-M3

HW

MONITOR

Samsung

Hynix

no supprot side port

3

SD

CARD

GBE

SERIAL

ATA

SPI

ROM

VGA

DAC

VGA

MAINLINK

Part 2 of 5

SD_CLK /SCLK_2/GP IO73

SD_CM D/SLOAD_2 /GPIO74

SD_CD #/GPIO75

SD_W P/GPIO76

SD_DAT A0/SDATI_2/ GPIO77