Page 1

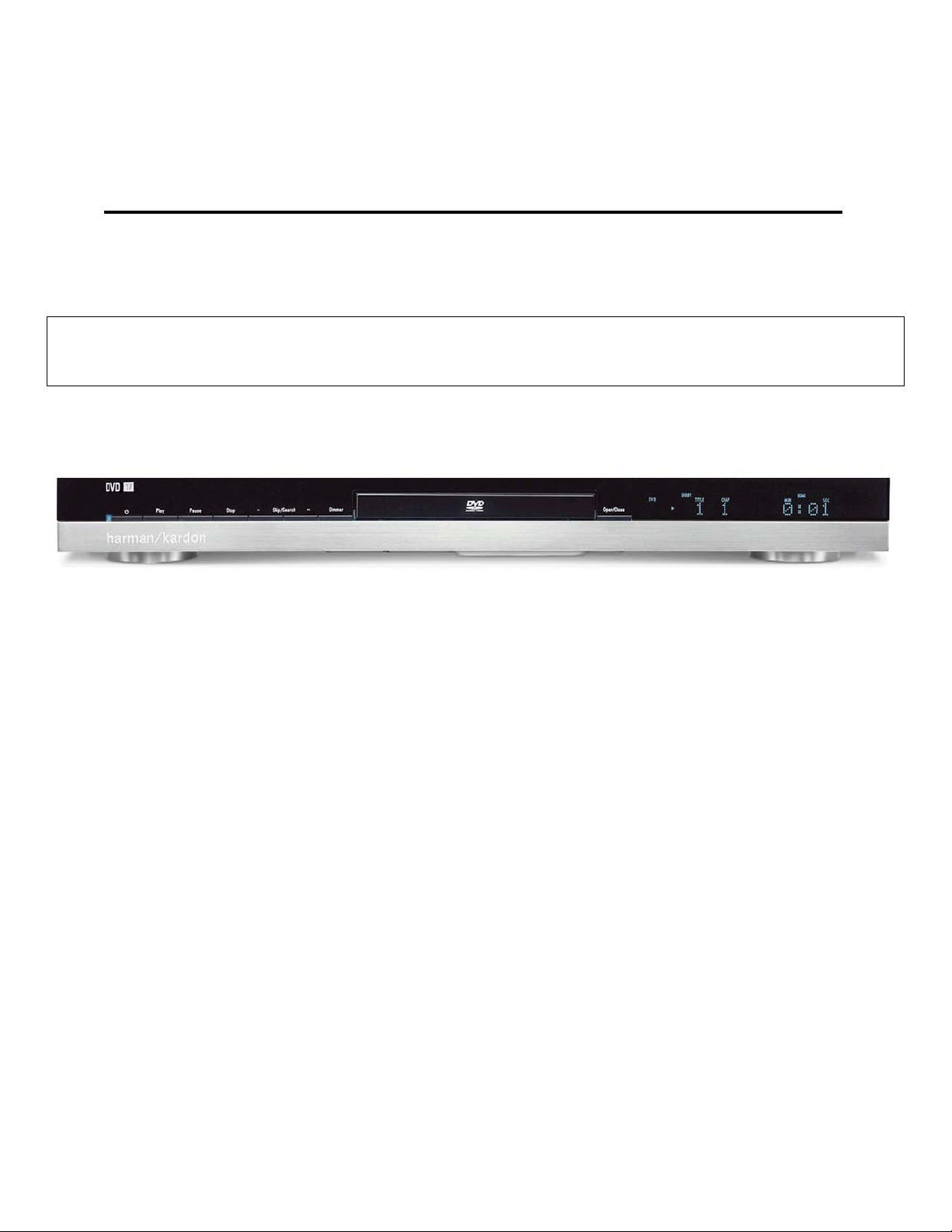

harman/kardon

Service manual DVD37EU

Page 1 of 117

Eu version

harman kardon

Model

DVD 37

DVD/CD/CD-R/CD-RW/VCD MP3 Player

Service Manual

CONTENTS

ESD WARNING............................ 2 ELECTRICAL PARTS LIST....... 14

SERVICING PRECAUTIONS....... 3 PCB DRAWINGS....................... 32

BASIC SPECIFICATIONS............ 5 SEMICONDUCTOR PINOUT.... 36

TROUBLESHOOTING GUIDE..... 10 BLOCK DIAGRAM................. 112

PACKAGE AND PACKAGE PARTS 11 WIRING DIAGRAM................ 113

DISASSEMBLY 12 SCHEMATIC DIAGRAMS....... 114

UNIT EXPLODED VIEW AND PARTS 13

harman/kardon, Inc.

250 Crossways Park Dr.

Woodbury, New York, 11797

Released 2007

Discontinued XXXX Rev 0, 8/2007

Page 2

harman/kardon

Service manual DVD37EU

Page 2 of 117

ESD PRECAUTIONS

Electrostatically Sensitive Devices (ESD)

Some semiconductor (solid state) devices can be damaged easily by static electricity. Such components commonly are called Electrostatically Sensitive Devices (ESD). Examples of typical ESD devices are integrated circuits and some field-effect transistors and semiconductor chip components. The following techniques should

be used to help reduce the incidence of component damage caused by static electricity.

1. Immediately before handling any semiconductor component or semiconductor-equipped assembly, drain off

any electrostatic charge on your body by touching a known earth ground. Alternatively, obtain and wear a

commercially available discharging wrist strap device, which should be removed for potential shock reasons

prior to applying power to the unit under test.

2. After removing an electrical assembly equipped with ESD devices, place the assembly on a conductive surface such as aluminum foil, to prevent electrostatic charge buildup or exposure of the assembly.

3. Use only a grounded-tip soldering iron to solder or unsolder ESD devices.

4. Use only an anti-static solder removal device. Some solder removal devices not classified as "anti-static"

can generate electrical charges sufficient to damage ESD devices.

5. Do not use freon-propelled chemicals. These can generate electrical charges sufficient to damage ESD

devices.

6. Do not remove a replacement ESD device from its protective package until immediately before you are

ready to install it. (Most replacement ESD devices are packaged with leads electrically shorted together by

conductive foam, aluminum foil or comparable conductive materials).

7. Immediately before removing the protective material from the leads of a replacement ESD device, touch the

protective material to the chassis or circuit assembly into which the device will by installed.

CAUTION : BE SURE NO POWER IS APPLIED TO THE CHASSIS OR CIRCUIT, AND OBSERVE ALL

OTHER SAFETY PRECAUTIONS.

8. Minimize bodily motions when handing unpackaged replacement ESD devices. (Otherwise harmless motion

such as the brushing together of your clothes fabric or the lifting of your foot from a carpeted floor can generate static electricity sufficient to damage an ESD device).

Page 3

SERVICING PRECAUTIONS

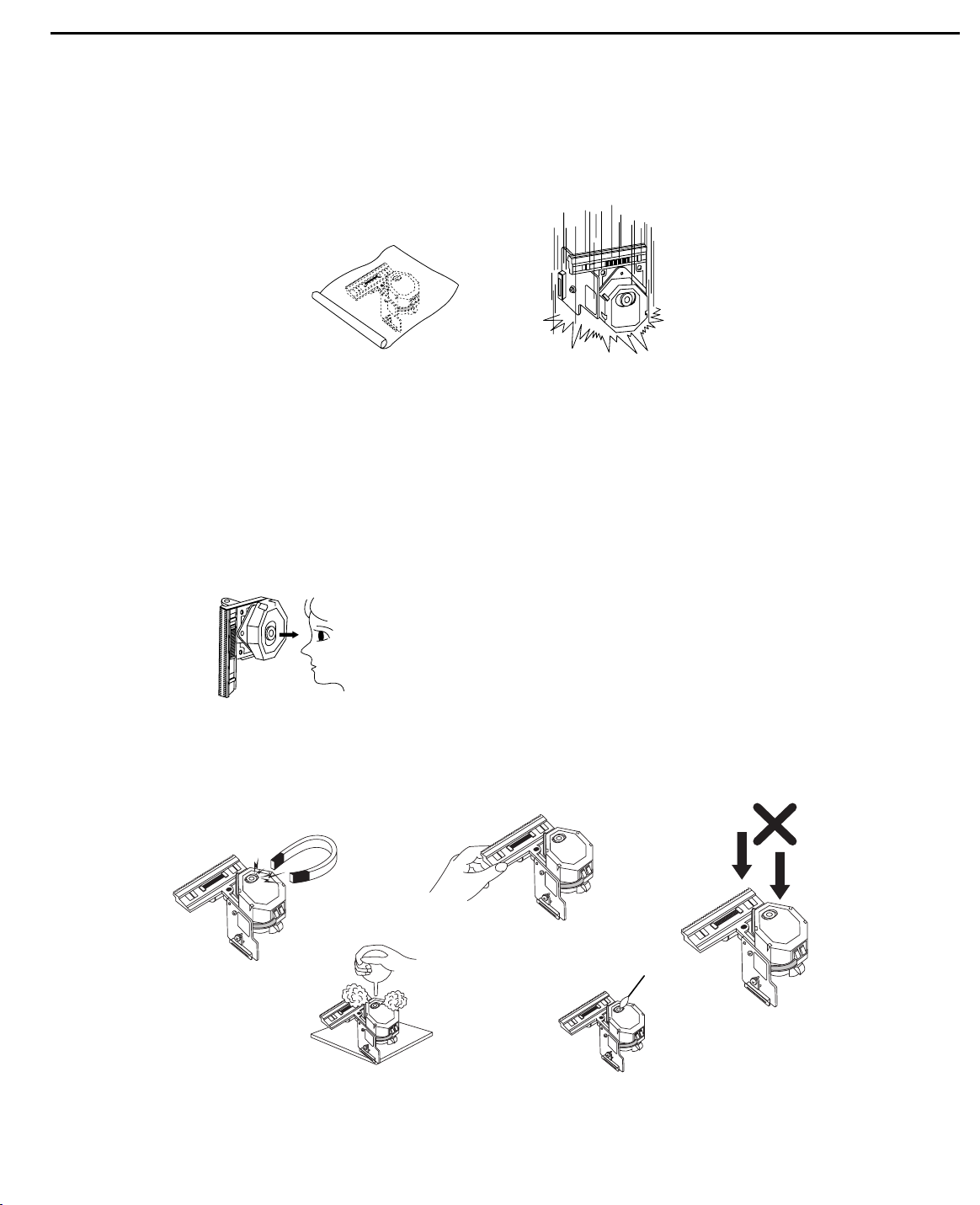

NOTES REGARDING HANDLING OF THE PICK-UP

1. Notes for transport and storage

1) The pick-up should always be left in its conductive bag until immediately prior to use.

2) The pick-up should never be subjected to external pressure or impact.

2. Repair notes

1) The pick-up incorporates a strong magnet, and so should never be brought close to magnetic materials.

2) The pick-up should always be handled correctly and carefully, taking care to avoid external pressure and

impact. If it is subjected to strong pressure or impact, the result may be an operational malfunction

and/or damage to the printed-circuit board.

3) Each and every pick-up is already individually adjusted to a high degree of precision, and for that reason

the adjustment point and installation

screws should absolutely never be touched.

4) Laser beams may damage the eyes!

Absolutely never permit laser beams to enter the eyes!

Also NEVER switch ON the power to the laser output part (lens, etc.) of the pick-up if it is damaged.

5) Cleaning the lens surface

If there is dust on the lens surface, the dust should be cleaned away by using an air bush (such as used

for camera lens). The lens is held by a delicate spring. When cleaning the lens surface, therefore, a cotton swab should be used, taking care not to distort this.

6) Never attempt to disassemble the pick-up.

Spring by excess pressure. If the lens is extremely dirty, apply isopropyl alcohol to the cotton swab. (Do

not use any other liquid cleaners, because they will damage the lens.) Take care not to use too much of

this alcohol on the swab, and do not allow the alcohol to get inside the pick-up.

Storage in conductive bag

NEVER look directly at the laser beam, and don’t let contact

fingers or other exposed skin.

Magnet

How to hold the pick-up

Conductive Sheet

Cotton swab

Pressure

Pressure

Drop impact

harman/kardon

Service manual DVD37EU

Page 3 of 117

Page 4

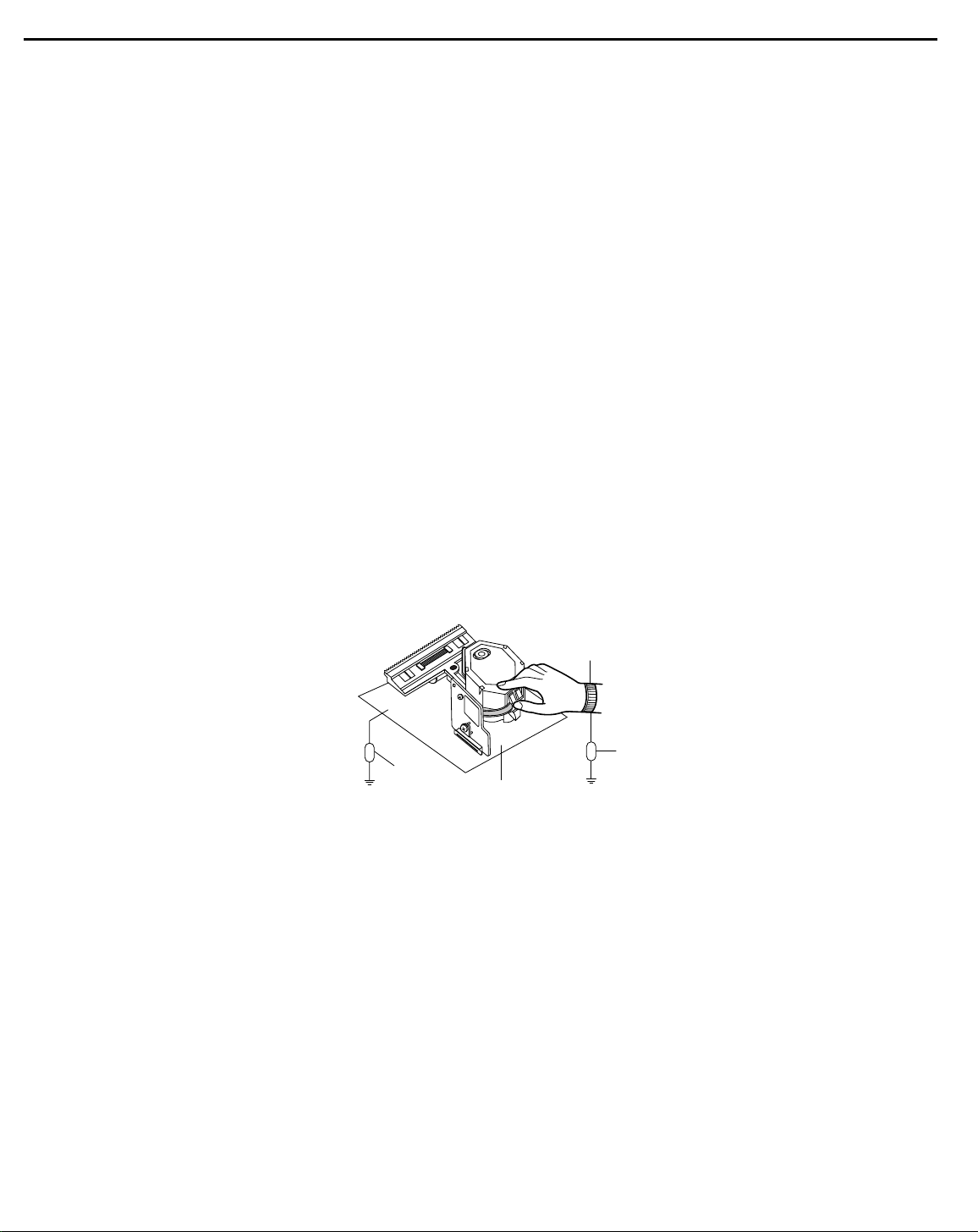

NOTES REGARDING COMPACT DISC PLAYER REPAIRS

1. Preparations

1) Compact disc players incorporate a great many ICs as well as the pick-up (laser diode). These components are sensitive to, and easily affected by, static electricity. If such static electricity is high voltage,

components can be damaged, and for that reason components should be handled with care.

2) The pick-up is composed of many optical components and other high-precision components. Care must

be taken, therefore, to avoid repair or storage where the temperature of humidity is high, where strong

magnetism is present, or where there is excessive dust.

2. Notes for repair

1) Before replacing a component part, first disconnect the power supply lead wire from the unit

2) All equipment, measuring instruments and tools must be grounded.

3) The workbench should be covered with a conductive sheet and grounded.

When removing the laser pick-up from its conductive bag, do not place the pick-up on the bag. (This is

because there is the possibility of damage by static electricity.)

4) To prevent AC leakage, the metal part of the soldering iron should be grounded.

5) Workers should be grounded by an armband (1MΩ)

6) Care should be taken not to permit the laser pick-up to come in contact with clothing, in order to prevent

static electricity changes in the clothing to escape from the armband.

7) The laser beam from the pick-up should NEVER be directly facing the eyes or bare skin.

Resistor

(1 Mohm)

Conductive

Sheet

Resistor

(1 Mohm)

Armband

harman/kardon

Service manual DVD37EU

Page 4 of 117

Page 5

DVD 37 TECHNICAL SPECIFICATIONS

harman/kardon

Service manual DVD37EU

Page 5 of 117

Applicable Disc: Disc formats: 5-inch (12cm) or 3-inch (8cm) DVD-Video, DVD-Audio, standard-conforming DVD-R, DVD+R, DVD-RW, DVD+RW,

VCD, CD, CD-R, CD-RW or MP3 discs

Region code: DVD video disc with Code 1 or 0 only

DVD layers: Single side/single layer, single side/dual layer, dual side/dual layer

Audio formats: DVD Audio MLP lossless, linear PCM, MPEG, Windows Media

Still-image format: JPEG

Video Signal System: NTSC

HDMI™Output: Video: 480p, 720p, 1080i

HDMI Version 1.0-compliant

HDCP Version 1.1-compliant

Composite Video Output: 1V p-p/75 ohms, sync negative polarity

S-Video Output: Y/luminance: 1V p-p/75 ohms, sync negative polarity

C/chrominance: 0.286V p-p

Component Video Output: Y: 1V p-p/75 ohms, sync negative polarity

Pr: 0.7V p-p/75 ohms

Pb: 0.7V p-p/75 ohms

Analog Audio Output: 2V RMS (1kHz, 0dB)

Frequency Response: DVD (linear PCM): 2Hz – 22kHz +0/–0.5dB (48kHz sampling)

2Hz – 44kHz +0/–1.5dB (96kHz sampling)

2Hz – 88kHz +0/–0.5dB (192kHz sampling)

CD: 2Hz – 20kHz +0/–0.5dB

Signal/Noise Ratio (SNR): 105dB (A-weighted)

Dynamic Range: DVD: 100dB (18-bit)/105dB (20-bit)

CD/DVD: 96dB (16-bit)

THD/1kHz: DVD/CD: 0.0025%

Wow & Flutter: Below measurable limits

AC Power: 110–240V AC/50–60Hz

Power Consumption: 1 Watt (on/standby)/13 watts (max)

Dimensions (H x W x D): 2" x 17-3/10" x 11-1/4" (50mm x 440mm x 285mm)

Weight: 6 lb (2.7kg)

Shipping Dimensions (H x W x D): 5" x 14-3/8" x 20" (127mm x 365mmx 508mm)

Shipping Weight: 8.8 lb (4kg)

®

9, Dolby®Digital or DTS®audio discs

Depth measurement includes knobs and connectors.

Height measurement includes feet and chassis.

All specifications subject to change without notice.

Harman Kardon and Harman International are trademarks of Harman International Industries, Incorporated, registered in the United States and/or other countries.

Dolby, Pro Logic and the double-D symbol are registered trademarks of Dolby Laboratories. Confidential Unpublished Works.

1992-1997 Dolby Laboratories, Inc.All rights reserved. Manufactured under license from Dolby Laboratories.

DTS and DTS-ES are registered trademarks of DTS, Inc.

Kodak and Photo CD are trademarks of Eastman Kodak Company.

Microsoft, Windows Media, HDCD and High Definition Compatible Digital are registered trademarks of Microsoft Corporation in the United States and/or other countries.

Blu-ray Disc is a trademark of the Blu-ray Disc Association.

HDMI, the HDMI logo and High-Definition Multimedia Interface are trademarks or registered trademarks of HDMI Licensing LLC.

HD-DVD is a trademark of the DVD Format/Logo Licensing Corporation (DVD FLLC).

SACD is a trademark of Sony Corporation.

This product incorporates copyright protection technology that is protected by method claims of certain U.S. patents and other intellectual property rights owned by

Macrovision Corporation and other rights owners. Use of this copyright protection technology must be authorized by Macrovision Corporation and is intended for home

and other limited viewing uses only unless otherwise authorized by Macrovision Corporation. Reverse engineering or disassembly is prohibited.

38 TECHNICAL SPECIFICATIONS

Page 6

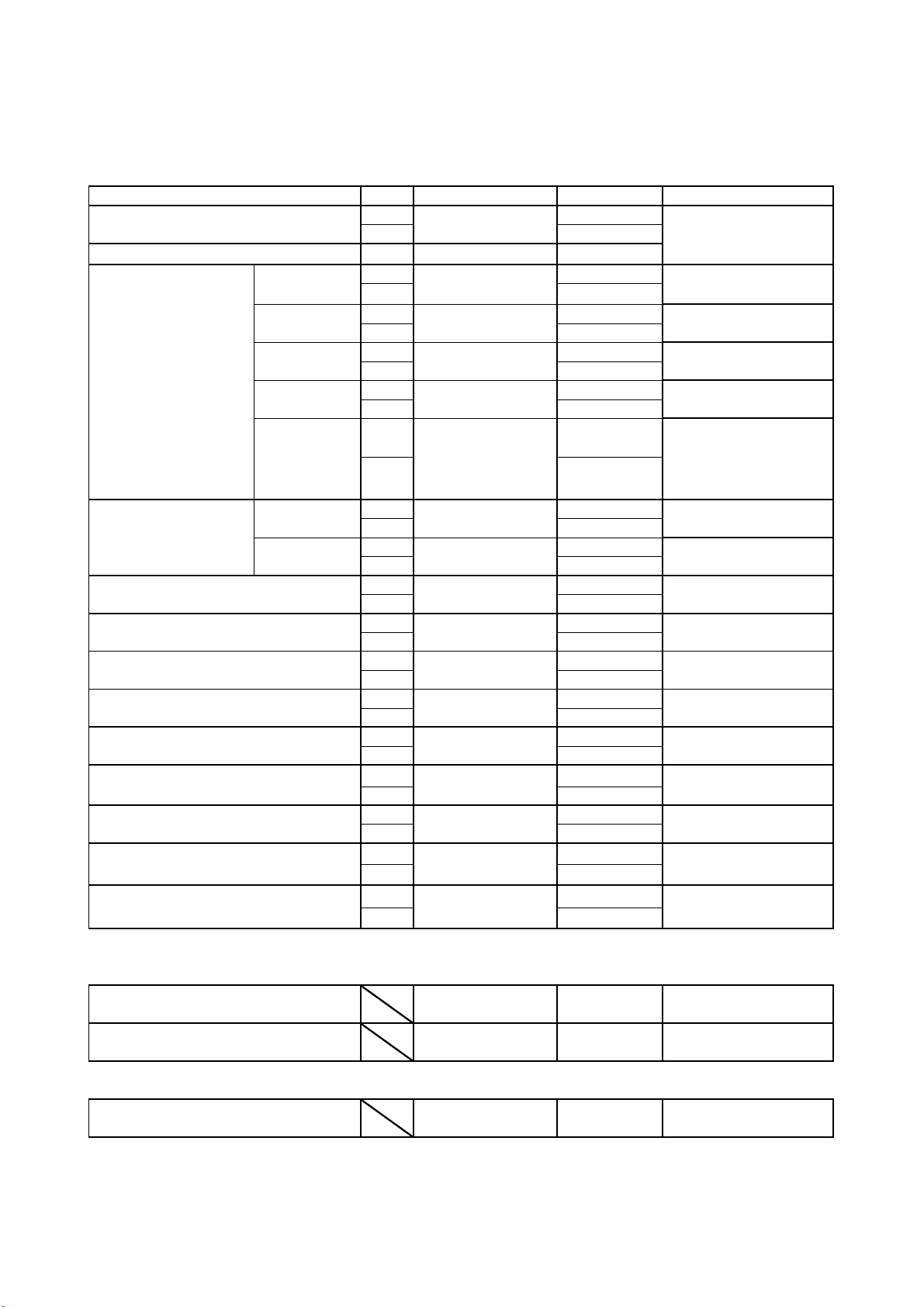

MODEL NAME : DVD 37 & DVD 37/230

D

ifi

f

Audi

o

TDV-540A (ABEX)

,

TDV-540A (ABEX)

harman/kardon

Service manual DVD37EU

Page 6 of 117

escription : Characteristics Spec

cation o

o

Test Disc : YEDS7 (SONY), TDV-540A (ABEX)

Test Conditions : 10kΩ Load Terminated, AC100V 50/60Hz

Test Measuerment : VP-7722A (Audio Analyzer) ,CASCADE SYS-2522(AP)

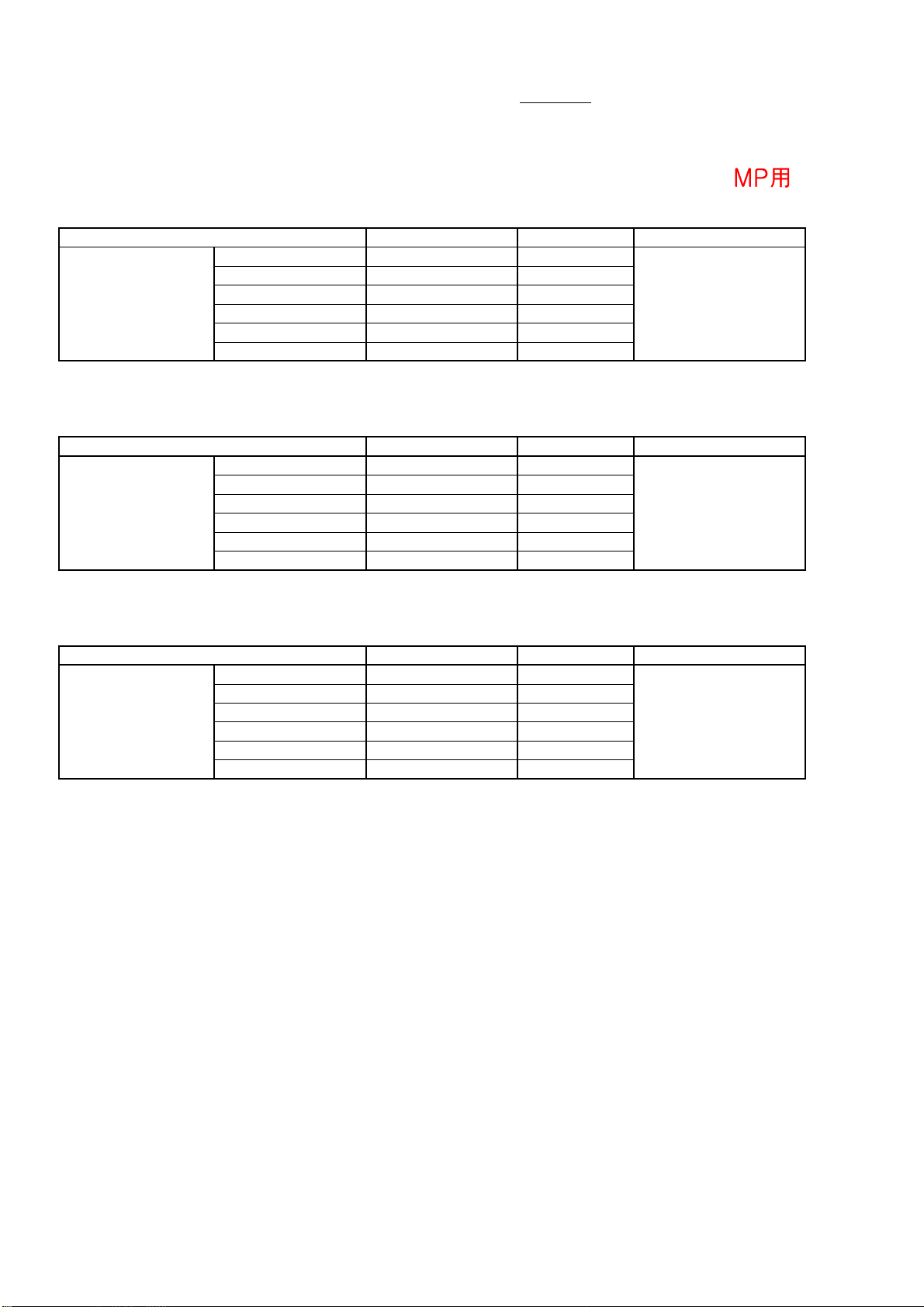

1.ANALOG AUDIO OUTPUT

Measurement Item

Output Level[Vrms] L

R

Limit Result

2.0 ± 0.2

YEDS7 (SONY)

Level difference [Vrms] < 0.2

F/ response [dB] L

Ref.1kHz 0dB L

z

2 0 H

100 Hz

10 KHz

20 KHz

R

R

L

R

L

R

L

44 KHz

R

Emphasis L

Characteristic[dB] R

Ref.1kHz 0dB L

5 KHz

16 KHz

R

S/N [dB] L

R

Channel Separation [dB] L→R

R→L

Linearity [dB] L

-90dB playback R

T.H.D [%] L

R

Dynamic Range [dB] L

-60dB playback R

全高調波歪率 [%] L

DVD 96k R

Dynamic Range [dB] L

DVD 96k R

全高調波歪率 [%] L

DVD 48k R

Dynamic Range [dB] L

DVD 48k R

0± 1.0

0± 1.0

0± 1.0

0± 1.5

0± 1.5

-4.53±1.0

-9.04 ± 1.0

>105

> 95

89.5±3

< 0.01

>93

< 0.01

>95

< 0.01

>95

YEDS7 (SONY)

YEDS7 (SONY)

YEDS7 (SONY)

YEDS7 (SONY)

TDV-540A (ABEX)

TITLE 4,CHAPTER

AUDIO STREAM 3

YEDS7 (SONY)

YEDS7 (SONY)

YEDS7 (SONY)

YEDS7 (SONY)

YEDS7 (SONY)

YEDS7 (SONY)

YEDS7 (SONY)

TDV-540A (ABEX)

TITLE 3, CHAPTER 1

TDV-540A (ABEX)

TITLE 3, CHAPTER 2

TITLE 2, CHAPTER 1

TITLE 2, CHAPTER 2

TEST DISC

TRACK 1

TRACK 2

TRACK 4

TRACK 10

TRACK 13

16

TRACK 40

TRACK 41

TRACK 23

TRACK 30

TRACK 22

TRACK 1

TRACK 20

34

2. DIGITAL OUTPUT

1) OPTICAL OUT

JITTER 44.1kHz Normal 44.1kHz

JITTER 96kHz Normal 96kHz

2) COAXIAL OUT

OUTPUT Level [mV] Normal CD or DVD

Peak to Peak Level at 75ohm L

(mUI) CD Playback

(mUI) DVD Playback

< 50mUI

< 50mUI

500±50 (mV)

Playback

Page 7

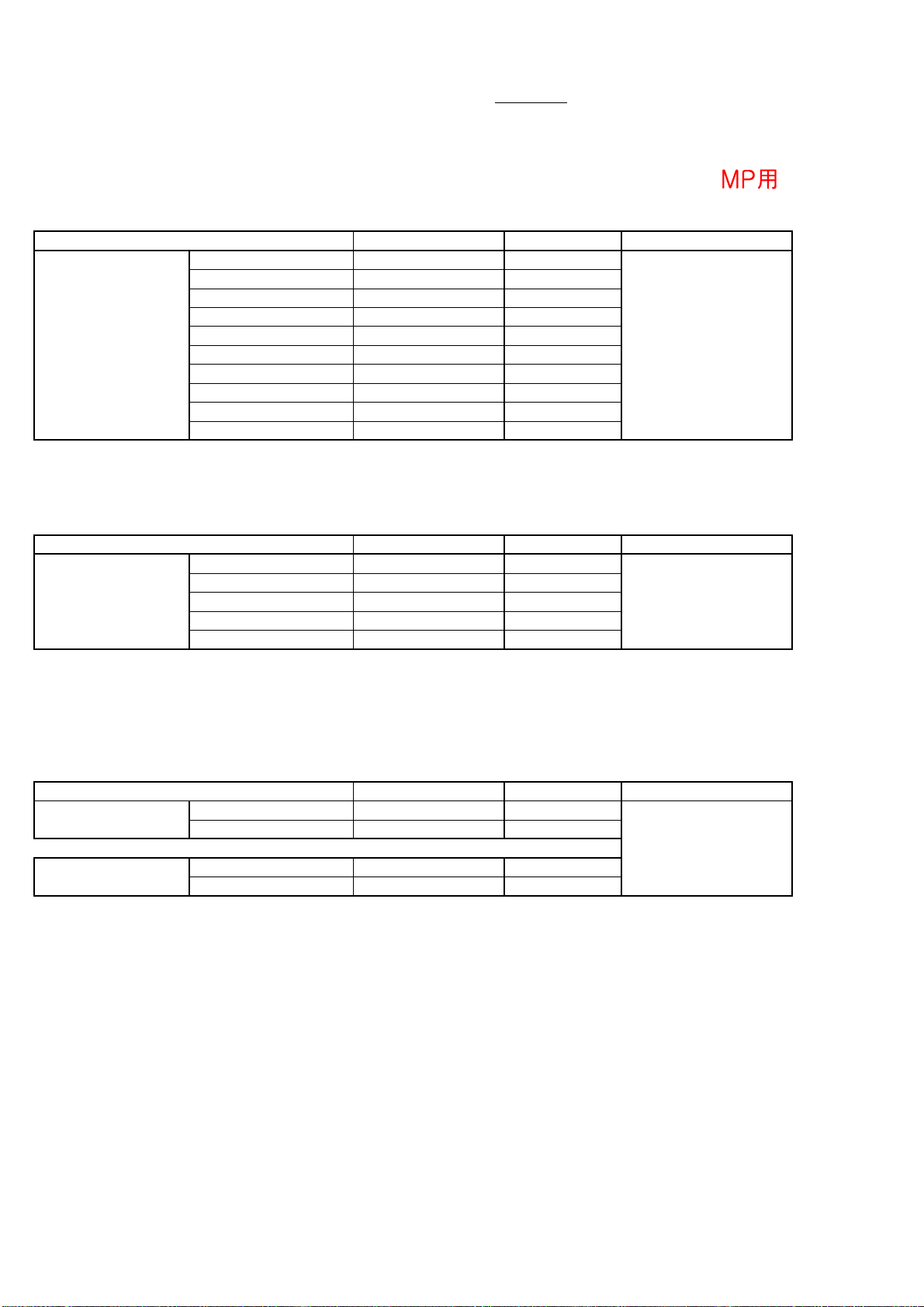

MODEL NAME : DVD 37& DVD 37/230

harman/kardon

Service manual DVD37EU

Page 7 of 117

Description : Characteristics Specification of Video

Test Disc : TDV-540A (ABEX) , MDVD-111 (TEAC) Serial NO.:

Test Conditions : 75Ω Load Terminated

AC Input : For USA (120V/60Hz) , For Europe (230V/50Hz)

Test Measuerment : VM-700T

4. Video Frequency Respoens (75Ω Terminated)

MP用

Measurement Item Result Test Disc

Composite [dB]

Measurement Item Result Test Disc

S-Video Y [dB]

Measurement Item Result Test Disc

Component Y

[dB]

Interace Mode

Limit

0.5MHz 0dB Ref. 0

1MHz 0dB ± 2dB

2MHz 0dB ± 2dB

3MHz 0dB ± 2dB

4MHz 0dB ± 2dB

5.8MHz -3dB ± 2dB

Limit

0.5MHz 0dB Ref. 0

1MHz 0dB ± 2dB

2MHz 0dB ± 2dB

3MHz 0dB ± 2dB

4MHz 0dB ± 2dB

5.8MHz -3dB ± 2dB

Limit

0.5MHz 0dB Ref. 0

1MHz 0dB ± 2dB

2MHz 0dB ± 2dB

3MHz 0dB ± 2dB

4MHz 0dB ± 2dB

5.8MHz -3dB ± 2dB

MDVD-111

TITLE2,CHAPTER9

100% Multi Brust

MDVD-111

TITLE2,CHAPTER9

100% Multi Brust

MDVD-111

TITLE2,CHAPTER9

100% Multi Brust

Page 8

MODEL NAME : DVD 37& DVD 37/230

harman/kardon

Service manual DVD37EU

Page 8 of 117

Description : Characteristics Specification of Video

Test Disc : TDV-540A (ABEX) , MDVD-111 (TEAC) Serial NO.:

Test Conditions : 75Ω Load Terminated

AC Input : For USA (120V/60Hz) , For Europe (230V/50Hz)

Test Measuerment : VM-700T

1. Video Level Test (75Ω Terminated)

MP用

Measurement Item Result Test Disc

Limit

Composite 1.0V ± 0.1V

S-Video Y 1.0V ± 0.1V

S-Video C 286mV ± 30mV

Video output [V]

Component Y 1.0V ± 0.1V

Component Pb 700mV ± 100mV

Component Pr 700mV ± 100mV

Scart CVBS 1.0V ± 0.15V

MDVD-111

TITLE2,CHAPTER1

100% COLOR BAR

Scart Red 700mV ± 100mV

Scart Green 700mV ± 100mV

Scart Blue 700mV ± 100mV

** Pb/Pr & RGB Video Level check before please setting the Black Level off in the set-up menu **

2. Video S/N Raito Test (75Ω Terminated)

Measurement Item Result Test Disc

Limit

Composite ≥ 65.0 dB

Video SNR [dB]

100KHz~4.2MHz

Use SC Trap

S-Video Y ≥ 65.0 dB

Component Y ≥ 65.0 dB

Component Pb ≥ 65.0 dB

MDVD-111

TITLE2,CHAPTER 4

50% Gray Color

Component Pr ≥ 65.0 dB

3. Chroma Signal AM.PM Test (75Ω Terminated)

Measurement Item Result Test Disc

Chroma AM [dB]

10KHz~500KHz

Chroma PM [dB]

10KHz~500KHz

Composite Chroma ≥ 65.0 dB

S-Video Chroma ≥ 65.0 dB

Composite Chroma ≥ 60.0 dB

S-Video Chroma ≥ 60.0 dB

Limit

TDV-540A

TITLE2,CHAPTER17

100% Magenta

Color

Page 9

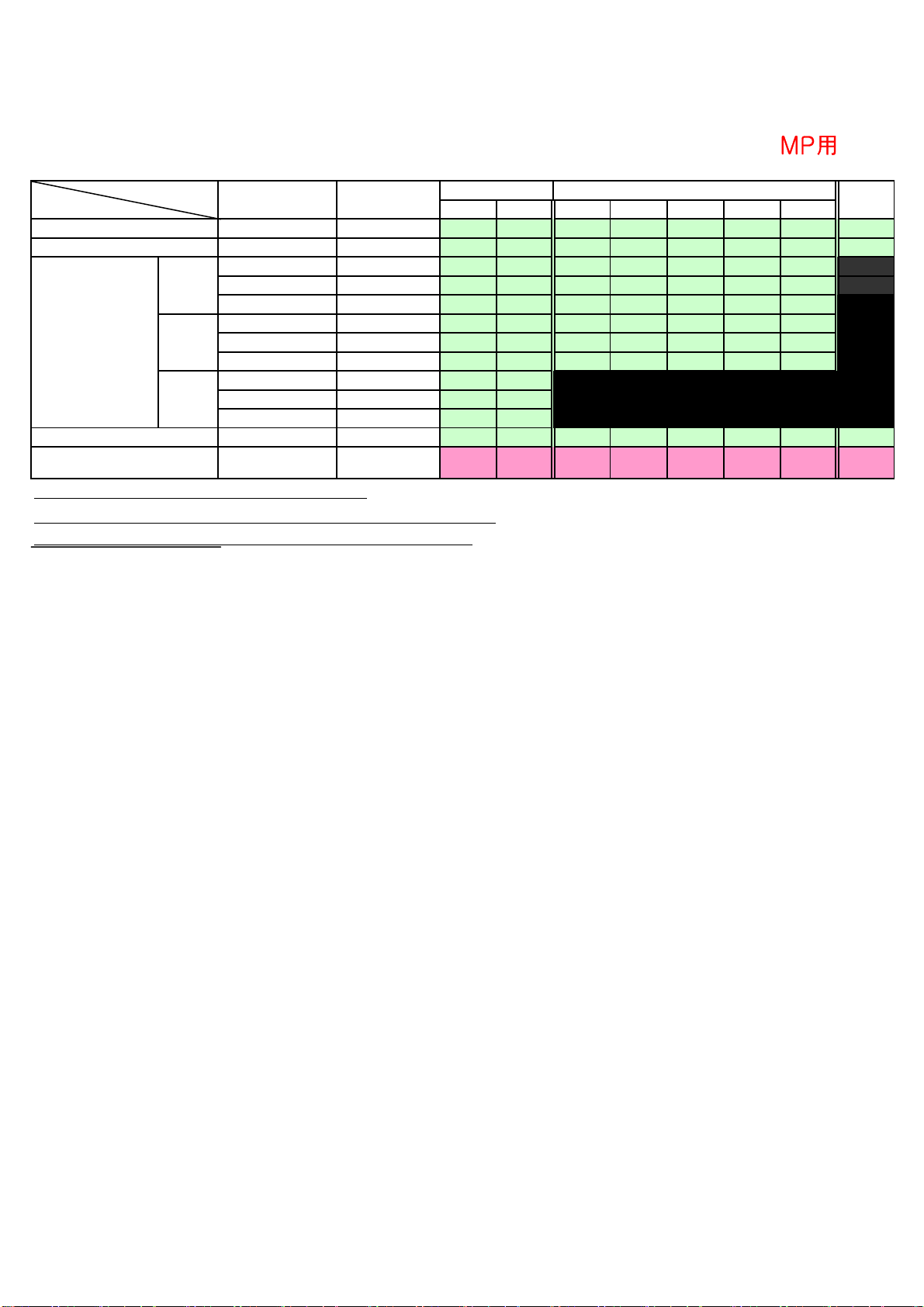

用

2. DVD-Audio Part (Test Disc V-612 , JVC)

harman/kardon

Service manual DVD37EU

Page 9 of 117

LimitTrack Inform.

Output Level (V)

T.H.D (%) 20KHz LPF

48 / 24

Frequency

Respones (dB)

Ref. : Tr. 38

S/N (dB) "A" Filter

Dynamic Range (dB)

20KHz LPF

96 / 20

192 / 24

Tr.38 1KHz 0dB 2.1±0.2Vrms

Tr.38 1KHz 0dB ↓0.01%

Tr.59 17Hz 0±1.0dB

Tr.54 10KHz 0±1.0dB

Tr.53 20KHz 0±2.0dB

Tr.49 17Hz 0±1.0dB

Tr.45 10KHz 0±1.0dB

Tr.44 20KHz 0±2.0dB

Tr.22 17Hz 0±1.0dB

Tr.18 10KHz 0±1.0dB

Tr.17 20KHz 0±2.0dB

Tr.40 Infinity Zero ↑90dB

Tr.39 -60dB ↑85dB

★ SW Level & THD --> Track 38 (30Hz) Play.

★ SW Frequency Respones -> Track 55(31Hz , 0dB) Reference

★ Track 54 (61Hz) , Track 53 (81Hz) , Track 51(127Hz) Play

Downmix 2CH Muiti 5 CH

LT RT FL FR SL SR C

MP

SW

Page 10

TROUBLESHOOTING GUIDE

harman/kardon

Service manual DVD37EU

Page 10 of 117

TROUBLESHOOTING GUIDE

SYMPTOM POSSIBLE CAUSE SOLUTION

Unit does not turn on • No AC power • Check AC power plug and make certain any switched

outlet is turned on.

Disc does not play • Disc loaded improperly • Load disc label-side up; align the disc with the guides and place

it in its proper position.

• Incorrect disc type • Check to see that disc is SACD, CD, CD-R, CD-RW, VCD, MP3, WMA, JPEG,

DVD-R, DVD-RW, DVD+R, DVD+RW (standard-conforming), DVD-Audio or

DVD-Video; other types will not play.

• Invalid Region Code • Use Region 1 or Open Region (0) disc only.

• Rating is above parental preset • Enter password to override or change rating settings (see page 20).

No picture • Intermittent connections • Check all video connections.

• Wrong input • Check input selection of TV or receiver.

• Progressive Scan output selected • Use Progressive Scan mode only with compatible TV. Press

Interlaced Button

• Video Off feature active • Press

•

HDMI Output 2 is connected to a • The HDMI Output 2 may not be used with video displays that are not

video display that is not HDCP-compliant. HDCP-compliant. Unplug the cable and select another audio and video

Video Off ButtonFto reactivate video circuitry.

connection (see pages 14 through 16).

I to toggle to the correct mode (see page 23).

Progressive Scan/

No sound • Intermittent connections • Check all audio connections.

• Incorrect digital audio selection • Check digital audio settings on DVD 47 and on receiver.

• DVD disc is in fast or slow mode • There is no audio playback on DVD discs during fast or slow modes.

• Surround receiver not compatible • Use analog audio outputs.

with 96kHz PCM audio

• DVD Audio or SACD disc is loaded • Use

without using analog audio connection

Picture is distorted or jumps during • MPEG-2 decoding • It is a normal artifact of DVD playback for pictures to jump or show

fast forward or reverse play some distortion during rapid play.

Some remote buttons do not operate • Function not permitted at this time • With most discs, some functions are not permitted at certain

during DVD play; prohibited symbol times (e.g., Track Skip) or at all (e.g., direct audio track selection).

appears (see below)

The OSD menu is in a foreign language • Incorrect OSD language • Change the display language selection (see page 23).

The symbol appears • Requested function not available at • Certain functions may be disabled by the DVD itself during

this time passages of a disc.

Picture is displayed in the • Incorrect match of aspect ratio settings • Change aspect ratio settings (see page 23).

wrong aspect ratio to disc

Remote control inoperative • Weak batteries • Change both batteries.

• Sensor is blocked • Clear path to sensor or use optional outboard remote sensor.

Disc will not copy to VCR • Copy protection • Many DVDs are encoded with copy protection to prevent

6-Channel Audio Outputs 9 or Analog Audio Outputs 8.

copying to VCR.

Password not accepted. • Incorrect password being used or • Stop play of disc. Press and hold

Clear Button 3 until the display blinks.

password has been forgotten. This resets the password and all settings to their defaults.

TROUBLESHOOTING GUIDE 37

Page 11

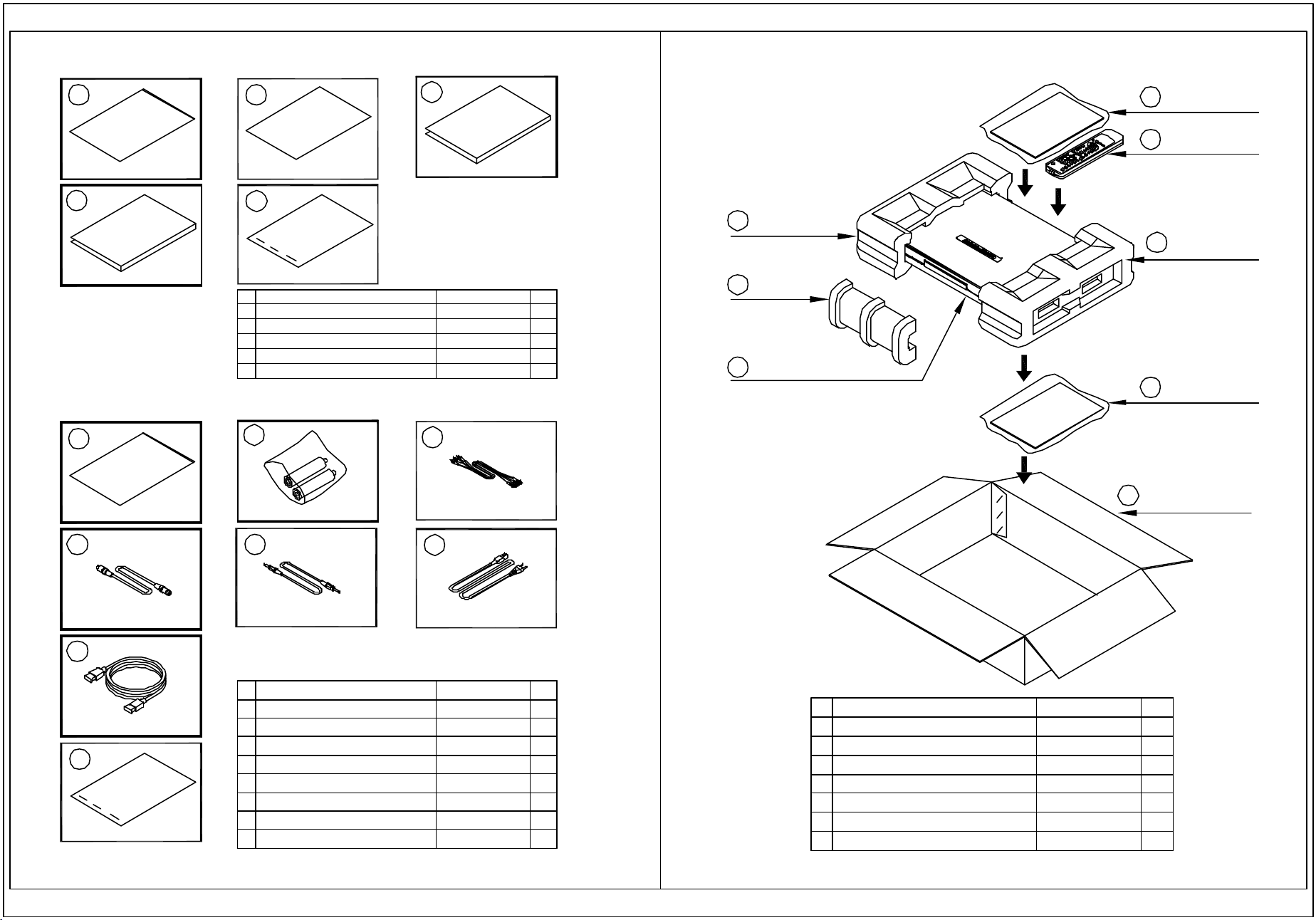

1. Instruction manual ass'y - Accessories 2. Package Drawing

harman/kardon

Service manual DVD37EU

Page 11 of 117

DVD37/230

1

POLY BAG

4

MANUAL INSTRUCTION

2

HARMAN IMAGE BROCHURES

4

STAPLE

NO DESCRIPTION PARTS NO.

1

2

SAFETY MANUAL CQX1A1049Z

3

4

INSTRUCTION MANUAL CQX1A1053Z

5

STAPLE CPL0905 3

1. Cable ass'y - Accessories

1

POLY BAG

2

BATTERY ASS'Y

3

MANUAL SAFETY

CPB1061YPOLY BAG

HQE1A273ZHARMAN IMAGE BROCHURES 1

3

CORD PIN(3P, W/R/Y)

Q,ty

MANUAL ASS'Y

1

REMOCON ASS'Y

6

3

SNOW PAD

SNOW PAD

3

4

SNOW PAD

1

1

1

1

SET

2

CABLE ASS'Y

7

BOX ,OUT CARTON

5

4

CABLE,S-VHS(1.5M)

7

CABLE, HDMI(2M)

8

STAPLE

5

CORF ,JACK(MONO)1200MM

NO DESCRIPTION PARTS NO. Q,ty

1

2

BATTERY

3

CORD,PIN(3P,W/R/Y)

4

CABLE,S-VHS(1.5M)

5

CORD,JACK(MONO)1200MM CJS9D002Z 1

6

AC CORD CJA2B020Z 1

7

CABLE,HDMI(2M) CJS8T001Z 1

STAPLE8 KPL0905

6

AC CORD

CABR03P

CJS4S004Z

CJS0I006Z

1CPB1061YPOLY BAG

MANUAL ASS'Y

2

1

1

3

1

2

SET DVD37/230 1

31SNOW,PAD

4

BOX,OUT CARTON

5

6

REMOCON ASS'Y CARTDVD37A 1

7

CABLE ASS'Y CQXDVD47 1

DESCRIPTIONNO

CQXDVD37A/230

CPS1A714

CPS1A715SNOW,PAD

CPG1A798V

Q,tyPARTS NO.

1

2

1

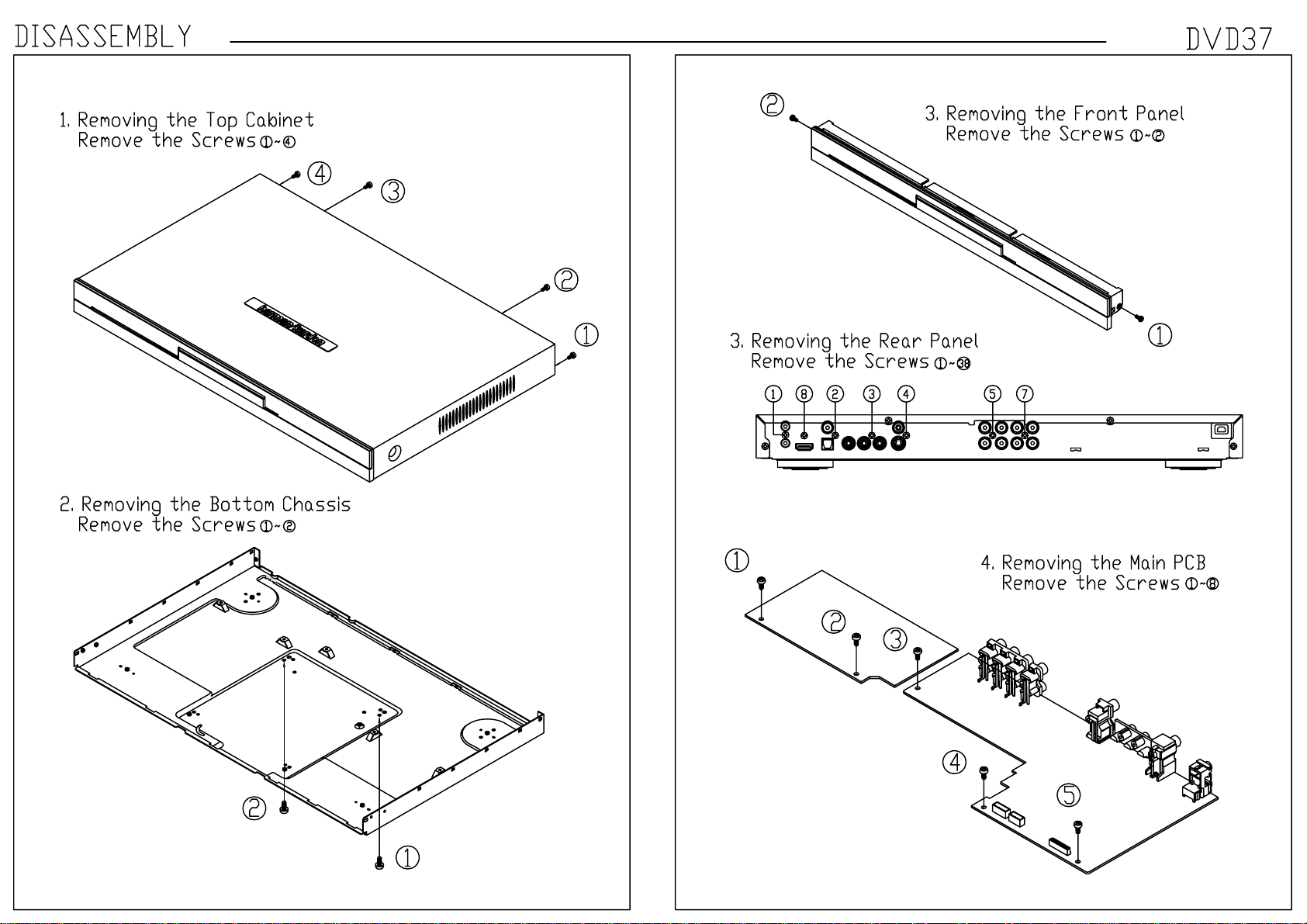

Page 12

harman/kardon

Service manual DVD37EU

Page 12 of 117

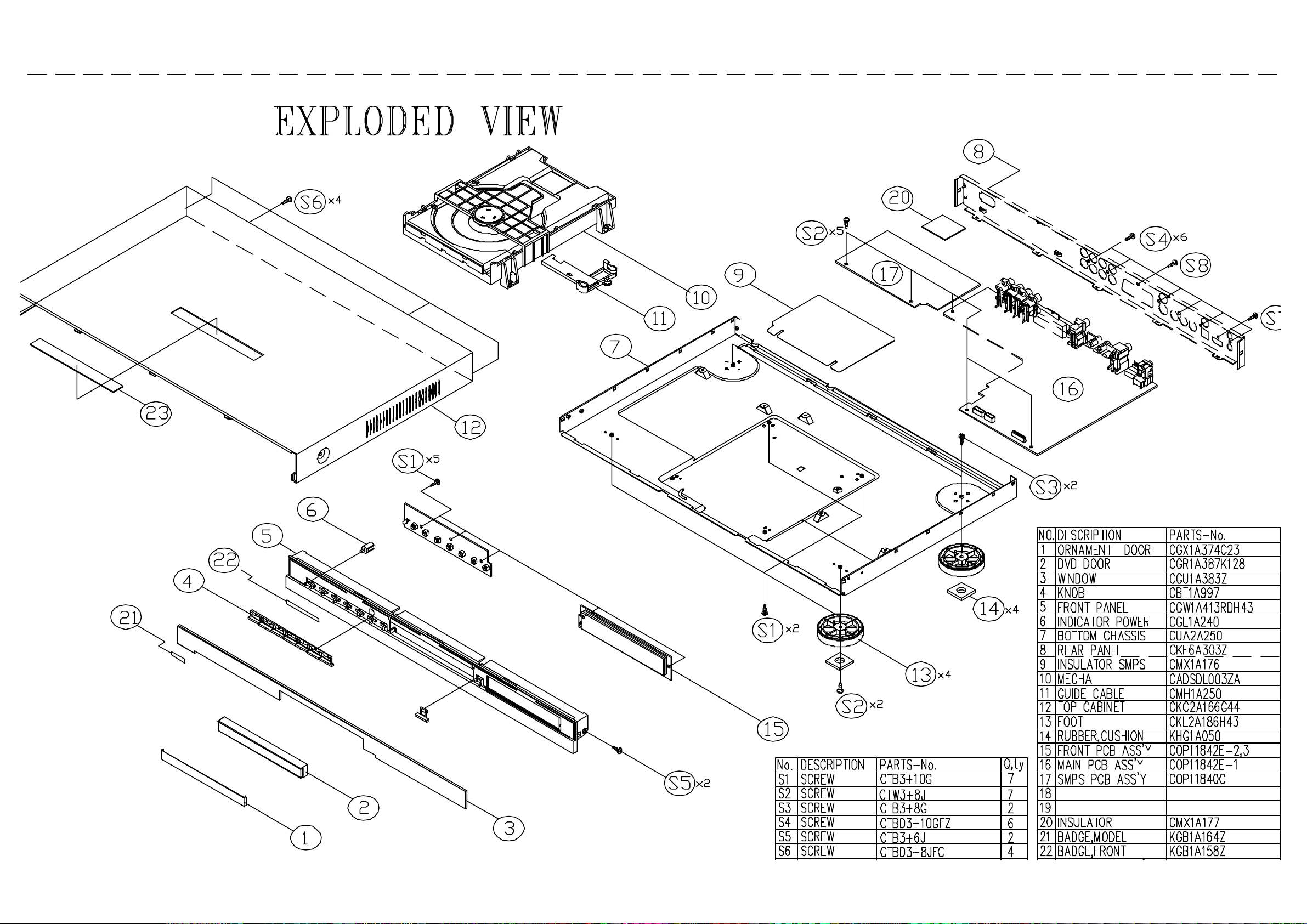

Page 13

harman/kardon

Service manual DVD37EU

Page 13 of 117

A

See part list

y

Page 14

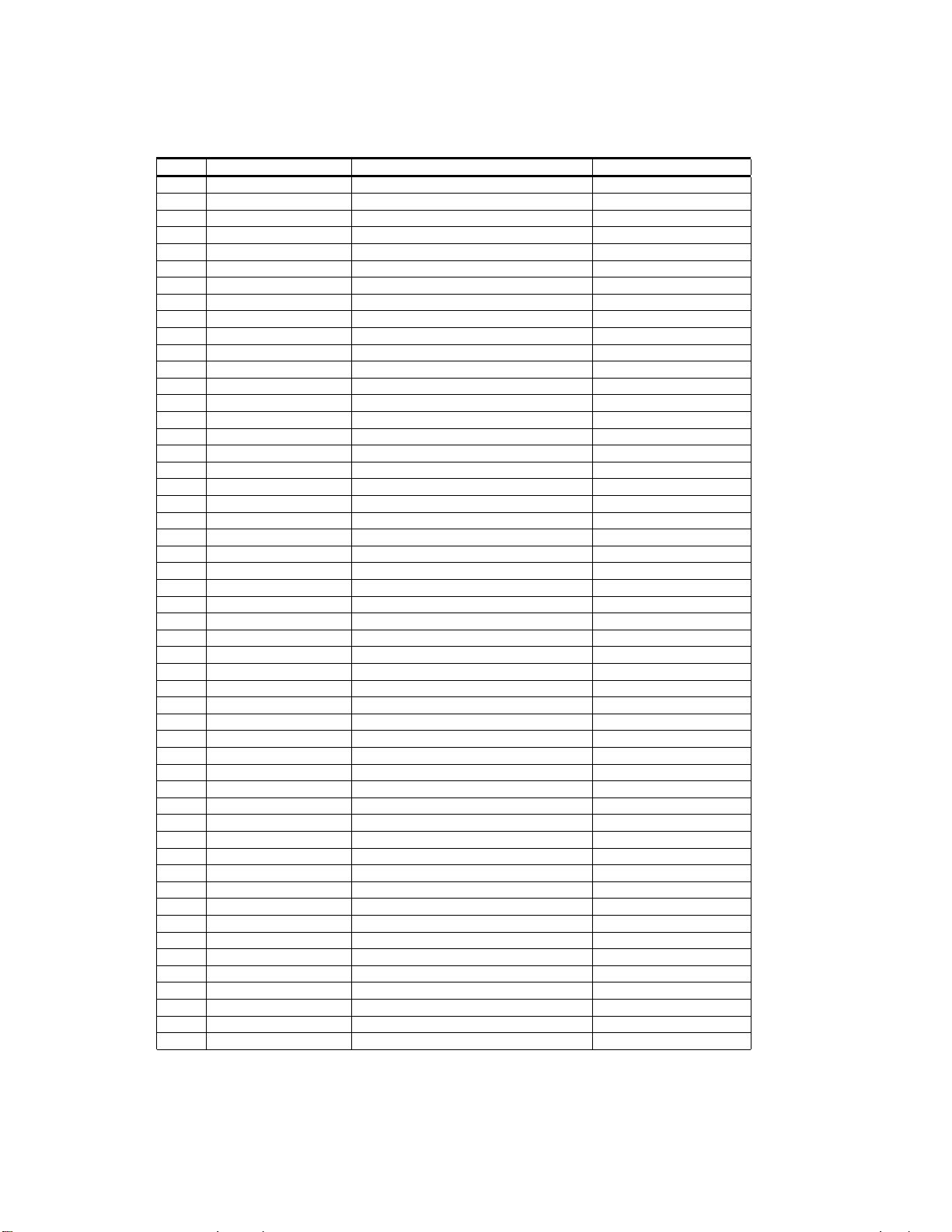

H

FRONT AND MAIN PCB

harman/kardon

Service manual DVD37EU

Page 14 of 117

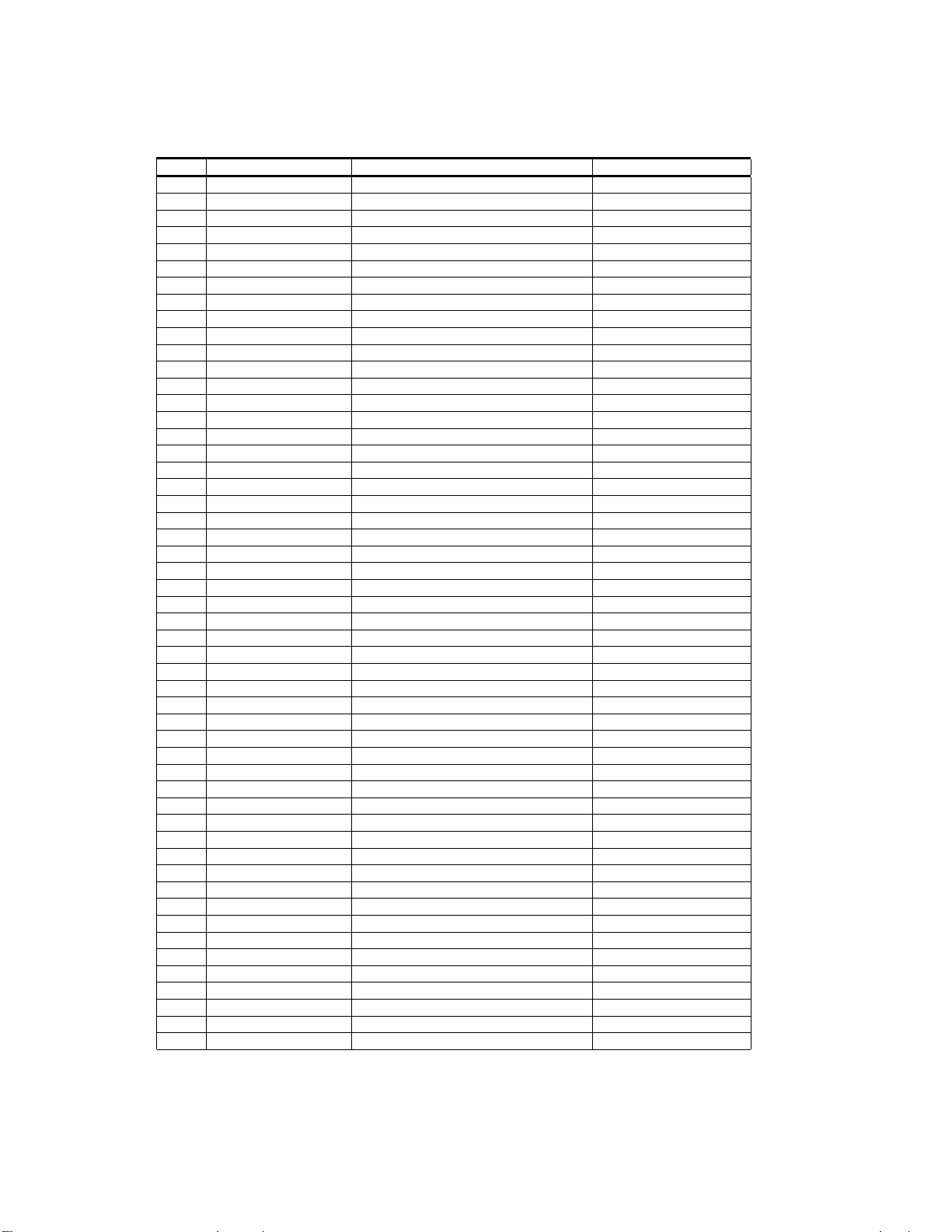

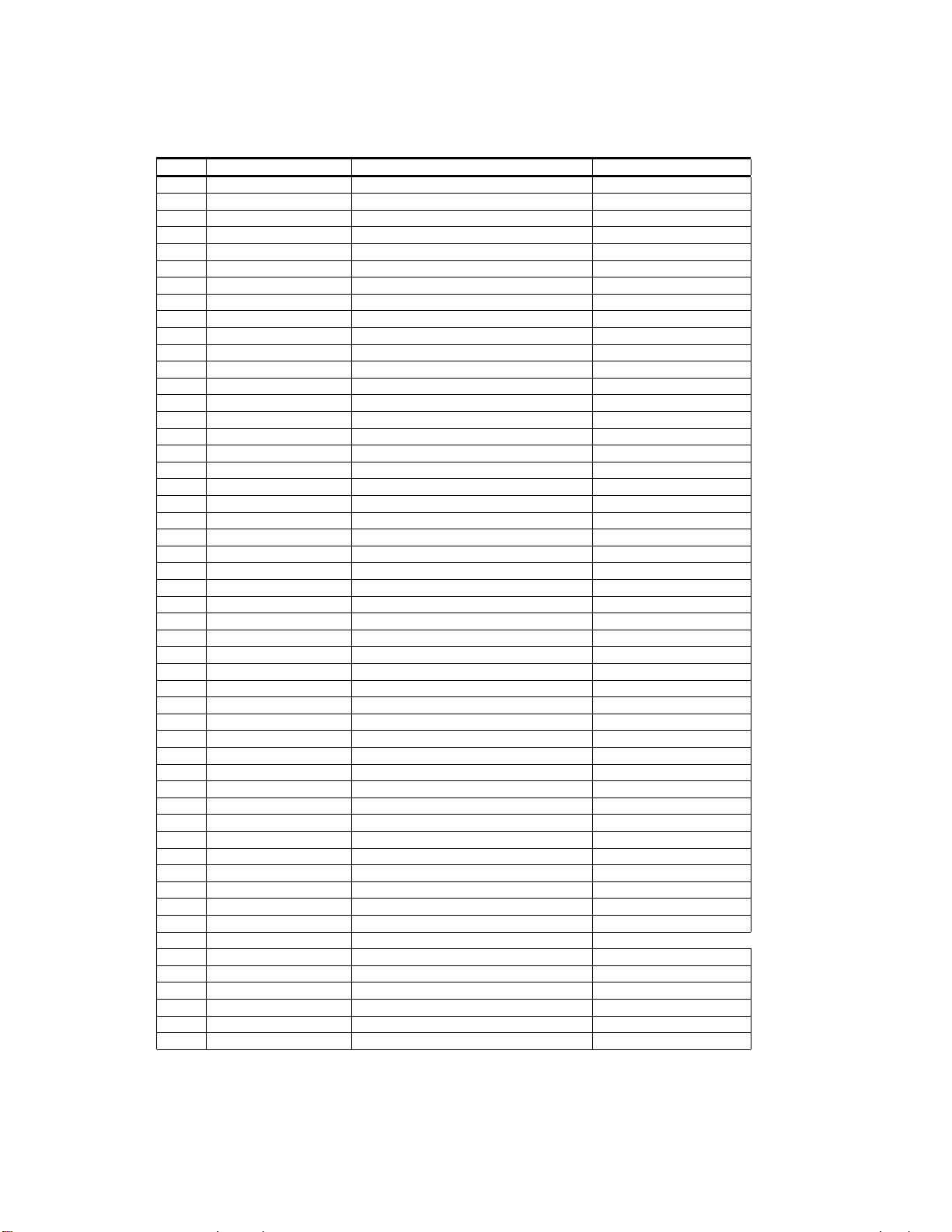

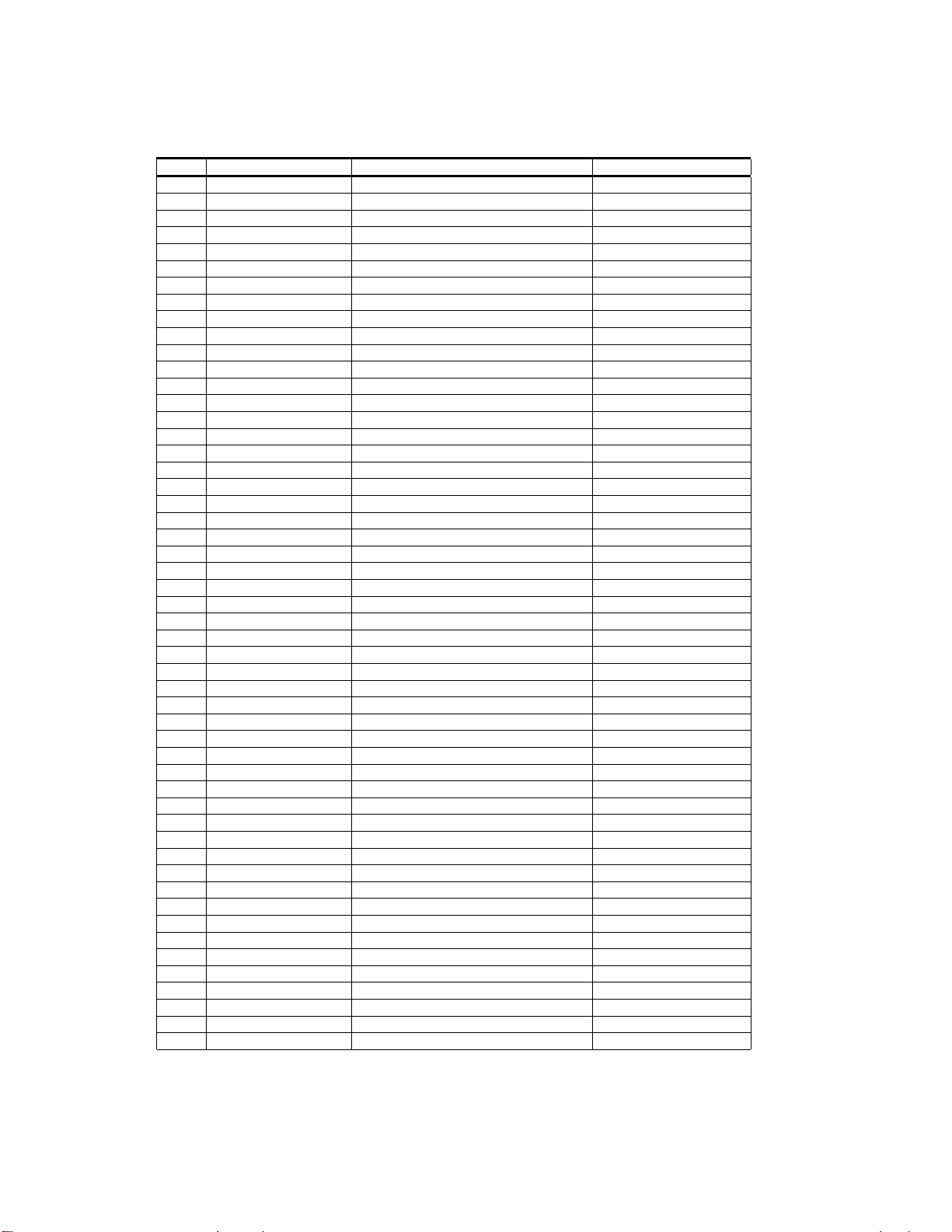

Ref# Component Description Drawing No

COP11842F DVD37/230 MAIN PCB ASS'Y DVD37A/230 (EUR)

COP11842F-1 FRONT PCB DISPLAY ASS'Y DVD37A/230 (EUR)

COP11842F-2 FRONT PCB CONTROL ASS'Y DVD37A/230 (EUR)

CN11 CJP24GA195ZM SMT FFC/FPC WAFER(0.5MM PITC

C100 CCUS1H104KC CAP , CHIP

C101 CCUS1H104KC CAP , CHIP

C102 CCUS1H104KC CAP , CHIP

C103 CCUS1H104KC CAP , CHIP

C104 CCUS1H104KC CAP , CHIP

C106 CCUS1H104KC CAP , CHIP

C107 CCUS1H104KC CAP , CHIP

C110 CCUS1H104KC CAP , CHIP

C112 CCUS1H104KC CAP , CHIP

C113 CCUS1H104KC CAP , CHIP

C115 CCUS1H104KC CAP , CHIP

C117 CCUS1H104KC CAP , CHIP

C120 CCUS1H104KC CAP , CHIP

C122 CCUS1H104KC CAP , CHIP

C124 CCUS1H104KC CAP , CHIP

C126 CCUS1H104KC CAP , CHIP

C127 CCUS1H104KC CAP , CHIP

C129 CCUS1H104KC CAP , CHIP

C131 CCUS1H104KC CAP , CHIP

C132 CCUS1H104KC CAP , CHIP

C133 CCUS1H104KC CAP , CHIP

C138 CCUS1H104KC CAP , CHIP

C140 CCUS1H104KC CAP , CHIP

C141 CCUS1H104KC CAP , CHIP

C143 CCUS1H104KC CAP , CHIP

52559-2472 (PB FREE)

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

C144 CCUS1H103KC CAP , CHIP 0.01UF ZF 1608

C146 CCUS1H104KC CAP , CHIP

C148 CCUS1H104KC CAP , CHIP

C149 CCUS1H104KC CAP , CHIP

C151 CCUS1H104KC CAP , CHIP

C152 CCUS1H104KC CAP , CHIP

C153 CCUS1H104KC CAP , CHIP

C154 CCUS1H104KC CAP , CHIP

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

C156 CCUS1H180JA CHIP, CAP 18PF/50V/1608 18PF/50V/1608

C156 CCUS1H180JA CHIP, CAP 18PF/50V/1608 18PF/50V/1608

C157 CCUS1H330JA CAP , CHIP

C158 CCUS1H330JA CAP , CHIP

C159 CCUS1H562KC CHIP CERAMIC CAP. 1608 (5600p)

C160 CCUS1H562KC CHIP CERAMIC CAP. 1608 (5600p)

C161 CCUS1H562KC CHIP CERAMIC CAP. 1608 (5600p)

C163 CCUS1H471JA CAP , CHIP

C164 CCUS1H104KC CAP , CHIP

C165 CCUS1H104KC CAP , CHIP

C166 CCUS1H102KC CAP , CHIP

C167 CCUS1H102KC CAP , CHIP

C168 CCUS1H102KC CAP , CHIP

C169 CCUS1H102KC CAP , CHIP

C170 CCUS1H102KC CAP , CHIP

33PF JA 1608

33PF JA 1608

5600PF KC 1608

5600PF KC 1608

5600PF KC 1608

470PF JA 1608

0.1UF ZF 1608

0.1UF ZF 1608

1000PF KC 1608

1000PF KC 1608

1000PF KC 1608

1000PF KC 1608

1000PF KC 1608

Page 15

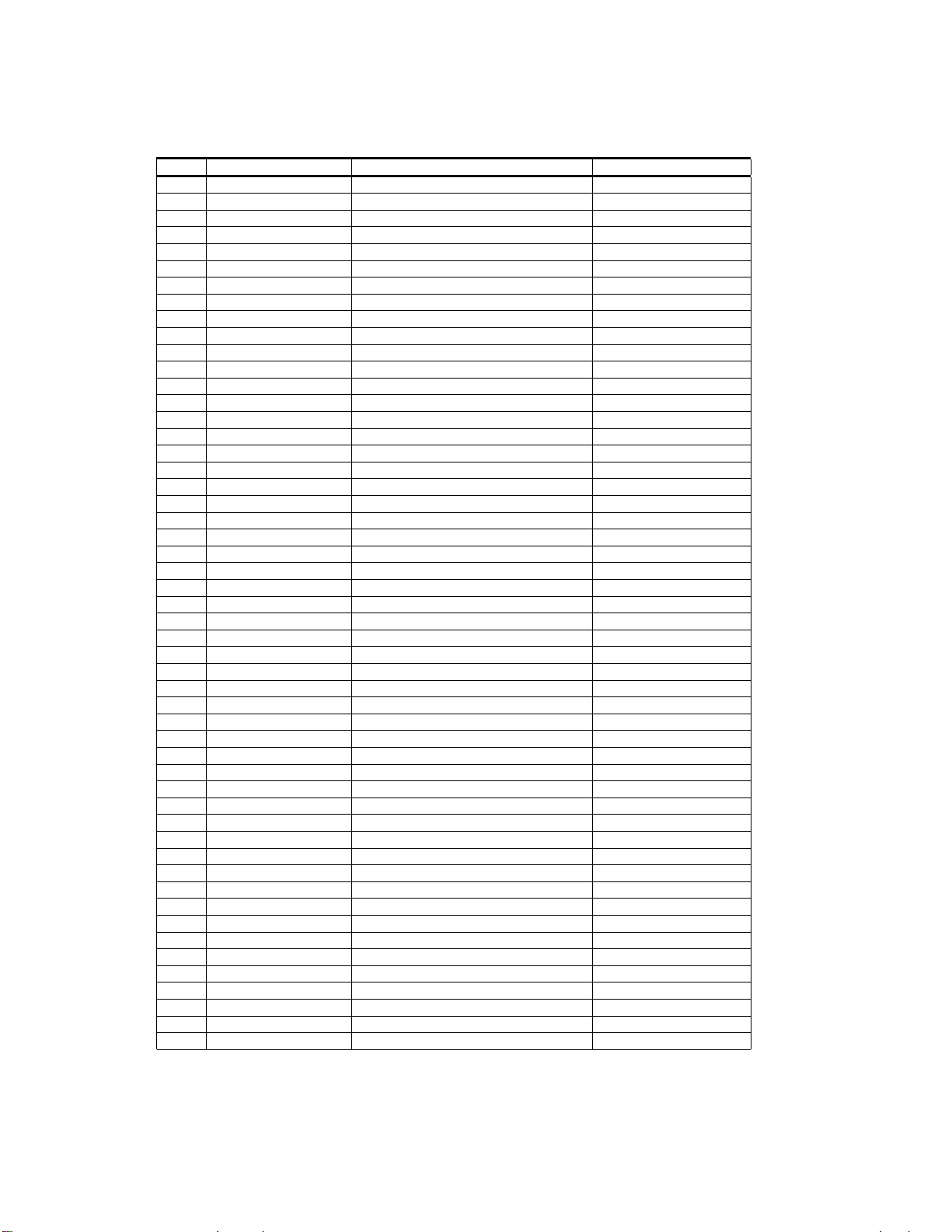

FRONT AND MAIN PCB

harman/kardon

Service manual DVD37EU

Page 15 of 117

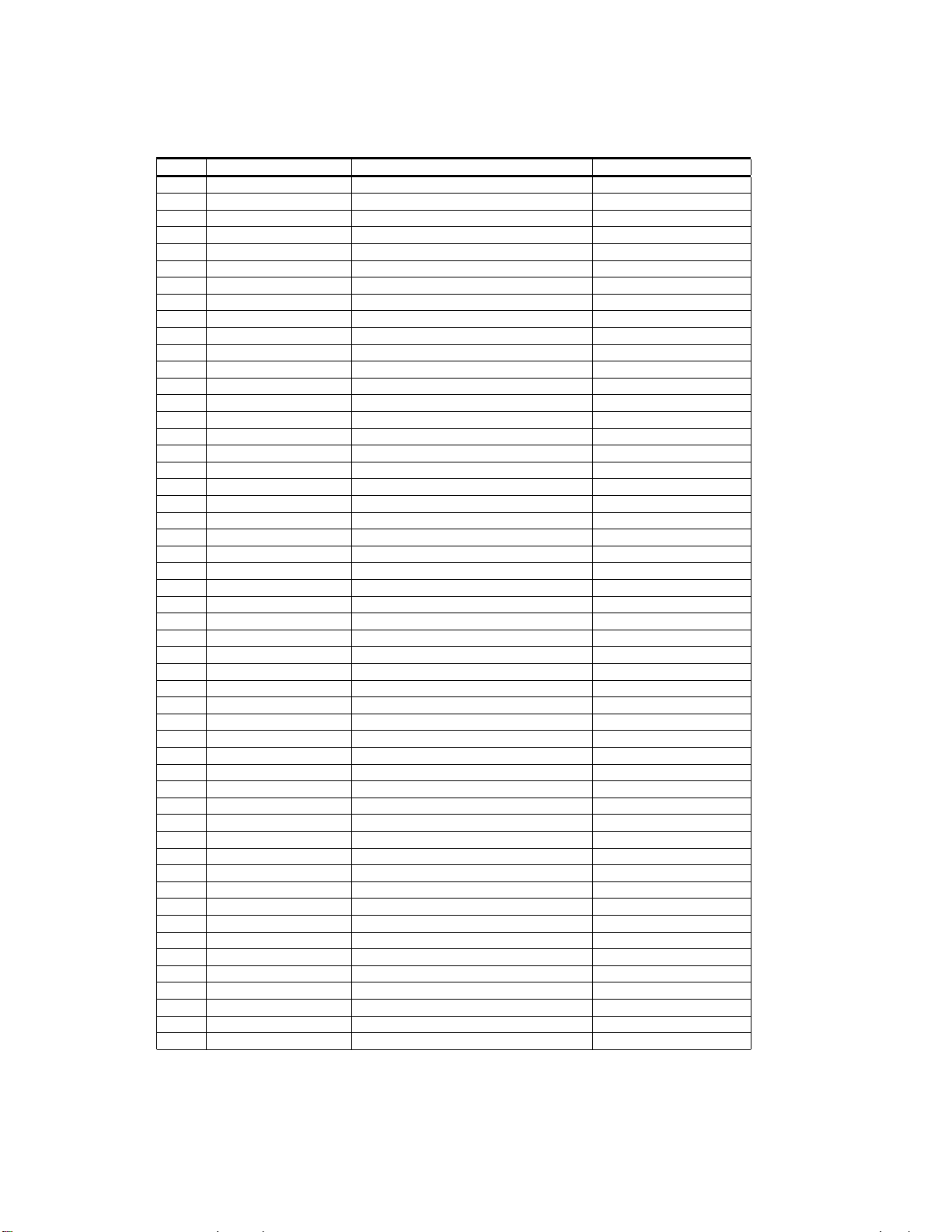

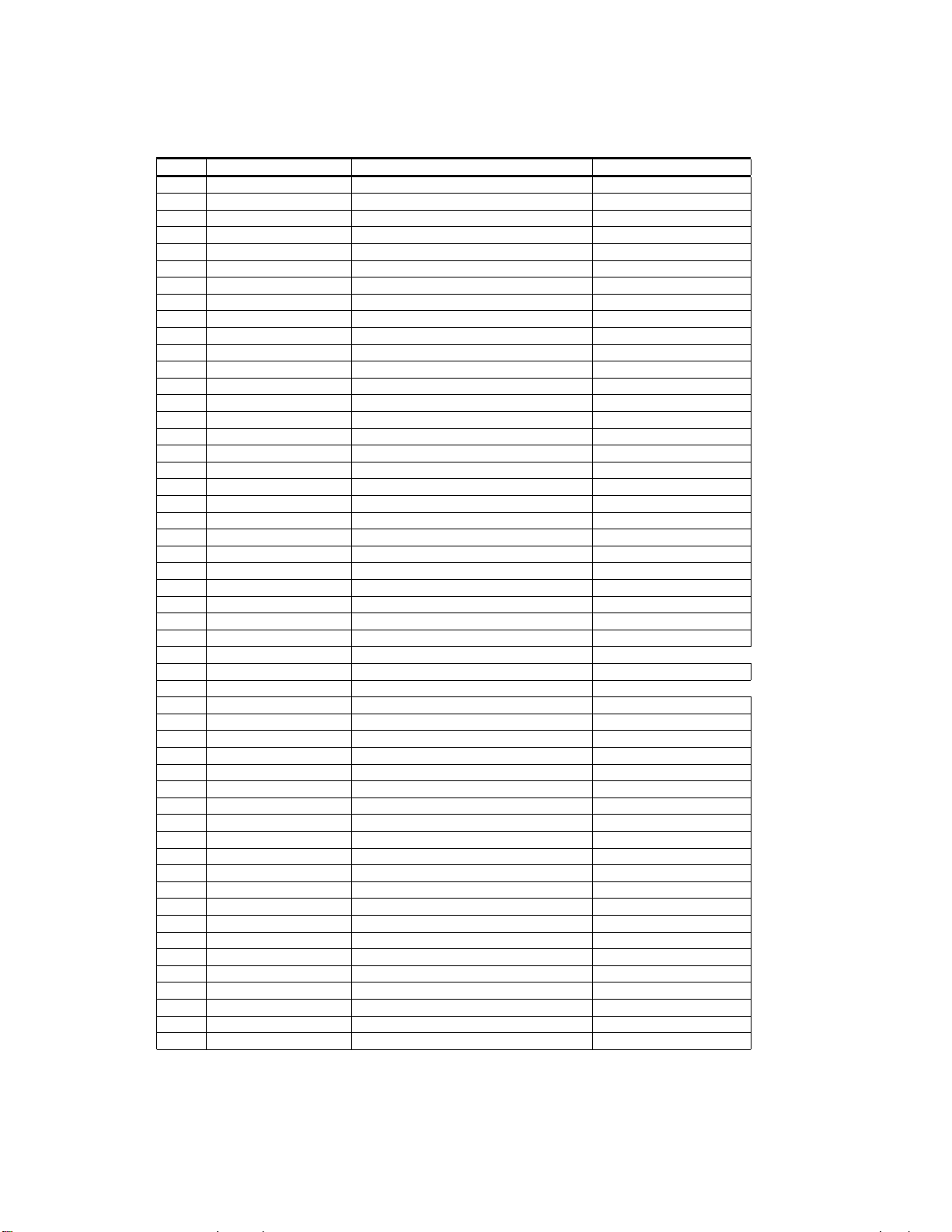

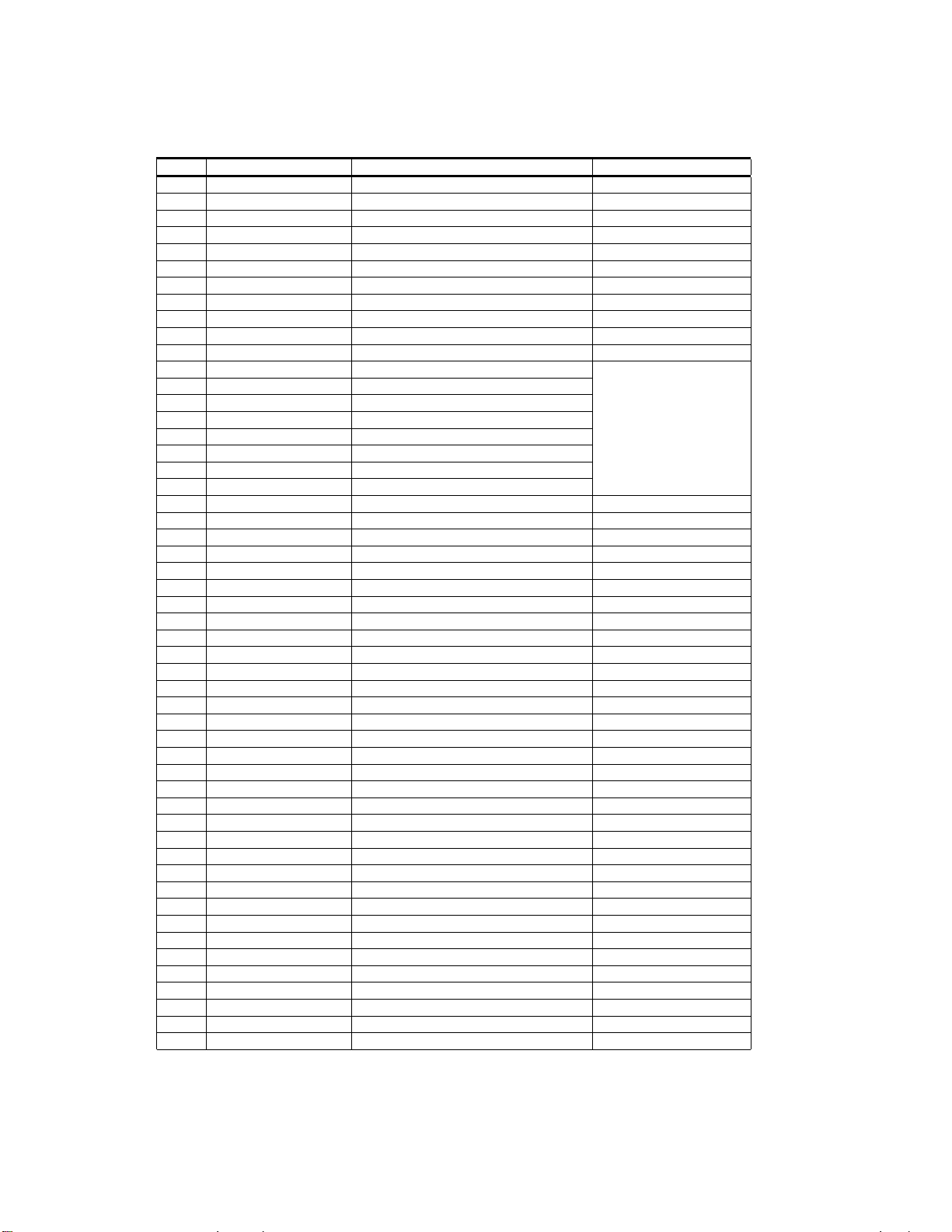

Ref# Component Description Drawing No

C172 CCUS1H102KC CAP , CHIP

C173 CCUS1H102KC CAP , CHIP

C174 CCUS1H333KC CAP , CHIP

C175 CCUS1H104KC CAP , CHIP

C176 CCUS1H102KC CAP , CHIP

C178 CCUS1H104KC CAP , CHIP

C179 CCUS1H104KC CAP , CHIP

C180 CCUS1H104KC CAP , CHIP

C181 CCUS1H104KC CAP , CHIP

C183 CCUS1H104KC CAP , CHIP

C185 CCUS1H104KC CAP , CHIP

C186 CCUS1H104KC CAP , CHIP

C187 CCUS1H104KC CAP , CHIP

C188 CCUS1H104KC CAP , CHIP

C189 CCUS1H104KC CAP , CHIP

C190 CCUS1H104KC CAP , CHIP

C191 CCUS1H104KC CAP , CHIP

C192 CCUS1H104KC CAP , CHIP

C193 CCUS1H104KC CAP , CHIP

C194 CCUS1H104KC CAP , CHIP

C195 CCUS1H104KC CAP , CHIP

C196 CCUS1H104KC CAP , CHIP

C197 CCUS1H104KC CAP , CHIP

C199 CCUS1H104KC CAP , CHIP

C200 CCUS1H104KC CAP , CHIP

C201 CCUS1H104KC CAP , CHIP

C204 CCUS1H104KC CAP , CHIP

C205 CCUS1H104KC CAP , CHIP

C207 CCUS1H272KC CAP , CHIP

C208 CCUS1H102KC CAP , CHIP

1000PF KC 1608

1000PF KC 1608

0.033PF KC 1608 SIZE

0.1UF ZF 1608

1000PF KC 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

2700PF KC 1608

1000PF KC 1608

C209 CCUS1H273KC CAP , CHIP 27000P KC 1608

C210 CCUS1H102KC CAP , CHIP

C214 CCUS1H104KC CAP , CHIP

C215 CCUS1H561JA CAP , CHIP

C217 CCUS1H273KC CAP , CHIP

C218 CCUS1H104KC CAP , CHIP

C220 CCUS1H104KC CAP , CHIP

C222 CCUS1H104KC CAP , CHIP

C225 CCUS1H104KC CAP , CHIP

C227 CCUS1H104KC CAP , CHIP

C228 CCUS1H222KC CAP , CHIP

C229 CCUS1H222KC CAP , CHIP

C230 CCUS1H222KC CAP , CHIP

C231 CCUS1H222KC CAP , CHIP

C232 CCUS1H330JA CAP , CHIP

C234 CCUS1H104KC CAP , CHIP

C235 CCUS1H104KC CAP , CHIP

C237 CCUS1H104KC CAP , CHIP

C240 CCUS1H104KC CAP , CHIP

C242 CCUS1H104KC CAP , CHIP

C244 CCUS1H104KC CAP , CHIP

C245 CCUS1H104KC CAP , CHIP

1000PF KC 1608

0.1UF ZF 1608

560PF JA 1608

0.027UF KC 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

2200PF KC 1608

2200PF KC 1608

2200PF KC 1608

2200PF KC 1608

33PF JA 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

Page 16

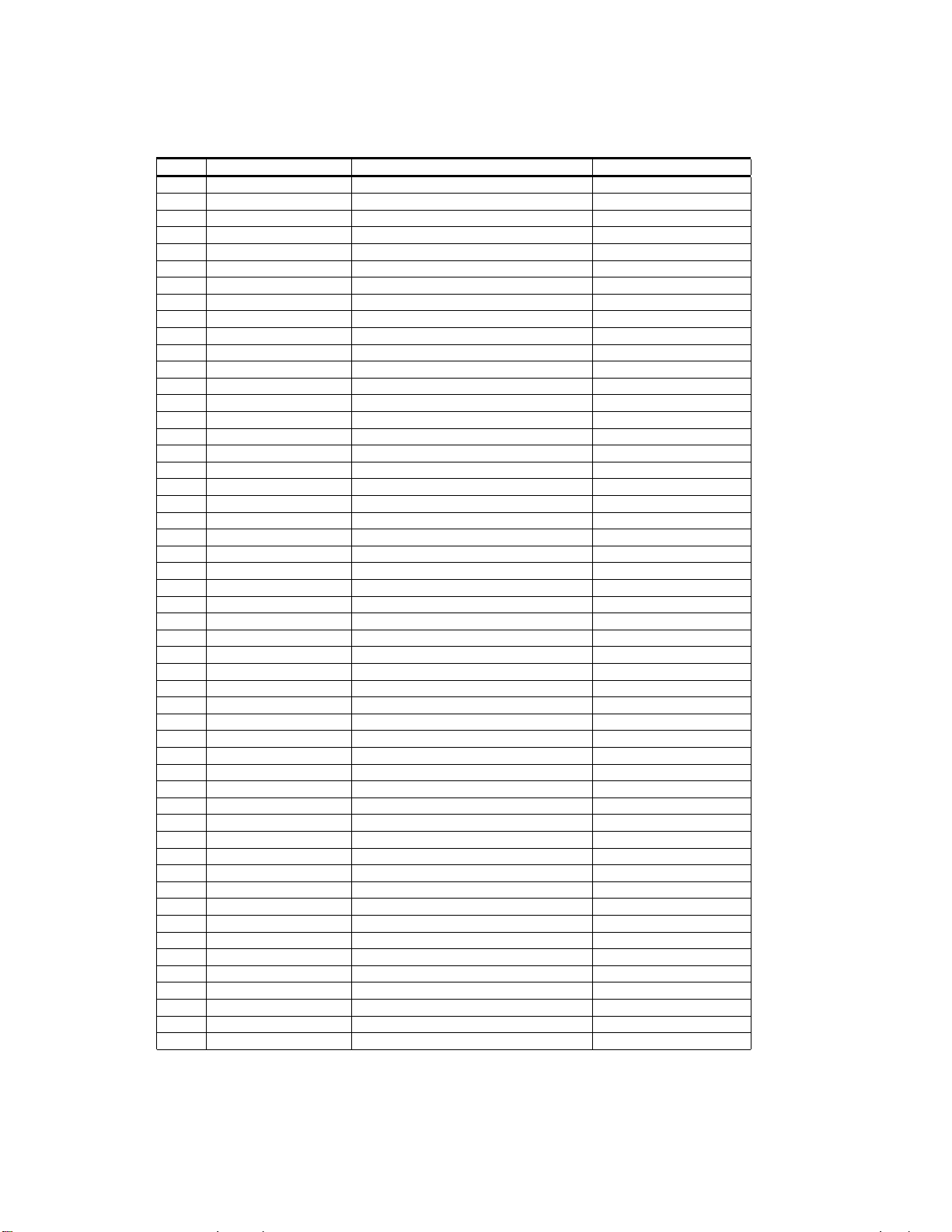

FRONT AND MAIN PCB

harman/kardon

Service manual DVD37EU

Page 16 of 117

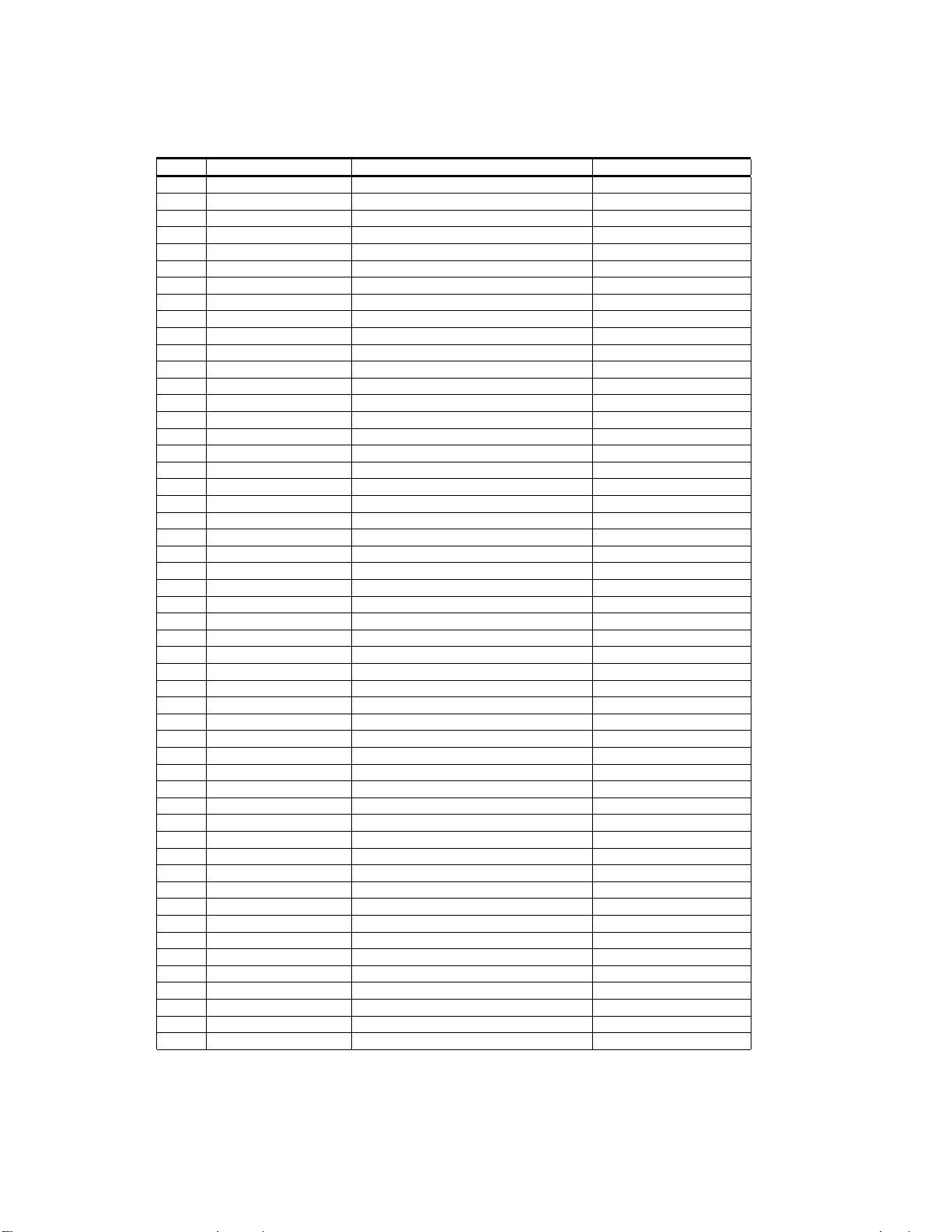

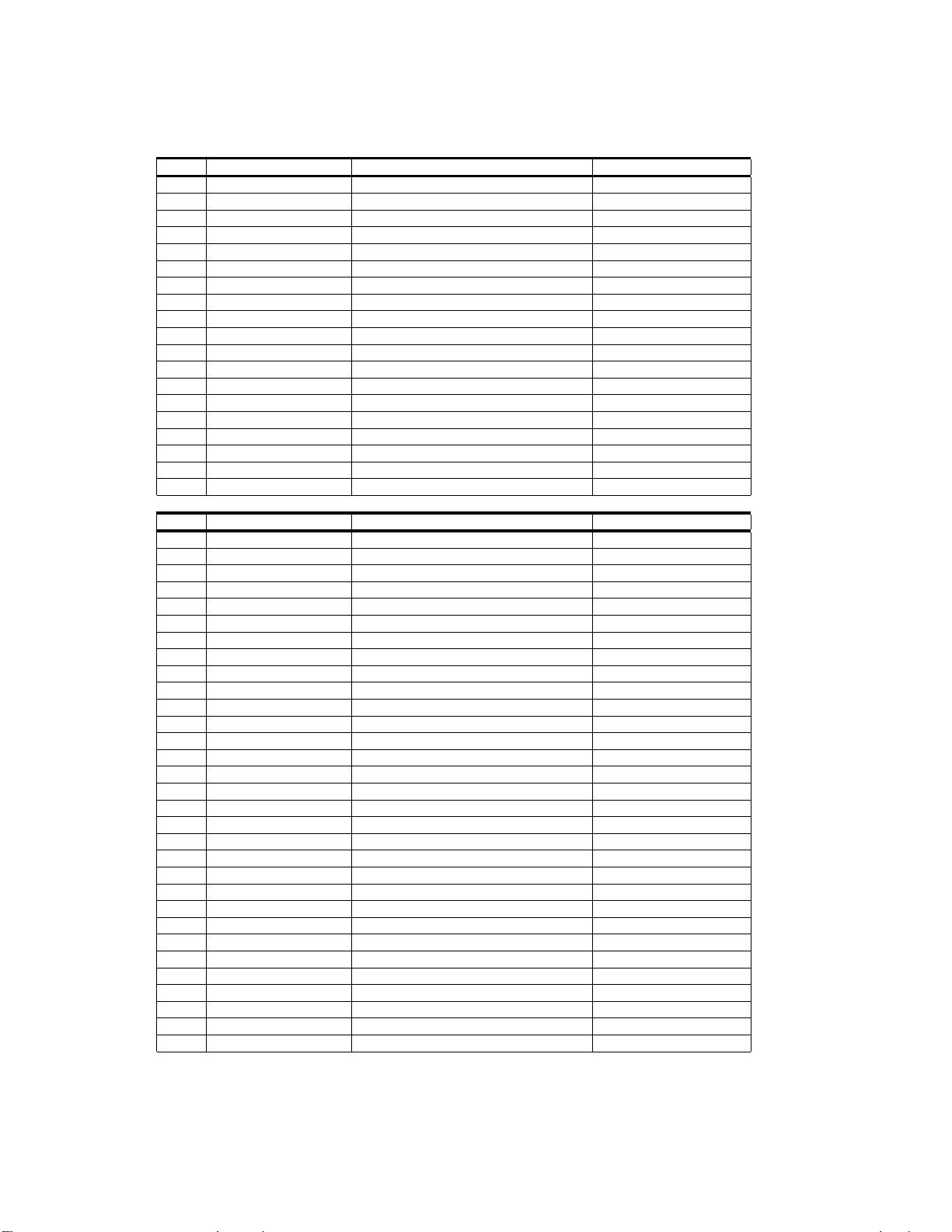

Ref# Component Description Drawing No

C247 CCUS1H104KC CAP , CHIP

C249 CCUS1H150JA CHIP, CAP 15PF/50V/1608

C250 CCUS1H150JA CHIP, CAP 15PF/50V/1608

C252 CCUS1H104KC CAP , CHIP

C253 CCUS1H104KC CAP , CHIP

C254 CCUS1H272KC CAP , CHIP

C255 CCUS1H104KC CAP , CHIP

C256 CCUS1H104KC CAP , CHIP

C257 CCUS1H104KC CAP , CHIP

C260 CCUS1H104KC CAP , CHIP

C261 CCUS1H104KC CAP , CHIP

C262 CCUS1H104KC CAP , CHIP

C263 CCUS1H104KC CAP , CHIP

C266 CCUS1H104KC CAP , CHIP

C267 CCUS1H104KC CAP , CHIP

C276 CCUS1H104KC CAP , CHIP

C277 CCUS1H104KC CAP , CHIP

C279 CCUS1H104KC CAP , CHIP

C280 CCUS1H104KC CAP , CHIP

C281 CCUS1H104KC CAP , CHIP

C282 CCUS1H104KC CAP , CHIP

C283 CCUS1H104KC CAP , CHIP

C284 CCUS1H104KC CAP , CHIP

C285 CCUS1H104KC CAP , CHIP

C286 CCUS1H104KC CAP , CHIP

C287 CCUS1H104KC CAP , CHIP

C295 CCUS1H104KC CAP , CHIP

C304 HCSHB21A220B CAP , TANTAL B2 SIZE

C306 HCSHB21A220B CAP , TANTAL B2 SIZE

C307 HCSHB21A220B CAP , TANTAL B2 SIZE

C308 HCSHB21A220B CAP , TANTAL B2 SIZE

C310 CCUS1H102KC CAP , CHIP

C311 CCUS1H560JA CAP , CHIP

C312 CCUS1H102KC CAP , CHIP

C313 CCUS1H102KC CAP , CHIP

C336 CCUS1H682KC CAP , CHIP

C337 CCUS1H223KC CAP , CHIP

C338 CCUS1H221JA CAP , CHIP

C339 CCUS1H104KC CAP , CHIP

C346 CCUS1H070DA CAP , CHIP

C380 CCUS1H150JA CHIP, CAP 15PF/50V/1608

C401 CCUS1H104KC CAP , CHIP

C402 CCUS1H104KC CAP , CHIP

C403 CCUS1H102KC CAP , CHIP

C405 CCUS1H104KC CAP , CHIP

C406 CCUS1H104KC CAP , CHIP

C408 CCUS1H104KC CAP , CHIP

C429 CCUS1H104KC CAP , CHIP

0.1UF ZF 1608

15PF JA 1608

15PF JA 1608

0.1UF ZF 1608

0.1UF ZF 1608

2700PF KC 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

22UF/50V

22UF/50V

22UF/50V

22UF/50V

1000PF KC 1608

56PF JA 1608

1000PF KC 1608

1000PF KC 1608

6800PF KB 1608

0.022UF KC 1608

220PF JA 1608

0.1UF ZF 1608

7PF D 1608

15PF JA 1608

0.1UF ZF 1608

0.1UF ZF 1608

1000PF KC 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

C430 CRJ10DJ0R0T RES , CHIP 0 ohm 1608

C431 CCUS1H221JA CAP , CHIP

C432 CCUS1H104KC CAP , CHIP

C511 CCUS1H151JA CAP , CHIP

220PF JA 1608

0.1UF ZF 1608

150PF JA 1608

Page 17

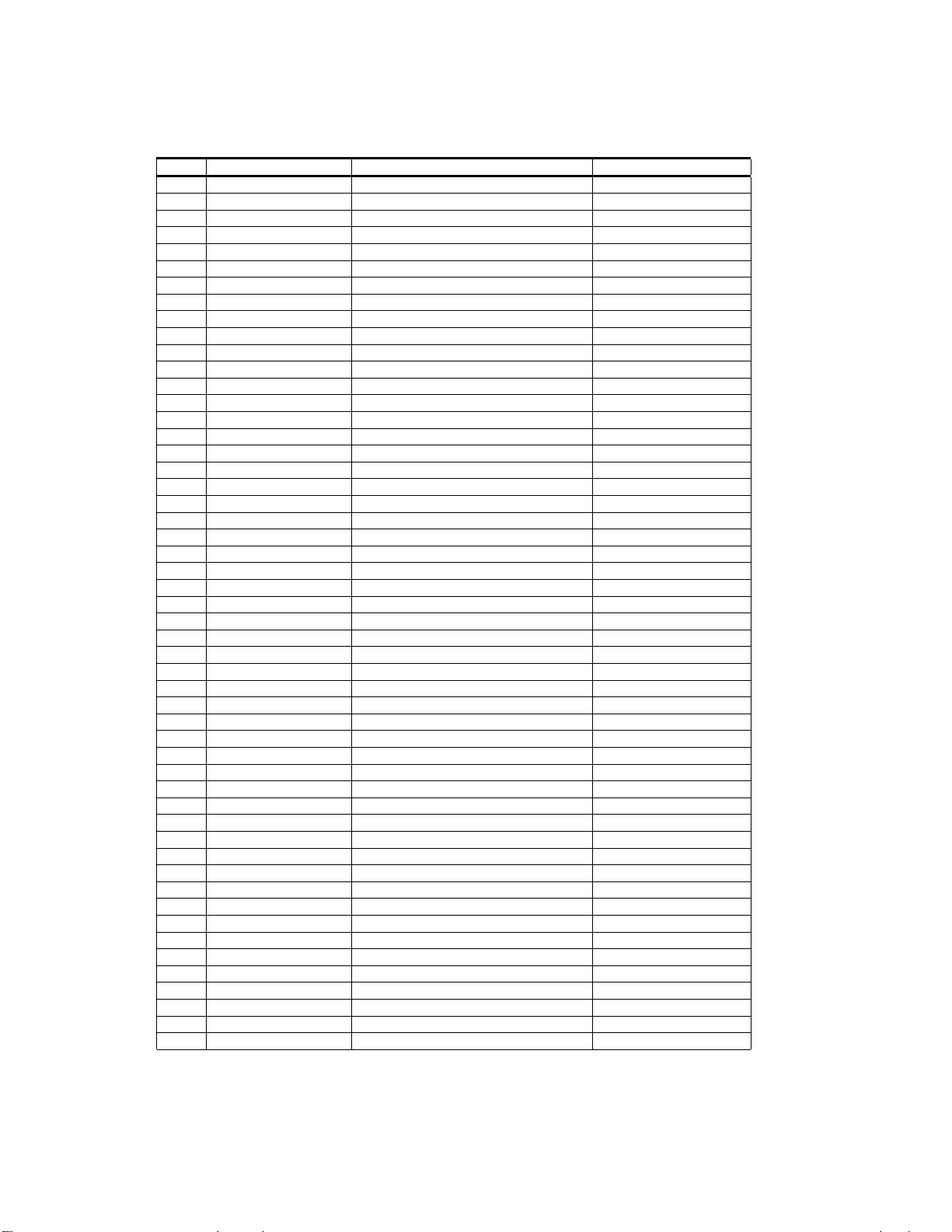

FRONT AND MAIN PCB

harman/kardon

Service manual DVD37EU

Page 17 of 117

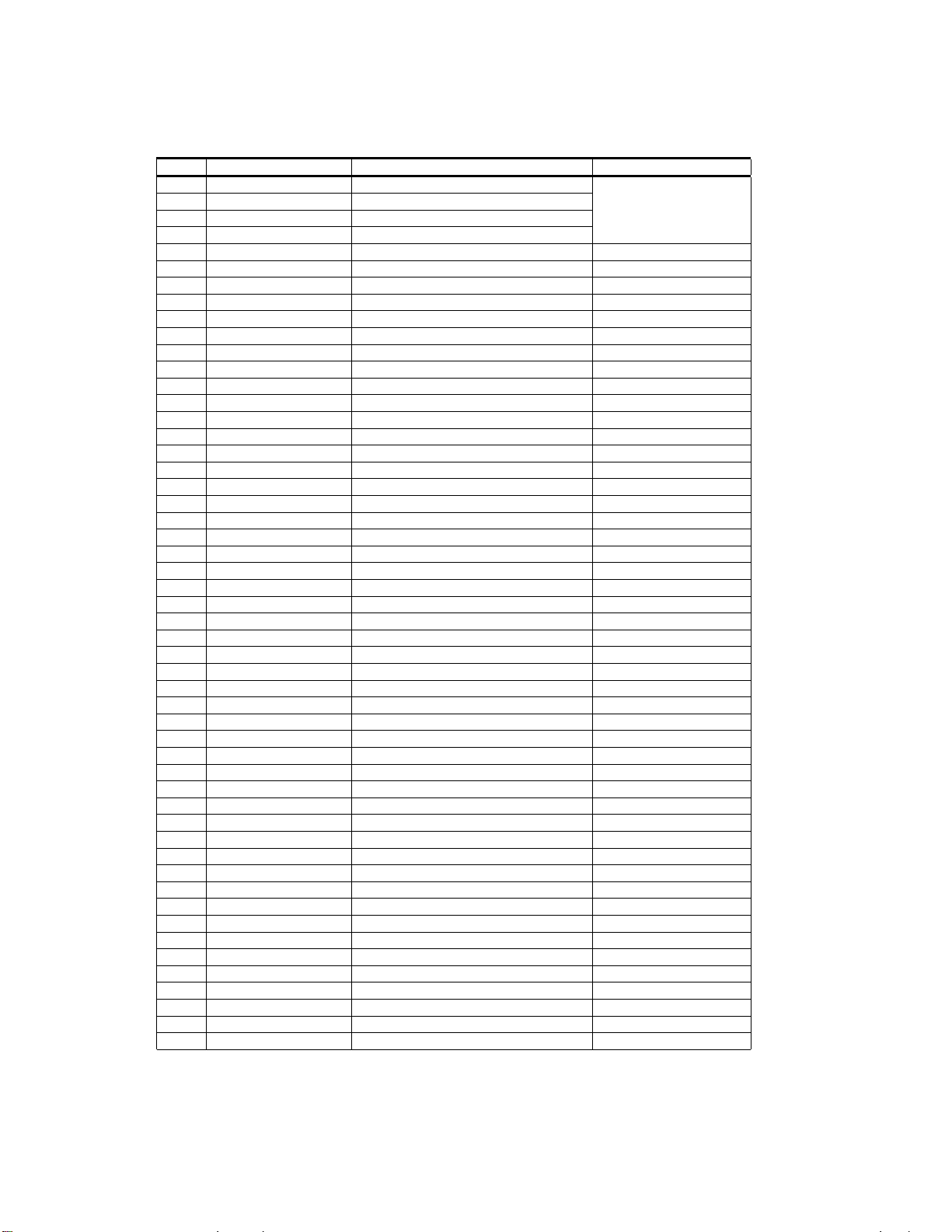

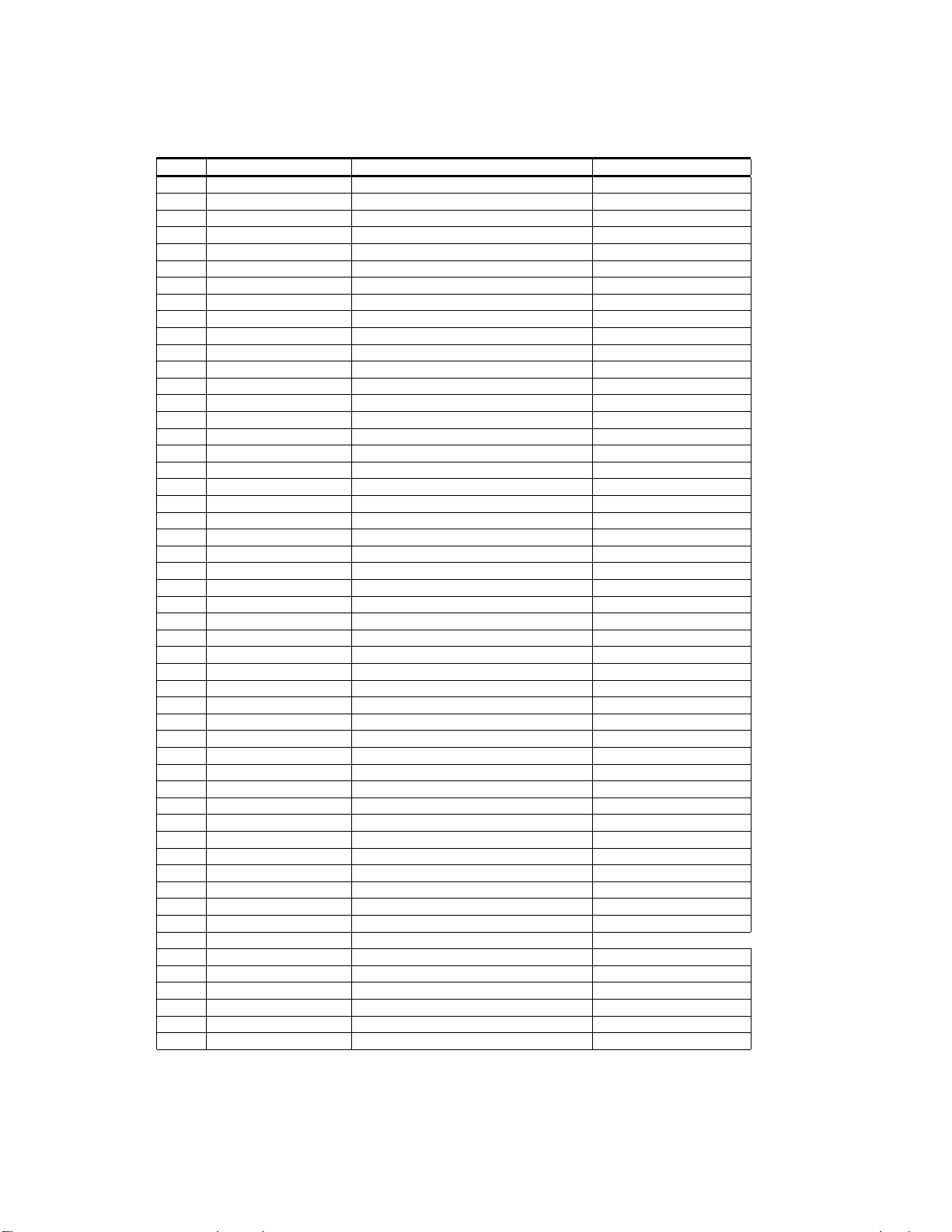

Ref# Component Description Drawing No

C531 CCUS1H104KC CAP , CHIP

C533 CCUS1H104KC CAP , CHIP

C552 CCUS1H104KC CAP , CHIP

C553 CCUS1H104KC CAP , CHIP

C555 CCUS1H150JA CHIP, CAP 15PF/50V/1608

C556 CCUS1H150JA CHIP, CAP 15PF/50V/1608

C578 CCUS1H104KC CAP , CHIP

C580 CCUS1H104KC CAP , CHIP

C581 CCUS1H104KC CAP , CHIP

C584 CCUS1H104KC CAP , CHIP

C585 CCUS1H104KC CAP , CHIP

C593 CCUS1H104KC CAP , CHIP

C594 CCUS1H104KC CAP , CHIP

C615 CCUS1H391JA CAP , CHIP

C617 CCUS1H104KC CAP , CHIP

C620 CCUS1H104KC CAP , CHIP

C630 CCUS1H104KC CAP , CHIP

C631 CCUS1H104KC CAP , CHIP

C636 CCUS1H391JA CAP , CHIP

C638 CCUS1H391JA CAP , CHIP

C639 CCUS1H391JA CAP , CHIP

C641 CCUS1H391JA CAP , CHIP

C644 CCUS1H391JA CAP , CHIP

C646 CCUS1H391JA CAP , CHIP

C650 CCUS1H391JA CAP , CHIP

C657 CCUS1H391JA CAP , CHIP

C659 CCUS1H391JA CAP , CHIP

C660 CCUS1H391JA CAP , CHIP

C662 CCUS1H391JA CAP , CHIP

C664 CCUS1H104KC CAP , CHIP

C665 CCUS1H104KC CAP , CHIP

C668 CCUS1H104KC CAP , CHIP

C671 CCUS1H104KC CAP , CHIP

C672 CCUS1H104KC CAP , CHIP

C674 CCUS1H104KC CAP , CHIP

C677 CCUS1H104KC CAP , CHIP

C678 CCUS1H104KC CAP , CHIP

C679 CCUS1H104KC CAP , CHIP

C809 CCUS1H104KC CAP , CHIP

C810 CCUS1H560JA CAP , CHIP

C812 CCUS1H101JA CAP , CHIP

C817 CCUS1H104KC CAP , CHIP

C819 CCUS1H101JA CAP , CHIP

C820 CCUS1H101JA CAP , CHIP

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

15PF JA 1608

15PF JA 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

390PF JA 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

390PF JA 1608

390PF JA 1608

390PF JA 1608

390PF JA 1608

390PF JA 1608

390PF JA 1608

390PF JA 1608

390PF JA 1608

390PF JA 1608

390PF JA 1608

390PF JA 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

0.1UF ZF 1608

56PF JA 1608

100PF JA 1608

0.1UF ZF 1608

100PF JA 1608

100PF JA 1608

C822 CCUS1H560JA CAP , CHIP 56PF JA 1608

C823 CCUS1H104KC CAP , CHIP

0.1UF ZF 1608

C828 CCUS1H220JA CAP , CHIP 22PF JA 1608

C830 CCUS1H150JA CHIP, CAP 15PF/50V/1608

C831 CCUS1H150JA CHIP, CAP 15PF/50V/1608

C834 CCUS1H104KC CAP , CHIP

15PF JA 1608

15PF JA 1608

0.1UF ZF 1608

D101 HVDRLS4148SR DIODE, SWITCHING, SMD TYPE RLS4148 TE-11

D102 HVDRLS4148SR DIODE, SWITCHING, SMD TYPE RLS4148 TE-11

Page 18

E

FRONT AND MAIN PCB

harman/kardon

Service manual DVD37EU

Page 18 of 117

Ref# Component Description Drawing No

D501 HVDRLS4148SR DIODE, SWITCHING, SMD TYPE RLS4148 TE-11

D502 HVDRLS4148SR DIODE, SWITCHING, SMD TYPE RLS4148 TE-11

D511 HVDRLS4148SR DIODE, SWITCHING, SMD TYPE RLS4148 TE-11

D601 HVDRLS4148SR DIODE, SWITCHING, SMD TYPE RLS4148 TE-11

D602 HVDRLS4148SR DIODE, SWITCHING, SMD TYPE RLS4148 TE-11

D603 HVDRLS4148SR DIODE, SWITCHING, SMD TYPE RLS4148 TE-11

IC10 HVIZR36778 IC,MPEG (ZORAN)

ZR36778

IC11 HVILM1117S-3V3 I.C , REGULATOR (3.3V) 1117S-3.3V

IC12 HVILM1117S-1V8 I.C , REGULATOR (1.8V) LM1117-1V8

IC13 HVILM1117S-3V3 I.C , REGULATOR (3.3V) 1117S-3.3V

IC14 HVILM1117S-1V8 I.C , REGULATOR (1.8V) LM1117-1V8

IC15 HVIAT24C08N10SC I.C AT24C08N10SC2.7

IC16 HVISAA7893HLC2 IC,DSD DECODER (Philips) SAA7893HL/C2 (PB FR

IC17 HVI74VHC04MX I.C , INVERTER 74VHC04M

IC18 HVIM12L64164A7T IC, 64M SDRAM (4X16)

IC19 HVIZR36721 IC,HDMI TRANSMITTER(ZORAN)

IC20 HVITL3472IDR IC,OP AMP 8-SOIC (TI)

M12L64164A7T

ZR36721

TL3472

IC21 HVIM29W160ET70N IC,16M FLASH (ST) M29W160ET-70N6

IC22 HVIM12L64164A7T IC, 64M SDRAM (4X16)

M12L64164A7T

IC23 HVIAM5888SLF I. C , Motor Driver(AMtek,Pb f AM5888S L/F

IC24 HVIZR36707 IC,RF (ZORAN)

ZR36707

IC40 HVICS4382-KQ I.C , DAC CS4382-KQ

IC41 BVIBH7862FS IC , 6CH VIDEO DRIVER ROHM (BH7862FS)

IC42 HVIBA7660FS IC , R.G.B DRIVER BA7660FS

IC43 HVI74LVC157ADBR I.C , MULTIPLEXER SN74LVC157A

IC44 HVI74LVC157ADBR I.C , MULTIPLEXER SN74LVC157A

IC45 HVIST72F324K2 IC,FLASH (ST)

ST72F324K2

IC47 HVITC74HCT7007F I.C TC74HC7007AFEL

IC51 HVILM1117S-5.0 IC REGULATOR/SOT-223

LM1117-1V8 (1.8V)

IC52 HVINJM2068MDTE1 I.C , OP AMP NJM2068MD-TE1

IC53 HVILM1117S-3V3 I.C , REGULATOR (3.3V) 1117S-3.3V

IC54 HVINJM2068MDTE1 I.C , OP AMP NJM2068MD-TE1

IC55 HVINJM2068MDTE1 I.C , OP AMP NJM2068MD-TE1

IC56 HVILM1117S-5.0 IC REGULATOR/SOT-223

LM1117-5V0 (5V)

IC57 HVTHN1K05FU MOS FET HN1K05FU

JK07 HJJ9H003Z JACK,HDMI (JALCO) YKF45-7009

L101 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L102 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L103 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L104 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L105 HLQ06E100KRZ INDUCTOR , CHIP

L106 HLQ06E100KRZ INDUCTOR , CHIP

L107 HLQ06E100KRZ INDUCTOR , CHIP

10UH 3225 SIZE

10UH 3225 SIZE

10UH 3225 SIZE

L109 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L110 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L111 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L112 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L113 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L114 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L115 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L116 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L117 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

Page 19

E

FRONT AND MAIN PCB

harman/kardon

Service manual DVD37EU

Page 19 of 117

Ref# Component Description Drawing No

L118 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L119 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L120 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L121 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L122 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L123 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L124 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L125 HLZ9R006Z BEAD , CHIP

L126 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L127 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L128 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L217 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L518 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L519 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L520 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L521 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L522 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L601 BLZ9R004Z BEAD CHIP 90 OHM (2012 SIZE) ACM2012H-900

L602 BLZ9R004Z BEAD CHIP 90 OHM (2012 SIZE) ACM2012H-900

L603 BLZ9R004Z BEAD CHIP 90 OHM (2012 SIZE) ACM2012H-900

L604 BLZ9R004Z BEAD CHIP 90 OHM (2012 SIZE) ACM2012H-900

L610 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L611 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L612 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L613 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L614 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L615 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L616 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L617 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L696 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L801 HLQ08ER68KRZ CHIP FERRITE INDUCTOR 2012-R68UH

L802 HLQ08E1R8KRZ CHIP , COIL (1.8UH) 1.8UH 2012 SIZE

L803 HLQ08E1R8KRZ CHIP , COIL (1.8UH) 1.8UH 2012 SIZE

L804 HLQ09E8R2KRZ CHIP , COIL 8.2UH 2012 SIZE

L805 HLQ08ER68KRZ CHIP FERRITE INDUCTOR 2012-R68UH

L806 HLQ08ER39KRZ CHIP FERRITE INDUCTOR 2012-R39UH

L807 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L808 HLZ9R001Z FB, 2012(0805)600E, 1.5A,POWER 600E, 1.5A

L809 HLQ09E8R2KRZ CHIP , COIL

8.2UH

L884 HLQ08E1R8KRZ CHIP , COIL (1.8UH) 1.8UH 2012 SIZE

Q105 HVTKTA1664YP tr

Q106 HVTKTA1664YP tr

KTA1664

KTA1664

Q108 HVT2N3904SP TR, CHIP (KEC) 2N3904S-RTK/PS

Q109 HVT2N3904SP TR, CHIP (KEC) 2N3904S-RTK/PS

Q110 HVT2N3904SP TR, CHIP (KEC) 2N3904S-RTK/PS

Q307 HVT2SA1955B T.R, TE85L,F, SSM Type, hFE=B TE85L,F SSM TYPE HF

Q308 HVT2N3904SP TR, CHIP (KEC) 2N3904S-RTK/PS

Q315 HVTKRC107S TR , CHIP

KRC107S

Q316 HVTKTA1504SYRTK T.R , CHIP KTA1504S Y RTK

Q404 HVT2N3904SP TR, CHIP (KEC) 2N3904S-RTK/PS

Q407 HVTKRC107S TR , CHIP

KRC107S

Q408 HVTKRA107ST T.R , CHIP KRA107S

Page 20

FRONT AND MAIN PCB

harman/kardon

Service manual DVD37EU

Page 20 of 117

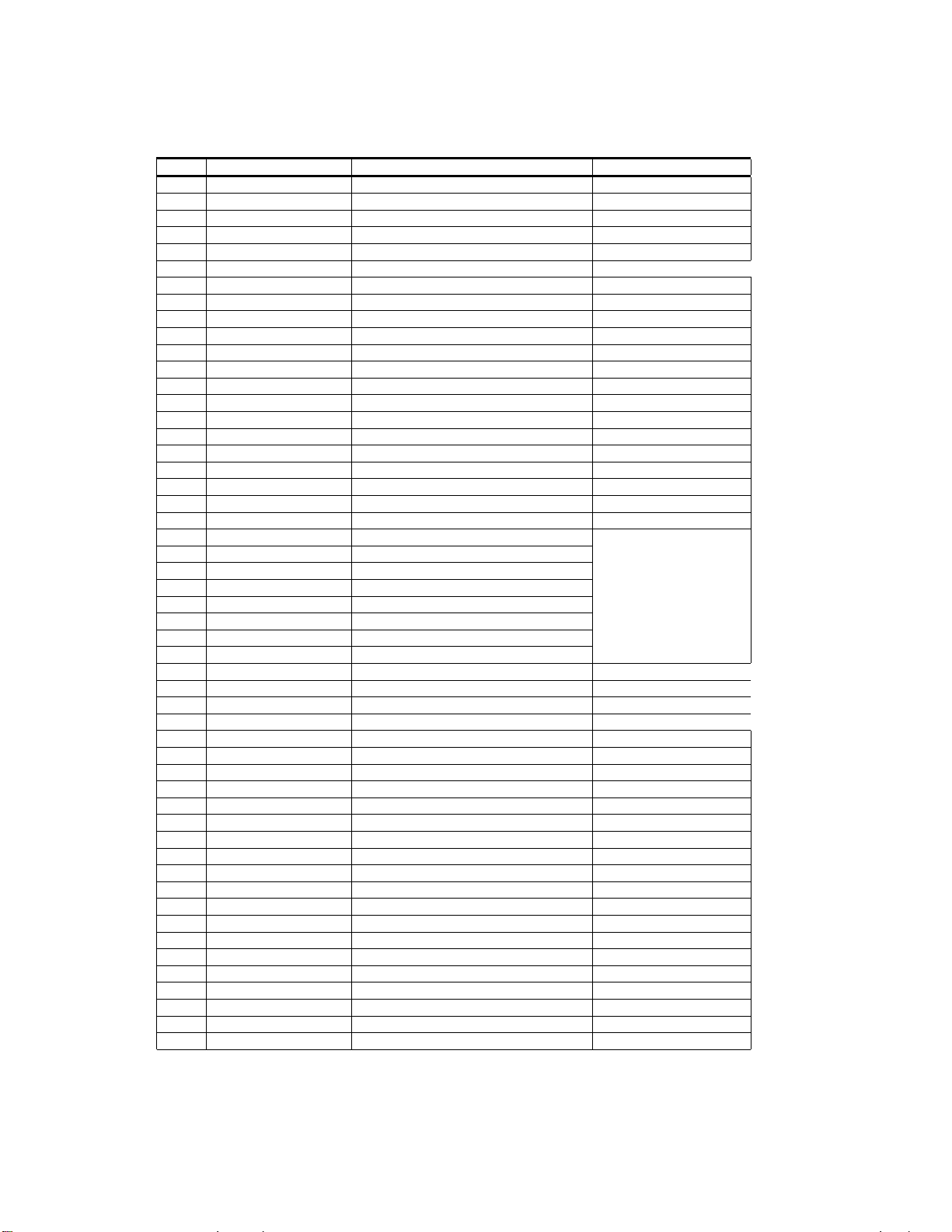

Ref# Component Description Drawing No

Q501 HVTKTA1504SYRTK T.R , CHIP KTA1504S Y RTK

Q502 HVTKTC3875SYRTK T.R , CHIP KTC3875S Y RTK

Q604 HVTKRA107ST T.R , CHIP KRA107S

Q606 HVTKRA107ST T.R , CHIP KRA107S

Q607 HVTKRA107ST T.R , CHIP KRA107S

Q608 HVTKRC107S TR , CHIP

KRC107S

Q609 HVTKTD1304T T.R , CHIP (MUTE) KTD1304

Q610 HVTKTD1304T T.R , CHIP (MUTE) KTD1304

Q611 HVTKTD1304T T.R , CHIP (MUTE) KTD1304

Q612 HVTKTD1304T T.R , CHIP (MUTE) KTD1304

Q613 HVTKTD1304T T.R , CHIP (MUTE) KTD1304

Q614 HVTKTD1304T T.R , CHIP (MUTE) KTD1304

Q615 HVTKRA107ST T.R , CHIP KRA107S

Q616 HVTKRC107S TR , CHIP

KRC107S

Q617 HVTKTD1304T T.R , CHIP (MUTE) KTD1304

Q618 HVTKTD1304T T.R , CHIP (MUTE) KTD1304

Q619 HVTKTD1304T T.R , CHIP (MUTE) KTD1304

Q620 HVTKTD1304T T.R , CHIP (MUTE) KTD1304

Q621 HVTKTD1304T T.R , CHIP (MUTE) KTD1304

Q622 HVTKTD1304T T.R , CHIP (MUTE) KTD1304

Q801 HVTKRC107S TR , CHIP KRC107S

Q802 HVTKRC107S TR , CHIP KRC107S

Q803 HVTKTA1504SYRTK T.R , CHIP KTA1504S Y RTK

Q804 HVTKTA1504SYRTK T.R , CHIP KTA1504S Y RTK

Q805 HVTKTD1304T T.R , CHIP (MUTE) KTD1304

Q806 HVTKRA107ST T.R , CHIP KRA107S

Q821 HVTKTA1504SYRTK T.R , CHIP KTA1504S Y RTK

R100 CRJ10DJ472T RES , CHIP 4.7K OHM 1608 SIZE

R101 CRJ10DF4700T RES, CHIP 470 OHM/1608/1%

470 OHM(1%) 1608 SIZ

R102 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

R103 CRJ10DF4300T RES

430 OHM(1%) 1608 SIZ

R104 CRJ10DF3920T RES. CHIP (392R 1%) 3.9K OHM 1608 SIZE

R105 CRJ10DJ0R0T RES , CHIP

0 OHM 1608 SIZE

R106 CRJ104DJ101T RES, ARRAY, 100R (1608) 100 OHM 1608 SIZE

R107 CRJ10DJ330T RES , CHIP 33 OHM 1608 SIZE

R108 CRJ10DJ101T RES , CHIP 100 OHM 1608 SIZE

R109 CRJ10DJ472T RES , CHIP

100 OHM 1608 SIZE

R110 CRJ10DJ332T RES , CHIP 3.3K OHM 1608 SIZE

R111 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4

R112 CRJ10DJ202T RES , CHIP

R113 CRJ10DJ202T RES , CHIP

R114 CRJ10DJ121T RES , CHIP

R115 CRJ10DJ0R0T RES , CHIP

R116 CRJ10DJ121T RES , CHIP

R117 CRJ10DJ121T RES , CHIP

2K OHM 1608 SIZE

2K OHM 1608 SIZE

120 OHM 1608 SIZE

0 OHM 1608 SIZE

120 OHM 1608 SIZE

120 OHM 1608 SIZE

R118 CRJ10DJ103T RES , CHIP 10K OHM1608 SIZE

R119 CRJ10DJ330T RES , CHIP 33 OHM 1608 SIZE

R120 CRJ10DJ123T RES , CHIP 12K OHM 1608 SIZE

R121 CRJ10DJ221T RES , CHIP 220 OHM 1608 SIZE

R122 CRJ10DJ221T RES , CHIP 220 OHM 1608 SIZE

R123 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

R124 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

Page 21

FRONT AND MAIN PCB

harman/kardon

Service manual DVD37EU

Page 21 of 117

Ref# Component Description Drawing No

R125 CRJ10DJ113T RES , CHIP 11K OHM 1608 SIZE

R126 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

R127 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

R128 CRJ10DJ121T RES , CHIP 120 OHM 1608 SIZE

R129 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4

R130 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4

R131 CRJ10DJ330T RES , CHIP 33 OHM 1608 SIZE

R132 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

R133 CRJ10DF3920T RES. CHIP (392R 1%) 3.9K OHM 1608 SIZE

R134 CRJ10DJ103T RES , CHIP 10K OHM 1608 SIZE

R135 CRJ10DJ100T RES , CHIP 10 OHM 1608 SIZE

R136 CRJ10DJ221T RES , CHIP 220 OHM 1608 SIZE

R137 CRJ10DJ221T RES , CHIP 220 OHM 1608 SIZE

R138 CRJ10DJ100T RES , CHIP 10 OHM 1608 SIZE

R139 CRJ10DJ472T RES , CHIP 4.7K OHM 1608 SIZE

R140 CRJ10DJ133T RES , CHIP 13K OHM 1608 SIZE

R141 CRJ10DJ474T RES , CHIP 470K OHM 1608 SIZE

R142 CRJ10DJ474T RES , CHIP 470K OHM 1608 SIZE

R143 CRJ10DJ330T RES , CHIP 33 OHM 1608 SIZE

R144 CRJ10DJ330T RES , CHIP 33 OHM 1608 SIZE

R145 CRJ10DJ750T RES , CHIP 75 OHM 1608 SIZE

R146 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

R147 CRJ10DJ104T RES , CHIP 100K OHM 1608 SIZE

R148 CRJ10DJ750T RES , CHIP 57 OHM 1608 SIZE

R149 CRJ104DJ470T RES , 4ARRAY (1608*4)

R150 CRJ104DJ470T RES , 4ARRAY (1608*4)

R151 CRJ10DJ0R0T RES , CHIP

R152 CRJ10DJ0R0T RES , CHIP

R153 CRJ10DJ0R0T RES , CHIP

R154 CRJ10DJ0R0T RES , CHIP

47 OHM/1608X4

47 OHM/1608X4

0 OHM 1608 SIZE

0 OHM 1608 SIZE

0 OHM 1608 SIZE

0 OHM 1608 SIZE

R155 CRJ10DJ101T RES , CHIP 100 OHM 1608 SIZE

R156 CRJ10DJ101T RES , CHIP 100 OHM 1608 SIZE

R157 CRJ10DJ0R0T RES , CHIP 1608 SIZE

R158 CRJ104DJ101T RES, ARRAY, 100R (1608) 100R (1608)

R159 CRJ10DJ472T RES , CHIP 1608 SIZE

R160 CRJ10DJ330T RES , CHIP 1608 SIZE

R161 CRJ10DJ0R0T RES , CHIP 1608 SIZE

R162 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4

R163 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4

R164 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4

R165 CRJ10DJ330T RES , CHIP 1608 SIZE

R166 CRJ10DJ330T RES , CHIP 1608 SIZE

R167 CRJ10DJ330T RES , CHIP 1608 SIZE

R168 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4

R169 CRJ10DJ750T RES , CHIP 1608 SIZE

R170 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4

R171 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4

R172 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4

R173 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4

R174 CRJ10DJ472T RES , CHIP

4.7K OHM 1608 SIZE

R175 CRJ10DJ912T RES , CHIP 9.1K OHM/1608

R176 CRJ10DJ132T RES , CHIP

1.3K OHM 1608 SIZE

Page 22

Z

Z

Z

Z

FRONT AND MAIN PCB

harman/kardon

Service manual DVD37EU

Page 22 of 117

Ref# Component Description Drawing No

R177 CRJ10DJ132T RES , CHIP

R178 CRJ10DJ272T RES , CHIP

R180 CRJ10DJ0R0T RES , CHIP

R181 CRJ10DJ0R0T RES , CHIP

R182 CRJ10DJ0R0T RES , CHIP

R183 CRJ10DF1202T RES , CHIP 1%

R184 CRJ10DJ471T RES , CHIP

R185 CRJ10DJ332T RES , CHIP

R186 CRJ10DJ332T RES , CHIP

R187 CRJ10DJ332T RES , CHIP

R188 CRJ10DJ113T RES , CHIP

R189 CRJ10DJ105T RES , CHIP

R190 CRJ10DJ223T RES , CHIP

R191 CRJ10DJ223T RES , CHIP

R192 CRJ10DJ103T RES , CHIP

R193 CRJ10DJ332T RES , CHIP

R194 CRJ10DJ330T RES , CHIP

R195 CRJ10DJ101T RES , CHIP

R196 CRJ10DJ472T RES , CHIP

R197 CRJ10DJ753T RES , CHIP

1.3K OHM 1608 SIZE

2.7K OHM 1608 SIZE

0 OHM 1608 SIZE

0 OHM 1608 SIZE

0 OHM 1608 SIZE

1.2K OHM(1%) 1608 SI

470 OHM 1608 SIZE

3.3K OHM 1608 SIZE

3.3K OHM 1608 SIZE

3.3K OHM 1608 SIZE

11K OHM 1608 SIZE

1M OHM 1608 SIZE

22K OHM 1608 SIZE

22K OHM 1608 SIZE

10K OHM 1608 SIZE

3.3K OHM 1608 SIZE

33 OHM 1608 SIZE

100 OHM 1608 SIZE

4.7K OHM 1608 SIZE

75K OHM 1608 SIZE

R198 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

R199 CRJ10DJ330T RES , CHIP 33 OHM 1608 SIZE

R200 CRJ10DJ330T RES , CHIP 33 OHM 1608 SIZE

R201 CRJ10DJ472T RES , CHIP 4.7K OHM 1608 SIZE

R202 CRJ10DJ622T RES , CHIP 6.2K OHM 1608 SIZE

R203 CRJ10DJ562T RES , CHIP 5.6K OHM 1608 SIZE

R204 CRJ10DJ562T RES , CHIP 5.6K OHM 1608 SIZE

R205 CRJ10DJ562T RES , CHIP 5.6K OHM 1608 SIZE

R206 CRJ10DJ103T RES , CHIP 10K OHM 1608 SIZE

R207 CRJ10DF4700T RES, CHIP 470 OHM/1608/1%

R209 CRJ10DF1002T RES , CHIP 1%

R210 CRJ10DF1002T RES , CHIP 1%

R211 CRJ10DF1002T RES , CHIP 1%

470 OHM(1%) 1608 SIZ

10K OHM(1%) 1608 SI

10K OHM(1%) 1608 SI

10K OHM(1%) 1608 SI

R212 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4

R213 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4

R214 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4

R215 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4

R216 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4

R217 CRJ10DJ330T RES , CHIP 1608 SIZE

R218 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4

R219 CRJ10DJ273T RES , CHIP 27K OHM 1608 SIZE

R220 CRJ10DJ562T RES , CHIP

R221 CRJ10DJ562T RES , CHIP

R222 CRJ10DJ562T RES , CHIP

5.6K OHM 1608 SIZE

5.6K OHM 1608 SIZE

5.6K OHM 1608 SIZE

R223 CRJ10DJ103T RES , CHIP 10K OHM 1608 SIZE

R224 CRJ10DJ472T RES , CHIP 4.7K OHM 1608 SIZE

R225 CRJ10DJ330T RES , CHIP 33 OHM 1608 SIZE

R226 CRJ10DJ330T RES , CHIP 33 OHM 1608 SIZE

R227 CRJ10DJ330T RES , CHIP 33 OHM 1608 SIZE

R228 CRJ10DJ330T RES , CHIP 33 OHM 1608 SIZE

R230 CRJ10DJ472T RES , CHIP 4.7K OHM 1608 SIZE

R241 CRJ10DF75R0T RES, CHIP 1% 75 OHM 75 OHM, 1%

Page 23

FRONT AND MAIN PCB

harman/kardon

Service manual DVD37EU

Page 23 of 117

Ref# Component Description Drawing No

R243 CRJ10DF75R0T RES, CHIP 1% 75 OHM 75 OHM, 1%

R244 CRJ10DF75R0T RES, CHIP 1% 75 OHM 75 OHM, 1%

R265 CRJ10DJ472T RES , CHIP

R284 CRJ10DJ472T RES , CHIP

R285 CRJ10DJ472T RES , CHIP

R287 CRJ10DJ113T RES , CHIP

R297 CRJ10DJ0R0T RES , CHIP

R298 CRJ10DJ103T RES , CHIP

R299 CRJ10DJ0R0T RES , CHIP

R301 CRJ10DJ0R0T RES , CHIP

R302 CRJ10DJ0R0T RES , CHIP

R303 CRJ10DJ0R0T RES , CHIP

R305 CRJ10DJ472T RES , CHIP

R306 CRJ10DJ0R0T RES , CHIP

R307 CRJ10DJ272T RES , CHIP

R308 CRJ10DJ102T RES , CHIP

R309 CRJ10DJ102T RES , CHIP

R377 CRJ10DJ221T RES , CHIP

R404 CRJ10DJ333T RES , CHIP

R409 CRJ10DJ100T RES , CHIP

R410 CRJ10DJ103T RES , CHIP

R412 CRJ10DJ681T RES , CHIP

R413 CRJ10DJ821T RES , CHIP

R414 CRJ10DJ122T RES , CHIP

R415 CRJ10DJ152T RES , CHIP

R416 CRJ10DJ222T RES , CHIP

R417 CRJ10DJ332T RES , CHIP

R418 CRJ10DJ472T RES , CHIP

R419 CRJ10DJ221T RES , CHIP

R420 CRJ10DJ750T RES , CHIP

R421 CRJ10DJ680T RES , CHIP

R422 CRJ10DJ121T RES , CHIP

R423 CRJ10DJ820T RES , CHIP

R424 CRJ10DJ4R7T RES , CHIP

R425 CRJ10DJ332T RES , CHIP

R501 CRJ10DJ182T RES , CHIP

R502 CRJ10DJ182T RES , CHIP

R503 CRJ10DJ103T RES , CHIP

R504 CRJ10DJ473T RES , CHIP

R505 CRJ10DJ470T RES , CHIP

R506 CRJ10DJ271T RES , CHIP

R511 CRJ10DJ0R0T RES , CHIP

R512 CRJ10DJ0R0T RES , CHIP

R513 CRJ10DJ103T RES , CHIP

R514 CRJ10DJ100T RES , CHIP

R515 CRJ10DJ103T RES , CHIP

R516 CRJ10DJ103T RES , CHIP

R517 CRJ10DJ103T RES , CHIP

R518 CRJ10DJ103T RES , CHIP

R519 CRJ10DJ473T RES , CHIP

R522 CRJ10DJ0R0T RES , CHIP

R533 CRJ10DJ0R0T RES , CHIP

4.7K OHM 1608 SIZE

4.7K OHM 1608 SIZE

4.7K OHM 1608 SIZE

11K OHM 1608 SIZE

0 OHM 1608 SIZE

10K OHM 1608 SIZE

0 OHM 1608 SIZE

0 OHM 1608 SIZE

0 OHM 1608 SIZE

0 OHM 1608 SIZE

4.7K OHM 1608 SIZE

0 OHM 1608 SIZE

2.7K OHM 1608 SIZE

1K OHM 1608 SIZE

1K OHM 1608 SIZE

220 OHM 1608 SIZE

33K OHM 1608 SIZE

10 OHM 1608 SIZE

10K OHM 1608 SIZE

680 OHM 1608 SIZE

820 OHM 1608 SIZE

1.2K OHM 1608 SIZE

1.5K OHM 1608 SIZE

2.2K OHM 1608 SIZE

3.3K OHM 1608 SIZE

4.7K OHM 1608 SIZE

220 OHM 1608 SIZE

75 OHM 1608 SIZE

68 OHM 1608 SIZE

120 OHM 1608 SIZE

82 OHM 1608 SIZE

4.7 OHM 1608 SIZE

3.3K OHM 1608 SIZE

1.8K OHM 1608 SIZE

1.8K OHM 1608 SIZE

10K OHM 1608 SIZE

47K OHM 1608 SIZE

47 OHM 1608 SIZE

270 OHM 1608 SIZE

0 OHM 1608 SIZE

0 OHM 1608 SIZE

10K OHM 1608 SIZE

10 OHM 1608 SIZE

10K OHM 1608 SIZE

10K OHM 1608 SIZE

10K OHM 1608 SIZE

10K OHM 1608 SIZE

47K OHM 1608 SIZE

0 OHM 1608 SIZE

0 OHM 1608 SIZE

Page 24

FRONT AND MAIN PCB

harman/kardon

Service manual DVD37EU

Page 24 of 117

Ref# Component Description Drawing No

R544 CRJ10DJ0R0T RES , CHIP

R549 CRJ10DJ105T RES , CHIP

R552 CRJ10DJ0R0T RES , CHIP

R553 CRJ10DJ0R0T RES , CHIP

R564 CRJ10DJ472T RES , CHIP

R593 CRJ10DJ0R0T RES , CHIP

R600 CRJ10DJ132T RES , CHIP

R601 CRJ10DJ132T RES , CHIP

R602 CRJ10DJ132T RES , CHIP

R603 CRJ10DJ132T RES , CHIP

R604 CRJ10DJ132T RES , CHIP

R605 CRJ10DJ132T RES , CHIP

R606 CRJ10DJ132T RES , CHIP

R607 CRJ10DJ132T RES , CHIP

R608 CRJ10DJ132T RES , CHIP

R609 CRJ10DJ132T RES , CHIP

R611 CRJ10DJ0R0T RES , CHIP

R612 CRJ10DJ332T RES , CHIP

R618 CRJ10DJ332T RES , CHIP

R619 CRJ10DJ101T RES , CHIP

R620 CRJ10DJ132T RES , CHIP

R621 CRJ10DJ132T RES , CHIP

R622 CRJ10DJ132T RES , CHIP

R623 CRJ10DJ132T RES , CHIP

R624 CRJ10DJ102T RES , CHIP

R625 CRJ10DJ332T RES , CHIP

R626 CRJ10DJ332T RES , CHIP

R627 CRJ10DJ332T RES , CHIP

R628 CRJ10DJ102T RES , CHIP

R629 CRJ10DJ332T RES , CHIP

R630 CRJ10DJ221T RES , CHIP

R631 CRJ10DJ221T RES , CHIP

R632 CRJ10DJ104T RES , CHIP

R633 CRJ10DJ104T RES , CHIP

R641 CRJ10DJ224T RES , CHIP

R642 CRJ10DJ224T RES , CHIP

R650 CRJ10DJ132T RES , CHIP

R651 CRJ10DJ132T RES , CHIP

R652 CRJ10DJ132T RES , CHIP

R653 CRJ10DJ132T RES , CHIP

R654 CRJ10DJ102T RES , CHIP

R655 CRJ10DJ332T RES , CHIP

R656 CRJ10DJ332T RES , CHIP

R657 CRJ10DJ332T RES , CHIP

R658 CRJ10DJ102T RES , CHIP

R659 CRJ10DJ332T RES , CHIP

R660 CRJ10DJ102T RES , CHIP

R661 CRJ10DJ102T RES , CHIP

R662 CRJ10DJ104T RES , CHIP

R663 CRJ10DJ104T RES , CHIP

R664 CRJ10DJ102T RES , CHIP

R665 CRJ10DJ102T RES , CHIP

0 OHM 1608 SIZE

1M OHM 1608 SIZE

0 OHM 1608 SIZE

0 OHM 1608 SIZE

4.7K OHM 1608 SIZE

0 OHM 1608 SIZE

1.3K OHM 1608 SIZE

1.3K OHM 1608 SIZE

1.3K OHM 1608 SIZE

1.3K OHM 1608 SIZE

1.3K OHM 1608 SIZE

1.3K OHM 1608 SIZE

1.3K OHM 1608 SIZE

1.3K OHM 1608 SIZE

1.3K OHM 1608 SIZE

1.3K OHM 1608 SIZE

0 OHM 1608 SIZE

3.3K OHM 1608 SIZE

3.3K OHM 1608 SIZE

100 OHM 1608 SIZE

1.3K OHM 1608 SIZE

1.3K OHM 1608 SIZE

1.3K OHM 1608 SIZE

1.3K OHM 1608 SIZE

1K OHM 1608 SIZE

3.3K OHM 1608 SIZE

3.3K OHM 1608 SIZE

3.3K OHM 1608 SIZE

1K OHM 1608 SIZE

3.3K OHM 1608 SIZE

220 OHM 1608 SIZE

220 OHM 1608 SIZE

1M OHM 1608 SIZE

1M OHM 1608 SIZE

220K OHM 1608 SIZE

220K OHM 1608 SIZE

1.3K OHM 1608 SIZE

1.3K OHM 1608 SIZE

1.3K OHM 1608 SIZE

1.3K OHM 1608 SIZE

1K OHM 1608 SIZE

3.3K OHM 1608 SIZE

3.3K OHM 1608 SIZE

3.3K OHM 1608 SIZE

1K OHM 1608 SIZE

3.3K OHM 1608 SIZE

1K OHM 1608 SIZE

1K OHM 1608 SIZE

100K OHM 1608 SIZE

100K OHM 1608 SIZE

1K OHM 1608 SIZE

1K OHM 1608 SIZE

Page 25

FRONT AND MAIN PCB

harman/kardon

Service manual DVD37EU

Page 25 of 117

Ref# Component Description Drawing No

R666 CRJ10DJ102T RES , CHIP

R667 CRJ10DJ102T RES , CHIP

R668 CRJ10DJ104T RES , CHIP

R669 CRJ10DJ104T RES , CHIP

R670 CRJ10DJ102T RES , CHIP

R671 CRJ10DJ102T RES , CHIP

R672 CRJ10DJ332T RES , CHIP

R673 CRJ10DJ102T RES , CHIP

R674 CRJ10DJ332T RES , CHIP

R675 CRJ10DJ102T RES , CHIP

R676 CRJ10DJ102T RES , CHIP

R677 CRJ10DJ102T RES , CHIP

R678 CRJ10DJ132T RES , CHIP

R679 CRJ10DJ132T RES , CHIP

R680 CRJ10DJ132T RES , CHIP

R681 CRJ10DJ132T RES , CHIP

1K OHM 1608 SIZE

1K OHM 1608 SIZE

100K OHM 1608 SIZE

100K OHM 1608 SIZE

1K OHM 1608 SIZE

1K OHM 1608 SIZE

3.3K OHM 1608 SIZE

1K OHM 1608 SIZE

3.3K OHM 1608 SIZE

1K OHM 1608 SIZE

1K OHM 1608 SIZE

1K OHM 1608 SIZE

1.3K OHM 1608 SIZE

1.3K OHM 1608 SIZE

1.3K OHM 1608 SIZE

1.3K OHM 1608 SIZE

R682 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

R683 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

R684 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

R685 CRJ10DJ101T RES , CHIP 100 OHM 1608 SIZE

R686 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

R687 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

R688 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

R689 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

R690 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

R691 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

R692 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

R694 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

R695 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

R698 CRJ10DJ132T RES , CHIP 1.3K OHM 1608 SIZE

R699 CRJ10DJ132T RES , CHIP 1.3K OHM 1608 SIZE

R726 CRJ10DJ474T RES , CHIP 470K OHM 1608 SIZE

R727 CRJ10DJ221T RES , CHIP 220 OHM 1608 SIZE

R728 CRJ10DJ223T RES , CHIP 22K OHM 1608 SIZE

R729 CRJ10DJ221T RES , CHIP 220 OHM 1608 SIZE

R730 CRJ10DJ221T RES , CHIP 220 OHM 1608 SIZE

R731 CRJ10DJ221T RES , CHIP 220 OHM 1608 SIZE

R732 CRJ10DJ221T RES , CHIP 220 OHM 1608 SIZE

R733 CRJ10DJ222T RES , CHIP 2.2K OHM 1608 SIZE

R734 CRJ10DJ222T RES , CHIP 2.2K OHM 1608 SIZE

R735 CRJ10DJ222T RES , CHIP 2.2K OHM 1608 SIZE

R736 CRJ10DJ222T RES , CHIP 2.2K OHM 1608 SIZE

R737 CRJ10DJ222T RES , CHIP 2.2K OHM 1608 SIZE

R738 CRJ10DJ222T RES , CHIP 2.2K OHM 1608 SIZE

R739 CRJ10DJ224T RES , CHIP 220K OHM 1608 SIZE

R744 CRJ10DJ222T RES , CHIP 2.2K OHM 1608 SIZE

R745 CRJ10DJ222T RES , CHIP 2.2K OHM 1608 SIZE

R746 CRJ10DJ222T RES , CHIP 2.2K OHM 1608 SIZE

R747 CRJ10DJ222T RES , CHIP 2.2K OHM 1608 SIZE

R748 CRJ10DJ222T RES , CHIP 2.2K OHM 1608 SIZE

R749 CRJ10DJ222T RES , CHIP 2.2K OHM 1608 SIZE

R801 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

Page 26

FRONT AND MAIN PCB

harman/kardon

Service manual DVD37EU

Page 26 of 117

Ref# Component Description Drawing No

R802 CRJ10DJ820T RES , CHIP 82 OHM 1608 SIZE

R803 CRJ10DJ0R0T RES , CHIP 0 OHM 1608 SIZE

R806 CRJ10DJ820T RES , CHIP 82 OHM 1608 SIZE

R807 CRJ10DJ680T RES , CHIP 68 OHM 1608 SIZE

R808 CRJ10DJ680T RES , CHIP 68 OHM 1608 SIZE

R809 CRJ10DJ680T RES , CHIP 68 OHM 1608 SIZE

R810 CRJ10DJ471T RES , CHIP 470 OHM 1608 SIZE

R811 CRJ10DJ471T RES , CHIP 470 OHM 1608 SIZE

R812 CRJ10DJ102T RES , CHIP 1K OHM 1608 SIZE

R813 CRJ10DJ821T RES , CHIP 820 OHM 1608 SIZE

R814 CRJ10DJ750T RES , CHIP 75 OHM 1608 SIZE

R815 CRJ10DJ181T RES , CHIP 1608 SIZE

R816 CRJ10DJ390T RES , CHIP

R817 CRJ10DJ750T RES , CHIP

R818 CRJ10DJ750T RES , CHIP

R821 CRJ10DJ0R0T RES , CHIP

R823 CRJ10DJ0R0T RES , CHIP

R824 CRJ10DJ750T RES , CHIP

R825 CRJ10DJ101T RES , CHIP

R826 CRJ10DJ222T RES , CHIP

R827 CRJ10DJ221T RES , CHIP

R828 CRJ18AJ221T RES , CHIP

R829 CRJ10DJ104T RES , CHIP

R830 CRJ10DJ390T RES , CHIP

39 OHM 1608 SIZE

75 OHM 1608 SIZE

75 OHM 1608 SIZE

0 OHM 1608 SIZE

0 OHM 1608 SIZE

75 OHM 1608 SIZE

100 OHM 1608 SIZE

2.2K OHM 1608 SIZE

220 OHM 1608 SIZE

220 OHM 1608 SIZE

100K OHM 1608 SIZE

39 OHM 1608 SIZE

R831 CRJ10DJ750T RES , CHIP 75 OHM 1608 SIZE

R832 CRJ10DJ102T RES , CHIP 1K OHM 1608 SIZE

R833 CRJ10DJ750T RES , CHIP 75 OHM 1608 SIZE

R834 CRJ10DJ820T RES , CHIP 82 OHM 1608 SIZE

R878 CRJ10DJ104T RES , CHIP

R879 CRJ10DJ101T RES , CHIP

100K OHM 1608 SIZE

100 OHM 1608 SIZE

R880 CRJ10DJ221T RES , CHIP 220 OHM 1608 SIZE

R895 CRJ10DJ221T RES , CHIP 220 OHM 1608 SIZE

R896 CRJ10DJ680T RES , CHIP 68 OHM 1608 SIZE

X101 HOX27000E180S CRYSTAL , CHIP(27MHZ,SMD) HC-49/US

C105 CCEA1CH470T CAP , ELECT 47UF 16V

C108 CCEA1CH101T CAP , ELECT 100UF 16V

C109 CCEA1CH101T CAP , ELECT 100UF 16V

C111 CCEA1CH101T CAP , ELECT 100UF 16V

C114 CCEA1CH101T CAP , ELECT 100UF 16V

C116 CCEA1CH101T CAP , ELECT 100UF 16V

C118 CCEA1CH101T CAP , ELECT 100UF 16V

C119 CCEA1CH101T CAP , ELECT 100UF 16V

C121 CCEA1CH101T CAP , ELECT 100UF 16V

C123 CCEA1CH101T CAP , ELECT 100UF 16V

C125 CCEA1CH101T CAP , ELECT 100UF 16V

C128 CCEA1CH101T CAP , ELECT 100UF 16V

C130 CCEA1CH101T CAP , ELECT 100UF 16V

C137 CCEA1CH470T CAP , ELECT 47UF 16V

C139 CCEA1CH470T CAP , ELECT 47UF 16V

C142 CCEA1CH470T CAP , ELECT 47UF 16V

C150 CCEA1CH101T CAP , ELECT 100UF 16V

C155 CCEA1CH470T CAP , ELECT 47UF 16V

Page 27

FRONT AND MAIN PCB

harman/kardon

Service manual DVD37EU

Page 27 of 117

Ref# Component Description Drawing No

C177 CCEA1CH101T CAP , ELECT 100UF 16V

C182 CCEA1CH470T CAP , ELECT 47UF 16V

C184 CCEA1CH470T CAP , ELECT 47UF 16V

C198 CCEA1CH101T CAP , ELECT 100UF 16V

C202 CCEA1CH470T CAP , ELECT 47UF 16V

C203 CCEA1CH470T CAP , ELECT 47UF 16V

C206 CCEA1CH470T CAP , ELECT 47UF 16V

C213 CCEA1CH221T CAP , ELECT 220UF 16V

C219 CCEA1CH470T CAP , ELECT 47UF 16V

C221 CCEA1CH101T CAP , ELECT 100UF 16V

C223 CCEA1CH101T CAP , ELECT 100UF 16V

C224 CCEA1CH101T CAP , ELECT 100UF 16V

C226 CCEA1CH101T CAP , ELECT 100UF 16V

C233 CCEA1CH101T CAP , ELECT 100UF 16V

C236 CCEA1CH470T CAP , ELECT 47UF 16V

C241 CCEA1CH470T CAP , ELECT 47UF 16V

C243 CCEA1CH470T CAP , ELECT 47UF 16V

C251 CCEA1CH470T CAP , ELECT 47UF 16V

C258 CCEA1HH4R7T CAP , ELECT 4.7UF 50V

C301 CCEA1CH101T CAP , ELECT 100UF 16V

C404 CCEA1CKS470T CAP , ELECT 47UF 16V

C504 CCEA1CH221T CAP , ELECT 220UF 16V

C508 CCEA1CH221T CAP , ELECT 220UF 16V

C510 CCEA1HH4R7T CAP , ELECT 4.7UF 50V

C530 CCEA1CH221T CAP , ELECT 220UF 16V

C532 CCEA1CH221T CAP , ELECT 220UF 16V

C548 CCEA1CH221T CAP , ELECT 220UF 16V

C549 CCEA1CH221T CAP , ELECT 220UF 16V

C561 CCEA1CH100T CAP , ELECT 10UF 16V

C562 CCEA1HH1R0T CAP , ELECT 1UF 50V

C574 CCEA1CH221T CAP , ELECT 220UF 16V

C579 CCEA1CH221T CAP , ELECT 220UF 16V

C582 CCEA1CH470T CAP , ELECT 47UF 16V

C583 CCEA1CH221T CAP , ELECT 220UF 16V

C586 CCEA1CH221T CAP , ELECT 220UF 16V

C616 CCEA1CH220T CAP , ELECT 22UF 16V

C618 CCEA1CH101T CAP , ELECT 100UF 16V

C628 CCEA1CH101T CAP , ELECT 100UF 16V

C629 CCEA1CH101T CAP , ELECT 100UF 16V

C637 HCQI1H222JZT CAP , MYLAR

C640 HCQI1H222JZT CAP , MYLAR

2200PF 50V J

2200PF 50V J

C642 CCEA1CH220T CAP , ELECT 22UF 16V

C643 CCEA1CH220T CAP , ELECT 22UF 16V

C645 HCQI1H222JZT CAP , MYLAR

C648 HCQI1H222JZT CAP , MYLAR

2200PF 50V J

2200PF 50V J

C653 CCEA1CH220T CAP , ELECT 22UF 16V

C658 HCQI1H222JZT CAP , MYLAR

C661 HCQI1H222JZT CAP , MYLAR

2200PF 50V J

2200PF 50V J

C666 CCEA1CH101T CAP , ELECT 100UF 16V

C667 CCEA1CH101T CAP , ELECT 100UF 16V

C669 CCEA1CH101T CAP , ELECT 100UF 16V

C670 CCEA1CH101T CAP , ELECT 100UF 16V

Page 28

FRONT AND MAIN PCB

harman/kardon

Service manual DVD37EU

Page 28 of 117

Ref# Component Description Drawing No

C673 CCEA1CH101T CAP , ELECT 100UF 16V

C675 CCEA1CH470T CAP , ELECT 47UF 16V

C676 CCEA1HH1R0T CAP , ELECT 1UF 50V

C680 CCEA1CH221T CAP , ELECT 220UF 16V

C681 CCEA1CH101T CAP , ELECT 100UF 16V

C685 HCQI1H222JZT CAP , MYLAR

C687 HCQI1H222JZT CAP , MYLAR

C688 HCQI1H222JZT CAP , MYLAR

C689 HCQI1H222JZT CAP , MYLAR

C690 HCQI1H222JZT CAP , MYLAR

C692 HCQI1H222JZT CAP , MYLAR

2200PF 50V J

2200PF 50V J

2200PF 50V J

2200PF 50V J

2200PF 50V J

2200PF 50V J

C733 CCEA1HH3R3T CAP , ELECT 3.3UF 50V

C751 CCEA1CH220T CAP , ELECT 22UF 16V

C752 CCEA1CH220T CAP , ELECT 22UF 16V

C795 CCEA1CH221T CAP , ELECT 220UF 16V

C801 CCEA1AH331T CAP , ELECT 330UF 10V

C802 CCEA1AH331T CAP , ELECT 330UF 10V

C803 CCEA1CH220T CAP , ELECT 22UF 16V

C804 CCEA1CH101T CAP , ELECT 100UF 16V

C811 CCEA1AH331T CAP , ELECT 330UF 10V

C813 CCEA1AH331T CAP , ELECT 330UF 10V

C815 CCEA1AH331T CAP , ELECT 330UF 10V

C818 CCEA1AH331T CAP , ELECT 330UF 10V

C824 CCEA1HH1R0T CAP , ELECT 1UF 50V

C825 CCEA1HH1R0T CAP , ELECT 1UF 50V

C826 CCEA1CH470T CAP , ELECT 47UF 16V

C827 CCEA1CH470T CAP , ELECT 47UF 16V

C829 CCEA1AH471T CAP , ELECT 470UF 10V

C835 CCEA1CH221T CAP , ELECT 220UF 16V

C882 CCEA1AH471T CAP , ELECT 470UF 10V

C891 CCEA1AH471T CAP , ELECT 470UF 10V

IC50 HVIKA79L08AZT REGULATOR, -8V KA79LXXAZTA

Q605 HVTKSA916YT T.R

S401 HST1A020ZT SW , TACT

S402 HST1A020ZT SW , TACT

S403 HST1A020ZT SW , TACT

S404 HST1A020ZT SW , TACT

S405 HST1A020ZT SW , TACT

S406 HST1A020ZT SW , TACT

S407 HST1A020ZT SW , TACT

S408 HST1A020ZT SW , TACT

KSA916Y

switch, Front panel

switch, Front panel

switch, Front panel

switch, Front panel

switch, Front panel

switch, Front panel

switch, Front panel

switch, Front panel

CMD1A504 BRACKET , FIP

BN01 CWB1C912060EN WIRE ASS'Y

BN07 CWB1A906190EN WIRE ASS'Y

CN01 CJP15GA117ZY WAFER , CARD CABLE

CN03 CJP07GA01ZY WAFER, STRAIGHT, 7PIN

CN05 CJP15GB113ZY WAFER

CN07 CJP06GA19ZY WAFER, STRAIGHT, 6PIN

CN12 CJP05GA19ZY WAFER, STRAIGHT, 5PIN

CN13 CJP06GA19ZY WAFER, STRAIGHT, 6PIN

12Pin, 60mm

6Pin, 190mm

15Pin connector

7Pin connector

15Pin connector

6Pin connector

5Pin connector

6Pin connector

D103 CVD1N4003ST RECT , DIODE 1N4003

D104 CVD1N4003ST RECT , DIODE 1N4003

Page 29

FRONT AND MAIN PCB

harman/kardon

Service manual DVD37EU

Page 29 of 117

Ref# Component Description Drawing No

D105 CVD1N4003ST RECT , DIODE 1N4003

D107 CVD1N4003ST RECT , DIODE 1N4003

D109 CVD1N4003ST RECT , DIODE 1N4003

D110 CVD1N4003ST RECT , DIODE 1N4003

D401 CVD50BOBBWGA L.E.D , 2 COLOR (ORG , BLUE) TOL-50BOBBWGA

ET01 CMC1A111 PLATE , EARTH

ET02 CMC1A111 PLATE , EARTH

F401 HFL13BT229GINK F.I.P 13-BT-229GINK

IC46 BVIKP1010B IC, PHOTO COUPLER

IC49 HVIKIA7808API REGULATOR, +8V KIA7808 (KEC)

IC61 HRVKSM603TH2 SENSOR IR KSM-603TH2

JK01 CJJ4R041Z 6P JACK, BOARD RCA-601DAG-11

JK02 CJJ4N067Z 2P, JACK RCA-201DAG-01

JK03 CJJ4S043Z JACK , BOARD

JK04 CJJ9N003Z JACK , (S-VIDEO+VHS)

JK05 CJJ6K003Z JACK, SCART CS-1071PB

JK06 HJS9U008Z Optical+Coaxial Jack (Gold Pla YKC22-0732N

JK08 HJJ1D002Z JACK, HOSIDEN SR7400

X501 HOX08000E160C CRYSTAL 8MHz

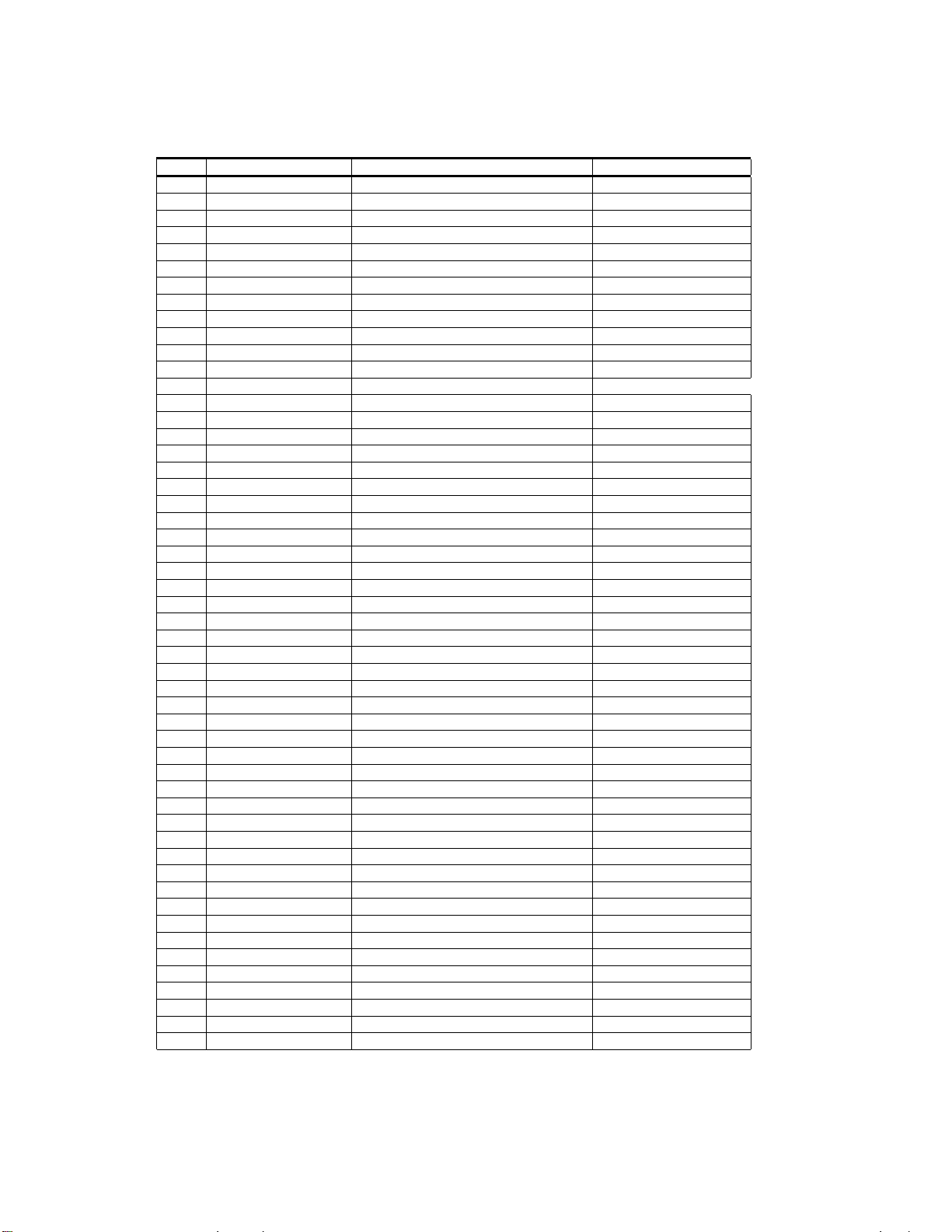

SMPS PCB

Ref# Component Description Drawing No

COP11840C SMPS ASS'Y (DVD37/47) DVD37 SMPS

C905 CCFT1H104ZF CAP , SEMICONDUCTOR

C906 CCKT1H391KB CAP , CERAMIC

C907 CCEA1HH100T CAP , ELECT 10UF 50V

C908 CCEA1HH470T CAP , ELECT 47UF 50V

C910 CCEA1HH1R0T CAP , ELECT 1UF 50V

C921 CCEA1EH331T CAP , ELECT 33OUF 25V

C922 CCEA1HH0R1T CAP , ELECT 0.1UF 50V

C923 CCEA1EH331T CAP , ELECT 33OUF 25V

C924 CCEA1VH101T CAP , ELECT 100UF 35V

C925 CCEA1EH331T CAP , ELECT 33OUF 25V

C926 HCQI1H102JZT CAP , MYLAR

1000PF 50V J

C927 CCEA1HH470T CAP , ELECT 47UF 50V

C928 CCEA1HH470T CAP , ELECT 47UF 50V

C929 CCFT1H104ZF CAP , SEMICONDUCTOR

C931 CCFT1H104ZF CAP , SEMICONDUCTOR

C935 CCFT1H104ZF CAP , SEMICONDUCTOR

0.1UF 50V ZF

0.1UF 50V ZF

0.1UF 50V ZF

D906 HVDMTZJ12BT DIODE , ZENER MTZJ12B 1/2W

D907 HVD1N4148T DIODE 1N4148

D909 HVDMTZJ24BT DIODE , ZENER MTZJ24BT 1/2W

D910 HVD1N4148T DIODE 1N4148

D911 HVD1N4148T DIODE 1N4148

D912 HVDMTZJ5.1BT DIODE , ZENER MTZJ5.1B 1/2W

D925 HVD1N4148T DIODE 1N4148

D926 HVDMTZJ12BT DIODE , ZENER MTZJ12B 1/2W

D928 HVDMTZJ2.7BT DIODE , ZENER MTZJ2.7B 1/2W

FH91 KJCFC5S HOLDER , FUSE

FH92 KJCFC5S HOLDER , FUSE

IC92 HVIKIA431BAT I.C , REGULATOR KIA431B

J901 C3A206 WIRE , COPPER SN95/PB5 , 0.6

J910 C3A206 WIRE , COPPER SN95/PB5 , 0.6

Page 30

S

SMPS PCB

harman/kardon

Service manual DVD37EU

Page 30 of 117

Ref# Component Description Drawing No

J915 C3A206 WIRE , COPPER SN95/PB5 , 0.6

J916 C3A206 WIRE , COPPER SN95/PB5 , 0.6

J923 C3A206 WIRE , COPPER SN95/PB5 , 0.6

J924 C3A206 WIRE , COPPER SN95/PB5 , 0.6

J925 C3A206 WIRE , COPPER SN95/PB5 , 0.6

L903 CLZ9Z040Z COIL , CHOKE(6.8UH) DR 6.5*7.5

L905 CLZ9Z040Z COIL , CHOKE(6.8UH) DR 6.5*7.5

NT91 KRT10D9MSFT THERMISTER

Q904 HVTKTC3198YT T.R KTC3198Y

Q905 HVTKTA1273YT TR NORMAL KTA1273/PNP/TO-92L

Q906 HVTKSC1008YT T.R KSC1008Y

Q907 HVTKRC102MT T.R KRC102M

Q908 HVTKRA102MT T.R KRA102M

Q910 HVTKSC1008YT T.R KSC1008Y

Q911 HVTKSA708YT T.R KSA708Y

Q912 HVDMCR100-6ZL1G SCR (ON SEMI)

R901 KROS1TJ105V RES , METAL FILM (1/2W , 1M OH

R903 CRD25TJ754T RES

R904 CRD25TJ754T RES

R905 CRD20TJ222T RES , CARBON 2.2K OHM 1/5W J

R906 CRD20TJ101T RES , CARBON 100 OHM 1/5W J

R907 CRD20TJ103T RES , CARBON 10K OHM 1/5W J

R909 CRD20TJ100T RES , CARBON 10 OHM 1/5W J

R910 CRD20TJ103T RES , CARBON 10K OHM 1/5W J

R911 CRD20TJ104T RES , CARBON 100K OHM 1/5W J

R912 CRD20TJ102T RES , CARBON 1K OHM 1/5W J

R913 CRD20TJ102T RES , CARBON 1K OHM 1/5W J

R914 CRD20TJ333T RES , CARBON 33K OHM 1/5W J

R920 CRD20TJ101T RES , CARBON 100 OHM 1/5W J

R921 CRD20TJ222T RES , CARBON 2.2K OHM 1/5W J

R922 CRD20TF3481T RES , CARBON

3.48K OHM 1/5W J

R923 CRD20TF3001T RES , CARBON 3K 1/5W F

R924 CRD20TJ101T RES , CARBON 100 OHM 1/5W J

R925 CRD25TJ101T RES , CARBON

100 OHM 1/4W J

R926 CRD20TJ101T RES , CARBON 100 OHM 1/5W J

R928 CRD20TJ102T RES , CARBON 1K OHM 1/5W J

R929 CRD20TJ102T RES , CARBON 1K OHM 1/5W J

R930 CRD20TJ101T RES , CARBON 100 OHM 1/5W J

R934 CRD20TJ102T RES , CARBON 1K OHM 1/5W J

R935 CRD20TJ153T RES , CARBON 15K OHM 1/5W J

R940 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J

CN91 KJP02KA060ZY WAFER 7.92MM(YUNHO)

CN92 CJP12GA19ZY WAFER

C901 HCQF2E104KZE CAP , POLYPROPYLENE FILM

0.1UF

0.1UF

C902 HCQF2E104KZE CAP , POLYPROPYLENE FILM 400V/47uF

C903 CCET400VKRH470K CAP , ELECT(400V/47uF) KOSHIN KRH SERIES (

C904 CCKT3A222KBL CAP , CERAMIC EKR3A222K05FK5

C920 CCEA1EH102T CAP , ELECT 1000UF 25V

C930 CCKDHS222ME CAP , CERAMIC (400V Y-CAP) SDE2G222M10FF7

C932 CCKDHS102ME CAP , CERAMIC (400V Y-CAP) SDE2G102M10FF7

C933 CCKDHS102ME CAP , CERAMIC (400V Y-CAP) SDE2G102M10FF7

D901 HVD1N4007T DIODE

1N4007 (1000V/1A)

Page 31

T

SMPS PCB

harman/kardon

Service manual DVD37EU

Page 31 of 117

Ref# Component Description Drawing No

D902 HVD1N4007T DIODE

D903 HVD1N4007T DIODE

D904 HVD1N4007T DIODE

1N4007 (1000V/1A)

1N4007 (1000V/1A)

1N4007 (1000V/1A)

D905 HVDUF4007T DIODE , SCHOTTKY UF4007

D908 HVD1N4007T DIODE 1N4007 (1000V/1A)

D913 HVD1N4148T DIODE 1N4148

D920 HVD31DQ06H DIODE 31DQ06-FC5

D921 HVDUF4007T DIODE , SCHOTTKY UF4007

D922 HVD1N4937T DIODE , RECTIFIERS 1N4937(600V/1A)

D923 HVD1N4937T DIODE , RECTIFIERS 1N4937(600V/1A)

D924 HVDSF26T DIODE , SUPER FAST

1N4007 (1000V/1A)

IC91 BVISG6848DZ IC,PWM SG6848DZ

LF91 CLZ9Z060Y LINE FILTER CLZ9Z060Y

PC91 HVIPC17L1CB I.C , PHOTO COUPLER

PC17L1C

Q901 CVICEF04N6YA FET. HEAT SINK ASS`Y

BVICEF04N6 FET , CEF04N6

CMY2A223 HEAT SINK

CTB3+8JR SCREW

Q903 HVTKSB1151Y T.R KSB1151Y

R902 KRG1SANJ104H RES,METAL OXIDE FILM

100K OHM

R908 KRW1PJ1R5V RES, WIRE WOUND 1W 1.5(J) NON-INDUC

R927 KRDS1TJ681V RES , CARBON 680OHM 1/2W J

T901 CLT9Z018ZE TRANS (DVD 27) EER2828H

Page 32

harman/kardon

Service manual DVD37EU

Page 32 of 117

H/K DVD 37 EU PCB DRAWING

Page 33

harman/kardon

Service manual DVD37EU

Page 33 of 117

Page 34

harman/kardon

Service manual DVD37EU

Page 34 of 117

Page 35

harman/kardon

Service manual DVD37EU

Page 35 of 117

Page 36

harman/kardon

Service manual DVD37EU

Page 36 of 117

Page 37

harman/kardon

Service manual DVD37EU

Page 37 of 117

Page 38

harman/kardon

Service manual DVD37EU

Page 38 of 117

Page 39

harman/kardon

Service manual DVD37EU

Page 39 of 117

Page 40

harman/kardon

Service manual DVD37EU

Page 40 of 117

Page 41

harman/kardon

Service manual DVD37EU

Page 41 of 117

Page 42

harman/kardon

Service manual DVD37EU

Page 42 of 117

Page 43

harman/kardon

Service manual DVD37EU

Page 43 of 117

Page 44

harman/kardon

Service manual DVD37EU

Page 44 of 117

Page 45

harman/kardon

Service manual DVD37EU

Page 45 of 117

Page 46

harman/kardon

Service manual DVD37EU

Page 46 of 117

Page 47

harman/kardon

Service manual DVD37EU

Page 47 of 117

Page 48

harman/kardon

Service manual DVD37EU

Page 48 of 117

Page 49

harman/kardon

Service manual DVD37EU

Page 49 of 117

Page 50

harman/kardon

Service manual DVD37EU

Page 50 of 117

Page 51

harman/kardon

Service manual DVD37EU

Page 51 of 117

Page 52

harman/kardon

Service manual DVD37EU

Page 52 of 117

Page 53

harman/kardon

Service manual DVD37EU

Page 53 of 117

Page 54

harman/kardon

Service manual DVD37EU

Page 54 of 117

Page 55

harman/kardon

Service manual DVD37EU

Page 55 of 117

Page 56

harman/kardon

Service manual DVD37EU

Page 56 of 117

Page 57

harman/kardon

Service manual DVD37EU

Page 57 of 117

Page 58

harman/kardon

Service manual DVD37EU

Page 58 of 117

Page 59

harman/kardon

Service manual DVD37EU

Page 59 of 117

Page 60

harman/kardon

Service manual DVD37EU

Page 60 of 117

Page 61

harman/kardon

Service manual DVD37EU

Page 61 of 117

Page 62

harman/kardon

Service manual DVD37EU

Page 62 of 117

Page 63

harman/kardon

Service manual DVD37EU

Page 63 of 117

Page 64

harman/kardon

Service manual DVD37EU

Page 64 of 117

Page 65

harman/kardon

Service manual DVD37EU

Page 65 of 117

Page 66

harman/kardon

Service manual DVD37EU

Page 66 of 117

Page 67

harman/kardon

Service manual DVD37EU

Page 67 of 117

Page 68

harman/kardon

Service manual DVD37EU

Page 68 of 117

Page 69

harman/kardon

Service manual DVD37EU

Page 69 of 117

Page 70

harman/kardon

Service manual DVD37EU

Page 70 of 117

Page 71

harman/kardon

Service manual DVD37EU

Page 71 of 117

Page 72

ESMT M12L64164A

harman/kardon

Service manual DVD37EU

Page 72 of 117

SDRAM

1M x 16 Bit x 4 Banks

Synchronous DRAM

FEATURES

JEDEC standard 3.3V power supply

LVTTL compatible with multiplexed address

Four banks operation

MRS cycle with address key programs

- CAS Latency (2 & 3)

- Burst Length (1, 2, 4, 8 & full page)

- Burst Type (Sequential & Interleave)

All inputs are sampled at the positive going edge of the

system clock

DQM for masking

Auto & self refresh

64ms refresh period (4K cycle)

GENERAL DESCRIPTION

The M12L64164A is 67,108,864 bits synchronous high data rate Dynamic RAM organized as 4 x 1,048,576 words by

16 bits. Synchronous design allows precise cycle controls with the use of system clock I/O transactions are possible on

every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same

device to be useful for a variety of high bandwidth, high performance memory system applications.

PIN ASSIGNMENT

ORDERING INFORMATION

54 Pin TSOP (Type II)

(400mil x 875mil )

PRODUCT NO. MAX FREQ. PACKAGE

M12L64164A-6T 166MHz

M12L64164A-7T 143MHz

TSOP II

V

DQ0

V

DDQ

DQ1

DQ2

V

SSQ

DQ3

DQ4

V

DDQ

DQ5

DQ6

V

SSQ

DQ7

V

LDQM

WE

CAS

RAS

CS

A

A12

A10/AP