Fairchild Semiconductor MM74HC148N, MM74HC148M, MM74HC148MX Datasheet

October 1987

Revised February 1999

MM74HC148 8-3 Line Priority Encoder

© 1999 Fairchild Semiconductor Corporation DS009390.prf www.fairchildsemi.com

MM74HC148

8-3 Line Priority Encoder

General Description

The MM74HC148 priority encoder utilizes advanced silicon-gate CMOS technology. It has the high noise immunity

and low power consumption typical of CMO S circuits, as

well as the s peeds and output drive similar to LB-TTL.

This priority encode r ac cepts 8 input request li ne s 0– 7 a nd

outputs 3 lines A0–A2. The priority encoding ensur es that

only the highest order data li ne is e ncoded . Cascad ing c ircuitry (enable input EI and enable output EO) has been

provided to allow octal expansion without the need for

external circuitry. All data inputs an d outputs are act ive at

the low logic level.

All inputs are protected from damage due to static discharge by internal diod e clamps to V

CC

and ground.

Features

■ Typical propagation delay: 13 ns

■ Wide supply voltage range: 2V–6V

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering cod e.

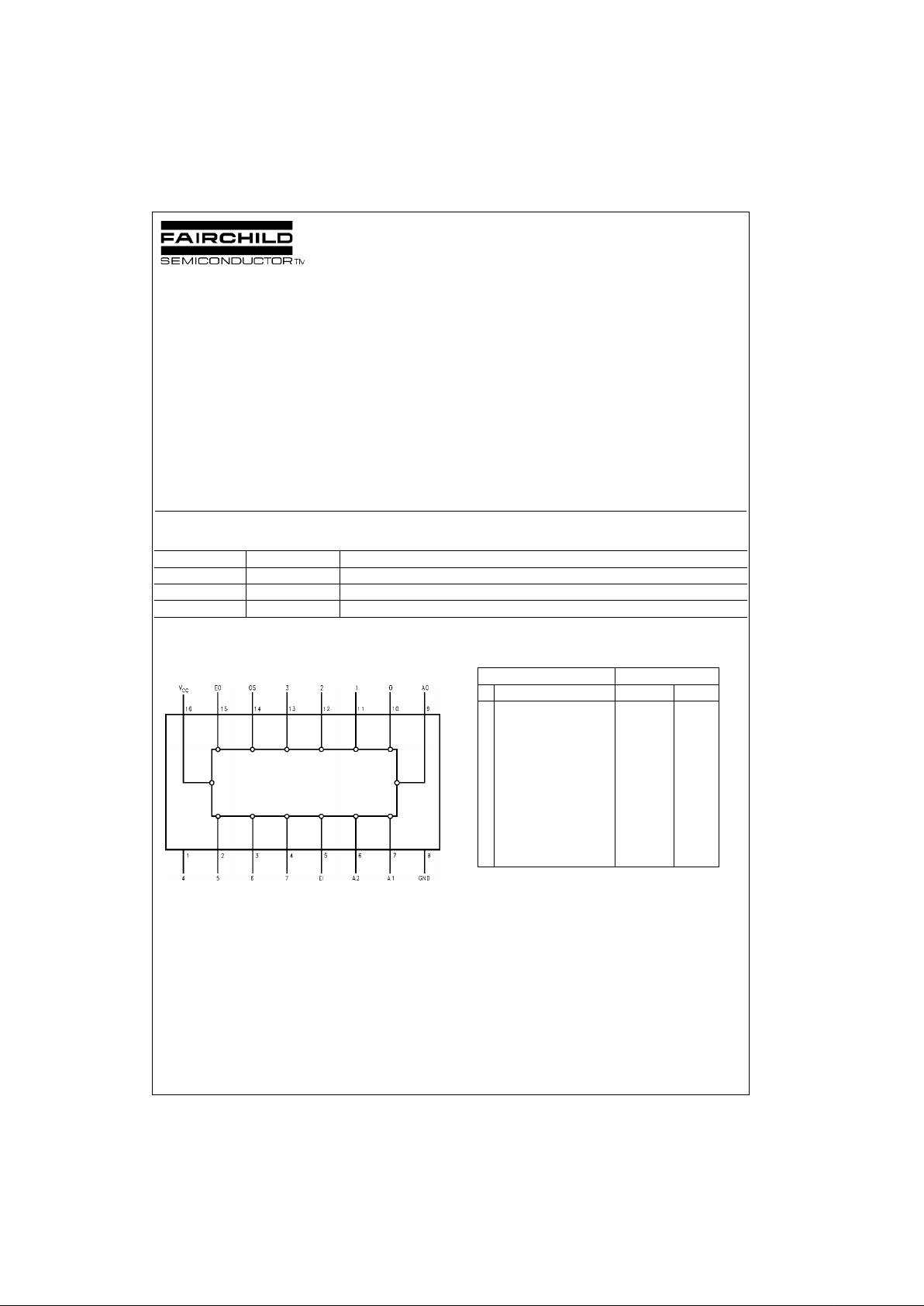

Connection Diagram

Pin Assignments for DIP, SOIC and TSSOP

Truth Table

H = HIGH

L = LOW

X = Irrelevant

Order Number Package Number Package Description

MM74HC148M M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow

MM74HC148MTC MTC16 16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

MM74HC148N N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

Inputs Outputs

EI01234567A2A1A0GSEO

HXXXXXXXXH H H H H

LHHHHHHHH H H H H L

LXXXXXXXL L L L L H

LXXXXXXLH L L H L H

LXXXXXLHH L H L L H

LXXXXLHHHL H H L H

LXXXLHHHHH L L L H

LXXLHHHHH H L H L H

LXLHHHHHH H H L L H

L LHHHHHHH H H H L H

www.fairchildsemi.com 2

MM74HC148

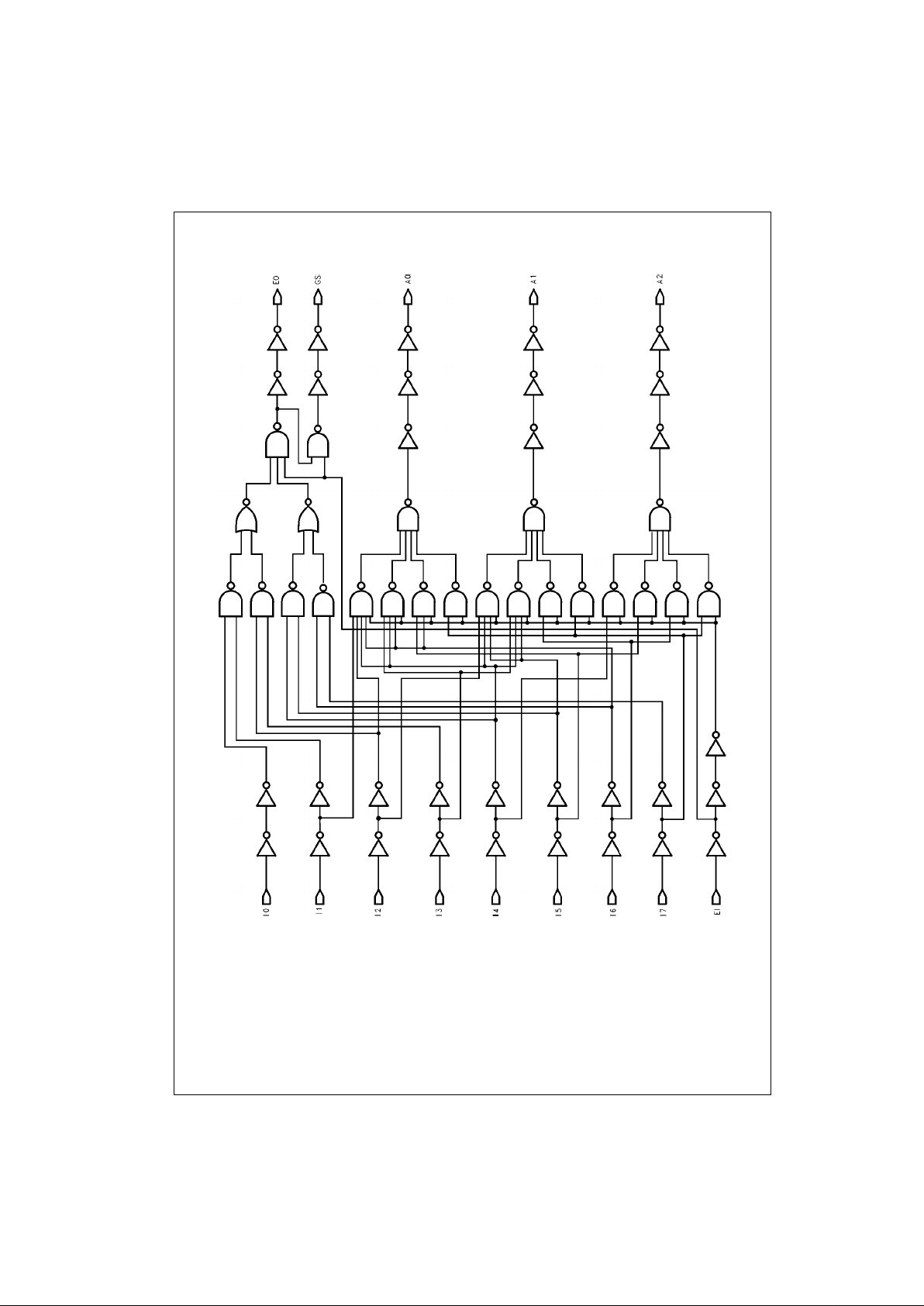

Schematic Diagram

3 www.fairchildsemi.com

MM74HC148

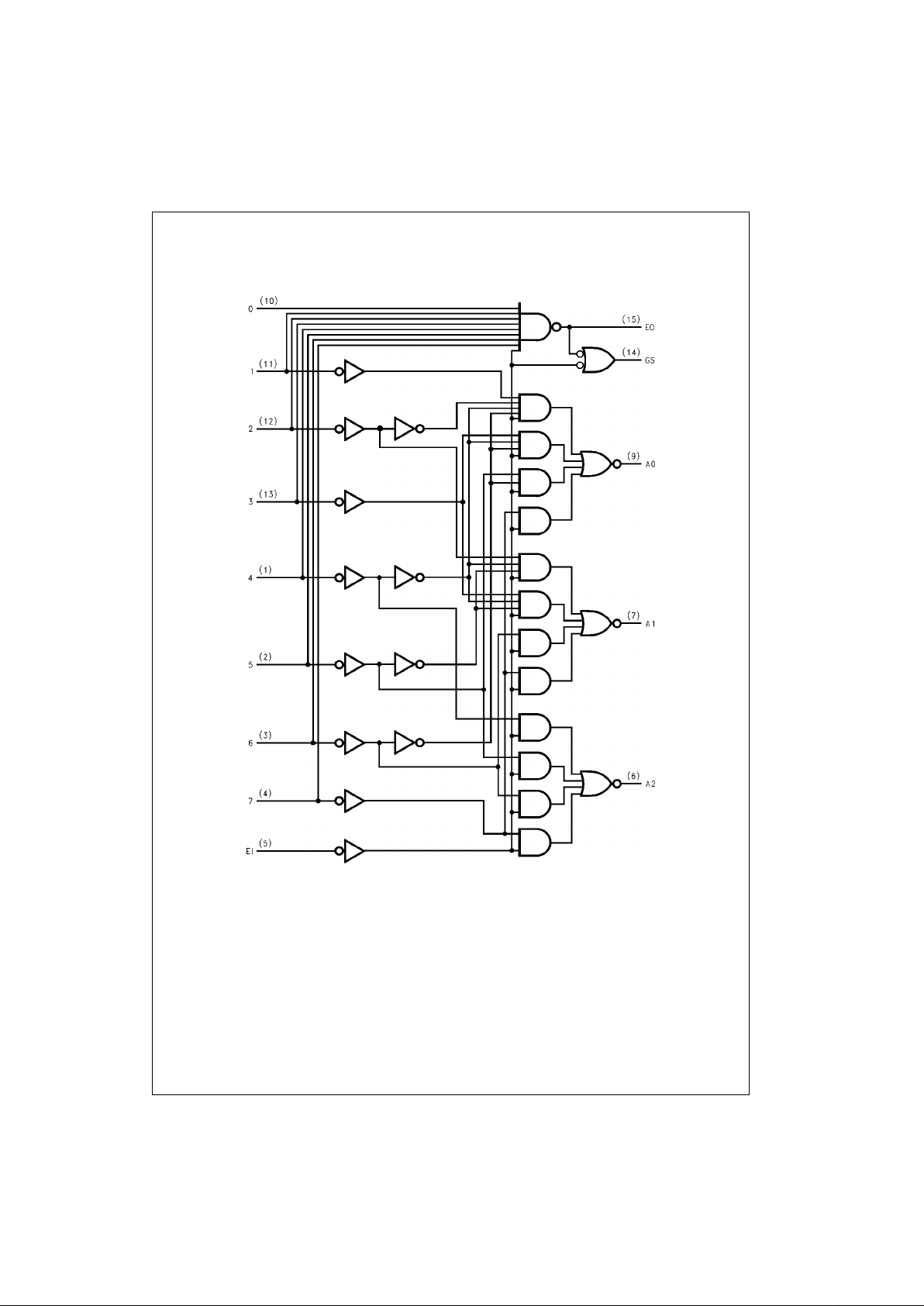

Logic Diagram

Loading...

Loading...