Fairchild Semiconductor MM74C89N Datasheet

October 1987

Revised January 1999

MM74C89

64-Bit 3-STATE Random Access Read/Write Memory

MM74C89 64-Bit 3-STATE Random Access Read/Write Memory

General Description

The MM74C89 is a 16- word by 4-bit random access read/

write memory. Inputs to the memory consist of four address

lines, four data input lines, a write

ory enable line. The four binary address inputs are

decoded internally to select each of the 16 possible word

locations. An interna l address r egister la tches the a ddress

information on the positive to negative transition of the

memory enable inpu t. The four 3-STATE data output lines

working in conjunct ion with the memor y enable input provide for easy memory expansion.

Address Operation: Address inputs must be stable t

prior to the positive to negative transition of memory

enable. It is thus not necessary to hold address information

stable for more than t

tive to negative transition of memory

Write Operation: Informa tion present at the data inp uts is

written into the memory at the selected address by bringing

enable and memory enable LOW.

write

after the memory is enabled (posi-

HA

enable line and a mem-

enable).

Read Operation: The complement of the information

which was written into the memory is non-destructively

read out at the four outputs. This is accomplished by

selecting the desired addre ss and br i n ging mem ory

LOW and write enable HIGH.

When the device is writing or disa bled the ou tput assu mes

a 3-STATE (Hi-z) condition.

Features

■ Wide supply voltage range: 3.0V to 15V

■ Guaranteed noise margin: 1.0V

SA

■ High noise immunity: 0.45 V

■ Low power TTL compatibility:

fan out of 2 driving 74L

■ Low power consumption: 100 nW/package (typ.)

■ Fast access time: 130 ns (typ.) at V

■ 3-STATE output

Note: The timing is dif fere nt t han the DM7489 in that a positive to negative

transition of the memory

enable must occur for the memory to be selected.

CC

(typ.)

CC

= 10V

Ordering Code:

Order Number Package Number Package Description

MM74C89N N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

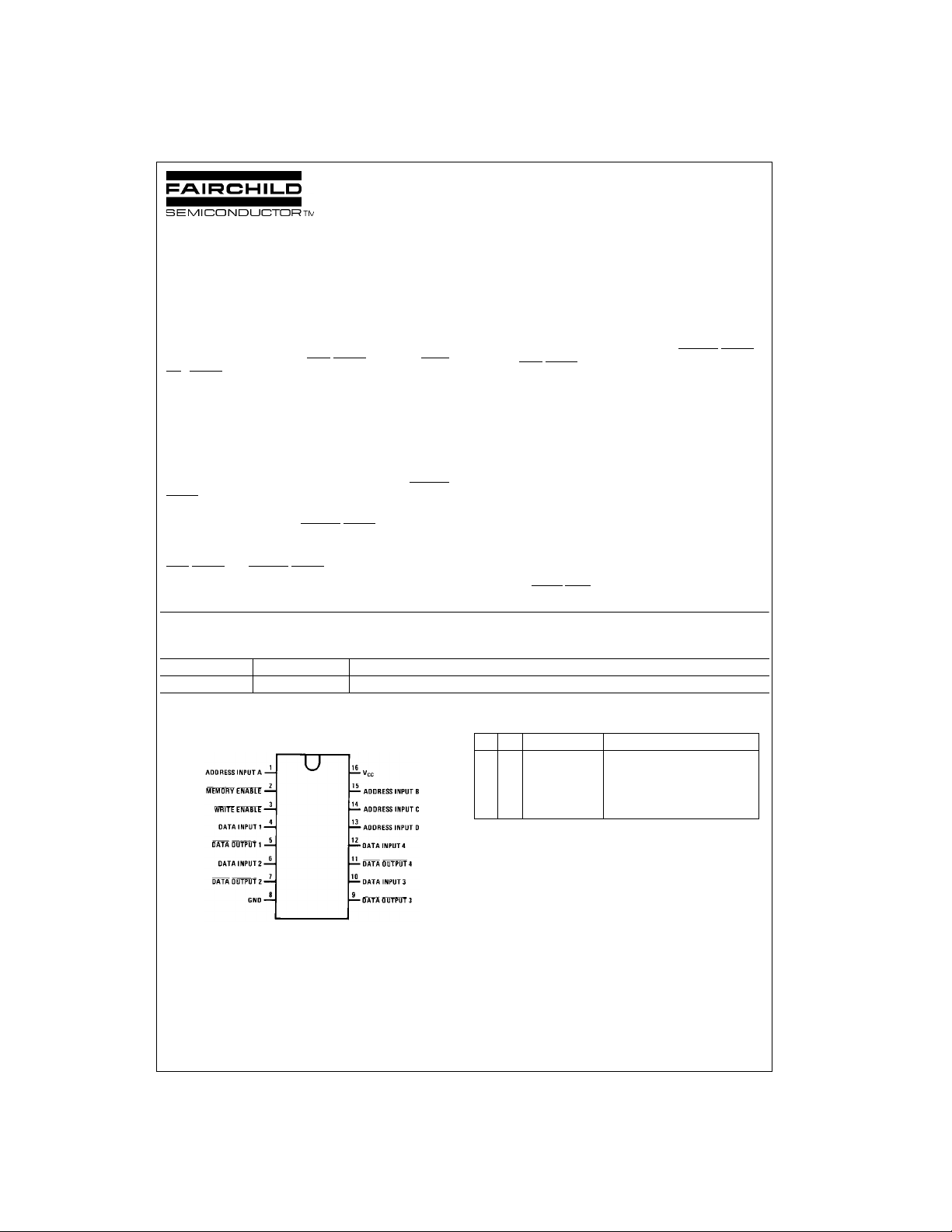

Connection Diagram

Pin Assignments for DIP

Truth T able

ME WE Operation Condition of Outputs

LLWrite 3-STATE

L H Read Complement of Selected Word

H L Inhibit, Storage 3-STATE

H H Inhibit, Storage 3-STATE

enable

Top View

© 1999 Fairchild Semiconductor Corporation DS005888.prf www.fairchildsemi.com

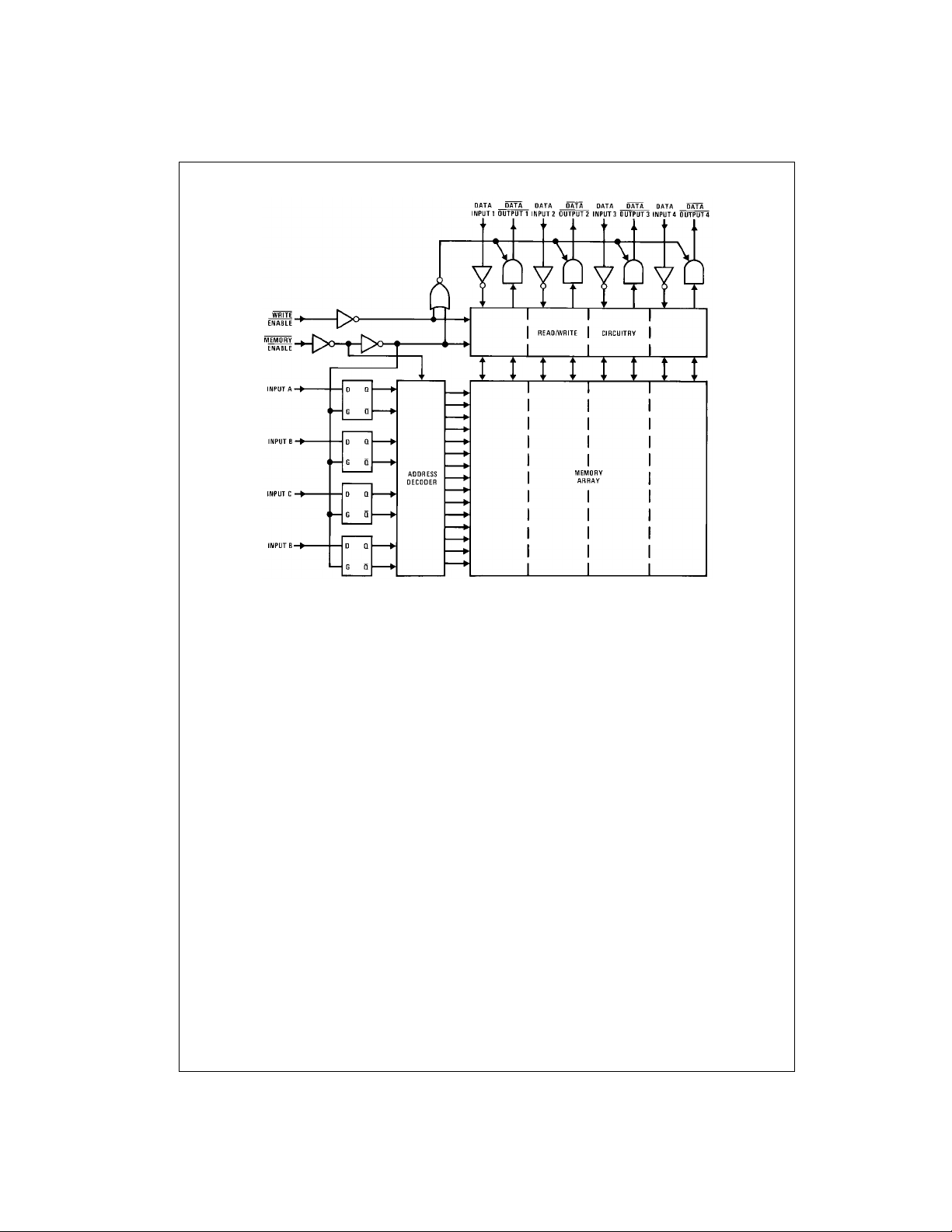

Logic Diagram

MM74C89

www.fairchildsemi.com 2

Loading...

Loading...