Fairchild Semiconductor MM74C85N Datasheet

October 1987

Revised January 1999

MM74C85

4-Bit Magnitude Comparator

(V

) applied to the A = B input and low level voltage

General Description

The MM74C85 i s a four-bit magnitude compa rator which

will perform comparison of straight binary or BCD codes.

The circuit consists of eight co mparin g inputs (A0 , A1, A2,

A3, B0, B1, B2, B3), three cascading inp uts (A > B, A < B

and A = B), and three outputs (A > B, A < B and A = B).

This device compares two four-bit words (A and B) and

determines whethe r they are “greate r than,” “le ss than,” or

“equal to” each other by a high level on the appropriate output. For words greater than four-bits, units can be cascaded by connecting the outpu ts (A > B, A < B, and A = B)

of the least significant stage to the cascade inputs (A > B, A

< B and A = B) of th e next-significant sta ge. In addi tion the

least significant stage must have a high level voltage

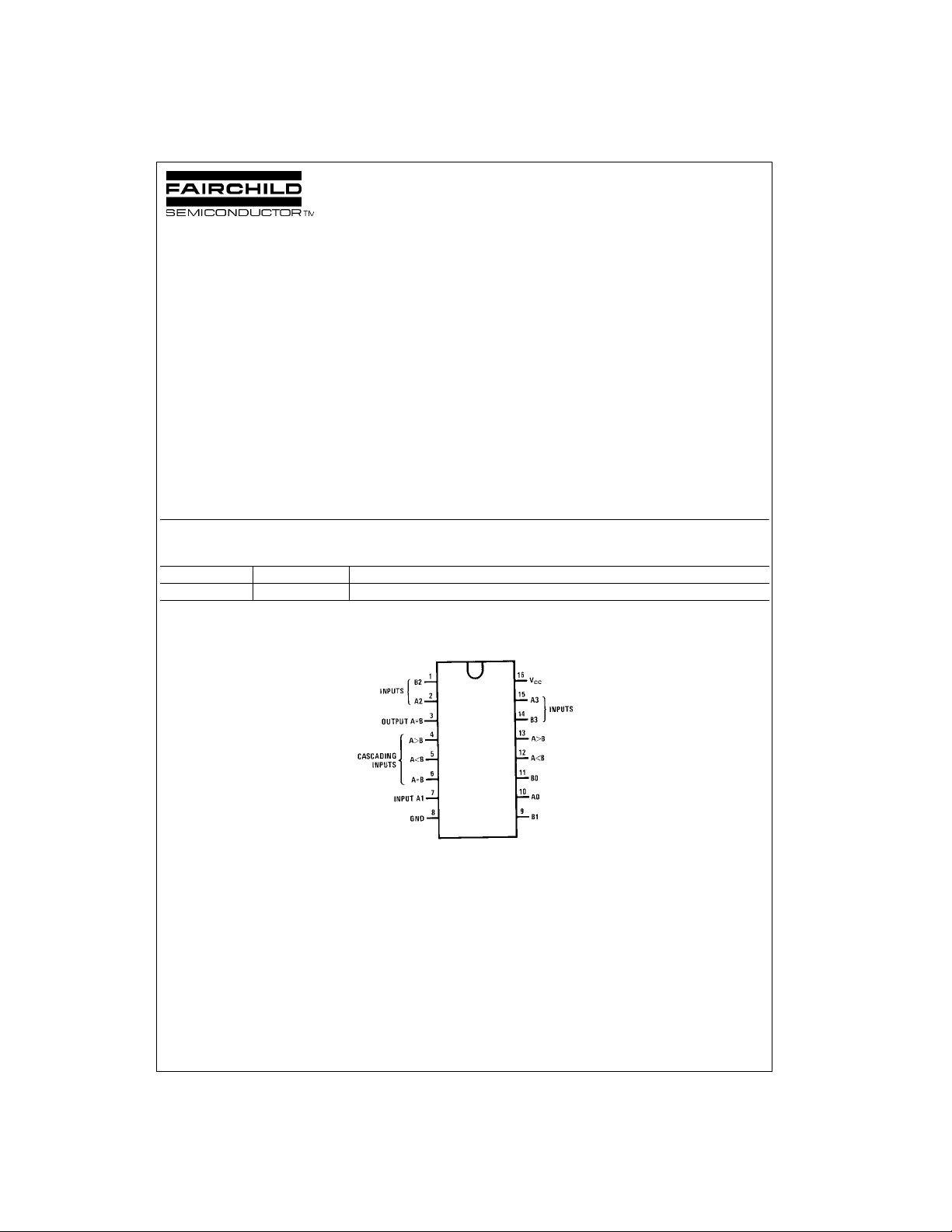

Ordering Code:

Order Number Package Number Package Description

MM74C85N N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

IN(1)

) applied to A > B and A < B inputs.

(V

IN(0)

Features

■ Wide supply voltage range: 3.0V to 15V

■ Guaranteed noise margin: 1.0V

■ High noise immunity: 0.4 V

■ Low power: TTL compatibility:

fan out of 2 driving 74L

■ Expandable to 'N' stages

■ Applicable to binar y or BC D

■ Low power pinout: 74L85

CC

(typ.)

MM74C85 4-Bit Magnitude Comparator

Connection Diagram

Pin Assignments for DIP

Top View

© 1999 Fairchild Semiconductor Corporation DS005886.prf www.fairchildsemi.com

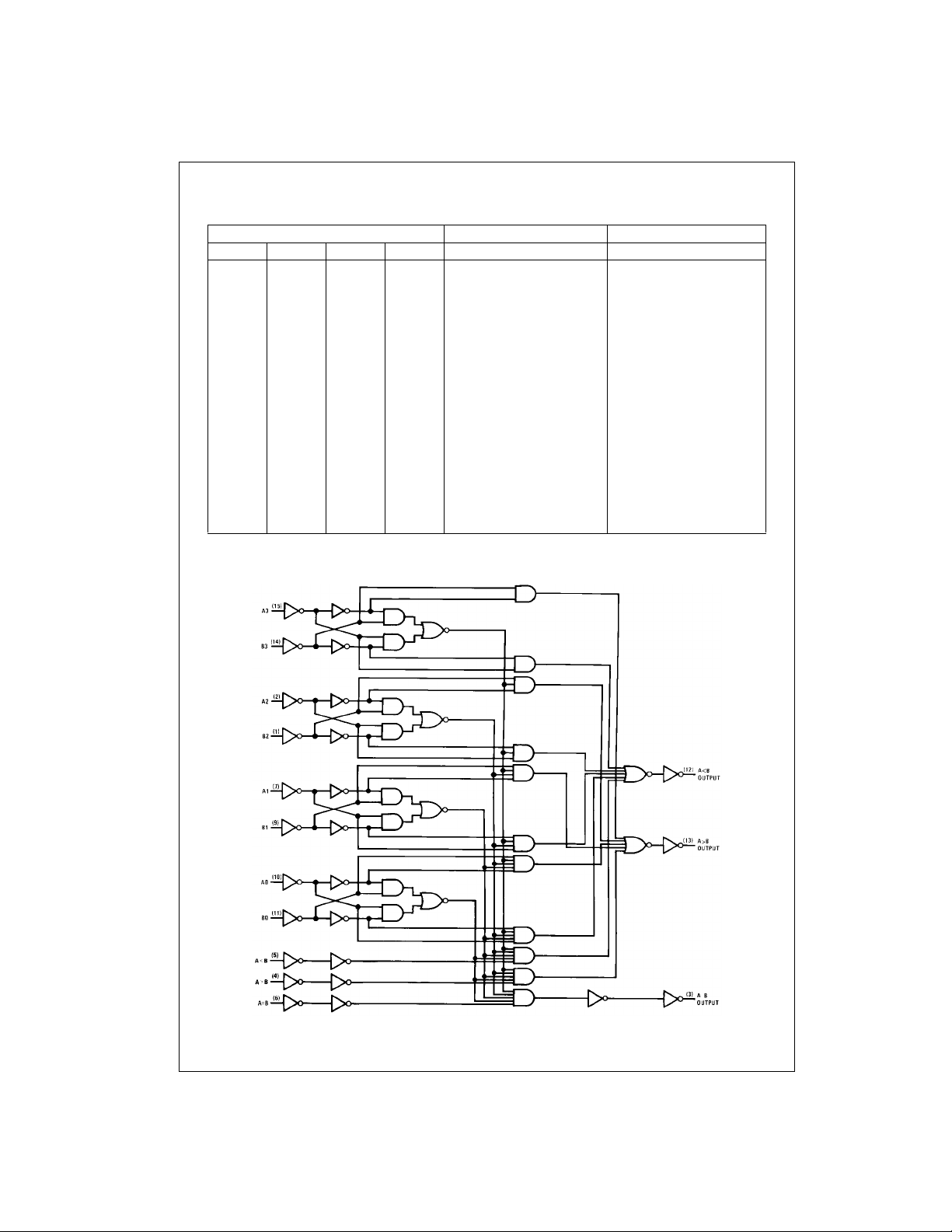

Truth Table

MM74C85

A3, B3 A2, B2 A1, B1 A0, B0 A > BA < BA = BA > BA < BA = B

A3 > B3 X X X X X X H L L

A3 < B3 X X X X X X L H L

A3 = B3 A2 > B2 X X X X X H L L

A3 = B3 A2 < B2 X X X X X L H L

A3 = B3 A2 = B2 A1 > B1 X X X X H L L

A3 = B3 A2 = B2 A1 < B1 X X X X L H L

A3 = B3 A2 = B2 A1 = B1 A0 > B0 X X X H L L

A3 = B3 A2 = B2 A1 = B1 A0 < B0 X X X L H L

A3 = B3 A2 = B2 A1 = B1 A0 = B0 H L L H L L

A3 = B3 A2 = B2 A1 = B1 A0 = B0 L H L L H L

A3 = B3 A2 = B2 A1 = B1 A0 = B0 L L H L L H

A3 = B3 A2 = B2 A1 = B1 A0 = B0 L H H L H H

A3 = B3 A2 = B2 A1 = B1 A0 = B0 H L H H L H

A3 = B3 A2 = B2 A1 = B1 A0 = B0 H H H H H H

A3 = B3 A2 = B2 A1 = B1 A0 = B0 H H L H H L

A3 = B3 A2 = B2 A1 = B1 A0 = B0 L L L L L L

H = HIGH Level, L = LOW Level, X = Irrelevant

Comparing Inputs Cascading Inputs Outputs

Logic Diagram

www.fairchildsemi.com 2

Loading...

Loading...