Fairchild Semiconductor MM74C240WM, MM74C240WMX, MM74C240N Datasheet

© 1999 Fairchild Semiconductor Corporation DS005905 www.fairchildsemi.com

October 1987

Revised July 1999

MM74C240 • MM74C244 Inverting • Non-Inverting Octal Buffer and Line Driver with 3-STATE Outputs

MM74C240 • MM74C244

Inverting • Non-Inverting Octal Buffer and

Line Driver with 3-STATE Outputs

General Description

The MM74C240 and MM74C244 octal buffers and line

drivers are monolithic complementary MOS (CMOS) integrated circuits with 3-STATE outputs. These outputs have

been specially designed to drive highly capacitive loads

such as bus-oriented sys tems. These devices have a fan

out of 6 low power Schottky loads. A high logic level on the

output disable contr ol input G makes the outputs go into

the high impedance state.

Features

■ Wide supply voltage range (3V to 15V)

■ High noise immunity (0.45 V

CC

typ)

■ Low power consumption

■ High capacitive load drive capability

■ 3-STATE outputs

■ Input protection

■ TTL compatibility

■ 20-pin dual-in-line package

■ High speed 25 ns (typ.) @ 10V, 50 pF (MM74C244)

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending su ffix le tter “X” to the ordering code.

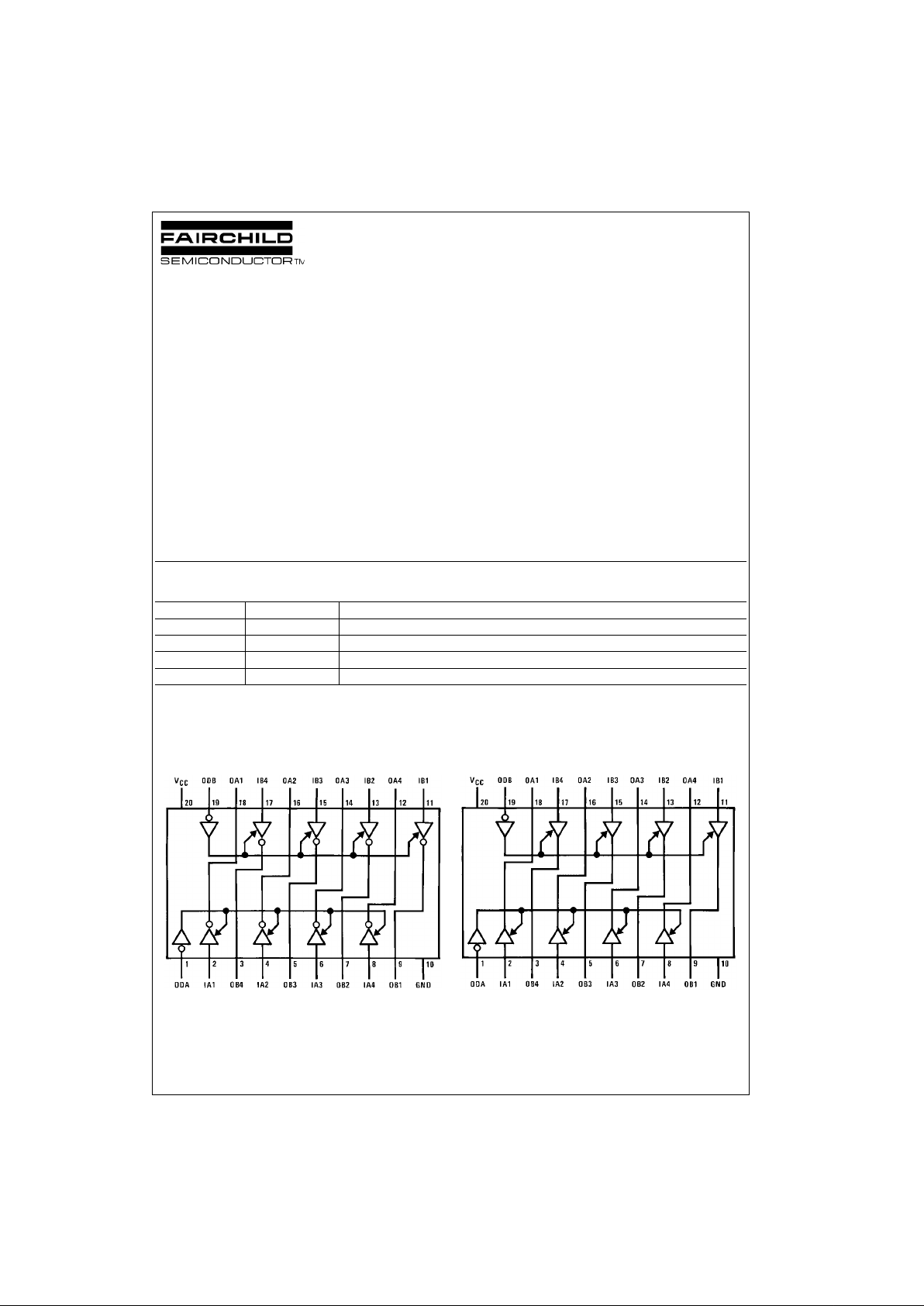

Connection Diagrams

Pin Assignments for DIP and SOIC

MM74C240

(Top View)

MM74C244

(Top View)

Order Number Package Number Package Description

MM74C240WM M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300” Wide Body

MM74C240N N20A 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

MM74C244WM M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300” Wide Body

MM74C244N N20A 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

www.fairchildsemi.com 2

MM74C240 • MM74C244

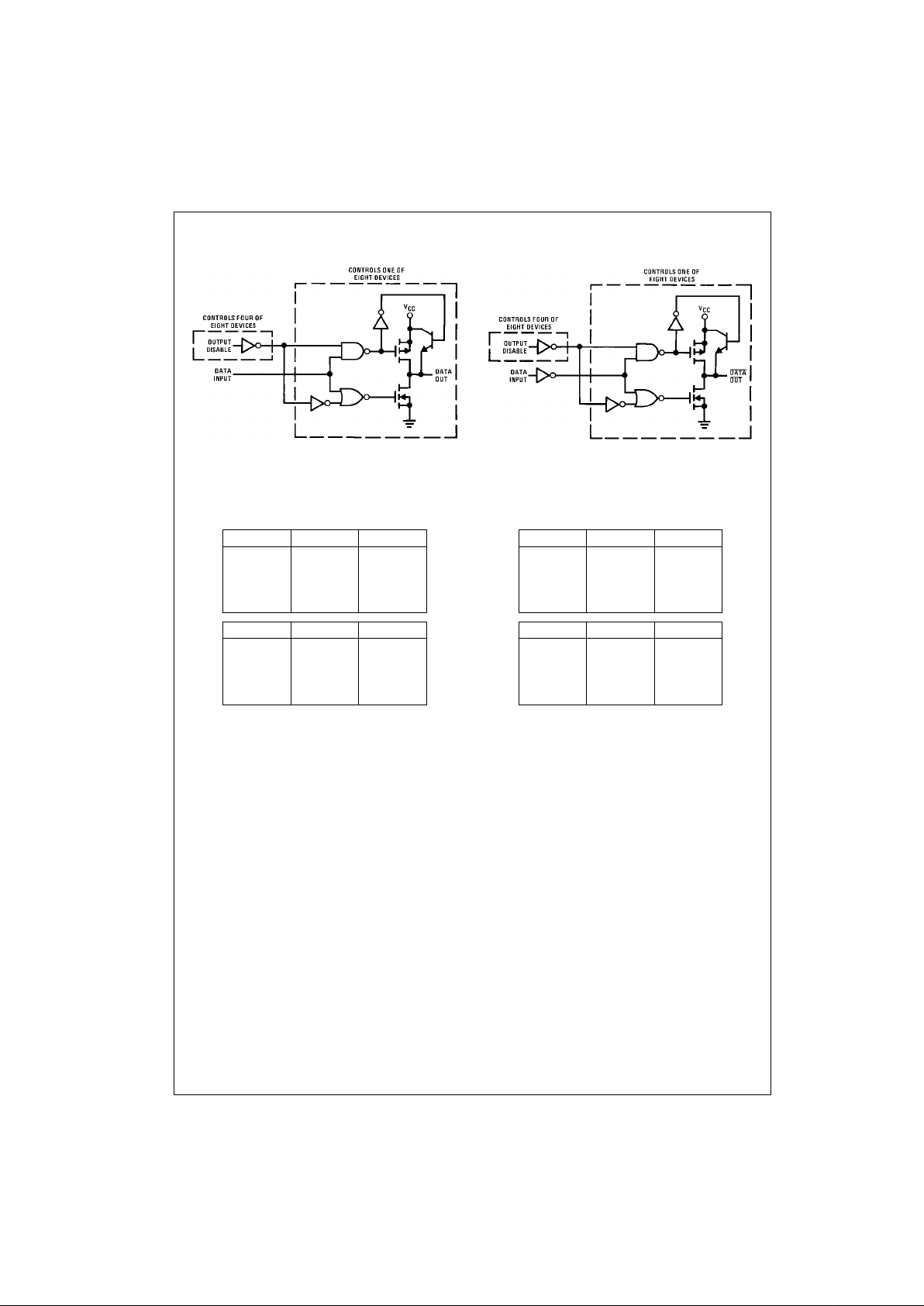

Logic Diagrams

MM74C240 MM74C244

Truth Tables

MM74C240 MM74C244

1 = HIGH

0 = LOW

X = Don’t Care

Z = 3-STATE

ODA IA OA

1XZ

1XZ

001

010

ODB IB OB

1XZ

1XZ

001

010

ODA IA OA

1XZ

1XZ

000

011

ODB IB OB

1XZ

1XZ

000

011

3 www.fairchildsemi.com

MM74C240 • MM74C244

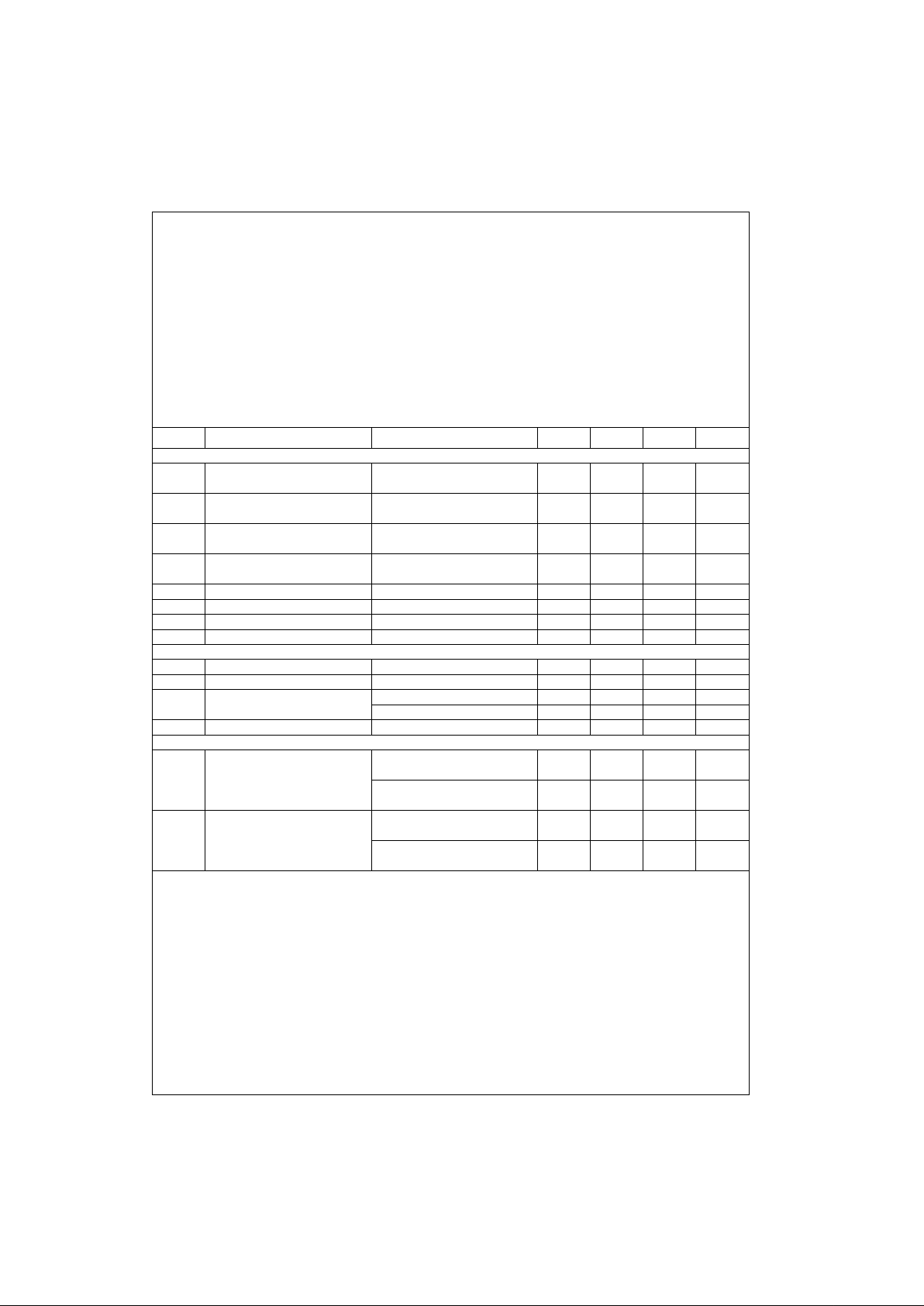

Absolute Maximum Ratings(Note 1)

Note 1: “Absolute Maximum Ratings” are those values beyond which the

safety of the device cannot be guaran teed. Excep t for “Operating Range”

they are not meant to imp ly that the devic es should be opera ted at these

limits. The Elec trical Characteristics table p rovides conditions for act ual

device operation.

DC Electrical Characteristics

Min/Max limits apply across temperature range, unless otherwise noted

Voltage at Any Pin −0.3V to VCC + 0.3V

Operating Temperature Range −40°C to +85°C

Storage Temperature Range −65°C to +150°C

Power Dissipation

Dual-In-Line 700 mW

Small Outline 500 mW

Operating V

CC

Range 3V to 15V

Absolute Maximum V

CC

18V

Lead Temperature

(Soldering, 10 seconds) 260°C

Symbol Parameter Conditions Min Typ Max Units

CMOS TO CMOS

V

IN(1)

Logical “1” Input Voltage VCC = 5V 3.5 V

VCC = 10V 8.0 V

V

IN(0)

Logical “0” Input Voltage VCC = 5V 1.5 V

VCC = 10V 2.0 V

V

OUT(1)

Logical “1” Output Voltage VCC = 5V, I O = −10 µA4.5 V

VCC = 10V, IO = −10 µA9.0 V

V

OUT(0)

Logical “0” Output Voltage VCC = 5V, I O = 10 µA0.5V

VCC = 10V, IO = 10 µA1.0V

I

OZ

3-STATE Output Current VCC = 10V, OD = V

IH

±10 µA

I

IN(1)

Logical “1” Input Current VCC = 15V, VIN = 15V 0.005 1.0 µA

I

IN(0)

Logical “0” Input Current VCC = 15V, VIN = 0V −1.0 −0.005 µA

I

CC

Supply Current VCC = 15V 0.05 300 µA

CMOS/LPTTL INTERFACE

V

IN(1)

Logical “1” Input Voltage VCC = 4.75V VCC − 1.5 V

V

IN(0)

Logical “0” Input Voltage VCC = 4.75V 0.8 V

V

OUT(1)

Logical “1” Output Voltage VCC = 4.75V, IO = −450 µAV

CC

− 0.4 V

VCC = 4.75V, IO = −2.2 mA 2.4 V

V

OUT(0)

Logical “0” Output Voltage VCC = 4.75V, IO = 2.2 mA 0.4 V

OUTPUT DRIVE (See Family Characteristics Data Sheet) (Short Circuit Current)

I

SOURCE

Output Source Current VCC = 5V, V

OUT

= 0V −14 −30 mA

(P-Channel) TA = 25°C

VCC = 10V, V

OUT

= 0V −36 −70 mA

TA = 25°C

I

SINK

Output Sink Current VCC = 5V, V

OUT

= V

CC

12 20 mA

(N-Channel) TA = 25°C

VCC = 10V, V

OUT

= V

CC

48 70 mA

TA = 25°C

Loading...

Loading...