October 1987

Revised January 1999

MM74C174 Hex D-Type Flip-Flop

© 1999 Fairchild Semiconductor Corporation DS005899.prf www.fairchildsemi.com

MM74C174

Hex D-Type Flip-Flop

General Description

The MM74C174 hex D-type flip-flop is a monolithic complementary MOS (CMOS ) integrated circuit constructed w ith

N- and P-channel enhancement transistors. All have a

direct clear input. Inform ation at the D inpu ts meeting the

setup time requirements is transferred to the Q outp uts on

the positive-going edge of the clock pulse. Cle ar is independent of clock and accomplished by a low level at the

clear input. All inputs are prot ected by diodes to V

CC

and

GND.

Features

■ Wide supply voltage range: 3.0V to 15V

■ Guaranteed noise margin: 1.0V

■ High noise immunity: 0.45 V

CC

(typ.)

■ Low power TTL compatibility:

Fan out of 2 driving 74L

Ordering Code:

Device also available in Tape and Reel. Specify by appendin g s uf f ix let t er “X” to the ordering code.

Connection Diagram

Pin Assignments for DIP and SOIC

Top View

Truth Table

Order Number Package Number Package Description

MM74C174M M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow

MM74C174N N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

Inputs Output

Clear Clock D Q

LXXL

H ↑ HH

H ↑ LL

HLXQ

www.fairchildsemi.com 2

MM74C174

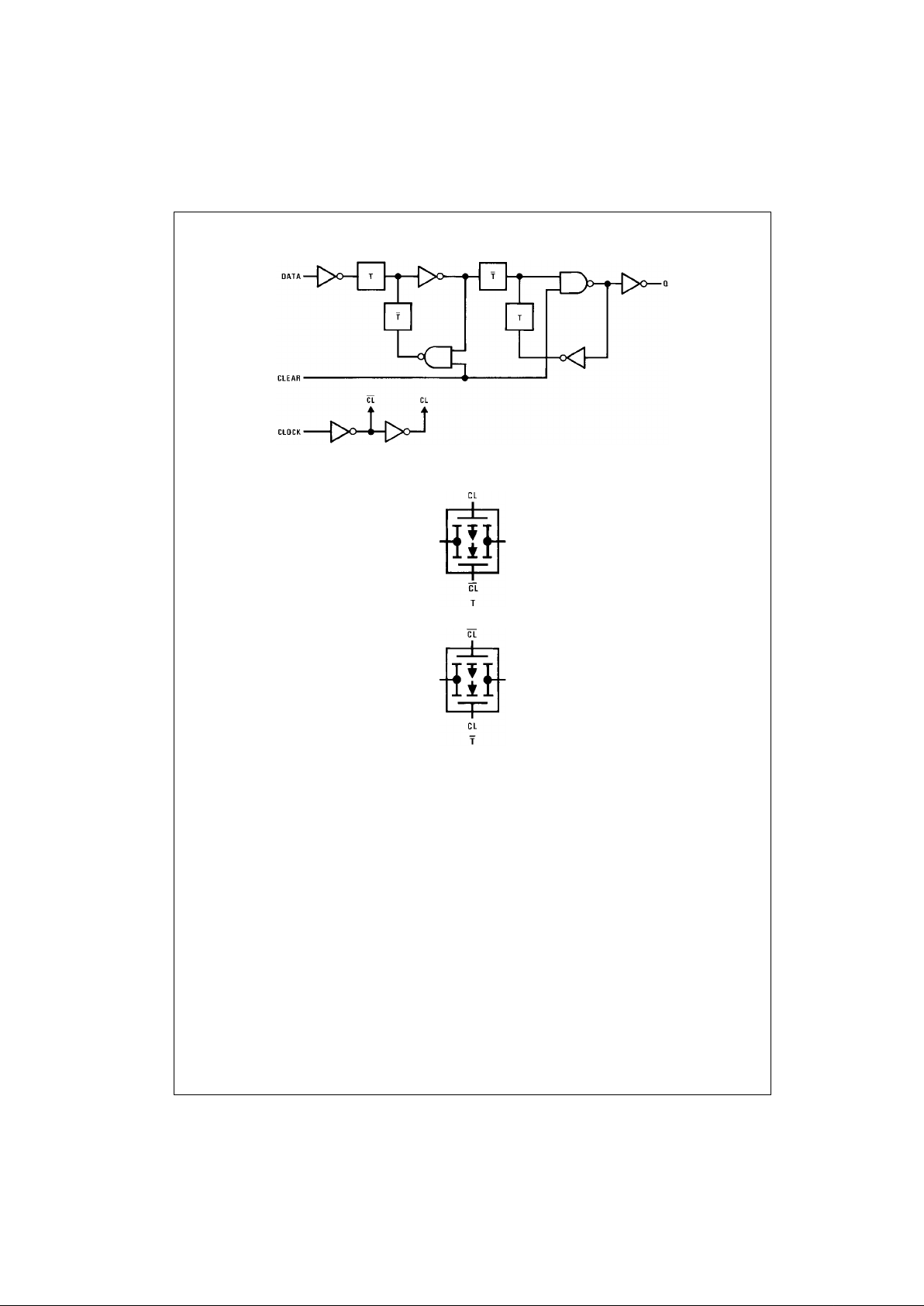

Logic Diagrams

Loading...

Loading...