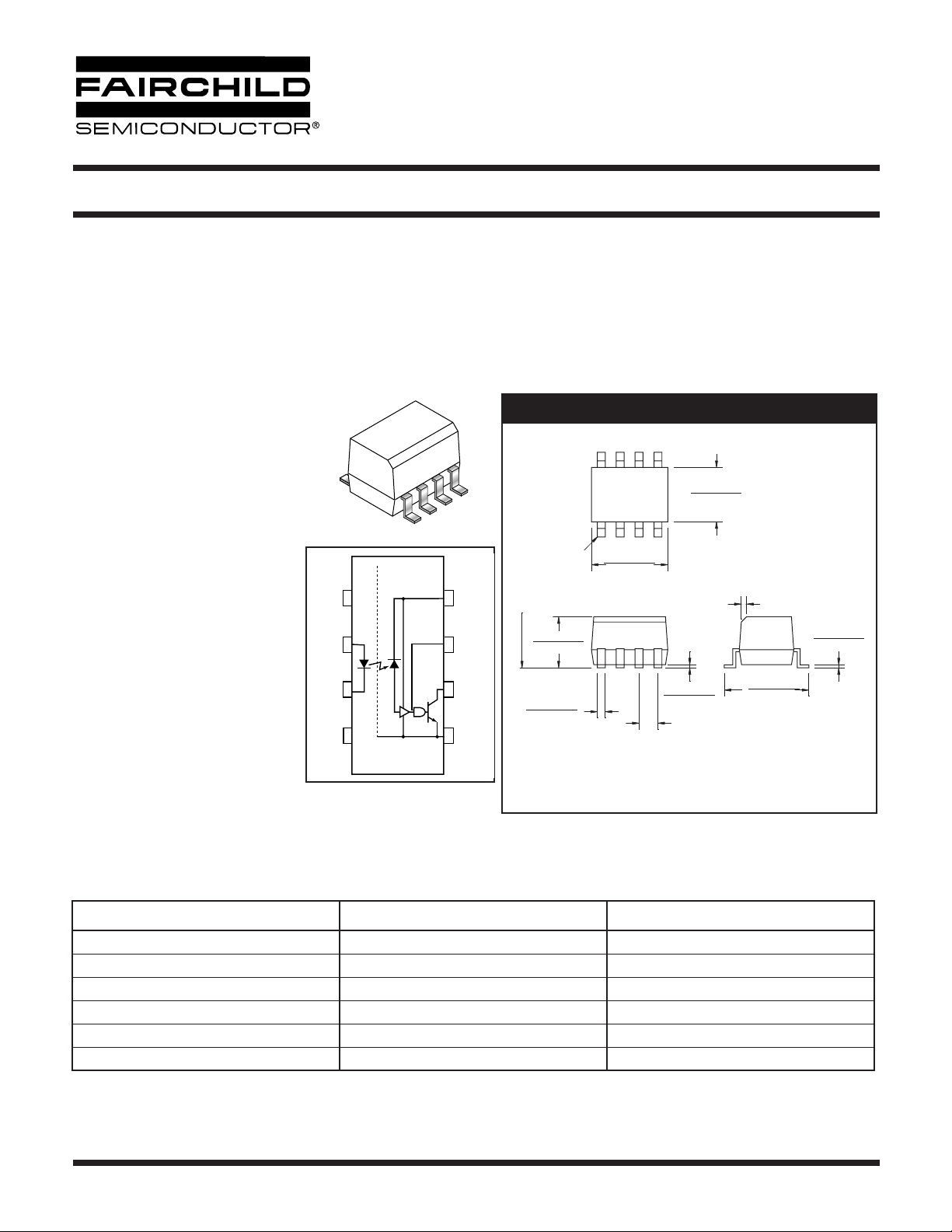

Fairchild Semiconductor HCPL-0601, HCPL-0600 Datasheet

Lead Coplanarity : 0.004 (0.10) MAX

0.202 (5.13)

Pin 1

0.019 (0.48)

0.182 (4.63)

0.021 (0.53)

0.011 (0.28)

0.050 (1.27)

TYP

0.244 (6.19)

0.224 (5.69)

0.143 (3.63)

0.123 (3.13)

0.008 (0.20)

0.003 (0.08)

0.010 (0.25)

0.006 (0.16)

SEATING PLANE

0.164 (4.16)

0.144 (3.66)

HIGH SPEED-10 MBit/s

LOGIC GATE OPTOCOUPLERS

HCPL-0600 HCPL-0601

DESCRIPTION

The HCPL-0600/0601optocouplers consist of a 870 nm AlGaAS LED, optically coupled to a very high speed integrated photodetector logic gate with a strobable output. The devices are housed in a compact small-outline package. This output features an

open collector, thereby permitting wired OR outputs. The coupled parameters are guaranteed over the temperature range of -40°C

to +85°C. A maximum input signal of 5 mA will provide a minimum output sink current of 13 mA (fan out of 8). An internal noise

shield provides superior common mode rejection of typically 10 kV/µs.

FEATURES

• Compact SO8 package

•Very high speed-10 MBit/s

• Superior CMR-10 kV/µs

•Fan-out of 8 over -40°C to +85°C

• Logic gate output

• Strobable output

• Wired OR-open collector

•U.L. recognized (File # E90700)

PACKAGE DIMENSIONS

APPLICATIONS

• Ground loop elimination

• LSTTL to TTL, LSTTL or

5-volt CMOS

• Line receiver, data transmission

• Data multiplexing

• Switching power supplies

• Pulse transformer replacement

• Computer-peripheral interface

N/C

1

+

2

V

F

_

3

N/C

4 5

Single-channel

circuit drawing

V

8

CC

V

7

E

V

6

O

GND

NOTE

All dimensions are in inches (millimeters)

TRUTH TABLE

(Positive Logic)

Input Enable Output

HHL

LHH

HLH

LLH

A 0.1 µF bypass capacitor must be connected between pins 8 and 5. (See note 1)

HNCL

LNCH

© 2003 Fairchild Semiconductor Corporation

Page 1 of 12

4/10/03

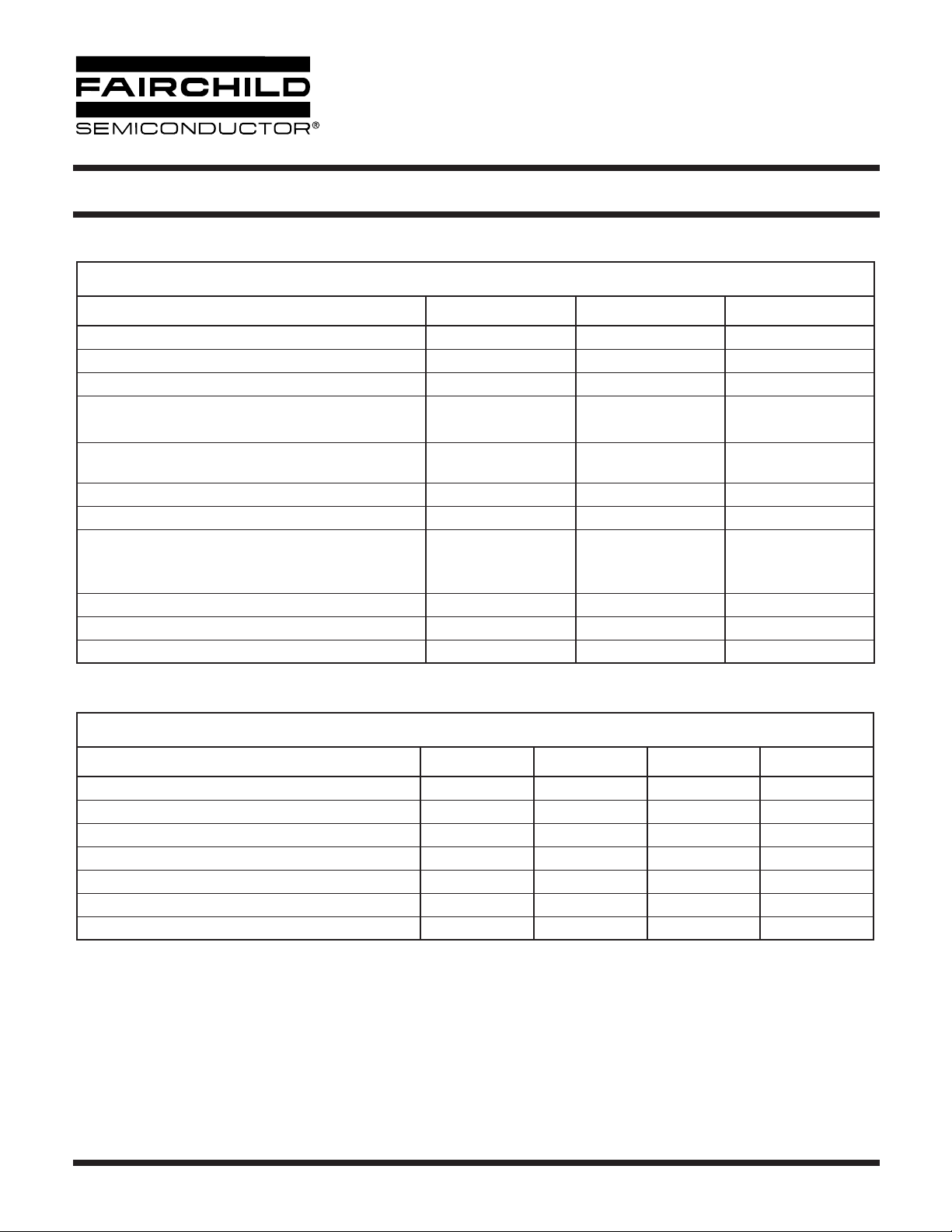

HIGH SPEED-10 MBit/s

LOGIC GATE OPTOCOUPLERS

HCPL-0600 HCPL-0601

ABSOLUTE MAXIMUM RATINGS

(No derating required up to 85°C)

Parameter Symbol Value Units

Storage Temperature T

Operating Temperature T

Lead Solder Temperature T

EMITTER

DC/Average Forward Input Current I

Enable Input Voltage

Not to exceed VCC by more than 500 mV

Reverse Input Voltage V

Power Dissipation P

DETECTOR

Supply Voltage

V

(1 minute max)

Output Current I

Output Voltage V

Collector Output Power Dissipation P

RECOMMENDED OPERATING CONDITIONS

STG

OPR

SOL

F

V

E

R

CC

O

O

O

-55 to +125 °C

-40 to +85 °C

260 for 10 sec °C

50 mA

5.5 V

5.0 V

I

45 mW

7.0 V

50 mA

7.0 V

85 mW

Parameter Symbol Min Max Units

Input Current, Low Level I

Input Current, High Level I

Supply Voltage, Output V

Enable Voltage, Low Level V

Enable Voltage, High Level V

Operating Temperature T

FL

FH

CC

EL

EH

A

0 250 µA

*6.3 15 mA

4.5 5.5 V

0 0.8 V

2.0 V

CC

V

-40 +85 °C

Fan Out (TTL load) N 8

*6.3 mA is a guard banded value which allows for at least 20% CTR degradation. Initial input current threshold value is 5.0 mA or

less

© 2003 Fairchild Semiconductor Corporation

Page 2 of 12

4/10/03

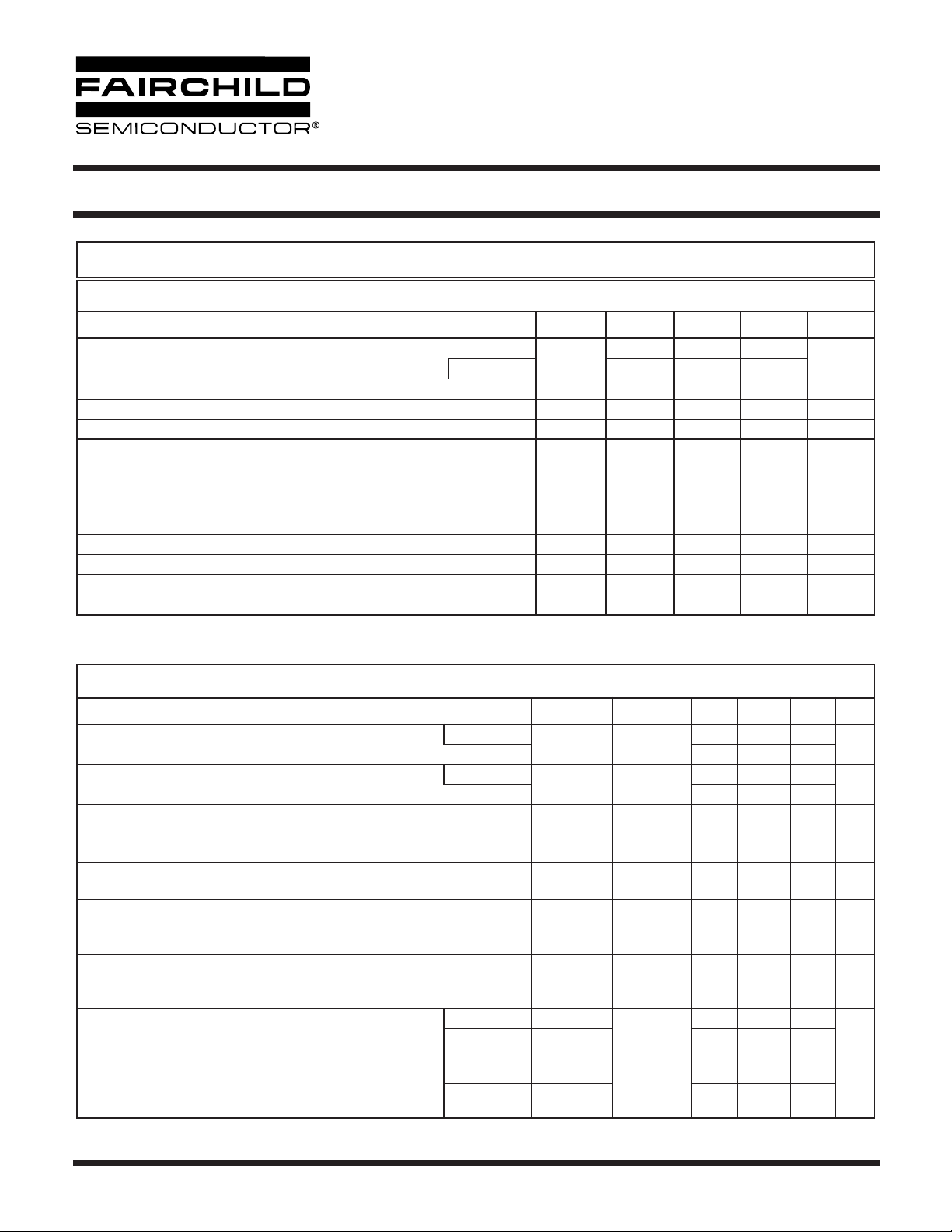

HIGH SPEED-10 MBit/s

LOGIC GATE OPTOCOUPLERS

HCPL-0600 HCPL-0601

ELECTRICAL CHARACTERISTICS

(T

= -40°C to +85°C Unless otherwise specified.)

A

INDIVIDUAL COMPONENT CHARACTERISTICS

Parameter Test Conditions Symbol Min Typ** Max Unit

EMITTER

Input Forward Voltage T

Input Reverse Breakdown Voltage (I

Input Capacitance (V

Input Diode Temperature Coefficient (I

= 10 mA)

(I

F

=25°C 1.75

A

= 10 µA) B

R

= 0, f = 1 MHz) C

F

= 10 mA) ∆ VF/ ∆ TA -1.4 mV/°C

F

V

F

VR

IN

5.0 V

60 pF

DETECTOR

High Level Supply Current

Low Level Supply Current

Low Level Enable Current (V

High Level Enable Current (V

High Level Enable Voltage (V

Low Level Enable Voltage (V

= 5.5 V, I

CC

SWITCHING CHARACTERISTICS

= 5.5 V, I

CC

(V

= 5.5 V, I

CC

= 5.5 V, V

CC

= 5.5 V, V

CC

= 5.5 V, I

CC

= 10 mA) (Note 2) V

F

(T

= -40°C to +85°C, V

A

= 0 mA)

F

(V

= 0.5 V)

E

= 10 mA)

F

(V

= 0.5 V)

E

= 0.5 V) I

E

= 2.0 V) I

E

= 10 mA) V

F

= 5 V, I

CC

I

CCH

I

CCL

710mA

913mA

EL

EH

EH

EL

2.0 V

= 7.5 mA Unless otherwise specified.)

F

-0.8 -1.6 mA

-0.6 -1.6 mA

(V

AC Characteristics Test Conditions Device Symbol Min Typ Max Unit

Propagation Delay Time

to Output High Level

(R

Propagation Delay Time

to Output Low Level

(R

Pulse Width Distortion (R

Output Rise Time

(10-90%)

Output Fall Time

(90-10%)

Enable Propagation

Delay Time

to Output High Level

Enable Propagation

Delay Time

to Output Low Level

Common Mode

Tr ansient Immunity

(I

= 0 mA, V

F

(R

= 350 Ω ) (T

L

(at Output High Level)

Common Mode

Tr ansient Immunity

(I

(R

= 350Ω) (TA =25°C)

= 7.5 mA, VOL (Max.) = 0.8 V)

F

L

(at Output Low Level)

(Note 3) (T

= 350 Ω , C

L

= 15 pF) (Fig. 12) 100

L

(Note 4) (T

= 350 Ω , C

L

= 350 Ω , C

L

= 15 pF) (Fig. 12) 100

L

= 15 pF) (Fig. 12) All |T

L

(R

= 350 Ω , C

L

(Note 5) (Fig. 12)

= 350 Ω , C

(R

L

(Note 6) (Fig. 12)

(I

= 7.5 mA, V

F

(R

= 350 Ω , C

L

(Note 7) (Fig. 13)

(I

= 7.5 mA, V

F

(R

= 350 Ω , C

L

(Note 8) (Fig. 13)

=25°C)

A

(Min.) = 2.0 V)

OH

(Note 9)(Fig. 14)

(Note 10)(Fig. 14)

=25°C)

A

=25°C)

A

= 15 pF)

L

= 15 pF)

L

= 3.5 V)

EH

= 15 pF)

L

= 3.5 V)

EH

= 15 pF)

L

|V

| = 10 V HCPL-0600

CM

|V

| = 50 V HCPL-0601 5000 10,000

CM

| = 10 V HCPL-0600

|V

CM

|V

| = 50 V HCPL-0601 5000 10,000

CM

All T

All T

PHL

All t

All t

All t

All t

|CM

|CM

PLH

PHL

-T

r

f

ELH

EHL

H

H

20 45 75

25 45 75

|335ns

PLH

|

|

1.8

0.8 V

50 ns

12 ns

20 ns

20 ns

10,000

10,000

V

ns

ns

V/µs

V/µs

© 2003 Fairchild Semiconductor Corporation

Page 3 of 12

4/10/03

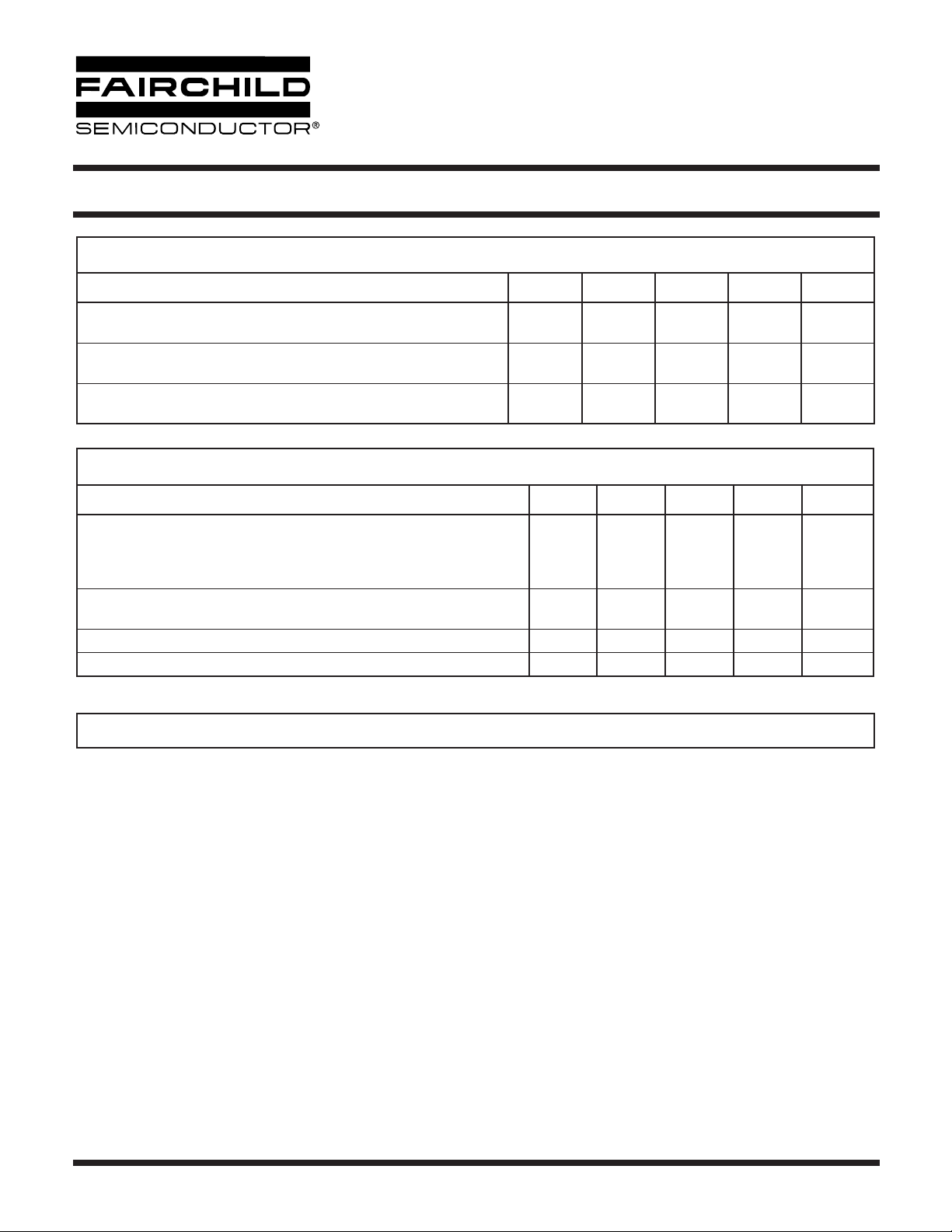

HIGH SPEED-10 MBit/s

LOGIC GATE OPTOCOUPLERS

HCPL-0600 HCPL-0601

TRANSFER CHARACTERISTICS (T

= -40°C to +85°C Unless otherwise specified.)

A

DC Characteristics Test Conditions Symbol Min Typ** Max Unit

= 5.5 V, VO = 5.5 V)

(V

High Level Output Current

Low Level Output Voltage

(I

= 250 µA, VE = 2.0 V) (Note 2)

F

(V

= 2.0 V, IOL = 13 mA) (Note 2)

E

Input Threshold Current

ISOLATION CHARACTERISTICS (T

CC

= 5.5 V, IF = 5 mA)

(V

CC

= 5.5 V, VO = 0.6 V,

(V

CC

V

= 2.0 V, IOL = 13 mA)

E

= -40°C to +85°C Unless otherwise specified.)

A

I

OH

V

OL

I

FT

100 µA

.35 0.6 V

35mA

Characteristics Test Conditions Symbol Min Typ** Max Unit

(Relative humidity = 45%)

Input-Output

Insulation Leakage Current

(T

= 25°C, t = 5 s)

A

(V

= 3000 VDC)

I-O

I

I-O

1.0* µA

(Note 11)

Withstand Insulation Test Voltage

Resistance (Input to Output) (V

Capacitance (Input to Output) (f = 1 MHz) (Note 11) C

(RH < 50%, TA = 25°C)

(Note 11) ( t = 1 min.)

= 500 V) (Note 11) R

I-O

V

ISO

I-O

I-O

2500 V

12

10

0.6 pF

** All typical values are at VCC = 5 V, TA = 25°C

RMS

Ω

NOTES

1. The V

tantalum capacitor with good high frequency characteristic and should be connected as close as possible to the package V

and GND pins of each device.

2. Enable Input - No pull up resistor required as the device has an internal pull up resistor.

3. t

PLH

1.5V level on the LOW to HIGH transition of the output voltage pulse.

4. t

PHL

1.5V level on the HIGH to LOW transition of the output voltage pulse.

5. t

r

6. t

f

7. t

ELH

to the 1.5V level on the LOW to HIGH transition of the output voltage pulse.

8. t

EHL

to the 1.5V level on the HIGH to LOW transition of the output voltage pulse.

9. CM

V

10. CM

(i.e., V

11. Device considered a two-terminal device: Pins 1,2,3 and 4 shorted together, and Pins 5,6,7 and 8 shorted together.

© 2003 Fairchild Semiconductor Corporation

supply to each optoisolator must be bypassed by a 0.1µF capacitor or larger. This can be either a ceramic or solid

CC

- Propagation delay is measured from the 3.75 mA level on the HIGH to LOW transition of the input current pulse to the

- Propagation delay is measured from the 3.75 mA level on the LOW to HIGH transition of the input current pulse to the

- Rise time is measured from the 90% to the 10% levels on the LOW to HIGH transition of the output pulse.

- Fall time is measured from the 10% to the 90% levels on the HIGH to LOW transition of the output pulse.

- Enable input propagation delay is measured from the 1.5V level on the HIGH to LOW transition of the input voltage pulse

- Enable input propagation delay is measured from the 1.5V level on the LOW to HIGH transition of the input voltage pulse

- The maximum tolerable rate of rise of the common mode voltage to ensure the output will remain in the high state (i.e.,

H

> 2.0 V). Measured in volts per microsecond (V/µs).

OUT

- The maximum tolerable rate of fall of the common mode voltage to ensure the output will remain in the low output state

L

< 0.8 V). Measured in volts per microsecond (V/µs).

OUT

Page 4 of 12

CC

4/10/03

Loading...

Loading...