Page 1

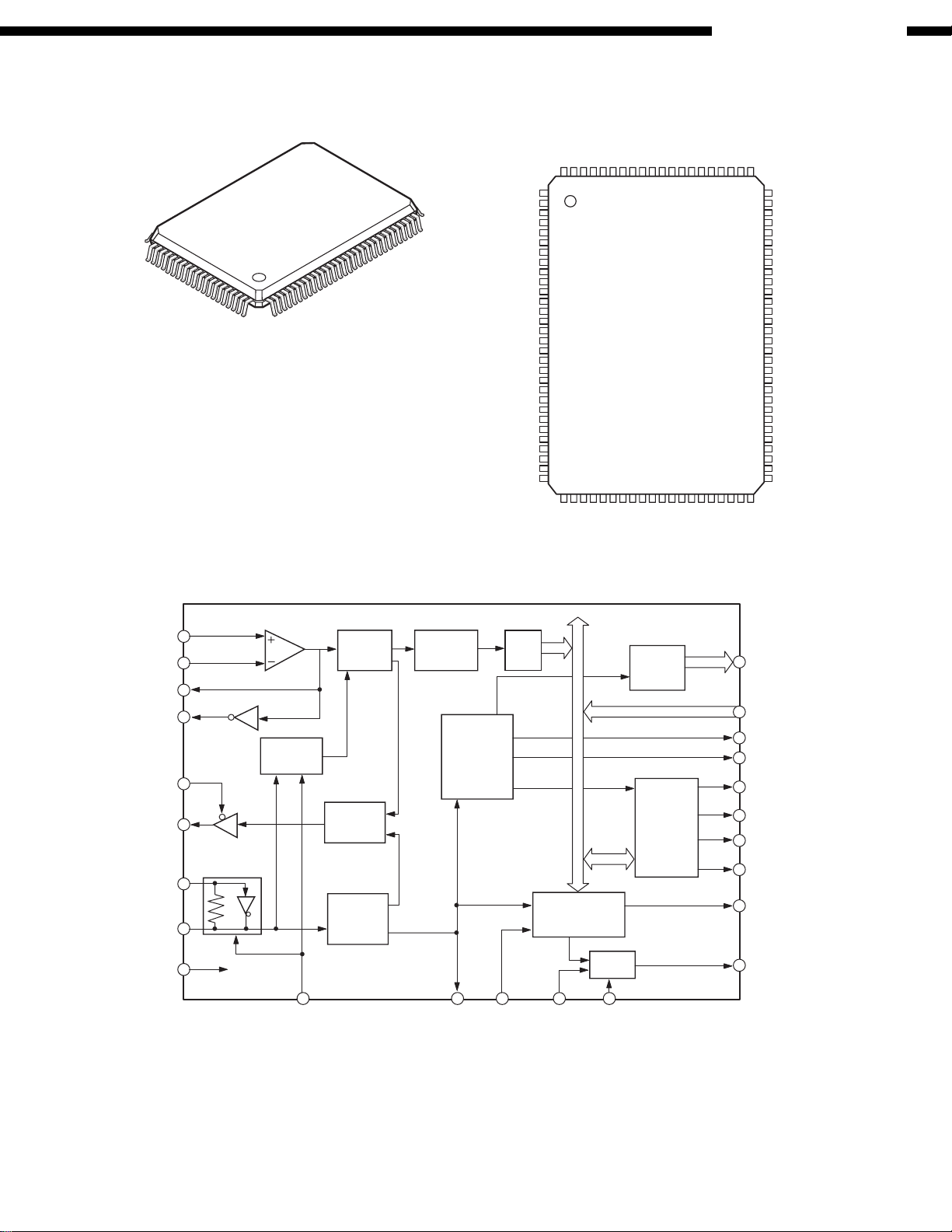

SERVICE MANUAL

Hi-Fi Component

MODEL

MODEL

AVC-A1D

AVR-5700

AV SURROUND AMPLIFIER / RECEIVER

— TABLE OF CONTENTS —

SAFETY PRECAUTIONS......................................................................................................................................................2

SPECIFICATIONS .................................................................................................................................................................2

WIRE ARRANGEMENT ........................................................................................................................................................3

DISASSEMBLY ................................................................................................................................................................ 4~7

LEVEL DIAGRAMS ............................................................................................................................................................8,9

CLOCK FLOW & WAVE FORM IN DIGITAL BLOCK ....................................................................................................10,11

ADJUSTMENT.............................................................................................................................................................. 12~14

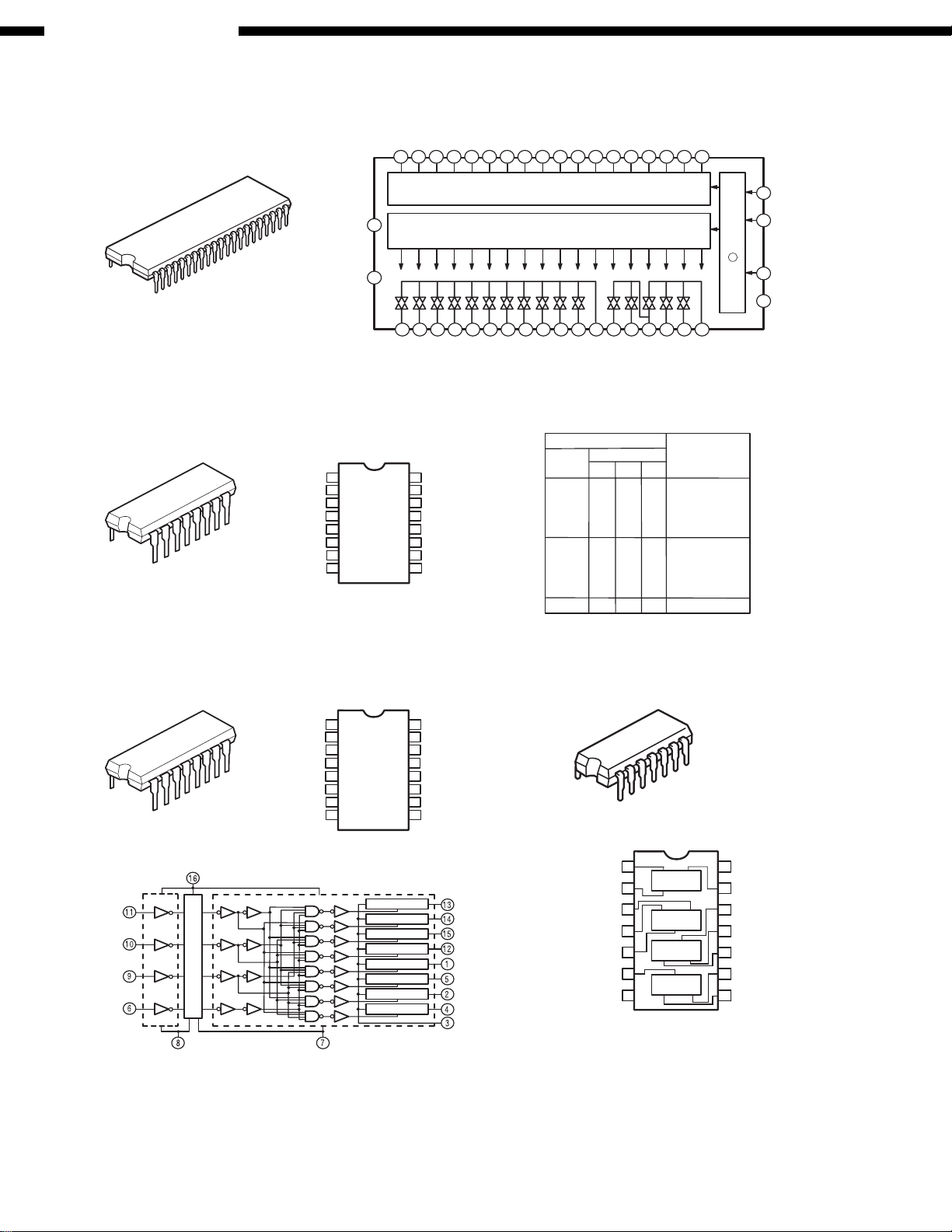

SEMICONDUCTORS ................................................................................................................................................... 15~39

PRINTED WIRING BOARDS ....................................................................................................................................... 40~47

NOTE FOR PARTS LIST.....................................................................................................................................................48

PARTS LIST OF P.W.B. UNIT ASS'Y .......................................................................................................................... 48~70

ADDENDUM PARTS LIST OF P.W.B. UNIT ASS'Y .................................................................................................... 71~75

EXPLODED VIEW ...............................................................................................................................................................76

PARTS LIST OF EXPLODED VIEW ...................................................................................................................................77

ADDENDUM PARTS LIST OF EXPLODED VIEW .............................................................................................................78

BLOCK DIAGRAM ...............................................................................................................................................................79

WIRING DIAGRAM..............................................................................................................................................................80

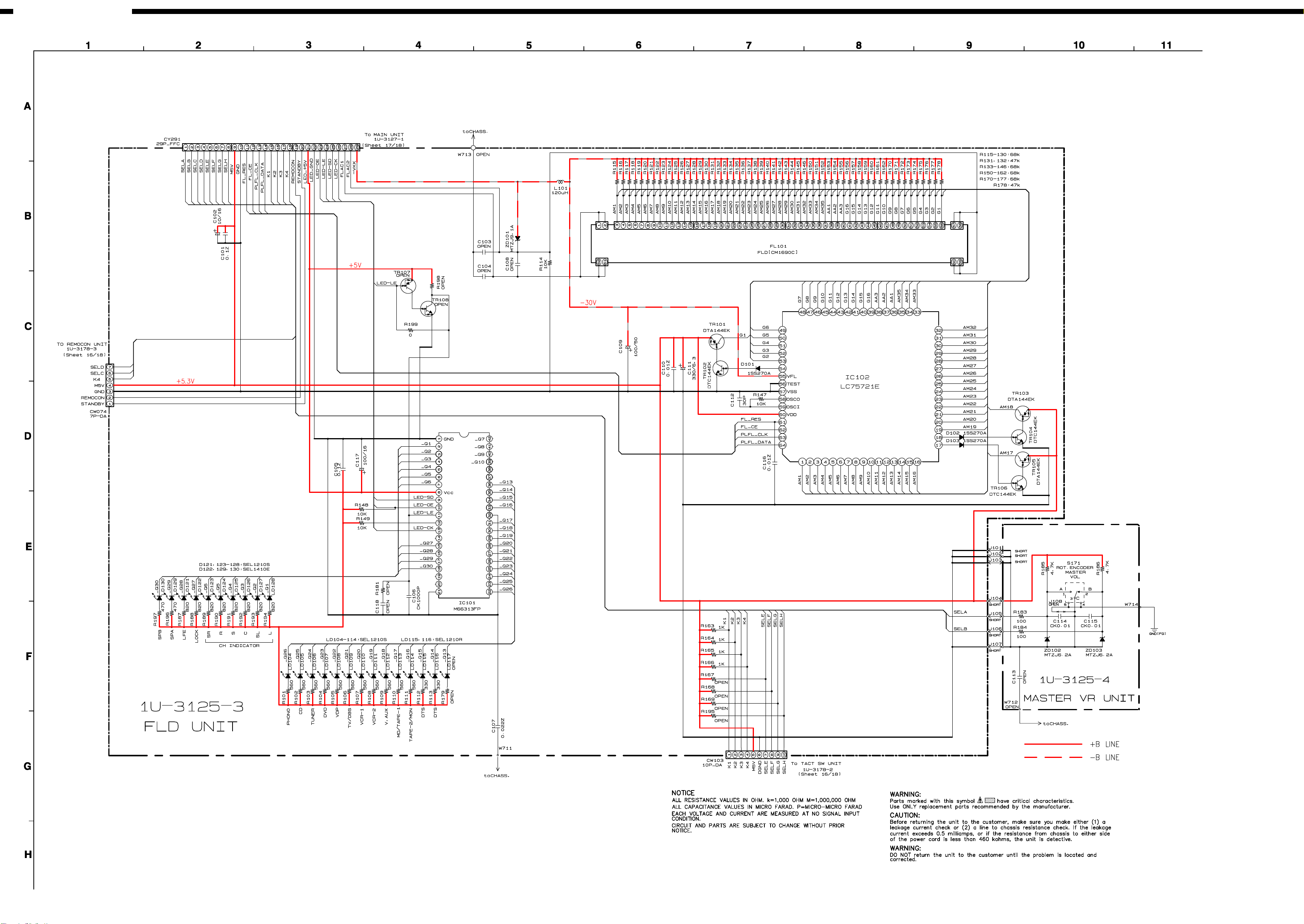

SCHEMATIC DIAGRAMS ............................................................................................................................................ 81~97

●●

● Some illustrations using in this service manual are slightly different from the actual set.

●●

Page 2

AVC-A1D/AVR-5700

SAFETY PRECAUTIONS

The following check should be performed for the continued protection of the customer and service technician.

LEAKAGE CURRENT CHECK

Before returning the unit to the customer, mak e sure y ou make either (1) a leakage current check or (2) a line to chassis

resistance check. If the leakage current exceeds 0.5 milliamps, or if the resistance from chassis to either side of the

power cord is less than 460 kohms, the unit is defective.

SPECIFICATIONS

Audio Section

(Power Amplifier)

Rated output: Front: 140 W + 140 W (8 Ω/ohms, 20 Hz ~ 20 kHz with 0.05 % T.H.D.)

Dynamic Power: 190 W × 2 ch (8 Ω/ohms), 310 W × 2 ch (4 Ω/ohms), 390 W × 2 ch (2 Ω/ohms)

Output terminals: Front/Center: 6 to 16 Ω/ohms

(Analog)

LINE input-PRE OUT

Input sensitivity/Input impedance: 200 mV/47 kΩ/kohms

Frequency response: 10 Hz ~ 100 kHz: +0, −3 dB (Direct mode)

S/N ratio: 105 dB (IHF-A weighted, Direct mode)

Total harmonic distortion: 0.005 % (20 Hz ~ 20 kHz, Direct mode)

Rated/Maximum output: 1.2 V/8 V

PHONO input-REC OUT

Input sensitivity/Input impedance: 2.5 mV/47 kΩ/kohms

RIAA deviation: ±1 dB (20 Hz ~ 20 kHz)

S/N ratio: 74 dB (IHF-A weighted, with 5 mV input)

Total harmonic distortion: 0.03 % (1 kHz, 3 V)

Rated/Maximum output: 150 mV/8 V

Maximum headphones output: 284 mW (8 Ω/ohms)

(Digital)

D/A output

Rated output: 2 V (at 0 dB playback)

Total harmonic distortion: 0.005 % (1 kHz, at 0 dB)

S/N ratio: 105 dB (IHF-A weighted)

Dynamic range: 96 dB

Digital input: Format-Digital audio interface

Video Section

(Standard Video Jacks)

Input/output level and impedance: 1 Vp-p, 75 Ω/ohms

Frequency response: 5 Hz ~ 10 MHz: +0, −3 dB

(S-Video Jack)

Input/output level and impedance: 1 Vp-p, 75 Ω/ohms (Y signal/luminance)

Frequency response: 5 Hz ~ 10 MHz: +0, −3 dB

(Video Comp. Jack)

Input/output level and impedance: 1 Vp-p, 75 Ω/ohms (Y signal/luminance)

Frequency response: 5 Hz ~ 20MHz: +0, −3 dB

Tuner section (AVR-5700 only)

Receiving range: 87.50 MHz ~ 107.90 MHz 520 kHz ~ 1710 kHz

Usable sensitivity: 1.0 µV (11.2 dBf)

50 dB quieting sensitivity: MONO: 1.6 µV (15.3 dBf)

S/N ratio: MONO: 80 dB (IHF-A weighted)

Total harmonic distortion: MONO: 0.15 % (1 kHz)

General

Power supply: AC230 V, 50 Hz (Europe & Asia models)

Power Consumption: 11 A

Maximum external dimensions: 434 (W) × 181 (H) × 494 (D) mm (17-3/32″ × 7-1/8″ × 19-29/64″)

Weight: 21.5 kg (47 lbs)

Remote control unit (RC-853)

Batteries: R6P/AA Type (two batteries)

External dimensions: 70(W) × 215 (H) × 24 (D) mm (2-3/4″ × 8-15/32″ × 15/16″)

Weight: 200 g (Approx. 7 oz) (including batteries)

2

Surround: 140 W × 5 ch (6 Ω/ohms, 1 kHz with 0.7 % T.H.D.)

Surround: A or B 6 to 16 Ω/ohms, A + B 12 to 16 Ω/ohms

0.286 Vp-p, 75 Ω/ohms (C signal/chrominance)

0.7 Vp-p, 75 Ω/ohms (Cb signal/blue)

0.7 Vp-p, 75 Ω/ohms (Cr signal/red)

[FM] (note: µV at 75 Ω/ohms, 0 dBf = 1 × 10

STEREO: 23 µV (38.5 dBf)

STEREO: 75 dB (IHF-A weighted)

STEREO: 0.3 % (1 kHz)

AC120 V, 60 Hz (U.S.A. / Canada & Taiwan R.O.C. models)

170 W + 170 W (8 Ω/ohms, 1 kHz with 0.7 % T.H.D.)

-15

W) [AM]

Page 3

AVC-A1D/AVR-5700

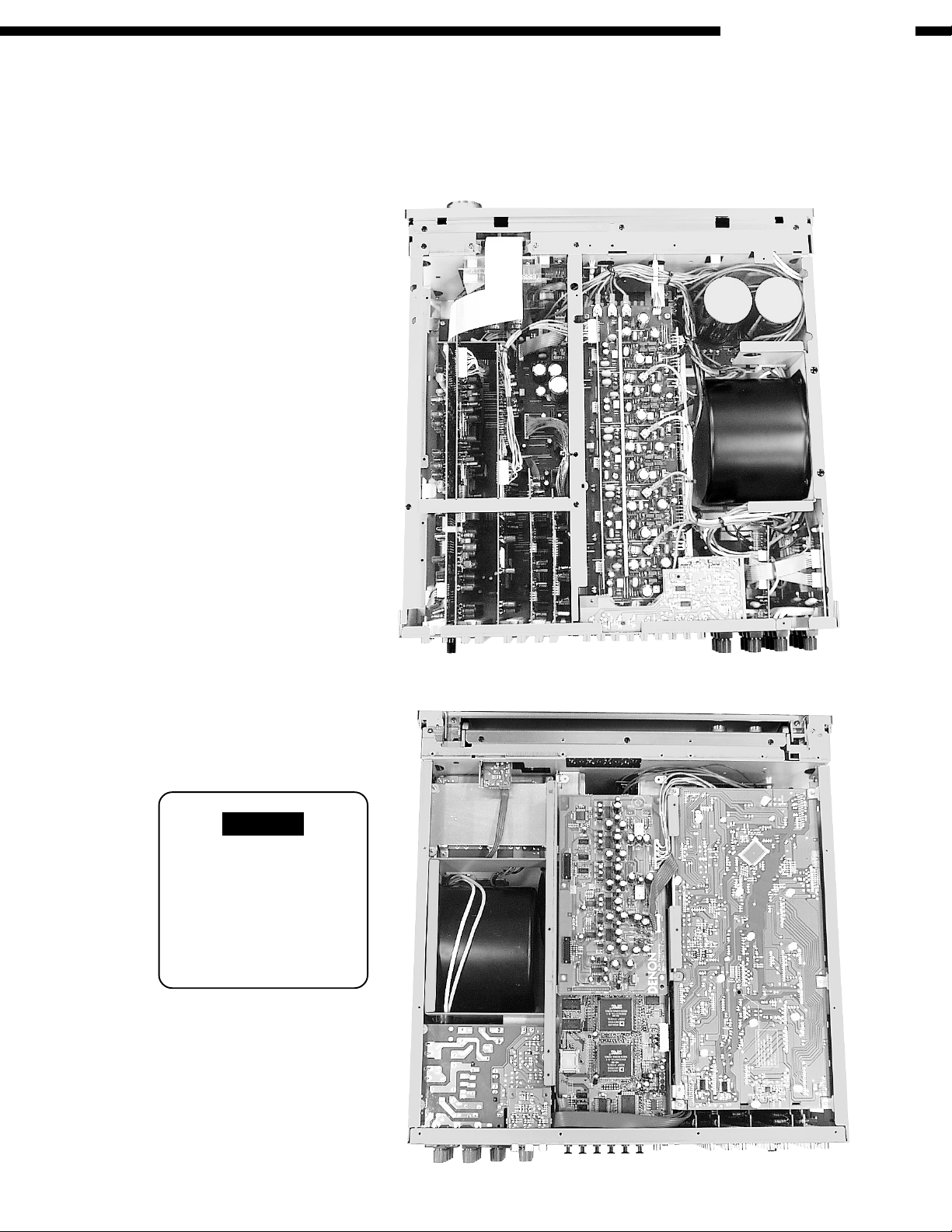

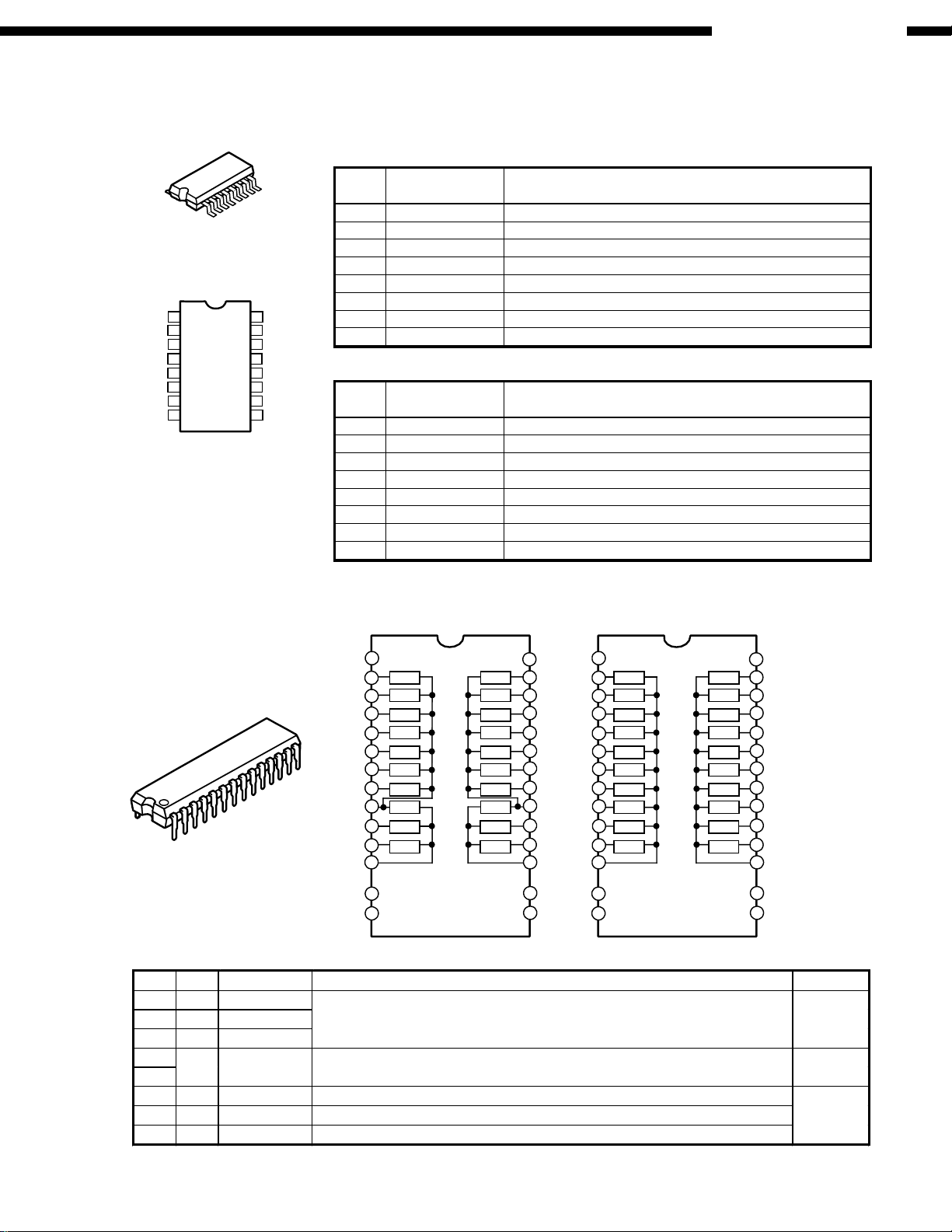

WIRE ARRANGEMENT

If wire bundles are untied or moved to perform adjustment or parts replacement etc.,be sure to rearrange them neatly as they

were originally bundled or placed afterward.

Otherwise, incorrect arrangement can be a cause of noise generation.

Wire arrangement viewed from the top

Wire arrangement viewed from the bottom.

CAUTION

Take care in case of the unit is

placed in the bottom down

position with its cover removed,

as the capacitors on D/A P.W.B.

and holders on Main P.W.B. are

come to be protruded from the

bottom level.

3

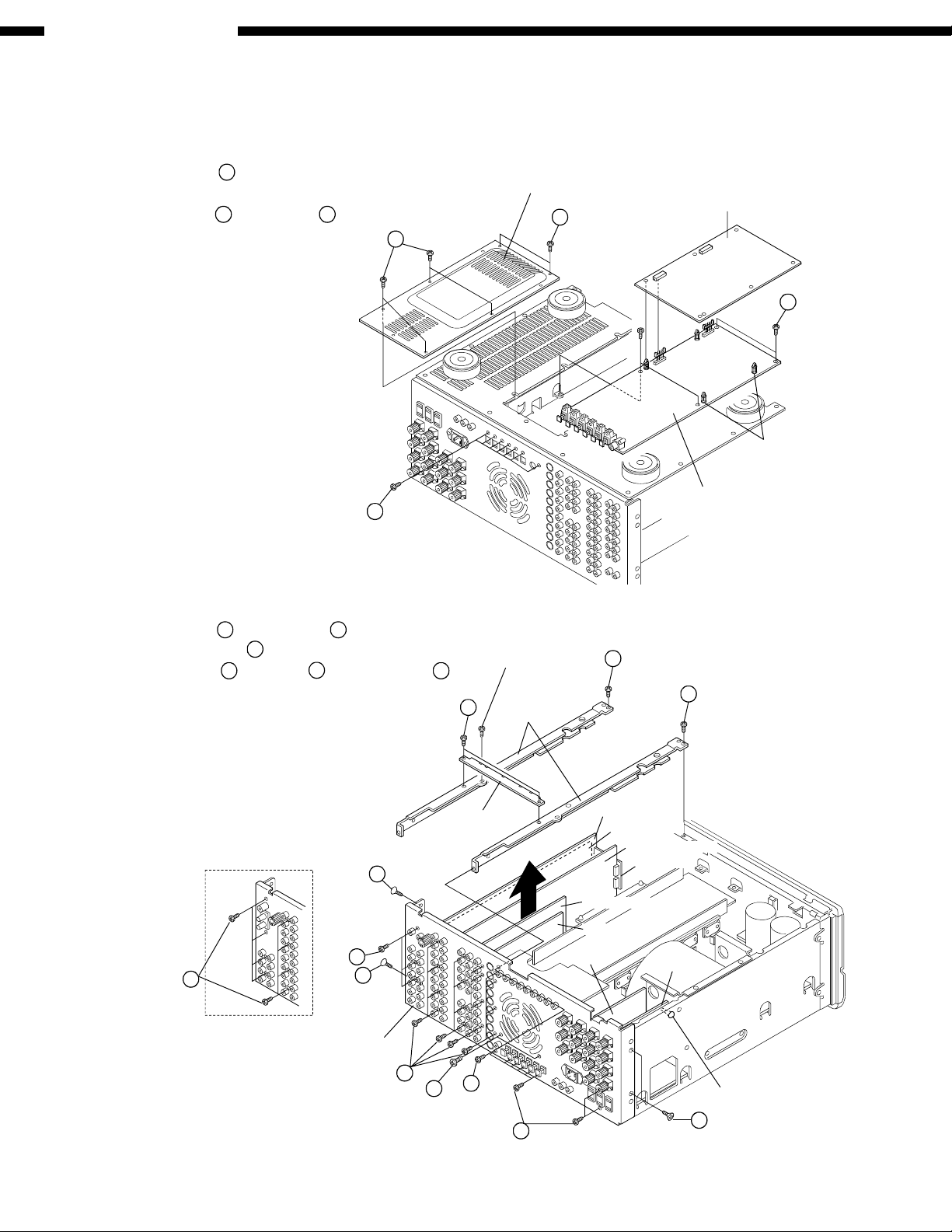

Page 4

AVC-A1D/AVR-5700

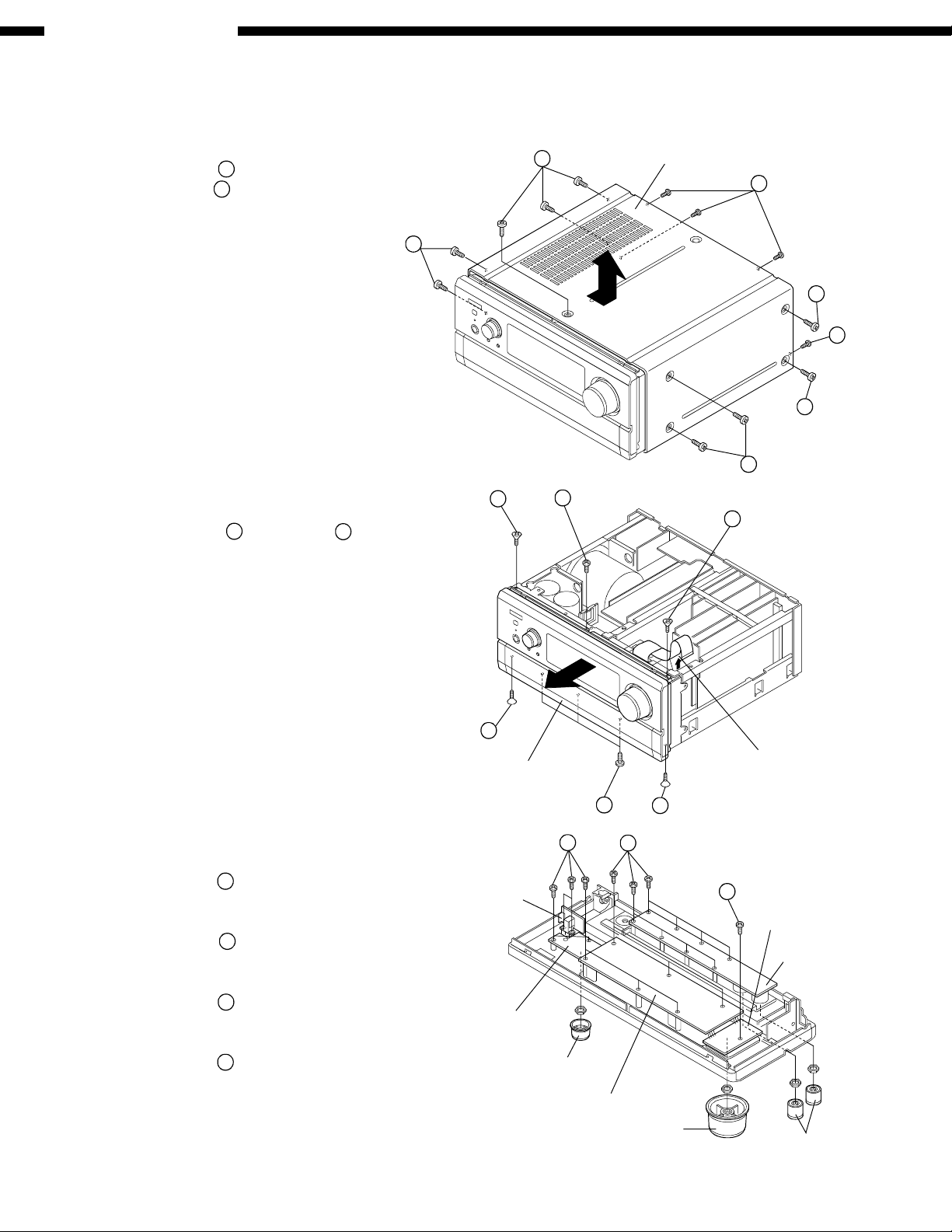

DISASSEMBLY

( Follow the procedure below in reverse order when reassembling )

Top Cover

(1) Remove 9 screws on both sides and on the top.

(2) Remove 4 screws on the rear and detach the top cover

by sliding to the arrow direction.

Front Panel

(1) Disconnect the FFC from its connector.

(2) Remove 4 screws and 4 screws fixing the front

panel at its top and bottom edges, then detach it to the

arrow direction.

1

2

1

2

3

1

3

2

Top Cover

2

1

2

1

1

3

P.W.B.s on Front Panel

(1) FLD, Master VR P.W.B.

Remove 7 screws after taking off the nut and knob for

the master volume.

(2) Tact SW P.W.B.

Remove 8 screws after taking off the nuts and knobs

for the tone volumes.

(3) Remo-con. P.W.B.

Remove 2 screws after taking off the nut and knob for

the input selector.

(4) Power SW P.W.B.

Remove 2 screws .

5

5

5

5

3

Front Panel

Power SW

P.W.B.

Remo-con.

P.W.B.

Input Selector Knob

2

5

FLD P.W.B.

Master VR Knob

5

FFC Cable

3

5

Master VR

P.W.B.

Tact SW

P.W.B.

Tone Knob

4

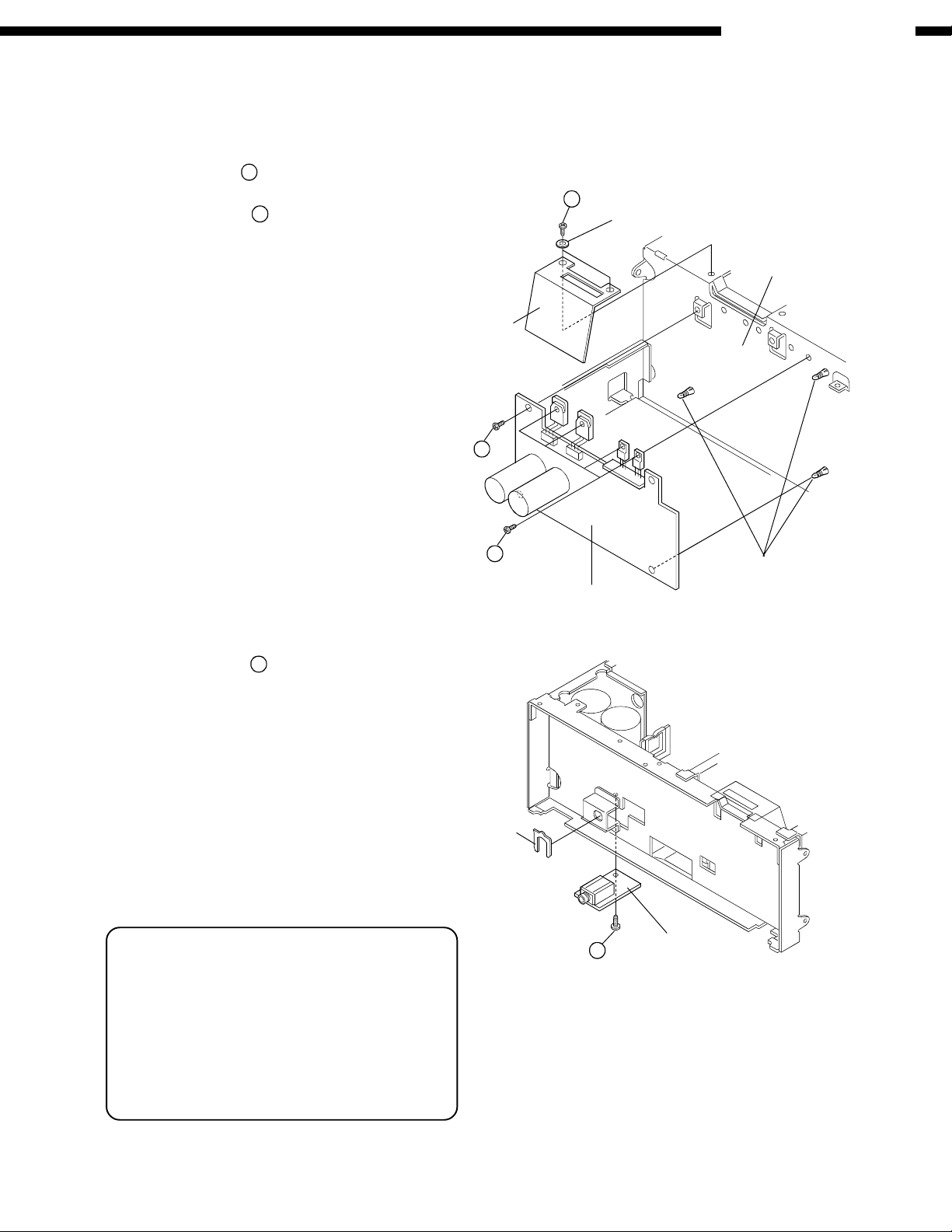

Page 5

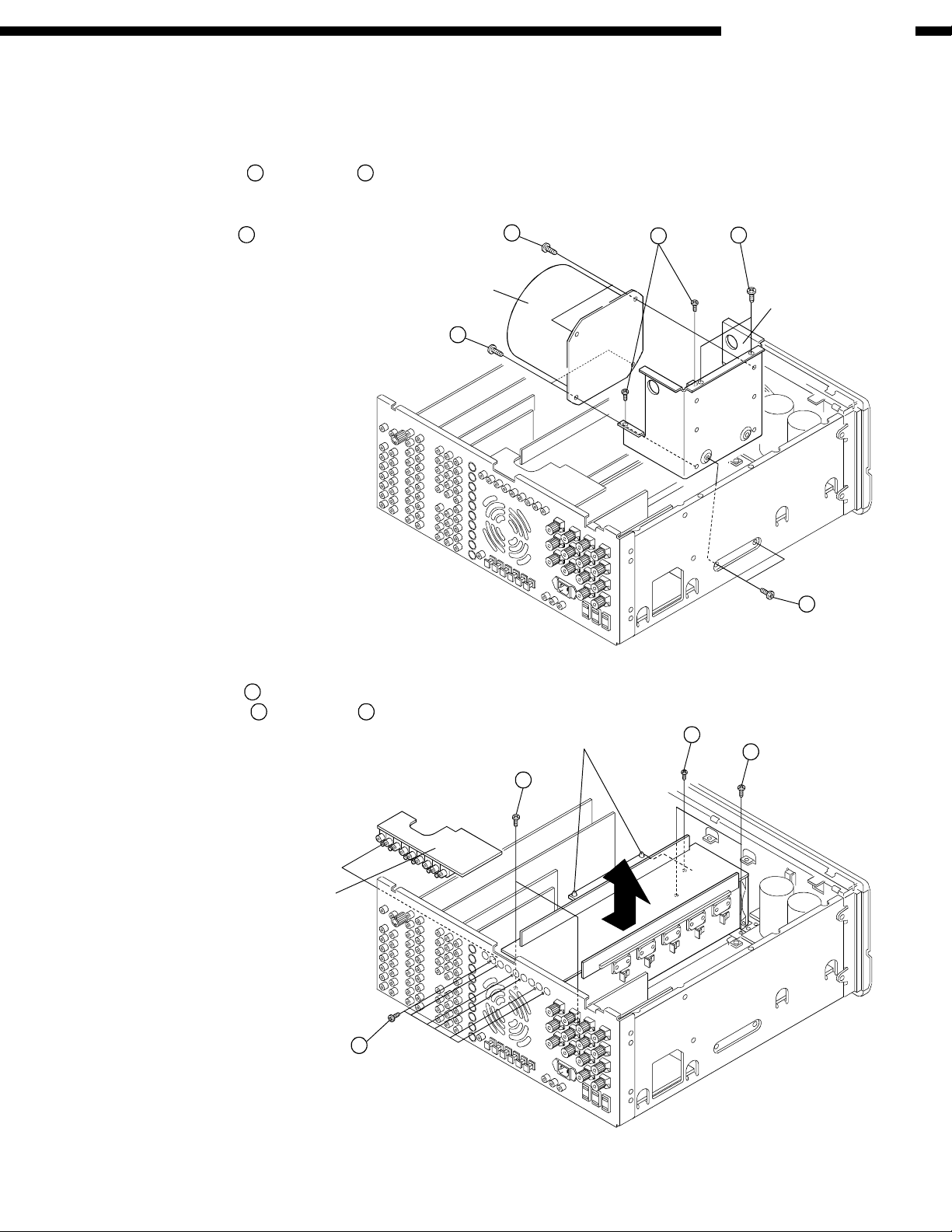

Power Trans.

AVC-A1D/AVR-5700

(1) Remove 4 screws and 2 screws fixing the trans.

bracket to the chassis.

(2) Pull out the power trans. upward.

(3) Remove 4 screws fixing the power trans. to the bracket.

5

5

2

Power Trans.

5

5

2

5

Trans. Bracket

5

Power Radiator

(1) Remove 6 screws to detach the comp. video P.W.B.

(2) Remove 4 screws and 1 screw , and release 2

P.W.B. holders, then pull out the radiator sub-ass’y in the

arrow direction.

6

7 8

Comp. Video P.W.B.

6

P.W.B. Holder

7

8

7

5

Page 6

AVC-A1D/AVR-5700

DSP, D/A P.W.B.

(1) Remove 6 screws to detach the D/A cover.

(2) Release 4 P.W.B. holders, and detach the D/A P.W.B.

(3) Remove 7 screws and 4 screws to detach the DSP

P.W.B.

2

6 4

D/A Cover

D/A P.W.B.

2

2

4

P.W.B. Holder

6

P.W.B.s on Back Panel

(1) Remove 1 screw (C) and 3 screws (D) fixing 2 support

brackets,and 2 screws (D) fixing P.W.B. support.

(2) Remove 3 screws (C), 2 screws (E), and 27 screws (F)

from the back panel.

(3) Detach the back panel after removing P.W.B. holder.

(4) Pull up each P.W.B. in the arrow direction.

3 4

4

3

5

AVR-5700 only

3

6

P.W.B.

Support

AVR-5700 only

Support

4

Bracket

DSP P.W.B.

4

4

Audio In P.W.B.

Ext. In VR P.W.B.

Tone Pre-out P.W.B.

Connect P.W.B.

C-video P.W.B.

S-video P.W.B.

6

6

3

SP1 P.W.B.

SP2 P.W.B.

Back

Panel

6

4

5

6

P.W.B. Holder

3

6

Page 7

Pre-reg. P.W.B.

(1) Remove 2 screws (G) to detach the washers and insulation

sheet.

(2) Remove 5 screws (I) fixing the Pre-reg. P.W.B. and

transistors.

(3) Detach the Pre-reg. P.W.B. after releasing 3 P.W.B.

holders.

7

9

Insulation Sheet

AVC-A1D/AVR-5700

7

Washer

Front Chassis

9

H/P P.W.B.

(1) Remove the bottom cover.

(2) Remove the screw (J) and snap plate to detach the H/P

P.W.B.

10

Snap Plate

CAUTION:

& Do not detach the back panel when placing the unit

other than normal position for servicing.

& Be careful not to give any stress when the unit is

placed in the bottom down position with its cover

removed, as the capacitors on D/A P.W.B. (1U-3179-

2) and holders on Main P.W.B. (1U-3127-1) are come

to be protruded from the bottom level.

9

Pre-reg. P.W.B.

10

H/P P.W.B.

P.W.B.Holder

7

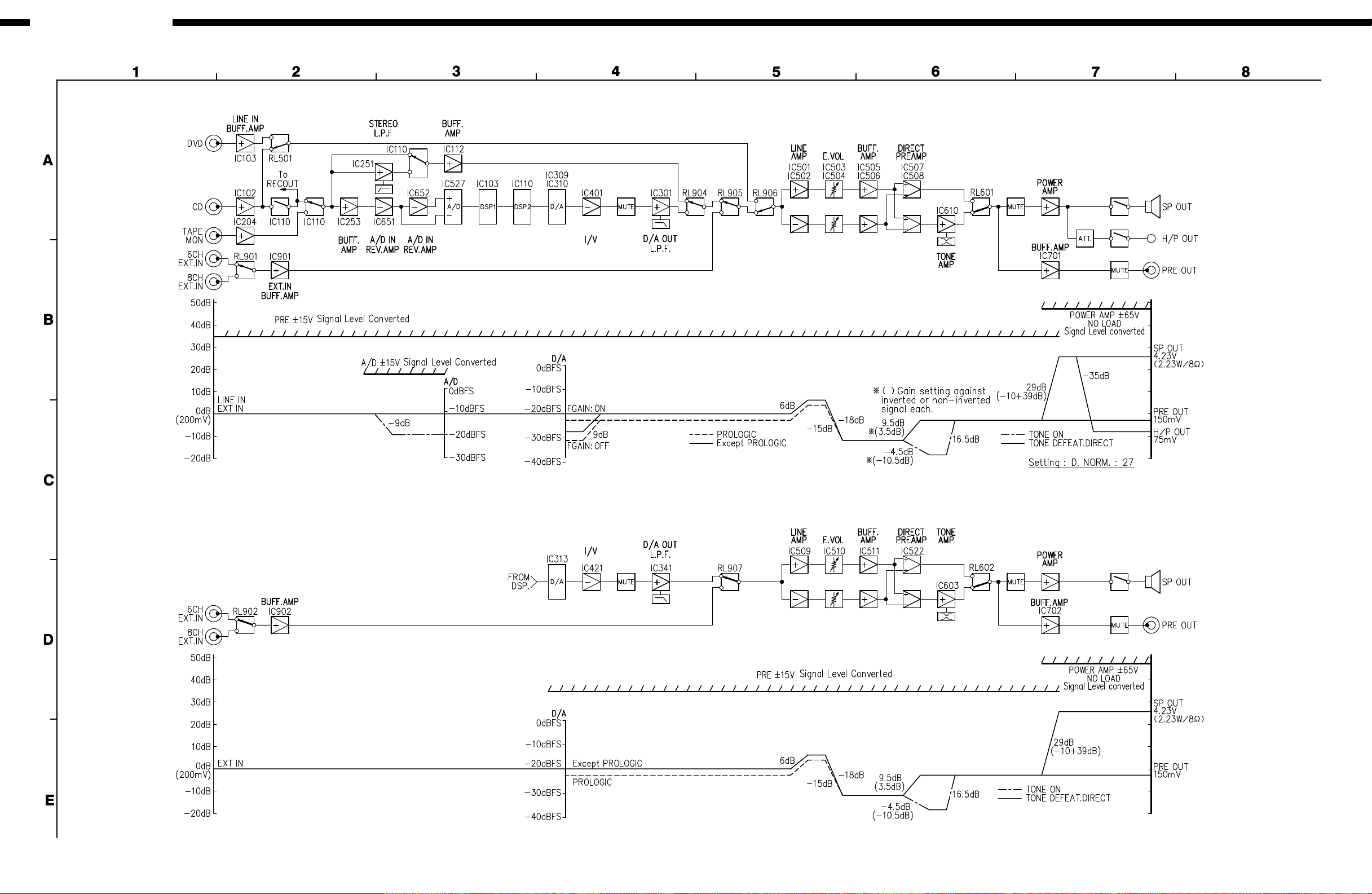

Page 8

AVC-A1D/AVR-5700

LEVEL DIAGRAMS

FRONT ch

CENTER ch

8

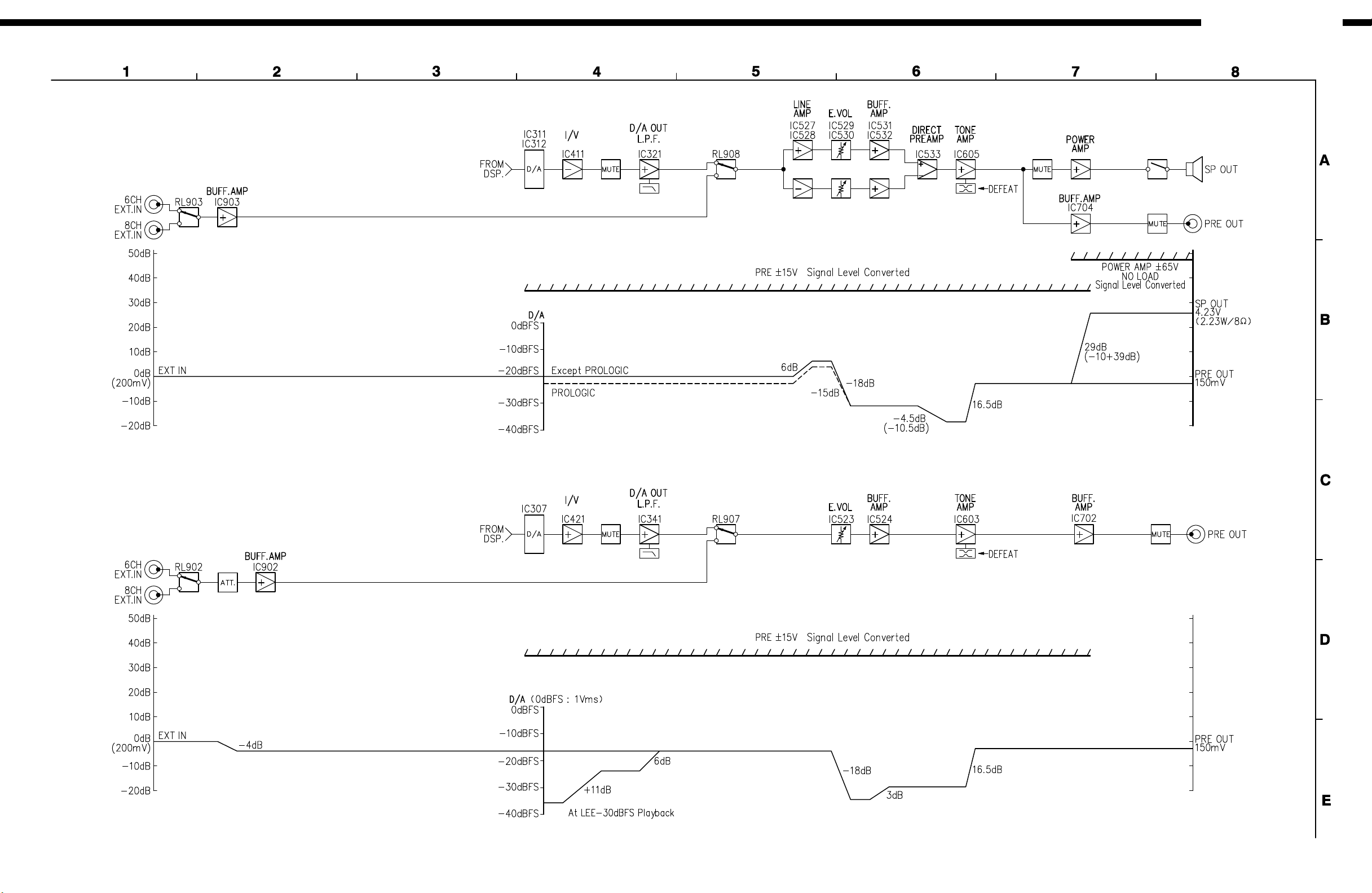

Page 9

AVC-A1D/AVR-5700

SURROUND ch

SUB. WOOFER ch

9

Page 10

AVC-A1D/AVR-5700

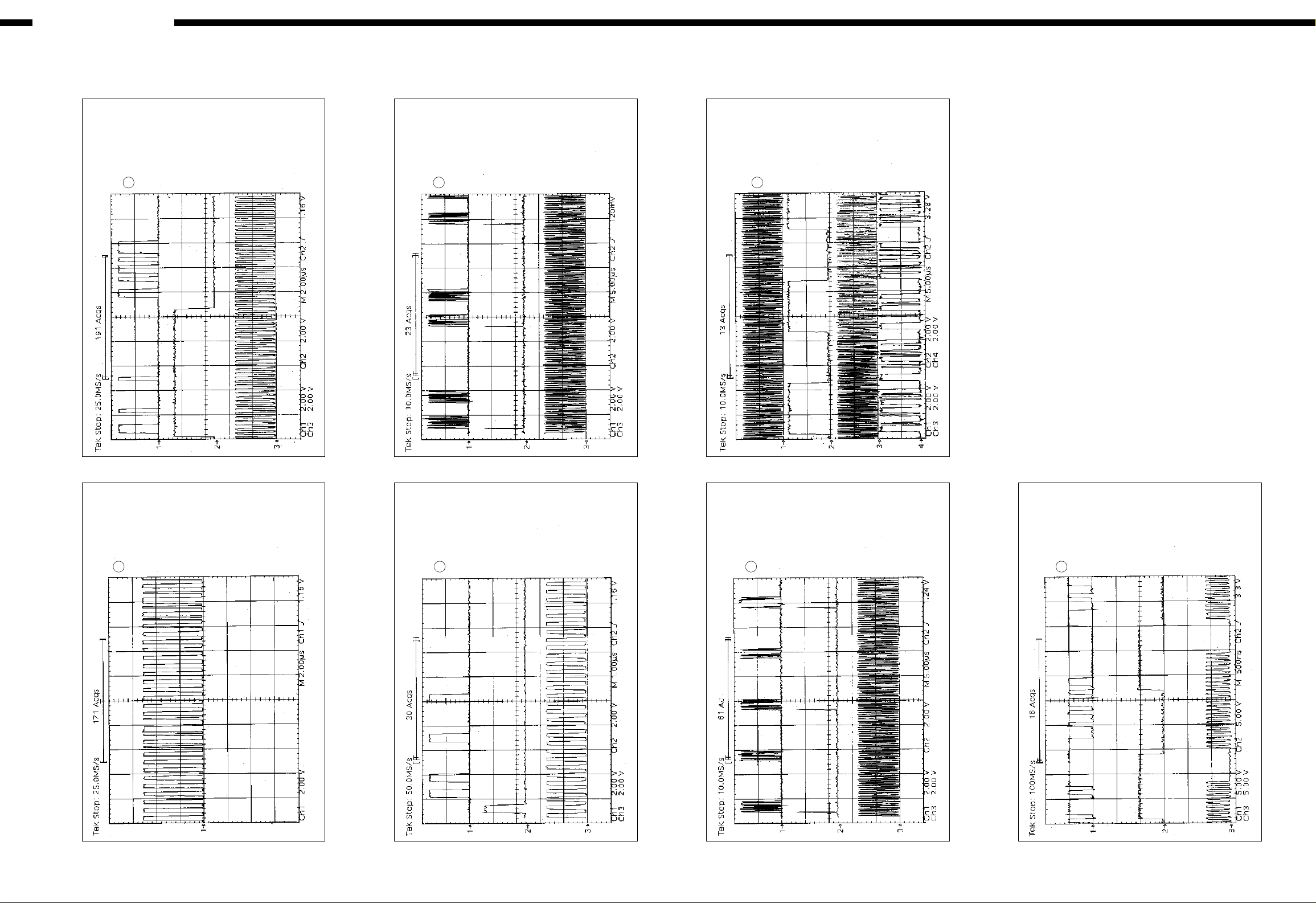

CLOCK FLOW & WAVE FORM IN DIGITAL BLOCK

Wave Form

CH1 DATA

CH2 fs

2

CH2 FSYNC

CH3 64fs

4

CH1 DATA

CH2 FSYNC

CH3 256fs

CH1 64fs

6

CH2 fs

CH3 256fs

CH1

IC510 (5)

1

CH3 64fs

3

CH1 DATA

CH1 DATA

CH2 FSYNC

5

CH3 256fs

FRONT DATA

CH4

CH1 DATA (L)

CH2 WCLK

7

10

Page 11

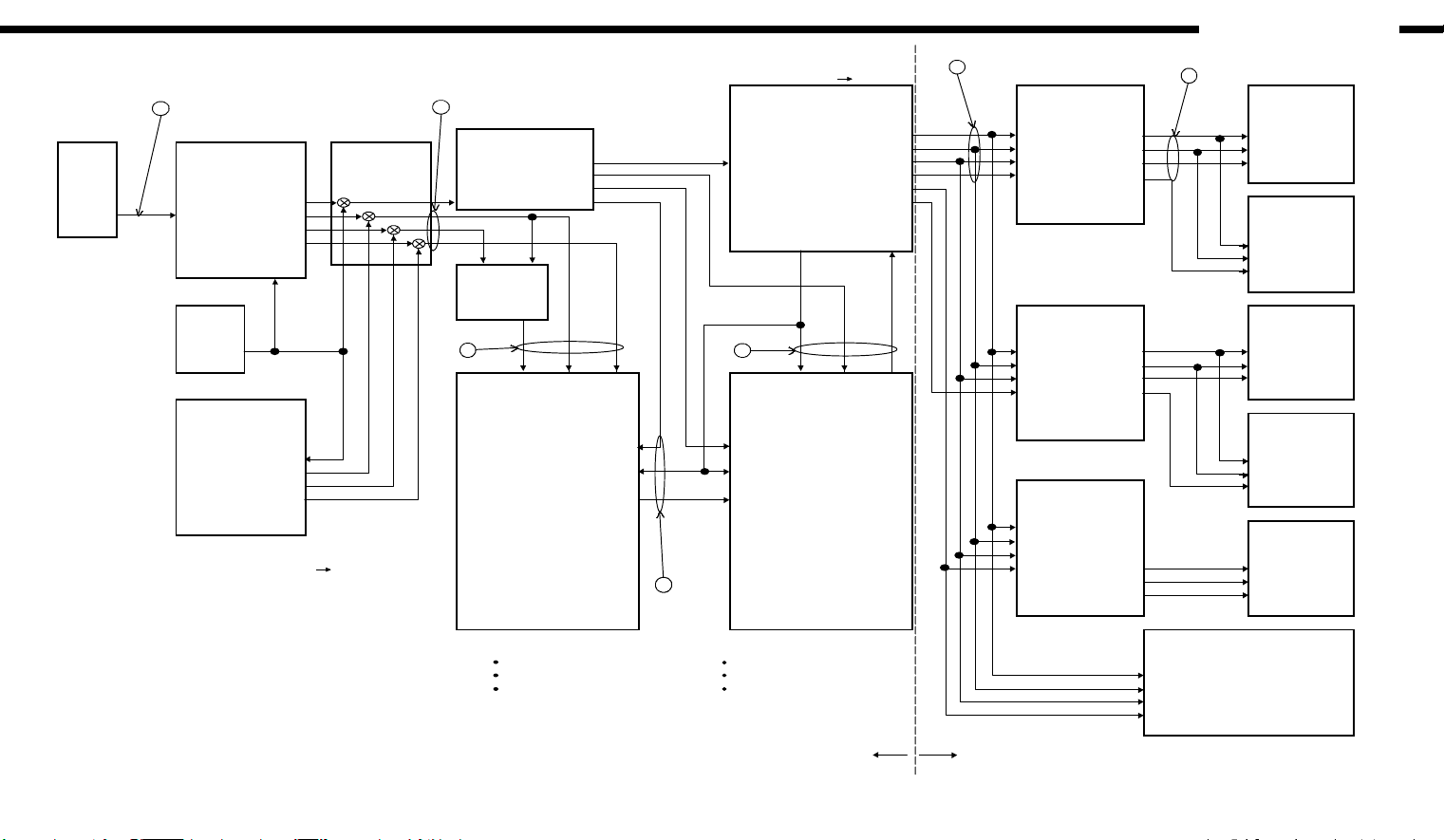

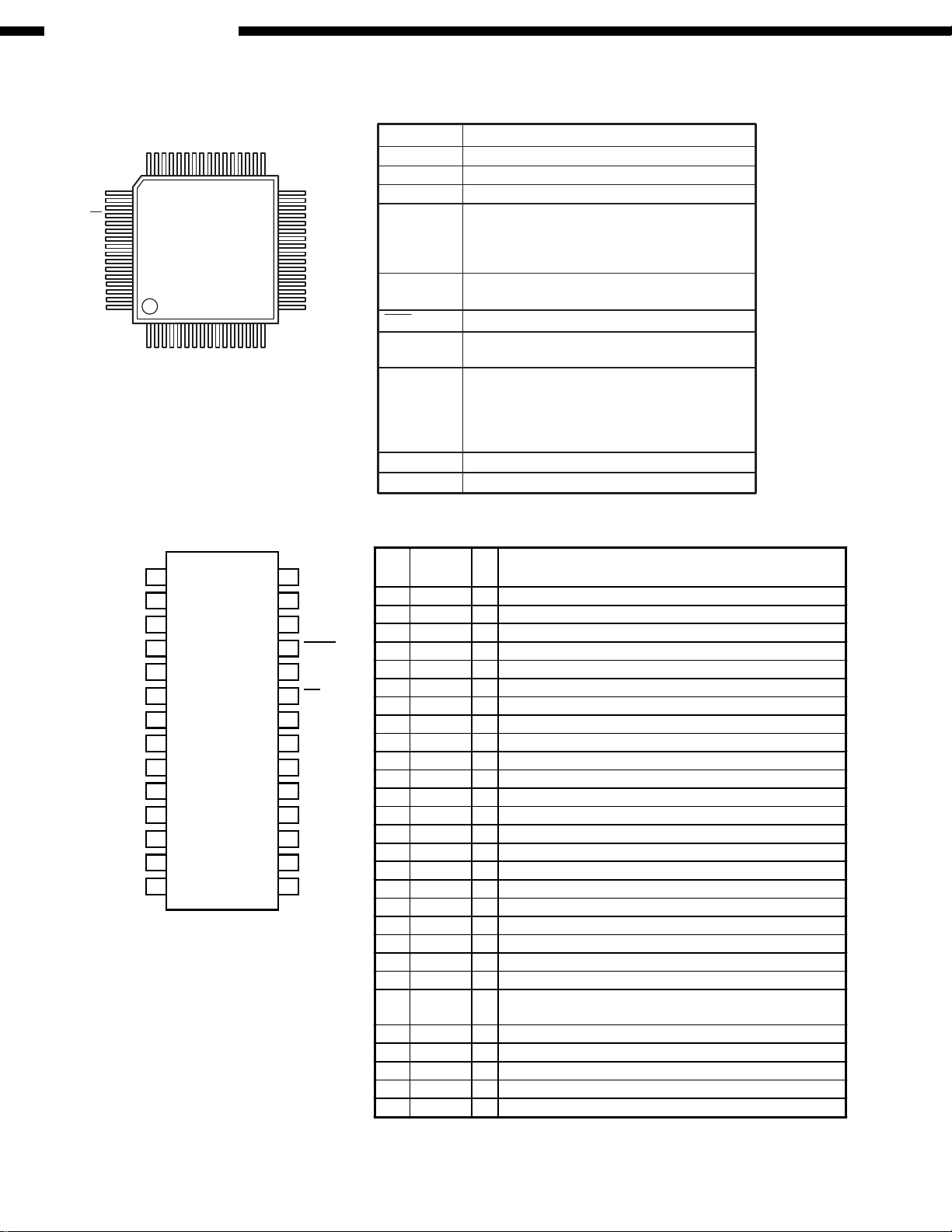

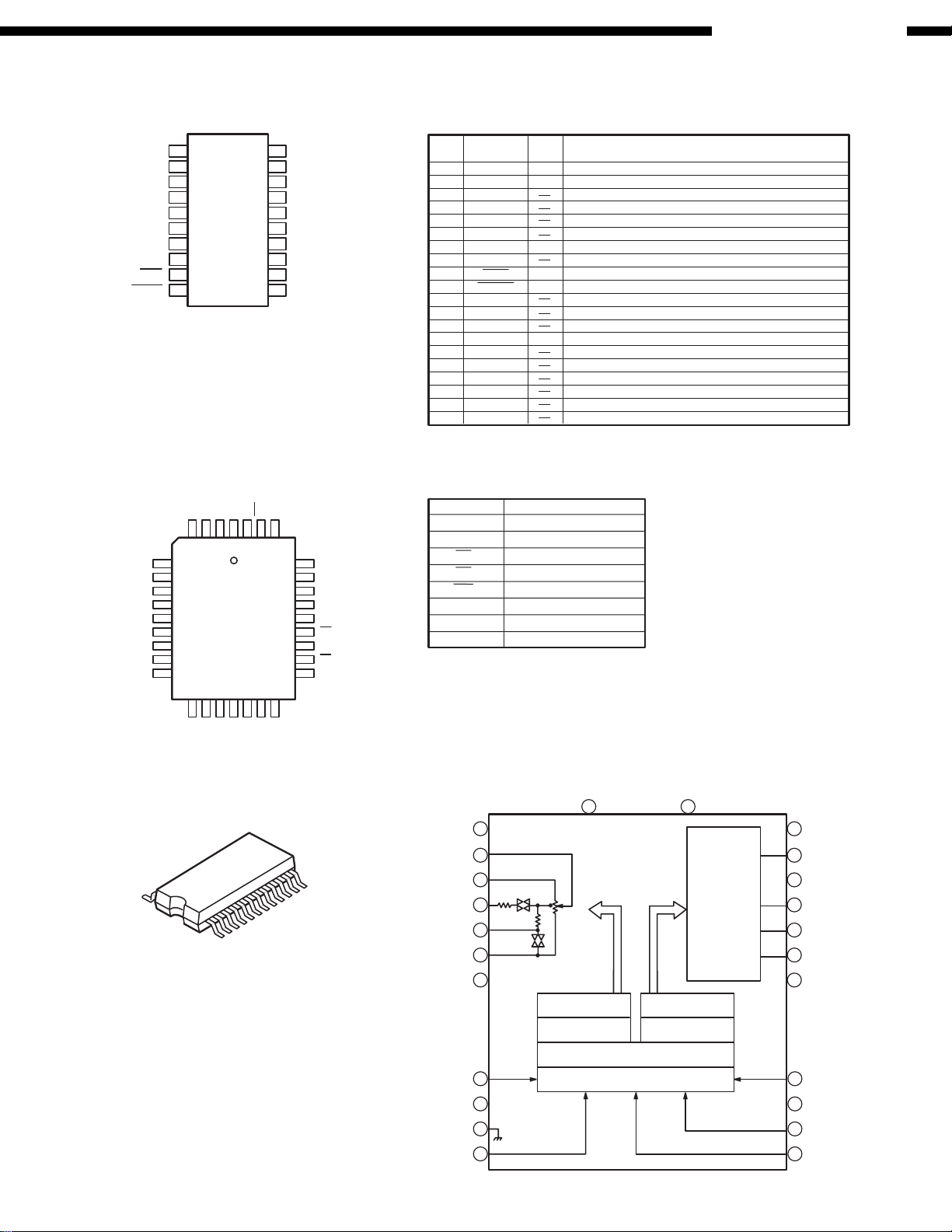

6chSERIAL I

S

AL24 PROCESSING

D/A CONVERTER

IC120

IC304

IC309

INPUT

BUFFER

SELECTOR

DIR

A/D SELECTOR

IC532

MCK1(22)

(42)XTI

BCKO(20)

(2)BCLK

SN74LV14APW

BCK1(20)

(7)DBCK

WCKO(21)

(7)WCLK

FLch

IC510

IC531

IC525

(8)

(33)MCK0

LRCK1(18)

SO1L(30)

(1)DATA

LC89055W

(6)

DATA3(10)

(8)DDT

SO1R(31)

151NS

(4)

DATA4(12)

CKOUT(13)

(13)

(2)

DATA5(14)

IC310

(5)

(5)DIN2

BCK(14)

PCM1704U

LRCK(15)

RFS1

DATAD(16)

(4)

(8)

(2)BCLK

(7)WCLK

FRch

XIN(22)

(13)

(9)

(1)DATA

IC102

12.288MHz

DIGITAL FILTER

IC528

(6)

IC305

IC311

SG-8002

FSYNC

DF1704

PCM1704U

(3)

(6)XTI

BCKO(26)

(2)BCLK

(2)BCKIN

(7)WCLK

SLch

(85)

(81)

(83)

(77)

(76)

(72)

(1)DATA

A/D CONVERTER

RFS0

RCLK0

DR0

RFS1

RCLK1

DT1

(1)DIN

DOR(23)

IC527

IC312

AK5351VS

PCM1704U

RCLK1(76)

(81)RCLK0

MCLK(17)

(2)BCLK

AIN

SCLK(18)

RFS1(77)

(85)RFS0

DIGITAL FILTER

(7)WCLK

SRch

LRCK(19)

IC306

(1)DATA

SDATA(21)

DT1(72)

(83)DR0

DF1704

e.g.:sampling frequency 48kHz fs=48kHz

(1)DIN

BCKO(26)

(2)BCLK

WCKO(25)

(7)WCLK

Cch*64fs and 256fs are 64 or 256 times the sampling

DOL(24)

(1)DATA

frequency respectively.

e.g.:sampling frequency 48kHz

64fs:48kHzX64=3.072MHz

1st DSP

2nd DSP

IC307

256fs:48kHzX256=12.288MHz

PCM1716E

DOLBY DIGITAL Decode

THX Filter Processing

*

The sampling frequency for analog input is fixed

DTS Decode

Sound Simulation

(5)XTI

to 48kHz internally.

Down-Mix Processing

Bus-Management Processing

(3)BCKIN

SWch

(1)LRCIN

*

(No.) indicates the pin number of individual IC.

(2)DIN*The arrow indicates the direction of signal flow,

as the input terminal pointed by the arrowhead

1U-3173-1 DSP UNIT

1U-3179-2 D/A UNIT

and the output terminal by the opposite.

11

256fs

64fs

fs

DATA

256fs

256fs

256fs

256fs

FSYNC

DATA

DATA

256fs

64fs

fs

FRONT

CENTER/SW

SURROUND

AVC-A1D/AVR-5700

6

SN74HC

2

1

SN74AHC157PW

2

3

MSM32R0050-521GS DXP6001AF PCM1704U

DATA2

SN74LV00APW

5

IC103 IC110 (6)XTI IC313

* fs is a sampling frequencey of input digital signal. ADSP-21061L ADSP-21061L (28)LRCIN

4

7

(5)DLRCK

(28)LRCIN DOL(24)

WCKO(25)

(2)BCKIN PCM1704U

Page 12

AVC-A1D/AVR-5700

ADJUSTMENT

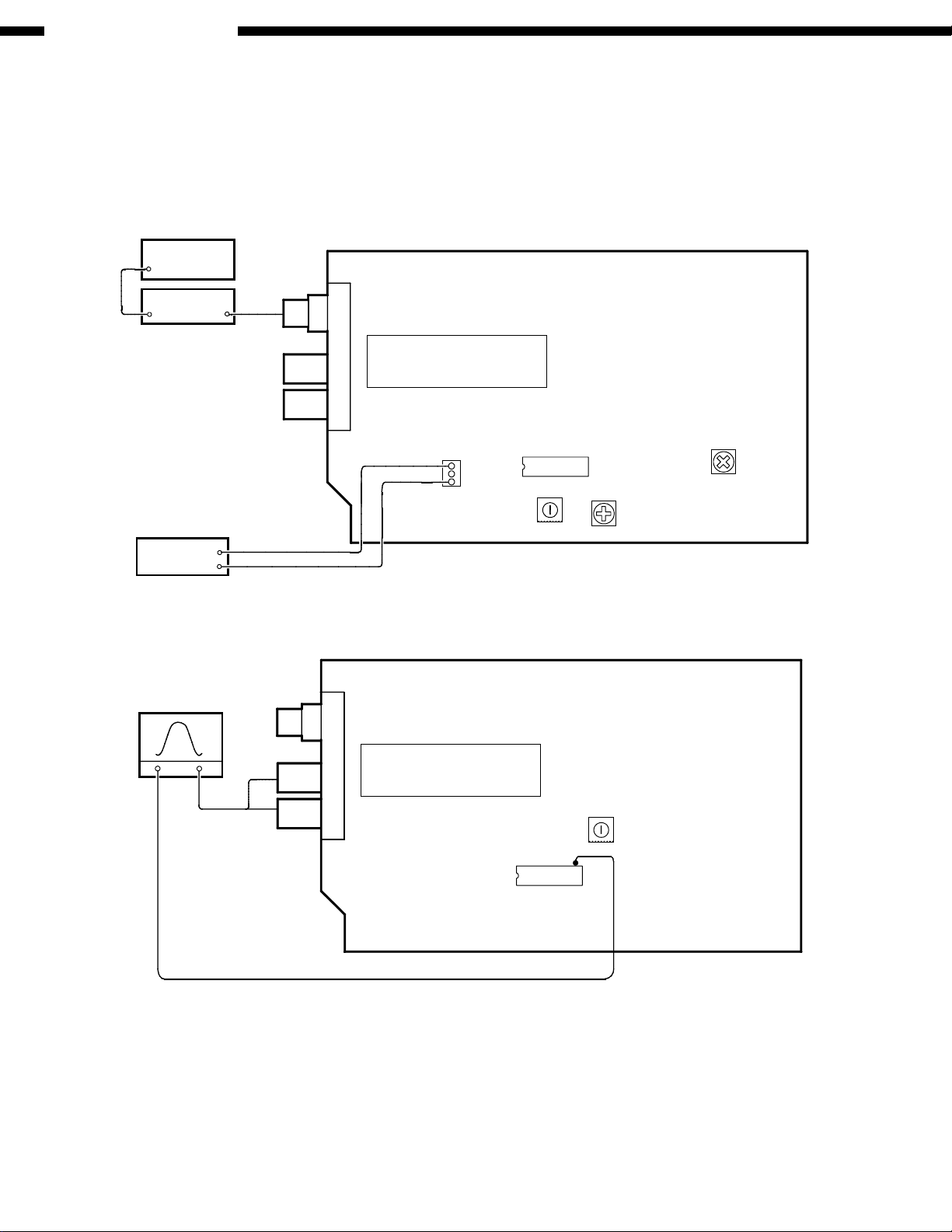

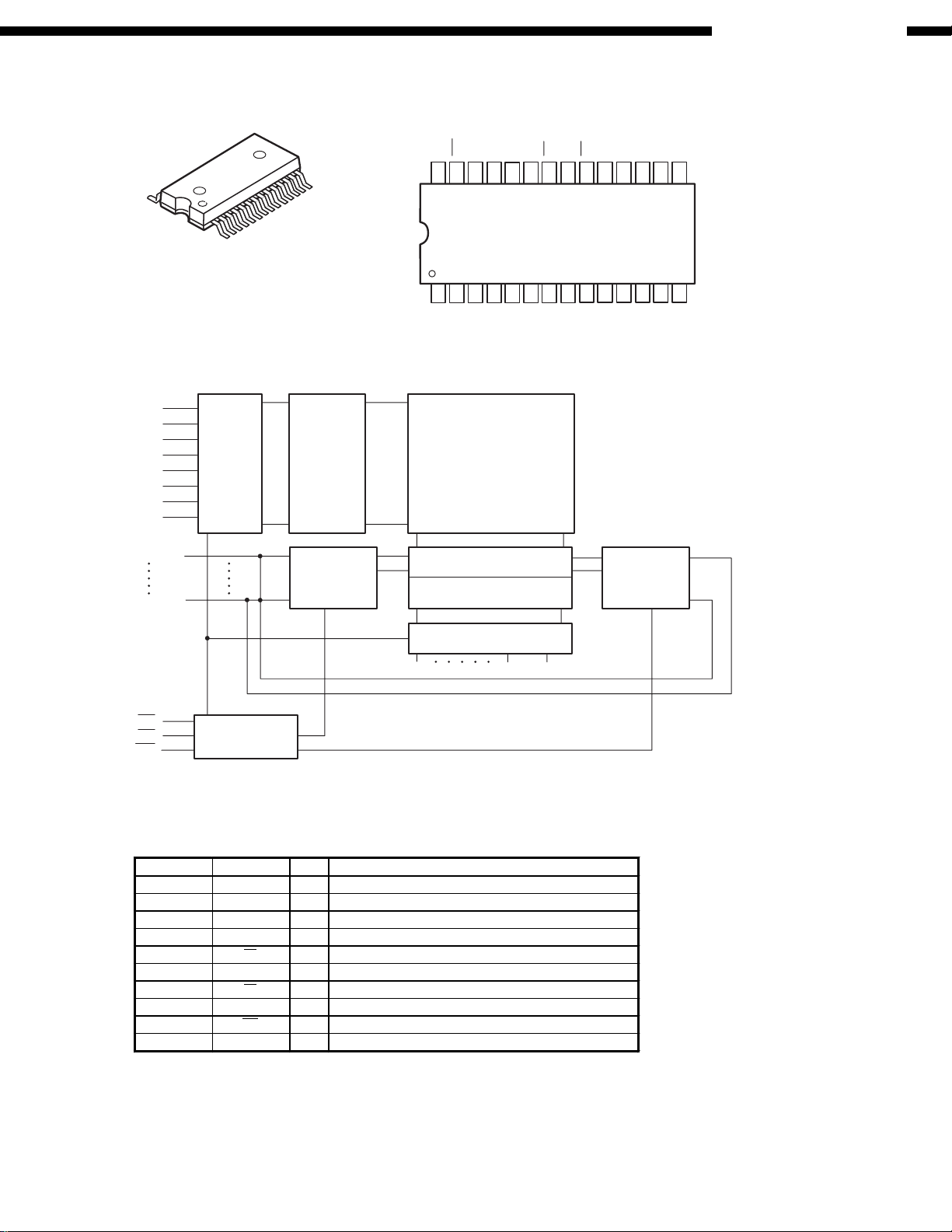

Tuner Section (AVR-5700 only)

CONNECTION DIAGRAM OF MEASURING INSTRUMENTS

''

' FM

''

STEREO

MODULATOR

1U-3126-1 TUNER UNIT

''

' AM

''

FMSSG

DIGITAL

VOLTMETER

OSCILLOSCOPE

75ohm

TP301

IC303

T302

VR301

1U-3126-1 TUNER UNIT

VR302

12

OUT

AM IF

GND

AM

T304

12 Pin

IC303

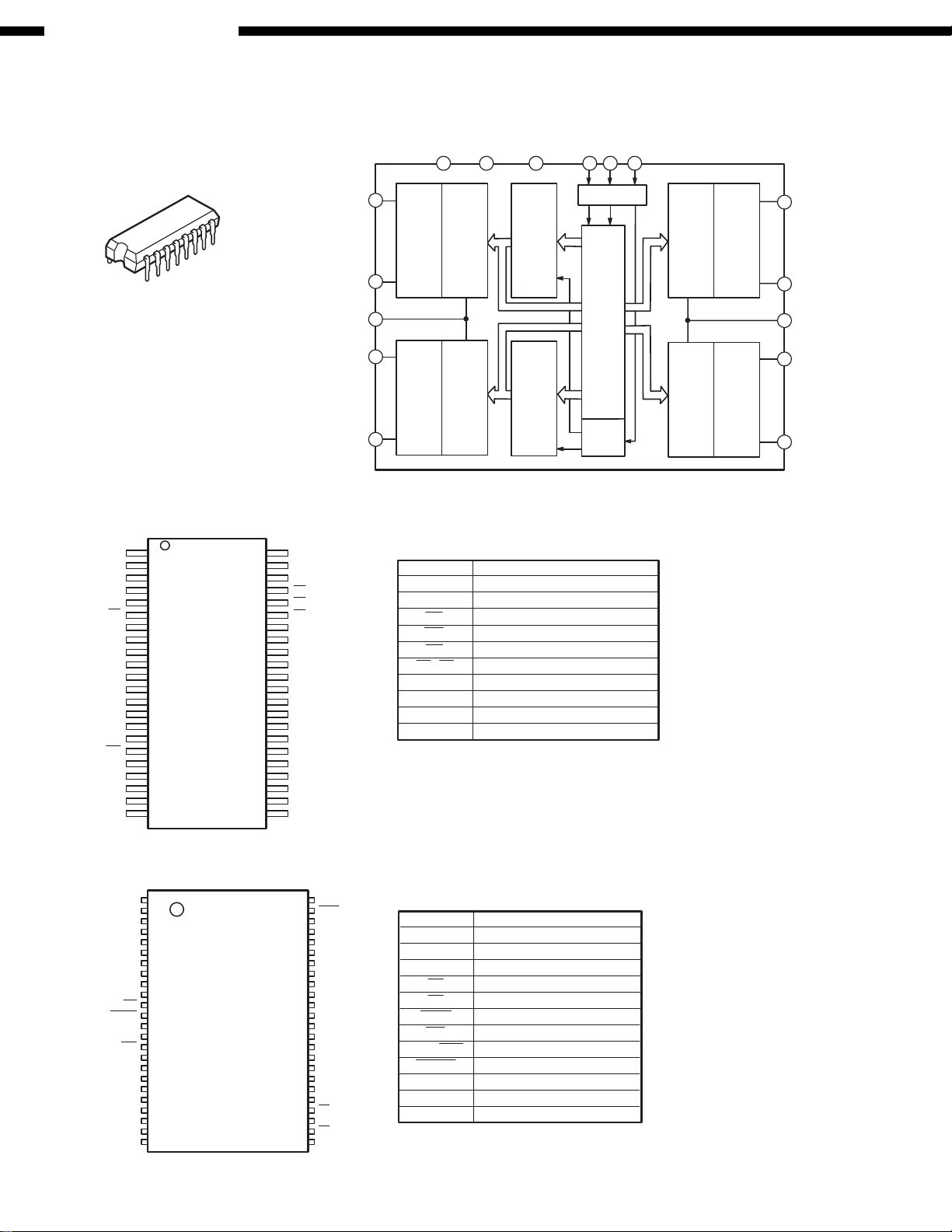

Page 13

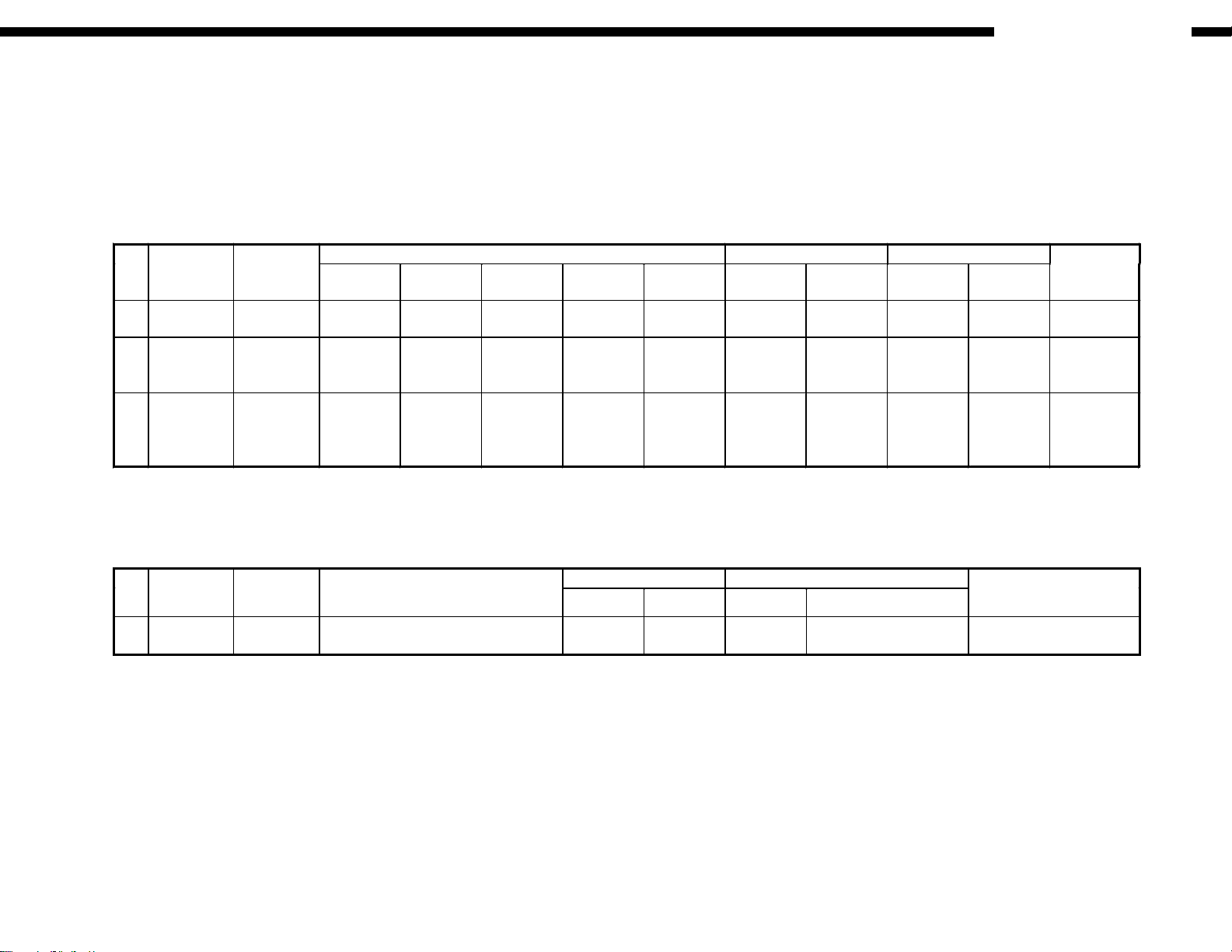

FM/MPX ALIGNMENT

Alignment

Step

1 Tuning Center 98.1 MHz FM SSG 98.1 MHz 60 dB

2 Separation 98.1 MHz FM SSG 98.1 MHz 60 dB

3 Signal Level 98.1 MHz FM SSG 98.1 MHz 20 dB

Item

Tuning

Frequency

Setting

Type Frequency Input Level Modulation Coupling Type Connect to Points Adjust to

Input Output Adjust

µ

µ

µ

None

Stereo (L)

1KHz 100%

Off

Antenna

Ter mi na l

Antenna

Ter mi na l

Antenna

Ter mi na l

Digital

Voltmeter

AC

Voltmeter

TP301 T302

AUDIO

OUT

Ter mi na l (R)

VR302

VR301

AVC-A1D/AVR-5700

Remarks

±

50mV

Maximum

Separation

Light

“TUNED”

FLD

Character

Function : FM

Mode : Auto

AM ALIGNMEN T

Alignment

Step

1IF

Item

Frequency I nput

IF SWEEP

(Input level is not over to work A.G.C.)

Output Adjustment

Type Connect to Points Adjust to

Oscilloscope IC303 12Pin T304

Maximum height and best

symmetry cu rve

Remarks

13

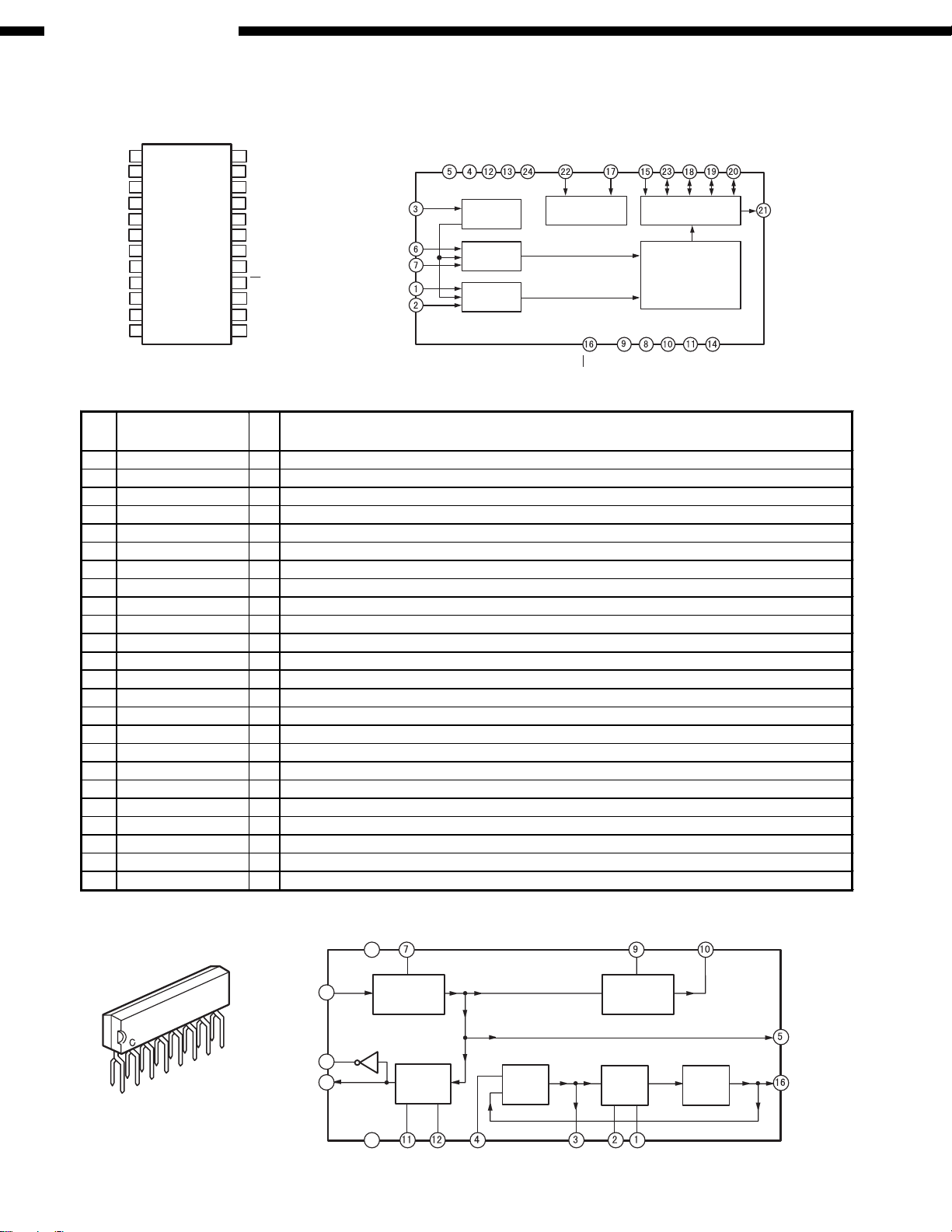

Page 14

AVC-A1D/AVR-5700

Audio Section

Idling Current (1U-3126-2)

Required measurement equipment : DC Voltmeter

Preparation

(1) Avoid direct blow from an air conditioner or an electric fan, and adjust the unit at normal room tempereture 15 °C ~ 30 °C

(59 °F ~ 86 °F).

(2) Presetting

● POWER (Power sourse switch) → OFF

● BASS, TREBLE (Tone control) → FLAT: (Controls to center)

● SPEAKER (Speaker terminal) → No load (Do not connect speaker, dummy resistor, etc.)

Adjustment

(1) Remove top cover and set VR701, VR702, VR781, VR741, VR742, on 1U-3126-2 (Power Unit) at full counterclockwise

( ) position.

(2) Connect DC Voltmeter to test points (FRONT-Lch: TP801, FRONT-Rch: TP802, CENTER ch: TP805, SURROUND-Lch:

TP803, SURROUND-Rch: TP804).

(3) Connect power cord to AC Line, and turn power switch "ON".

(4) Presetting. MASTER VOLUME : "---" counterclockwise (

min.)

MODE : 5CH STEREO

FUNCTION : CD

(5) Within 2 minutes after the power on, turn VR701 clockwise ( ) to adjust the TEST POINT voltage to 1.5 mV ±0.5 mV

DC.

(6) After 10 minutes from the preset above, turn VR701 to set the voltage to 3 mV ±0.5 mV DC.

(7) Adjust the Variable Resistors of other channels in the same way.

VR742

TP804

DC Voltmeter

1U-3128-3

Power Trans

S Rch

VR702

F Rch

VR781

C ch

VR701

F Lch

VR741

S Lch

TP802

TP805

TP801

TP803

14

1U-3126-2

Page 15

AVC-A1D/AVR-5700

SEMICONDUCTORS

''

' IC's

''

Note: Abbreviation ahead of IC No. indicates the name of P.W.B.

AU: Audio In & SP P.W.B. TU: Tuner & Amp P.W.B.

RE: Rectifier P.W.B. TO: Tone, Pre-out P.W.B.

VI: Video & FLD P.W.B. MA: Main & Reg. P.W.B.

DS: DSP P.W.B. EX: Ext. In & DA P.W.B.

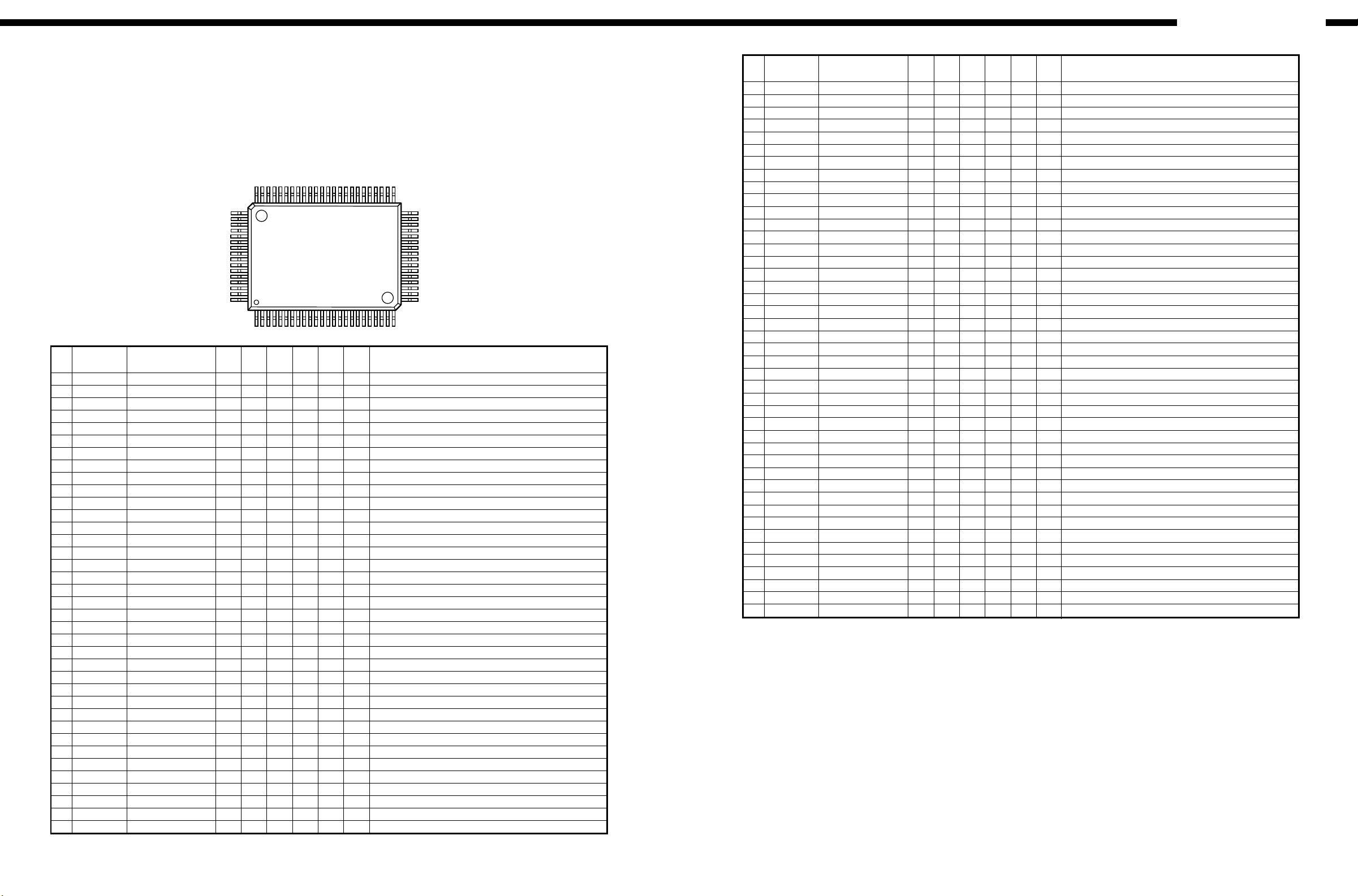

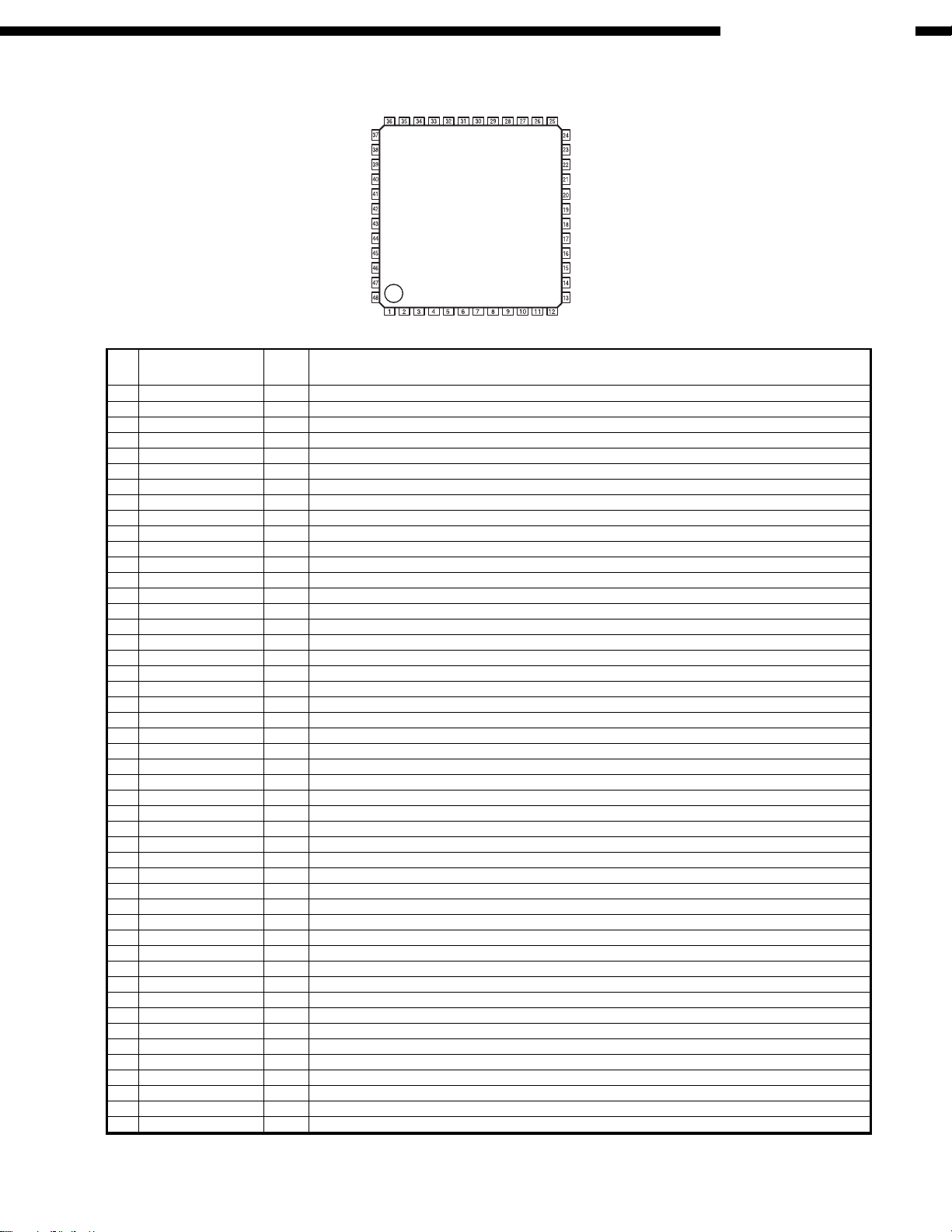

TMP88CU74F

(MA: IC201)

TMP88CU74F Terminal Function

Pin

Name Function

No.

Symbol

64

65

80

124

I/O Type Op Det Res Init

1 P02/S01 OSD DATA O C Eu S Z L OSD control output (M35015)

2 P03 OSD RST O C Z H OSD control output (M35015)

3 P04 ST/MONO O C Z L STEREO/MONO control signal (L: Stereo)

4 P05 PLFL DATA O C S Z L PLL, FL control terminal (LC72131 & LC7511NE)

5 P06 PLL STB O C Z L PLL control terminal (LC72131)

6 P07 PLFL CLK O C S Z L PLL, FL control terminal (LC72131 & LC7511NE)

7 Vss Vss I GND L GND

8 Xout Xout O XTAL

9 Xin Xin I XTAL

10 RESET_ RESET_ I Eu Lv L Reset input

11 P22/XTOUT TUNES_ I Eu Lv Z Tuned detection (L: Tuned)

12 P21/XTIN STEREO_ I Eu Lv Z At stereo receive: L

13 TEST TEST I GND S Connect to GND

14 P20/INT5_ B.DOWN_ I Eu Lv Z Power down detect (L: Power down)

15 P10/INT0_ PROTEST_ I Ed E&L Z PROTECTION detect input (L: Detected)

16 P11/INT1 S1 O C Z L Video switching control terminal

17 P12 SELC(F) I Eu Lv Z Input selector SW rotary detect input (rotary encoder)

18 P13 SELD(F) I Eu Lv Z Input selector SW rotary detect input (rotary encoder)

19 P14 SW L/R 7.1 O C Z L EFFECT L/R muting control terminal

20 P15/INT3 REMOCON I Ed E&L Z Remote control signal input

21 P16/INT2 ACK O C Z L MAIN-SUB CPU comm. control terminal

22 P17/INT4 REQ I Eu Z L MAIN-SUB CPU comm. control terminal

23 P30/SCL SI I (C) MAIN-SUB CPU comm. control terminal

24 P31/SDA S O O (C) MAIN-SUB CPU comm. control terminal

25 P32/SCK0_ CLK I/O (C) MAIN-SUB CPU comm. control terminal

26 P40/AIN0 MODE I Eu Lv Z Destination switching input

27 P41/AIN1 KEY1 I Eu Lv Z Button input 1

28 P42/AIN2 KEY2 I Eu Lv Z Button input 2

29 P43/AIN3 KEY3 I Eu Lv Z Button input 3

30 P44/AIN4 KEY4 I Eu Lv Z Button input 4

31 P45/AIN5 FUNC/T. CON CLK O C Ed ZL

32 P46/AIN6 FUNC/T. CON DATA O C Ed ZL

33 P47/AIN7 S2 O C Z L Video switching control terminal

34 P50/AIN8 E.VOL STB-1 O C Ed L L E. volume control output (TC9459)

35 P51/AIN9 E.VOL STB-2 O C Ed L L E. volume control output (TC9459)

36 P52/AIN10 E.VOL DATA O C Ed L H E. volume control output (TC9459)

37 P53/AIN11 E.VOL CLK O C Ed L H E. volume control output (TC9459)

41

40

25

Function (TC9274N, TC9273) / Tone (TC9184P) control output

Function (TC9274N, TC9273) / Tone (TC9184P) control output

Pin

No.

Name

Symbol

I/O Type Op Det Res Init

Function

38 VASS VASS I Ref. V (GND)

39 VAREF VAREF I Ref. V (VDD)

40 VDD VDD I Power

41 P61 FL CE I P Ed S L H FL display control output (LC75711NE)

42 P61 FL RES O P Ed S L H FL display control output (LC75711NE)

43 P62 FUNC STBA O P Ed Z L Function control output (TC9274N) INPUT

44 P63 FUNC STBB O P Ed Z L Function control output (TC9273) REC OUT, REC INH

45 P64 TONE CON. STB O P Ed Z L TONE control output (TC9184P)

46 P65 STANDBY O P Id L H Standby LED drive output (H: Light)

47 P66 EXP OE O P Ed L H Port expander control terminal (TC4094B)

48 P67 EXP CLK O P Ed L L Port expander control terminal (TC4094B)

49 P70 EXP DATA O P Ed L L Port expander control terminal (TC4094B)

50 P71 EXP STB1 O P Ed L L Port expander control terminal (TC4094B)

51 P72 LED CLK O P S Z H LED control terminal (M66313)

52 P73 LED DATA O P S Z H LED control terminal (M66313)

53 P74 LED LE O P Z H LED control terminal (M66313)

54 P75 LED OE O P Z H LED control terminal (M66313), set input port at STBY

55 P76 MULTI MUTE O P Ed L H MULTI MUTE output (L: Mute)

56 P77 H/P RELAY O P Id L L H/P OUT relay control output (L: Mute)

57 P80 POWER O P Id L H Power relay control output (L: ON)

58 P81 RESET2_ O P Id L H Sub CPU control reset output (H: Reset control)

59 P82 F RELAY O P Id Lv L Front SP relay control terminal (L: Mute)

60 P83 C RELAY O P Id L H Center SP relay control terminal (L: Mute)

61 P84 SA RELAY O P Lv L Surround SP relay A control terminal (L: Mute)

62 P85 SB RELAY O P Lv L Surround SP relay B control terminal (L: Mute)

63 P86 PRE F MUTE O P Ed L H Front PREOUT mute control terminal (L: Mute)

64 P87 PRE C MUTE O P Lv L Center PREOUT mute control terminal (L: Mute)

65 P90 PRE S MUTE O P Ed L H Surround PREOUT mute control terminal (L: Mute)

66 P91

SUB WOOFER MUTE

OPEd L L Sub-woofer PREOUT mute control terminal (L: Mute)

67 P92 S MONI DET I Eu Lv Z S monitor connection detect input (L: connected)

68 P93 S SIG DET I Eu Lv Z S signal detect input (H: S signal input)

69 P94 SYNC DET I Eu Lv Z Sync. detect input (H: External sync.)

70 P95 SEL A (M) I Eu Lv Z Master volume rotary detect input (rotary encoder)

71 P96 SEL B (M) I Eu Lv Z Master volume rotary detect input (rotary encoder)

72 P97 H/P DET I Eu Lv Z L H/P input detect (H: Detect)

73 PD0 VOL MUTE O P Ed L L Master volume infinite control (L: Infinite)

74 PD1 SEL E (B) I Eu Lv Z BASS volume rotary detect input (rotary encoder)

75 PD2 SEL F (B) I Eu Lv Z BASS volume rotary detect input (rotary encoder)

76 PD3 SEL G (T) I Eu Lv Z TTEBLE volume rotary detect input (rotary encoder)

77 PD4 SEL H (T) I Eu Lv Z TTEBLE volume rotary detect input (rotary encoder)

78 Vkk Vkk Fixed to GND

79 P00/SCK1_ OSD CLK O C Eu S Z H OSD control output (M35015)

80 P01/SI1 OSD STB1 O C Eu Z H OSD control output (M35015)

NOTE:

Pin No. : Terminal number of microcomputer.

Port Name : The name entered in the data sheet of microcomputer.

Symbol : Symbolized interface function.

I/O : Input or out of part.

Type : Composition of port in case of output port.

Op : Pull up/Pull down selection information.

Det : Indicates judging state of input port. Level detection is “LV”; Edge detection is “Ed”; Detection by both shifting is “E&L”;

Res : State at reset.

Ini : Initial output state.

Function : Function and logical level explanation of signals to be interface.

Serial data detection is “S” (Serial data output is also “S”).

“I” = Input port

“O” = Output port

“C” = CMOS output

“N” = NMOS open drain output

“P” = PMOS open drain output

“Iu” = Inner microcomputer pull up

“Id” = Inner microcomputer pull down

“Eu”= External microcomputer pull up

“Ed”= External microcomputer pull down

“H” = Outputs High Level at reset

“L” = Outputs Low Level at reset

“Z” = Becomes High impedance mode at reset

15

Page 16

AVC-A1D/AVR-5700

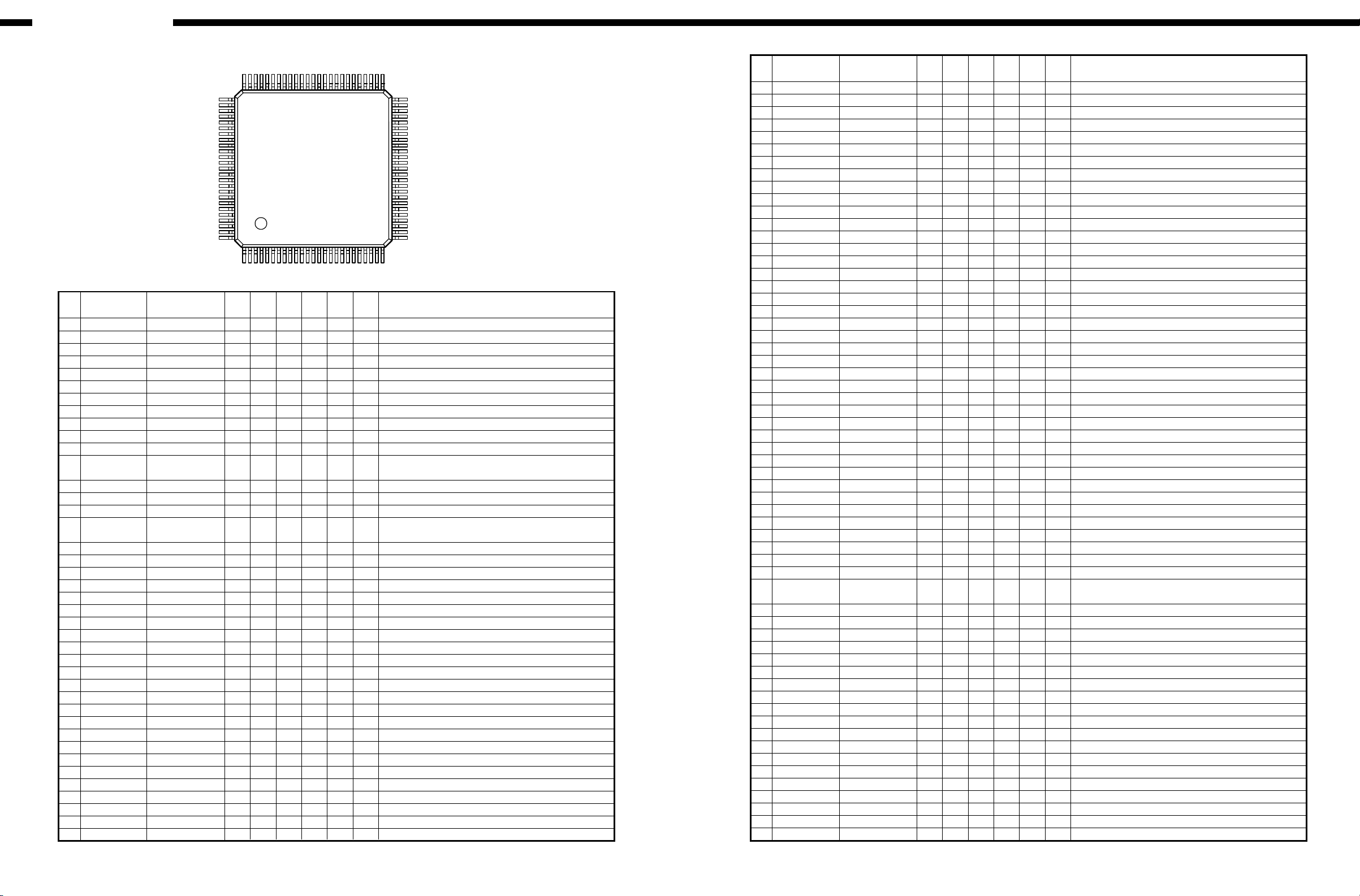

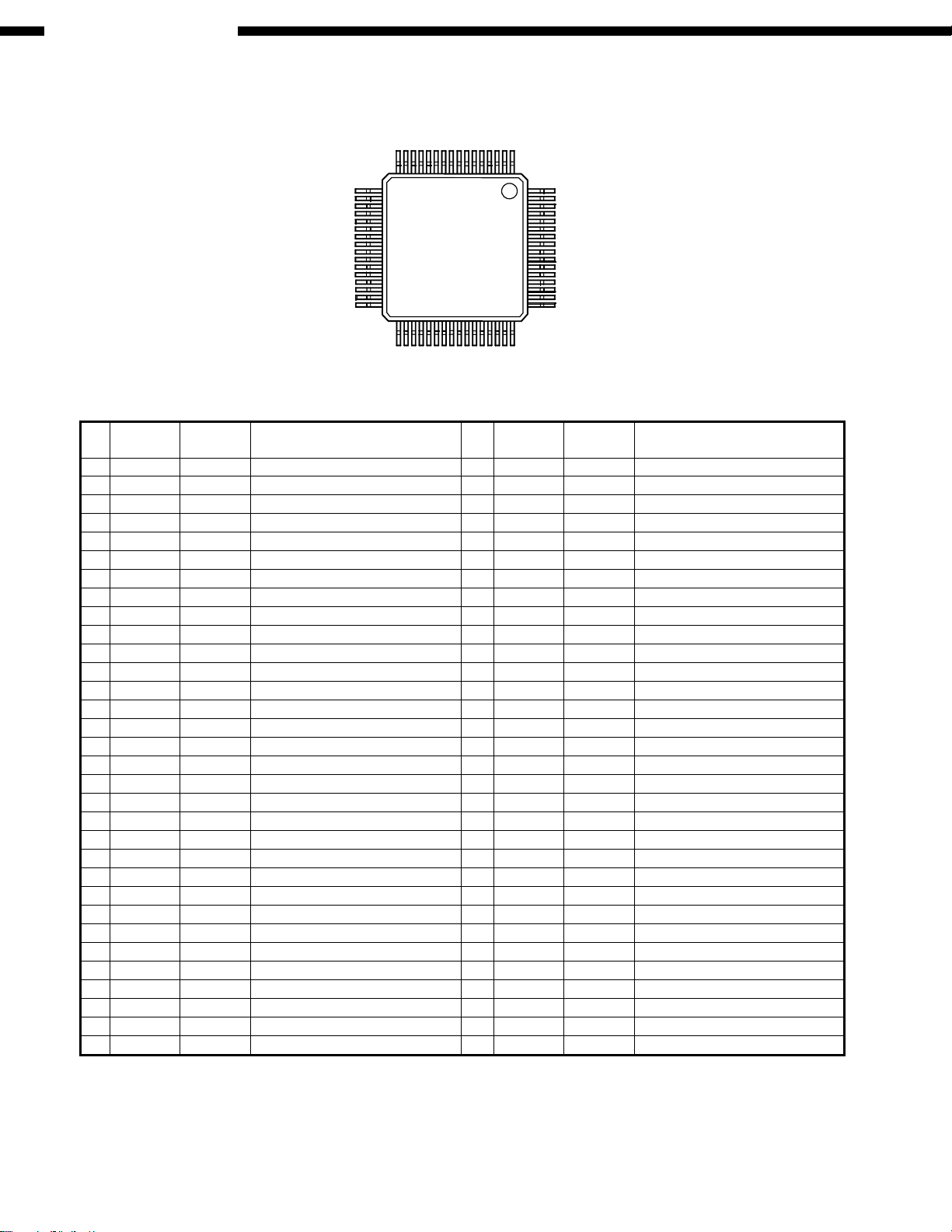

TMP93CS41F

(DS: IC301)

76

100

75

1

51

50

26

25

TMP93CS41F Terminal Function

Pin

No.

10 P81/INT5/TI5 DSP ACK I E↑&L Host I/F comm. response input (L: OK)

11 P82/TO4 AC-3 RF DET I E↓&L AC-3 RF signal judge input (L: AC-3 data input)

12 P83/TO5 _REQ O C Eu HL

13 P84/INT6/TI6 _ACK I Eu E↓&L MAIN-SUB CPU comm. control input (L: Ack. return from main)

14 P85/INT7/TI7 ERR I E↑&L DIR control input terminal (LC89055Q)( H: ERR)

15 P86/TO6 _DSP RESET O C Ed L L DSP reset output terminal (L: Reset)

16 P97/INT0 _CS I Ed E↑&L

17 P90/TXD0 SI O C MAIN-SUB CPU comm. control terminal (data output)

18 P91/RXD0 SO I MAIN-SUB CPU comm. control terminal (data input)

19

20 P93/TXD1 DF DATA O C Z L (DXP6001) control data output

21 P94/RXD1 DIR MISO I Lv DIR control input terminal (LC89055Q) control data input

22 P95/SCLK1 DIR CLK O C Z L DIR control terminal (LC89055Q) control clock output

23 AM8/_16 ← Fixed to +5V

24 CLK O C Eu

25 Vcc ← +5V

26 Vss I/O1 GND

27 X1 Xin I X′tal connection

28 X2 Xout O X′tal connection

29 _EA ← Fixed to +5V

30 _RESET RESET2_ I Eu Lv L Reset input (controlled by main CPU)

31 P96/XT1 A/D RESET O N Eu H H A/D control terminal (L: Reset)

32 P97/XT2 DAC RESET O N Eu H H D/A control terminal (L: Reset)

33 TEST1 ←ΙConnected to TEST2

34 TEST2 ←ΙConnected to TEST1

35 PA0 DINA O C Ed L L Digital input switching control output

36 PA1 DINB O C Ed L L Digital input switching control output

37 PA2 DINC O C Ed L L Digital input switching control output

38 PA3 DIND O C Ed L L Digital input switching control output

39 PA4 DINE O C Ed L L Digital input switching control output

40 PA5 DOUTA O C Ed L L Digital input switching control output

Name

1 V REFL A/D ref. GND

2 A Vss ← A/D GND

3 A Vcc ← AD +5V

4 _NMI I Not used (fixed to H)

5 P70/TI0 _DEMOD RESET O C Ed L L Demodulator reset output (L: Reset)

6 P71/TO1 DEMOD ON O C Ed L L Demodulator osc. control output (H: Osc.)

7 P72/TO2 FAN1 O C Ed L L FAN control output (H: ON, L: OFF)

8 P73/TO3 FAN2 O C Ed L L FAN control output (H: Hi, L: Low & off)

9 P80/INT4/TI4 B.DOWN_ I Eu E↓&L Z Power down detect (L: Detected)

P92/_CTS0/SCLK0

Symbol

CLK I/O C MAIN-SUB CPU comm. control terminal (I2C clock in/output)

I/O Type Op Det Res Init

MAIN-SUB CPU comm. control output (L: Comm. request from

sub)

DIR control input terminal (LC89055Q), when CH status change L

•¨H

Function

Pin

No.

41 PA6 DOUTB O C Ed L L Digital input switching control output

42 PA7/SCOUT DOUTC O C Ed L L Digital input switching control output

43 ALE ← OC L L Address latch enable

44 Vcc +5V

45 P00/AD0 AD0 I/O C Z L EPROM data in D0 / address out A0

46 P01/AD1 AD1 I/O C Z L EPROM data in D1 / address out A1

47 P02/AD2 AD2 I/O C Z L EPROM data in D2 / address out A2

48 P03/AD3 AD3 I/O C Z L EPROM data in D3 / address out A3

49 P04/AD4 AD4 I/O C Z L EPROM data in D4 / address out A4

50 P05/AD5 AD5 I/O C Z L EPROM data in D5 / address out A5

51 P06/AD6 AD6 I/O C Z L EPROM data in D6 / address out A6

52 P07/AD7 AD7 I/O C Z L EPROM data in D7 / address out A7

53 P10/AD8/A8 A8 O C Z L EPROM address out A8

54 P11/AD9/A9 A9 O C Z L EPROM address out A9

55 P12/AD10/A10 A10 O C Z L EPROM address out A10

56 P13/AD11/A11 A11 O C Z L EPROM address out A11

57 P14/AD12/A12 A12 O C Z L EPROM address out A12

58 P15/AD13/A13 A13 O C Z L EPROM address out A13

59 P16/AD14/A14 A14 O C Z L EPROM address out A14

60 P17/AD15/A15 A15 O C Z L EPROM address out A15

61 _WDTOUT ← OCZ H Watch dog output

62 Vss ← GND

63 Vcc ← +5V

64 P20/A0/A16 A16 O C Z L EPROM address out A16

65 P21/A1/A17 DF CLK O C Z L (DXP6001) control clock output

66 P22/A2/A18 ADIRCE O C Z L DIR control terminal (LC89055Q) control chip enable output

67 P23/A3/A19 DIR MOSI O C Z L DIR control terminal (LC89055Q) control data output

68 P24/A4/A20 DF STB1 O C Z L (DXP6001) control strobe output

69 P25/A5/A21 FGAIN O C Ed L L IV AMP gain switching control output (L: Sub-woofer on)

70 P26/A6/A22 HDCD O C Ed L L HDCD control terminal (fixed to L)

71 P27/A7/A23 SEL CK O C Ed Z L ADC/DIR data clock switching control terminal (L: ADC)

72 P30/_RD _RD O C Ed Z L Flash memory control terminal

73 P31/_WR _WR O C Ed Z L Flash memory control terminal

74 P32/_HWR CSI I Ed Lv DIR control input terminal (DIR1700) (L: PCM)

75 P33/_WAIT ERR MUTE_ O C Ed L L Pop noise preventive mute control output (L: Mute)

76 P34/_BUSRQ _DSP REQUEST O C Ed ZL

77 P35/_BUSRQ DIG.(AC39 MUTE O C Ed Z L Digital mute control output (L: AC-3 or DTS decode enable)

78 P36/_R/W WRITE O C Z L DSP comm. control terminal (H: Data write)

79 P37/_RAS DIR RESET O C Z L DIR control output (LC89055Q) (L: Reset)

80 P40/\CS0/_CAS0 FLAG 1B I Lv (ADSP21061L-B:FLAG1B) input

81

82

83 P60/PG00 I/01 I/O C Z L DSP comm. terminal (ADSP21061L: D16)

84 P61/PG01 I/02 I/O C Z L DSP comm. terminal (ADSP21061L: D17)

85 P62/PG02 I/03 I/O C Z L DSP comm. terminal (ADSP21061L: D18)

86 P63/PG03 I/04 I/O C Z L DSP comm. terminal (ADSP21061L: D19)

87 P64/PG10 I/05 I/O C Z L DSP comm. terminal (ADSP21061L: D20)

88 P65/PG11 I/06 I/O C Z L DSP comm. terminal (ADSP21061L: D21)

89 P66/PG12 I/07 I/O C Z L DSP comm. terminal (ADSP21061L: D22)

90 P67/PG13 I/08 I/O C Z L DSP comm. terminal (ADSP21061L: D23)

91 Vss ← GND

92 P50/AN0 AUDIO LEVEL I Eu Lv Z Signal level detect, set to A/D input

93 P51/AN1 POSI (FAN) I Eu Lv Z Temperature detect, set to A/D input

94 P52/AN2 EMP I Lv H: EMP on

95 P53/AN3 96K DET I Lv 96k signal detect input, H: 96k

96 P54/AN4 BUSY1 I Lv (ADSP21061L-A:FLAG2A)

97 P55/AN5 FLAG 3A I Lv (ADSP21061L-A:FLAG3A)

98 P56/AN6 BUSY2 I Lv (ADSP21061L-B:FLAG2B) input

99 P57/AN7 I Lv

100 V REFH ← AD ref. +5V

Name

P41/_CS1/_CAS1

P42/_CS2/_CAS2

Symbol

LFE PRESENCE I Lv

_CS0 O C Z L Flash memory control terminal

I/O Type Op Det Res Init

(ADSP21061L-A:IRQ1_) host I/F interrupt request output (L: REQ)

(ADSP21061L-B:FLAG0B) LFE signal detect input, H: LFE

detected

Function

16

Page 17

(−)

(−)

)

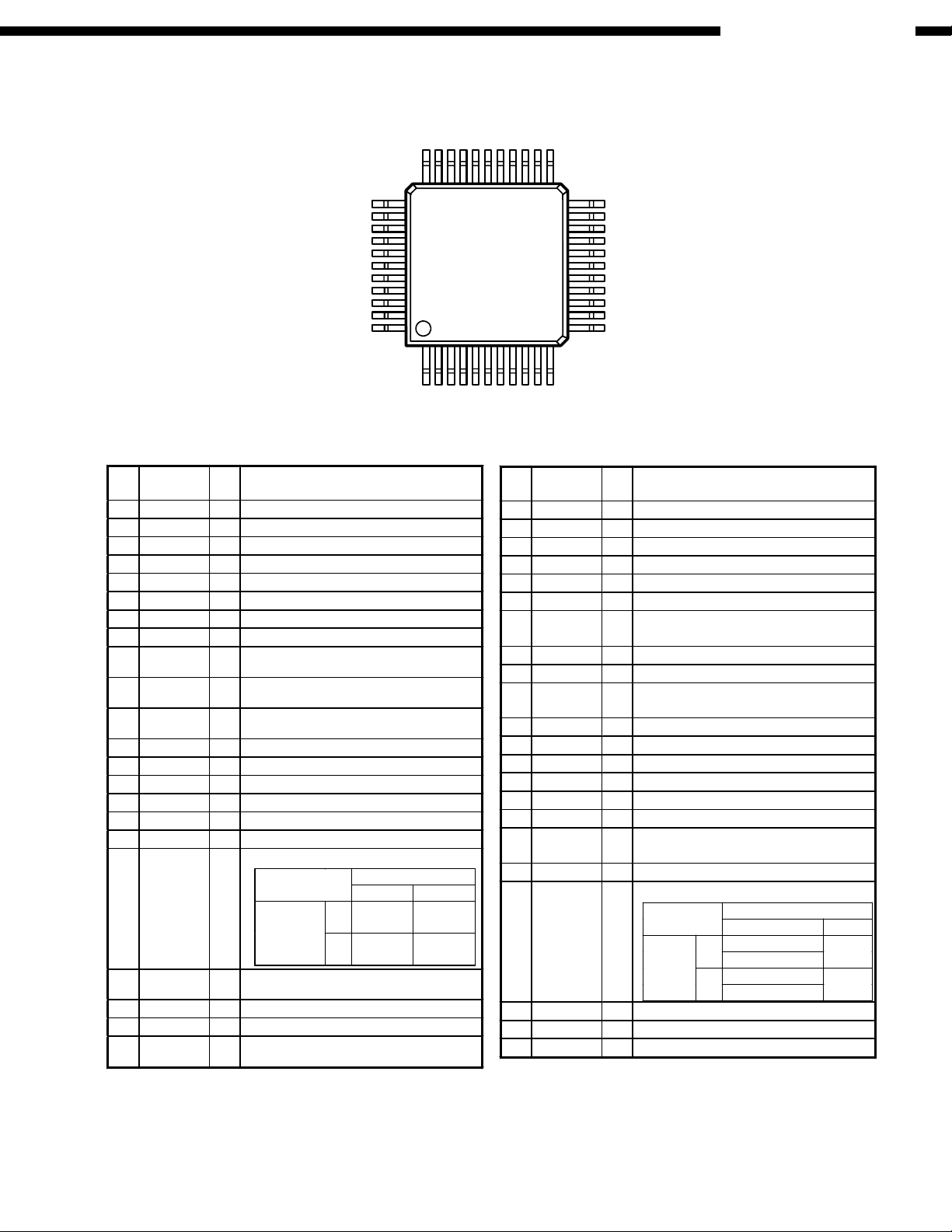

DXP6001AF

(IC304)

AVC-A1D/AVR-5700

33 23

34

44

DXP6001AF Terminal Function

Pin

Pin Name I/O Desc r pti on

No.

MDT Ip Microcomputer Interface Data

1

MCK Ip Microcomputer Interface Clock

2

MLEN Ip Microcomputer Interface Latch Enable

3

RSTN Ip Reset Terminal

4

DLRCK Ip Audio Serial Input Data L/R Clock

5

VSS

6

DBCK Ip Audio Serial Input Bit Clock

7

DDT Ip Audio Serial Input Data

8

TEST2N Ip

9

10

TEST3N Ip

TEST4N Ip

11

12

DFBCK Ip Lambda-processor Input Bit Clock

13

DFWCK Ip Lambda-processor Input Word Clock

14

DOL Ip Lambda-processor Input Data L-channel

15

DOR Ip Lambda-processor Input Data R-channel

16

LMOD Ip Lambda-processor Operation Mode Set

17

OMOD1 Ip Output Mode Setting Terminal 1

OMOD2 Ip

18

19

INVIN Ip

BCKO O Lambda-processor Output Bit Clock

20

WCKO O Lambda-processor Output Word Clock

21

WCKO2 O

22

−

Ground Terminal

Test Setting Terminal 2 (Alpha-processor 1

Output shifts 12-bit.)

Test Setting Terminal 3 (Alpha-processor 2

Output stops.)

Test Setting Terminal 4 (Lambda-processor

Output stops.)

Output Mode Setting Terminal 2

LH

18bit

L

H

Alternate

20bit

Parallel

OMOD2

Lambda-processor Input Reversed

Polarity Terminal

Lambda-processor Output Word Clock 2

(for Canceling OFFSET on 1DAC

22

12

111

Pin

Pin Name I/O Descrption

No.

23−P24L O−/Lambda- processor Lch 24th bit Output *1, *2

24−P23L O−/Lambda- processor Lch 23rd bit Output *1, *2

25−P22L O−/Lambda- processor Lch 22nd bit Output *1, *2

26−P21L O−/Lambda- processor Lch 21st bit Output *1

27−P20L O−/Lambda- processor Lch 20th bit Output *1

−

O

O

Ip System Clock Select (384fs system /

OMOD1

24bit

Alternate

24bit

Parallel

28 VDD

29

SO2L/P19L

30 SO1L O Lambda-processor Lch(+) Output

31 SO1R O Lambda-processor Rch(+) Output

32

SO2R/P19R

33−P20R O−/Lambda- processor Rch 20th bit Output *1

34−P21R O−/Lambda- processor Rch 21st bit Output *1, *2

35−P22R O−/Lambda- processor Rch 22nd bit Output *1, *2

36−P23R O−/Lambda- processor Rch 23rd bit Output *1, *2

37−P24R O−/Lambda- processor Rch 24th bit Output *1, *2

38 TEST1N Ip Test Terminal 1 (Alpha-processor 1 stops

39 CKSLN

40 CKDV1 Ip System Clock Divider Select Terminal 1

41 CKDV2 Ip

42 XTI I X-TAL Oscillator Input Terminal

43 XTO O X-TAL Oscillato r Ou t pu t Ter minal

44 CKO O Clock Output Terminal

Power Supply Terminal

Lambda-processor Lch

Output /19th bit

Output *1

Lambda-processor Rch

Output/19th bit

Output *1

256fs system)

System Clock Divider Select Terminal 2

CKDV1

LH

192fs (CKSLN=H)

L

CKDV2

256fs (CKSLN=H)

192fs (CKSLN=H)

H

256fs (CKSLN=H)

768fs

384fs

(Ip = Input Terminal with pull-up)

*1: Outputted on OMOD1=L (18-bit Alternate Output or 20

-

bit Parallel Output)

*2: Internal Signal is outputted on OMOD1=H (24-bit Alternate Output or 24

or TEST4N is set to L.

-

bit Parallel Output) and one of TEST1N, TEST2N, TEST3N

17

Page 18

AVC-A1D/AVR-5700

ADSP-21061L

(DS: IC103, 110)

240

1

181

180

ADSP-21061L Terminal Function

Pin

Pin Name

No.

1 TDI

2 TRST

3 VDD

4 TDO

5 TIMEXP

6 EMU

7 ICSA

8 FLAG3

9 FLAG2

10 FLAG1

11 FLAG0

12 GND

13 ADDR0

14 ADDR1

15 VDD

16 ADDR2

17 ADDR3

18 ADDR4

19 GND

20 ADDR5

21 ADDR6

22 ADDR7

23 VDD

24 ADDR8

25 ADDR9

26 ADDR10

27 GND

28 ADDR11

29 ADDR12

30 ADDR13

31 VDD

32 ADDR14

33 ADDR15

34 GND

35 ADDR16

36 ADDR17

37 ADDR18

38 VDD

39 VDD

40 ADDR19

Pin

Pin Name

No.

41 ADDR20

42 ADDR21

43 GND

44 ADDR22

45 ADDR23

46 ADDR24

47 VDD

48 GND

49 VDD

50 ADDR25

51 ADDR26

52 ADDR27

53 EGND

54 MS3

55 MS2

56 MS1

57 MS0

58 SW

59 BMS

60 ADDR28

61 GND

62 VDD

63 VDD

64 ADDR29

65 ADDR30

66 ADDR31

67 GND

68 SBTS

69 DMAR2

70 DMAR1

71 HBR

72 DT1

73 TCLK1

74 TFS1

75 DR1

76 RCLK1

77 RFS1

78 GND

79 CPA

80 DT0

60

61

Pin

Pin Name

No.

81 TCLK0

82 TFS0

83 DR0

84 RCLK0

85 RFS0

86 VDD

87 VDD

88 GND

89 ADRCLK

90 REDY

91 HBG

92 CS

93 RD

94 WR

95 GND

96 VDD

97 GND

98 CLKIN

99 ACK

100 DMAG2

101 DMAG1

102 PAGE

103 VDD

104 BR6

105 BR5

106 BR4

107 BR3

108 BR2

109 BR1

110 GND

111 VDD

112 GND

113 DATA47

114 DATA46

115 DATA45

116 VDD

117 DATA44

118 DATA43

119 DATA42

120 GND

Pin

Pin Name

No.

121 DATA41

122 DATA40

123 DATA39

124 VDD

125 DATA38

126 DATA37

127 DATA36

128 GND

129 NC

130 DATA35

131 DATA34

132 DATA33

133 VDD

134 VDD

135 GND

136 DATA32

137 DATA31

138 DATA30

139 GND

140 DATA29

141 DATA28

142 DATA27

143 VDD

144 VDD

145 DATA26

146 DATA25

147 DATA24

148 GND

149 DATA23

150 DATA22

151 DATA21

152 VDD

153 DATA20

154 DATA19

155 DATA18

156 GND

157 DATA17

158 DATA16

159 DATA15

160 VDD

121

120

Pin

Pin Name

No.

161 DATA14

162 DATA13

163 DATA12

164 GND

165 DATA11

166 DATA10

167 DATA9

168 VDD

169 DATA8

170 DATA7

171 DATA6

172 GND

173 DATA5

174 DATA4

175 DATA3

176 VDD

177 DATA2

178 DATA1

179 DATA0

180 GND

181 GND

182 NC

183 NC

184 NC

185 NC

186 NC

187 NC

188 VDD

189 NC

190 NC

191 NC

192 NC

193 NC

194 NC

195 GND

196 GND

197 VDD

198 NC

199 NC

200 NC

Pin

Pin Name

No.

201 NC

202 NC

203 NC

204 NC

205 VDD

206 NC

207 NC

208 NC

209 NC

210 NC

211 NC

212 GND

213 NC

214 NC

215 NC

216 NC

217 NC

218 NC

219 VDD

220 GND

221 VDD

222 NC

223 NC

224 NC

225 NC

226 NC

227 NC

228 GND

229 ID2

230 ID1

231 ID0

232 LBOOT

233 RPBA

234 RESET

235 EBOOT

236 IRQ2

237 IRQ1

238 IRQ0

239 TCK

240 TMS

18

Page 19

LC89055W

(DS:IC531)

LC89055W Terminal Function

Pin

No.

Pin Name

1 DISEL I Data input terminal (select input pin of DIN0, DIN1)

2 DOUT O Input bi-phase data through output terminal

3 DIN0 I Amp built-in coaxial/optical input correspond data input terminal

4 DIN1 I Amp built-in coaxial/optical input correspond data input terminal

5 DIN2 I Optical input correspond data input terminal

6 DGND Digital GND

7 DVDD Digital power supply

8 R I VCO gain control input terminal

9 VIN I VCO free-run frequency setting input terminal

10 LPF O PLL loop filter setting terminal

11 AVDD Analog power supply

12 AGND Analog GND

13 CKOUT O Clock output terminal (256fs, 384fs, 512fs, X′tal osc., VCO free-run osc.)

14 BCK O 64fs clock output terminal

15 LRCK O fs clock output terminal (L: Rch, H: Lch, I2S: Reverse)

16 DATAO O Data output terminal

17 XSTATE O Input data detecting result output terminal

18 DGND Digital GND

19 DVDD Digital power supply

20 XMCK O X′tal osc. clock output terminal (24.576MHz or 12.288MHz)

21 XOUT O X′tal osc. connection output terminal

22 XIN I X′tal osc. connection output terminal

23 EMPHA O Emphasis information output terminal of channel status

24 AUDIO O Bit1 output terminal of channel status

25 CSFLAG O Top 40bit revise flag output terminal of channel status

26 F0/P0/C0 O Input fs cal. sig. out / data type out / input word inf. output terminal

27 F1/P1/C1 O Input fs cal. sig. out / data type out / input word inf. output terminal

28 F2/P2/C2 O Input fs cal. sig. out / data type out / input word inf. output terminal

29 VF/P3/C3 O Validity flag out / data type out / input word inf. output terminal

30 DVDD Digital power supply

31 DGND Digital GND

32 AUTO O Non PCM burst data transfer detect sig. output terminal

33 BPSYNC O Non PCM burst data preamble Pa, Pb, Pc, Pd sync sig. output terminal

34 ERROR O PLL lock error, data error flag output terminal

35 DO O CPU I/F read data output terminal

36 DI I CPU I/F write data input terminal

37 CE I CPU I/F chip enable input terminal

38 CL I CPU I/F clock input terminal

39 XSEL I Frequency select input pin of XIN X′tal osc. (24.576MHz or 12.288MHz)

40 MODE0 I Mode setting input terminal

41 MODE1 I Mode setting input terminal

42 DGND Digital GND

43 DVDD Digital power supply

44 DOSEL0 I Data output format select input terminal

45 DOSEL1 I Data output format select input terminal

46 CKSEL0 I Output clock select input terminal

47 CKSEL1 I Output clock select input terminal

48 XMODE I Reset input terminal

* For latch-up countermeasure, set digital (DVDD) and analog (AVDD) power on/off in the same timing.

I/O

CE

CL

XSEL

MODE0

MODE1

DGND

DVDD

DOSEL0

DOSEL1

CKSEL0

CKSEL1

XMODE

DIDOERROR

BPSYNC

DIN0

DIN1

DOUT

DISEL

AUTO

DIN2

DGND

DVDD

VF/P3/C3

F2/P2/C2

F1/P1/C1

F0/P0/C0

CSFLAG

AUDIO

EMPHA

XIN

XOUT

XMCK

DVDD

DGND

XSTATE

DATA0

LRCK

BCK

CKOUT

R

VIN

LPF

DVDD

DGND

AVDD

AGND

Function

AVC-A1D/AVR-5700

19

Page 20

AVC-A1D/AVR-5700

MSM32R0050-521GS

(DS: IC120)

49

64

MSM32R0050-521GS Terminal Function

Pin

Name

No.

1 Vcc Vcc

2 RFS0 I/O RFS for SHARC(64fs)

3 GND GND

4 N.C. I/O

5 GND I/O

6 RFS1 I/O RFS for SHARC(256fs)

7 GND I/O

8 RFS1A I/O Same as RFS1

9 GND I/O

10 N.C. I/O

11 GND I/O

12 DATA2 I/O Output data from SHARC

13 GND I/O

14 N.C. I/O

15 GND I/O

16 DATA3 I/O Data for L/R DAC

17 GND I/O

18 DATA4 I/O Data for C/SW DAC

19 GND I/O

20 DATA5 I/O Data for SL/SR DAC

21 GND I/O

22 DATA6 I/O Data for reserve DAC

23 GND I/O

24 GND I/O

25 LRCK1 I/O LRCK for all DAC

26 Vcc

27 N.C. I/O

28 GND GND

29 BCK1 I/O BCK for all DAC

30 GND I/O

31 GND I/O

32 MCK1 I/O MCK for all DAC

Symbol

Function

48

33

32

17

1

Pin

No.

33 GND I/O

34 N.C. I/O

35 N.C. I/O

36 N.C. I/O

37 N.C. I/O

38 N.C. I/O

39 N.C. I/O

40 Vcc Vcc

41 N.C. I/O

42 GND GND

43 N.C. I/O

44 N.C. I/O

45 N.C. I/O

46 N.C. I/O

47 N.C. I/O

48 N.C. I/O

49 N.C. I/O

50 LRCK0 I/O LRCK for RFS0 generation

51 GND I/O

52 GND I/O

53 BCK0 I / O BCK for RFS0 generation

54 GND I/O

55 Vcc Vcc

56 MCK0 I/O MCK for RFS1 generation

57 N.C. I/O

58 GND GND

59 /SRESET RESET System reset (L: Reset)

60 GND I/O

61 /CRESET I/O Clock reset (L: Reset)

62 GND I/O

63 GND I/O

64 /D_MUTE I/O DAC mute (L: Mute)

16

Name

Symbol

Function

20

Page 21

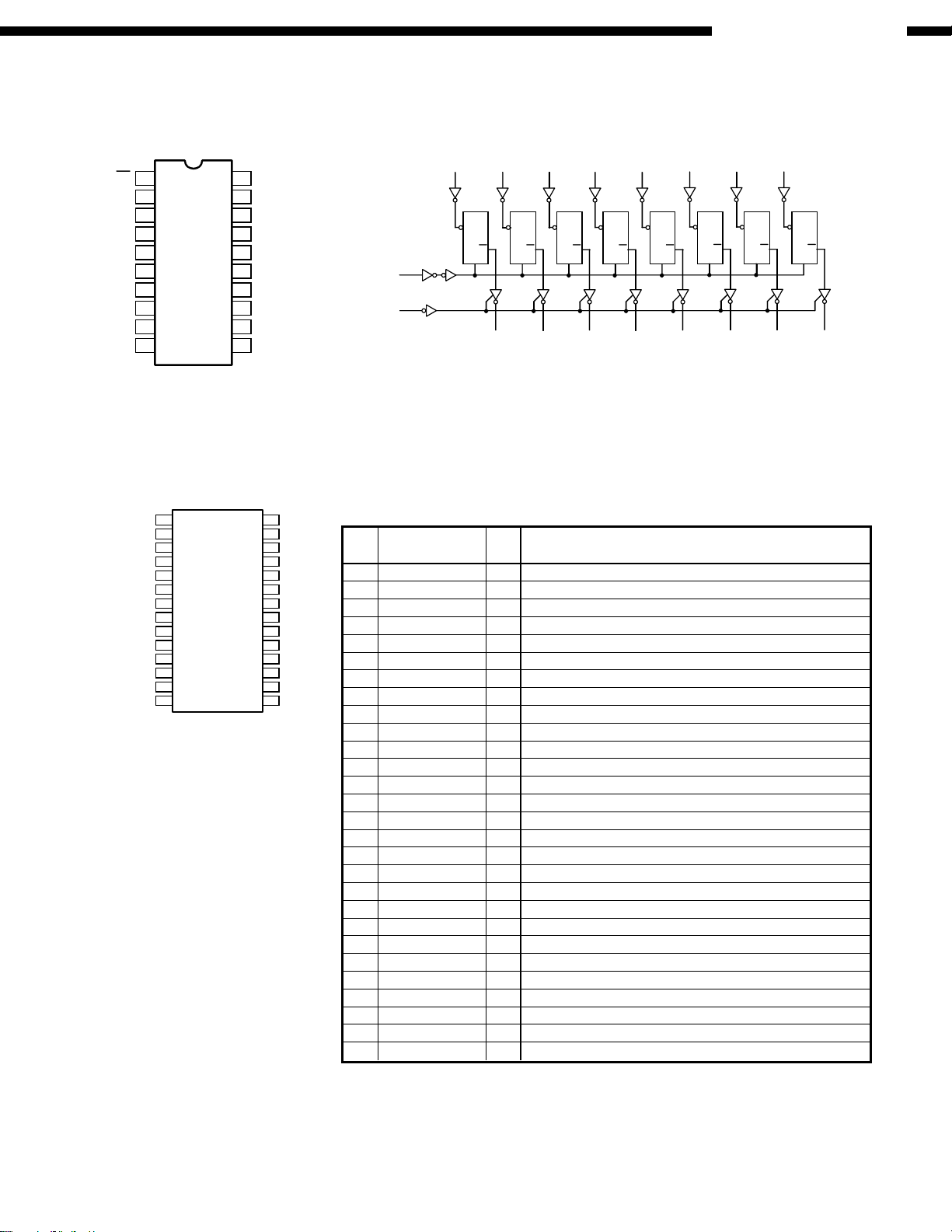

SN74AHCT573PW (DS: IC111)

SN74LV573APW (DS: IC113, 302)

AVC-A1D/AVR-5700

Vcc

OE

D0

D1

D2

D3

D4

D5

D6

D7

GND

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

LE

DF1704

(EX: IC305, 306)

DF1704 (EX: IC305, 306)

1

DIN

2

BCKIN

3

IIS

IW0

4

5

IW1

XTI

6

XTO

7

VSS

8

CLKO

9

MODE

10

MD/CKO

11

MC/LRIP

RST

12

13

14

ML/RESV

28

27

26

25

24

23

22

21

20

19

18

17

16

15

LRCIN

SRO

BCKO

WCKO

DOL

DOR

VDD

NC

OW1

OW0

SF1

SF0

DEM

MUTE

LE

OE

D0 D1 D2

234 56 789

D

D

Q

11

1

L

Q

L

1819

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

D3 D4 D5

D

D

Q

L

Q

L

17

D

Q

L

D

L

D6 D7

Q

D

D

Q

L

L

DF1704 Terminal Function

Pin

No.

1 DIN I Serial audio data input

2 BCKIN I Bit clock input for serial audio data

3 II S I Input audio data format select

4 IW0 I Input audio data word select

5 IW1 I Input audio data word select

6 XT1 I Oscillator input / external clock input

7 XTO O Oscillator output

8 Vss Digital GND

9 CLKO O System clock buffer output

10 MODE I Mode control select (H: Software, L: Hardware)

11 MD/CKO I Mode control, data / external clock (1/2) frequency select

12 MC/LRIP I Mode control, BCKIN / LRCK polarity select

13 ML/RESV I Mode control, LRCIN / spare

14 RST I Reset (L: DF & modulator reset)

15 MUTE I Mute control

16 DEM I De-emphasis control

17 SF0 I Sampling rate select for de-emphasis

18 SF1 I Sampling rate select for de-emphasis

19 OW0 I Output audio data word/format select

20 OW1 I Output audio data word/format select

21 NC No connection

22 VDD Digital power +5V

23 DOR O Rch serial audio data output

24 DOL O Lch serial audio data output

25 WCKO O Word clock output for serial audio data output

26 BCKO O Word clock output for serial audio data output

27 SRO I Filter response select

28 LRCIN I L/R clock input (fs)

Note: (1) Terminal 10~15: Schmitt trigger input with a pull-up resister

Name Function

I/O

(2) Terminal 3~5, 16~20, 27: Schmitt trigger input with a pull-down resister

(3) Terminal 1, 2, 28: Schmitt trigger input

(4) Terminal 3~5, 15~20, 27: Invalid when Mode (pin10) = H

(5) Terminal 11~13: Function varies according to Mode (pin10) H/L

Q

1213141516

21

Page 22

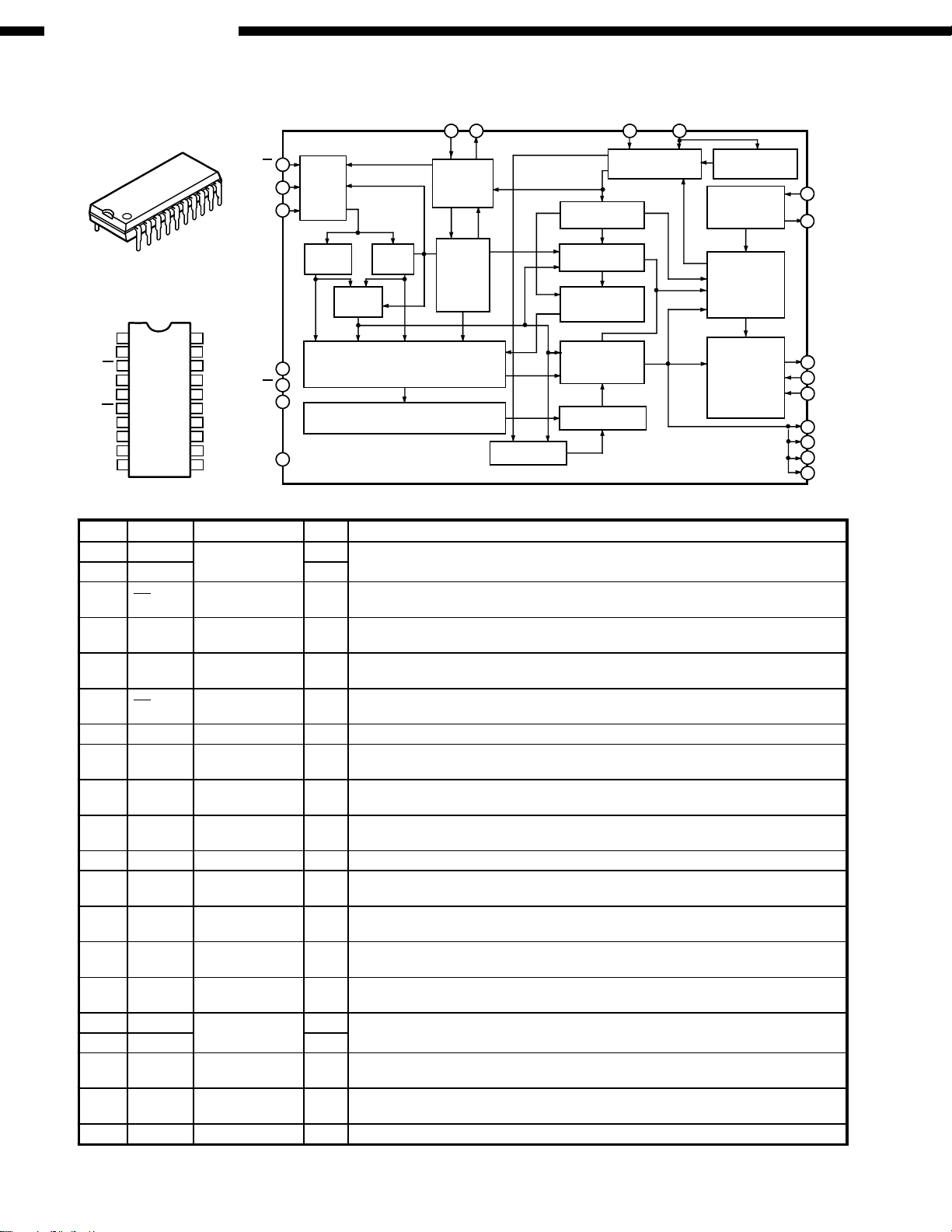

AVC-A1D/AVR-5700

M35015-204SP (VI:IC310)

10

20

1

OSC1

OSC2

CS

SCK

SIN

AC

V

DD2

CVIDEO

LECHA

CVIN

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

V

DD1

VERT*

HOR*

OSCIN

OSCOUT

P3

P2

P1

P0

Vss

SCK

SIN

V

Vss

V

1 2 19 18

3

CS

DD1

AC

DD2

4

5

20

6

11

7

INPUT

CONTROL

CIRCUIT

DATA

CONTROL

CIRCUIT

ADDRESS

CONTROL

CIRCUIT

INDICATION

CONTROL

REGISTER

INDICATION RAM

INDICATION CHARACTER ROM

INDICATION

OSCILLATOR

TIMING

GENERATOR

BLINKING CIRCUIT

IINDICATION LOCATION

DETECTION CIRCUIT

READ OUT ADDRESS

CONTROL CIRCUIT

CONTROL CIRCUIT

SWITCHING CIRCUIT

H COUNTER

INDICATION

SHIFT REGISTER

HOR*VERT*OSC2OSC1

SYNC SIGNAL

SYNC SIGNAL DIS-

CRIMINATING CIRCUIT

OSC CIRCUIT

FOR SYNC SIGNAL

GENERATION

TIMING

GENERATOR

NTSC

VIDEO OUTPUT

CIRCUIT

M35015-204SP Terminal Function

Pin No. Symbol Name I/O Function

1 OSC1 Osc. circuit ext. I External terminal for indication oscillat or circ uit. Standard OSC. freq. is approx. 7MHz.

2 OSC2 terminal . O With this OSC. freq., decides horizontal indicatin and chara ct er width.

3 CS Chip sel ect input I

4 SCK Serial clock input I

5 SIN Serial data input I

6 AC A uto-clear input I

7V

DD2

8CVIDEO

9 LE CHA

10 CVIN

Power supply

Combined

video output

Character level

input

Combined video

input

11 Vss Ground Ground terminal. Connect to GND.

12 P0 Output port p0 O

13 P1 Output port P1 O

14 P2 Output port P2 O

15 P3 Output port P3 O

16 OSCOUT O Terminal for external use of sync signal OSC. circuit. Use the freq.: 14.32MHz at NTSC

17 OSCIN I sys tem , 17.73MHz at PAL. system, 14.30MHz at MPAL system.

18 HOR*

19 VERT*

20 V

DD1

Ext. terminal

for sync s ig.

OSC. Circuit

Horizontal sync

signal

Vertical sync

signal

Power supply I Power supply terminal of digital system. Connect to +5V.

Chip select terminal and turns to “L” when transfer serial data.

Hysteresis input. Pull up resis tor i s built-in.

Takes in serial data of SIN at SCK rise when CS terminal is in “L”.

Hysteresis input. Pull up rersis t is built-in.

Serial input of register for indicati on control and data, and address for indication data

memory. Hysteresis input. Pull up rersi stor is built-in.

Resets internal circuit of IC at “L” mode.

Hysteresi input. Pull up resistor is built-in.

Power supply terminal of analog system. Connect to +5V.

Output terminal of combined video signal. Outputs 2Vp-p combined signal. Character

O

output, etc. Overlap CVIN signal and outputs at superimpose.

Input terminal deciding character output level in combined video signal. color of character

I

is white.

Input terminal of external combine d video signal.

I

Character output etc. overlap this external com bi ned video signal.

General output or character background signal BL NK1* output is s wi tc hable.

Polarity can be selected at ROM mask.

General output or character background signal CO1* output is switchable.

Polarity can be selected at ROM mask.

General output or character background signal BLNK2* output is switchable.

Polarity can be selected at ROM mask.

General output or character background signal CO2* output is switchable.

Polarity can be selected at ROM mask.

Inputs horizontal sync sig nal .

I

Hysteresis input.

Input vertical sync signal. Hysteresis input. Polarity can be selec ted at ROM mask.

17

16

8

9

10

12

13

14

15

OSCIN

OSCOUT

CVIDEO

LECHA

CVIN

P0

P1

P2

P3

22

Page 23

TC4094BF

(MA: IC202, 203)

AVC-A1D/AVR-5700

IC202

16

8

Port

Q1 INA Video input switching

1

Q2 INB Video input switching

Symbol Function

Q3 INC Video input switching

Q4 RECA Video output switching

Q5 RECB Video output switching

Q6 RECC Video output switching

STROBE

DATA

CLOCK

Q1

Q2

Q3

Q4

V

SS

1

2

3

4

5

6

7

8

16

VDD

15

OE

14

Q5

13

Q6

12

Q7

Q8

11

Q'

10

S

Q

9

S

Q7 V-1 Video REC OUT INH control

Q8 V-2 Video REC OUT INH control

IC203

Port

Symbol Function

Q1 EXT A_/B EXT.IN relay A or B select (L: A select)

Q2 STEREO_/DSP DSP DA OUT or NOT relay switching (L: NOT)

Q3 T MUTE Tuner mute output (H: Mute)

Q4 TONE_ Tone control (H: ON / DIRECT, THX, TEST, TONE, PEAK LIMIT)

Q5 INT_/EFFECT EFFECT or NOT relay switching (L: NOT)

Q6 INT_/EXT EXT A, B or NOT relay switching for front (L: INT)

Q7 NOT_/DIRECT DIRECT or NOT relay output switching (L: NOT)

Q8 DIRECT DVD/CD_ DIRECT DVD or DIRECT CD relay switching (L: CD)

TC9273N-004 (AU: IC111)

TC9273N-004 (AU: IC111)

TC9273N-007 (TO: IC705) TC9273N-007 TC9273N-004

TC9273N-007 (TO: IC705)

TC9273N-007

TC9273N-004

14

28

1

TC9273N Terminal Function

TC9273N Terminal Function

1

Vss

S1

2

S2

3

4

S3

S4

5

6

S5

S6

7

8

S7

9

S8

10

S9

11

S10

12

13

GND

14

CK

S1

S2

S3

S4

S5

S6

S7

S8

S9

S10

DATA

V

STB

28

DD

27

26

25

24

23

22

21

20

19

18

17

16

15

1

Vss

S1

2

S2

3

4

S3

S4

5

6

S5

S6

7

8

S7

9

S8

10

S9

11

S10

12

13

GND

14

CK

S1

S2

S3

S4

S5

S6

S7

S8

S9

S10

DATA

V

STB

28

DD

27

26

25

24

23

22

21

20

19

18

17

16

15

Pin No.Symbol Name Function Note

1 Vss−Power Terminal

13 GND Digital Gr ou nd

28 VDD +Power Terminal

2~12

S1~11 I/O Terminal Input terminal of analog switch.

17~27

14 CK Clock Input Clock input for data transfer.

15 DATA Data Input Serial input for switch setting.

16 STB Strobe Input Strobe input for data writing.

Dual Power Use: VDD = 8.0~17 V Signal Power Use: VDD = 8.0~18V

GND = 0V Vss = GND = 0V

Vss = −8.0~17V

Low level

Border Inpu t

Terminal

23

Page 24

AVC-A1D/AVR-5700

LC75721E (VI: IC102)

G 7

G 8

G 9

G 10

G 11

AA8/G12

AA7/G13

AA6/G14

AA5/G15

AA4/G16

AM 5

AM 6

AM 7

AM 8

AM 9

AA 3

AM 10

CL

CE

RES

V

OSCI

OSCO

Vss

TEST

V

G1

G2

G3

G4

G5

G6

48

49

DI

DD

FL

64

1

AM 1

AM 2

AM 3

AM 4

PCM1716E (EX: IC307)

DIN

CLKO

XTI

XTO

DGND

V

EXTR

NC

1

2

3

4

5

6

7

8

DD

9

10

11

12

13

14

LRCIN

BCKIN

VCC2R

AGND2R

VOUTR

AGND1

AA 2

AA 1

AM 35

AM 34

AM 33

33

32

AM 17

AM 18

AM 19

AM 20

AM 21

AM 22

AM 23

AM 24

AM 25

AM 26

AM 27

AM 28

AM 29

AM 30

AM 31

AM 32

17

16

AM 11

AM 12

AM 13

AM 14

AM 15

AM 16

Symbol

DD

V

Vss

FL

V

DI

CL

CE

OSCI

OSCO

RES

AM1~AM35

AA1~AA3

Power terminal +5V

Power terminal GND

Power terminal FL drive

Serial data transfer terminal

DI: Data

CL: Clock

CE: Chip enable

External CR connecting terminal

System reset terminal

Anode output terminal

Function

AA4/G16

AA5/G15

AA6/G14

Anode/Grid output terminal

AA7/G13

AA8/G12

G1~G11 Grid output terminal

TEST LSI test terminal

Pin

28

27

26

25

24

23

22

21

20

19

18

17

16

15

M/L IIS

M/L IIS

MD/DM0

MUTE

MODE

CS/IWO

RST

ZERO

Vcc2L

AGND2L

EXTL

NC

VOUTL

Vcc1

Name I/O Description

No.

1 LRCIN I

Left & Right clock input. This clock is equal to the sampling rate-fs. *1

2 DIN I Serial audio data i nput.

3 BCKIN O Bit clock input for serial audio data.

4CLKO

5 XTI

Buffered output of oscillator. Equivalent to system clock.

Oscillator input (Extermal c l ock input).

6 XTO I Oscillator output.

7 DGND I Digital ground.

8 VDD Digital power. +5V

9 VCC2R I Digital power. +5V

10 AGND2R Analog power. +5

11 EXTR R-ch, common pin of analog amp.

12 NC

13 VOUTR

No connection.

R-ch, analog volt age output of audio signal.

14 AGND1 Analog ground

15 VCC1 I Analog power. +5V

16 VOUTL I L-ch, analog voltage output of audio signal.

17 NC I Non connection.

18 EXTL I /O L-ch, common pin of analog output amp.

19 AGND2L I/O Analog ground.

20 VCC2L I/O Analog power. +5V

21 ZERO O Zero data flag.

22 RST I

23 CS/IWO I

24 MODE

Reset. When this pin is low, the DF & modulations are held in reset. *2

Chip select / I nput format selection

When this pin is low, the MODE Control is eff ective. *3

Mode control Select. (H: Software, L: Hardware) *2

25 MUTE Mute contr ol. *2

26

27

MD / DM0

MC / DM1

Mode control, data / De-emphasis selecti on 1. *2

Mode control, BCK / De-emphasis selection 2. *2

28 ML / IIS Mode control, WDCK / input format selection. *2

NOTE1: Pins 1, 2, 3; Schmitt Trigger input.

NOTE2: Pins 22, 24, 25, 26, 27, 28; Schmitt Trigger input with pull-up resister.

NOTE3: Pin 23; Schmitt trigger input with pull-down resister.

24

Page 25

BR62256F-70LL (DS: IC516)

AVC-A1D/AVR-5700

28

A0

A1

A2

A3

A4

A5

A6

A14

I/O 0

I/O 7

1

Address

Buffer

14

Low

Decode

Input

data control

VCCWEA13A8A9

26

252423222120191817

27

28

1

2

3

5

4

A7A6A5A4A3A2A1

A14

A12

262144 bit

(512x512)

Memory Cell Array

Column Switch

Column Decode

A11OEA10CSI/O7

678

9

10

A0

data control

I/O6

I/O5

12

11

I/O0

I/O1

Output

I/O4

16

13

A/02

I/O3

15

14

VSS

Address Buffer

A7

CS

OE

Control Buffer

WE

BR62256F-70LL Terminal Function

BR62256F-70LL Terminal Function

Pin No. Symbol I/O Function

1~10 A0~ A 9 I 32K byte memory address input.

11~13, I/00~I/02 I/O 8 bit data input/output.

14 Vss GND

15~19 I/03~I/07 I/O 8 bit data input/output.

20 CS I Chip select control input.

21 A10 I 32K byte memory address input.

22 OE I Output enable control input.

23~26 A11~A14 I 32K byte memory address input.

27 WE I Write enable control input.

28 Vcc

+5V power supply.

A12

A13

25

Page 26

AVC-A1D/AVR-5700

AK5351 (DS: IC527)

AINR+

AINR-

VREF

VA

AGND

AINL+

AINL-

TST1

HPFE

TST2

TST3

VD

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

VB

SMODE1

CMODE

SDATA

FSYNC

LRCK

SCLK

MCLK

PD

SMODE2

TST4

DGND

VREF

AINL+

AINL-

AINR+

AINR-

AGNDVAVD

Voltage

Reference

∇

Modulator

∇

Modulator

DGNDVBCMODE

Clock Driver

Σ

Σ

AK5351 Terminal Function

Pin

No.

1 AINR+ I Rch analog non-invert ed input pin.

2AINR

3 VREF O Vref. output pin (VA- 2.6V)

4VA

5AGND

6 AINL+ I Lch analog non-inverted input pin

7AINL

8 TST1 Test pin

9 HPFE I Hi-pass filter enable pin, "H": ON, "L": OFF

10 TST2 Test pin

11 TEST3 Test pin

12 VD

13 DGND

14 TST4 Test pin

15 SMODE2 I Interface clock select pin

16 PD I Power down pin, "L": power down mode

17 MCLK I Master clock input pin, CMODE="H": 384fs , "L": 256fs

18 SCLK I/O Serial data clock pin

19 LRCK I/O Input channel select pi n

20 FSYNC I/O Frame sync clock pin

21 SDATA O Serial data output pin

22 CMODE I Master clock selec t pin, "H": MCLK=384fs, "L": 256fs

23 SMODE2 I Interface clock select pin

24 VB

Symbol I/O Function

−

−

I Rch analog inverted i nput pin

Analog part power supply pin (+5V)

Analog ground pin

I Lch analog inverted input pin

Digital part power supply pin (+5V)

Digital ground pin

Bulk power supply pin (+5V)

PD

MCLK

SMODE2

TST1

HPFE

SMODE1

SCLK

LRCK

Serial Output

Interface

Digital Decimation

Filter

TST2

TST3

FSYNC

SDATA

TST4

NJM2229S (VI: IC312)

1

26

16

15

6

14

13

Sync Sepa

8

Sync Det

Phase

Det

Vsync Sepa

32fH

VCO

1/32

Page 27

PM4007A (DS: IC512)

80

81

100

AVC-A1D/AVR-5700

51

50

GND

31

30

1

VDD

RESET

OSCON

DATA

MCK

ML TB

IDST

IDCK

IDO

TM0

ECCK

DEY

DRY

MSYC

TM1

TM2

TM3

XOUT

XIN

XNET

GND

VDD

AVDD

AGND

BUNR1

TMS

ADST1

ADST0

SYST1

SYST0

WINGT

99989796959493929190898887868584838281

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

A0

17

A1

18

A2

19

A3

20

A4

21

A5

22

23

24

25

26

27

28

29

A6

30

31323334353637383940414243444546474849

GND

C9M

DOUTB

DOUT

DIN

TM4

CPIN

CMIN

AGND

AVDD

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

GND

VDD

MUTI

C1F0

C1F1

C2F0

C2F1

TI8

DASEL

DAIN

DAOUT

DASYO

VLDY

TI5

MUTO

PDDIS

TI4

PD0

TD0

TRP

TCK

TLDB

TI3

TI2

VOUT

VIN

TI1

GND

VDD

D0

VDD

CPIN

CMIN

DOUT

DOUTB

P0DIS

PDO

VO

RESET

A7

VDD

GND

9KHz

SYNC Detection

& Protection

Generator

S / P

Timing

9.216MHz

DAI Controller

Demodulator

46.08MHz

Oscillator

Phase

Comparator

VI

1/2048

dividing sync

1/2

A8

SW

A9

A14

A13

WEB

Address

Generator

Correction

A12

GND

Error

A11

D7D6D5D4D3D2D1

A10

OEB

A (0~14)

DB (0~7)

OEB

WEB

C2F1

C2F0

C1F1

C1F0

MUT0

DAOUT

OSCON C9M

MUTI DAIN

DASEL

27

Page 28

AVC-A1D/AVR-5700

TC9274N-011 (AU: IC110)

42

1

MC74HC4053N (VI: IC309)

8

16

1

21

Enable

GND

S1S2S3S4S5S6S7S8S9

41

V

DD

42

SS

V

1

2

3839

40

3456

35

36

37

18 bit Latch Circuit (Rch)

(Lch) Same as Rch

89

7

S1S2S3S4S5S6S7S8S9

S10

S11

S12

S13

S14

S15

S16

S17

S18

26

25

17 18 19

S15

S16

S17

24

23

STB

22

DATA

21

CK

Level Shift + Shift Register Circuit

20

GND

S18

S10

12 13

S11

29

28

3031

14 15

S12

S13

27

16

S14

32

34

33

10 11

Control Inputs

Select

Enable

C

1

Y1

2

Y0

3

Z1

4

Z

5

Z0

6

EE

7

V

8

16

Vcc

15

Y

14

X1

13

X

12

X0

11

C

10

A

9

B

L

L

L

L

L

L

L

L

H

B

L

L

L

L

H

L

H

L

L

H

L

H

H

H

H

H

X

X

A

L

H

L

H

L

H

L

H

X

ON Switches

Z0

Z0

Z0

Z0

Z1

Z1

Z1

Z1

None

Y0

X0

Y0

X1

X0

Y1

X1

Y1

X0

Y0

X1

Y0

X0

Y1

X1

Y1

X = Don't Care

TC4051BP (VI: 304, 305, 403, 404, 407, 408)

1

4

2

6

3

COM

4

7

5

INH

V

Vss

5

6

7

EE

8

OUT C IN

OUT C IN

OUT C IN

OUT C IN

OUT C IN

OUT C IN

OUT C IN

OUT C IN

EE

V

INH

8

16

1

DD

V

A

B

C

LOGIC LEVEL CONVERTER

8

Vss

HD14066BP (VI: IC307, 411)

16

DD

V

15

2

14

1

13

0

12

3

11

A

10

B

9

C

0

1

2

3

4

5

6

7

COMMON

14

IN 1

OUT 1

OUT 2

IN 2

CONTROL 2

CONTROL 3

VSS

1

1

2

3

4

5

6

7

IN

OUT

IN

7

VDD

14

C

IN

OUT

C

C

OUT

C

OUT

13

CONTROL 1

CONTROL 4

12

IN 4

11

OUT 4

10

IN

OUT 3

9

IN 3

8

28

Page 29

PCM1704U (EX: IC309~313)

DATA

BCLK

NC

-V

DD

DGND

+V

DD

WCLK

NC

20BIT

INVERT

1

2

3

4

5

6

7

8

9

10

-V

20

REF DC

19

NC

18

SERVO DC

17

AGND

16

AGND

15

I

OUT

14

NC

13

12

BPO DC

11

+V

W29EE011P-90 (DS: IC303)

A12

A15

A16NCVDDWENC

3132

A7

A6

A5

A4

A3

A2

A1

A0

DQ0

4

5

6

7

8

9

10

11

12

13

14 15 16

23

1

17 18

30

29

28

27

26

25

24

23

22

21

19 20

AVC-A1D/AVR-5700

Terminal Function

CC

CC

Pin No. Name Function

DATA

1

BCLK

2

NC

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

V

−

DGND

+V

WCLK

NC

20BIT

INVERT

+V

BPO DC

NC

I

OUT

AGND

AGND

SERVO DC

NC

REF DC

V

−

I/O

Serial audio data input

IN

Bit clock input for serial audio data

IN

No connection

DD

DD

CC

CC

Digital power −5V

Digital GND

Digital power +5V

IN

Data latch enable input

No connection

IN

Input data word select

IN

Input data polarity (phase) select

Analog power +5V

Bipolar offset de-coupling capacitor

No connection

OUT

Audio signal analog current output

Analog GND

Analog GND

Servo amp de-coupling capacitor

No connection

Band gap ref. de-coupling capacitor

Analog power −5V

Terminal Function

Name Function

A14

A13

A8

A9

A11

OE

A10

CE

DQ7

A0 - A16

DQ0 - DQ7

CE

OE

WE

V

DD

GND

NC

Address input

Data in/output

Chip enable

Output enable

Write enable

Power terminal

GND

No connection

DQ1

DQ2

GND

DQ3

DQ4

DQ5

DQ6

TC9459F

(EX: IC503, 504, 510, 523, 525, 529, 530)

24

1

12

NC

L-OUT

L-IN

L-LD1

L-LD2

L-A-GND

NC

CS1

NC

GND

CK

10

11

12

3

2

4

5

6

7

8

9

50kΩ/

91STEP

VR

V

SS

1

L-ch 7 to 91 decoder R-ch 7 to 91 decoder

L-ch latch circuit R-ch latch circuit

Shift register (24 Bit)

Level shift circuit

V

DD

24

Same as L-ch

22

23

21

20

19

18

17

16

15

14

13

NC

R-OUT

R-IN

R-LD1

R-LD2

R-A-GND

NC

CS2

NC

STB

DATA

29

Page 30

AVC-A1D/AVR-5700

TC9184AP (TO: IC602, 604, 606)

8

16

1

TREBLE-

TREBLE+

TC55V1664BFT-12 (DS: IC108, 112)

A4

A3

A2

A1

A0

CE

I/O1

I/O2

I/O3

I/O4

V

DD

GND

I/O5

I/O6

I/O7

I/O8

WE

A15

A14

A13

A12

N.C.

10

11

12

13

1

2

3

4

5

6

7

8

9

14

15

16

17

18

19

20

21

22

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

A5

A6

A7

OE

UB

LB

I/O16

I/O15

I/O14

I/O13

GND

V

DD

I/O12

I/O11

I/O10

I/O9

N.U.

A8

A9

A10

A11

N.C.

BASS+

BASS-

COM

VSS

VDD

16

1

2

Analog switch

3

4

5

6

Ladder resister

Ladder resister

Analog switch

Terminal Function

Symbol Function Name

A0~A15

I/O1~I/O16

CE

WE

OE

LB, UB

DD

V

GND

N.C.

N.U.

Address input

Data in/output

Write enable input

Output buffer control input

Data byte control input

Power terminal (+3.3V)

Data byte control input

GND

No connection

Unusable (input)

GND

78

13 bit latch circuit

13 bit latch circuit

DATA

CK

9

Level shift

20 bit Shift register circuit

Code

detect

circuit

STB

10

BASS+

15

Analog switch

Ladder resister

14

BASS-

COM

13

12

TREBLE-

Analog switch

Ladder resister

11

TREBLE+

TC58FVT800FT-12 (DS: IC119)

1

A15

2

A14

3

A13

4

A12

5

A11

6

A10

7

A9

8

A8

9

NC

10

NC

11

WE

12

RESET

13

NC

14

NC

A18

A17

15

16

17

18

A7

19

A6

20

A5

21

A4

22

A3

23

A2

24

A1

RDY/BSY

30

48

A16

47

BYTE

46

SS

V

45

DQ15/A-1

44

DQ7

43

DQ14

42

DQ6

41

DQ13

DQ5

40

DQ12

39

DQ4

38

V

DD

37

DQ11

36

DQ3

35

DQ10

34

DQ2

33

DQ9

32

DQ1

31

DQ8

30

DQ0

29

OE

28

V

SS

27

CE

26

A0

25

Terminal Function

Symbol Function Name

A0~A18

DQ0~DQ14

DQ15/A-1

CE

OE

BYTE

WE

RDY/BSY

RESET

NC

V

DD

V

Address input

Data in/output

Data in/output/Address input

Chip enable input

Output enable input

Word/bute select input

Write enable input

Ready/busy output

Hardware reset input

No connection

Power

SS

GND

Page 31

TC74VHC541FT (DS: IC114)

TC74VHCT541AFT (DS: IC116)

AVC-A1D/AVR-5700

20

1

TC74VHC123FT

(DS: IC517, 523)

SN74AHC157PW

(DS: IC525)

TC74HCT157AF

(EX: IC301, 303)

SN74HC151NS

(DS: IC509, 510, 513)

16

1

8

10

1

G1

2

A1

3

A2

4

A3

5

A4

6

A5

7

A6

8

A7

9

A8

10

GND

1 CLR

1Q

2Q

2Cex1

2Rext / Cext

GND

20

Vcc

19

G2

18

Y1

17

Y2

16

Y3

15

Y4

14

Y5

13

Y6

12

Y7

11

Y8

TC74VHC123FT SN74AHC157PW

TC74HCT157AF

1A

1B

1

2

3

4

5

6

7

8

CLR

QQ

QQ

CLR

16

15

14

13

12

11

10

9

Vcc

1Rex / Cext

1Cext

1Q

2Q

2CLR

2B

2A

SELECT

GND

1A

2A

2Y

1B

1Y

2B

1

2

3

4

5

6

7

8

SEL

16

15

14

13

12

11

10

Vcc

ST

4A

4B

4Y

3A

3B

3Y

9

SN74HC151NS

3

1

2