Dell Inspiron N411Z Schematic

5

4

3

2

1

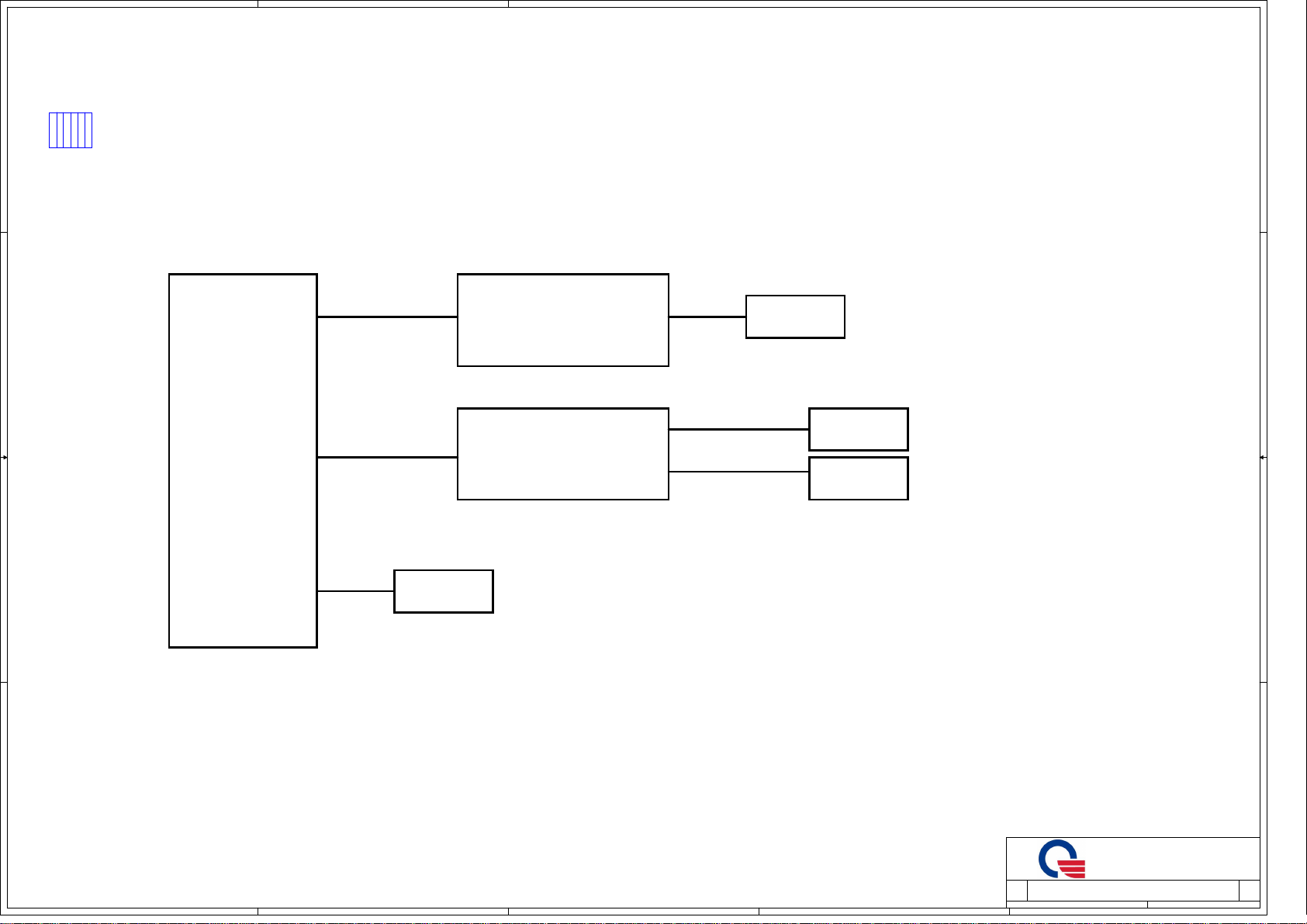

R05 DB USB3.0*2, RJ45 and Combo Jack Block Diagram

Label

D D

Label

Label

Label

PCIE

AR8152B

C C

DB_Connector

50 pin

PCIE

NEC

UPD720200A

B B

PG 02

USB3.0

USB3.0

RJ45

CONN

PG 02

USB3.0

CONN

USB3.0

CONN

PG 04

PG 04PG 03

Combo Jack

PG 05

PG 2

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, June 17, 2011

Date: Sheet of

Friday, June 17, 2011

Date: Sheet of

5

4

3

2

Friday, June 17, 2011

PROJECT :

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

R05

R05

R05

1A

1A

1 5

1 5

1

1 5

1A

5

4

3

2

1

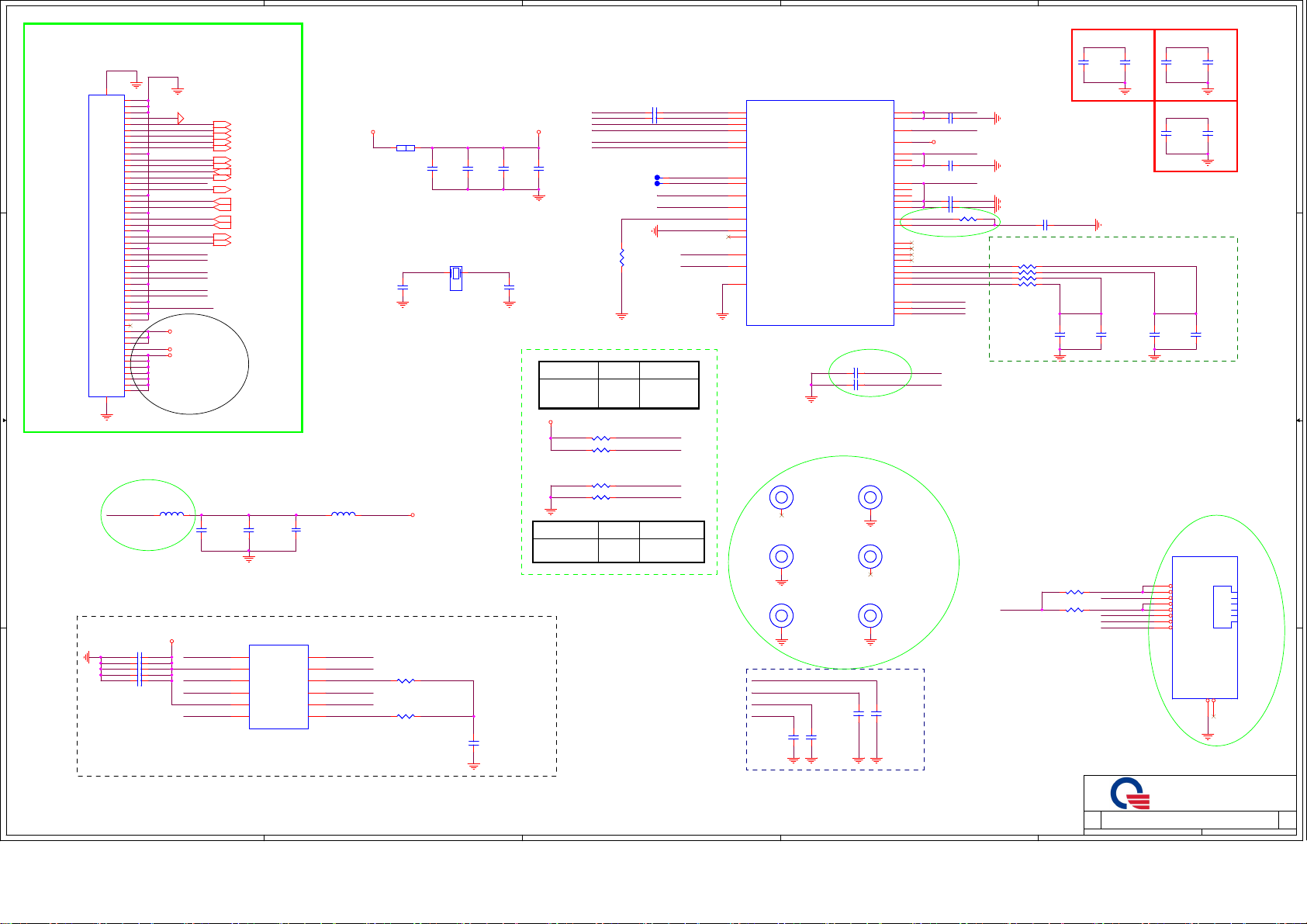

Close to Pin37

LAN + USB3.0 + Combo Jack CONNECTOR

51

CON1

CON1

FPC/FFC_50 P

D D

C C

B B

FPC/FFC_50 P

2/10: modify pin define, same as MB.

2/14: change QPN to DFFC50FR015.

2/14: change footprint from lap-yba-fpc-019-p03-50p-l to fh52-50s-0_5sh-50p-l-smt (follow GM7C).

51

52

52

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

*4.7uH/70 0mA_8_NC

*4.7uH/70 0mA_8_NC

L2

L2

2/15: follow SS8 ST2 schematic (use 0805).

TRANSFORMER

A A

C27 close to L8206.

C28 and C29 close

to Pin7 of transformer.

C30 and C31 close to

Pin2 of transformer.

C271U/6.3V_4 C271U/6.3V_4

C280.1U/10V_4 C280.1U/10V_4

C290.1U/10V_4 C290.1U/10V_4

C30100P/50V_4 C30100P/50V_4

C31100P/50V_4 C31100P/50V_4

AVDD_CEN

3/31 Change CON3

footprint : lap-yba-fpc-019-p03-50p-l

AGND

PCIE_CLK_REQ5#

CLK_PCIE_LANN

CLK_PCIE_LANP

PCIE_TXN6

PCIE_TXP6

PCIE_RXN6

PCIE_RXP6

EC_PCIE_WAKE#

+3.3V_SUS

+5V_ALW

+5V_SUS

PCIE_W AKE# 3

PCIE_CLK_REQ4# 3

CLK_PCIE_USB30P 3

CLK_PCIE_USB30N 3

PCIE_RXN4 3

PCIE_RXP4 3

4/2

PT

Close to pin40

+VDDCT+1.7V_LX

12

C24

C24

0.1U/10V

0.1U/10V

MDI0-

MDI0+

MDI1+

MDI1-

EXT_MIC_L 5

JACK_SENSE 5

+5VA_R 5

HPOUT_RB 5

HPOUT_LB 5

SMIB 3

USB_SIDE_EN 4

PLTRST# 3

PCIE_TXN4 3

PCIE_TXP4 3

C25

C25

1U/6.3V

1U/6.3V

Rotate for EMI

U2

16

RX+

15

CT

14

RX-

9

TX-

10

CMT

11

TX+

NS0013B LFU2NS0013B LF

C26

C26

10U/6.3V/X5R_6

10U/6.3V/X5R_6

RD+

RD-

CT

TD+

TD-

CT

These Caps close LAN Chip VDD33 pins

Close to pin40

SJ1 SJ_060 3SJ1 SJ_060 3

2

112

C9

10UC910U

Y1

1 2

C18

C18

33P/50V/NPO_4

33P/50V/NPO_4

25MHzY125MHz

PCIE_RXN6

C1 0.1U/ 10VC1 0.1U/ 10V

PCIE_RXP6

C2 0.1U/ 10VC2 0.1U/ 10V

+3.3V_LA N+3.3V_SUS

C11

C11

C10

C10

1U

1U

10

10

LAN_XTAL2LAN_XTAL1

0.1U/ 10V

0.1U/ 10V

10

10

C19

C19

33P/50V/NPO_4

33P/50V/NPO_4

C12

C12

1000P

1000P

PCIE_TXN6

PCIE_TXP6

CLK_PCIE_LANN

CLK_PCIE_LANP

TP1TP1

TP2TP2

R2

2.37K/FR22.37K/F

PCIE_RXN6 _C

PCIE_RXP6_C

LAN_SMBDAT

LAN_SMBCLK

PLTRST#

EC_PCIE_WAKE#

PIN 28 NC for AR8152

LAN_XTAL1

LAN_XTAL2

2/14: Follow UM8C (DB1)

SWR LDO

LED_LINK 1 0

Default

+3.3V_LA N

R14 *5.1K_NCR14 *5.1K_NC

R13 *5.1K_NCR13 *5.1K_NC

LED_ACT

12

LED_LINK

12

Pin 38,39 internal pull up 36k ohm

R7 4.7K/J_4R7 4.7K/J_4

L1 close to U1

L1

L1

1 2

HCB1608K F-181T15_6

HCB1608K F-181T15_6

LAN_MX0-

1

LAN_MX0+

3

TXCT0

2

LAN_MX1-

6

LAN_MX1+ MDI0+

8

TXCT1

7

AVDD_CEN

R11 75/FR11 75/F

R12 75/FR12 75/F

CRB use 2KV

TXCT0_R

2/21 P/N CH2100GKI04 EOD

change to CH2100GKI12

C34

C34

1000P/3KV/X7R_1 8

1000P/3KV/X7R_1 8

R8 4.7K/J_4R8 4.7K/J_4

Overclock enable disable

LED_ACT 1 0

Default

LED_ACT

12

LED_LINK

12

U1

U1

29

TX_N

30

TX_P

36

RX_N

35

RX_P

32

REFCLKN

33

REFCLKP

26

SMDATA

25

SMCLK

2

PERSTn

3

WAKEn

10

RBIAS

27

TESTMODE

28

TEST_RST

8

XTLI

7

XTLO

41

GND_PAD

AR8151/A R8152

AR8151/A R8152

*6.8P/50V_4_NC

*6.8P/50V_4_NC

Atheros

Atheros

AR8151

AR8151

AR8152

AR8152

H1

1

H3

H3

1

PAD1

PAD1

1

MDI1+

MDI1-

MDI0-

C35

C35

DVDDL_REG

AVDDH_REG

AVDDL_REG

VDDCT_REG/CLKREQn

CLKREQn/LED2

C88 0.1U/ 10VC88 0.1U/ 10V

C89 1U/0603 /10VC89 1U/0603 /10V

C88, C89 Close to U1,Pin4

h-c118d118nH1h-c118d118n

h-tc335bc276d118p2

h-tc335bc276d118p2

spad-pad-1np

spad-pad-1np

C32

C32

*6.8P/50V_4_NC

*6.8P/50V_4_NC

C36

C36

*6.8P/50V_4_NC

*6.8P/50V_4_NC

DVDDL

LX

VDD33

AVDDH

AVDDH

AVDDL

AVDDL

AVDDL

AVDDL

VDDCT

TRXN[3]

TRXP[3]

TRXN[2]

TRXP[2]

TRXN[1]

TRXP[1]

TRXN[0]

TRXP[0]

LED0

LED1

H2

H2

h-tc217bc276d94p2

h-tc217bc276d94p2

1

H4

H4

h-o118x138d118x138n

h-o118x138d118x138n

1

PAD2

PAD2

spad-pad-2np

spad-pad-2np

1

For EMI

C33

C33

*6.8P/50V_4_NC

*6.8P/50V_4_NC

24

37

40

1

9

16

22

6

13

19

31

34

4

5

21

20

18

17

15

14

12

11

38

39

23

C708 Close to Pin24

+1.1V_DVDD

C7 0.1U/ 10VC7 0.1U/ 10V

+1.7V_LX

+3.3V_LA N

+2.7V_AV DD

C8 0.1U/ 10VC8 0.1U/ 10V

+1.1V_AV DD

PIN 13,19 NC for AR8152

C15 0.1U/ 10VC15 0.1U/ 10V

C16 0.1U/ 10VC16 0.1U/ 10V

+VDDCT_L

1 2

R46 0_4R46 0_4

PIN 17,18,20,21 NC for AR8152

MDI1MDI1+

MDI0MDI0+

LED_ACT

LED_LINK

PCIE_CLK_REQ5#

+VDDCT_L

+VDDCT_L

+VDDCT

C17 0.1 U/ 10VC17 0.1 U/ 10V

R3 49.9/F_4R3 49.9/F_4

1 2

R4 49.9/F_4R4 49.9/F_4

1 2

R5 49.9/F_4R5 49.9/F_4

1 2

R6 49.9/F_4R6 49.9/F_4

1 2

2/8: Add screw.

2/10: change FP to rj45-c100g5-108a4-l-8p-luv.

TXCT0_R

change RJ45 CONN from DFTJ08FR197 to DFTJ08FR740 on 5/19 modify

+1.1V_DVDD +2.7V_AV DD

C3

0.1U/ 10VC30.1U/ 10V

2/14: Option for pin4/pin5

Pin45

Pin45

C17 Close to U1,Pin5

Close to LAN chip

C20

C20

C21

C21

1000P/50V_4

1000P/50V_4

0.1U/10V

0.1U/10V

R9 75/FR9 75/F

R10 75/FR10 75/F

LAN_MX1-

LAN_MX1+

LAN_MX0LAN_MX0+

Close to Pin9

C5

0.1U/ 10VC50.1U/ 10V

+1.1V_AV DD

C13

C13

0.1U/ 10V

0.1U/ 10V

C6

1U/6.3VC61U/6.3V

C14

C14

1U/6.3V

1U/6.3V

C23

C23

1000P/50V_4

1000P/50V_4

C4

1U/6.3VC41U/6.3V

Close to Pin6

LDO Mode

SWR Mode

C22

C22

0.1U/ 10V

0.1U/ 10V

2/9: Change QPN to DFTJ08FR197.

1/31: Change QPN / FP.

CN1 C100F3-10 804-LCN1 C100F3-10 804-L

8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

CHSGND110CHSGND2

9

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Nu mber Rev

Size Document Nu mber Rev

Size Document Nu mber Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

LAN(AR8151B/RJ45 CONN)

LAN(AR8151B/RJ45 CONN)

LAN(AR8151B/RJ45 CONN)

R05

R05

R05

2 5Friday, June 17, 2011

2 5Friday, June 17, 2011

1

2 5Friday, June 17, 2011

1A

1A

1A

Loading...

Loading...