Page 1

TK75005

OVP

DRV

EA

IN

V

CC

GND

EA

OUT

F

B

C

T

ADVANCED

INFORMATION

LOW-COST FLEXIBLE PWM CONTROLLER

FEATURES

■ Can Be Used For Power Factor Correction/Line

Harmonics Reduction to Meet IEC1000-3-2

Requirements

■ Maximum Duty Ratio 89% (typ.)

■ Low Standby Current for Current-Fed Start-Up

■ Current-Mode or Voltage-Mode Control

■ Internal User-Adjustable Slope Compensation

■ Pulse-by-Pulse Current Limiting

DESCRIPTION

The TK75005 is an 8-pin PWM controller suitable for both

voltage-mode and current-mode control. It also has

advanced features not available in controllers with a higher

pin count. One such feature is a sawtooth current flowing

out of the feedback pin (FB), which provides a slope

compensation ramp (in current mode applications) in

proportion to the resistance terminating that FB pin.

The TK75005 offers the same features as the TK75003

with the addition of the Error Amplifier and the Overvoltage

Protection (OVP) functions, and the deletion of the

Overcurrent Frequency Reduction feature.

This PWM has features similar to the UC3842 (please

refer to UC3842 Comparison Section).

APPLICATIONS

■ Power Factor Correction Converters

■ Off-Line Power Supplies

■ Industrial Power Supplies

■ Off-Line Battery Charger

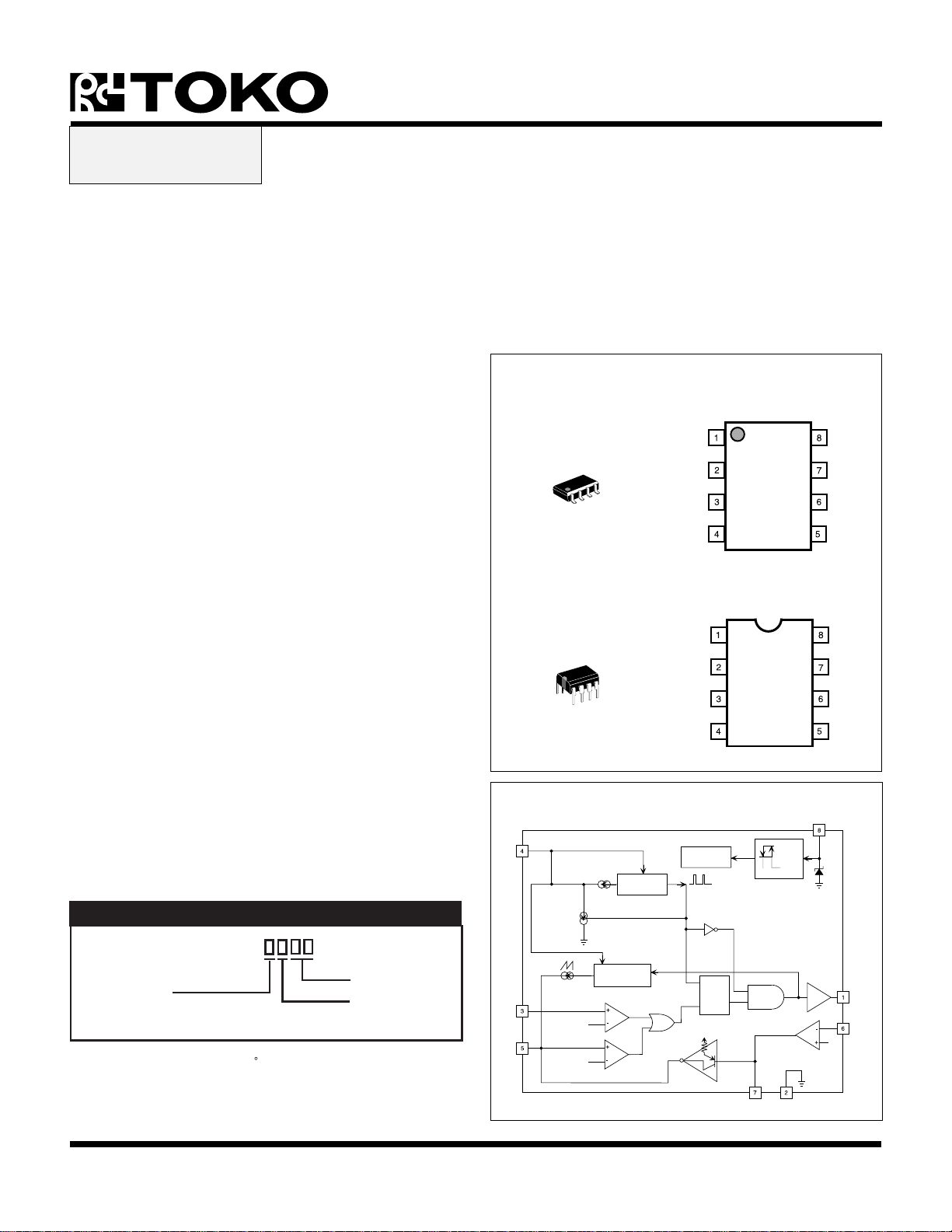

TK75005

75005

SOP-8

DRV

75005

DIP-8

GND

OVP

C

T

V

CC

EA

OUT

EA

IN

F

B

BLOCK DIAGRAM

I

CT

C

T

I

CHG

175 µA

I

DS

1.975 mA

OSCILLATOR

BANDGAP

REFERENCE

f

CLK

8.0 V

UVLO

10.0 V

ORDERING INFORMATION

TK75005

GM STAGE

PWM LATCH

S

R

Q

GND

EA

OUT

SLOPE

Package Code

PACKAGE CODE

D: DIP-8

M: SOP-8

TEMPERATURE RANGE

C: -40 TO 80 C

Tape/Reel Code

Temp. Range

TAPE/REEL CODE

TL: Tape Left

MG: Magazine

OVP

FB

OVERVOLTAGE

DETECTOR

2.6 V

CURRENT

CONTROL

DETECTOR

1.02 V

COMPENSATION

January 1999 TOKO, Inc. Page 1

V

CC

DRV

EA

IN

2.5 V

Page 2

TK75005

ABSOLUTE MAXIMUM RATINGS

Supply Voltage (Low Impedance) ............................ 18 V

Supply Voltage (ICC < 30 mA) ...................... Self Limiting

Power Dissipation (Note 1) ................................ 800 mW

Output Energy ...........................................................5 µJ

CT and FB Pins ........................................................ 10 V

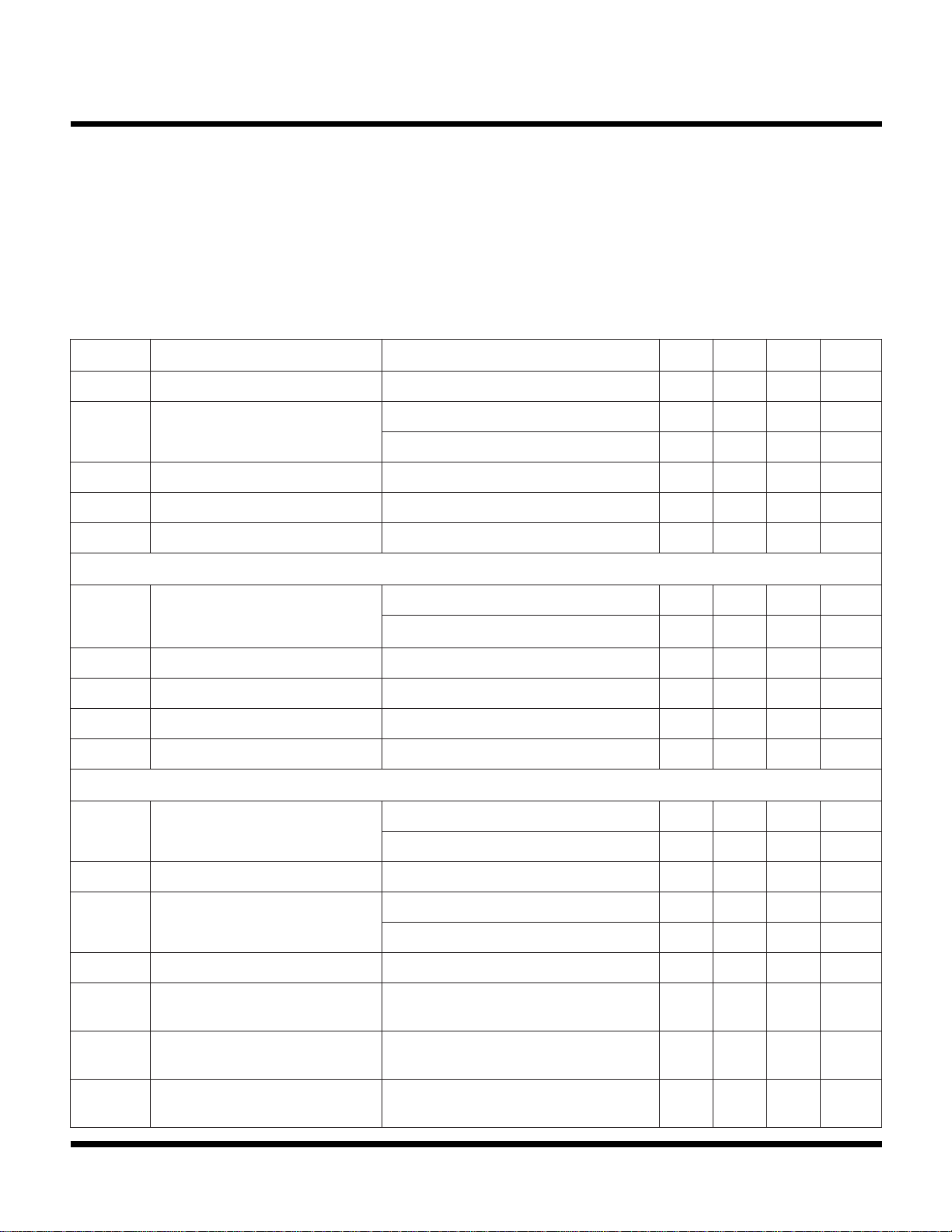

TK75005 ELECTRICAL CHARACTERISTICS

Test Conditions: VCC = 13 V, CCC = 4.7 µF, CT = 680 pF, C

unless otherwise specified.

LOBMYSRETEMARAPSNOITIDNOCTSETNIMPYTXAMSTINU

Junction Temperature ...........................................150 °C

Storage Temperature Range ................... -55 to +150 °C

Operating Temperature Range ...................-20 to +80 °C

Extended Temperature Range................... -40 to +85 °C

Lead Soldering Temperature (10 s) ......................235 °C

= 1000 pF, TA = Tj = Full Operating Temperature Range,

DRV

I

I

V

V

V

)TRATS(CC

)NO(CC

)NO(CC

)FFO(CC

TSYH

siseretsyHOLVU 10.2V

C(NOITCESROTALLICSO

f

VRD

V

)KP(TC

V

)LV(TC

I

)SID(TC

C

)XAM(T

egatloVkaeP 5.22.39.3V

egatloVyellaV 1.1V

tnerruCylppuSpu-tratSVotecruoStnerruC

tnerruCylppuSgnitarepO

AE

AE

NOegatloVOLVUV

FFOegatloVOLVUV

)NIP

T

T

AT=j

)3etoN(niPVRDtaycneuqerF

T

AT=j

tnerruCegrahcsiDV

V2=2171Am

NI

V3=5.410.91Am

NI

CC

CC

C°52=09001011zHk

V=

TC

)KP(TC

niP52.09.0Am

NI

drawpUspeewS90111V

drawnwoDspeewS789V

egnaRlluF=58511zHk

ecnaticapaCgnimiTmumixaM 7.4Fn

0.18.10.3Am

SNOITCESNOITASNEPMOCEPOLSDNA)NIPPVO(NOITCETORPEGATLOVREVO,ROTCETEDTNERRUC

T

V

DCC

t

DCC

V

DVO

t

PVO

i

)KP(CS

i

)LV(CS

i

)LV-KP(CS

tnerruC

tnerruC

yellaV

rotceteDlortnoCtnerruC

egatloVecnerefeR

noitcetorPegatlovrevO

egatloVecnerefeRrotceteD

kaePnoitasnepmoCepolS

yellaVnoitasnepmoCepolS

otkaePnoitasnepmoCepolS

AT=j

T

AT=j

niPVRDotyaleDnoitagoporPV

niPVRDotyaleDnoitagoporPV

T

AT=j

T

AT=j

C

T

BF

PVO

AE

C

T

AE

C

T

AE

C°52=99.020.150.1V

egnaRlluF=669.0770.1V

V2ot0morfspets08081sn

C°52=15.206.296.2V

egnaRlluF=64.247.2V

V3ot2morfspets08081sn

V=niP

)HGIH(TUO

V=niP

)HGIH(TUO

V=niP

)HGIH(TUO

)KP(TC

)LV(TC

)KP(TC

T,

AT=j

)2etoN(,

T,

AT=j

)2etoN(,

T,

AT=j

)2etoN(,

,C°52=

,C°52=

,C°52=

052-502-061-Aµ

55-03-5-Aµ

512-571-531-Aµ

Page 2 January 1999 TOKO, Inc.

Page 3

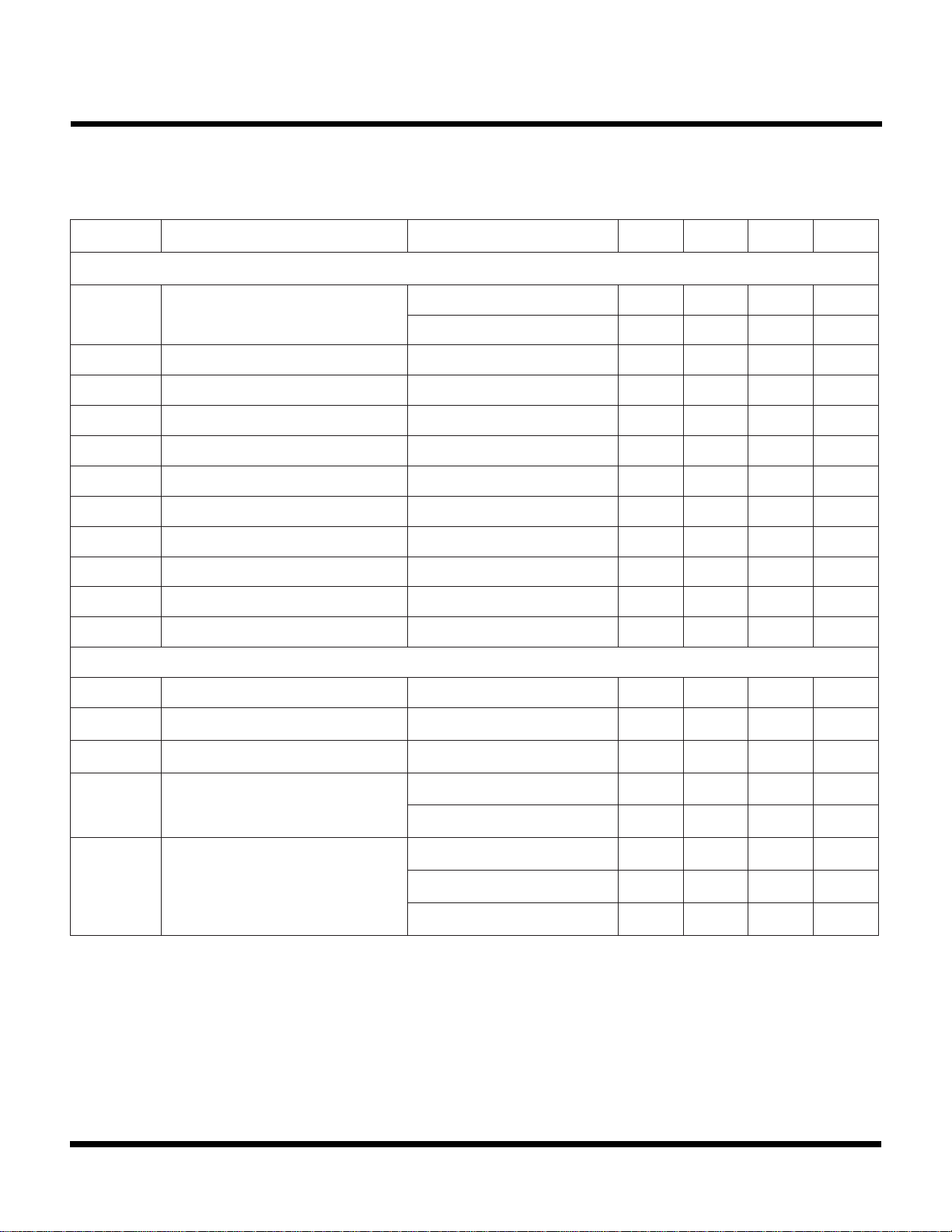

TK75005 ELECTRICAL CHARACTERISTICS (CONT.)

Test Conditions: VCC = 13 V, CCC = 4.7 µF, CT = 680 pF, C

unless otherwise specified.

LOBMYSRETEMARAPSNOITIDNOCTSETNIMPYTXAMSTINU

= 1000 pF, TA = Tj = Full Operating Temperature Range,

DRV

TK75005

AE(SNOITCESEGATSMGDNAREIFILPMARORRE

NI

T

V

fer

I

BI

A

DV

egatloVecnerefeR

tnerruCsaiBtupnI 0.1Aµ

niaGpooLnepO5657Bd

AT=j

TAT=

j

AEDNA

)SNIP

TUO

C°52=34.205.275.2V

egnaRlluF=73.246.2V

htdiwdnaBniaGytinU)3etoN(2zHM

RRSPoitaRnoitcejeRylppuSrewoP)3etoN(0607Bd

I

I

V

V

I

I

)KNIS(TUO

)ECRUOS(TUO

V

)HGIH(TUO

V

)WOL(TUO

)XAM(MG

)NIM(MG

I

I

)HGIH(TUO

)WOL(TUO

)XAM(TUO

)NIM(TUO

tnerruCkniStuptuOAE

AEta

AEta

niPAE

TUO

niPAE

TUO

tnerruCecruoStuptuOAE

egatSMGmorfniPBFtaAE

egatSMGmorfniPBFtaAE

TUO

TUO

NI

NI

V2.1=28.6Am

V5.3=1.1-5.0-Am

V2@5.31.4V

V3@4.07.0V

)WOL(TUO

)HGIH(TUO

V2@BF,59.1-05.1-50.1-Am

V2@BF,0.1-Aµ

)NIPVRD(NOITCESTUPTUO

D

t

)XAM(VRD

)ESIR(VRD

emiTesiRdaolFp00015257sn

oitarytuDmimixaM689829%

t

V

V

Note 1: Power dissipation for both packages (TK75005M and TK75005D) is 800 mW when mounted. Derate at 6.4 mW/°C for operation above

Note 2: For temperature dependence refer to "Slope Compensation Peak Current vs. Temperature" graph.

Note 3: Guaranteed by design; not 100% tested.

)LLAF(VRD

)HGIH(VRD

)WOL(VRD

25 °C.

emiTllaFdaolFp00015257sn

I

HGIHegatloVtuptuO

WOLegatloVtuptuO

VRD

I

VRD

I

VRD

I

VRD

I

VRD

Am04-=1.010.11V

Am001=0.018.01V

Am04-=1.052.0V

Am001=2.005.0V

,Am5=VNIV6=9.005.1V

January 1999 TOKO, Inc. Page 3

Page 4

TK75005

DRV

GND

OVP

TEST CIRCUIT

1 nF

100 k

EA

EA

OUT

IN

C

CC

4.7 µF

V

CC

SUPPLY CURRENT vs.

SUPPLY VOLTAGE

20

16

DEVICE ON

12

(mA)

CC

I

0.8

STANDBY

0.4

0.0

0 4 8 12 16 20

VCC (V)

C

T

C

T

680pF

3 k 3 k

F

B

INV AMP IN

TYPICAL PERFORMANCE CHARACTERISTICS

FREQUENCY AT DRV PIN

CAPACITANCE (-25 TO 85 °C)

10000

1000

100

FREQUENCY (kHz)

10

10 100 1000 10000

CT (pF)

VS.

TIMING

(µA)

SC(PK)

I

SLOPE COMPENSATION PEAK

CURRENT vs. TEMPERATURE

-100

-140

-180

-220

-260

-50 0 50 100

TEMPERATURE (°C)

50

SUPPLY CURRENT vs.

FREQUENCY AT DRV

2.6

REFERENCE VOLTAGE vs.

TEMPERATURE

SLOPE COMPENSATION RAMP

600

(mA)

CC

I

40

30

20

C

DRV

= 1 nF

C

DRV

= 470 pF

(V)

ref

V

2.56

2.52

2.48

450

(mV)

300

FB

V

150

10

0

0 400 800 1200 1600

C

DRV

= 0 pF

FREQUENCY (kHz)

2.44

2.40

-50 0 50 100

TEMPERATURE (°C)

RFB = 3 k TO GND

0

CT = 680 pF, E

AOUT(HIGH)

0 5 10 15 20

TIME (µs)

Page 4 January 1999 TOKO, Inc.

I

SC(PK)

I

SC(PK)

- I

I

SC(VL)

SC(VL)

Page 5

PIN DESCRIPTIONS

TK75005

DRIVE PIN (DRV)

This pin drives the external MOSFET with a totem pole

output stage capable of sinking or sourcing a peak current

of about 1 A. In standby mode, the DRV pin can sink about

5 mA while keeping the drive pin pulled down to about 1 V.

This ensures that the external MOSFET can not be

inadvertently turned on by leakage currents. The maximum

duty cycle of the output signal is typically 89%.

GROUND PIN (GND)

This pin provides ground return for the IC.

OVERVOLTAGE PROTECTION INPUT PIN (OVP)

This pin provides a means of turning off the external

transistor drive output independent of the PWM loop. This

pin is normally used for overvoltage protection, but can

also be used to provide a drive disabled function. The pin

is the input to comparator with its other input referenced to

2.6 V, which tracks V

its output controlling the output driver of the IC. Therefore,

if a voltage appears at this pin over 2.6 V, the voltage at

the DRV pin drops to zero.

TIMING CAPACITOR PIN (CT)

The external timing capacitor is connected to the CT pin.

That capacitor is the only component needed for setting

the clock frequency. The frequency measured at the CT pin

is the same frequency as measured at the DRV pin. As the

frequency of operation increases above 200 kHz, the

maximum duty cycle decreases from a typical 89% at

200 kHz to 82% at 1.6 MHz. The maximum recommended

clock frequency of the device is 1.6 MHz. At normal

operation, during the rising section of the timing-capacitor

voltage, a trimmed internal current of 175 µA flows out from

the CT pin and charges the capacitor. During the falling

section of the timing-capacitor voltage, an internal current

of about 1.8 mA discharges the capacitor.

FEEDBACK INPUT PIN (FB)

The feedback pin normally receives the sum of three

signals: the switch current signal, the error signal (from the

internal error amplifier and the GM stage), and a voltage

ramp (from an internal sawtooth-shaped current with a

peak value of about 205 µA) generated across the external

terminating resistance. The switch current signal is needed

of error amp over temperature. and

ref

in current-mode controlled converters and in converters

with cycle-by-cycle overload protection. The error signal is

needed for stabilizing the output voltage or current. The

voltage ramp is needed for slope compensation (necessary

for avoiding subharmonic instability in constant-frequency

peak-current controlled current-mode converters above

50% duty ratio), or for Pulse Width Modulation (PWM) (in

voltage-mode controlled converters).

At higher clock frequencies, the bandwidth limitation of the

internally-generated sawtooth-shaped current source

becomes more apparent. The degree to which ramp

bandwidth is tolerable depends on performance

requirements at narrow pulse widths. A low impedance at

the feedback pin can effectively eliminate the internallygenerated ramp effects and an external ramp can be

readily created to attain higher performance at high

frequencies, if desired.

ERROR AMPLIFIER COMPENSATION INPUT PIN (EAIN)

This pin is the inverting input of an operational amplifier

which has its non-inverting input connected to 2.5 V. This

is called the error amp because it amplifies the error

between this pin’s voltage and 2.5 V reference, which

should reflect the error in the power supply’s output

regulation. The error amp provides a high gain stage so

that the voltage loop gain can be high enough to provide

good output voltage regulation.

ERROR AMPLIFIER COMPENSATION OUTPUT PIN (EA

This pin is the output of the operational amplifier mentioned

in the EAIN pin description. By picking the proper resistor

and capacitor network connected between pins 6 and 7,

the gain and frequency response of the error amp block of

the voltage loop can be set, thus providing gain and

frequency compensation into the PWM voltage loop as

needed. This pin also acts as the input to the GM stage of

the voltage control loop.

SUPPLY VOLTAGE PIN (VCC)

This pin is connected to the supply voltage. The IC is in a

low-current (250 µA typ.) standby mode before the supply

voltage exceeds 10 V (typ.), which is the upper threshold

of the undervoltage lockout circuit. The IC switches back

to standby mode when the supply voltage drops below 8 V

(typ.).

OUT

)

January 1999 TOKO, Inc. Page 5

Page 6

TK75005

THEORY OF OPERATION

The TK75005 is intended for use as a highly flexible

primary-side PWM controller. The TK75005 is much like

the TK75003 with the addition of an error amplifier, a GM

stage and an overvoltage comparator, and the deletion of

the TK75003 overcurrent frequency reduction feature.

The many features integrated into a simple 8-pin design

allow it to be easily configured for voltage-mode or currentmode control, fixed frequency or fixed off-time operation,

off-line boot-strapping, and direct drive of a power MOSFET.

Using a control technique referenced in the “Application

Information” section, the TK75005 can be used as a highly

cost-effective controller for power factor correction.

The most noteworthy integrated feature in the TK75005 is

the way in which the feedback control pin is configured to

receive the error signal and the current signal for currentmode control. Rather than receiving both inputs into a

comparator, a single input receives both signals summed

together and compares them against a fixed internal

reference. This yields two desirable effects: 1) a currentlimit threshold is automatically established, and 2) the

required error-signal polarity is the inverse of that of a

standard two-input current-mode control system. Generally,

the signal summation requires no additional external

components and adds the flexibility to add more control

signals if desired.

timing ramp.

UC3842 COMPARISON

Similarities to the UC3842

1) a single-ended transistor driver output with similar

drive performance

2) an inverting error amplifier referenced to 2.5 V with

similar electrical characteristics

3) a maximum threshold of ~1V on the current sense

voltage used to terminate the PWM pulse

4) an 8-pin SOP-8 or DIP-8 package

Unique features of the TK75005

1) a multi-signal summation point at the FB pin, instead

of a single function UC1842 C/S pin

2) built-in slope compensation sawtooth current coming

out of the FB pin, reduced parts

3) an overvoltage protection pin compared to 2.6 V

4) switching frequency set using a single capacitor,

reduced parts

5) different UVLO thresholds 10 V / 8 V

6) maximum duty cycle set at 89%

Another function is integrated into the FB pin. A current

ramp, which can be used to establish either the slopecompensation ramp for a current-mode control design or

the voltage-comparison ramp for a voltage-mode control

design, flows out of the FB pin. By adjusting the terminating

resistance at the FB pin, the desired ramp magnitude is

established.

The switching frequency is determined by an internal

current source charging an external timing capacitor. The

timing capacitor is ramped between internally-fixed

thresholds, valley to peak, and then quickly discharged. A

fixed off-time control technique can readily be implemented

by using a small transistor to keep the timing capacitor

discharged during the on-time. When the on-pulse is

terminated, the timing capacitor ramps up to a fixed

threshold at a fixed rate to set the off-time.

The Undervoltage Lockout (UVLO) feature with hysteresis

minimizes the start-up current which allows a low-power

boot-strap technique to be used for the housekeeping

power. The duty ratio of the TK75005 is limited to

approximately 89% by the time required to discharge the

Page 6 January 1999 TOKO, Inc.

Page 7

APPLICATIONS INFORMATION

BOOST POWER FACTOR CORRECTOR APPLICATION

CIRCUIT

Figure 7 shows a universal-input, 100 W boost power

factor corrector application circuit. The control technique is

called “current-clamped control.” Both the control technique

and the application circuit with waveforms are described in

the paper “Low-Cost Power Factor Correction/LineHarmonics Reduction with Current-Clamped Boost

Converter,” published in the conference proceedings of

Power Conversion Electronics ’95/Powersystems World™

’95. A copy of the paper can be obtained by contacting

Toko.

TK75005

Switching frequency: f = 100 kHz

Inductance of boost inductor: L1 = 2.5 mH

Maximum duty ratio of TK75005: D

Peak value of ramp current

flowing out of the FB pin: I

Threshold voltage of the

current-control detector: V

Calculations:

MAX

SC(PK)

CCD

= 0.88

= 200 µA

= 0.98 V

For designers who wish to explore other performance

optimizations of the current-clamped boost power factor

corrector, aside from the conference paper Toko offers a

Mathcad© file which can accurately display current

waveforms and predict power factor, harmonic distortion,

and individual harmonic currents. The Mathcad file and the

text which describes how to use it are available from the

Colorado Springs Toko IC Design Center.

The power factor corrector in Figure 7 has been optimized

for general wide-range-input use. In order to obtain the

same performance at power levels other than 100 W, the

control components do not need to change. The power

component values change as follows: C8 scales in

proportion to the power level, and L1 and R8 scales in

inverse proportion to the power level. Typically, although

not directly related to the line-current shaping capability of

the application circuit, C1 and C10 would scale in proportion

to the power level. All the components in the power stage

should have a current rating as needed to accommodate

the power level.

Below is a step-by-step design example, showing how to

determine the resistance of R7 terminating the feedback

pin and the resistance of the current-sense resistor R8, for

the boost corrector of Figure 7.

Assumptions:

Peak value of minimum line voltage:

V

I(MIN)(PK)

= 2 x V

I(MIN)

= 120 V

PK

Switch duty ratio at peak of minimum line voltage:

D = 1 - V

I(MIN)(PK)

/ V

OUT

= 0.684

Peak-to-peak ripple current in inductor L1:

I = V

I(MIN)(PK)

x D / (f x L1) = 0.33 A

Input power at minimum line voltage:

PI = P

/ EFF = 107.5 W

OUT

Peak current in L1 (at peak of minimum line voltage):

I

=2 x PI / V

L1(PK)

I(MIN)(PK)

+ I/2 = 1.95 A

Output power: P

Output voltage: V

Minimum line voltage: V

= 100 W

OUT

= 380 Vdc

OUT

= 85 Vrms

I(MIN)

Resistance of resistor R7 (Note 1):

R7 = D

MAX

x V

CCD

/ I

SC(PK)

= 4.312 kohms

Efficiency at 85 Vrms: EFF = 0.93

January 1999 TOKO, Inc. Page 7

Page 8

TK75005

APPLICATIONS INFORMATION (CONT.)

Select for R7:

R7 = 4.3 kohms

Resistance of current-sense resistor R8 (Note 2):

R8 = (V

CCD

- I

x R7 x D) / I

SC(PK)

= 0.201 ohms

L1(PK)

Select for R8:

R8 = 0.18 ohms

Note 1: This value of R7 ensures that the line current will be zero around

the zero-crossing of the line voltage, which is the required condition for

low-distortion line current.

Note 2: This value of R8 ensures that the sum of the voltage drop across

R8 (caused by the peak inductor current) and the voltage drop across R

(caused by the instantaneous value of the stabilizing current) is equal to

the threshold voltage of the current-control detector at the peak of the

line voltage.

F

1

TH

10 Ω

2

1

B

1

4

600 V, 1.5 A

1

R

1a

3

R

1b

24 k

0.5 W

C

10

1 nF

400 V

0.5 W

5.6 k

470

24 k

R

C

2

D

4

30 V

150 k

2

F

R

3

5.6 k

D

1

1N4148

C

3

100 nF

C

4

100 nF

D

2

IN4148

R

4

85-265

VAC

250 V/ 2 A

C

1

0.1

F

7

2.5 mH

t: 220

EA

V

FB

GND

L

1

t:9

CC

C

1

R

100 k

OUT

U

1

TK75005

ETD-29 core

gap in center leg

7

F

9

EA

IN

OVP

DRV

C

T

R

3 k

C

680 pF

10

R

5

10

5

10 nF

R

6

51

C

6

D

3

HFA04TB60

R

11b

200 k

0.25 W

Q

1

IRF840

R

8

0.18

0.5 W

R

11a

200 k

0.25 W

R

12

2.43 k

0.25 W

C

100

400 V

R

51a

200 k

8

380 V DC

100 W

R

51b

200 k

0.25 W

F

R

52

2.43 k

R

7

4.3 k

FIGURE 7: BOOST POWER FACTOR CORRECTOR APPLICATION CIRCUIT

Page 8 January 1999 TOKO, Inc.

Page 9

PACKAGE OUTLINE

)

TK75005

DIP-8

SOP-8

8

1

Dimensions are shown in millimeters

Tolerance: x.x =

85

5

4

9.5

e

2.54

+ 0.15

- 0.05

0.46

0.2 mm (unless otherwise specified)

6.4

3.3

0.5 min

3.9

Marking

Lot Number

Country of Origin

0.3

+

3.8

0.3

+

3.3

0.25

1.27

+ 0.15

- 0.05

0.25

M

0.76

Recommended Mount Pad

Marking Information

Marking

TK75005 xxx

e1

0 ~15

7.62

5.4

1

e

e

1.27

1

0.42

Dimensions are shown in millimeters

Tolerance: x.x =

4.89

e

1.27

l

0.12

0.2 mm (unless otherwise specified

4

0.5

0 ~ 10

0.3

+

1.45

1.64

0 ~ 0.25

0.1

6.07

0.2

+

0.3

Toko America, Inc. Headquarters

1250 Feehanville Drive, Mount Prospect, Illinois 60056

Tel: (847) 297-0070 Fax: (847) 699-7864

TOKO AMERICA REGIONAL OFFICES

Midwest Regional Office

Toko America, Inc.

1250 Feehanville Drive

Mount Prospect, IL 60056

Tel: (847) 297-0070

Fax: (847) 699-7864

Western Regional Office

Toko America, Inc.

2480 North First Street , Suite 260

San Jose, CA 95131

Tel: (408) 432-8281

Fax: (408) 943-9790

Eastern Regional Office

Toko America, Inc.

107 Mill Plain Road

Danbury, CT 06811

Tel: (203) 748-6871

Fax: (203) 797-1223

Semiconductor Technical Support

Toko Design Center

4755 Forge Road

Colorado Springs, CO 80907

Tel: (719) 528-2200

Fax: (719) 528-2375

Visit our Internet site at http://www.tokoam.com

The information furnished by TOKO, Inc. is believed to be accurate and reliable. However, TOKO reserves the right to make changes or improvements in the design, specification or manufacture of its

products without further notice. TOKO does not assume any liability arising from the application or use of any product or circuit described herein, nor for any infringements of patents or other rights of

third parties which may result from the use of its products. No license is granted by implication or otherwise under any patent or patent rights of TOKO, Inc.

January 1999 TOKO, Inc. Page 9

© 1999 Toko, Inc.

All Rights Reserved

IC-xxx-TK75005

0798O0.0K

Printed in the USA

Loading...

Loading...