Page 1

LZ93N61

LZ93N61

DESCRIPTION

The LZ93N61 is a CMOS timing generator LSI

which provides timing pulses used to drive a

CCD

area sensor, in combination with the SSG

LSI (LZ93NI 9, LZ93B53).

FEATURES

●

Switchable

320000 pixels CCD

●

Switchable between NTSC

(CCIR)

●

Internal electronic shutter :

Shutter speed is selectable from 1/W, 1/125,

1/250, 1/500, 1/1 000, 1/2 000, 1/4 000 and

1/10 000 s, in addition to this, 1/100 s (PAL

: 1/120 s) in Flicker-less mode using parallel

or serial code. Shutter speed can also be

controlled in 1 H period using an external

trigger to the EXST input.

c

Single +5

●

Package : 48-pin

between 270000 pixels

systems

V

power supply

QFP(QFP048-P-I

(EIA)

CCD

and

and PAL

01 O)

Timing Pulse Generator LSI for CCD

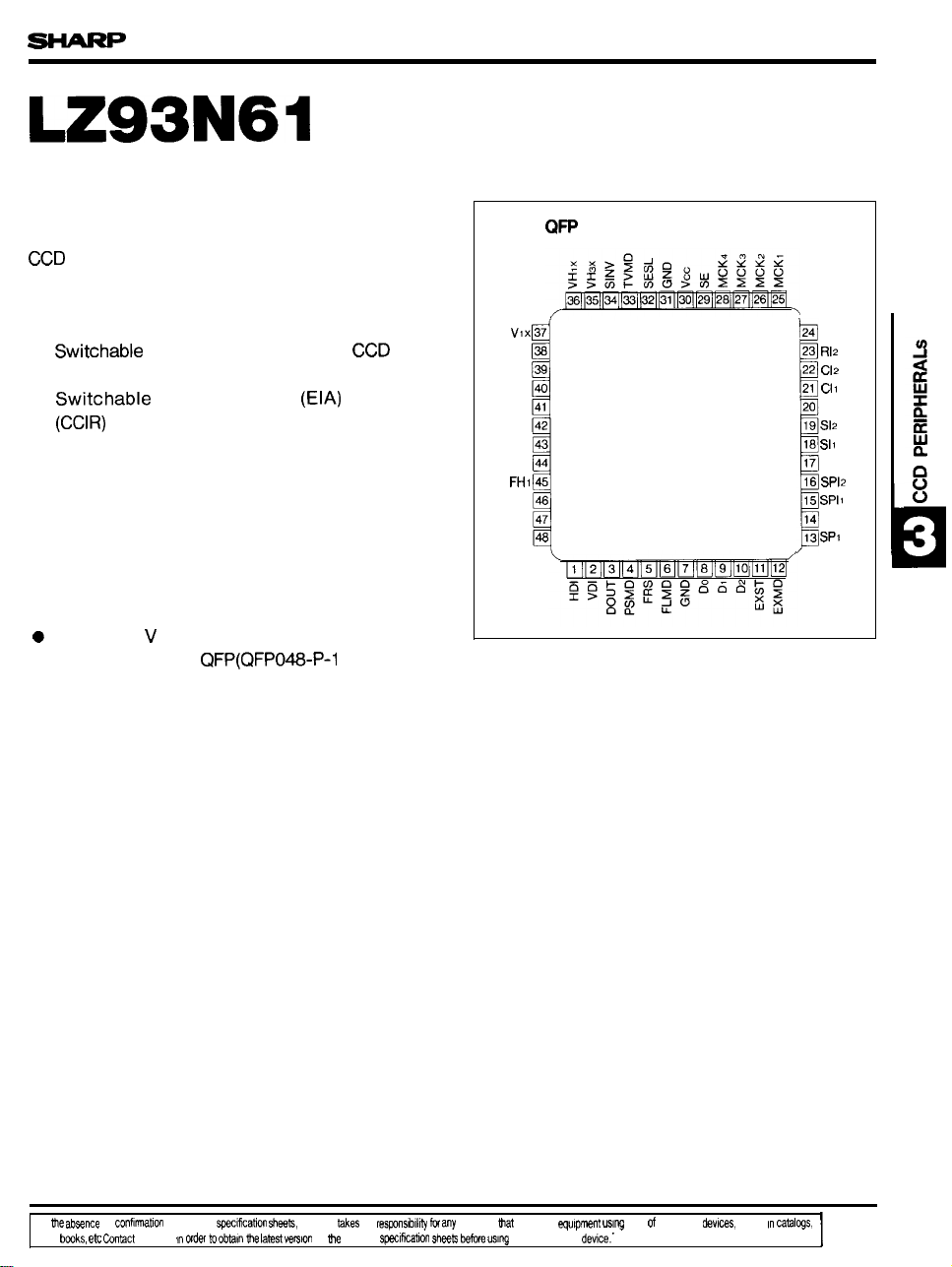

PIN CONNECTIONS

48-PIN

Vlx

V2X 3a

V3X

V4X 40

OFDX 41

FR 42

GND 43

FH2 44

FHI 45

CKI 46

CKO 47

TSTI

QFP

37

39

W

o

I

TOP VIEW

24 R12

23

R12

22

C12

21

CI1

20 FCDS

19

S12

18

SI1

17 FS

16

SP12

15

SPII

14 SP2

13

SPI

1

“In

deta

tie

abeence

bwks, etc

of

conf[mtlon

hn~ct WARP !n

by device

acecification ehwf?,

mder to obtain

tie

Iateat vefilon

WARP

fakee

no

of he device swIkaiim

reswns!blhty b

anY

defects

shw~ ktie USIW

hat

recur In

qutpment USIW

any 8HARPs

dewce.”

any of WARPS

davIces,

show In

Cahlws,

I

287

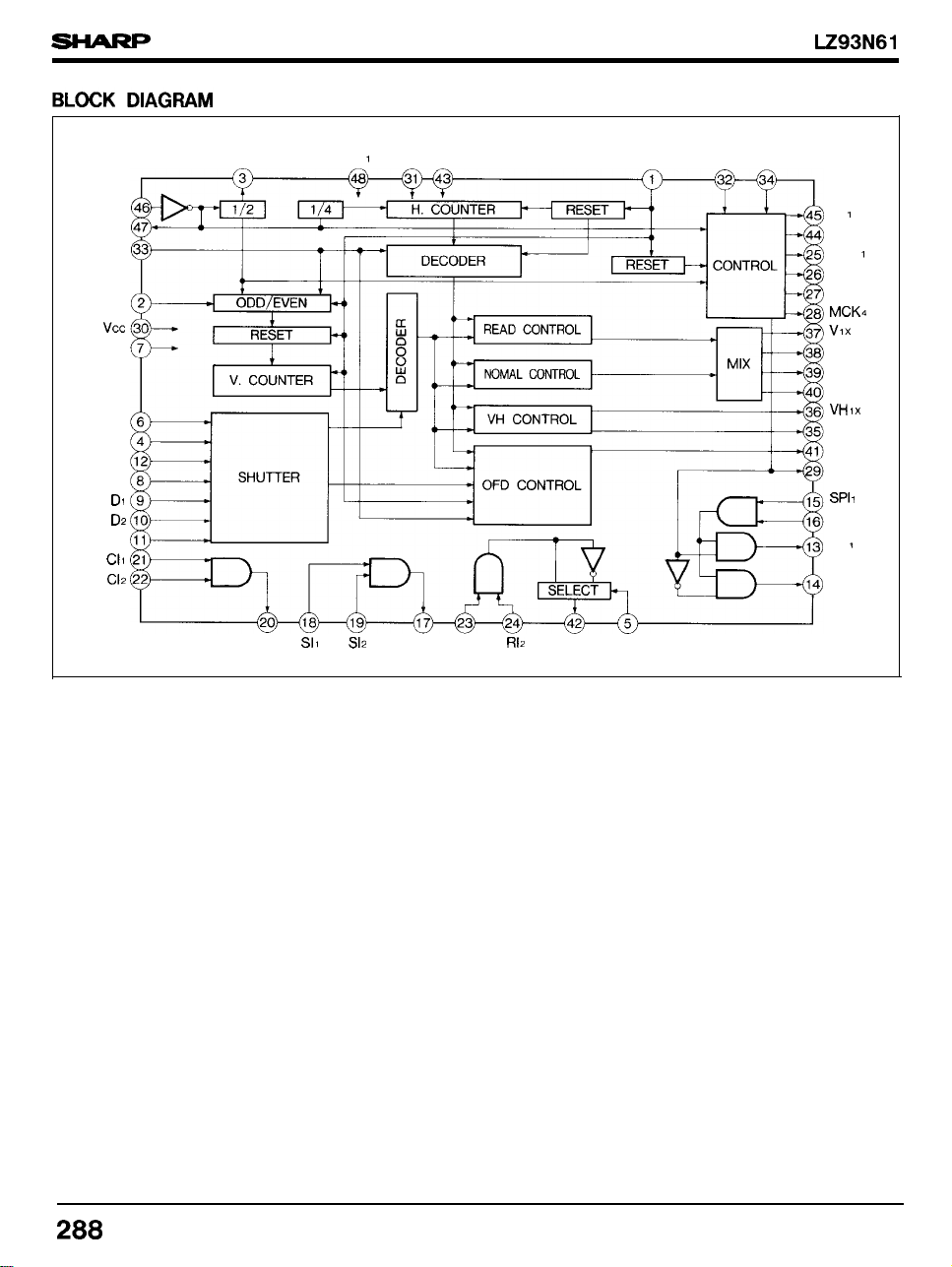

Page 2

LZ93N61

CKI

CKO

TVMD

VDI

Vcc

GMD

FLMD

PSMD

EXMD

EXST

Do

DI

D,

Cll

C12

DOUT

FCDS

S1,

TST

S12

I

GND GND

FS

RI I

R12

FR

FRS

HDI

SESL SINV

FH

I

FH2

MCK

MCK2

MCK3

MCK.

Vlx

V2X

V3X

V4X

VHIX

VH3X

OFDX

SE

SPI 1

SPI 2

SP

1

SP2

I

288

Page 3

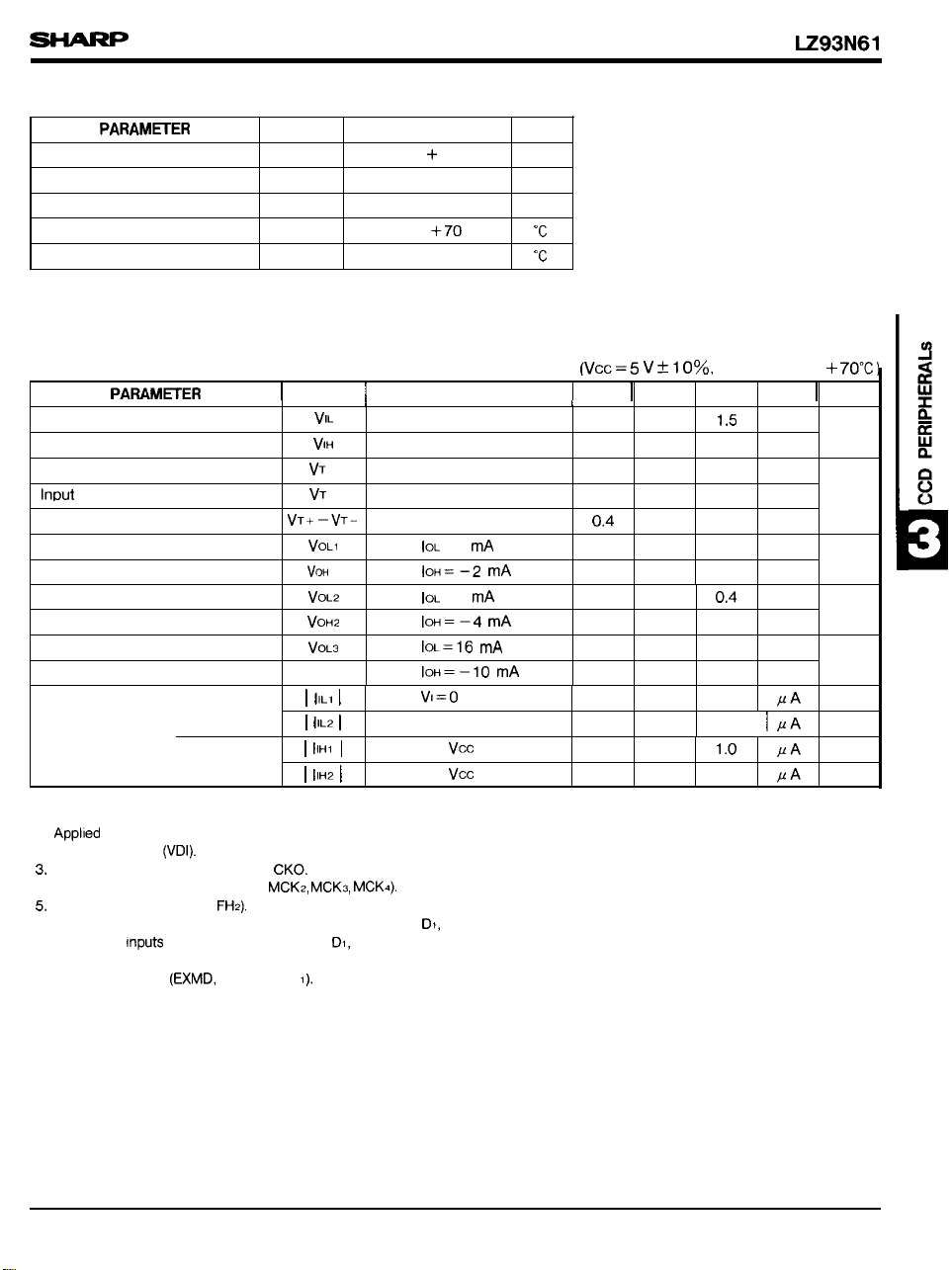

ABSOLUTE MAXIMUM RATINGS

PARAM=ER

Supply voltage

Input voltage

Output voltage

Operating temperature

Storage temperature

SYMBOL

Vcc

VI

Vo

Topr

Tstg

RATING

– 0.3 to

+ 7.0 v

UNIT

–0.3 to Vcc + 0.3

– 0.3 to Vcc + 0.3 v

–20 to

+70

–55 to +150

LZ93N61

v

“c

‘c

DC CHARACTERISTICS

PARAMHER

Input Low voltage

Input High voltage

Input High threshold voltage

lnDut Low threshold voltage

Hysteresis voltage

Output Low voltage

Output High voltage

Output Low voltage

Output High voltage

Output Low voltage

Output High voltage

Input Low current

Input High current

NOTES :

Applled to

1.

2. Applied to

3.

Applied to

4. Applied to

5,

Applied to

6. Applied to

7. Applied to

8. Applied to

9. Applied to

all inputs except for VDI, CKI.

input

(VDI).

all outputs except for

outputs (FR, MCK I,

outputs (FH 1,

FH2).

all inputs except for PSMD, FRS, FLMD, Do,

Inputs

(PSMD, FRS, FLMD, Do,

all inputs except for EXMD, TVMD, TST

(EXMD,

inputs

TVMD, TST

~

SYMBOL

VIL

[

I

vlH

vT +

vT -

vT+

–VT-

VOLI

vOH

1

vOL2

vOH2

vOL3

v0H3

I IIL1 I

I IIL2 I

1

tlHl

I

I IIH2 I

CKO.

MCK2, MCK3, MCK4).

D!,

D2, EXST, SESL, StNV).

I).

CONDITIONS MIN.

IOL

= 4 mA

IoH=–P

mA

IOL

=8 mA

IoH=–4

mA

IoL=16

mA

IoH=–10

Vl=o

mA

v

Vl=o v

VI= Vcc

VI= Vcc

DI,

D2, EXST, SESL, SINV

1.

(VCC=5 V~l OYO.

]

1

TYP. I MAX.

Ta=–10 to

1.5

3.5 v

2.2

1,0

3,8

2.4 v

0.4

0.4

4.0 v

0.4 v

4.0

0.4

4.0

1.0

8.0

60

1.0

8.0 60

UNIT

v

v

v

v

v

v

v

PA

\ AA

PA

PA

+70”C)

I

NOTE

1

2

3

4

5

6

7

8

9

289

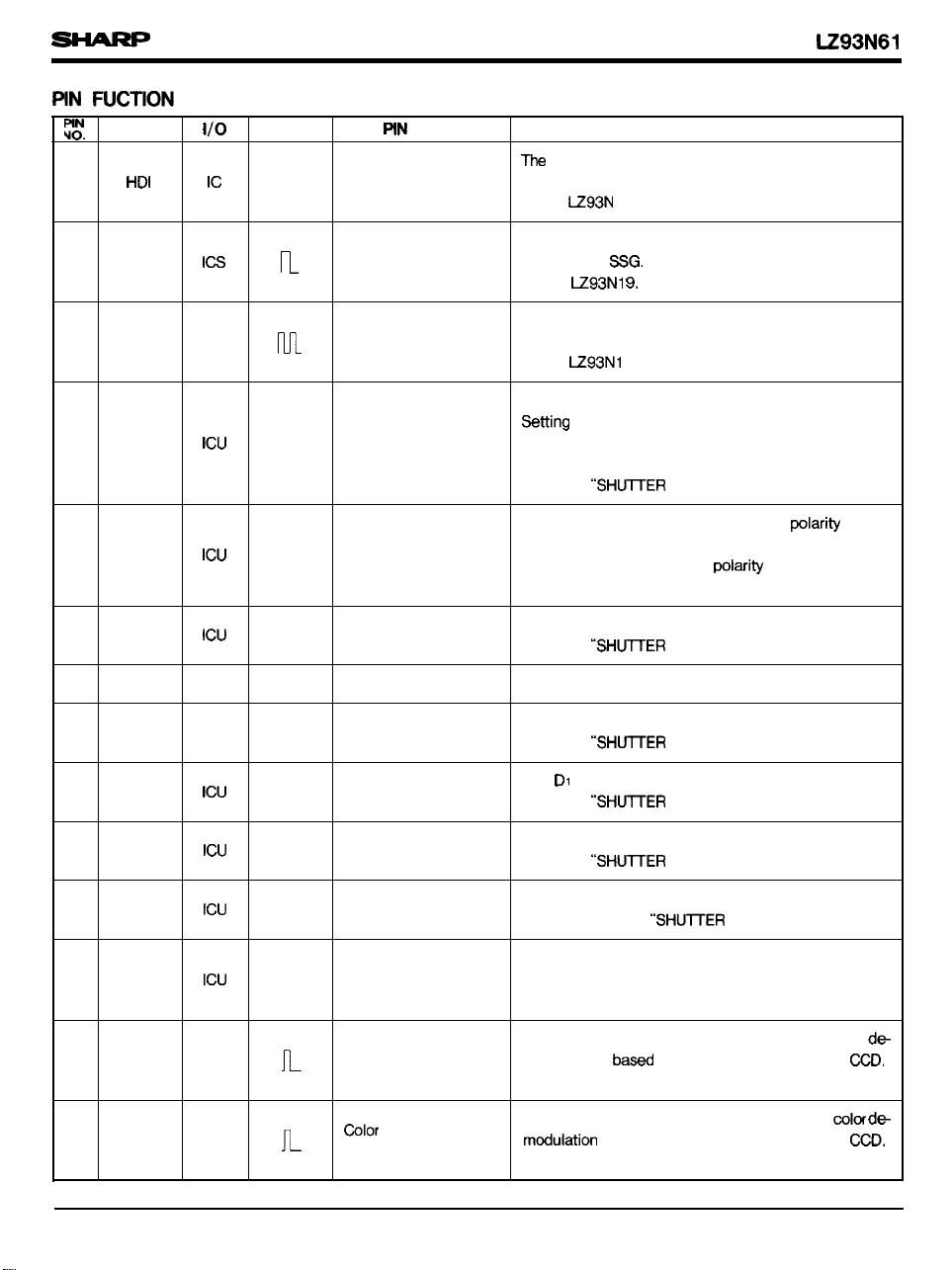

Page 4

LZ93N61

~:.

SYMBOL

1

HDI

2

VDI

3 DOUT

4 PSMD

FRS

5

6

FLMD

7

GND

1/0

POLARITY

Ic

Ics

o

Icu –

Icu –

Icu –

— —

MM

n

nn

PfN

NAME

Horizontal drive pulse

Vertical drive pulse

Delay-Line clock

Shutter mode select

input

FR control input

Flicker-less mode

select

Ground

FUNCTION

Ths

HDI pin is used to input the horizontal reference

signal from SSG. It is connected to the HD (pin 31)

I-Z93N

of the

The VDI pin is used to input the vertical reference

signal from

of the

The DOUT pin output 1/2 dividing clock input to

the CKI (pin 46). It is connected to the CLKI (pin 27)

of the

The PSMD pin is used to switch the Shutter Speed

%tting

(Refer to

The FRS pin is used to selects the

FR (pin 42).

The FLMD pin is used to prevent the flicker.

(Refer to “SHU~ER MODE TABLE ”.)

The GND is a ground pin.

19.

SG.

It is connected to the VD (pin 34)

U93NI 9,

~93Nl

9.

mode.

High level : Parallel Setting mode

Low level : Serial Setting mode

“SHU~ER MODE TABLE”. )

~larity of the

High level : negative ~larity

Low level : positive polarity

6

9 D

10

11

12

13

14

290

Do

I

D2

EXST

EXMD

SP1

SP2

Icu

Icu

Icu

Icu

Icu

o

o

Shutter speed

—

switching input O

Shutter speed

—

switching input 1

Shutter speed

—

switching input 2

Shutter speed

—

control 1

Shutter speed

—

control 2

L

L

Color sampling

pulse 1

@lor sampling

pulse 2

The Do pin is used to control the shutter speed.

(Refer to

The DI pin is used to control the shutter speed.

(Refer to

The D2 pin is used to control the shutter speed.

(Refer to

The EXST pin used to control the shutter speed 1 H

by 1 H. (Refer to “SHU~ER MODE TABLE ”,)

When the EXMD input pin is Low level, the EXST

(pin 11) is prohibited. (Refer to “SHUTTER MODE

TABLE” .)

The SPI pin output the sampling pulse for color

modulation

It outputs at High level of the SE (pin 29).

The SP2 pin output the sampling pulse for

mdulation

It outputs at Low level of the SE (pin 29).

“SHLflTER

“SH~ER

“SHUITER

based upon the output signal of

MODE TABLE”. )

MODE TABLE ”.)

MODE TABLE ”.)

ba~

upon the output signal of

d~

~D,

COIW de

CCD,

Page 5

PrN

.-

Uo.

15

1

CVMR~

--------

SPI 1

U93N61

I/n

I MLAR~

.- —.....

-$-

IC

I

m

PIN NAME

SPI

and SP2 phase

control input 1

The

SPII

pin sets the falling edge of

pulses

SP1

(pin 13) and SP2 (pin 14).

FUNCTON

COICS

sampling

16

17

18

19

20

21

22

23

24

25

26

SP12

FS

SI

1

S12

FCDS

c11

C12

RI

j

R12

MCKI

MCK2

SP1

and

SPZ

Ic

o

Ic

Ic

o

Ic

Ic

Ic

Ic

o

o

N

n

m

nn

n

m

N

nn

nn

nn

nn

control input 2

CDS pulse 2

FS phase control input 1

FS phase control input 2The

FCDS pulse 1

FCDS phase control

input 1

FCDS phase control

input 2

FR phase control

input 1

FR phase control

input 2

Clock output 1

Clink output 2

phase

The SP12 pin sets the rising edge of color sampling

pulses SPI (pin 13) and SP2 (pin 14).

The FS pin outputs the pulses for sampling output

signals of

The

The FCDS pin outputs the pulse to clamp the out-

put signals of

The Cl 1 pin sets the phase of the FCDS (pin 20).

The

The RI I pin sets the pahse of the FR (pin 42).

The

The MCKI pin outputs 1/2 dividing pulse of

46). It is the same phase with the FH i (pin 45).

The MCK2 pin outputs 1/2

46). It is delayad by approximately

respect to FH1 (pin 45).

CCD.

SII

pin sets the phase of the FS (pin 17).

SIZ

pin sets the width of the FS (pin 17).

CCD.

CIZ

pin sets the width of the FCDS (pin 20).

R12

pin sets the width of the FR (pin 42).

dividi~ pulse of

90°

in phase with

CKI

CKI

(pin

(pin

27

28

29

30

31

MCK3

MCK4

SE

Vcc

GND

Tk

o

o

o

–

–

nrl

m

rL

Clwk output 3

Clock output 4

Color demodulation

pulw

—

Power supply

Ground

–

MCK3 pin outputs 1/2 dividing pulse of

46). It is the same phase with the

The

MCK4

pin outputs 1/2 dividing pulse of

46). It is delayed by approximately

respect to FH2 (pin 44).

The SE pin outputs the demodulation carrier of output signals of CCD, and input the switching signal

of color sampling pulses

14). It outputs 1/4 dividing pulse of the

(pin 46), and selects the phase in

the SESL (pin 32) and the SINV (pin 34).

The Vcc is a + 5 V power supply pin.

The GND is a ground pin.

SP1

90”

(pin 13) and

mmbination

FHz

(pin 44).

in phase

CKI

CKI

CKI

SPZ

input

(pin

(pin

witi

(pin

with

291

Page 6

I-Z93N61

::

SYMBOL

32

SESL

33 TVMD

SINV Icu

34

VH3X

35

36 VH

37

38

39

40

VI x

V2X

V3X

V4X

1/0

POLARITY

Icu SF control input

ICD

0

IX

0

o

o

o

o

—

– TV mode input

—

r

lr

L

n

u

u

PIN NAME

tiior

line input

Read out pulse 3

Read out pulse 1

Vertical transfer pulse 1

Vertical transfer pulse 2

Vertical transfer pulse 3

Vertical transfer pulse 4

FUNCTION

The SESL input pin selects the phase of color demodulation carrier output SE (pin 29).

Low level : synchronized with the rising edge

of FHI (pin 45).

High level : synchronized with the rising edge

of FH2 (pin 44).

The TVMD input pin selects the TV system.

Low level : NTSC system

Hige level : PAL system

The

SINV input pin is used to invert the color de-

modulation carrier output SE (pin 29) at 1 H rate.

VH3X is a pulse output pin to transfer the photc-

The

diode charge of CCD to the vertical shift register.

It is connected to the 3BX (pin 11) of the LR366B3N

vertical driver

The VHIX is a pulse output pin to transfer the photcdiode charge of CCD to the vertical

It

is connected to the 1 BX (pin 8) of the

vertical driver

The V

I x, V2X, V3X and V4X are transfer pulse output

pins for CCD vertical shift register,

LSI.

LSI.

shifi

register.

LR-N

41

42

43

44

45

46

292

OFDX

FR

GND –

FH2

FH

I

CKI ICK

02

05

05

o

lr

L

Uu

nn

nlllul

OFD pulse output

T

Reset pulse

–

Ground

Horizontal transfer The FH2 pin outputs the horizontal transfer pulse of

pulse 2 CCD shift register. It is connected to the

Horizontal transfer The FHI pin outputs the horizontal transfer pulse of

pulse 1 CCD shift register, It is connected to the

Clock input 1212 fH : CCD of 542 horizontal pixels.

The OFDX pin is used to output for controlling OFD

voltage during electronic shutter operation.

The FR pin outputs the reset pulse of CCD. It is

connected to the ~ R through the offset circuit.

The GND is a ground pin.

~

Hz.

#HI,

CKI

is a reference clock input pin of horizontal

The

and vertical pulses,

Frequency for NTSC

Frequency for PAL

fH

: CCD of 542 horizontal pixels.

1236

(TVMD = L)

(TVMD = H)

(fH

= Horizontal frequency)

Page 7

LZ93N61

]

::.

SYMBOL

I47I

I

48 I TSTI I ICD I - I Test terminal 1

Ic

:

Icu

ICD :

Ics

ICK :

OCK :

0:

02 :

05 :

CKO

I

Input pln (CMOS level).

Input pin

:

Input pin

Input pin

:

Input pin for oscillation.

Output pin for oscillation.

Output pin.

Output pin.

Output pin.

(CMOS level with buflt-in pull-up resistor).

(CMOS level with built-in pull-down resistor).

(CMOS level schmitt).

1/0

OCK

POLARITY

Uuuv

I

PIN NAME

]

Clock output

I

I

The CKO pin outputs clocks at the reverse of the

CKI (pin 46).

I

The TSTI input pin is normally kept

FUNCTION

Low or

open.

293

Page 8

SUPPLEMENTARY EXPLANATION

SH~ER

PIN

I

I

t

1

MODE TABLE

Ps

FL

Tv

MD MD MD MD ST

4 6 33

H H

H H

1

I

H H

H H

J

u

J

~

: :

H

n.

H

Iui,

n

H

L

L

L

L

L

L

<

E

L

&

L

L

L

L

L

L

L

L L

1

1 1 1

H

H

iii,

L

L

L

H

H

H

H

H

H

H

H

H

H H

H H

H

L

H

L

H

L

L

H

1

1

INPUT PIN

EX EX

12

11

L L

L L

L L

L L

L

L

L

L

1

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

J

H

1

t

1

‘2“

10

9 8

L

L

H

H H

H

L

H

L

H H

H H H

I

1 1

REGISTER IN

LSl

SHUITER

m

D,

D6

D5

D4

D3 D2

L NORMAL

H

I

L

L 1/1 000

H

L

1

1

I

1 1 1

H H

H H

H H

H

H H

H H

H H

H H

H H

H

H

H

L

1

I

I

H

L 1/100

L

L 1/120

H

L

L L 1/120

DI

1

I

L

L

L

L

H

H

H

H

I

1

L

L

H

H H

L

L

H

H H

1

I

SPEED (S]

Do

I

I

L

H

L

L 1/1 000

H

L

1 /125

1 /250

1 /500

1/2 000

1/4 000

1/10000

,..

.

/.nfi

1/

1/120

NORMAL

1/125

1 /250

1

/500

1/2 000

1/4 000

1/10000

1/100

OFDX = H

1/100

1/120

OFDX = H 2

EXST

LZ93N61

NOTE

)

H

I

I

Iuu

(

1

I

1

3

NOTES :

NTSC=l/W

1.

2. The data of shutter speed was decided by the control pulse EXST (pin 11), is deleted.

3. The shutter

4. The data of shutter

lNmAL STATUS IN SERIAL MODE AND EXTERNAL TRIGGER MODE

When power is turned on in Serial mode

(EXMD

= H), the mode is not established until data is input from serial code or

S,

PAL=l/50

s@ed is decided by the falling edge of control pulse EXST (pin 11).

S.

s-d

was decided by the control pulse EXST (pin 11), hold as it is

(PSMD

= L) or External Trigger mode

EXST,

294

Page 9

SERIAL DATA FORMAT

D I (pin 9)

D2

(pin 10)

Do

DI

D2 D3 D. D, De D7

LZ93N61

Do (pin 8)

NOTE :

D&D7

are latched by the rising edge of pulse D, (pin 9).

By the falling edge of pulse Do (pin 8), the shutter

DESCRIPTION OF EXTERNAL SYNCHRONOUS SHUTTER MODE

1. When EXMD = H, this mode is given priority over other

modes. On applying falling edge of trigger input to

IC

EXST (pin 11), the

reads at the rising edge of HDI

and latches the V period counter value, and controls

final output of the OFDX pulse during this H period.

(The pulse must lasts until HDI goes high.)

2. Once latched, the value of V period counter is retained until the next trigger is input as long as EXMD

= H, even trigger input is for odd (ODD) w even (EVEN)

field, the storage time of another field becomes the

same as the field with trigger input automatically.

NTSC

PAL 19/331 H

HOI

EXST

(PATTERN)

OFDX

(PATTERN)

17/279 H 18/280 H 19/281 H 20/282 H 21/2S3 H

~~~~

000/lst, 3rd FIELD

WEN/2nd,

[

20/W2 H

a

4th FIELD

n n

~

~

21/W

H

b (INVALID)

a c d e

END

C (EVEN

,

n

speed is decided.

Note that when changing in high speed shutter direction, the internally stored data is used first, This

caue-es

the delay to control by one field.

[Trigger input disabled range]

stomge

To match ODD storage time with EVEN

time, the

pulse start position is set at 20/283 H for NTSC and

22/335 H for PAL. This means that inputting the trigger

at 18/280, 281 H in NTSC mode and 20/332, 333 H in

PAL mode is made disabled.

22/2W H

241W

22/=4

H

23/=5

I-1

IWALIO)

000 START EVEN START

n

~

d[

w

b-u

H

H

e

295

Page 10

LZ93N61

TIMING

(ODD

DAIGRAM

FIELD)

CBLK

HDI

VDI

VI

x

V2X

V3X

V4X

VHIX

VH3X

OFDX

(EVEN FIELD)

CBLK

HDI

..-.

Vul ~

VI.

n@2n4wn4ffiflwn4mn4’2fl

V2X

V3X

V4X

VHIX

VH3X

OFDX

525 1

n

n

H

482 .M ap

M

~-------

~uuuuuuu

u

1

1

4y 4P

++

465 487 4= 491

u u u u

n

JUUUUUUUUL

----- -----

263

nnn

481 4P 465 a7 m 4~1

u

n]

n n

++++

11

u u u

~

VERTICAL PULSE TIMING < NTSC > Shutter speed

;:+:

24681:

n

n

u

u u uuu

12468

n

u

“

21

n

[

n

59111315

n n n n

Uuuuuu

I

n n

+++++

3579111315

n

n

n

u u

u u

u

10

n

nnnnn nnnnn

4W

n

n

nnnnn

u uuu u

--~

uu~uuuu

H u

u

272 283

nnnnn

n

n

nnn

u uuu

u u

u

u uIJu

n

L

nnn

Uuu

n

n

n nnn n

n

n

nnn

u

u u

n

n n

n

n

u

u u

u

u u

nnn n

-n

. . ----- ----

II

uuu u

nnn n0n

n

n

n n n n

u u u

uuu u u u

n

IJu

1/10000 s

nnn n

1+2?416

n

n n

uuu

n

n

n

10 1+2 1+4

nnn

uuu

u

u u u

++

n

n

u

(l St,

(2nd,

296

3rd

CBLK

OFDX

4th

CBLK

OFDX

FIELD)

625 1

623

U—

HDI

VDI

J

5:6 5;8 ~ 5=

VIX n’mn’’’nn’n

V2X

V3X

V4X

VHIX

VH3X

n

u

u

nnn

u u

u u

u

uuu

flELD)

310

HDI

VDI

VIx n577f1579n58’J=’n

V2X

V3X u

V4X

VHIX

VH3X

n n

n

n

5:6 518 5P 5~

u u11u u uuu

u

u u u

VERTICAL PULSE TIMING < PAL >

nnn n n n

n n n n

u

H

nnn

n

o uIu u u

n

uuu

u u u u u u u

u

n n n

n n

n n n n

10 16 21 23

n

n n

11HuulJuuuu u

318 332 336

uuu u

n n

n n

n

n

n n

n

11

nnn

u

n

1

u

nnn

n n

n

u u uuu u

u

u

n

n

n n n

n n

n

u uuuuu u

n n nnn n

n n

n nnn n

11 11

n

n

n n

n nnn

u u

nnn

u

Uu

u

n

llu

n

u

u u

n

n

u u

. . .

UUUL

n

i+i

246

n

u u

I

n

146

n

u

u

u uuu u u u u u uuu

u u u u

Shutter speed

1/10000

3

:7

n

n n

u u

—

u u u

n n

t++

357

n

n

n

u u

u

s

Page 11

(ODD FIELD)

(EVEN FIELD)

HD

VI

V2X

V3X

v..

VHIX

VH3X

OFDX

HD

v!.

V2X

V3X

V4X

VHIX

VH3X

OFDX

x

18

}~.r+.

28Il

=..———~

CHARGE READ TIMING < NTSC >

H

98

5~

-,

I

H

I

—,

~——.—~

78

118

I

6a 128

19 H

121 2(01

1!

3;2;

898

I

———?z,?”~

L-—

II

281 H

121

+~

120

5~

w

I

118

78

2(o) 120

128

LZ93N61

(Ist,

3rd FIELD)

VHIX

VH3X

OFDX

(2nd, 4th FIELD)

VHIX

VH3X

OFDX

HD

VIX

V2X

V3X

V4X

332 H

HD

VI

V2X

V3X

V4X

x

o

—~—Y___

——

CHARGE READ TIMING < PAL >

,4

.——,

812 7M

-1

—

—

333 H

12WOI

~

L

118

lm

I

128

I

—

~

?~

I

m

I

———

120

_——

_——

118 322

I

i

28

__—

I

————

1

——wY—

Page 12

HDI

DOUT

FH

FH2

MCKI

MCK,

LZ93N61

HORIZONTAL PULSE TIMING

( )=

PAL

o

T

48

120

,!

169 (193)

.

SE

VI

V2X

V3X

V4X

OFDX

SINV SESL

W:h

LL

LH

T

,’

[~

x

58

48 108

6s

98

78

118

128

140

15s

298

Loading...

Loading...