Page 1

LZ93BE0

LZ93BE0

DESCRIPTION

The LZ93BE0 is a CMOS timing generator LSI

which provides horizontal transfer pulse, reset

Timing Pulse Generator

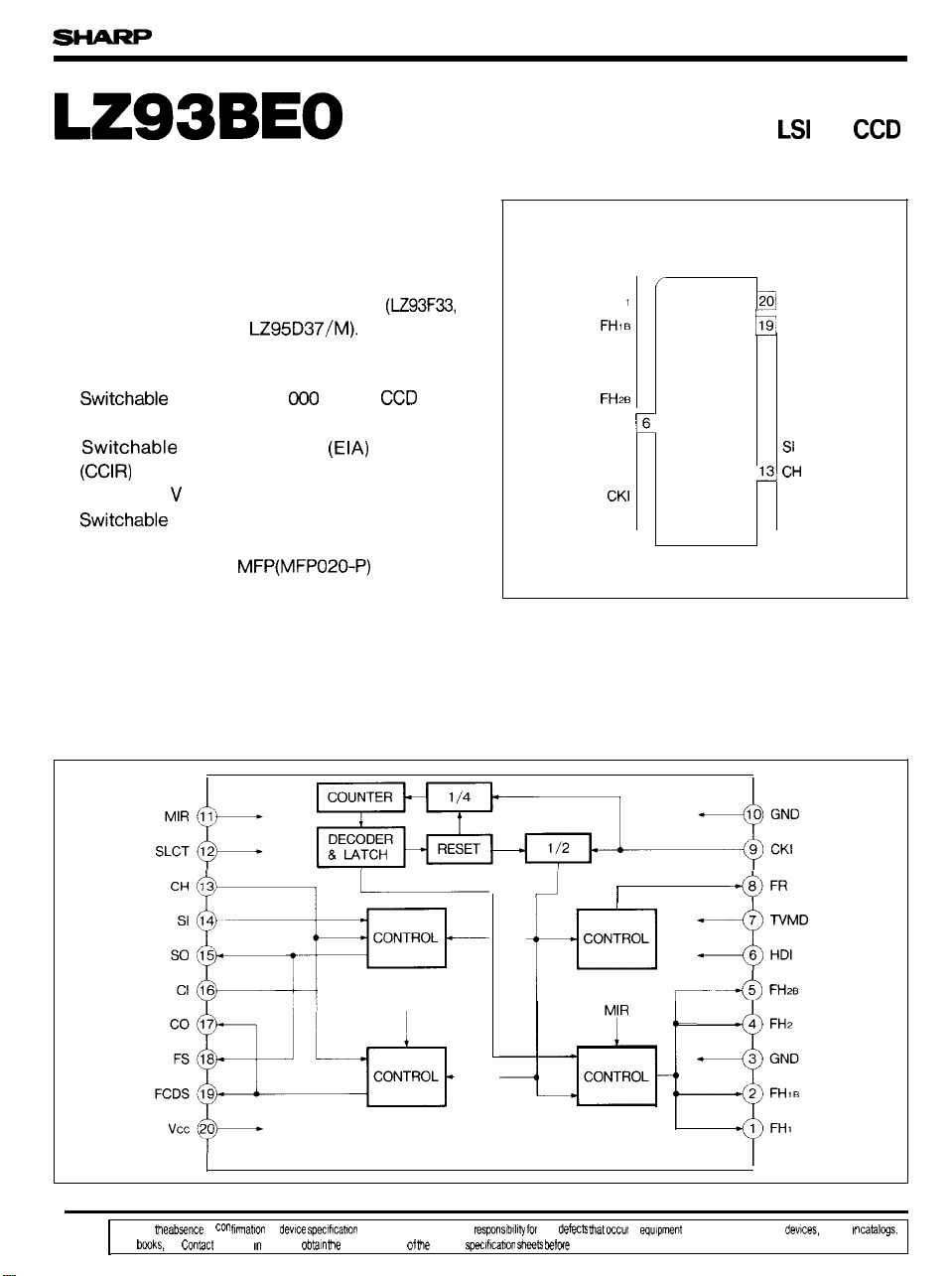

PIN CONNECTIONS

20-PIN MFP

pulse, and sample-hold pulse used for separate

camera, in combination with single-chip driver

LSI (LZ95G55, LZ95G41 ) and timing LSI

(LZ93F33,

LZ93F50, LZ93N61 or LZ95D37/M).

FEATURES

●

Switchable

320000 pixels CCD

●

Switchable between NTSC

(CCIR)

●

Single +5 V power supply

●

Switchable

●

Suitable for separate camera

●

Package : 20-pin

☛

Designed for A-type and B-type CCD area sensors :

A-type CCD area sensor : LZ2314J, LZ2324J, LZ231 32, LZ23232

B-type CCD area sensor : LZ2414J, LZ2424J, LZ2313H5,

between 270 ~0 pixels

(EIA)

and PAL

systems

between normal and mirror-image

MFP(MFP020-P)

LZ2323H5, LZ2413, LZ2423

CCD

and

FH

FHIB

GND

FH2

FH2B

HDI

TVMD

CKI

GND

FR

LSI

for

CCD

TOP VIEW

/“

I

1

=

o

2

3

4

5

~

7

8

9

10

a

Vcc

~

FCDS

18 FS

17

co

16 cl

15 so

14

SI

g

CH

12 SLCT

11 MIR

BLOCK DIAGRAM

“in

tie

ab%nce

of

256

I

data

bwks, etc

con f(nnatlon

CQntacl

SHARP In order to obkln he latest version of

by

device $pectf{cation

sheets, SHARP takes no respnslb(l[v

tie

device

wlf!cation *wts betcn’e

for

any defecs hat

using any SHARPs device’

xcur

in

equipment

using any of SHARPs

devices,

shown In cahlcgs,

Page 2

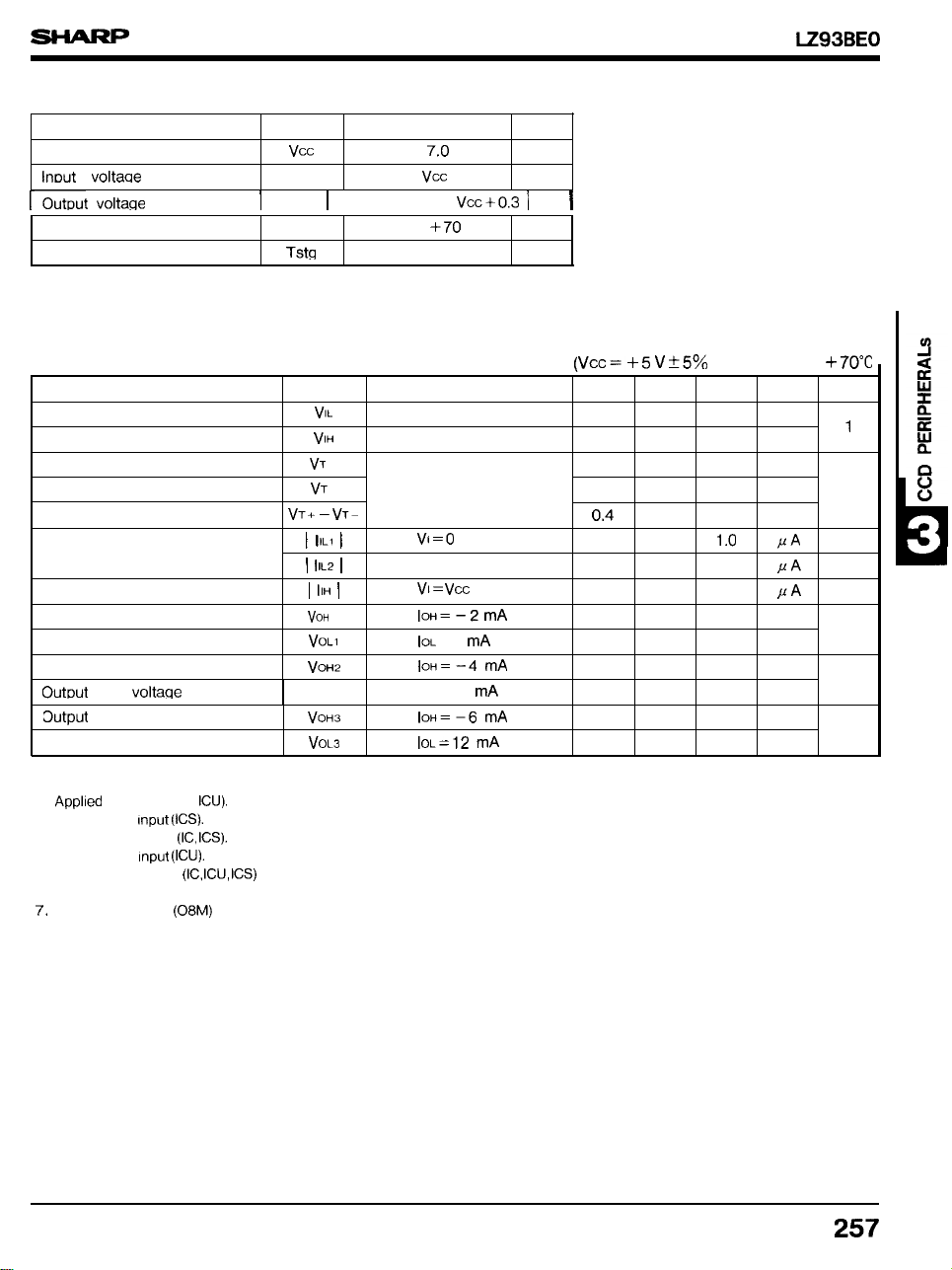

ABSOLUTE MAXIMUM RATINGS

PARAMETER SYMBOL RATING

Supply voltage

lnDut

voltaae

Gt

voltage

Operation temperature

Storaae temperature

Vcc

VI

I

Vo I -0.3 to VCC+O.3 ] v

Topr

Tstq

– 0.3 to

–0,3 to

–20 to

7.0

Vcc

+70

–55 to +150

+ 0.3

LZ93BE0

UNIT

v

v

I

‘c

“c

DC CHARACTERISTICS

PRAMETER

Input Low voltage

Input High voltage

Input High threshold voltage

Input Low threshold voltage

Hysteresis voltage

Input Low current

Input High current

Output High voltage

Output Low voltage

Output High voltage

OutDut

LOW voltaae

output

High voltage

Output Low voltage

NOTES :

Applled

1.

2. Applied to

to inputs (IC,

Input (ICS).

3. Applied to inputs

4. Applied to

Input (ICU).

5. Applied to inputs

6. Applied to output (0)

7.

Applied to output (08M)

8 Applied to output (012M)

ICU).

(IC, ICS).

(IC, ICU, ICS)

SYMBOL

vlL

vlH

vT +

vT

vT+

–VTI IIL1 I

I

11L2 I

I

IIH

vOH

vOL1

vOH2

v0L2

vOH3

vOL3

(VCC=+5

CONDITIONS MIN.

Vf5%

Ta=–20 to

TYP.

MAX.

1.5 v

UNIT

3.5 v

+7UC

NOTE

1

2.2 3.8 v

Schmitt Buffer 1.0 2.4 v

2

0.4 v

Vl=o

v

Vl=o v

I

1

VI= Vcc

IoH=– Z

IOL

= 4

IoH=–4

IOL = 8

mA

mA

mA

mA

IoH=–6 mA

8.0 60

4.0 v

4.0 v

4.0 v

10.=12 mA

1.0

1,0

0.4

0.4

0.4 v

,uA 3

,uA

PA

v

v

4

5

6

7

8

257

Page 3

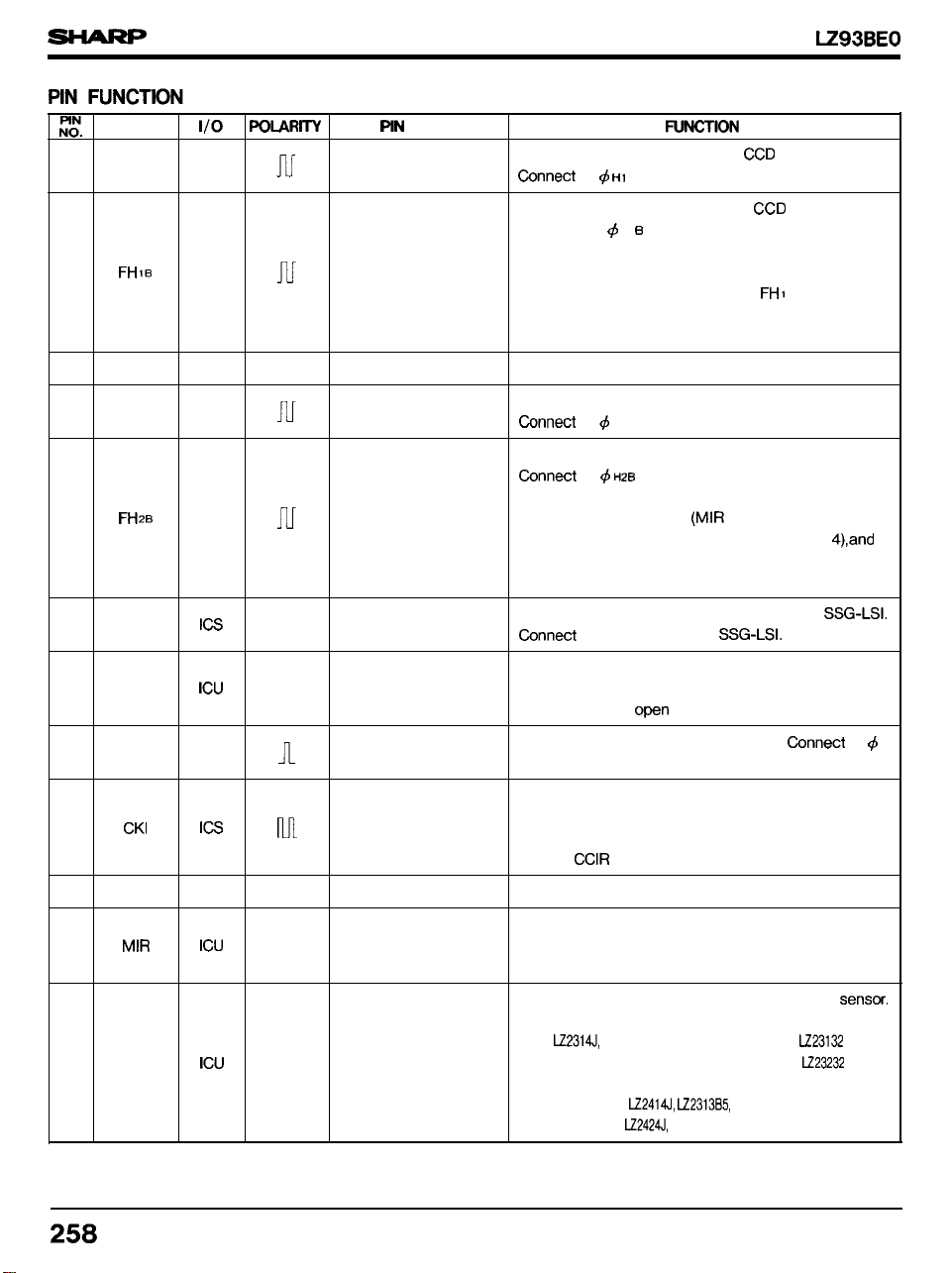

:!.

10

11

12

1

2

3

4

5

6

7

8

9

SYMBOL

FH

I

FHIB

GND

FH2

FHZB

HDI

TVMD

FR

CKI

GND

MIR

SLCT

1/0

012M

08M

–

012M

08M

Ics

Icu

08M

Ics

–

Icu

Icu

POIARITY

N

m

–

m

m

–

–

n

nn

–

—

—

PfN

NAME

Horizontal transfer

pulse 1

Horizontal transfer

pulse 1 B

Ground

Horizontal transfer

pulse 2

Horizontal transfer

pulse 2B

Horizontal reference

pulse

TV mode select

Reset pulse

Clock input

Ground

Mirror mode select

CCD type select

LZ93BE0

FLfNCTION

A horizontal transfer pulse for

tinnect

to 4 HI of CCD area sensor.

A horizontal transfer pulse for

Connect to

area sensor which corresponds to Mirror mode is

driven at Normal mode (MIR = L), its drive-pulse is

the same phase as the pulse of

is the same phase as the pulse of FH2 (pin 4) at

Mirror mode (MIR = H).

A grounding pin.

A horizontal transfer pulse for CCD area sensor.

~nfleCt to ~ HZ of CCD area sensor,

A horizontal transfer pulse for CCD area sensor.

bnnect

area sensor which corresponds to Mirror mode is

driven at Normal mode

the same phase as the pulse of FH2 (pin

is the same phase as the pulse of FH

Mirror mode (MIR = H).

Put in a horizontal reference pulse from

~nnect

An input-pin to select TV standards,

A reset pulse for CCD area sensor, bnnect to ~ R

of CCD area sensor through the DC offset circuit.

An input pin for reference clock.

The frequencies are as follows :

A grounding pin.

An input pin to select Mirror mode or Normal mode.

An input pin to select the type of CCD area

L level (A type)

H level or open (B type)

4 HI E of CCD area sensor. If the CCD

to 4

H2E

of CCD area sensor. If the CCD

to HD terminal of

L level : NTSC mode

o~n

H level or

At EIA mode : 19.06993 MHz (1212 fH)

CCIR

mode : 19.31250 MHz (1 236 fH)

At

L level : Normal Drive mode

H level or open : Mirror Drive mode

LZ23t4J,

LZ2314Z, LZ23t42, LZ2313A9,

LZ2324J, LZ2324Z, LZ23242, LZ2323A9,

LZ2314BK,

LZ2324BK,

: PAL mode

LZ2414J, LZ2313B5,

U2424J,

LZ2323B5, LZ2323H5, LZ2423

CCD

area sensor.

CCD

area sensor,

FHI

(pin 1), and it

(MIR

= L), its drive-pulse is

SSG-LSI.

LZ23132

LZ23232

LZ2313H5, LZ2413

4),and

I (pin 1 ) at

SSG-LSI.

sensw,

it

Page 4

U93BE0

WN

“~

SYMBOL

13

14

15

18

17

18

CH

SI

so o

cl Ic

co o

FS

19 FCDS

20

Vcc

POtARiTY

1/0

Icu

Ic –

o

o

–

nn

nrl

PIN NAME

FUNCTION

An input pin to select the phase of FCDS (pin 19)

Phase control terminal

—

for FCDS and FS

pulse and FS (pin 18) pulse.

L level : adjustable

H level or open : fixed

Phase-adjust input

for FS

Phase-adjust output

for FS

—

Phase-adjust input

for FCDS

Phase-adjust output

for FCDS

An input pin to control the phase of FS (pin 18).

SO (pin

15)

pulse put in this terminal after make it

delay with resistor and capacitor.

An output pin to control the phase of FS (pin 18).

The output pulse put in

S1

(pin 14) after make it

delay with resistor and capacitor.

An input pin to control the phase of FCDS (pin 19).

CD

(pin 17) pulse put in this terminal after make it

delay with resistor and capacitor.

An output pin to control the phase of FCDS (pin 19).

The output pulse put in Cl (pin 16) after make it

delay with resistor and capacitor.

A pulse to sample-hold the signal from CCD area

n

output

Sample-hold pulse

sensor. The phase of FS is fixed if CH (pin 13)

equals H level and it can be adjustable if CH (pin

13) equals L level.

A pulse to clamp the feed-through level form CCD

n

CDS pulse output

—

Power supply Supply +5 V power.

area sensor. The phase of FCDS is fixed if CH (pin

13) equals H level and it can be adjustable if CH

13)

equals L level.

(pin

Ic

Icu

Ics

O, 08M, 012M : Output pin

: Input pin (CMOS level input)

: Input pin (CMOS level input with pull-up resistor)

: Input pin (CMOS

scnmiti

input )

NOTE :

the input pin, the rising edge of HDI (pin 6) is f 20 ns shorter than that of CKI (pin 9).

At

259

Page 5

TIMING DIAGRAM

LZ93BE0

1212,0

HDI

CBLK

CKI

FH

I

FHz

FHIB

FH2B

FR

FCDS

FS

114 120

HDI

CBLK

CKI

FH

I

FH2

FHIB

FHZB

FR

~wnnnnn

FCDS

FS

Ulnllnnnnnl lnnnnmnnnnlllln

1212,0 8

HDI

CBLK

CKI

FH

I

FH2

FHIB

FH2B

OBIXXX XXX

FR

Pw~nnnn

FCDS

m~nnnnL!lnnnnllnnn

FS

lnnnnnnn~

114

116 120

T

HDI

CBLK

CKI

FH

I

FHz

FHIe

FH2B

NTSC(EIA) < A-TYPE, NORMAL MODE >

49

166

–—

XX X X1212345678

nnnnnnnn~nnnnnnnn

~~~m

NTSC(EIA)

1111 JIJlnnn Mnn nnnnnn~flflflnnnflfl~flfl

< A-TYPE, MIRROR MODE >

nnnnlln nluLJlnnflnnn

nnnrlnnnnnnnn

~d~w

~~JL

101214161

~mdw~

210

210

flfl

1 clock = 52.4 ns

~202224 26

1~

clock = 52.4 ns

1

n

rd~

114

114

FCDS

FR

FS

Page 6

HDI

CBLK

CKI

FH 1

FH2

FHIB

FH2B

FCDS

HDI

CBLK

CKI

FH

FH2

FHiB

FHZB

FCDS

FR

LZ93BE0

1

!

clock= 52.4 ns

—

174

NTSC(EIA) < B-TYPE, NORMAL MODE >

163

47

210

1212,0

1

I

FS

120

14

I

I

FR

FS

HDI

CBLK

CKI

FH

FH2

FHIB

FHZB

FCDS

HDI

CBLK

CKI

FH

FH2

FHIB

FH2B

FCDS

T

FR

FS

114 120

I

FR

FS

1212,0 3

J

OBIXX X X

1

XX X X XOB28

nnnll~nn

Jflflflflflflnflflfl~

NTSC(EIA)

nnnnruulnnnnnnn~n

nnnnnluln nnnluuuulnllnnnn

0B20

< B-TYPE, MIRROR MODE >

nnn~flflnflnflflfl

nnluuuuLnnnfl~flflflflfl

OB1O

nnlLrLn nnnrLnflnnn~

OBI 512 510 W

5C6 W W2

1 clock

=52.4

flnflfl~

210

,

500 498 496 494 492 4W

flflfl~

‘nnnm

111 114

flu

W

ns

x

261

Page 7

U93BE0

1236,0

HDI

—

CBLK

CKI

FH

I

FH.

FHi

B

FH2B

FR

FCDS

HDI

CBLK

CKI

FH

FH2

FHIB

FH2B

FR

FCDS

HDI

CBLK

CKI

FH

FH2

FHIB

FH2B

FR

FCDS

0B4

nnnflnnn nnnnnn~nnnmnnnnnm

FS

mflnnnn

nnflnflnnnn~

114 120

I

I

nnnnnnn nnnnnJnnnnnMnnnn

FS

lnnnnll nMnnflnnnnunnn

12%,0

3

I

m

m

Ju

lr

JL

OBIXXXXXX

FS

mnnnlLll

nnllnnluLll_n nnnnnn~

nnnnn~n

PAL(CCIR)

OB1O

nnllnnn nnwflflnnnnJLluLll

nllnnllmnnnn~nnnnn

OB20

PAL(CCIR)

nnnfl Mnnllnn nnnnnnn nflnnn Mnnnnflfln~

nnnnnMnnnnnllnnn

< A-TYPE, NORMAL MODE >

48

0B28

nnnnnnn nnnnnnflnnnnnnnnn~

nnnnn Mnnnnnn

nnnnnn Mnnnnnnn

nnflnnnnnnnn

192

J

JunUL--

XXXX1212345878 10 12 14

nmnnnnn

nllflfl nnnnllll n~nllnnnnll

nn~llnllnnnnnnn

< A-TYPE, MIRROR MODE >

nnnnnnn nnnnnnnnnnnnnnnn

nnnnnlLn_lLn nllflllnllnnnnmfl

nmnnnnnnnnnnnn

m

u“mT’-1

MnnnnnJ

nnnnfln~

UlnMMM

m

u

J-LnnrL

1-nruLrL

1

nmnnnnllnnm

nnnnnnllnn~

1 clock = 51.8 ns

nnflm

nnnnLILIL

~

UuuLrLr

UuuLnr

m~

clock

1

nnLILrLJuLILIL

llln

I

1.-

n~

=51.8

ns

114

234

1

_-

r

114

262

114i 20 140

HDI

CBLK

CKI

FH

FHz

FH

FH2B

FR

FCDS

I

IB

FS

I

m

Uul

~

-uuLv~

u

ULruL

nn~

XX X

Mnnnnnn ruLnnnhnnnnn~ nnnnnnn nnnnnnnnnn~n

XOB28

nnnnnnn nnnnnnnnnnnnnnnn

JMnnnnn

nnnn Mnnnnnnnnn

OB20

nnflnnn nnnnnnnnnnnnnnnnn

nnnJnnn nn~nnnnnnnnnufl

~

mnnnn~

OB1O

OB1 512 510 5W 506 504 502

nnnnnnnnnnnn

nnnnn~

~L

flflflflfl~

234

L

~

Page 8

LZ93BE0

PAL(CCIR)

7236,0 47 114

HDI

CBLK

CKI

FH

I

FH.

FHIe

FH2B

FR

FCDS

FS

HDI

CBLK

CKI

FH

FH2

FHIB

FH2B

FR

FCDS

FS

OB4

m~Lrlnn

lnnflnn nnmnnnnnnllnn~

114 120

t

OB1O

nnnllnn~

m~nn

0

PAL(CCIR)

i236,0

3

HDI

CBLK

CKI

M

UIM

FH

FHz

FHIB

FH2B

FR

FCDS

FS

HDI

CBLK

CKI

FH

FHz

I

I

~~

m

m

7n

rLul7n

OBIX

X X X

nnnllnlln~

114 120 135 234

Hum

~

< B-TYPE, NORMAL MODE > 1 clock =51,8 ns

OB~

llnnnnnnllllfln

OB28

Ln

nnnnnnn nMnnflnnnnnnnnn~

nnnn~

187

u

Juuu

u

W

mJm

m1m

M

m

nn~

nnnnnMn

nnnnnnnnn~nnnlln~

nnnnnn Lnnnnflnn nnnnn~

< B-TYPE, MIRROR MODE > 1 clock=51.8 ns

XXXXXX121234567 8 10 12 14

234

mJ-nv.

mJnu

nnllnllnrL

nnnnr

L

-

i14

L

FR

mnnnnnnn~

FCDS

nnnnnnn nnnnnnnnnnnnnnnnn

FS

lnnnnnn nnnnJnnnnnnnnnn nlLILnnnllnnnllnn~

XXXXXXOB28

OBm

nnnnnnn nnnnnnnnnMnnnnnn

OB1O

nnnnnnn nnnnflnnnnnnnnnnnn

OBI 512 510 W ~ 504 W2 500

ruuuuulnllllllllll

nnnn;

:

263

Page 9

LZ93F33

264

LZ93F33

DESCRIPTION

The LZ93F33 is a CMOS timing generator LSI

which provides timing pulses used to drive a

CCD

area sensor, in combination with the SSG

LSI (LZ93N19 or LZ93B53).

FEATURES

●

Switchable

320000 pixels CCD

●

Switchable between NTSC

(CCIR)

●

Built-in EE (Electronic Exposure) control

●

Flicker-less function

●

Switchable between normal and mirror image

●

Single +5 V power supply

●

Package : 48-pin QFP(QFP048-P-101 O)

between 270000 pixels CCD and

(EIA)

systems

TO GND

and PAL

GND

Timing Pulse Generator LSI for CCD

PIN CONNECTIONS

48-PIN QFP

cx$:i~::$ic~

v3k

37 24 MCDI

V4X

$

OFDX

39

FR

40

FHZB 41

FH2

42

GND 43

FH Iz

FHIB

45

CKI 46

CKO

47

TEST 48

GND Vcc TEST

>S>>oa>z+>z

0

llf121131141]

aaogoood>om

r>nzzzz~~~z

511611711811911101111 ]l12

~tiu<uwwm

Vlx

TSTO

UJwu.lk

2

o

+

TOP VIEW

23

MFS2

22

MFSI

21

FS

20

FCDS

19

INSL

18

TO

17

SE

16

SINV

15

SESL

14

SP2

13 SP1

VDI

TVMD

MIR

ACL

TOSL

DO

CKI

CKO

HDI

EEST

EEUD

EENR

EEMD

FLMD

“In be abwnce of

I

data

confinnahon

Wks, etc.

Contact SHARP Im uder to

by

dev[ce

sw[flcahon aheek, SHARP

obm(n tie Iateat

4

i

wmlon of the

r

SHU~ER

UP/DOWN

CONTROL

SHUTTER

SPEED

CONTROL

takes

no rewnmblllv fci any

dev!ce Wlfcahon

defacta tiat cccur

shwts

kf~

using any SHARPs device”

in

equipment

1

V2X

V3X

V4X

VHIX

VH3X

OBCP

SINV

SESL

FHI

FHIE

FH2

FHZB

FR

FS

FCDS

C“NTR”’

using any of WARPs

SE

B

SP2

SPI

MFSI

MFS2

MCDI

MCD2

I

MFR

MFR2

INS’

OFDX

devices, ah~ In

ca~lws,

Loading...

Loading...