Daewoo 20T1, 20Q2, 21T2, 14T1, 20Q1 User Manual

...

Service Manual

38 / 48 / 51 Cm Mono Colour Television

CHASSIS : CP-370

MODEL : 14Q1/20Q1/21Q1 14Q2/20Q2/21Q2 14Q3/20Q3/21Q4 14T1/20T1/21T1 14T2/20T2/21T2 14T3/20T3

¿Ä@,

¿Ä@,

DAEWOO ELECTRONICS CO., LTD.

CONTENTS |

|

Specifications ................................................................................................................ |

1 |

Safety Instruction ......................................................................................................... |

2 |

Circuit block Diagram ................................................................................................. |

3 |

Alignment Instructions ............................................................................................... |

4 |

IC Description ................................................................................................................ |

7 |

Circuit Description ....................................................................................................... |

31 |

PCB Layouts |

|

PRINTED CIRCUIT BOARDS .................................................................................... |

38 |

SCHEMATIC DIAGRAM ............................................................................................. |

39 |

Trouble Shooting Charis ............................................................................................. |

40 |

Important IC Voltage Charts .............................................................................................. |

47 |

Electrical Part List............................................................................................................... |

49 |

Q Model T Model Difference Part List ............................................................................... |

64 |

Inch difference Part List ..................................................................................................... |

65 |

Mechanical Exploded View and Part List ......................................................................... |

66 |

Specifications

Specifications

Q : 1SPEAKER MODEL, T : 2SPEAKER MODEL

Q : 1SPEAKER MODEL, T : 2SPEAKER MODEL

VM : WITHOUT TXT. MODEL, TM : WITH TXT. MODEL

TV Standard |

PAL/SECAM-B/G, D/K, I, H, NTSC-3.58/4.43 |

||||

|

|

|

|

|

|

Mains Voltage |

100~250V AC, 50/60Hz |

|

|

||

|

|

|

|

|

|

Power Consumption |

14”Q = 69W, 14”T = 74W |

|

|

||

|

20”Q = 79W, 20”T = 84W |

|

|

||

|

21”Q = 79W, 21”T = 84W |

|

|

||

|

|

|

|

|

|

Sound output |

|

|

. 1 Speaker : 3W( at 80% MOD. 10% THD) |

||

|

|

||||

|

|

|

. 2 Speaker : 4W + 4W( at 80% MOD. 10% THD) |

||

|

|

|

|||

|

|

|

|

|

|

Speaker |

|

|

. 1 Speaker : 3W, 16 ohm |

||

|

|

||||

|

|

|

. 2 Speaker : 7.5W, 8 ohm(2EA) |

||

|

|

|

|||

|

|

|

|

||

Antenna |

75 ohm unbalanced |

|

|

||

Impedance |

300 ohm balanced with supplied balun |

||||

|

|

|

|||

Tuning system |

Voltage Synthesize Tuning System |

||||

|

|

|

|||

Memory channel |

VM : 100 channels, TM : 70 channels |

||||

|

|

|

|

||

Reception |

VHF - L : CH2 - CH4 |

|

|

||

channel Unit |

VHF - H : CH5 - CH12 |

|

|

||

|

Cable Band : CHS1’ - CHS3’, CHS1 - CHS20 |

||||

|

Hyper Band : CHS21 - CHS40(option) |

||||

|

UHF : CH21 - CH69 |

|

|

||

|

|

|

|||

Remote control |

VM : R-28B04, TM : R-28B03 |

||||

|

|

|

|

||

Screen size |

14” : 34cm (A34JLL 90 |

02) |

|

||

|

20” : 48cm (A48JLL 90 |

02) |

|

||

|

21” : 51cm (A51JLL 90 |

02) |

|

||

|

|

|

|

||

Weight |

14” : 9.5Kg(set) |

|

|

||

|

20” : 16.5Kg(set) |

|

|

||

|

21” : 20.5Kg(set) |

|

|

||

|

|

|

|

||

Indication |

On-Screen Display |

|

|

||

|

- MENU |

|

|

||

|

|

|

Picture(Bright, Color, Contrast, Sharpness, TINT) |

||

|

|

|

TIMER(CLOCK, WAKE-UP-TIME, ACTIVATE, WAKE-UP-PROG) |

||

|

|

|

LANGUAGE |

|

|

|

|

|

PRESET |

|

|

|

|

|

EDIT |

|

|

|

|

|

SLEEP TIMER |

|

|

|

|

|

AV |

|

|

|

|

|

SOUND MUTE |

|

|

|

|

|

VOLUME CONTROL |

|

|

|

|

|

|

|

|

1

Safety Instruction

Safety Instruction

WARNING: Before servicing this chassis, read the “X-RAY RADIATION precaution”, “safety precaution” and “product safety notice” below.

X-RAY RADIATION PRECAUTION

X-RAY RADIATION PRECAUTION

1.Excessive high voltage can produce potentially hazardous X-RAY RADIATION.To avoid such hazards, the high voltage must not exceed the specified limit. The nominal value of the high voltage of this receiver is 22-23kv(14”), 2526kv(20”, 21”) at max beam current. The high voltage must not, under any circumstances, exceed 27.5kv (14", 20”), 29.0kv(21”).

Each time a receiver requires servicing, the high

voltage should be checked. It is recommended the reading of the high voltage recorded as a part of the service records. it is important to use an accurate and reliable high voltage meter.

2.The only source of X-RAY Radiation in this TV receiver is the picture tube. For continuous RADIATION protection, the replacement tube must be exactly the same type tube as specified in the parts list.

SAFETY PRECAUTION

SAFETY PRECAUTION

1.Potentials of high voltage are present when this receiver is operating. Operation of the receiver outside the cabinet or with the back cover removed involves a shock hazard from the receiver.

1)Servicing should not be attempted by anyone who is not thoroughly familiar with the precautions necessary when working on highvoltage equipment.

2)Always discharge the picture tube to avoid the shock hazard before removing the anode cap.

3)Discharge the high potential of the picture tube before handling the tube. The picture tube is highly evacuated and if broken, glass fragments will be violently expelled.

PRODUCT SAFETY NOTICE

PRODUCT SAFETY NOTICE

Many electrical and mechanical parts in this chassis have special safety-related characteristics.

These characteristics are often passed unnoticed by a visual inspection and the X-RAY RADIATION protection afforded by them cannot necessarily be obtained by using replacement components rated for higher voltage, wattage, etc. Replacement parts which have these special safety characteristics are identified in this manual and its supplements, electrical components having such features are

2.If any Fuse in this TV receiver is blown, replace it with the FUSE specified in the Replacement Parts List.

3.When replacing a high wattage resistor(oxide metal film resistor) in circuit board, keep the resistor 10mm away from circuit board.

4.Keep wires away from high voltage or high temperature components.

5.This receiver must operate under AC260 volts, 50Hz/60Hz. (AC 100~250 volts, 50/60Hz)NEVER connect to DC supply or any other power or frequency.

identified by designated symbol on the parts list. Before replacing any of these components, read the parts list in this manual carefully. The use of substitute replacement parts which do not have the same safety characteristics as specified in the parts list may created X-RAY Radiation.

2

Alignment Instructions

Alignment Instructions

1.AFT

1.1Standard B/G,D/K,I

1)Set a Signal Generator with

-RF FREQUENCY = 38.9 MHz,

- RF OUTPUT LEVEL = 80 5 dBuV

- System = PAL / SECAM - B/G, D/K, I

NTSC - 3.58/4.43

2)Connect the Signal Generator RF Output to P101 (Tuner IF Output). There must be no signal input to the tuner.

3)Press the “AFT” KEY and wait until the TV screen display “AFT OK”.

2.AGC

1)Set a Pattern Generator with RF LEVEL 63° 2 dBuV .

2)Connect a OSCILLOSCOPE PROBE to P102 (TUNER AGC INPUT).

3)Adjust AGC UP/DOWN KEY the voltage drop 3.5V dc point its maximum voltage.(TDA8374A N1 VERSION) Adjust AGC UP/DOWN KEY the voltage drop 1.5V dc over blow its maximum voltage(TDA8374A N3 VERSION)

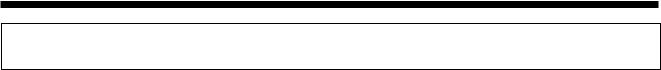

Alternative Method

1) Set a Pattern Generator with

- RF LEVEL 80 |

5 dBuV |

- PAL CROSSHATCH |

|

( without SOUND CARRIER ) |

|

2) Connect a OSCILLOSCOPE |

|

( Bandwidth |

100MHz ) PROBE |

to P101 (TUNER IF OUTPUT).

3) Use AGC UP/DOWN KEY to obtain |

|

|

||

|

an envelop amplitude 200 + 20 mVp-p. |

|

|

|

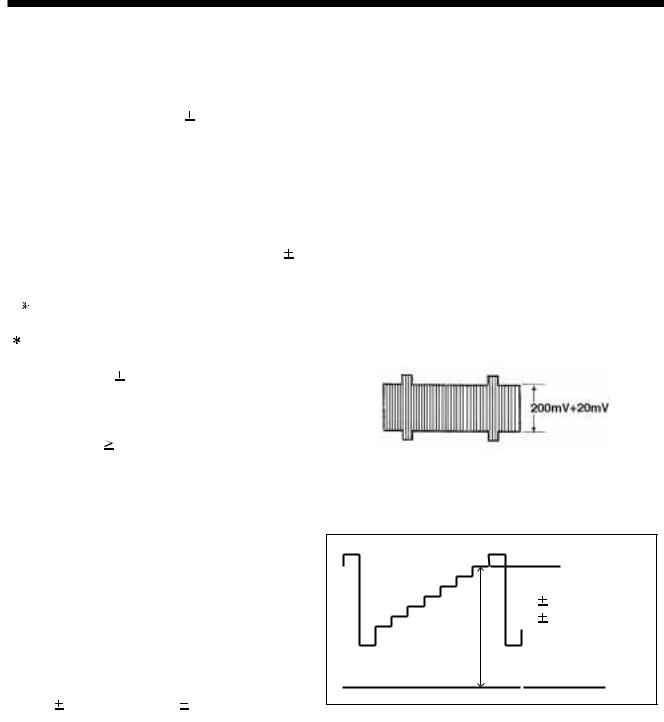

3. SCREEN |

|

|

|

|

1) |

Apply a COLOR BAR pattern signal. |

|

|

|

2) |

Set the CONTRAST, BRIGHTNESS |

|

Black level |

|

|

to MAX, COLOR to MIN. |

|

|

|

3) |

Set the R,G,B LEVEL to CENTER (31/63) |

160 |

5Vdc ( 20”, 21” ) |

|

|

with R,G,B UP/DOWN KEY. |

|

130 |

5Vdc ( 14” ) |

4) Connect a OSCILLOSCOPE PROBE |

|

|

||

|

to P904 ( CRT CATHOD R, G, B ). |

|

|

|

5) Adjust the SCREEN VOLUME on FBT |

|

|

||

|

such that the highest black level voltage |

|

GND |

|

|

160 5Vdc (20”, 21”), 130 |

5Vdc (14”). |

|

|

4.WHITE BALANCE

1)Set the TV to NOR I mode.

2)Set the R,G,B LEVEL to CENTER with R,G,B UP/DOWN KEY .

3)Adjust the R,G,B UP/DOWN KEY of the other color which did not appear on the screen to obtain WHITE.

5.FOCUS

1)Apply a RETMA PATTERN signal.

2)Adjust the FOCUS VOLUME on FBT to obtain optimal resolution.

4

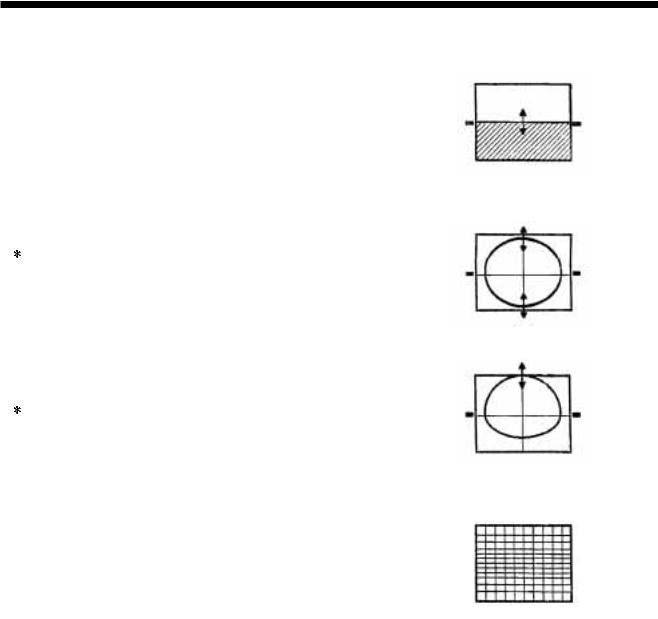

6.GEOMETRY

6.1VERTICAL CENTER

1)Set the TV to NOR I mode.

2)Pressing the V-SIZE UP/DOWN KEY, the lower half of the screen is blanked.

3)Adjust the border line of blanked picture coincident with the mechanical center marks

of the CRT using the V-CENTER UP/DOWN KEY.

6.2VERTICAL SIZE

The VERTICAL CENTER adjustment has to be done in advance.

1)Apply a RETMA PATTERN signal.

2)Set the TV to NOR I mode.

3)Adjust the upper part of the picture with the V-SIZE UP/DOWN keys.

6.3VERTICAL SLOPE

The VERTICAL SIZE adjustment has to be done in advance.

1)Apply a RETMA PATTERN signal.

2)Adjust the lower part of the picture with the V-SLOPE UP/DOWN keys.

6.4VERTICAL S-CORRECTION

1)Apply a CROSSHATCH PATTERN signal.

2)Adjust the S-COR UP/DOWN KEY to obtain the same distance between horizontal lines.

6.5HORIZONTAL CENTER

1)Apply a RETMA PATTERN signal.

2)Adjust picture centering with H-CENTER LEFT/RIGHT keys.

5

If EEPROM(1703) has been changed ;

-Option data has to be changed and

-all alignment function has to be readjusted.

The initial state of adjustment are as follows;

The initial state of adjustment are as follows;

- V-Center, V-Slope V-Size, H-Center, R, G, B, AFT = Center (30/64 - 33/64)

-S-Correction = 00/64

-AGC = 15~60/64

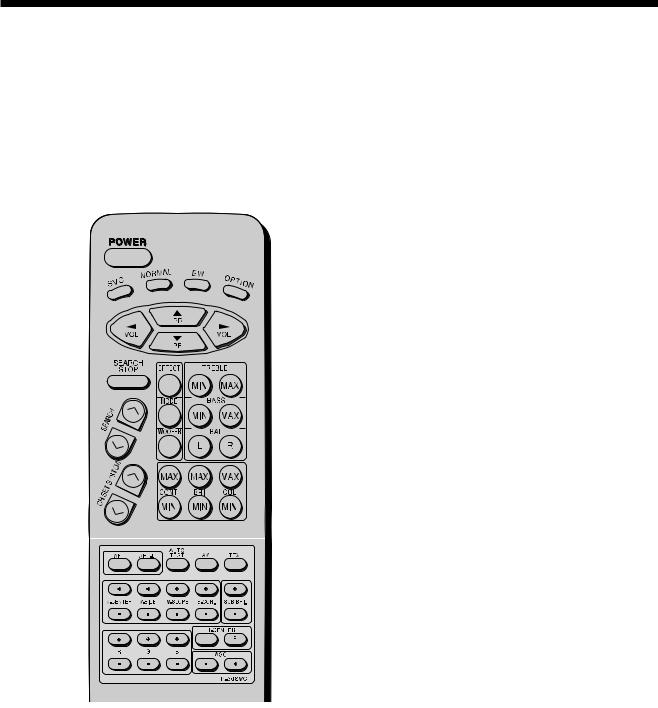

Service Remocon

Service Remocon

6

IC Description

IC Description

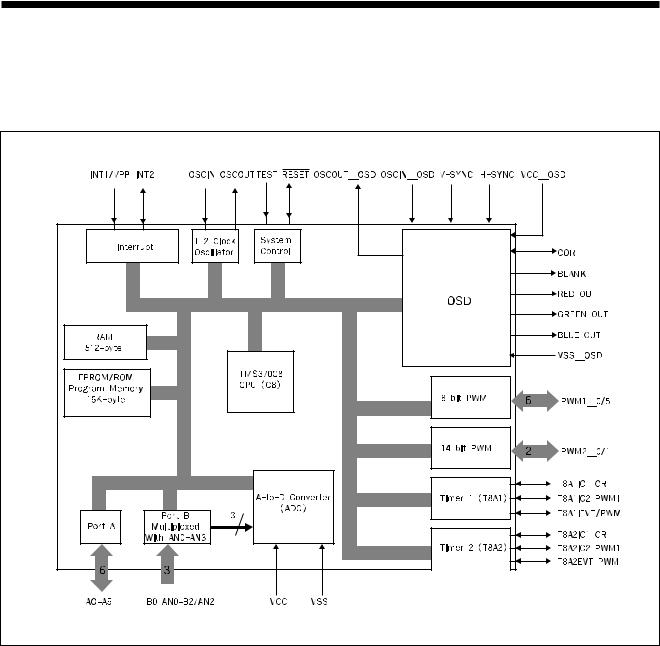

DW370ASM* (Micro-controller for Non-Teletext Model) =TMS370C08A05 ( TI Type No.)

(1)General Description

The TMS370C08A05 devices are members of the cMCU370 family single-chip microcontrollers.

The cMCU370 family provides cost effective real-time system control through use of the PRISM methodology.

The PRISM methodology modular fabrication process integrates analog, digital, linear and power technologies on a single chip, thereby maximizing the total integration strategy.

The TMS370C08A05 devices are designed with the high-performance 8-bit TMS370C8 CPU.

Features of the ‘C8 CPU and system module as implemented on this device include three CPU registers (stack pointer, status register, and the program counter), two external interrupts, reset, memory mapped control registers.

(2)Feature

•Internal Memory Configurations

-16K-Byte ROM Program Memory

-512-Byte RAM

•Operating Features

- Supply Voltage (VCC) 5 V ° 10%

-Input Clock Frequency 2, 20MHz

-Industrial Temperature Range

•Device Integrity Features

-Address Out-of-Range Reset

-Stack Overflow Reset

-Parallel Signature Analysis (CRC)

•Two 16-Bit General Purpose Timer(T8A)

Each Includes:

-16-Bit Resettable Counters with individual 8-Bit Prescaler

-2 PWM Channels or

-2 Input Captures or

-1 Input Capture and 1 PWM Channel

•One 14-Bit PWM Module

-14-Bit Resettable Counters

-14-Bit PWM Output Port

•One 8-Bit PWM Module

-8-Bit Resettable Counters

-8-Bit PWM Output Port with 12V Open Drain

•OSD Module

-Blanking/ Contrast reduction out

-Transparent Background

-Transparent Foreground

-Full Screen Background Color

-Controlled Color, Blink, Size, Smoothing, Fringe of Each lines of Character

-Two size of different Font 12x10 and 12x18 by Hard Masking

-OSD Window Display with 40x25 lines

•8-Bit A/D Converter With 3 Inputs

-Single or Dual Channel Operation

-Single or Continuous Conversion Modes

•Flexible Interrupt Handling

-Global and Individual Interrupt Masking

-2 S/W Programmable Interrupt Levels

-2 External Interrupt (1 Non-Maskable)

-Programmable Rising or Falling Edge Detect

7

•09 CMOS Compatible I/O Pins

-All Peripheral Function Pins Software Configurable for Digital I/O

-6 Bidirectionals, 3 Input Pins

•Plastic 42 YSDP Pins Package

(3)Block Diagram

8

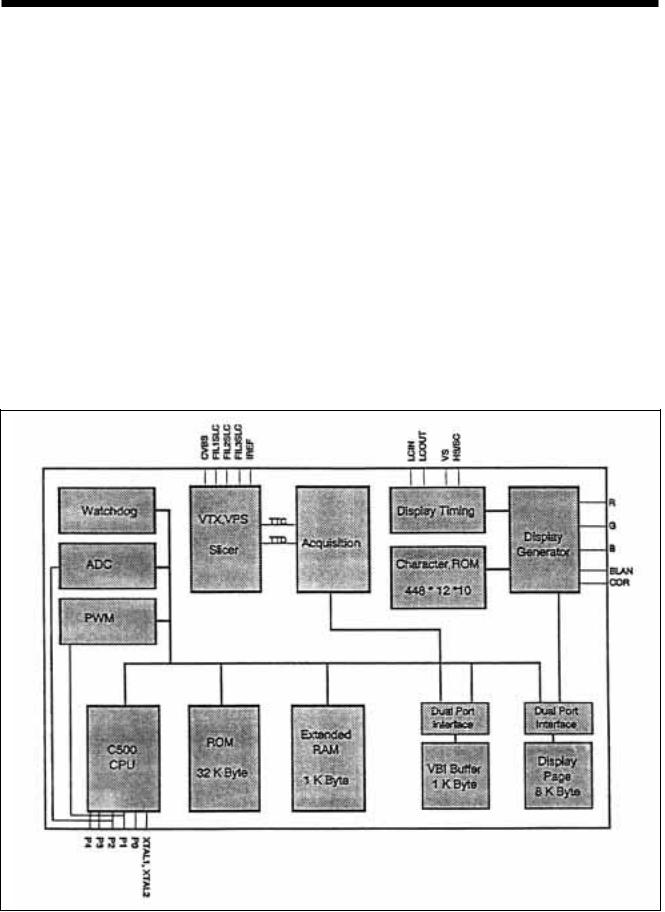

DW5255M*(Micro-controller & West/East Teletext Decoder)

DW5255RM*(Micro-controller & Cyrillic Teletext Decoder)

=SDA5255-A*** (SIEMENS Type No.)

(1)General Description

The TDA5255 contains a slicer for VPS and TTX, an accelerating acquisition hardware module, a display generator for “LEVEL 1” TTX data and a 8 bit u-controller running at 333 nsec cycle time.

The controller with dedicated hardware guarantees flexibility, does most of the internal processing of TTX acquisition , transfers data to/from the external memory interface and receives/transmits data via I2C and UART user interfaces.

The Slicer combined with dedicated hardware stores TTX data in a VBI 1Kbyte buffer. The u-controller firmware does the total acquisition task (hammingand parity -checks, page search and evaluation of header control bits) once per field.

(2)Feature

•Acquisition:

-feature selection via special function register

-simultaneous reception of TTX and VPS

-fixed framing code for VPS and TTX

-programmable framing code window for TTX

-Acquisition during VBI

-direct access to VBI RAM buffer

-Acquisition of packets x/26, x/27, 8/30 (firmware)

-assistance of all relevant checks (firmware)

-1-bit framing-code error tolerance (switchable)

•Display:

-features selectable via special function register

-50/60 Hz display

-level 1 serial attribute display pages

-blanking and contrast reduction output

-8 direct addressable display pages

-12 x 10 character matrix

-96 character ROM (standard G0 character set)

-143 national option characters for 11 languages

-288 characters for X/26 display

-64 block mosaic graphic characters

-32 free addressable characters for OSD in expanded character ROM + 32 inside OSD box

-double height (TOP/BOTTOM)

-conceal/reveal

-transparent foreground/background -inside/outside of a box

-cursor (colour changes from foreground to background colour)

-flash (flash rate 1s)

-programmable horizontal und vertical sync delay

-hardware assisted fast display page erase

-full screen background colour in outer screen

•Synchronization:

display synchronization to sandcastle or Horizontal Sync (HS) and Vertical Sync (VS) with startstop-oscillator or display synchronization to sandcastle or Horizontal Sync and Vertical Sync with external clock

independent clock systems for acquisition, display and controller

9

•Controller:

-8 bit configuration

-18 MHz internal clock

-0.33 us instruction cycle

-eight 16-bit data pointer registers (DPTR)

-two 16-bit timers

-watchdog timer

-serial interface (UART)

-256 bytes on-chip RAM

-1 Kbyte on-chip extended RAM (access via MOVX)

-8 Kbyte on-chip ACQ-buffer-RAM (access via MOVX)

-6 channel 8-bit pulse width modulation unit

-2 channel 14-bit pulse width modulation unit

-4 multiplexed ADC inputs with 8-bit resolution

-one 8-bit I/O port with open drain output and optional I2C emulation

-two 8-bit multifunctional I/O ports

-one 4-bit port working as digital or analog inputs

-one 2-bit I/O port with optional address latch enable function

•P-SDIP 52 package

•5 V supply voltage

(3)Block Diagram

10

(4)Pin Description

*A : DW5255M*/DW5255RM*, *B : DW370ASM*

Pin |

|

Name |

|

|

Symbol |

Description |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

A* |

B* |

A* |

B* |

|

A* |

|

|

|

|

B* |

|

|

|

|

|

|

|

||||||

1 |

1 |

P3.1 |

T1IC1/CR |

SYS |

NTSC OUT for switching SAW filter |

||||||

|

|

|

|

|

|

K6259 |

|

|

|

|

|

|

|

|

|

|

|

- PAL/SECAM : L |

|

||||

|

|

|

|

|

|

- NTSC : H |

|

||||

|

|

|

|

|

|

|

|

|

|||

2 |

2 |

P0.7/Open Drain |

A0 |

BUSSTOP |

I2C BUS STOP IN for Computer |

||||||

|

|

|

|

|

|

controlled alignment in Factory |

|||||

|

|

|

|

|

|

( Active Low ) |

|

||||

|

|

|

|

|

|

|

|

|

|||

3 |

3 |

P0.6/Open Drain |

A1 |

SDA |

Serial data IN/OUT for I2C |

||||||

|

|

|

|

|

|

|

|

|

|||

4 |

4 |

P0.5/Open Drain |

A2 |

SCL |

Serial clock IN/OUT for I2C |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

5 |

5 |

P0.4/Open Drain |

A3 |

OPTION |

#5 |

#6 |

Teletext |

|

#6 |

||

|

|

|

|

|

|

|

|

|

|

|

|

6 |

6 |

P0.3/Open Drain |

A4 |

OPTION |

H |

H |

West Teletext |

|

H : STAND-BY |

||

|

|

|

|

|

|

L |

H |

East Teletext |

|

L : POWER ON |

|

|

|

|

|

|

|

H |

L |

Turkish Teletext |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

7 |

7 |

P0.2/Open Drain |

A5 |

OPTION |

Not Used |

|

|||||

|

|

|

|

|

|

|

|

|

|

||

8 |

8 |

P0.1/Open Drain |

PWM1-0/ Open Drain |

OPTION |

Not Used |

|

|||||

|

|

|

|

|

|

|

|

|

|

||

9 |

9 |

P0.0/Open Drain |

PWM1-1/ Open Drain |

LED |

LED drive OUT |

|

|||||

|

|

|

|

|

|

- Stand-by mode : H |

|

||||

|

|

|

|

|

|

- Operating mode : L |

|

||||

|

|

|

|

|

|

|

|

( IR reception : pulse ) |

|||

|

|

|

|

|

|

|

|

|

|

|

|

10 |

10 |

VSS |

|

|

VSS |

ground |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

11 |

11 |

VCC |

|

|

VCC |

Power Supply |

|

||||

|

|

|

|

|

|

|

|

|

|||

12 |

12 |

XTAL1 |

OSCIN |

|

OSCIN |

Input to inverting osc. Amplifier |

|||||

|

|

|

|

|

|

|

|

|

|||

13 |

13 |

XTAL2 |

OSCOUT |

|

OSCOUT |

Output of inverting osc. Amplifier |

|||||

|

|

|

|

|

|

|

|

|

|

||

14 |

14 |

P4.0/ALE |

PWM1-2/Open Drain |

|

|

Not Used |

|

H : I/M, L : B/D |

|||

|

|

|

|

|

|

|

|

|

|||

15 |

15 |

RESET |

RESET/Open Drain |

RST |

RESET IN (ACTIVE LOW) |

||||||

|

|

|

|

|

|

|

|

|

|

||

16 |

16 |

P1.7/14BIT PWM |

PWM2-0 |

|

VT |

TUNING VOLTAGE OUT |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

17 |

17 |

P1.6/14BIT PWM |

PWM2-1 |

|

SW |

H : I/M |

|

|

|

Not Used |

|

|

|

|

|

|

|

L : B/D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

18 |

18 |

P1.5/8BIT PWM |

PWM1-3/Open Drain |

F/SW |

Not Used |

|

|||||

|

|

|

|

|

|

|

|

|

|

||

19 |

19 |

P1.4/8BIT PWM |

PWM1-4/Open Drain |

|

|

Not Used |

|

||||

|

|

|

|

|

|

|

|

|

|

||

20 |

20 |

P1.3/8BIT PWM |

PWM1-5/Open Drain |

MUTE |

AUDIO MUTE OUT |

|

|||||

|

|

|

|

|

|

|

|

|

|||

21 |

21 |

P1.2/8BIT PWM |

TEST |

|

GND |

(Must be tied 0V for DW370M*) |

|||||

|

|

|

|

|

|

|

|

|

|

||

22 |

|

P1.1/8BIT PWM |

|

|

|

Not Used |

|

||||

|

|

|

|

|

|

|

|

|

|

||

23 |

|

P1.0/8BIT PWM |

|

|

|

Not Used |

|

||||

|

|

|

|

|

|

|

|

|

|

||

24 |

|

VSSA |

|

VSSA |

Analog GND for Slicer |

|

|||||

|

|

|

|

|

|

|

|

|

|||

25 |

|

FIL3 |

|

|

FIL3 |

PLL Loop Filter I/O for Phase Shifting |

|||||

|

|

|

|

|

|

|

|

|

|||

26 |

|

FIL2 |

|

|

FIL2 |

PLL Loop Filter I/O for TTX Slicing |

|||||

|

|

|

|

|

|

|

|

|

|||

27 |

|

FIL1 |

|

|

FIL1 |

PLL Loop Filter I/O for VPS Slicing |

|||||

|

|

|

|

|

|

|

|

|

|||

28 |

|

VCCA |

|

VCCA |

Analog Supply for Slicer |

|

|||||

|

|

|

|

|

|

|

|

||||

29 |

|

IREF |

|

IREF |

Reference Current for Slicer PLLs |

||||||

11

Pin |

|

Name |

|

Symbol |

Description |

|

|

|

A* |

B* |

A* |

B* |

A* |

|

B* |

|

|

|

|

|

||||||

30 |

|

CVBS |

|

CVBS |

CVBS IN |

|

|

|

|

|

|

|

|

|

|

|

|

31 |

|

P2.3/8 bit ADC |

|

|

Not Used |

|

|

|

|

|

|

|

|

|

|

|

|

32 |

22 |

P2.2/8 bit ADC |

B0/AN0/ADC |

AGC |

IF AGC INPUT for Auto Tuning System |

|

||

|

|

|

|

|

|

|

|

|

33 |

23 |

P2.1/8 bit ADC |

B1/AN1/ADC |

KS |

Local KEY SCAN IN |

|

|

|

|

|

|

|

|

|

|

|

|

34 |

24 |

P2.0/8 bit ADC |

B2/AN2/ADC |

S/SW |

Not Used |

|

|

|

|

|

|

|

|

|

|

|

|

35 |

25 |

VSS |

VSS-OSD |

VSS |

Ground |

|

|

|

|

|

|

|

|

|

|

|

|

36 |

26 |

P3.3/INT1 |

INT1 |

IR |

REMOTE IR IN |

|

|

|

|

|

|

|

|

|

|

|

|

37 |

27 |

VDD |

VCC-OSD |

VDD |

Power Supply |

|

|

|

|

|

|

|

|

|

|

|

|

38 |

28 |

LCIN |

OSCIN-OSD |

LCIN |

CLOCK IN for OSD |

|

|

|

|

|

|

|

|

|

|

|

|

39 |

29 |

LCOUT |

OSCOUT-OSD |

LCOUT |

CLOCK OUT for OSD |

|

|

|

|

|

|

|

|

|

|

|

|

40 |

30 |

P3.7/TXT I/O |

T2EVT/PWM2 |

BL |

BAND VHF-L OUT ( Active High ) |

|

||

|

|

|

|

|

|

|

|

|

41 |

31 |

P3.6/RXD |

T2IC2/PWM1 |

BH |

BAND VHF-H OUT ( Active High ) |

|

||

|

|

|

|

|

|

|

|

|

42 |

32 |

P3.5/T1 |

T2IC1/CR |

BU |

BAND UHF OUT ( Active High ) |

|

||

|

|

|

|

|

|

|

|

|

43 |

33 |

P3.4/T0 |

T1EVT/PWM2 |

POWER |

POWER CONTROL OUT |

|

|

|

|

|

|

|

|

|

|

|

|

44 |

34 |

P3.2/INT0 |

INT2 |

|

Not Used |

|

|

|

|

|

|

|

|

|

|

|

|

45 |

35 |

HS/SC |

HSYNC |

HSYNC |

HOR. SYNC. IN |

(Active High) |

|

|

|

|

|

|

|

|

|

|

|

46 |

36 |

P4.7/VS |

VSYNC |

VSYNC |

VERT. SYNC. IN |

(Active High) |

|

|

|

|

|

|

|

|

|

|

|

47 |

37 |

R |

|

R |

RED OUT |

|

|

|

|

|

|

|

|

|

|

|

|

48 |

38 |

G |

|

G |

GREEN OUT |

|

|

|

|

|

|

|

|

|

|

|

|

49 |

39 |

B |

|

B |

BLUE OUT |

|

|

|

|

|

|

|

|

|

|

|

|

50 |

40 |

BLANK |

|

BL |

BLANK OUT |

|

|

|

|

|

|

|

|

|

|

|

|

51 |

41 |

COR |

|

COR |

Not Used |

|

|

|

|

|

|

|

|

(CONTRAST REDUCTION OUT) |

|

||

|

|

|

|

|

|

|

|

|

52 |

42 |

P3.0 |

T1C2/PWM1 |

EVEN/ODD |

EVEN/ODD OUT for non-interlacing |

|

||

|

|

|

|

|

in TTX mode |

|

|

|

|

|

|

|

|

|

|

|

|

12

24LC08B (EEPROM)

(1) Features |

|

• Single supply with operation down to 2.5V |

• Page-write buffer for up to 16 bytes |

• Low power CMOS technology |

• 2ms typical write cycle time for page-write |

- 1mA active current typical |

• Hardware write protect for entire memory |

- 10 A standby current typical at 5.5V |

• Can be operated as a serial ROM |

- 5 A standby current typical at 3.0V |

• Factory programming(QTP) available |

• Organized as two or four blocks of 256 bytes |

• ESD protection > 4,000V |

(2x256x8) and (4x256x8) |

• 1,000,000 ERASE/WRITE cycles(typical) |

• Two wire serial interface bus, I2CTM compatible |

• Data retention > 40 years |

• Schmitt trigger, filtered inputs for noise suppression |

• 8-pin DIP, 8-lead or 14-lead SOIC packages |

• Output slope control to eliminate ground bounce |

• Available for extended temperature ranges |

• 100KHz(2.5V) and 400KHz(5V) compatibility |

- Commercial : 0 C to +70 C |

• Self-timed write cycle(including auto-erase) |

-Industrial : -40 C to +85 C |

(2)General Description

The Microchip Technology Inc. 24LC08B is a 8K-bit Electrically Erasable PROM.

The device is organized as four blocks of 256x9bit memory with a two wire serial interface. Low voltage

design permits operation down to 2.5 volts with standby and active currents of only 5 A and 1mA respectively. The 24LC08B also has a page-write capability for up to 16 bytes of data.

A and 1mA respectively. The 24LC08B also has a page-write capability for up to 16 bytes of data.

The 24L08B is available in the standard 8-pin DIP surface mount 80IC packages.

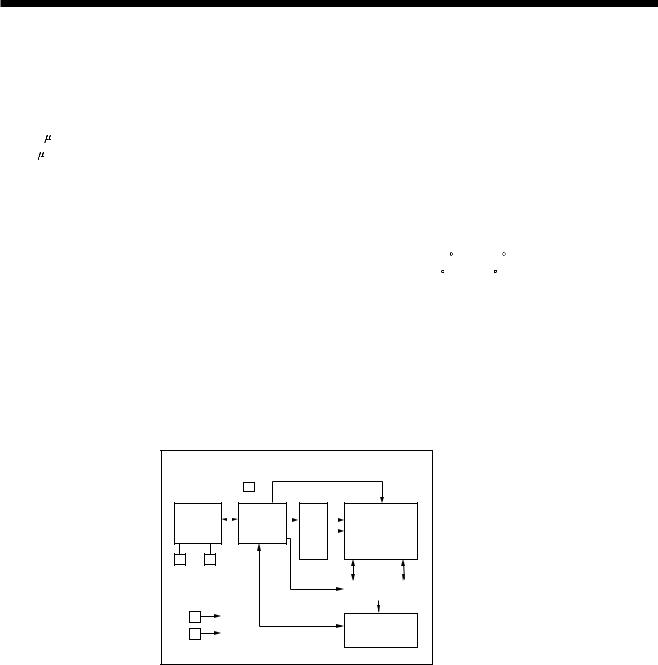

(3)Block Diagram

|

|

|

|

WP |

|

|

|

|

HV GENERATOR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I/O |

|

MEMORY |

|

|

|

|

EEPROM ARRAY |

|||

CONTROL |

|

CONTROL |

|

|

|

|

||||

|

|

XDEC |

|

|

(4X256X8) |

|||||

LOGIC |

|

|

LOGIC |

|

|

|

||||

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

PAGE LATCHES |

|

|

|

|

|

|

|

|

|

|

|

SDA SCL |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

YDEC |

|

|

|

|

|

|

|

|

|

|

|

VCC

V SENSE AMP

SS

R/W CONTROL

(4) Pin Description

PIN |

SYMBOL |

DESCRIPTION |

1-3 |

A0, A1, A2 |

Device Address lnputs |

|

|

|

4 |

Vss |

Ground |

|

|

|

5 |

SDA |

Serial Data/Address |

|

|

|

6 |

SCL |

Serial Clock |

|

|

|

7 |

WP |

|

|

|

|

8 |

Vcc |

+5V Power supply |

|

|

|

13

TDA8374A (Single chip TV Processor for Negative modulation IF ) TDA8374 (Single chip TV Processor for Negative & positive modulation IF)

(1)General Description

The TDA8374(A) is I2C-bus controlled single chip TV processors which are intended to be applied in PAL/NTSC television receiver.

The IC is mounted in a S-DIL 56 envelope.

(2)Feature

•IF

-Vision IF amplifier with high sensitivity and good figures for differential phase and gain

-PLL demodulator with high linearity offering the possibility for (single standard) intercarrier stereo audio application .

-Alignment PLL via I2C

-[TDA8374] Multistandard IF with negative and positive modulation, switchable via I2C

•AUDIO

-Alignment free multi standard PLL audio demodulator (4.5 to 6.5 MHz.)

-Mono volume control

•Video

-Integrated luminance delay line

-Integrated chroma trap and bandpass filters (auto calibrated)

-Asymmetrical peaking circuit in the luminance channel

-Black stretching of non standard CVBS or luminance signals

•Colour

-SECAM interface for application with SECAM add-on TDA8395.

•RGB

-RGB control (brightness, contrast, saturation)

-Black current stabilization and white point adjustment

•Input / Output

-Flexible video source select with CVBS input for the internal signal and two external video inputs(one switchable for CVBS or Y/C).

-The output signal of the video source select is externally available ( also as CVBS when Y/C input is used).

-External audio input.

-Linear RGB input with fast blanking.

•Synchronization and Deflection

-Horizontal synchronization with two control loops and alignment free horizontal oscillator.

-Slow start and slow stop of the horizontal drive output to enable low stress start-up and switch-off from the line circuit at nominal line supply voltage.

-Vertical count-down circuit for stable behavior with provisions for non-standard signals.

-Vertical geometry control.

-Vertical drive optimized for DC coupled vertical output stages.

•Control

-Full I2C bus control, as well for customer controls as for factory alignment.

-All automatic controls have an option for forced mode.

•Power consumption

-Low power consumption (900 mW at 8.0 Volts).

•Packaging

-SDIL-56 (Shrinked Dual In Line, 56 pins).

14

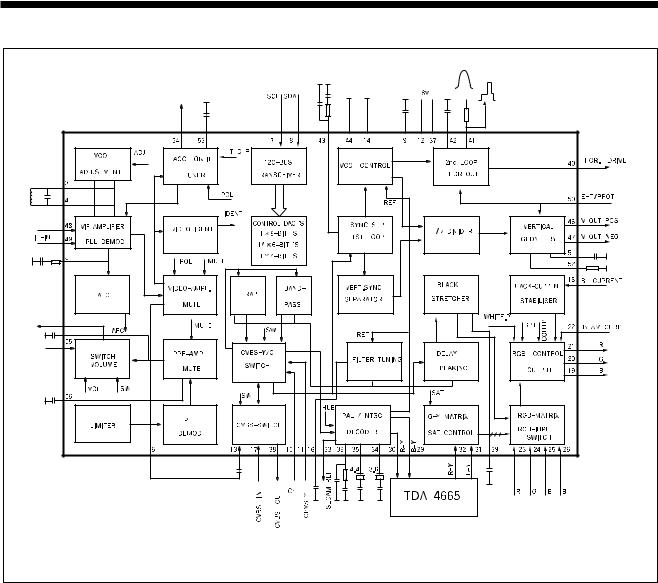

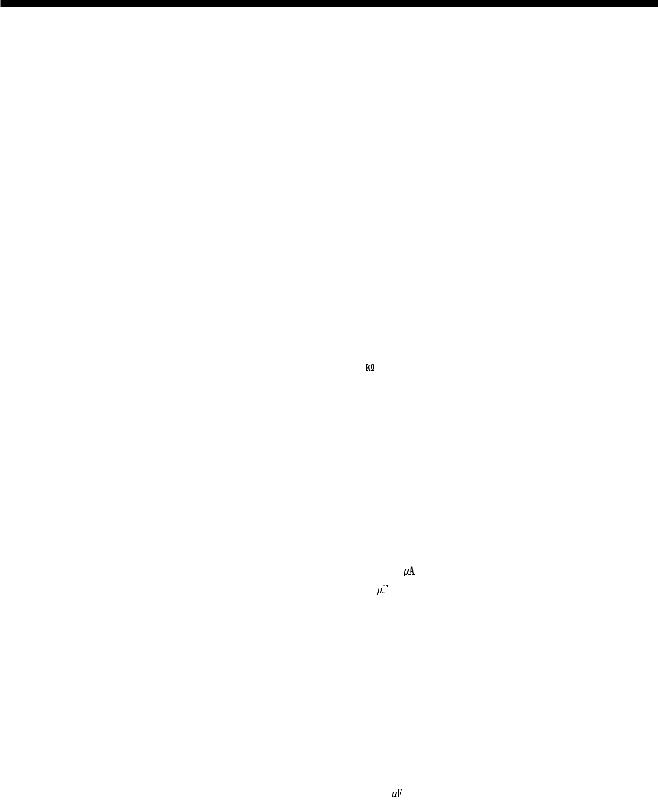

(3) Block Diagram

15

(4) Pin Description

No |

Name |

Description |

|

|

|

1 |

SOUND IF INPUT |

The sound equivalent input impedance is 8k5 ohm // 5pF which has to be |

|

|

taken into account for proper termination of the ceramic filters. |

|

|

The DC impedance is very high. |

|

|

The minimum input signal for catching is l mV rms. |

|

|

|

2 |

EXT AUDIO INPUT |

An external sound signal (500mVrms) for example from SCART can be |

|

|

applied to this pin via a coupling capacitor. |

|

|

The input impedance is 25kohm. |

|

|

|

3 |

VCO REF FILTER |

The IF VCO tuned circuit is applied to these pin. |

4 |

|

Its resonance frequency must be two times the IF-frequency and in between a |

|

|

range of 64-120MHz. |

|

|

This range is suitable for the IF standards as 33.4, 38.9, 45.75 and 58.75MHz. |

|

|

The VCO frequency can be adjusted by I2C bus so a fixed coil can be used. |

|

|

|

5 |

PLL LOOP FILTER |

The PLL loopfilter is a first order filter with R=390 ohm and C = 100nF in |

|

|

series to ground. |

|

|

The loopfilter bandwidth is 60kHz and is optimal for both fast catching and |

|

|

sufficient video suppression for optimal sound performance. |

|

|

Sound performance can theoretically be improved by adding a small |

|

|

capacitor (approx.0- 4.7nF) between pin 5 and ground. |

|

|

This however must be evaluated further because the normal video signal |

|

|

response should not be effected. |

|

|

|

6 |

IF VIDEO OUTPUT |

Although the video output impedance is low it is recommended to avoid |

|

|

high frequency current in the output due to for instance sound trap filters. |

|

|

This can be achieved by means of an emitter follower at the video output with |

|

|

a 1 resistor in series with the base. |

|

|

|

7 |

BUS INPUT : SCL |

Serial clock line |

|

|

|

8 |

BUS INPUT : SDA |

Serial data line |

|

|

|

9 |

BANDGAP |

The bandgap circuit provides a very stable and temperature independent |

|

DECOUPLING |

reference voltage. |

|

|

This reference voltage (6.7V) ensures optimal performance of the TDA8374 |

|

|

and is used in almost all functional circuit blocks. |

|

|

|

10 |

CHROMA INPUT |

The supplied C S-VHS input burst amplitude should be nominally 300mVpp |

|

|

(assumed is a colour bar signal with 75% saturation and with chroma/burst |

|

|

ratio of 2.2/1 ). The C S-VHS input is internally clamped to 4V via 50 . |

|

|

The external AC coupling capacitor with 50 forms a high pass filter. |

|

|

A recommended coupling capacitor is 1 nF; the high pass filter cut off |

|

|

frequency is then approximately 3KHz. |

|

|

|

11 |

Y/CVBS INPUT |

The Y S-VHS signal of 1Vpp ( inclusive sync amplitude) is AC coupled to pin11. |

|

|

|

12 |

MAIN |

The TDA8374 has a main supply pin 12 and a horizontal supply pin 37. Both |

37 |

POSITIVE SUPPLY |

pins have to be supplied simultaneously. |

|

|

Notice that the IC has not been designed to use this pin 37 as start pin. |

|

|

(pin 37 supplies the horizontal oscillator, PHI-1 and PHl-2) |

|

|

(pin 12 supplies the rest of the circuits in the IC) |

|

|

The nominal supply voltage is 8V. With min/max values of 7.2-8.8V. |

|

|

Also in stand-by condition the IC must be supplied with 8V. |

|

|

|

16

No |

Name |

Description |

|

|

|

|

A voltage detection circuit is connected to both pins. |

||

|

|

- pin12 if V12 <6.8V than a power on reset, POR, is generated. The Hout |

||

|

|

output is disabled immediate. |

||

|

|

- pin37 if V37 <5.8V than the horizontal output is disabled immediate. |

||

|

|

|

||

13 |

INT CVBS INPUT |

It is recommended that the CVBS1 int and CVBS2 ext input amplitudes are |

||

17 |

EXT CVBS INPUT |

1 Vpp (inclusive sync amplitude). |

||

|

|

This, because the noise detector switches the 1 loop to slow mode |

||

|

|

(i.e. auto |

1mode when FOA, FOB = 0,0) when noise level exceeds |

|

|

|

100mVrms (i.e. at S/N of 20dB). |

||

|

|

|

||

14 |

GROUND |

All internal circuits are connected to this ground pin 14. |

||

|

|

|

||

15 |

AUDIO OUTPUT |

The output signal is volume controlled and is active for both internal and |

||

|

|

external audio signals. The nominal gain is +9dB and -71dB, which gives |

||

|

|

a total control range of 80dB. |

||

|

|

The output signal range therefor is 0.141400mVrms |

||

|

|

The bandwidth is >100kHz, the DC level is 3.3V and the output impedance |

||

|

|

is 250 . |

|

|

|

|

|

||

16 |

DECOUPLING |

Voltage variations at pin 16, which can be due to external leakage current or |

||

|

FILTER TUNING |

crosstalk from interference sources, should be less than 50mV to ensure that |

||

|

|

tuning of filters/delay cells remains correct. |

||

|

|

|

||

18 |

BLACK CURRENT |

For correct operation of the loop CURRENT information is supplied to the |

||

|

INPUT |

black current input pin. |

|

|

|

|

|

||

19 |

BLUE OUTPUT |

The RGB outputs are supplied to the video output stages from pins 21, 20 |

||

20 |

GREEN OUTPUT |

and 19 respectively. |

|

|

21 |

RED OUTPUT |

For nominal signals (i.e. CVBS/S-VHS, -(R-Y)/- (R-Y), TXT inputs) and for |

||

|

|

nominal control settings, then the RGB output Signal amplitudes is |

||

|

|

typically 2VBLACK_WHITE. |

|

|

|

|

|

|

|

22 |

V-GUARD INPUT/ |

Vertical Guard |

|

|

|

BEAM CURRENT |

With this function, the correct working of the vertical deflection can be |

||

|

LIMITER |

monitored. If the vertical deflection fails, the RGB outputs are blanked to |

||

|

|

prevent damage to the picture tube. |

||

|

|

Beam current limitinq |

|

|

|

|

The beam current limiting function is realised by reducing the contrast (and |

||

|

|

finally the brightness) when the beam current reaches s too high level. The |

||

|

|

circuit falls apart in two functions: |

||

|

|

- Average beam current limiting (ABL): reacting on the average content of |

||

|

|

the picture |

|

|

|

|

- Peak white limiting (PWL): reacting on high local peaks in the RGB signal. |

||

|

|

|

||

23 |

RED INPUT |

The Rin, Gin, Bin input signals (nominal signal amplitude of 700mV) are |

||

24 |

GREEN INPUT |

AC coupled to pin 23, 24 and 25 respectively. |

||

25 |

BLUE INPUT |

Clamping action occurs during burstkey period. |

||

|

|

|

||

26 |

RGB INSERTION |

The table below a survey is given of the three modes which can be selected |

||

|

SWITCH INPUT |

with a voltage on RGB insertion switch input pin ; |

||

|

|

Vpin26 |

I2C function |

Selected RGB signal |

|

|

0.9V-3V |

IE1=0 |

RGB(internal) |

|

|

|

IE1=1 |

Rin,Gin,Bin |

|

|

|

|

(fast insertion on pin23,24,25) |

|

|

> 4V |

IE1=X |

OSD can be inserted at the RGBout pins |

|

|

|

||

27 |

LUMINANCE INPUT |

An nominal input signal amplitude of 1 Vblack-white MUST be DC coupled |

||

|

|

|

|

|

|

|

|

|

|

17

|

No |

Name |

Description |

|

|

|

to the luminance input pin 27. |

|

|

|

The pin is internally AC coupled to the luminance clamp via a capacitor of |

|

|

|

50pF; clamping action occurs during burstkey period. |

|

|

|

|

|

28 |

LUMINANCE |

The luminance output signal is approximately l V black-white with typical |

|

|

OUTPUT |

output impedance of 25O ohm. |

|

|

|

|

29 |

B-Y OUTPUT |

The maximum output impedance of pins 29 and 30 is 500 when PAL/NTSC |

|

30 |

R-Y OUTPUT |

signals are identified. When SECAM is identified by the SECAM add-on and |

|

|

|

|

no PAL/NTSC is already identified by the ASM, then the ASM sets the |

|

|

|

-(B-Y)/-(R-Y) output switch open (via DEMSW). |

|

|

|

This enables the -(B-Y)/-(R-Y) outputs of the TDA8395 to be directly connected |

|

|

|

to pins 29 and 3O respectively. |

|

|

|

|

|

31 |

B-Y INPUT |

The -(B-Y),-(R-Y) output signals (supplied from baseband delay line) are AC |

32 |

R-Y INPUT |

coupled, via a coupling capacitor of 10nF or greater, to the -(B-Y)/-(R-Y) inputs; |

|

|

|

|

both inputs are clamped during burstkey period. |

|

|

|

|

|

33 |

SECAM REF |

The SECAM reference output is directly connected to pin l of the TDA8395 for |

|

|

OUTPUT |

SECAM decoding ; it also can be used as a reference for comb filter applications. |

|

|

|

|

|

34 |

X-TAL 3.58 |

To ensure correct operation of both: |

35 |

X-TAL 4.43 |

- colour processing internal circuits, |

|

|

|

|

- sync calibration internal circuits, |

|

|

|

it is only allowed to have 3.6MHz Xtals on pin34: both 4.4MHz,3.6MHz Xtals |

|

|

|

are allowed on pin 35. |

|

|

|

If pin 35 is not used: then it is left open in application (also XA,XB=O,1 ). |

|

|

|

|

|

36 |

LOOP FILTER |

One of the important aspects of the PLL is the 1oop filter connected to pin 36; |

|

|

BURST PHASE |

it influences the dynamic performance of the loop. |

|

|

DETECTOR |

|

|

|

|

|

|

38 |

CVBS OUTPUT |

The output amplitude is 1Vpp (transfer gain ratio between CVBS1int or |

|

|

|

CVBS2ext or CVBS3ext/Ys-vhs and CVBSout is 1). |

|

|

|

The maximum output impedance is 250 ohm. |

|

|

|

|

|

39 |

BLACK PEAK |

For the correct working of the black stretcher an external time constant should |

|

|

HOLD CAPACITOR |

be added at the black peak hold capacitor input. |

|

|

|

|

|

40 |

HOR OUTPUT |

This open collector output is meant to drive the horizontal output stage. |

|

|

|

The output is active low, i.e. the line transistor should conduct during the low |

|

|

|

period of the output. |

|

|

|

|

|

41 |

SANDCASTLE |

Pin 41 is a combined input/output pin. |

|

|

OUTPUT/ |

The pin provides a three level sandcastle pulse. |

|

|

FLYBACK INPUT |

Both burstkey pulse and vertical blanking pulse are always available, the line |

|

|

|

blanking pulse is only present when the external flyback pulse is fed to this pin. |

|

|

|

The line flyback pulse, fed to this pin is used for two functions: |

|

|

|

- input signal for the PHI-2 1oop and |

|

|

|

- RGB line blanking. (without flyback pulse blanking occurs only during the |

|

|

|

burstkey pulse) |

|

|

|

To ensure correct working of the delay line and SECAM add-on, the output |

|

|

|

should not be loaded with more than: |

|

|

|

- Sandcastle input delay line TDA 4665 |

|

|

|

- Sandcastle input SECAM add-on TDA 8395 |

|

|

|

|

|

42 |

PHI-2 FILTER / |

The loopfilter is a first order filter. |

|

|

FLASH PROTECT |

This pin requires a capacitor (C) only. |

|

|

|

|

18

No |

Name |

Description |

|

|

|

A flash protection becomes active when this pin is forced >6V. The horizontal |

|

|

|

drive is switched-off immediately. |

|

|

|

Once the voltage is <6V the horizontal drive is switched-on again via the slow |

|

|

|

start procedure. |

|

|

|

|

|

43 |

PHI-1 FILTER |

The loopfilter connected to pin 43 is suitable for various signal conditions as |

|

|

|

strong/weak and VCR signal. |

|

|

|

This is achieved by switching of the loopfilter time constant by changing the |

|

|

|

PHI-1 output current. |

|

|

|

Via I2C bus FOA/B, different time constants can be chosen, including an |

|

|

|

automatic mode which gives optimal performance under varying conditions. |

|

|

|

|

|

44 |

GROUND |

To this pin are connected the IC-substrate and horizontal output. |

|

|

|

|

|

45 |

EAST-WEST DRIVE |

not used |

|

|

|

|

|

46 |

VERT DRIVE + |

The vertical drive has a current output. The output is balanced which ensures |

|

47 |

VERT DRIVE - |

a good common mode behavior with temperature and makes the output signal |

|

|

|

less sensitive for disturbances. |

|

|

|

|

|

48 |

IF INPUT |

The PLL frequency range is 32-60MHz with corresponding VCO frequency |

|

49 |

|

64-120MHz. |

|

|

|

The IF input impedances is 2 in parallel with 3pF and matches the required |

|

|

|

load for commonly used SAW filters. |

|

|

|

A DC coupling is allowed, so no series capacitors between SAW filter and IF |

|

|

|

input are necessary. |

|

|

|

|

|

50 |

EHT/OVERVOLTAGE |

not used |

|

|

PROTECT INPUT |

|

|

|

|

|

|

51 |

VERT |

This pin requires a capacitor to ground of l00nF +, - 5%. |

|

|

SAWTOOTH |

The optimal sawtooth amplitude is 3.5V and is determined by the external |

|

|

CAPACITOR |

capacitor and charge current. |

|

|

|

The sawtooth bottom-level is 2V. |

|

|

|

|

|

52 |

REFERENCE |

This pin requires a resistor to ground. |

|

|

CURRENT INPUT |

The optimal reference current is 100 |

. which is determined by this resistor. |

|

|

|

|

53 |

AGC |

The AGC capacitor value is 2.2 and has been defined for an optimal |

|

|

DECOUPLING |

compromise between AGC speed and tilt for all AGC modes |

|

|

CAPACITOR |

(negative/positive modulation). |

|

|

|

|

|

54 |

TUNER AGC |

This output is used to control (reduce) the tuner gain for strong RF signals. |

|

|

OUTPUT |

The tuner AGC is an open collector output which is acting as a variable |

|

|

|

current source to ground. |

|

|

|

|

|

55 |

AUDIO |

Only a capacitor has to be connected to this pin that defines the deemphasis |

|

|

DEEMPHASSIS |

time constant. |

|

|

|

The signal is internally connected through to the Audio switch. |

|

|

|

The deemphasis output is fixed, thus not controlled by the volume, and can be |

|

|

|

used for SCART. |

|

|

|

|

|

56 |

DECOUPLING |

This pin requires a capacitor of 10 |

connected to ground. |

|

SOUND |

The pin acts as a low pass filter needed for the DC feedback loop. |

|

|

DEMODULATOR |

|

|

|

|

|

|

19

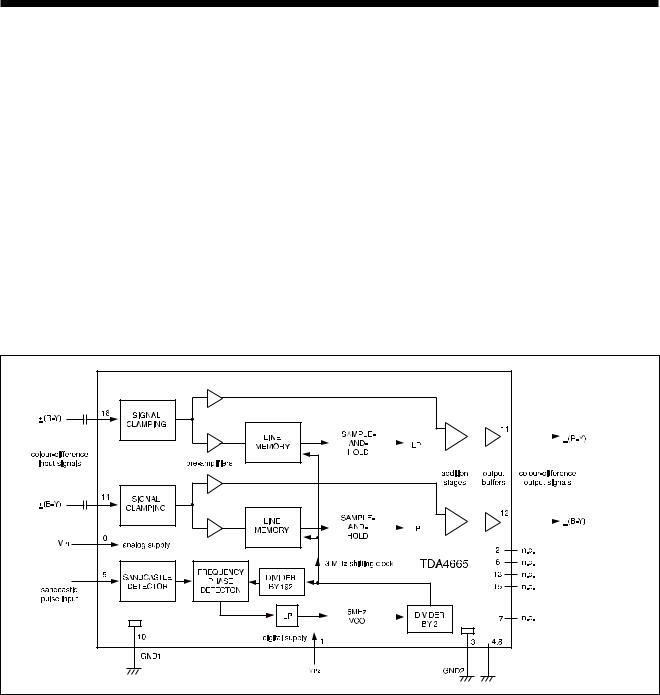

TDA4665(Base Band Delay Line)

(1)Features

•Two comb filters, using the switched-capacitor technique,for one line delay time (64µs)

•Adjustment free application

•No crosstalk between SECAM colour carriers

•Handles negative or positive colour-difference input signals

•Clamping of AC-coupled input signals(±(R-Y)and±(B-Y))

•VCO without external components

•3MHz internal clock signal derived from a 6MHz VCO, line-locked by the sandcastle pulse (64µs line)

•Sample-and -hold circuits and low-pass filters to suppress the 3 MHz clock signal

•Addition of delayed and non-delayed output signals

•Output buffer amplifiers

•Comb filtering functions for NTSC colour-difference signals to suppress cross-colour

(2)General Description

The TDA4661 is an integrated baseband delay line circuit with one line delay. It is suitable for decoders with colour-difference signal outputs±(R-Y)and±(B-Y).

(3)Block Diagram

(4) Pin Description

SYMBOL |

PIN |

DESCRIPTION |

Vp2 |

1 |

+5V supply voltage for digital part |

n.c. |

2 |

not connected |

GND2 |

3 |

ground for digital part (0V) |

i.c. |

4 |

internally connected |

SAND |

5 |

sandcastle pulse input |

n.c. |

6 |

not connected |

i.c. |

7 |

internally connected |

i.c. |

8 |

internally connected |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SYMBOL |

|

PIN |

|

|

|

|

DESCRIPTION |

|||||||

|

Vp1 |

|

9 |

|

|

+5V supply voltage for analog part |

|||||||||

|

GND1 |

|

10 |

|

ground for analog part (0V) |

||||||||||

|

V0 (R-Y) |

|

11 |

|

± (R-Y) output signal |

||||||||||

|

V0 (B-Y) |

|

12 |

|

± (B-Y) output signal |

||||||||||

|

n.c. |

|

13 |

|

not connected |

||||||||||

|

V1 (B-Y) |

|

14 |

|

± (B-Y) input signal |

||||||||||

|

n.c. |

|

15 |

|

not connected |

||||||||||

|

V1 (R-Y) |

|

16 |

|

± (R-Y) input signal |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

20

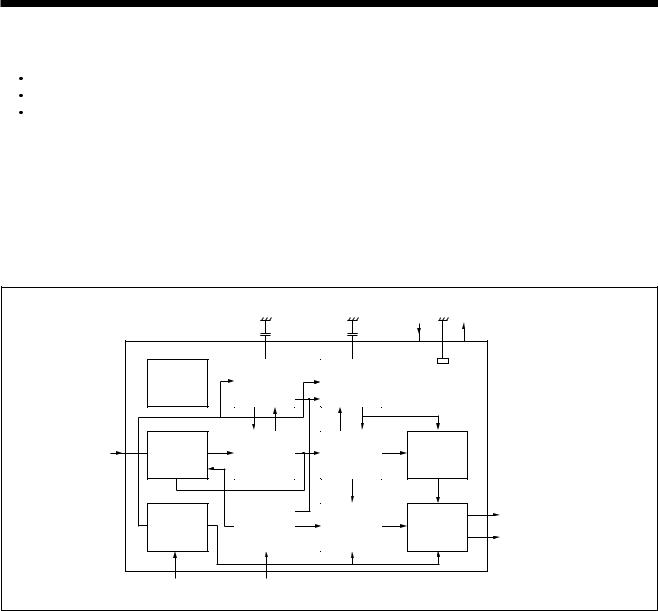

TDA8395 (Secam Decoder)

(1) Features

Fully integrated filters Alignment free

For use with baseband delay

(2)Description

The TDA8395 is a self-calibrating,fully integrated SECAM decoder. The IC should preferably be used in conjunction with the PAL/NTSC decoder TDA8362 and with the switch capacitor baseband delay circuit TDA4665. The IC incorporates HF and LF filters, a demodulator and an identification circuit (Iuminance is not processed in this IC).

A highly stable reference frequency is required for calibration and a two-level sandcastle pulse for blanking and burst gating.

(3)Block Diagram

|

|

CLOCHEref |

PLLref |

|

GND |

|

|

|

|

|

|

Vp |

TEST |

|

|

|

|

100 nF |

220 nF |

|

|

|

|

|

|

7 |

8 |

3 |

6 |

2 |

|

|

BANDGAP |

TUNING |

TUNING |

TDA8395 |

|

||

|

|

|

|

|

|||

CVBS |

16 |

CLOCHE |

|

|

DE- |

|

|

|

ACC |

PLL |

|

|

|

||

|

FILTER |

EMPHASIS |

|

|

|||

|

|

|

|

|

|||

|

|

|

|

|

|

9 |

–(R-Y) |

|

|

|

|

|

|

|

|

|

INTERFACE |

CONTROL |

IDENT- |

|

OUTPUT |

|

|

|

IFICATION |

|

STAGE |

10 |

|

||

|

|

|

|

|

|||

|

|

|

|

|

|

|

–(B-Y) |

|

1 |

15 |

|

|

|

|

|

fref/IDENT SAND

(4) Pin Description

SYMBOL |

PIN |

DESCRIPTION |

fp1/IDENT |

1 |

reference frequency input/identification input |

TEST |

2 |

test output |

Vp |

3 |

positive supply voltage |

n.c. |

4 |

not connected |

n.c. |

5 |

not connected |

GND |

6 |

ground |

CLOCHEref |

7 |

Cloche reference filter |

PLL ref |

8 |

PLL reference |

-(R-Y) |

9 |

-(R-Y) output |

-(B-Y) |

10 |

-(B-Y) output |

n.c. |

11 |

not connected |

n.c. |

12 |

not connected |

n.c. |

13 |

not connected |

n.c. |

14 |

not connected |

SAND |

15 |

sandcastle pulse input |

CVBS |

16 |

video (chrominance) input |

|

|

|

21

TDA6106Q ( Video Output Amplifier )

(1)General Description

The TDA6106Q is a monolithic video output amplifier (5MHz bandwidth) in a SIL 9 MPpackage, using high-voltage DMOS technology, and is intended to drive the cathode of CRT directly .

To obtain maximum performance, the amplifier should be used with black-current control.

(2)Feature

•Black - current measurement output for automatic black current stabilization (ABS)

•Single supply voltage of 200V

•Internal protection against positive appearing CRT flash-over discharge

•Protection against ESD

•Internal 2.5V reference circuit

•Controllable switch-off behavior

(3)Block Diagram

– |

(4) Pin Description

PIN |

SYMBOL |

DESCRIPTION |

1 |

|

N.C |

|

|

|

2 |

|

N.C |

|

|

|

3 |

V in |

inverting input |

|

|

|

4 |

GND |

ground, substrate |

|

|

|

5 |

I om |

Black-current measurement output |

|

|

|

6 |

V dd |

supply voltage high |

|

|

|

7 |

|

N.C |

|

|

|

8 |

V oc |

cathode output |

|

|

|

9 |

V of |

feedback/transient output |

|

|

|

22

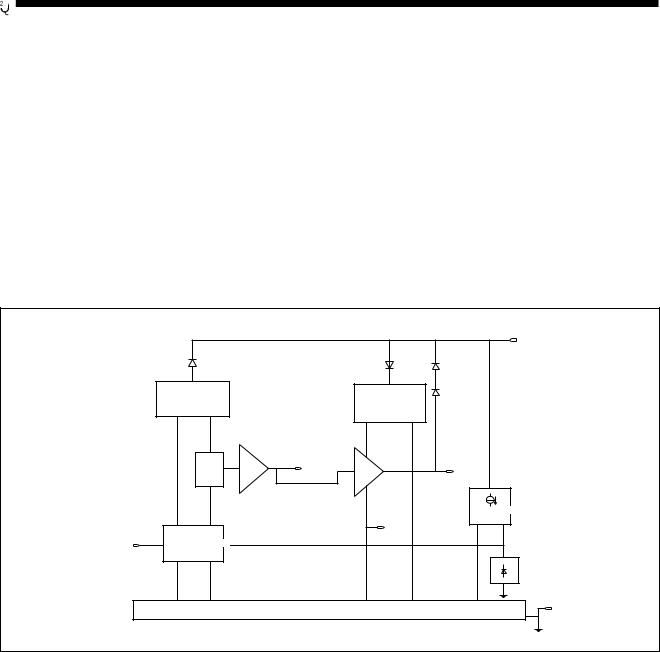

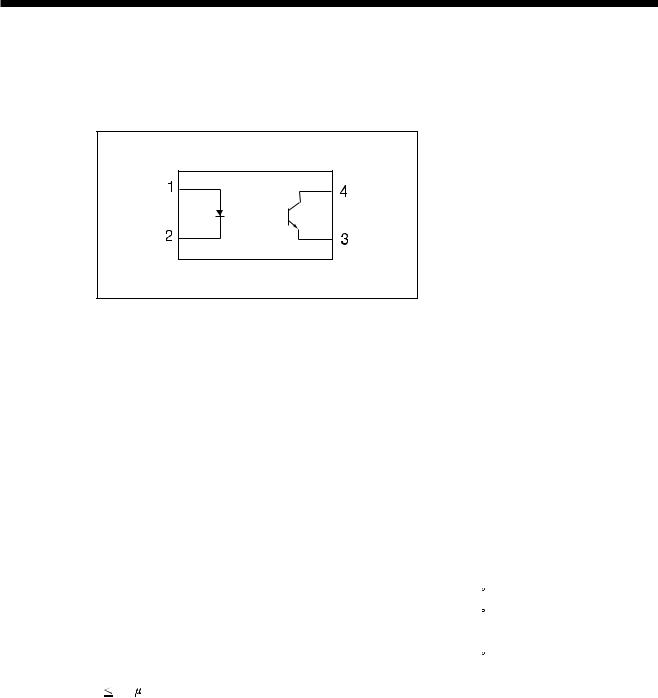

I802 PC817

(1)General Description

The specification applies to the structures and characteristics of Model No. PC817

(2)Block Diagram

(3) Absolute maximum ratings

|

|

Parameter |

Symbol |

Rating |

Unit |

|

|

|

|

|

|

|

|

Forward current |

IF |

50 |

mA |

|

|

|

|

|

|

|

|

*1) Peak forward current |

IFM |

1 |

A |

|

|

|

|

|

|

Input |

|

Reverse voltage |

VR |

6 |

V |

|

|

|

|

|

|

|

|

Power dissipation |

P |

70 |

mW |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Collector-emitter voltage |

VCEO |

35 |

V |

|

|

|

|

|

|

Output |

|

Emitter-collector voltage |

VECO |

6 |

V |

|

|

|

|

|

|

|

|

Collector current |

IC |

50 |

mA |

|

|

|

|

|

|

|

|

Collector power dissipation |

Pc |

150 |

mW |

|

|

|

|

|

|

Total Power dissipation |

Ptot |

200 |

mW |

||

|

|

|

|

|

|

Operating temperature |

Topr |

-30~+100 |

C |

||

|

|

|

|

|

|

Storage temperature |

Tstg |

-55~+125 |

C |

||

|

|

|

|

|

|

*2) Isolation voltage |

Viso |

5 |

kVrms |

||

|

|

|

|

|

|

*3) Soldering temperature |

Tsol |

260 |

C |

||

|

|

|

|

|

|

*1) Pulse width |

100 s, duty ratio: 0.001 |

|

|

|

|

*2) AC for 1 minute, 40~60% RH

*3) For 10 seconds.

23

Loading...

Loading...