Page 1

A

B

C

D

E

Compal Confidential

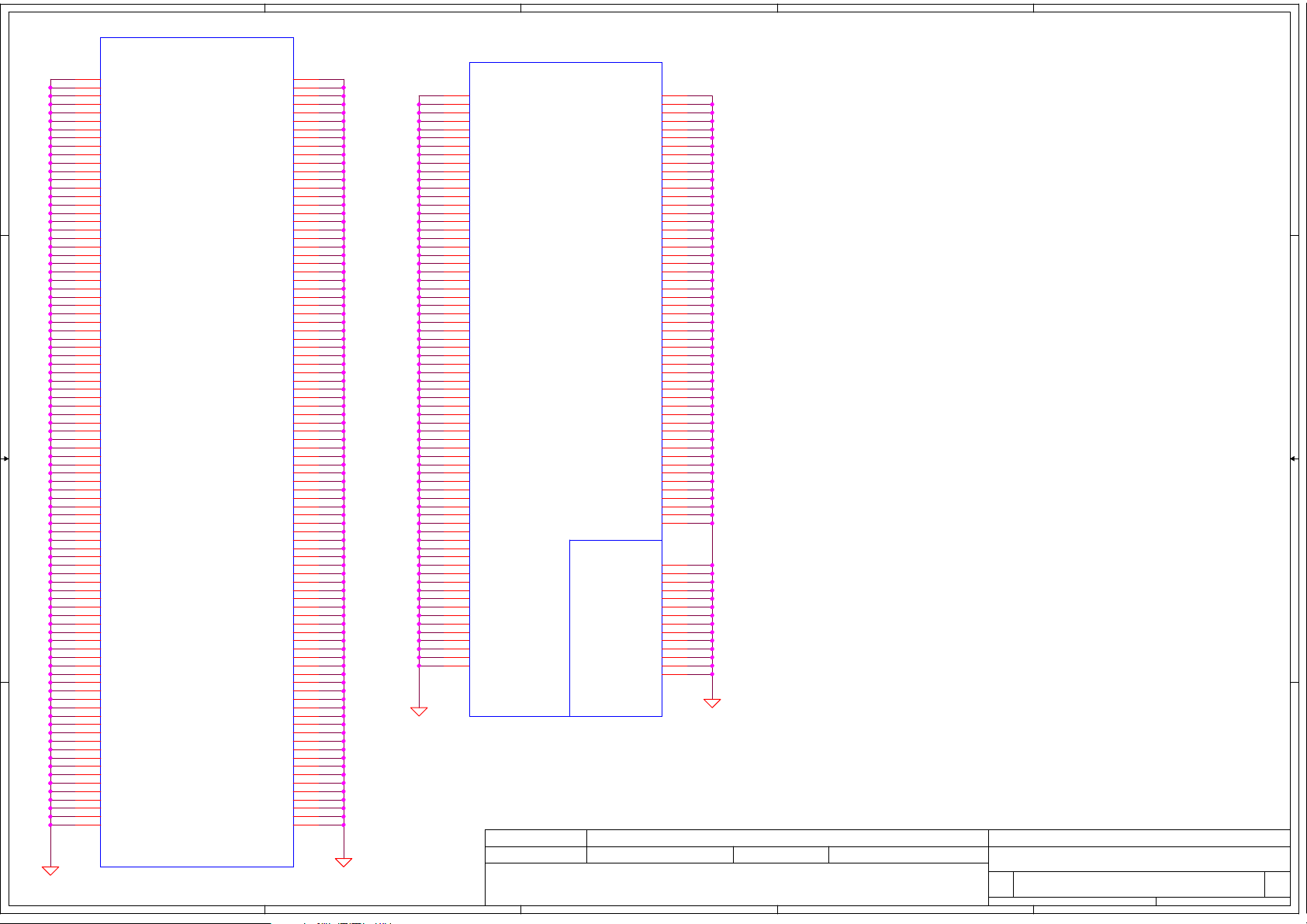

ZZZ5

Model Name : Q1VZC

1 1

File Name :LA-8941P

BOM P/N:43

PCB

DAZ@

ZZZ1

LA-8941P

DA2@

ZZZ2

LS-8941P

DA2@

ZZZ3

LS-8942P

DA2@

ZZZ4

LS-8943P

DA2@

Compal Confidential

2 2

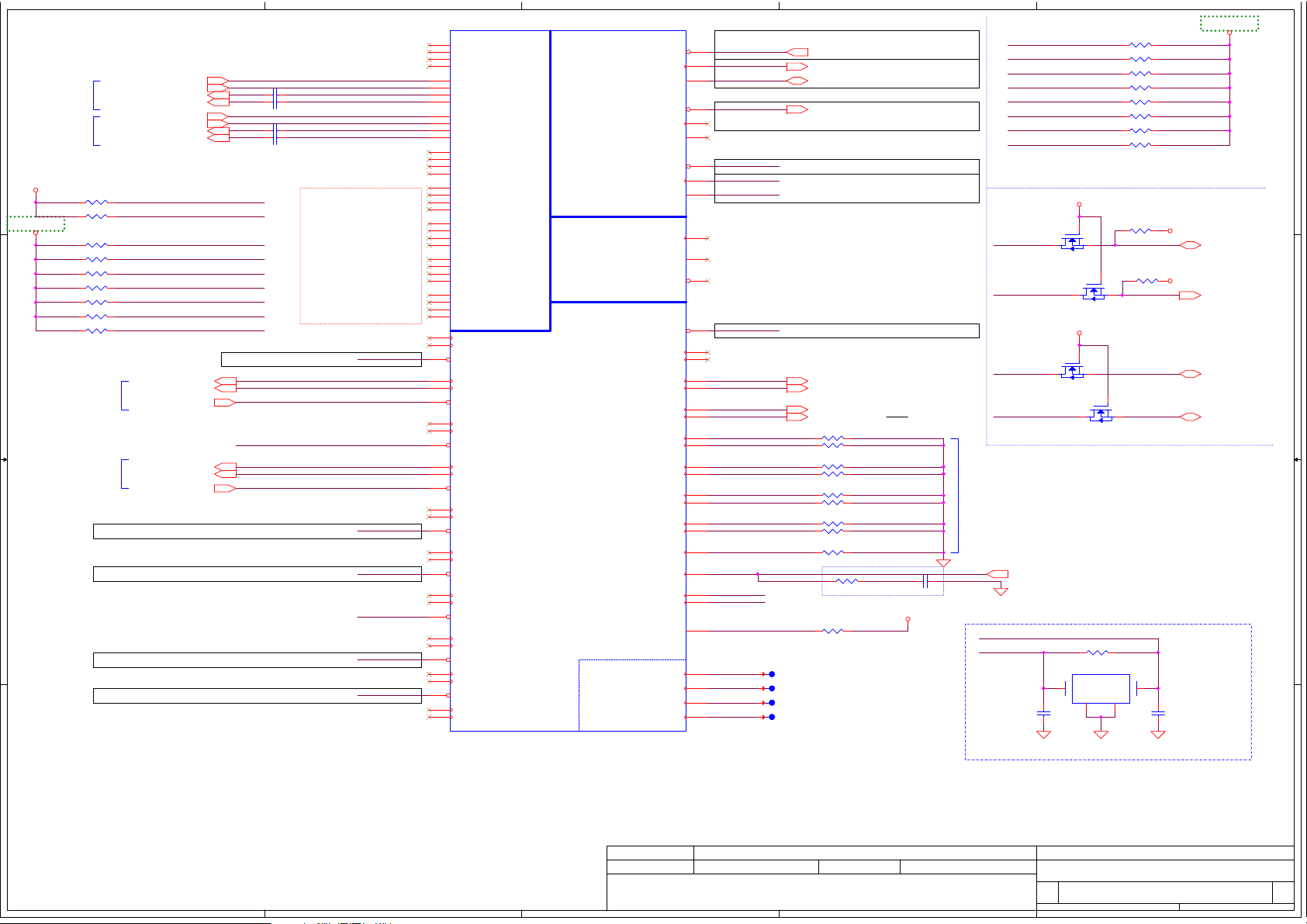

Q1VZC M/B Schematics Document

Intel Sandy Bridge ULV Processor + Panther Point PCH

3 3

2012-04-19

REV:1.0

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

C

2011/11/22 2012/11/22

2011/11/22 2012/11/22

2011/11/22 2012/11/22

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

Q1VZC M/B LA-8941P Schematic

Q1VZC M/B LA-8941P Schematic

Q1VZC M/B LA-8941P Schematic

E

1 45Friday, April 20, 2012

1 45Friday, April 20, 2012

1 45Friday, April 20, 2012

1.0

1.0

1.0

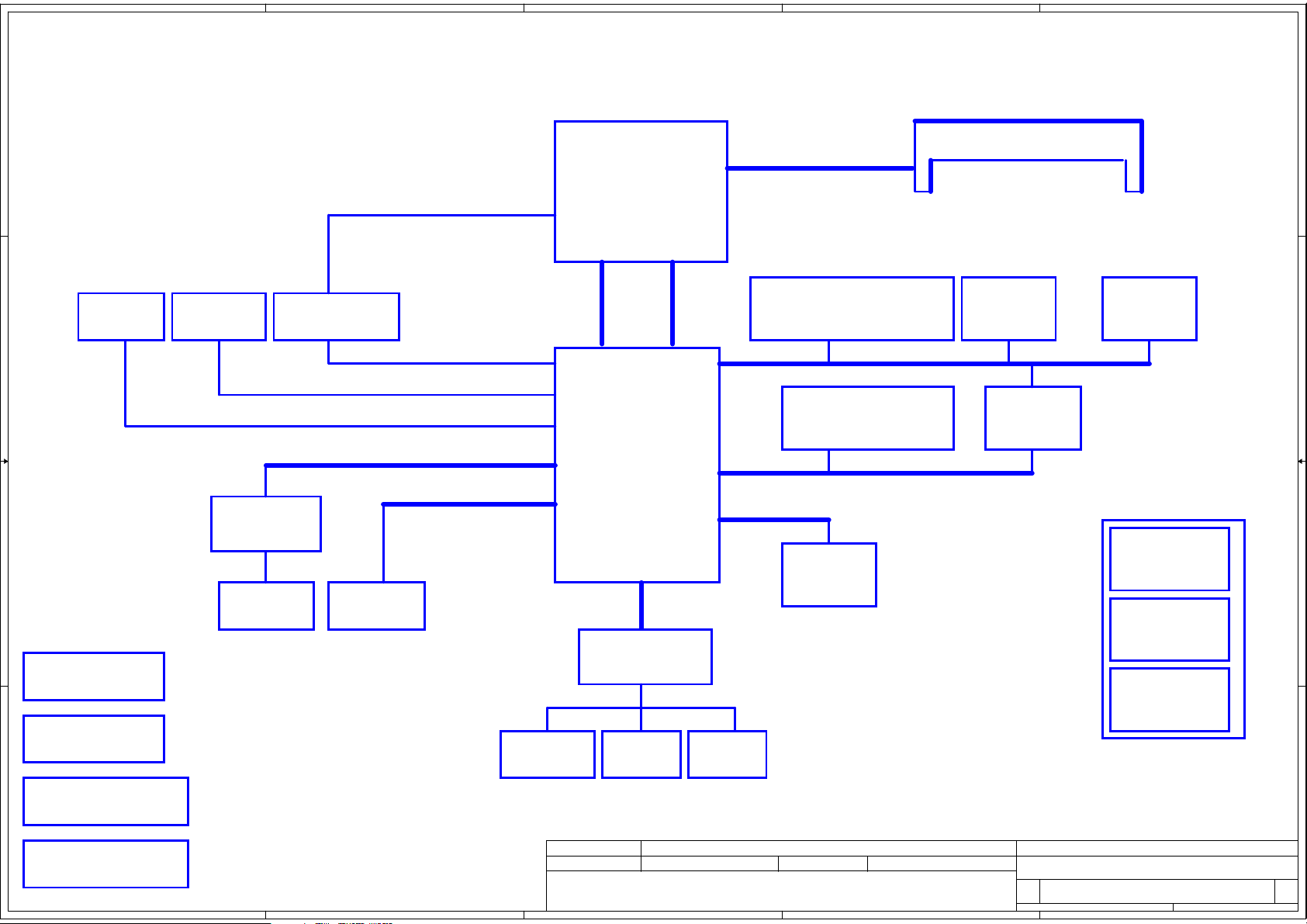

Page 2

A

B

C

D

E

Compal Confidential

Model Name : Q1VZC

e Name :LA-8941P

Fil

1 1

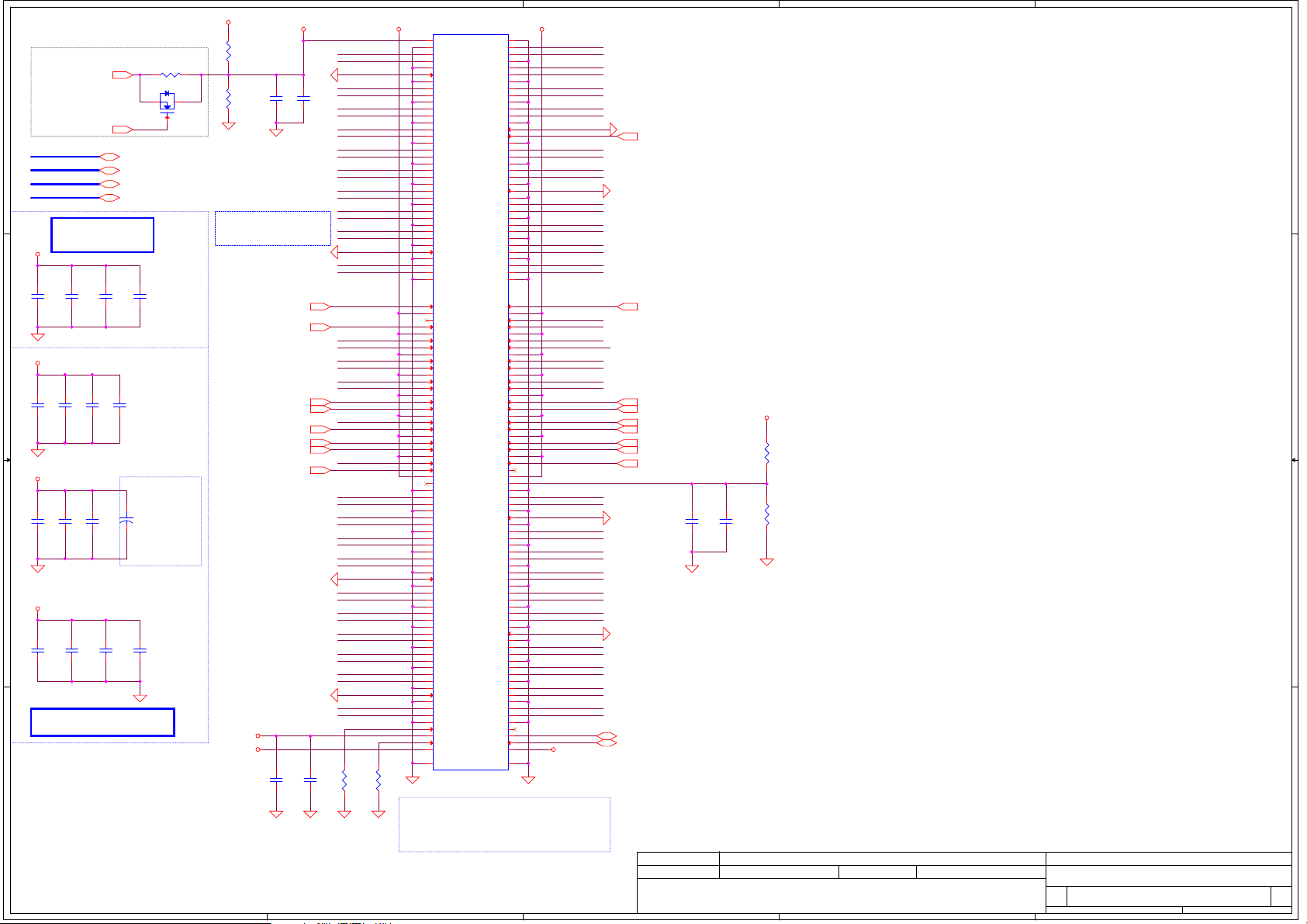

Intel

Sandy Bridge ULV

Processor

eDP(UMA)

BGA1023

17W

page 4~10

Memory BUS(DDRIII)

Dual Channel

1.5V DDRIII 1066/1333

204pin DDRIII-SO-DIMM X2

BANK 0, 1, 2, 3

page 11,12

FDI x8

CRT Conn

page 24

2 2

HDMI Conn.

LVDS/eDP Conn.

page 22page 23

LVDS(UMA)

TMDS(UMA)

CLK=100MHz

2.7GT/s

Intel

RGB(UMA)

HD Audio

3.3V 24MHz

Panther Point-M

PCH

DMI x4

CLK=100MHz

2.5GB/s x4

USBx14

3.3V 48MHz

PCI-Express x 8

(PCIE2.0 5GT/s)

USB 2.0

conn x1(Option for USB3.0)

page 34 page 22

Port 1

LAN(GbE)/CardReader

Broadcom

57785

page 25

Port 3 Port 2

100MHz

USB 2.0

conn x2

page 30

Port 2,3

MINI Card

WLAN

CMOS

Camera

Port 10

Port 8

page 36

SPI

HDA Codec

ALC271X-VB6

page 31

3 3

Int. Speaker

page 31

SPI ROM x2

page 13

989pin BGA

page 13~21

LPC BUS

CLK=33MHz

ENE

RTC CKT.

page 13

KB9012

page 29

SATA x 6 (GEN2 3.0GT/S ,GEN3 6GT/S)

100MHz

GEN3

Port 0

SATA HDD

Conn.

page 24

LS-8941P

LED/B

page 30

LS-8942P

IO/B

page 28

LS-8943P

HDD/B

page 24

Power On/Off CKT.

page 36

Touch Pad

page 30

Int.KBD

page 30

TPM

page 30

DC/DC Interface CKT.

4 4

Power Circuit DC/DC

page 33

page 34~43

A

Security Class ification

Security Class ification

Security Class ification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/11/ 22 2012/11/ 22

2011/11/ 22 2012/11/ 22

2011/11/ 22 2012/11/ 22

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Block Diagrams

Block Diagrams

Block Diagrams

Q1VZC M/B LA-8941P Schematic

Q1VZC M/B LA-8941P Schematic

Q1VZC M/B LA-8941P Schematic

2 45Friday, April 20, 2012

2 45Friday, April 20, 2012

2 45Friday, April 20, 2012

E

1.0

1.0

1.0

Page 3

A

Voltage Rails

Power Plane Description

VIN

BATT+ Battery power supply (12.6V) N/A N/A N/A

B+

1 1

+CPU_CORE

+VGFX_CORE Core voltage for UMA graphic ON OFF OFF

+0.75VS +0.75VP to +0.75VS switched power rail for DDR terminator

+1.05VS_VTT

+1.5V

+1.5VS

+1.8VS (+5VALW or +3VALW) to 1.8V switched power rail to PCH & GPU

+3VALW +3VALW always on power rail

+VCCSUS3_3 +3VALW to +VCCSUS3_3 power rail for PCH (Short Jump) ON ON

+3VS

+5VALW

+5VREF_SUS

+5VS +5VALW to +5VS switched power rail OFFON OFF

+VSB +VSBP to +VSB always on power rail for sequence control ON ON*

+RTCVCC RTC power

2 2

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

+1.05VS_VTTP to +1.05VS_VTT switched power rail for CPU

+1.5VP to +1.5V power rail for DDRIII ON ON OFF

+1.5V to +1.5VS switched power rail

+3VALW to +3VS power rail

+5VALWP to +5VALW power rail

+5VALW to +5VREF_SUS power rail for PCH (Short resister)

EC SM Bus1 address

Device

Smart Battery

Address

0001 011X b

PCH SM Bus address

Device Address

ChannelA DIMM0

ChannelB DIMM0

3 3

A0 1010 000X

B0 1010 010X

JDIMM1(STD)

JDIMM2(REV)

B

S1

S3 S5

N/A N/A N/A

ON

ON OFF OFF

ON OFF OFF

ON OFF OFF

ON

ON

ON

ON

ON ON

ON

ON

N/AN/AN/A

OFF

OFF

OFF

OFF

ON ON*

ON*

OFF

OFF

ON ON*

ON*

ONON

C

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SIGNAL

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

HIGH HIGH HIGH HIGH

LOW

LOW

LOW

HIGH

LOWLOWLOW

LOW LOW LOW LOW

Board ID / SKU ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7 NC

100K +/- 5%Ra/Rc/Re

Rb / Rd / Rf V min

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

AD_BID

0 V

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

BOARD ID Table

Board ID

0

1

2

3

4

5

6

7

PCB Revision

0.1

0.2

0.3

1.0

USB Port Table

USB 2.0 USB 1.1 Port

UHCI0

UHCI1

EHCI1

UHCI2

UHCI3

UHCI4

EHCI2

UHCI5

UHCI6

10

11

12

13

0

1

2

3

4

5

6

7

8

9

3 External

USB Port

USB 2.0(Options for USB3.0)

USB port(Left 2.0)

USB Port(Left 2.0)

Mini Card(WLAN)

Camera

D

ON

ON

ON

HIGHHIGHHIGH

HIGH

HIGH

V typ

AD_BID

ON

ON

ON

ON

OFF

ON

OFF

V

0 V 0 V

0.503 V

0.819 V

1.185 V 1.264 V

2.200 V

3.300 V

BTO Item BOM Structure

Celeron 867

Pentium 977

Unpop @

eDP Panel

LVDS Panel

Deep S3 DS3@

Normal S3 S3@

Intel i5/i7 CPU only

Celeron/Pentium/i3

CPU only

XHCI

ON ON

ON

LOW

OFF

OFF

OFF

OFF

OFF

OFF

max

AD_BID

0.538 V

0.875 V

2.341 V

3.300 V

BTO Option Table

PortUSB 3.0

1

2

USB Port(Right 3.0)

3

4

E

C867@

P977@

EDP@

LVDS@

CONN@Connector

USB3@USB3 Only

I57@

CP3@

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

C

2011/11/22 2012/11/22

2011/11/22 2012/11/22

2011/11/22 2012/11/22

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Notes List

Notes List

Notes List

Q1VZC M/B LA-8941P Schematic

Q1VZC M/B LA-8941P Schematic

Q1VZC M/B LA-8941P Schematic

E

3 45Friday, April 20, 2012

3 45Friday, April 20, 2012

3 45Friday, April 20, 2012

1.0

1.0

1.0

Page 4

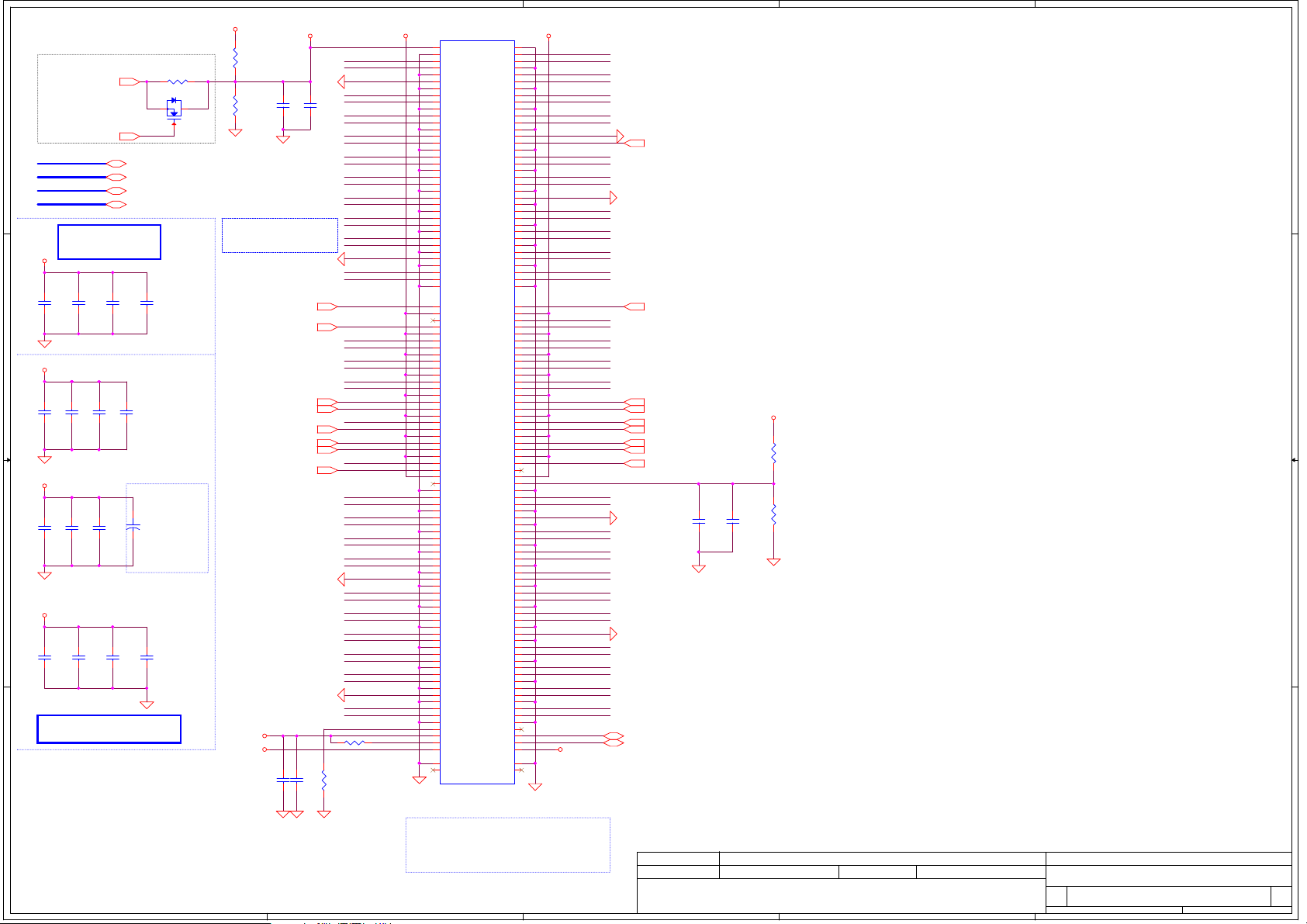

A

1 1

2 2

12

R3

1K_0402 _5%

EDP@

EDP_HPD #

+1.05VS_ VTT

12

R2

24.9_040 2_1%

eDP_COMPIO and ICOMPO signals

should be shorted near balls and

routed with typical impedance

<25 mohms

can't be left floating

,even if disable eDP function...

3 3

+1.05VS_ VTT

EDP_HPD #<22>

B

DMI_CRX_P TX_N0<15>

DMI_CRX_P TX_N1<15>

DMI_CRX_P TX_N2<15>

DMI_CRX_P TX_N3<15>

DMI_CRX_P TX_P0<15>

DMI_CRX_P TX_P1<15>

DMI_CRX_P TX_P2<15>

DMI_CRX_P TX_P3<15>

DMI_CTX_P RX_N0<15>

DMI_CTX_P RX_N1<15>

DMI_CTX_P RX_N2<15>

DMI_CTX_P RX_N3<15>

DMI_CTX_P RX_P0<15>

DMI_CTX_P RX_P1<15>

DMI_CTX_P RX_P2<15>

DMI_CTX_P RX_P3<15>

FDI_CTX_P RX_N0<15>

FDI_CTX_P RX_N1<15>

FDI_CTX_P RX_N2<15>

FDI_CTX_P RX_N3<15>

FDI_CTX_P RX_N4<15>

FDI_CTX_P RX_N5<15>

FDI_CTX_P RX_N6<15>

FDI_CTX_P RX_N7<15>

FDI_CTX_P RX_P0<15>

FDI_CTX_P RX_P1<15>

FDI_CTX_P RX_P2<15>

FDI_CTX_P RX_P3<15>

FDI_CTX_P RX_P4<15>

FDI_CTX_P RX_P5<15>

FDI_CTX_P RX_P6<15>

FDI_CTX_P RX_P7<15>

FDI_FSYNC0<15>

FDI_FSYNC1<15>

FDI_INT<15>

FDI_LSYNC0<15>

FDI_LSYNC1<15>

W=12mil L=500mil S=15mil

EDP_COM P

EDP_HPD #

EDP_AUX N<22>

EDP_AUX P<22>

EDP_TXN 0<2 2>

EDP_TXN 1<2 2>

EDP_TXP 0<22>

EDP_TXP 1<22>

UCPU1A

M2

DMI_RX#[0]

P6

DMI_RX#[1]

P1

DMI_RX#[2]

P10

DMI_RX#[3]

N3

DMI_RX[0]

P7

DMI_RX[1]

P3

DMI_RX[2]

P11

DMI_RX[3]

K1

DMI_TX#[0]

M8

DMI_TX#[1]

N4

DMI_TX#[2]

R2

DMI_TX#[3]

K3

DMI_TX[0]

M7

DMI_TX[1]

P4

DMI_TX[2]

T3

DMI_TX[3]

U7

FDI0_TX#[0]

W11

FDI0_TX#[1]

W1

FDI0_TX#[2]

AA6

FDI0_TX#[3]

W6

FDI1_TX#[0]

V4

FDI1_TX#[1]

Y2

FDI1_TX#[2]

AC9

FDI1_TX#[3]

U6

FDI0_TX[0]

W10

FDI0_TX[1]

W3

FDI0_TX[2]

AA7

FDI0_TX[3]

W7

FDI1_TX[0]

T4

FDI1_TX[1]

AA3

FDI1_TX[2]

AC8

FDI1_TX[3]

AA11

FDI0_FSYNC

AC12

FDI1_FSYNC

U11

FDI_INT

AA10

FDI0_LSYNC

AG8

FDI1_LSYNC

AF3

eDP_COMPIO

AD2

eDP_ICOMPO

AG11

eDP_HPD#

AG4

eDP_AUX#

AF4

eDP_AUX

AC3

eDP_TX#[0]

AC4

eDP_TX#[1]

AE11

eDP_TX#[2]

AE7

eDP_TX#[3]

AC1

eDP_TX[0]

AA4

eDP_TX[1]

AE10

eDP_TX[2]

AE6

eDP_TX[3]

IVY-BRIDGE_BGA1 023

C867@

C

W=12mil L=500mil S=15mil

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

G3

G1

G4

H22

J21

B22

D21

A19

D17

B14

D13

A11

B10

G8

A8

B6

H8

E5

K7

K22

K19

C21

D19

C19

D16

C13

D12

C11

C9

F8

C8

C5

H6

F6

K6

G22

C23

D23

F21

H19

C17

K15

F17

F14

A15

J14

H13

M10

F10

D9

J4

F22

A23

D24

E21

G19

B18

K17

G17

E14

C15

K13

G13

K10

G10

D8

K4

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#[0]

PEG_RX#[1]

DMI Intel(R) FDI

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PCI EXPRESS -- GRAPHICS

eDP

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

PEG_COM P

C867@

P977@

I2467@ i5-2467M

I2367@ i3-2367M

C877@

P987@

P967@

I2377@ i3-2377M

I3317@ i5-3317U

I3667@ i7-3667U

I32

I3427@ i5-3427U

I3517@ i7-3517U

D

PEG_ICOMPI and RCOMPO signals should be

shorted and routed

+1.05VS_ VTT

R1

24.9_040 2_1%

Celeron 867

Pentium 977

Celeron 877

Pentium 987

Pentium 967

17@ i3-3217U

UCPU1

AV80627 01147701

P977@

SA00005BJ50

UCPU1

AV80627 01147601

P987@

12

with - max length = 500 mils - typical

impedance = 43 mohms

PEG_ICOMPO signals should be routed with max length = 500 mils

- typical impedance = 14.5 mohms

HRHR1.3G

HR 1.6G

HR 1.4G

HR

HR

HR

HR 1.5G

CR 1.7G

CR 2G

CR 1.8G

CR

CR

UCPU1

AV80627 01047504

I2467@

SA00004X010

UCPU1

AV80627 01147801

P967@

SA00005BH40(S IC AV80627 01148901 SR0FK J1 1. 3G ABO!)

SA00005BJ50(S IC AV80627 01147701 SR0FB J1 1 .4G ABO!)

1.4G

SA00004X010(S IC AV8062 701047504 SR0D6 J1 1.6G ABO!)

SA000051H60( S IC AV8062 701047904 SR0CV J1 1 .4G ABO! )

SA00005QI00( S IC AV806270 1148001 QB35 J1 1. 4G BGA)

1.4G

SA00005QH00(S IC AV80627 01147601 QB31 J1 1 .5G BGA)

1.5G

SA000051J40(S IC AV8062 701147801 SR0FC J1 1.3 G ABO!)

1.3G

SA00005MX10(S IC AV80627010 48004 QAXQ J1 1.5G BGA)

SA00005K650(S IC AV8063 801058002 QC9E L1 1.7G BGA)

SA00005LA50(S IC AV8063 801057405 QC9B L1 2G BGA 1023)

SA00005L530(S IC AV806 3801058400 QC56 L 0 1.8G ABO!)

SA00005L9A0(S IC AV8063 801057801 SR0N7 L1 1.8G BGA)

1.8G

SA00005K540(S IC AV8063 801057605 QC9C L1 1 .9G BGA)

1.9G

UCPU1

AV80627 01047904

I2367@

000051H60

SA

UCPU1

AV80627 01048004

I2377@

SA00005QH50 SA000051J40 SA00005MX60

UCPU1

AV80638 01058002

I3317@

SA00005K6B0

UCPU1

UCPU1

AV80638 01057405

I3667@

SA00005LAA0

UCPU1

UCPU1

AV80638 01058401

I3217@

00005L5C0

SA

UCPU1

AV80627 01148001

C877@

SA00005QI40

HR(Sandy Bridge)

E

AV80638 01057801

I3427@

SA00005L9B0 SA00005K5B0

4 4

Security Class ification

Security Class ification

Security Class ification

2011/11/ 22 2012/11/ 22

2011/11/ 22 2012/11/ 22

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/11/ 22 2012/11/ 22

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

AV80638 01057605

I3517@

D

CR(Ivy Bridge)

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

PROCESSOR(1/7) DMI,FDI,PEG

PROCESSOR(1/7) DMI,FDI,PEG

PROCESSOR(1/7) DMI,FDI,PEG

Q1VZC M/B LA-8941P Schematic

Q1VZC M/B LA-8941P Schematic

Q1VZC M/B LA-8941P Schematic

4 45Friday, April 20, 2012

4 45Friday, April 20, 2012

4 45Friday, April 20, 2012

E

1.0

1.0

1.0

Page 5

A

B

C

D

E

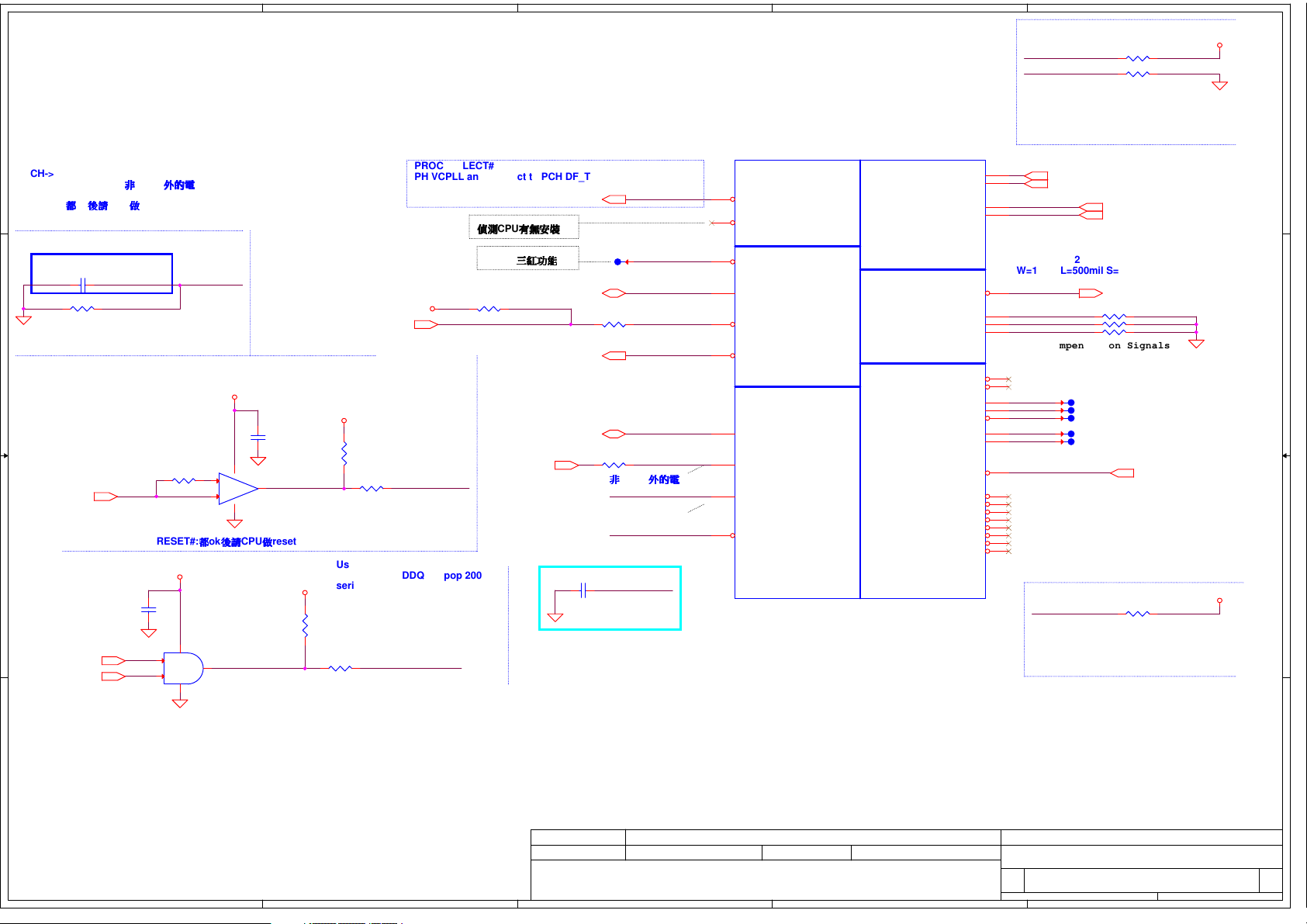

0921 LVDS@->@

CLK_CPU _DPLL#

CLK_CPU _DPLL

Checklist1.5 P.67 Graphis Disable Guide

eDP disable:

1 1

PCH->CPU

UNCOREPWRGOOD:

SM_DRAMPWROK:DRAM power ok

都都都都ok後後後後後後後後

RESET#:

CPU

非非非非

做做做做

CORE

reset

外外外外外外外外外外外外

OK

PROC_SELECT#

PH VCPLL and connect to PCH DF_TVS

H_SNB_IVB #<17>

偵偵偵偵偵偵偵偵

CPU

有有有有有有有有有有有有有有有有

Follow DG 1.5& Tacoma_Fall2 1.0

H_PROCH OT#_RH_PROCH OT#

H_CPUPW RGD_R

非非非非

CORE

外外外外外外外外外外外外

BUF_CPU _RST#

H_CATER R#

OK

reserve XBOX

@

12

C65 0.1U_0 402_16V4Z

R6 10K_0402_5%

2 2

12

Follow DG 1.5 & Tacoma_Fall2 1.0 Use open drain logic gate:

Buffered reset to CPU

PLT_RST #<17>

Follow DG 1.5 & Tacoma_Fall2 1.0

3 3

SYS_PW ROK<15>

PM_DRAM _PWRGD<15>

PLT_RST # PM_DRAM _PWRGD_R

C67

0.1U_040 2_16V4Z

H_CPUPW RGD

R14

0_0402_ 5%

1 2

@

RESET#:

都都都都ok後後後後後後後後

+3VALW

1

2

5

U2

1

B

Y

VCC

2

A

G

MC74VHC 1G09DFT2G_SC 70-5

3

+3VS

1

2

5

U1

1

P

NC

Y

2

A

G

SN74LVC 1G07DCKR_SC7 0-5

3

CPU

4

PM_SYS_PW RGD_BUF

C66

0.1U_040 2_16V4Z

4

BUFO_CP U_RST#

做做做做

reset

+1.5V_CP U_VDDQ

12

follow Checklist 1.5

+1.05VS_ VTT

H_PROCH OT#<29,35>

+1.05VS_VTT PU pop 75ohm

series resister pop 43ohm

+1.05VS_ VTT

12

R12

75_0402 _5%

R15

43_0402 _1%

1 2

Use open drain logic gate:

+1.5V_CPU_VDDQ PU pop 200ohm

series resister pop 130ohm

R16

200_040 2_5%

1 2

R18 130_040 2_5%

BUF_CPU _RST#

PM_DRAM _PWRGD_R

R7 6 2_0402_5%

三三三三三三三三三三三三三三三三

12

H_THRMT RIP#<18>

H_PM_SYNC<15>

H_CPUPW RGD<18>

UNCOREPWRGOOD:

SM_DRAMPWROK:DRAM power ok

T1 PAD@

H_PECI<18,29>

R8

56_0402 _5%

1 2

1 2

R13 0_040 2_5%

C476

@

12

H_CPUPW RGD_R

180P_04 02_50V8J

12/22 Add(ESD request)

UCPU1B

F49

PROC_SELECT#

C57

PROC_DETECT#

C49

CATERR#

A48

PECI

C45

PROCHOT#

D45

THERMTRIP#

C48

PM_SYNC

B46

UNCOREPWRGOOD

BE45

SM_DRAMPWROK

D44

RESET#

IVY-BRIDGE_BGA1 023

C867@

MISC THERMAL PWR MANAGEMENT

BCLK

BCLK#

DPLL_REF_CLK

DPLL_REF_CLK#

CLOCKS

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

DDR3

MISC

PRDY#

PREQ#

TCK

TMS

TRST#

TDI

TDO

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

JTAG & BPM

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

DPLL_REF_SSCLK PD 1K_5% to GND

DPLL_REF_SSCLK# PU 1K_5% to +1.05VS_VTT

J3

H2

AG3

AG1

AT30

BF44

BE43

BG43

CLK_CPU _DMI < 14>

CLK_CPU _DMI# <14>

CLK_CPU _DPLL

CLK_CPU _DPLL#

SM_RCOMP0,SM_RCOMP1

W=20mil L=500mil S=13mil

SM_RCOMP2

W=15mil L=500mil S=13mil

SM_DRAM RST#H_PECI

SM_RCOM P0

SM_RCOM P1

SM_RCOM P2

R9 140_0402_1%

R10 25.5_ 0402_1%

R11 200_ 0402_1%

DDR3 Compensation Signals

N53

N55

L56

XDP_TCK

L55

XDP_TMS

J58

XDP_TRS T#

M60

XDP_TDI

L59

XDP_TDO

K58

XDP_DBR ESET#

G58

E55

E59

G55

G59

H60

J59

J61

XDP_DBR ESET#

Tacoma_Fall2 1.0 PU 1K +3VS

Check list 1.5 PU 1K +3VS

Debug port DG1.1-1.3 50~5K ohm

LVDS@

R4 1K_0402_5%

LVDS@

R5 1K_0402_5%

CLK_CPU _DPLL <14>

CLK_CPU _DPLL# <14>

SM_DRAM RST# <6>

12

12

12

T2PAD@

T3PAD@

T4PAD@

T5PAD@

T6PAD@

XDP_DBR ESET# <15>

R17 1 K_0402_5%

+1.05VS_ VTT

12

12

+3VS

12

4 4

Security Class ification

Security Class ification

Security Class ification

2011/11/ 22 2012/11/ 22

2011/11/ 22 2012/11/ 22

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/11/ 22 2012/11/ 22

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

e Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Siz

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

PROCESSOR(3/7) DDRIII

PROCESSOR(3/7) DDRIII

PROCESSOR(3/7) DDRIII

Q1VZC M/B LA-8941P Schematic

Q1VZC M/B LA-8941P Schematic

Q1VZC M/B LA-8941P Schematic

5 45Friday, April 20, 2012

5 45Friday, April 20, 2012

5 45Friday, April 20, 2012

E

1.0

1.0

1.0

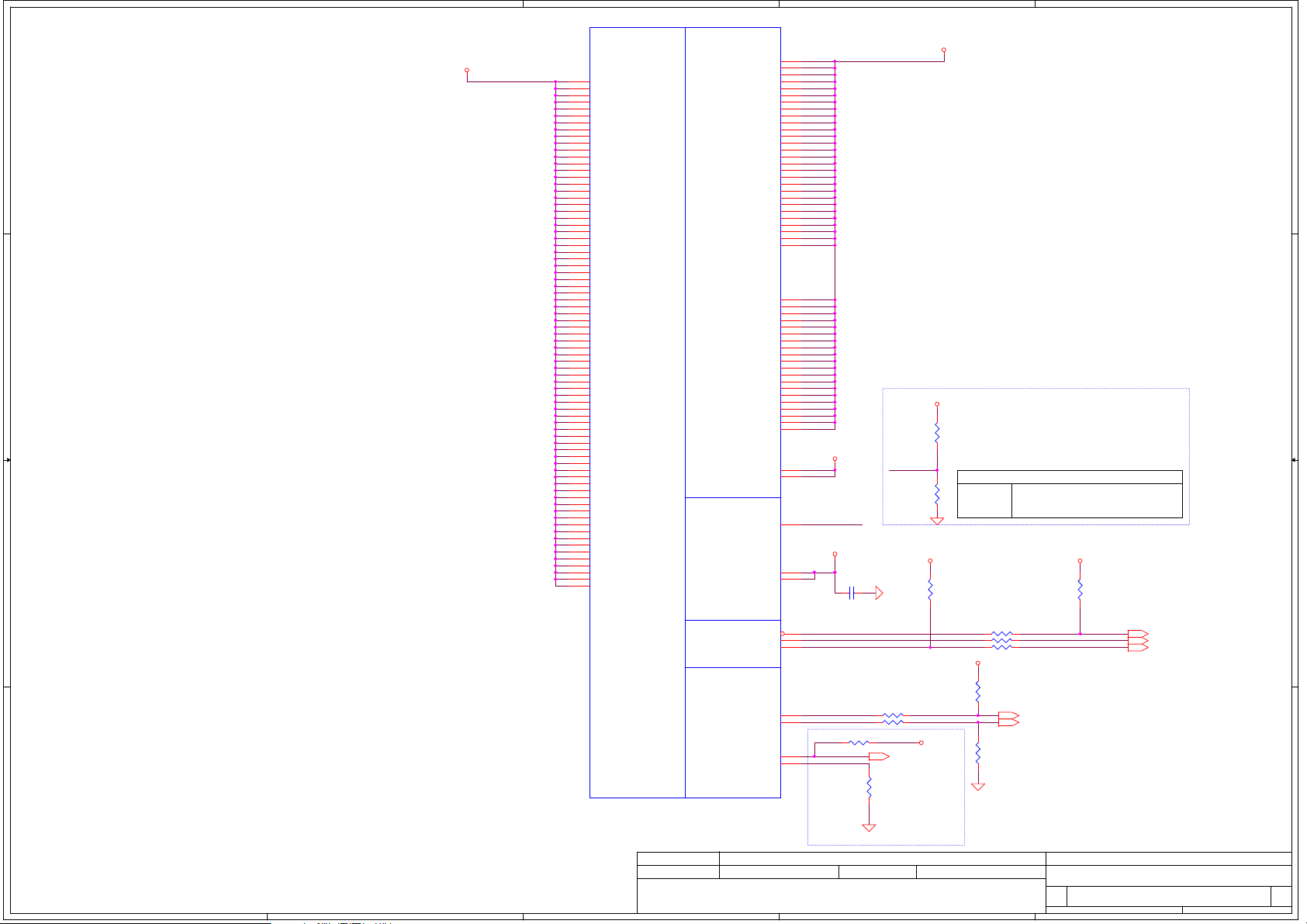

Page 6

A

B

C

D

E

BD13

BF12

BD10

BD14

BE13

BF16

BE17

BE18

BE21

BE14

BG14

BG18

BF19

BD50

BF48

BD53

BF52

BD49

BE49

BD54

BE53

BF56

BE57

BC59

AY60

BE54

BG54

BA58

AW59

AW58

AU58

AN61

AN59

AU59

AU61

AN58

AR58

AK58

AL58

AG58

AG59

AM60

AL59

AF61

AH60

BG39

BD42

AT22

AV43

BF40

BD45

AN3

AR4

AK4

AK3

AN4

AR1

AU4

AT2

AV4

BA4

AU3

AR3

AY2

BA3

BE9

BD9

BF8

UCPU1D

AL4

SB_DQ[0]

AL1

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

DDR SYSTEM MEMORY B

SB_CK[0]

SB_CK#[0]

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

BA34

AY34

AR22

BA36

BB36

BF27

BE41

BE47

AT43

BG47

AL3

AV3

BG11

BD17

BG51

BA59

AT60

AK59

AM2

AV1

BE11

BD18

BE51

BA61

AR59

AK61

BF32

BE33

BD33

AU30

BD30

AV30

BG30

BD29

BE30

BE28

BD43

AT28

AV28

BD46

AT26

AU22

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

SB_CLK_DDR0 <12>

SB_CLK_DDR#0 <12>

DDRB_CKE0_DIMMB <12>

SB_CLK_DDR1 <12>

SB_CLK_DDR#1 <12>

DDRB_CKE1_DIMMB <12>

DDRB_CS0_DIMMB# <12>

DDRB_CS1_DIMMB# <12>

SB_ODT0 <12>

SB_ODT1 <12>

DDR_B_DQS#[0..7] <12>

DDR_B_DQS[0..7] <12>

DDR_B_MA[0..15] <12>

DDR_A_D[0..63]<11>

1 1

2 2

3 3

DDR_A_BS0<11>

DDR_A_BS1<11>

DDR_A_BS2<11>

DDR_A_CAS#<11>

DDR_A_RAS#<11>

DDR_A_WE#<11>

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

AG6

AP11

AJ10

AR11

AP6

AU6

AV9

AR6

AP8

AT13

AU13

BC7

BB7

BA13

BB11

BA7

BA9

BB9

AY13

AV14

AR14

AY17

AR19

BA14

AU14

BB14

BB17

BA45

AR43

AW48

BC48

BC45

AR45

AT48

AY48

BA49

AV49

BB51

AY53

BB49

AU49

BA53

BB55

BA55

AV56

AP50

AP53

AV54

AT54

AP56

AP52

AN57

AN53

AG56

AG53

AN55

AN52

AG55

AK56

BD37

BF36

BA28

BE39

BD39

AT41

UCPU1C

SA_DQ[0]

AJ6

SA_DQ[1]

SA_DQ[2]

AL6

SA_DQ[3]

SA_DQ[4]

AJ8

SA_DQ[5]

AL8

SA_DQ[6]

AL7

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

DDR SYSTEM MEMORY A

SA_CK[0]

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AU36

AV36

AY26

AT40

AU40

BB26

BB40

BC41

AY40

BA41

AL11

AR8

AV11

AT17

AV45

AY51

AT55

AK55

AJ11

AR10

AY11

AU17

AW45

AV51

AT56

AK54

BG35

BB34

BE35

BD35

AT34

AU34

BB32

AT32

AY32

AV32

BE37

BA30

BC30

AW41

AY28

AU26

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

SA_CLK_DDR0 <11>

SA_CLK_DDR#0 <11>

DDRA_CKE0_DIMMA <11>

SA_CLK_DDR1 <11>

SA_CLK_DDR#1 <11>

DDRA_CKE1_DIMMA <11>

DDRA_CS0_DIMMA# <11>

DDRA_CS1_DIMMA# <11>

SA_ODT0 <11>

SA_ODT1 <11>

DDR_A_DQS#[0..7] <11>

DDR_A_DQS[0..7] <11>

DDR_A_MA[0..15] <11>

DDR_B_D[0..63]<12>

DDR_B_BS0<12>

DDR_B_BS1<12>

DDR_B_BS2<12>

DDR_B_CAS#<12>

DDR_B_RAS#<12>

DDR_B_WE#<12>

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

IVY-BRIDGE_BGA1023

C867@

R20

1K_0402_5%

+1.5V

12

1 2

R21 1K_0402_5%

S0

DRAMRST_CNTRL_PCH hgih ,MOS ON

SM_DRAMRST# HIGH,DDR3 DRAMRST# HIGH

Dimm not reset

S3

DRAMRST_CNTRL_PCH Low ,MOS OFF

SM_DRAMRST# lo,DDR3 DRAMRST# HIGH

Dimm not reset

S4,5

DRAMRST_CNTRL_PCH Low ,MOS OFF

SM_DRAMRST# lo,DDR3 DRAMRST# low

Dimm reset

B

DIMM_DRAMRST# <11,12>

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

C

2011/11/22 2012/11/22

2011/11/22 2012/11/22

2011/11/22 2012/11/22

Follow CRB1.0

R19

0_0402_5%

1 2

1 2

@

D

S

13

G

2

RST_GATE_R

1

C68

0.047U_0402_16V7K

2

DIMM_DRAMRST#_RSM_DRAMRST#

Q1

BSS138_NL_SOT23-3

RST_GATE_R <11,12>

CPU通通DIMM做reset

SM_DRAMRST#<5>

R22

4.99K_0402_1%

4 4

RST_GATE<14>

EC_RST_GATE<29>

0_0402_5%

1 2

0_0402_5%

1 2

A

R23

DS3@

R24

DS3@

IVY-BRIDGE_BGA1023

C867@

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

PROCESSOR(3/7) DDRIII

PROCESSOR(3/7) DDRIII

PROCESSOR(3/7) DDRIII

Q1VZC M/B LA-8941P Schematic

Q1VZC M/B LA-8941P Schematic

Q1VZC M/B LA-8941P Schematic

E

6 45Friday, April 20, 2012

6 45Friday, April 20, 2012

6 45Friday, April 20, 2012

1.0

1.0

1.0

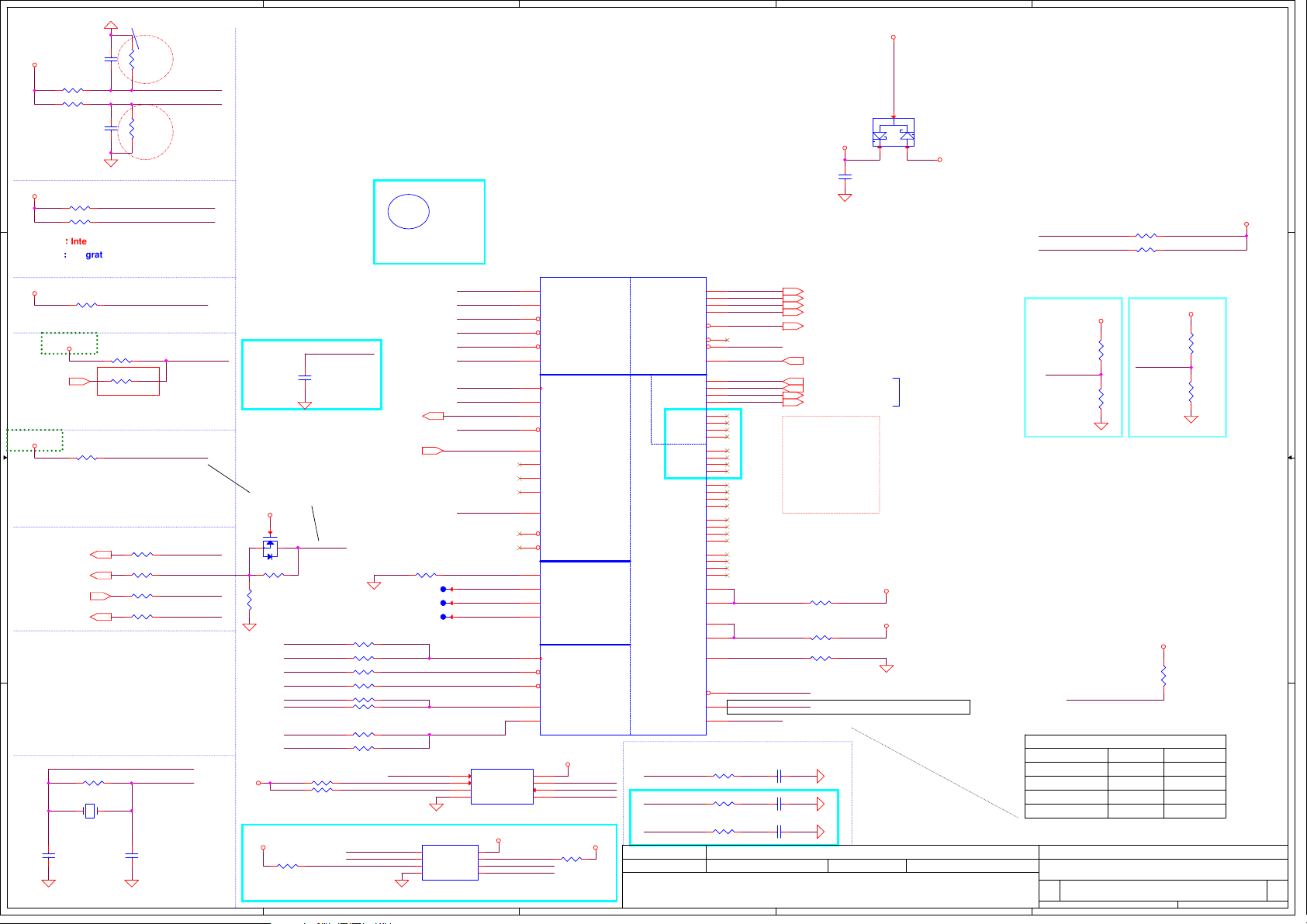

Page 7

A

B

C

D

E

CFG Straps for Processor

CFG6

CFG5

1K_0402 _1%

CFG2

*

*

R31

12

R25

1K_0402 _1%

@

1: Normal Operation; Lane # definition matches

socket pin map definition

0:Lane Reversed

CFG4

EDP@

12

R28

1K_0402 _1%

UMA,Optimus eDP

DISO eDP

1:Disable

0:Enable

12

12

R32

@

1K_0402 _1%

@

11: (Default) 1x16 PCI Express

10: 2x8 PCI Express

*

01: Reserved

00: 1x8,2x4 PCI Express

CFG7

12

R33

1K_0402 _1%@

關關關關關關關關

啟啟啟啟啟啟啟啟

UCPU1E

T7 P AD@

1 1

T37 PAD @

T38 PAD @

T39 PAD @

T40 PAD @

2 2

CFG0

CFG2

CFG4

CFG5

CFG6

CFG7

VCC_VAL _SENSE

VSS_VAL _SENSE

VAXG_VA L_SENSE

VSSAXG_ VAL_SENSE

T8 P AD@

B50

CFG[0]

C51

CFG[1]

B54

CFG[2]

D53

CFG[3]

A51

CFG[4]

C53

CFG[5]

C55

CFG[6]

H49

CFG[7]

A55

CFG[8]

H51

CFG[9]

K49

CFG[10]

K53

CFG[11]

F53

CFG[12]

G53

CFG[13]

L51

CFG[14]

F51

CFG[15]

D52

CFG[16]

L53

CFG[17]

H43

VCC_VAL_SENSE

K43

VSS_VAL_SENSE

H45

VAXG_VAL_SENSE

K45

VSSAXG_VAL_SENSE

F48

VCC_DIE_SENSE

H48

RSVD6

K48

RSVD7

BA19

RSVD8

AV19

RSVD9

AT21

RSVD10

BB21

RSVD11

BB19

RSVD12

AY21

RSVD13

BA22

RSVD14

AY22

RSVD15

AU19

RSVD16

AU21

RSVD17

BD21

RSVD18

BD22

RSVD19

BD25

RSVD20

BD26

RSVD21

BG22

RSVD22

BE22

RSVD23

BG26

RSVD24

BE26

RSVD25

BF23

RSVD26

BE24

RSVD27

RESERVED

DC_TEST_A4

DC_TEST_C4

DC_TEST_D3

DC_TEST_D1

DC_TEST_A58

DC_TEST_A59

DC_TEST_C59

DC_TEST_A61

DC_TEST_C61

DC_TEST_D61

DC_TEST_BD61

DC_TEST_BE61

DC_TEST_BE59

DC_TEST_BG61

DC_TEST_BG59

DC_TEST_BG58

DC_TEST_BG4

DC_TEST_BG3

DC_TEST_BE3

DC_TEST_BG1

DC_TEST_BE1

DC_TEST_BD1

BCLK_ITP

BCLK_ITP#

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

N59

N58

N42

L42

L45

L47

M13

M14

U14

W14

P13

AT49

K24

AH2

AG13

AM14

AM15

N50

A4

C4

D3

D1

A58

A59

C59

A61

C61

D61

BD61

BE61

BE59

BG61

BG59

BG58

BG4

BG3

BE3

BG1

BE1

BD1

DC_TEST _C4_D3

DC_TEST _A59_C59

DC_TEST _A61_C61

DC_TEST _BE59_BE61

DC_TEST _BG59_BG61

DC_TEST _BE3_BG3

DC_TEST _BE1_BG1

These pins are for solder joint

reliability and non-critical to

function. For BGA only.

PEG Static Lane Reversal - CFG2 is for the 16x

CFG2

eDP enable

CFG4

PCIE Port Bifurcation Straps

CFG[6:5]

IVY-BRIDGE_BGA1 023

3 3

C867@

PEG DEFER TRAINING

CFG7

1: (Default) PEG Train immediately following

xxRESETB de assertion

Tacoma_Fall2 1.0 P.12

0: PEG Wait for BIOS for training

4 4

Security Class ification

Security Class ification

Security Class ification

2011/11/ 22 2012/11/ 22

2011/11/ 22 2012/11/ 22

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/11/ 22 2012/11/ 22

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

PROCESSOR(4/7) RSVD,CFG

PROCESSOR(4/7) RSVD,CFG

PROCESSOR(4/7) RSVD,CFG

Q1VZC M/B LA-8941P Schematic

Q1VZC M/B LA-8941P Schematic

Q1VZC M/B LA-8941P Schematic

7 45Friday, April 20, 2012

7 45Friday, April 20, 2012

7 45Friday, April 20, 2012

E

1.0

1.0

1.0

Page 8

A

1 1

INTEL Recommend VCC

4*470UF,12*22uF(0805) and 35*2.2uF(0402)

PD0.8

CAP at P.51

2 2

3 3

B

UCPU1F

A26

VCC[1]

A29

VCC[2]

A31

VCC[3]

A34

VCC[4]

A35

VCC[5]

A38

VCC[6]

A39

VCC[7]

A42

VCC[8]

C26

VCC[9]

C27

VCC[10]

C32

VCC[11]

C34

VCC[12]

C37

VCC[13]

C39

VCC[14]

C42

VCC[15]

D27

VCC[16]

D32

VCC[17]

D34

VCC[18]

D37

VCC[19]

D39

VCC[20]

D42

VCC[21]

E26

VCC[22]

E28

VCC[23]

E32

VCC[24]

E34

VCC[25]

E37

VCC[26]

E38

VCC[27]

F25

VCC[28]

F26

VCC[29]

F28

VCC[30]

F32

VCC[31]

F34

VCC[32]

F37

VCC[33]

F38

VCC[34]

F42

VCC[35]

G42

VCC[36]

H25

VCC[37]

H26

VCC[38]

H28

VCC[39]

H29

VCC[40]

H32

VCC[41]

H34

VCC[42]

H35

VCC[43]

H37

VCC[44]

H38

VCC[45]

H40

VCC[46]

J25

VCC[47]

J26

VCC[48]

J28

VCC[49]

J29

VCC[50]

J32

VCC[51]

J34

VCC[52]

J35

VCC[53]

J37

VCC[54]

J38

VCC[55]

J40

VCC[56]

J42

VCC[57]

K26

VCC[58]

K27

VCC[59]

K29

VCC[60]

K32

VCC[61]

K34

VCC[62]

K35

VCC[63]

K37

VCC[64]

K39

VCC[66]

K42

VCC[67]

L25

VCC[68]

L28

VCC[69]

L33

VCC[70]

L36

VCC[71]

L40

VCC[72]

N26

VCC[73]

N30

VCC[74]

N34

VCC[75]

N38

VCC[76]

+CPU_CORE

ULV type

DC 33A

C

POWER

CORE SUPPLY

8.5A

AF46

VCCIO[1]

AG48

VCCIO[3]

AG50

VCCIO[4]

AG51

VCCIO[5]

AJ17

VCCIO[6]

AJ21

VCCIO[7]

AJ25

VCCIO[8]

AJ43

VCCIO[9]

AJ47

VCCIO[10]

AK50

VCCIO[11]

AK51

VCCIO[12]

AL14

VCCIO[13]

AL15

VCCIO[14]

AL16

VCCIO[15]

AL20

VCCIO[16]

AL22

VCCIO[17]

AL26

VCCIO[18]

AL45

VCCIO[19]

AL48

VCCIO[20]

AM16

VCCIO[21]

AM17

VCCIO[22]

AM21

VCCIO[23]

AM43

VCCIO[24]

AM47

VCCIO[25]

AN20

VCCIO[26]

AN42

VCCIO[27]

AN45

VCCIO[28]

AN48

VCCIO[29]

AA14

VCCIO[30]

AA15

VCCIO[31]

AB17

VCCIO[32]

VCCIO[33]

VCCIO[34]

VCCIO[35]

VCCIO[36]

VCCIO[37]

VCCIO[38]

VCCIO[39]

VCCIO[40]

VCCIO[41]

VCCIO[42]

VCCIO[43]

VCCIO[44]

VCCIO[45]

VCCIO[46]

VCCIO[47]

VCCIO[48]

VCCIO[49]

VCCIO50

VCCIO51

VCCIO_SEL

VCCPQE[1]

VCCPQE[2]

AB20

AC13

AD16

AD18

AD21

AE14

AE15

AF16

AF18

AF20

AG15

AG16

AG17

AG20

AG21

AJ14

AJ15

W16

W17

BC22

AM25

AN22

PEG IO AND DDR IO

RAILS

D

+1.05VS_VTT

For DDR

INTEL Recommend VCCIO

2*330UF,10*10uF(0603) and 26*1uF(0402)

PD0.8

CAP at P.51

For PEG

+3VS

12

R34

10K_0402_5%

VCCIO_SEL

R35

10K_0402_5%

@

VCCIO_SEL after Ivy bridge ES2 Voltage support

12

@

12

R36

130_0402_5%

BC22

*

+1.05VS_VTT

VCCIO_SEL

+1.05VS_VTT

C69

1U_0402_6.3V6K

1 2

1/NC : (Default) +1.05VS_VTT

0: +1.0VS_VTT

+1.05VS_VTT+ 1.05VS_VTT

12

R37

75_0402_5%

Place the PU

re

E

sistors close to CPU

A44

VIDALERT#

VIDSCLK

VIDSOUT

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSS_SENSE_VCCIO

SENSE LINES SVID QUIET

4 4

A

B

IVY-BRIDGE_BGA1023

C867@

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Issued Date

Issued Date

C

2011/11/22 2012/11/22

2011/11/22 2012/11/22

2011/11/22 2012/11/22

H_CPU_SVIDALRT#

B43

H_CPU_SVIDCLK

C44

H_CPU_SVIDDAT

F43

VCCSENSE_R

G43

VSSSENSE_R

R44 10_04 02_5%

AN16

AN17

VSSIO_SENSE

Compal Secret Data

Compal Secret Data

Compal Secret Data

Place the PU

resistors close to VR

1 2

R42 0_0402_5%

R43 0_0402_5%

1 2

1 2

VCCIO_SENSE <40>

12

R46

10_0402_5%

Check list 1.5

Deciphered Date

Deciphered Date

Deciphered Date

D

+1.05VS_VTT

1 2

R38 43_0402_ 1%

R39 0_0402_5 %

1 2

1 2

R40 0_0402_5 %

+CPU_CORE

12

R41

100_0402_1%

VCCSENSE <41>

12

VSSSENSE <41>

R45

100_0402_1%

Should change to connect form

power cirucit & layout differential

with VCCIO_SENSE.

SVID_ALERT# <41>

SVID_CLK <41>

SVID_DATA <41>

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

PROCESSOR(5/7) PWR,BYPASS

PROCESSOR(5/7) PWR,BYPASS

PROCESSOR(5/7) PWR,BYPASS

Q1VZC M/B LA-8941P Schematic

Q1VZC M/B LA-8941P Schematic

Q1VZC M/B LA-8941P Schematic

E

8 45Friday, April 20, 2012

8 45Friday, April 20, 2012

8 45Friday, April 20, 2012

1.0

1.0

1.0

Page 9

A

+VGFX_CORE

1 1

INTEL Recommend VAXG

2*470uF,6*22uF(0805) and 6*10uF(0603)

11*1U(0402)

PD0.8

2 2

CR CheckList Rev1.5

+VGFX_CORE

INTEL Recommend VCCPLL

1*330uF,2*1uF(0402)

PD0.8

3 3

SGA00001700 S POLY C 220U

220U 2.5V M B2 ESR35 TPE H1.9

SGA20331E10 S POLY C 330U

2V Y D2 LESR9M EEFSX H1.9

INTEL Recommend VCCSA

4 4

1*330uF,5*10uF(0603) ,5*1uF(0402)

+1.8VS

+VCCSA

VCC_GFXSENSE<41>

VSS_GFXSENSE<41>

Place BOT OUT Conn

1

+

C91

@

220U_B2_2.5VM_R35

2

1

+

C94

330U_D2_2V_Y

2

Place TOP IN BGA

+VCCSA

C95

C96

1U_0402_6.3V6K

12

C97

1U_0402_6.3V6K

1U_0402_6.3V6K

12

12

Place BOT OUT BGA

C101

C100

10U_0603_6.3V6M

12

C102

10U_0603_6.3V6M

10U_0603_6.3V6M

12

12

12

R51

100_0402_5%

12

R52

100_0402_5%

1U_0402_6.3V6K

1

2

C98

1U_0402_6.3V6K

12

C103

10U_0603_6.3V6M

12

C92

1

2

12

12

B

DC 16A

C93

1U_0402_6.3V6K

C99

1U_0402_6.3V6K

C104

10U_0603_6.3V6M

1.2A

6A

UCPU1G

AA46

VAXG[1]

AB47

VAXG[2]

AB50

VAXG[3]

AB51

VAXG[4]

AB52

VAXG[5]

AB53

VAXG[6]

AB55

VAXG[7]

AB56

VAXG[8]

AB58

VAXG[9]

AB59

VAXG[10]

AC61

VAXG[11]

AD47

VAXG[12]

AD48

VAXG[13]

AD50

VAXG[14]

AD51

VAXG[15]

AD52

VAXG[16]

AD53

VAXG[17]

AD55

VAXG[18]

AD56

VAXG[19]

AD58

VAXG[20]

AD59

VAXG[21]

AE46

VAXG[22]

N45

VAXG[23]

P47

VAXG[24]

P48

VAXG[25]

P50

VAXG[26]

P51

VAXG[27]

P52

VAXG[28]

P53

VAXG[29]

P55

VAXG[30]

P56

VAXG[31]

P61

VAXG[32]

T48

VAXG[33]

T58

VAXG[34]

T59

VAXG[35]

T61

VAXG[36]

U46

VAXG[37]

V47

VAXG[38]

V48

VAXG[39]

V50

VAXG[40]

V51

VAXG[41]

V52

VAXG[42]

V53

VAXG[43]

V55

VAXG[44]

V56

VAXG[45]

V58

VAXG[46]

V59

VAXG[47]

W50

VAXG[48]

W51

VAXG[49]

W52

VAXG[50]

W53

VAXG[51]

W55

VAXG[52]

W56

VAXG[53]

W61

VAXG[54]

Y48

VAXG[55]

Y61

VAXG[56]

F45

VAXG_SENSE

G45

VSSAXG_SENSE

BB3

VCCPLL[1]

BC1

VCCPLL[2]

BC4

VCCPLL[3]

L17

VCCSA[1]

L21

VCCSA[2]

N16

VCCSA[3]

N20

VCCSA[4]

N22

VCCSA[5]

P17

VCCSA[6]

P20

VCCSA[7]

R16

VCCSA[8]

R18

VCCSA[9]

R21

VCCSA[10]

U15

VCCSA[11]

V16

VCCSA[12]

V17

VCCSA[13]

V18

VCCSA[14]

V21

VCCSA[15]

W20

VCCSA[16]

IVY-BRIDGE_BGA1023

C867@

POWER

VREF

DDR3 - 1.5V RAILS

GRAPHICS

SENSE

LINES

1.8V RAIL

SA RAIL

VCCSA VID

SM_VREF

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

VDDQ[1]

VDDQ[2]

VDDQ[3]

VDDQ[4]

VDDQ[5]

VDDQ[6]

VDDQ[7]

VDDQ[8]

VDDQ[9]

VDDQ[10]

VDDQ[11]

VDDQ[12]

VDDQ[13]

VDDQ[14]

VDDQ[15]

VDDQ[16]

VDDQ[17]

VDDQ[18]

VDDQ[19]

VDDQ[20]

VDDQ[21]

VDDQ[22]

VDDQ[23]

VDDQ[24]

VDDQ[25]

VDDQ[26]

VCCDQ[1]

VCCDQ[2]

QUIET RAILS

VDDQ_SENSE

VSS_SENSE_VDDQ

VCCSA_SENSE

SENSE LINES

VCCSA_VID[0]

VCCSA_VID[1]

lines

C

AY43

+V_SM_VREF

BE7

SA_DIMM_VREFDQ

BG7

SB_DIMM_VREFDQ

5A

AJ28

AJ33

AJ36

AJ40

AL30

AL34

AL38

AL42

AM33

AM36

AM40

AN30

AN34

AN38

AR26

AR28

AR30

AR32

AR34

AR36

AR40

AV41

AW26

BA40

BB28

BG33

+1.5V_CPU_VDDQ

AM28

AN26

BC43

BA43

U10

CPU EDS1.3 P.93

CSA_VID0 Must PD

VC

D48

D49

1K_0402_1%

C71

1U_0402_6.3V6K

12

12

C90

1U_0402_6.3V6K

H_VCCSA_VID0

H_VCCSA_VID1

D

+1.5V_CPU_VDDQ

+V_SM_VREF should

have 20 mil trace width

SA_DIMM_VREFDQ <11>

12

12

R49

1K_0402_1%

@

@

SB_DIMM_VREFDQ <12>

R50

INTEL Recommend VDDQ

0.1U_0402_16V4Z

C70

12

R47

1K_0402_5%

12

1

R48

1K_0402_5%

2

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

Check list1.5 P18 M1 default M3 no stuff

E

1*330uF,8*10uF(0603) ,10*1uF(0402)

PD0.8

Place TOP IN BGA

C73

C72

1U_0402_6.3V6K

12

C74

1U_0402_6.3V6K

1U_0402_6.3V6K

12

12

C76

C75

1U_0402_6.3V6K

12

C77

1U_0402_6.3V6K

12

C78

1U_0402_6.3V6K

1U_0402_6.3V6K

12

12

12

+1.5V_CPU_VDDQ

C79

C80

1U_0402_6.3V6K

1U_0402_6.3V6K

12

1

+

C81

330U_D2_2V_Y

2

Place BOT OUT BGA

12

VID0

0

0

1 1

C89

C88

10U_0603_6.3V6M

10U_0603_6.3V6M

12

SGA20331E10 S POLY C 330U

2V Y D2 LESR9M EEFSX H1.9

VCCSA

VID1

Vout

0

0.9V

1

0.85V

0 X1

0.775V

0.75V

HR CR

V V

V

V

V

VX

@

12

R53

0_0402_5%

C86

C82

C83

10U_0603_6.3V6M

10U_0603_6.3V6M

12

12

C85

C84

10U_0603_6.3V6M

10U_0603_6.3V6M

12

12

VCCSA_SENSE < 39>

H_VCCSA_VID0 <39>

H_VCCSA_VID1 <39>

C87

10U_0603_6.3V6M

10U_0603_6.3V6M

12

12

J1

1 2

JUMP_43X118

@

+1.5VS

PD0.8

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/11/22 2012/11/22

2011/11/22 2012/11/22

2011/11/22 2012/11/22

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Siz

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

PROCESSOR(6/7) PWR

PROCESSOR(6/7) PWR

PROCESSOR(6/7) PWR

e Document Number Rev

Q1VZC M/B LA-8941P Schematic

Q1VZC M/B LA-8941P Schematic

Q1VZC M/B LA-8941P Schematic

E

9 45Friday, April 20, 2012

9 45Friday, April 20, 2012

9 45Friday, April 20, 2012

1.0

1.0

1.0

Page 10

A

UCPU1H

A13

VSS[1]

A17

VSS[2]

A21

VSS[3]

A25

VSS[4]

A28

VSS[5]

A33

VSS[6]

1 1

2 2

3 3

4 4

A37

VSS[7]

A40

VSS[8]

A45

VSS[9]

A49

VSS[10]

A53

VSS[11]

A9

VSS[12]

AA1

VSS[13]

AA13

VSS[14]

AA50

VSS[15]

AA51

VSS[16]

AA52

VSS[17]

AA53

VSS[18]

AA55

VSS[19]

AA56

VSS[20]

AA8

VSS[21]

AB16

VSS[22]

AB18

VSS[23]

AB21

VSS[24]

AB48

VSS[25]

AB61

VSS[26]

AC10

VSS[27]

AC14

VSS[28]

AC46

VSS[29]

AC6

VSS[30]

AD17

VSS[31]

AD20

VSS[32]

AD4

VSS[33]

AD61

VSS[34]

AE13

VSS[35]

AE8

VSS[36]

AF1

VSS[37]

AF17

VSS[38]

AF21

VSS[39]

AF47

VSS[40]

AF48

VSS[41]

AF50

VSS[42]

AF51

VSS[43]

AF52

VSS[44]

AF53

VSS[45]

AF55

VSS[46]

AF56

VSS[47]

AF58

VSS[48]

AF59

VSS[49]

AG10

VSS[50]

AG14

VSS[51]

AG18

VSS[52]

AG47

VSS[53]

AG52

VSS[54]

AG61

VSS[55]

AG7

VSS[56]

AH4

VSS[57]

AH58

VSS[58]

AJ13

VSS[59]

AJ16

VSS[60]

AJ20

VSS[61]

AJ22

VSS[62]

AJ26

VSS[63]

AJ30

VSS[64]

AJ34

VSS[65]

AJ38

VSS[66]

AJ42

VSS[67]

AJ45

VSS[68]

AJ48

VSS[69]

AJ7

VSS[70]

AK1

VSS[71]

AK52

VSS[72]

AL10

VSS[73]

AL13

VSS[74]

AL17

VSS[75]

AL21

VSS[76]

AL25

VSS[77]

AL28

VSS[78]

AL33

VSS[79]

AL36

VSS[80]

AL40

VSS[81]

AL43

VSS[82]

AL47

VSS[83]

AL61

VSS[84]

AM13

VSS[85]

AM20

VSS[86]

AM22

VSS[87]

AM26

VSS[88]

AM30

VSS[89]

AM34

VSS[90]

IVY-BRIDGE_BGA1023

C867@

VSS

A

VSS[91]

VSS[92]

VSS[93]

VSS[94]

VSS[95]

VSS[96]

VSS[97]

VSS[98]

VSS[99]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[162]

VSS[163]

VSS[164]

VSS[165]

VSS[166]

VSS[167]

VSS[168]

VSS[169]

VSS[170]

VSS[171]

VSS[172]

VSS[173]

VSS[174]

VSS[175]

VSS[176]

VSS[177]

VSS[178]

VSS[179]

VSS[180]

AM38

AM4

AM42

AM45

AM48

AM58

AN1

AN21

AN25

AN28

AN33

AN36

AN40

AN43

AN47

AN50

AN54

AP10

AP51

AP55

AP7

AR13

AR17

AR21

AR41

AR48

AR61

AR7

AT14

AT19

AT36

AT4

AT45

AT52

AT58

AU1

AU11

AU28

AU32

AU51

AU7

AV17

AV21

AV22

AV34

AV40

AV48

AV55

AW13

AW43

AW61

AW7

AY14

AY19

AY30

AY36

AY4

AY41

AY45

AY49

AY55

AY58

AY9

BA1

BA11

BA17

BA21

BA26

BA32

BA48

BA51

BB53

BC13

BC5

BC57

BD12

BD16

BD19

BD23

BD27

BD32

BD36

BD40

BD44

BD48

BD52

BD56

BD8

BE5

BG13

B

UCPU1I

BG17

VSS[181]

BG21

VSS[182]

BG24

VSS[183]

BG28

VSS[184]

BG37

VSS[185]

BG41

VSS[186]

BG45

VSS[187]

BG49

VSS[188]

BG53

VSS[189]

BG9

VSS[190]

C29

VSS[191]

C35

VSS[192]

C40

VSS[193]

D10

VSS[194]

D14

VSS[195]

D18

VSS[196]

D22

VSS[197]

D26

VSS[198]

D29

VSS[199]

D35

VSS[200]

D4

VSS[201]

D40

VSS[202]

D43

VSS[203]

D46

VSS[204]

D50

VSS[205]

D54

VSS[206]

D58

VSS[207]

D6

VSS[208]

E25

VSS[209]

E29

VSS[210]

E3

VSS[211]

E35

VSS[212]

E40

VSS[213]

F13

VSS[214]

F15

VSS[215]

F19

VSS[216]

F29

VSS[217]

F35

VSS[218]

F40

VSS[219]

F55

VSS[220]

G51

VSS[221]

G6

VSS[222]

G61

VSS[223]

H10

VSS[224]

H14

VSS[225]

H17

VSS[226]

H21

VSS[227]

H4

VSS[228]

H53

VSS[229]

H58

VSS[230]

J1

VSS[231]

J49

VSS[232]

J55

VSS[233]

K11

VSS[234]

K21

VSS[235]

K51

VSS[236]

K8

VSS[237]

L16

VSS[238]

L20

VSS[239]

L22

VSS[240]

L26

VSS[241]

L30

VSS[242]

L34

VSS[243]

L38

VSS[244]

L43

VSS[245]

L48

VSS[246]

L61

VSS[247]

M11

VSS[248]

M15

VSS[249]

IVY-BRIDGE_BGA1023

C867@

B

VSS

NCTF

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

M4

VSS[250]

M58

VSS[251]

M6

VSS[252]

N1

VSS[253]

N17

VSS[254]

N21

VSS[255]

N25

VSS[256]

N28

VSS[257]

N33

VSS[258]

N36

VSS[259]

N40

VSS[260]

N43

VSS[261]

N47

VSS[262]

N48

VSS[263]

N51

VSS[264]

N52

VSS[265]

N56

VSS[266]

N61

VSS[267]

P14

VSS[268]

P16

VSS[269]

P18

VSS[270]

P21

VSS[271]

P58

VSS[272]

P59

VSS[273]

P9

VSS[274]

R17

VSS[275]

R20

VSS[276]

R4

VSS[277]

R46

VSS[278]

T1

VSS[279]

T47

VSS[280]

T50

VSS[281]

T51

VSS[282]

T52

VSS[283]

T53

VSS[284]

T55

VSS[285]

T56

VSS[286]

U13

VSS[287]

U8

VSS[288]

V20

VSS[289]

V61

VSS[290]

W13

VSS[291]

W15

VSS[292]

W18

VSS[293]

W21

VSS[294]

W46

VSS[295]

W8

VSS[296]

Y4

VSS[297]

Y47

VSS[298]

Y58

VSS[299]

Y59

VSS[300]

G48

VSS[301]

VSS_NCTF_1

VSS_NCTF_2

VSS_NCTF_3

VSS_NCTF_4

VSS_NCTF_5

VSS_NCTF_6

VSS_NCTF_7

VSS_NCTF_8

VSS_NCTF_9

VSS_NCTF_10

VSS_NCTF_11

VSS_NCTF_12

VSS_NCTF_13

VSS_NCTF_14

A5

A57

BC61

BD3

BD59

BE4

BE58

BG5

BG57

C3

C58

D59

E1

E61

Compal Secret Data

Compal Secret Data

2011/11/22 2012/11/22

2011/11/22 2012/11/22

2011/11/22 2012/11/22

C

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title