Page 1

A

1 1

B

C

D

E

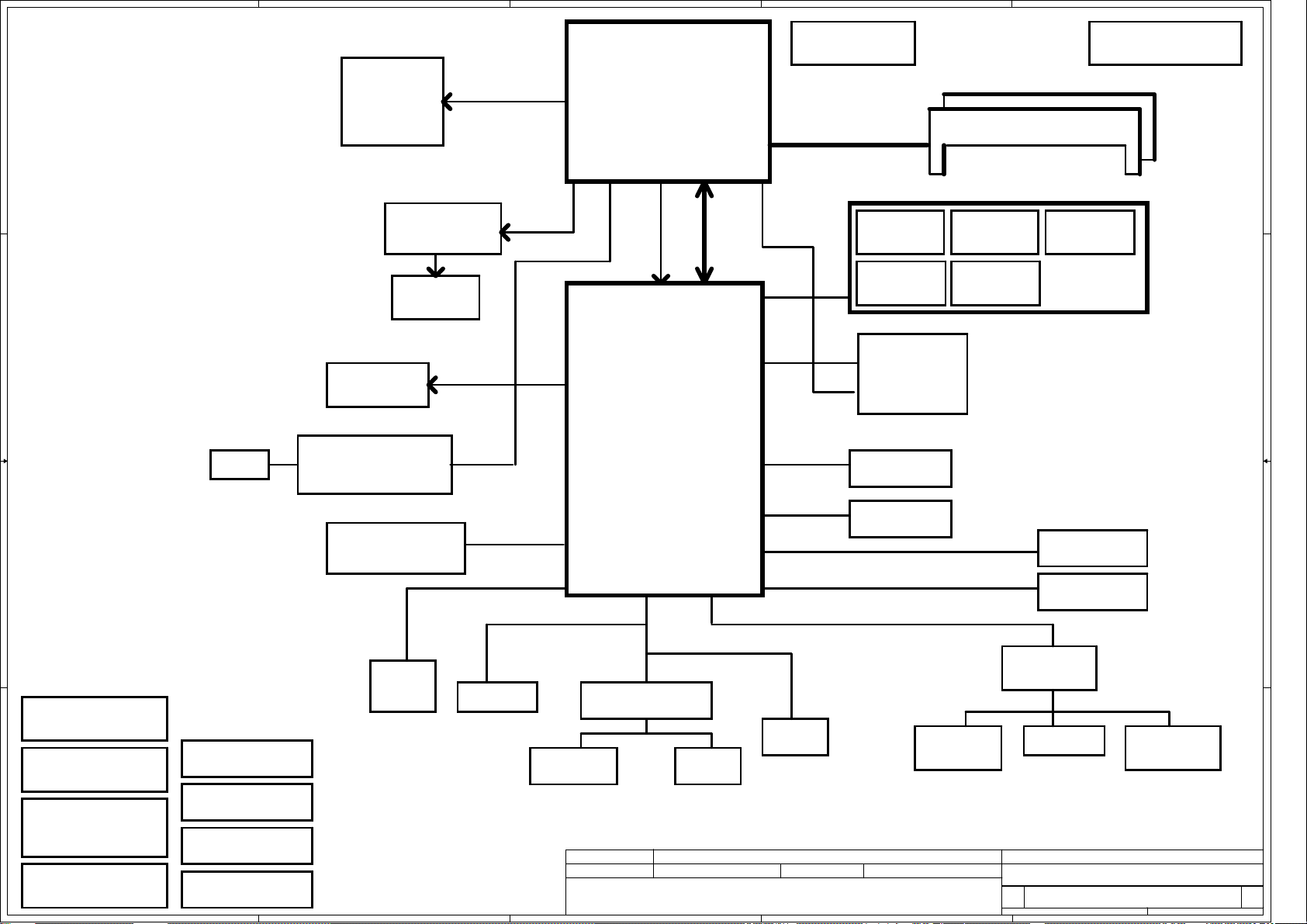

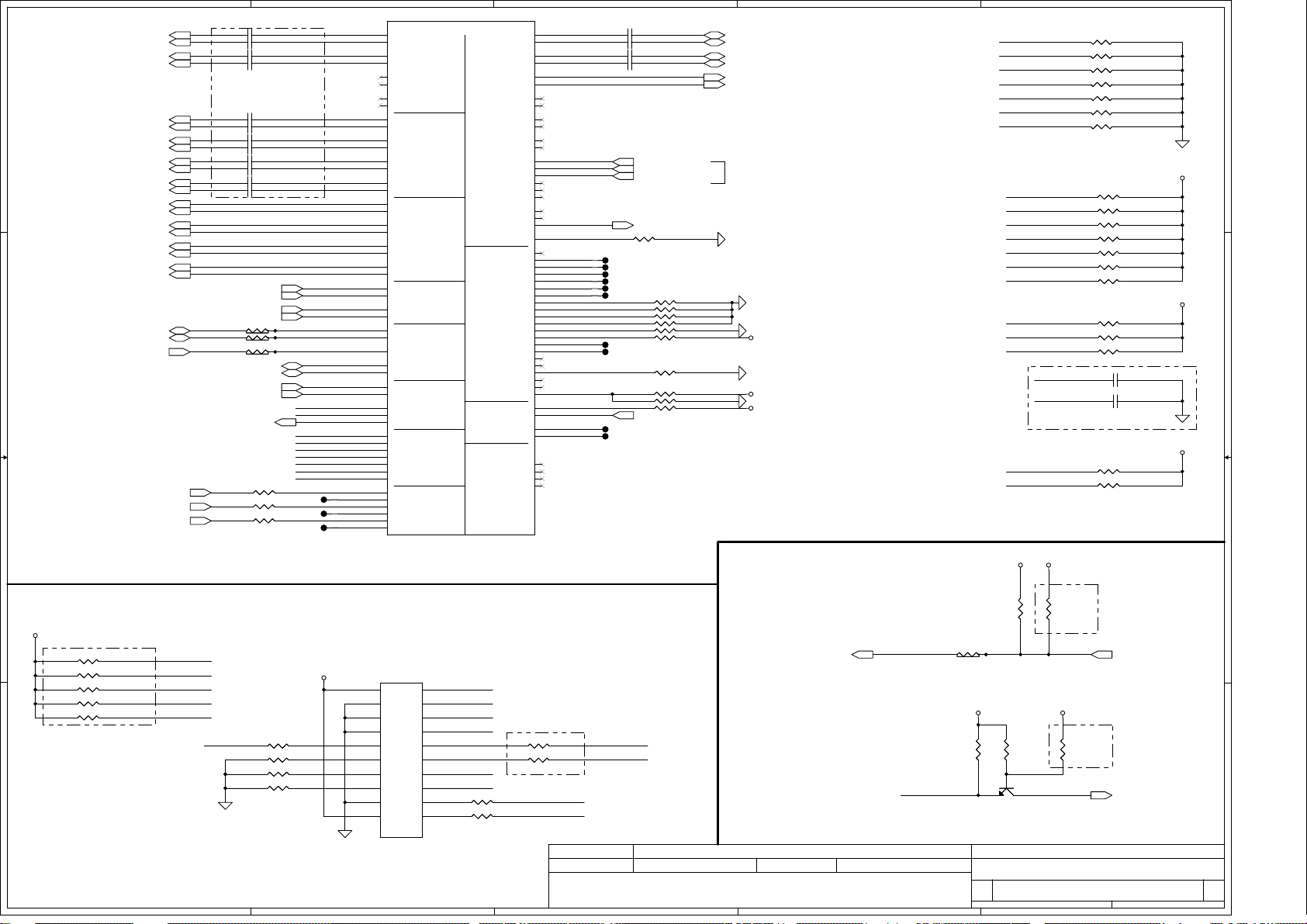

QMLE4/5

2 2

Eureka UMA

LA-8864P SchematicREV 0.3

3 3

4 4

AMD Trinity FS1r2 APU / Hudson M3 FCH

2012-03-14 Rev 0.3

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/11/21 2011/12/11

2011/11/21 2011/12/11

2011/11/21 2011/12/11

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB LA-8864

SCHEMATIC,MB LA-8864

SCHEMATIC,MB LA-8864

4019IS

4019IS

4019IS

140Monday, March 26, 2012

140Monday, March 26, 2012

140Monday, March 26, 2012

E

A

A

A

of

of

of

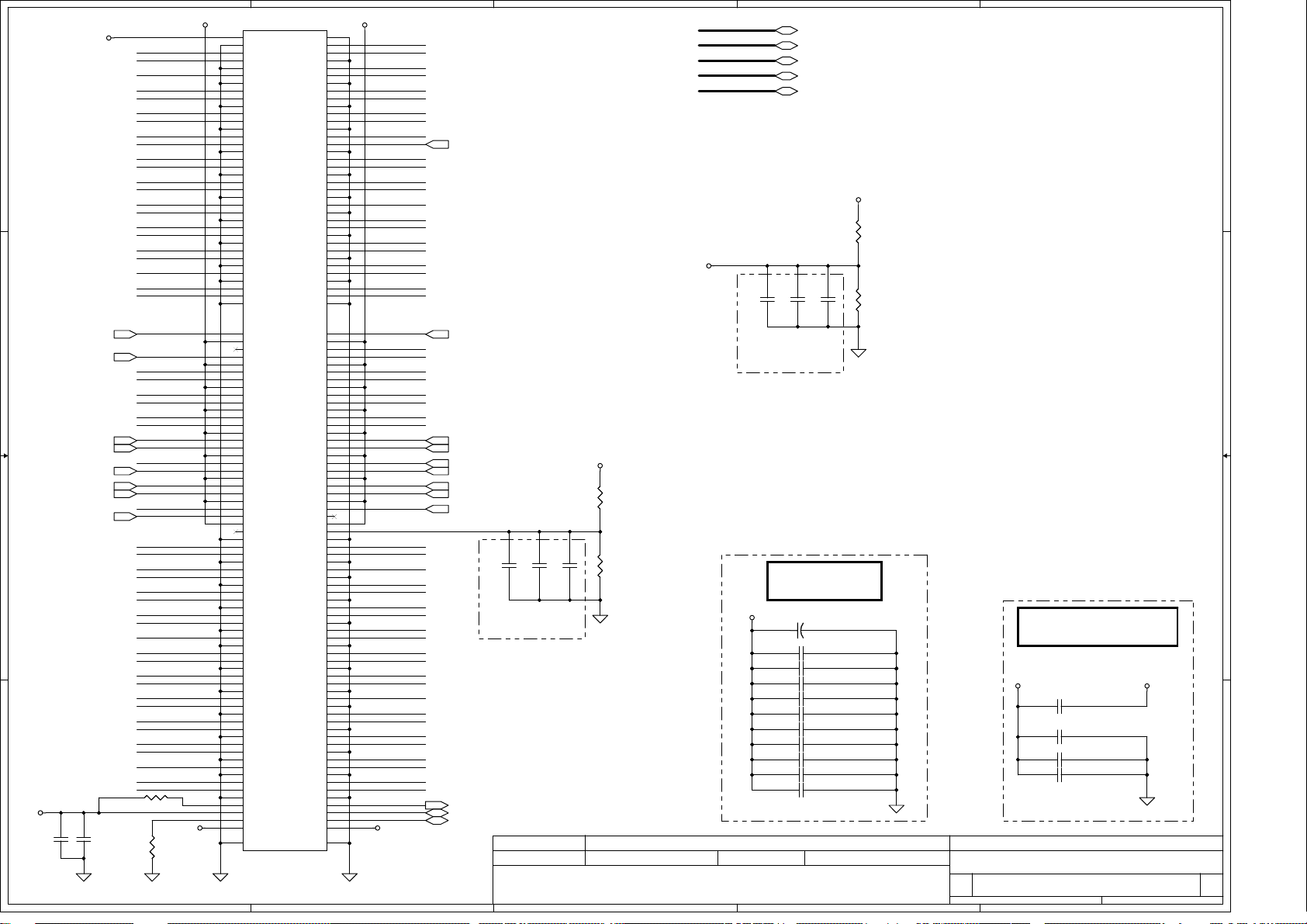

Page 2

A

B

C

D

E

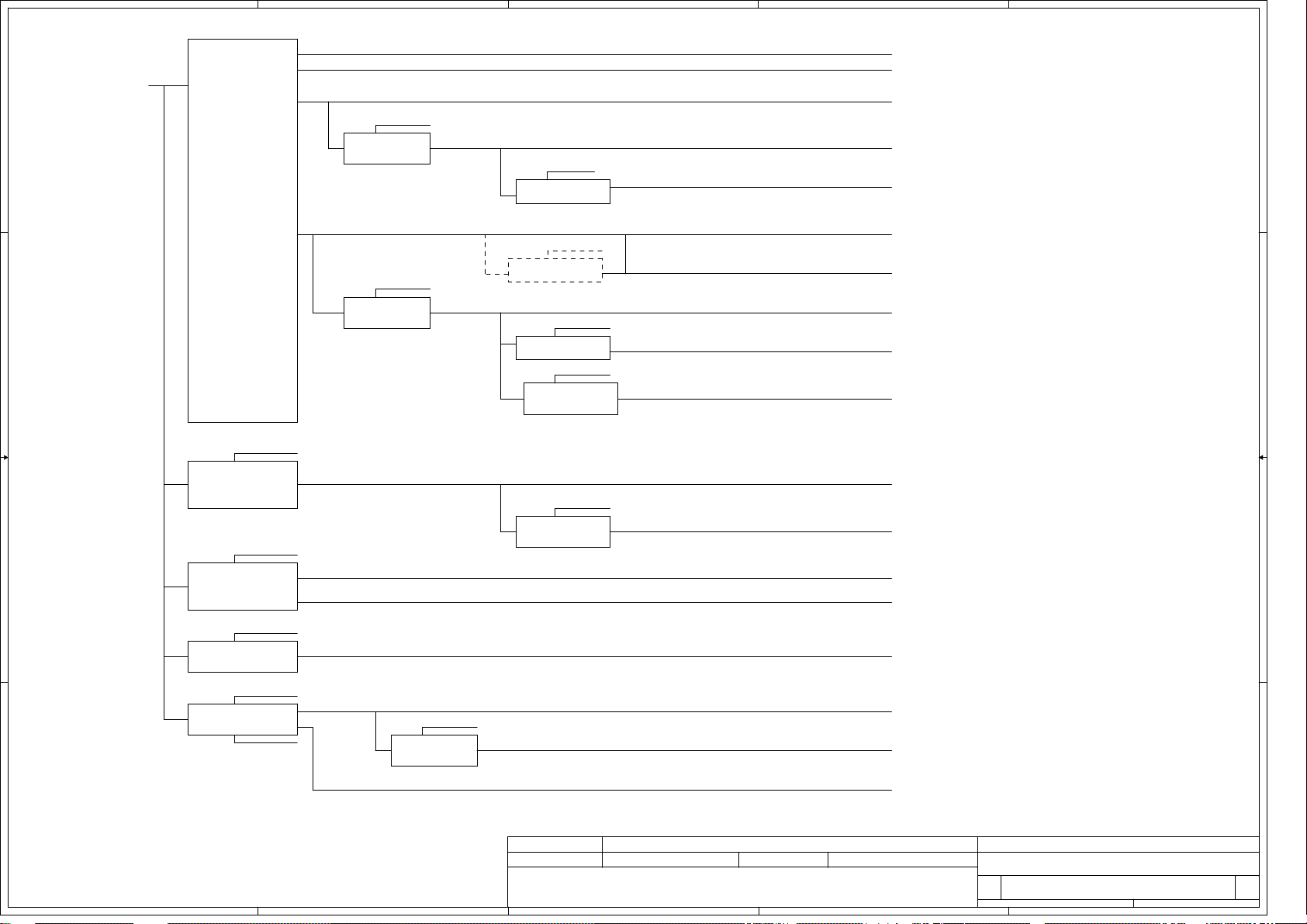

RPM Fan Control

AMD APU

HDMI Conn.

1 1

page 20

DP2 (X4)

LVDS Translator

RTD2136S

page 17

LVDS Conn.

page 18

2 2

CRT

page 19

FS1r2 Processor

Trinity uPGA-722

page 5,6,7,8,9

DP0

(X2)

PCIe X1

1.2V 5GT/s

35mm*35mm

DP1

(X4)

UMI X4

2.5GT/s

Memory BUS(DDRIII)

Dual Channel

1.5V DDRIII 1333/1600 MT/s

PCIe X1

1.2V 5GT/s

USB2.0

5V 480MHz

USB2.0

5V 480MHz

page 5

200pin DDRIII-SO-DIMM X2

BANK 0, 1, 2, 3

Right USB2.0 Right USB2.0

USB port 0

page 21

Left USB 3.0

USB port 10

page 24

USB port 1

page 21

Left USB 3.0

USB port 11

page 24

PCIeMini Card

WLAN + BT

USB port 3

APU PCIe port 1

page 22

GCLK

SLG3NB238VTR

page 10,11

Int. Camera

USB port 4

page 18

page 22

AMD FCH

RJ45

page 23

3 3

RTL8111E 1G

APU PCIe port 0

Cardreader Conn.

RTS5129

page 23

USB port 2

page 26

USB2.0

5V 480MHz

SPI Bus

3.3V 33 MHz

RTL8105E 10/100M

Hudson M3

FCBGA-656

24.5mm*24.5mm

page 12,13,14,15,16

LPC Bus

3.3V 33 MHz

HD Audio

SATA port 0

5V 6GHz(600MB/s)

SATA port 1

5V 6GHz(600MB/s)

USB 3.0

5GHz

USB 3.0

5GHz

3.3V 24MHz

SATA HDD

SATA port 0

page 21

SATA ODD

SATA port 1

page 21

USB 3.0

USB 3.0

USB3.0 port 0

page 24

USB3.0 port 1

page 24

HDA Codec

SPI ROM

(4MB)

page 14

RTC CKT.

page 12

ODD/B

DC/DC Interface CKT.

page 30

4 4

Power Circuit DC/DC

page 31,32,33,34,35

36,37,38,39

LS-8862P

Touchpad/B

LS-8863P

CR & Audio/B

LS-8864P

Power On/Off CKT.

page 29

A

USB & PWR/B

LS-8865P

page 21

page 29

page 40

page 31

B

Debug Port

page 28

ENE KB9012

Touch Pad

page 29

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

page 27

TPM 1.2

page 26

Int.KBD

page 28

Compal Secret Data

Compal Secret Data

2011/11/21 2011/12/11

2011/11/21 2011/12/11

2011/11/21 2011/12/11

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

MIC Conn

page 18

ALC259

page 25

SPK ConnInt.

page 25

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB LA-8864

SCHEMATIC,MB LA-8864

SCHEMATIC,MB LA-8864

4019IS

4019IS

4019IS

JCRIO

(HP & MIC)

page 26

240Monday, March 26, 2012

240Monday, March 26, 2012

240Monday, March 26, 2012

E

of

of

of

A

A

A

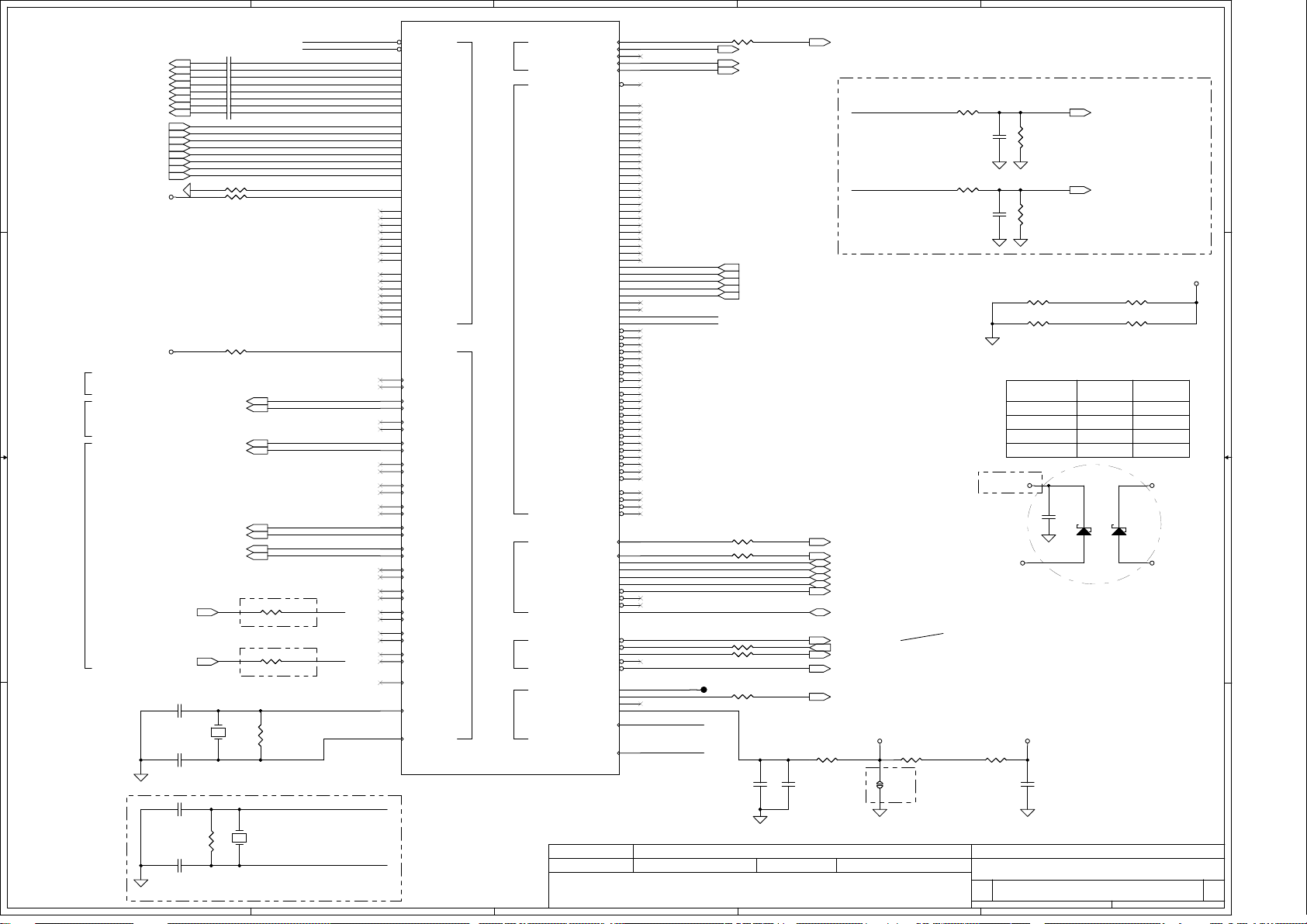

Page 3

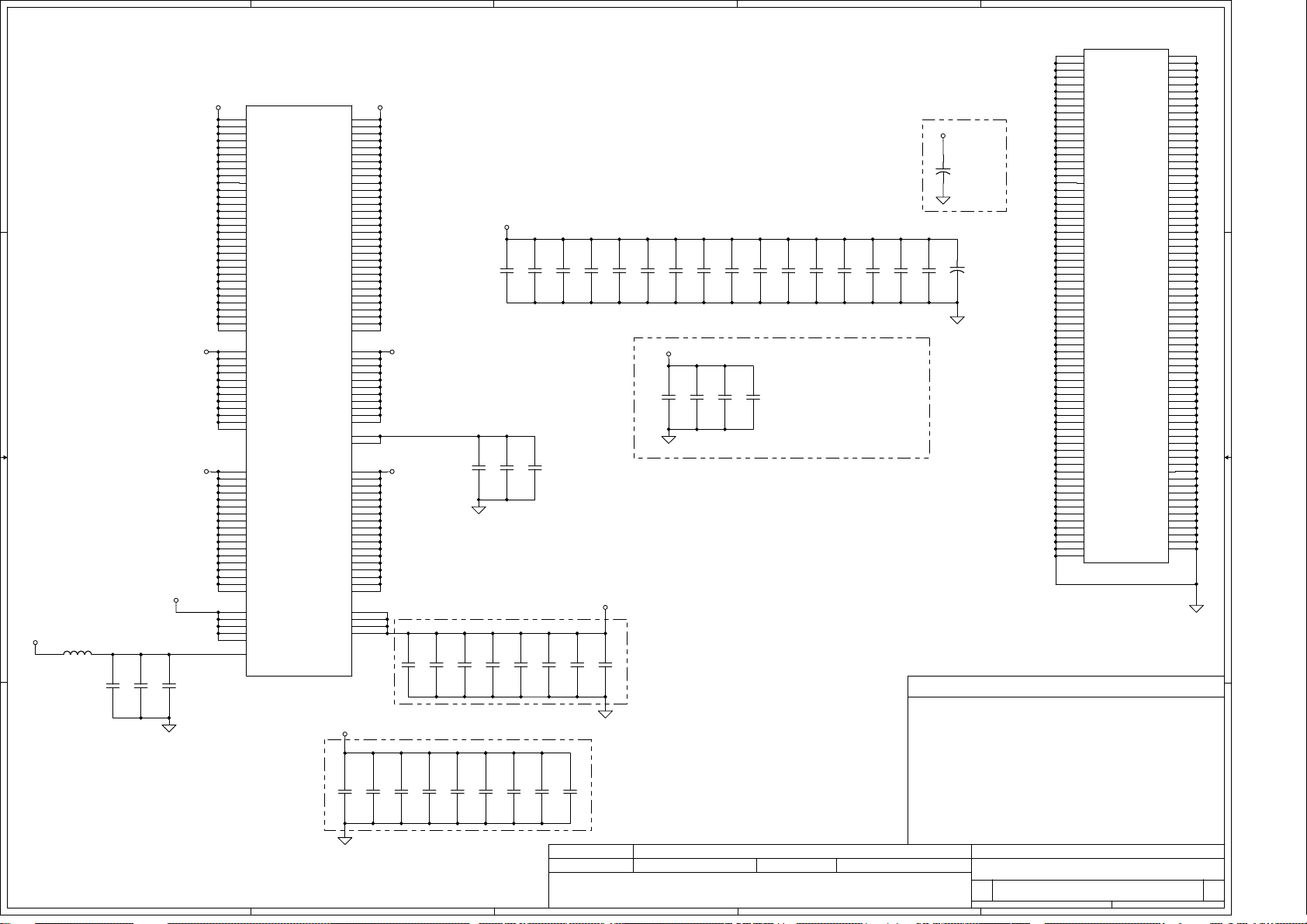

5

4

3

2

1

DESIGN CURRENT 0.1A

DESIGN CURRENT 0.1A

+3VL

+5VL

B+

Ipeak=5A, Imax=3.5A, Iocp min=7.9A

D D

SUSP

N-CHANNEL

SI4800

ODD_PWR

P-CHANNEL

AO-3413

DESIGN CURRENT 7A

DESIGN CURRENT 6A

DESIGN CURRENT 1.6A

+5VALW

+5VS

+5VS_ODD

RT8205LZQW

Ipeak=5A, Imax=3.5A, Iocp min=7.7A

WOL_EN#

P-CHANNEL

SUSP

AO-3413

N-CHANNEL

SI4800

C C

LCD_ENVDD

P-CHANNEL

AO-3413

+3VS

LDO

APL5508-25DC

FCH_PWR_EN

SY8036LDBC

Ipeak=5.3A, Imax=3.71A, Iocp min=6.814A

SUSP

N-CHANNEL

VR_ON

B B

ISL6277HRTZ-T

Ipeak=54A, Imax=36A, Iocp min=65A

Ipeak=27.5A, Imax=22A, Iocp min=35A

FDS6676AS

DESIGN CURRENT 5A

DESIGN CURRENT 330mA

DESIGN CURRENT 4A

DESIGN CURRENT 1.5A

DESIGN CURRENT 1A

DESIGN CURRENT 4A

DESIGN CURRENT 4A

DESIGN CURRENT 36A

DESIGN CURRENT 25A

+3VALW

+3V_LAN

+3VS

+LCD_VDD

+2.5VS

+1.1VALW

+1.1VS

+APU_CORE

+APU_CORE_NB

VR_ON

TPS51212DSCR

Ipeak=6.5A, Imax=4.55A, Iocp min=8.553A

DESIGN CURRENT 8.5A

+1.2VS

SYSON

Ipeak=20A, Imax=11.2A, Iocp min=24.136A

RT8207MZQW

SUSP#

A A

5

4

SUSP

N-CHANNEL

FDS6676AS

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DESIGN CURRENT 12A

DESIGN CURRENT 1A

DESIGN CURRENT 1A

Compal Secret Data

Compal Secret Data

2011/11/21 2011/12/11

2011/11/21 2011/12/11

2011/11/21 2011/12/11

3

Compal Secret Data

+1.5V

+1.5VS

+0.75VS

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

SCHEMATIC,MB LA-8864

SCHEMATIC,MB LA-8864

SCHEMATIC,MB LA-8864

4019IS

4019IS

4019IS

340Monday, March 26, 2012

340Monday, March 26, 2012

340Monday, March 26, 2012

1

A

A

A

of

of

of

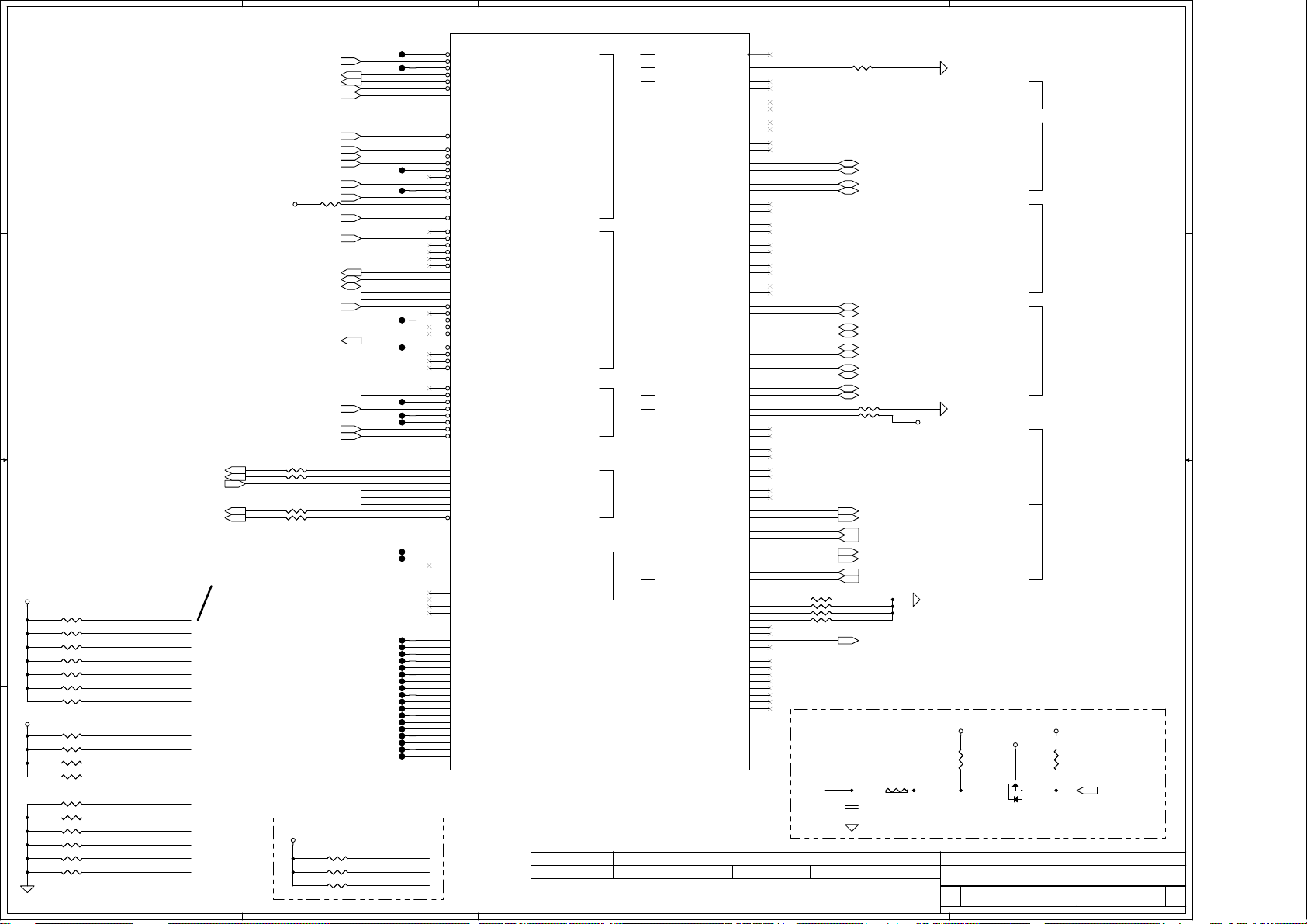

Page 4

A

B

C

D

E

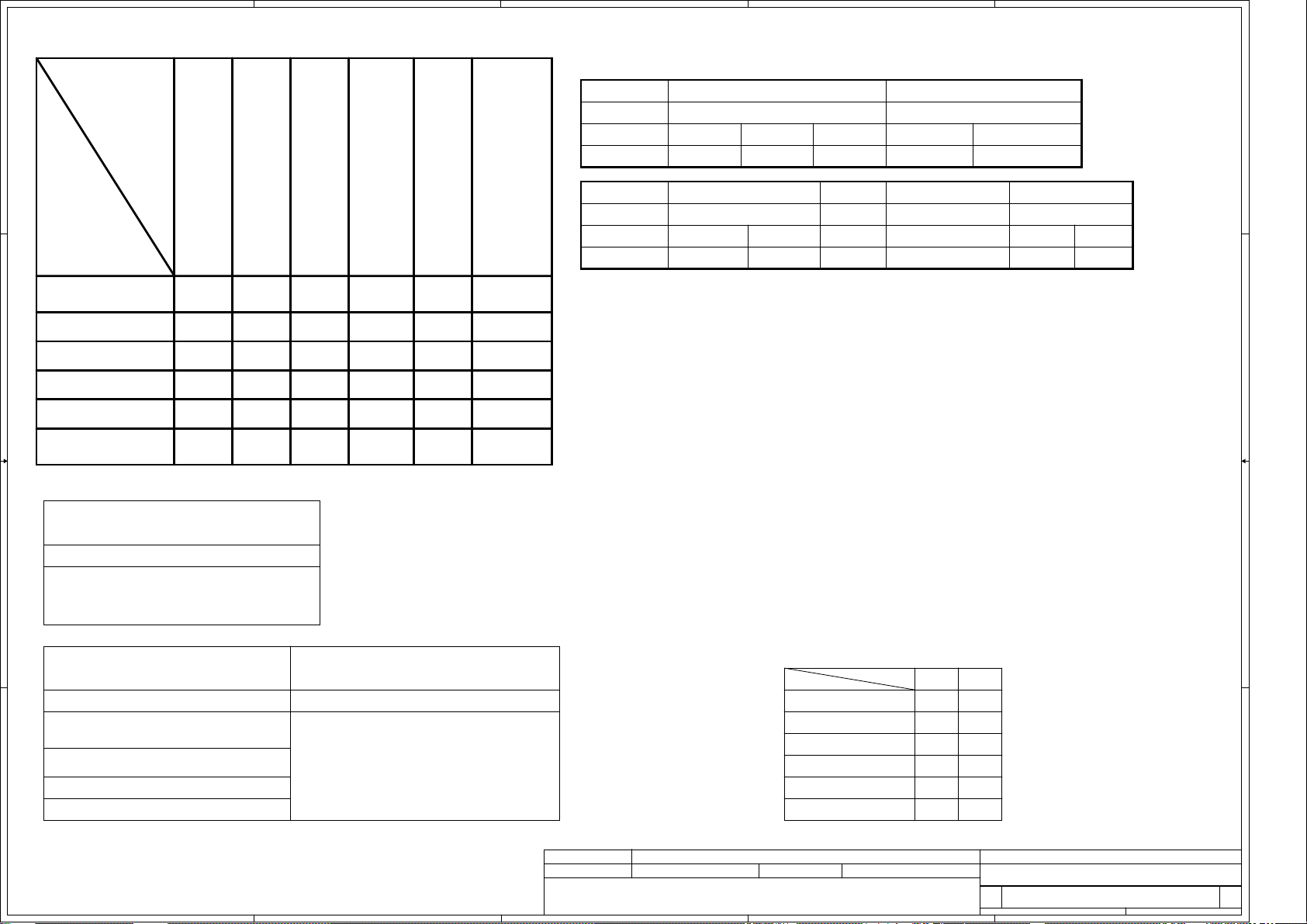

Voltage Rails

State

S0

S1

S3

S5 S4/AC

power

plane

1 1

2 2

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

( O MEANS ON X MEANS OFF )

+RTCVCC

O

O

O

O

O

O

B+

O

O

O

O

O

X

VL

+3VL

O

O

O

O

O

X

+5VALW

+3VALW

+1.1VALW

+VSB

O

O

O

O

X

X

+1.5V

+5VS

+3VS

+2.5VS

+1.5VS

+1.2VS

+1.1VS

+0.75VS

+APU_CORE

+APU_CORE_NB

OO

OO

O

X

XX

X

X

XX

BTO Option Table

Function

description

explain

BTO

Function

description

explain

BTO

R1

HUDM3R1@

10/100M GIGA

8105ELDO@

FCH

Hudson-M3

R3

HUDM3R3@

LAN

LAN

8111FVB@

UNBW

HUDM3UNBW@

Camera

Camera

Camera

CAM@

Clock

Clock

Green Clock

GCLK@ NOGCLK@

Internal Analog MIC

Internal Analog MIC

Internal Analog MIC

AMIC@

No Green Clock

TPM

TPM

9635 9655

TPM9635@

TPM9655@

FCH SM Bus Address (SCL0/SDA0)

HEX

Power

3 3

+3VS

+3VS

+3VS

Device

DDR SO-DIMM 0

DDR SO-DIMM 1

WLAN

EC SM Bus1 Address

Power

+3VL

+3VL

Device Address

Charger 12 H 0001 0010 b

HEX

16 H

EC SM Bus2 Address

4 4

+3VL

DevicePower

SB-TSI

A

HEX Address

98 H

Address

1010 000X bA0 H

1010 001X bA2 H

0001 0110 bSmart Battery

1001 1001 b

+3VS

EC SM Bus3 Address

HEX AddressDevicePower

94 H

1001 0100 bLVDS Translator

B

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

G3 LOW LOW

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/11/21 2011/12/11

2011/11/21 2011/12/11

2011/11/21 2011/12/11

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

SIGNAL

D

SLP_S3#

HIGH HIGH

LOW

LOW

SLP_S5#

HIGHHIGH

HIGH

HIGH

LOWLOW

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB LA-8864

SCHEMATIC,MB LA-8864

SCHEMATIC,MB LA-8864

4019IS

4019IS

4019IS

440Monday, March 26, 2012

440Monday, March 26, 2012

440Monday, March 26, 2012

E

A

A

A

of

of

of

Page 5

A

JAPUA

JAPUA

AB8

AB7

AA9

AA8

AA5

1 1

LAN

WLAN

2 2

PCIE_FRX_C_LANTX_P0<23>

PCIE_FRX_C_LANTX_N0<23> PCIE_FTX_C_LANRX_N0 <23>

PCIE_FRX_WLANTX_P1<22>

PCIE_FRX_WLANTX_N1<22>

UMI_MTX_C_FRX_P0<12>

UMI_MTX_C_FRX_N0<12>

UMI_MTX_C_FRX_P1<12>

UMI_MTX_C_FRX_N1<12>

UMI_MTX_C_FRX_P2<12>

UMI_MTX_C_FRX_N2<12>

UMI_MTX_C_FRX_P3<12>

UMI_MTX_C_FRX_N3<12>

+1.2VS

PCIE_FRX_C_LANTX_P0

PCIE_FRX_C_LANTX_N0

PCIE_FRX_WLANTX_P1

PCIE_FRX_WLANTX_N1

UMI_MTX_C_FRX_P0

UMI_MTX_C_FRX_N0

UMI_MTX_C_FRX_P1

UMI_MTX_C_FRX_N1

UMI_MTX_C_FRX_P2

UMI_MTX_C_FRX_N2

UMI_MTX_C_FRX_P3

UMI_MTX_C_FRX_N3

1 2

R1 196_0402_1%R1 196_0402_1%

AA6

Y8

Y7

W9

W8

W5

W6

V8

V7

U9

U8

U5

U6

T8

T7

R9

R8

R5

R6

P8

P7

N9

N8

N5

N6

M8

M7

AE5

AE6

AD8

AD7

AC9

AC8

AC5

AC6

AG8

AG9

AG6

AG5

AF7

AF8

AE8

AE9

P_ZVDDP P_ZVSS

AG11

LOTES_ACA-ZIF-109-P12-A_FS1R2 @

LOTES_ACA-ZIF-109-P12-A_FS1R2 @

P_GFX_RXP0

P_GFX_RXN0

P_GFX_RXP1

P_GFX_RXN1

P_GFX_RXP2

P_GFX_RXN2

P_GFX_RXP3

P_GFX_RXN3

P_GFX_RXP4

P_GFX_RXN4

P_GFX_RXP5

P_GFX_RXN5

P_GFX_RXP6

P_GFX_RXN6

P_GFX_RXP7

P_GFX_RXN7

P_GFX_RXP8

P_GFX_RXN8

P_GFX_RXP9

P_GFX_RXN9

P_GFX_RXP10

P_GFX_RXN10

P_GFX_RXP11

P_GFX_RXN11

P_GFX_RXP12

P_GFX_RXN12

P_GFX_RXP13

P_GFX_RXN13

P_GFX_RXP14

P_GFX_RXN14

P_GFX_RXP15

P_GFX_RXN15

P_GPP_RXP0

P_GPP_RXN0

P_GPP_RXP1

P_GPP_RXN1

P_GPP_RXP2

P_GPP_RXN2

P_GPP_RXP3

P_GPP_RXN3

P_UMI_RXP0

P_UMI_RXN0

P_UMI_RXP1

P_UMI_RXN1

P_UMI_RXP2

P_UMI_RXN2

P_UMI_RXP3

P_UMI_RXN3

P_ZVDDP

PCI EXPRESS

PCI EXPRESS

GPP GRAPHICS

GPP GRAPHICS

UMI

UMI

B

P_GFX_TXP0

P_GFX_TXN0

P_GFX_TXP1

P_GFX_TXN1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

P_GFX_TXP4

P_GFX_TXN4

P_GFX_TXP5

P_GFX_TXN5

P_GFX_TXP6

P_GFX_TXN6

P_GFX_TXP7

P_GFX_TXN7

P_GFX_TXP8

P_GFX_TXN8

P_GFX_TXP9

P_GFX_TXN9

P_GFX_TXP10

P_GFX_TXN10

P_GFX_TXP11

P_GFX_TXN11

P_GFX_TXP12

P_GFX_TXN12

P_GFX_TXP13

P_GFX_TXN13

P_GFX_TXP14

P_GFX_TXN14

P_GFX_TXP15

P_GFX_TXN15

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_UMI_TXP0

P_UMI_TXN0

P_UMI_TXP1

P_UMI_TXN1

P_UMI_TXP2

P_UMI_TXN2

P_UMI_TXP3

P_UMI_TXN3

P_ZVSS

AB2

AB1

AA3

AA2

Y5

Y4

Y2

Y1

W3

W2

V5

V4

V2

V1

U3

U2

T5

T4

T2

T1

R3

R2

P5

P4

P2

P1

N3

N2

M5

M4

M2

M1

PCIE_FTX_LANRX_P0

AD5

PCIE_FTX_LANRX_N0

AD4

PCIE_FTX_WLANRX_P1

AD2

PCIE_FTX_WLANRX_N1

AD1

AC3

AC2

AB5

AB4

UMI_FTX_MRX_P0

AG2

UMI_FTX_MRX_N0

AG3

UMI_FTX_MRX_P1

AF4

UMI_FTX_MRX_N1

AF5

UMI_FTX_MRX_P2

AF1

UMI_FTX_MRX_N2

AF2

UMI_FTX_MRX_P3

AE2

UMI_FTX_MRX_N3

AE3

AH11

C50 0.1U_0402_16V7KC50 0.1U_0402_16V7K

C55 0.1U_0402_16V7KC55 0.1U_0402_16V7K

C51 0.1U_0402_16V7KC51 0.1U_0402_16V7K

C54 0.1U_0402_16V7KC54 0.1U_0402_16V7K

C59 0.1U_0402_16V7KC59 0.1U_0402_16V7K

C60 0.1U_0402_16V7KC60 0.1U_0402_16V7K

C61 0.1U_0402_16V7KC61 0.1U_0402_16V7K

C62 0.1U_0402_16V7KC62 0.1U_0402_16V7K

C122 0.1U_0402_16V7KC122 0.1U_0402_16V7K

C123 0.1U_0402_16V7KC123 0.1U_0402_16V7K

C120 0.1U_0402_16V7KC120 0.1U_0402_16V7K

C121 0.1U_0402_16V7KC121 0.1U_0402_16V7K

1 2

R2 196_0402_1%R2 196_0402_1%

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

C

PCIE_FTX_C_LANRX_P0 <23>

PCIE_FTX_C_WLANRX_P1 <22>

PCIE_FTX_C_WLANRX_N1 <22>

UMI_FTX_C_MRX_P0 <12>

UMI_FTX_C_MRX_N0 <12>

UMI_FTX_C_MRX_P1 <12>

UMI_FTX_C_MRX_N1 <12>

UMI_FTX_C_MRX_P2 <12>

UMI_FTX_C_MRX_N2 <12>

UMI_FTX_C_MRX_P3 <12>

UMI_FTX_C_MRX_N3 <12>

LAN

WLAN

D

E

3 3

FAN Control Circuit

+5VS

1A

C13

C13

10U_0603_6.3V6M

10U_0603_6.3V6M

U2

U2

1

EN

2

EN_DFAN1<27>

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/11/21 2011/12/11

2011/11/21 2011/12/11

2011/11/21 2011/12/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

+FAN

10mil

Deciphered Date

Deciphered Date

Deciphered Date

3

4

1

C17

C17

APL5607KI-TRG_SO8

APL5607KI-TRG_SO8

10U_0603_6.3V6M

10U_0603_6.3V6M

2

D

VIN

VOUT

VSET

GND

GND

GND

GND

8

7

6

5

+FAN

2

2

C15

C15

1000P_0402_50V7K

1000P_0402_50V7K

@

@

1

1

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB LA-8864

SCHEMATIC,MB LA-8864

SCHEMATIC,MB LA-8864

1

2

3

4

5

ACES_85204-0300N

ACES_85204-0300N

R59 10K_0402_5%R59 10K_0402_5%

1

C14

C14

0.01U_0402_25V7K

0.01U_0402_25V7K

@

@

2

4019IS

4019IS

4019IS

E

JFAN

1

2

3

GND

GND

12

@JFAN

@

+3VS

FAN_SPEED1 <27>

540Monday, March 26, 2012

540Monday, March 26, 2012

540Monday, March 26, 2012

A

A

A

of

of

of

Page 6

A

B

C

D

E

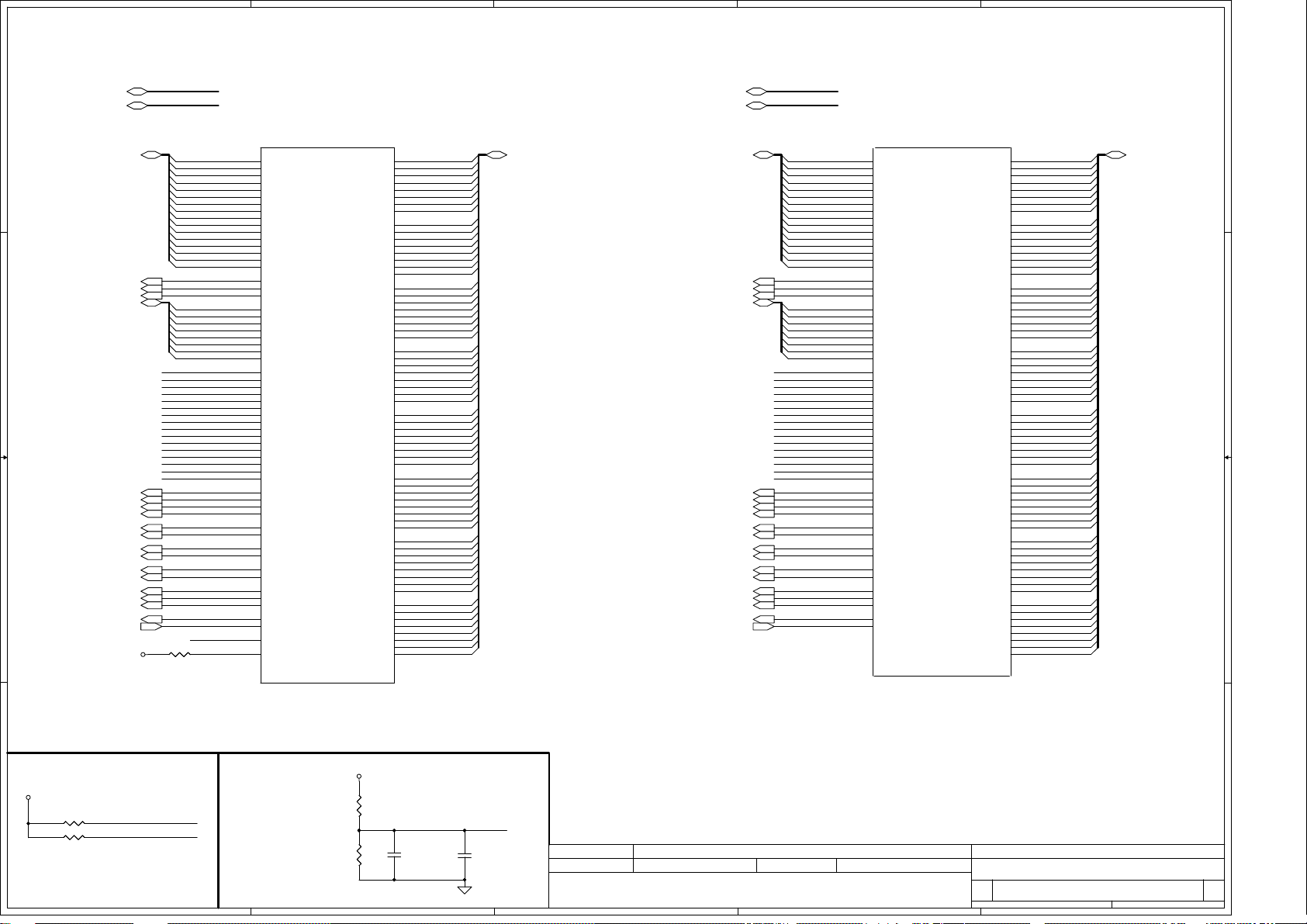

DDR_A_DQS[0..7]<10>

DDR_A_DQS#[0..7]<10>

1 1

JAPUB

JAPUB

MEMORY CHANNEL A

DDR_A_MA[0..15]<10>

DDR_A_BS0<10>

DDR_A_BS1<10>

DDR_A_BS2<10>

DDR_A_DM[0..7]<10>

2 2

DDR_A_CLK0<10>

DDR_A_CLK0#<10>

DDR_A_CLK1<10>

DDR_A_CLK1#<10>

DDR_A_CKE0<10>

DDR_A_CKE1<10>

DDR_A_ODT0<10>

DDR_A_ODT1<10>

3 3

DDR_A_SCS0#<10>

DDR_A_SCS1#<10>

DDR_A_RAS#<10>

DDR_A_CAS#<10>

DDR_A_WE#<10>

MEM_MA_RST#<10>

MEM_MA_EVENT#<10>

+1.5V

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DQS7

DDR_A_DQS#7

DDR_A_CLK0

DDR_A_CLK0#

DDR_A_CLK1

DDR_A_CLK1#

DDR_A_CKE0

DDR_A_CKE1

DDR_A_ODT0

DDR_A_ODT1

DDR_A_SCS0#

DDR_A_SCS1#

DDR_A_RAS#

DDR_A_CAS#

MEM_MA_RST#

MEM_MA_EVENT#

15mil

+MEM_VREF

M_ZVDDIO

1 2

R60 39.2_0402_1%R60 39.2_0402_1%

M21

M22

AA25

AD27

AC23

AD19

AC15

AE26

AD26

AB22

AA22

AB18

AA18

AA14

AA15

AA27

AA26

W24

W23

W20

W21

U20

R20

R21

P22

P21

N24

N23

N20

N21

U23

L24

L21

L20

U24

U21

L23

E14

J17

E21

F25

G14

H14

G18

H18

J21

H21

E27

E26

T21

T22

R23

R24

H28

H27

Y25

V22

V21

H25

T24

MEMORY CHANNEL A

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

MA_BANK0

MA_BANK1

MA_BANK2

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

MA_CLK_H0

MA_CLK_L0

MA_CLK_H1

MA_CLK_L1

MA_CKE0

MA_CKE1

MA_ODT0

MA_ODT1

MA_CS_L0

MA_CS_L1

MA_RAS_L

MA_CAS_L

MA_WE_L

MA_RESET_L

MA_EVENT_L

M_VREF

M_ZVDDIO

LOTES_ACA-ZIF-109-P12-A_FS1R2 @

LOTES_ACA-ZIF-109-P12-A_FS1R2 @

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

E13

J13

H15

J15

H13

F13

F15

E15

H17

F17

E19

J19

G16

H16

H19

F19

H20

F21

J23

H23

G20

E20

G22

H22

G24

E25

G27

G26

F23

H24

E28

F27

AB28

AC27

AD25

AA24

AE28

AD28

AB26

AC25

Y23

AA23

Y21

AA20

AB24

AD24

AA21

AC21

AA19

AC19

AC17

AA17

AB20

Y19

AD18

AD17

AA16

Y15

AA13

AC13

Y17

AB16

AB14

Y13

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56DDR_A_WE#

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_A_D[0..63] <10>

DDR_B_DQS[0..7]<11>

DDR_B_DQS#[0..7]<11>

JAPUC

JAPUC

MEMORY CHANNEL B

DDR_B_MA[0..15]<11>

DDR_B_BS0<11>

DDR_B_BS1<11>

DDR_B_BS2<11>

DDR_B_DM[0..7]<11>

DDR_B_CLK0<11>

DDR_B_CLK0#<11>

DDR_B_CLK1<11>

DDR_B_CLK1#<11>

DDR_B_CKE0<11>

DDR_B_CKE1<11>

DDR_B_ODT0<11>

DDR_B_ODT1<11>

DDR_B_SCS0#<11>

DDR_B_SCS1#<11>

DDR_B_RAS#<11>

DDR_B_CAS#<11>

DDR_B_WE#<11>

MEM_MB_RST#<11>

MEM_MB_EVENT#<11>

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

DDR_B_BS0

DDR_B_BS1

DDR_B_BS2

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS0

DDR_B_DQS#0

DDR_B_DQS1

DDR_B_DQS#1

DDR_B_DQS2

DDR_B_DQS#2

DDR_B_DQS3

DDR_B_DQS#3

DDR_B_DQS4

DDR_B_DQS#4

DDR_B_DQS5

DDR_B_DQS#5

DDR_B_DQS6

DDR_B_DQS#6

DDR_B_DQS7

DDR_B_DQS#7

DDR_B_CLK0

DDR_B_CLK0#

DDR_B_CLK1

DDR_B_CLK1#

DDR_B_CKE0

DDR_B_CKE1

DDR_B_ODT0

DDR_B_ODT1

DDR_B_SCS0#

DDR_B_SCS1#

DDR_B_RAS#

DDR_B_CAS#

DDR_B_WE#

MEM_MB_RST#

MEM_MB_EVENT#

M28

M27

M24

M25

W26

AF25

AG22

AH18

AD14

AG24

AG25

AG21

AF21

AG17

AG18

AH14

AG14

W27

T27

P24

P25

N27

N26

L26

U26

L27

K27

K25

K24

U27

T28

K28

D14

A18

A22

C25

C15

B15

E18

D18

E22

D22

B26

A26

R26

R27

P27

P28

J26

J27

Y28

V25

Y27

V24

V27

V28

J25

T25

MEMORY CHANNEL B

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

MB_CLK_H0

MB_CLK_L0

MB_CLK_H1

MB_CLK_L1

MB_CKE0

MB_CKE1

MB_ODT0

MB_ODT1

MB_CS_L0

MB_CS_L1

MB_RAS_L

MB_CAS_L

MB_WE_L

MB_RESET_L

MB_EVENT_L

LOTES_ACA-ZIF-109-P12-A_FS1R2 @

LOTES_ACA-ZIF-109-P12-A_FS1R2 @

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

A14

B14

D16

E16

B13

C13

B16

A16

C17

B18

B20

A20

E17

B17

B19

C19

C21

B22

C23

A24

D20

B21

E23

B23

E24

B25

B27

D28

B24

D24

D26

C27

AG26

AH26

AF23

AG23

AG27

AF27

AH24

AE24

AE22

AH22

AE20

AH20

AD23

AD22

AD21

AD20

AF19

AE18

AE16

AH16

AG20

AG19

AF17

AD16

AG15

AD15

AG13

AD13

AG16

AF15

AE14

AF13

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

DDR_B_D[0..63] <11>

EVENT# pull high 0.75V Reference Voltage

+1.5V

4 4

R15 1K_0402_5%R15 1K_0402_5%

1 2

R61 1K_0402_5%R61 1K_0402_5%

1 2

MEM_MA_EVENT#

MEM_MB_EVENT#

A

R64

R64

1K_0402_1%

1K_0402_1%

R65

R65

1K_0402_1%

1K_0402_1%

+1.5V

1 2

1 2

B

1

C124

C124

1000P_0402_50V7K

1000P_0402_50V7K

2

15mil

+MEM_VREF

2

C125

C125

0.1U_0402_16V7K

0.1U_0402_16V7K

1

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2010/11/11 2011/11/11

2010/11/11 2011/11/11

2010/11/11 2011/11/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB LA-8864

SCHEMATIC,MB LA-8864

SCHEMATIC,MB LA-8864

4019IS

4019IS

4019IS

640Monday, March 26, 2012

640Monday, March 26, 2012

640Monday, March 26, 2012

E

of

of

of

A

A

A

Page 7

A

Close to APU

C56 0.1U_0402_16V7KC56 0.1U_0402_16V7K

DP0_TXP0_C<17>

LVDS

1 1

CRT

(To FCH)

HDMI

DP0_TXN0_C<17>

DP0_TXP1_C<17>

DP0_TXN1_C<17>

ML_VGA_TXP0<14>

ML_VGA_TXN0<14>

ML_VGA_TXP1<14>

ML_VGA_TXN1<14>

ML_VGA_TXP2<14>

ML_VGA_TXN2<14>

ML_VGA_TXP3<14>

ML_VGA_TXN3<14>

UMA_HDMI_TX2+<20>

UMA_HDMI_TX2-<20>

UMA_HDMI_TX1+<20>

UMA_HDMI_TX1-<20>

UMA_HDMI_TX0+<20>

UMA_HDMI_TX0-<20>

UMA_HDMI_TXC+<20>

UMA_HDMI_TXC-<20>

100MHz (SS)

100MHz (NSS)

APU_SVC<37>

2 2

APU_SVD<37>

APU_SVT<37>

SB-TSI

APU_VDD_RUN_FB_L<37>

APU_VDDNB_SEN<37>

APU_VDD_SEN<37>

3 3

1 2

C48 0.1U_0402_16V7KC48 0.1U_0402_16V7K

1 2

C58 0.1U_0402_16V7KC58 0.1U_0402_16V7K

1 2

C53 0.1U_0402_16V7KC53 0.1U_0402_16V7K

1 2

C63 0.1U_0402_16V7KC63 0.1U_0402_16V7K

1 2

C64 0.1U_0402_16V7KC64 0.1U_0402_16V7K

1 2

C65 0.1U_0402_16V7KC65 0.1U_0402_16V7K

1 2

C66 0.1U_0402_16V7KC66 0.1U_0402_16V7K

1 2

C67 0.1U_0402_16V7KC67 0.1U_0402_16V7K

1 2

C68 0.1U_0402_16V7KC68 0.1U_0402_16V7K

1 2

C69 0.1U_0402_16V7KC69 0.1U_0402_16V7K

1 2

C70 0.1U_0402_16V7KC70 0.1U_0402_16V7K

1 2

APU_CLKP<12>

APU_CLKN<12>

APU_DISP_CLKP<12>

APU_DISP_CLKN<12>

R31 0_0402_5%@R31 0_0402_5%@

1 2

R32 0_0402_5%@R32 0_0402_5%@

1 2

R33 0_0402_5%@R33 0_0402_5%@

1 2

APU_SIC<9>

APU_SID<9>

APU_RST#<12>

APU_PWRGD<12,37>

APU_ALERT#<14>

R212 0_0402_5%R212 0_0402_5%

1 2

R214 0_0402_5%R214 0_0402_5%

1 2

R215 0_0402_5%R215 0_0402_5%

1 2

APU_PROCHOT#

APU_THERMTRIP#

APU_ALERT#

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

T9T9

T10T10

T13T13

UMA_HDMI_TX2+

UMA_HDMI_TX2-

UMA_HDMI_TX1+

UMA_HDMI_TX1-

UMA_HDMI_TX0+

UMA_HDMI_TX0-

UMA_HDMI_TXC+

UMA_HDMI_TXC-

APU_CLKP

APU_CLKN

APU_DISP_CLKP

APU_DISP_CLKN

APU_SVC_R

APU_SVD_R

APU_SVT_R

APU_SIC

APU_SID

APU_RST#

APU_PWRGD

VSS_SENSE

VDDNB_SENSE

VDD_SENSE

DP0_TXP0

DP0_TXN0

DP0_TXN1

DP1_TXP0

DP1_TXN0

DP1_TXP1

DP1_TXN1

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

B

JAPUD

JAPUD

ANALOG/DISPLAY/MISC

ANALOG/DISPLAY/MISC

DP0_TXP0

DP0_TXN0

DP0_TXP1

DP0_TXN1

DP0_TXP2

DP0_TXN2

DP0_TXP3

DP0_TXN3

DP1_TXP0

DP1_TXN0

DP1_TXP1

DP1_TXN1

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

DP2_TXP0

DP2_TXN0

DP2_TXP1

DP2_TXN1

DP2_TXP2

DP2_TXN2

DP2_TXP3

DP2_TXN3

CLKIN_H

CLKIN_L

DISP_CLKIN_H

DISP_CLKIN_L

SVC

SVD

SVT

SIC

SID

RESET_L

PWROK

PROCHOT_L

THERMTRIP_L

ALERT_L

TDI

TDO

TCK

TMS

TRST_L

DBRDY

DBREQ_L

VSS_SENSE

VDDP_SENSE

VDDNB_SENSE

VDDIO_SENSE

VDD_SENSE

VDDR_SENSE

LOTES_ACA-ZIF-109-P12-A_FS1R2 @

LOTES_ACA-ZIF-109-P12-A_FS1R2 @

DISPLAY PORT 0

DISPLAY PORT 0

DISPLAY PORT MISC.

DISPLAY PORT MISC.

DISPLAY PORT 2 DISPLAY PORT 1

DISPLAY PORT 2 DISPLAY PORT 1

TEST

TEST

CTRL SER. CLK

CTRL SER. CLK

JTAG

JTAG

SENSE

SENSE

AE11

AD11

AB11

AA11

AG12

AH12

AF10

AB12

AC10

AE12

AF12

L3

L2

K5

K4

K2

K1

J3

J2

H5

H4

H2

H1

G3

G2

F2

F1

L9

L8

L5

L6

K8

K7

J6

J5

B3

A3

C3

H10

J10

F10

G10

F9

G9

H9

B4

C5

A4

A5

C4

B5

DP0_AUXP

DP0_AUXN

DP1_AUXP

DP1_AUXN

DP2_AUXP

DP2_AUXN

DP3_AUXP

DP3_AUXN

DP4_AUXP

DP4_AUXN

DP5_AUXP

DP5_AUXN

DP0_HPD

DP1_HPD

DP2_HPD

DP3_HPD

DP4_HPD

DP5_HPD

DP_BLON

DP_DIGON

DP_VARY_BL

DP_AUX_ZVSS

TEST10

TEST14

TEST15

TEST16

TEST17

TEST18

TEST19

TEST20

TEST24

TEST25_H

TEST25_L

TEST28_H

TEST28_L

TEST30_H

TEST30_L

TEST31

TEST32_H

TEST32_L

TEST35

DMAACTIVE_L

RSVD

RSVD

TEST6

TEST9

FS1R2

TEST4

TEST5

RSVD1

RSVD2

RSVD3

RSVD4

DP0_AUXP

D1

DP0_AUXN

D2

DP1_AUXP

E1

DP1_AUXN

E2

UMA_HDMI_CLK

D5

UMA_HDMI_DATA

D6

E5

E6

F5

F6

G5

G6

LVDS_HPD

D3

FCH_CRT_HPD

E3

HDMI_HPD

D7

E7

F7

G7

C6

B6

A6

DP_AUX_ZVSS

C1

AD12

M18

N18

F11

G11

H11

J11

APU_TEST18

F12

APU_TEST19

G12

APU_TEST20

J12

APU_TEST24

H12

TEST25_H

AE10

TEST25_L

AD10

L10

M10

P19

R19

APU_TEST31

K22

T19

N19

APU_TEST35

AA12

FS1R2

W10

DMA_ACTIVE#

AC12

P18

R18

Y10

AA10

Y12

K21

C

C47 0.1U_0402_16V7KC47 0.1U_0402_16V7K

1 2

C49 0.1U_0402_16V7KC49 0.1U_0402_16V7K

1 2

C57 0.1U_0402_16V7KC57 0.1U_0402_16V7K

1 2

C52 0.1U_0402_16V7KC52 0.1U_0402_16V7K

1 2

LVDS_HPD <17>

FCH_CRT_HPD <14>

HDMI_HPD <20>

DP_INT_PWM <9>

1 2

R16 150_0402_1%R16 150_0402_1%

T5T5

T6T6

T1T1

T2T2

T3T3

T4T4

R18 1K_0402_5%R18 1K_0402_5%

1 2

R19 1K_0402_5%R19 1K_0402_5%

1 2

R21 1K_0402_5%R21 1K_0402_5%

1 2

R22 1K_0402_5%R22 1K_0402_5%

1 2

R23 510_0402_1%R23 510_0402_1%

1 2

R24 510_0402_1%R24 510_0402_1%

1 2

T7T7

T8T8

R27 39.2_0402_1%R27 39.2_0402_1%

1 2

R28 300_0402_5%R28 300_0402_5%

1 2

R29 300_0402_5%@R29 300_0402_5%@

1 2

R30 10K_0402_5%R30 10K_0402_5%

1 2

DMA_ACTIVE# <12>

T11T11

T12T12

DP0_AUXP_C <17>

DP0_AUXN_C <17>

ML_VGA_AUXP <14>

ML_VGA_AUXN <14>

UMA_HDMI_CLK <20>

UMA_HDMI_DATA <20>

3.3V Tolerance

+1.2VS

Change TEST35 to pull-high

+1.5V

for HDMI issue

+3VALW

D

LVDS

CRT (To FCH)

HDMI

E

DP0_AUXP

DP0_AUXNDP0_TXP1

DP1_AUXP

DP1_AUXN

LVDS_HPD

FCH_CRT_HPD

HDMI_HPD

APU_SVT_R

APU_SVC_R

APU_SVD_RDP_INT_PWM

APU_SIC

APU_SID

APU_ALERT#

DMA_ACTIVE#

DMA_ACTIVE#

APU_RST#

APU_PWRGD

Stuff C126 and C127 for EMI request on DVT

UMA_HDMI_CLK

UMA_HDMI_DATA

Aux signal are re-configured as I2C signals for DDC

APU AUX pin are 3.3V tolerant

+1.5V +1.5VS

R25 1.8K_0402_5%R25 1.8K_0402_5%

R58 1.8K_0402_5%R58 1.8K_0402_5%

R10 1.8K_0402_5%R10 1.8K_0402_5%

R11 1.8K_0402_5%R11 1.8K_0402_5%

R74 100K_0402_5%R74 100K_0402_5%

R75 100K_0402_5%R75 100K_0402_5%

R95 100K_0402_5%R95 100K_0402_5%

R36 1K_0402_5%@R36 1K_0402_5%@

R39 1K_0402_5%@R39 1K_0402_5%@

R41 1K_0402_5%@R41 1K_0402_5%@

R42 1K_0402_5%R42 1K_0402_5%

R44 1K_0402_5%R44 1K_0402_5%

R46 1K_0402_5%R46 1K_0402_5%

R48 1K_0402_5%R48 1K_0402_5%

R57 1K_0402_5%@R57 1K_0402_5%@

R52 300_0402_5%R52 300_0402_5%

R54 300_0402_5%R54 300_0402_5%

APU_RST#

APU_PWRGD

1 2

C126 1000P_0402_50V7KC126 1000P_0402_50V7K

1 2

C127 1000P_0402_50V7KC127 1000P_0402_50V7K

R66 4.7K_0402_5%R66 4.7K_0402_5%

R67 4.7K_0402_5%R67 4.7K_0402_5%

12

12

12

12

12

12

12

+1.5V

12

12

12

12

12

12

12

+1.5VS

12

12

12

+3VS

12

12

R77

R55

R55

1K_0402_5%

+1.5V

Close to JHDT

R97 1K_0402_5%R97 1K_0402_5%

1 2

R100 1K_0402_5%R100 1K_0402_5%

1 2

R110 1K_0402_5%R110 1K_0402_5%

1 2

R116 1K_0402_5%R116 1K_0402_5%

1 2

R117 1K_0402_5%R117 1K_0402_5%

1 2

4 4

APU_TDI

APU_TCK

APU_TMS

APU_TRST#

APU_DBREQ#

@

@

1 2

R121 0_0402_5%

R121 0_0402_5%

@

@

1 2

R122 10K_0402_5%

R122 10K_0402_5%

@

@

1 2

R123 10K_0402_5%

R123 10K_0402_5%

@

@

1 2

R124 10K_0402_5%

R124 10K_0402_5%

A

HDT Debug conn

+1.5V

JHDT

1

1

3

3

5

5

7

7

9

9

11

11

13

13

15

15

17

17

19

19

SAMTE_ASP-136446-07-B

SAMTE_ASP-136446-07-B

B

@JHDT

@

2

4

6

8

10

12

14

16

18

20

2

4

6

8

10

12

14

16

18

20

APU_TCK

APU_TMS

APU_TDI

APU_TDO

APU_PWRGD_RR

APU_RST#_R

APU_DBRDY

APU_DBREQ#

Close to APU side, Debug Stuff

R125 0_0402_5%

R125 0_0402_5%

R127 0_0402_5%

R127 0_0402_5%

@

@

1 2

R118 0_0402_5%

R118 0_0402_5%

@

@

1 2

R119 0_0402_5%

R119 0_0402_5%

@

@

1 2

@

@

1 2

APU_TEST19

APU_TEST18

Security Classification

Security Classification

Security Classification

APU_PWRGDAPU_TRST#

APU_RST#

2011/11/21 2011/12/11

2011/11/21 2011/12/11

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/11/21 2011/12/11

Asserted as an input to force the

processor into the HTC-active state

APU_PROCHOT#

Thermal Shutdown Temperature:

115 degree

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

APU_THERMTRIP#

1K_0402_5%

@

@

1 2

R136 0_0402_5%

R136 0_0402_5%

+1.5V

R68

R68

1K_0402_5%

1K_0402_5%

12

1 2

B

B

2

E

E

3 1

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

R77

1K_0402_5%

1K_0402_5%

@

@

1 2

1 2

H_PROCHOT# <27,37>APU_PROCHOT#<12>

Reserve R77 and R85 for

DeepS3 leakage on DVT

+1.5VS

R69

R69

10K_0402_5%

10K_0402_5%

C

C

12

R85

R85

10K_0402_5%

10K_0402_5%

@

@

Q5

Q5

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SCHEMATIC,MB LA-8864

SCHEMATIC,MB LA-8864

SCHEMATIC,MB LA-8864

4019IS

4019IS

4019IS

H_THERMTRIP# <13>

E

A

A

A

of

of

of

740Monday, March 26, 2012

740Monday, March 26, 2012

740Monday, March 26, 2012

Page 8

A

+APU_CORE

1 1

2 2

3 3

+2.5VS

FBMA-L11-201209-300LMA30T

FBMA-L11-201209-300LMA30T

4 4

L1

L1

1 2

C165

C165

1

2

C170

C170

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

A

+APU_CORE_NB

+1.2VS

C164

C164

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

1

12

2

+1.5V

3300P_0402_50V7K

3300P_0402_50V7K

+VDDA+VDDA

40mil

JAPUE

JAPUE

F8

VDD_1

H6

VDD_2

J1

VDD_3

J14

VDD_4

P6

VDD_5

P10

VDD_6

J16

VDD_7

J18

VDD_8

J9

VDD_9

K19

VDD_10

K3

VDD_11

K17

VDD_12

M3

VDD_13

K6

VDD_14

V10

VDD_15

V18

VDD_16

V3

VDD_17

50A

VDD_18

VDD_19

VDD_20

VDD_21

VDD_22

VDD_23

VDD_24

VDD_25

VDD_26

VDD_27

VDD_28

VDD_29

VDD_30

VDD_31

VDDNB_1

VDDNB_2

VDDNB_3

VDDNB_4

VDDNB_5

VDDNB_6

33A

VDDNB_7

VDDNB_8

VDDNB_9

VDDNB_10

VDDNB_11

VDDNB_12

VDDIO_1

VDDIO_2

VDDIO_3

VDDIO_4

VDDIO_5

VDDIO_6

VDDIO_7

VDDIO_8

VDDIO_9

VDDIO_10

VDDIO_11

3.2A

VDDIO_12

VDDIO_13

VDDIO_14

VDDIO_15

VDDIO_16

VDDIO_17

VDDIO_18

VDDP_1

VDDP_2

VDDP_3

VDDP_4

VDDP_5

VDDA

0.75A

LOTES_ACA-ZIF-109-P12-A_FS1R2

LOTES_ACA-ZIF-109-P12-A_FS1R2

AA28

AB10

F3

L18

V6

W1

T18

Y14

AA1

AB6

AC1

R1

P3

K10

H3

M19

C8

D10

B8

B12

C9

A9

A10

A8

A11

E10

E11

C10

H26

K20

J28

K23

K26

L22

L25

L28

M20

M23

M26

N22

N25

N28

P20

P23

P26

AH6

AH5

AH4

AH3

AH7

VDD_32

VDD_33

VDD_34

VDD_35

VDD_36

VDD_37

VDD_38

VDD_39

VDD_40

VDD_41

VDD_42

VDD_43

VDD_44

VDD_45

VDD_46

VDD_47

VDD_48

VDD_49

VDD_50

VDD_51

VDD_52

VDD_53

VDD_54

VDD_55

VDD_56

VDD_57

VDD_58

VDD_59

VDD_60

VDD_61

VDD_62

VDDNB_13

VDDNB_14

VDDNB_15

VDDNB_16

VDDNB_17

VDDNB_18

VDDNB_19

VDDNB_20

VDDNB_21

VDDNB_22

VDDNB_23

VDDNB_CAP_1

VDDNB_CAP_2

VDDIO_19

VDDIO_20

VDDIO_21

VDDIO_22

VDDIO_23

VDDIO_24

VDDIO_25

VDDIO_26

VDDIO_27

VDDIO_28

VDDIO_29

VDDIO_30

VDDIO_31

VDDIO_32

VDDIO_33

VDDIO_34

VDDIO_35

VDDIO_36

VDDR_1

VDDR_2

VDDR_3

3.5A5A

VDDR_4

C71

C71

+1.2VS

+APU_CORE

R11

T10

H8

G1

U11

W11

W13

W15

W17

W19

AB3

AD3

AD6

AE1

L1

Y6

M6

N11

N1

T3

T6

U19

U1

Y16

Y18

Y3

D4

F4

AF6

AF3

L11

C11

C12

D9

D8

D12

D11

B11

A12

B10

E12

B9

K13

K12

T23

T26

U22

U25

U28

Y26

T20

R28

R25

R22

V20

V23

V26

W22

W25

W28

Y24

G28

AG10

AH8

AH9

AH10

@

@

22U_0805_6.3V6M

22U_0805_6.3V6M

1

2

C72

C72

B

C109

C109

10U_0603_6.3V6M

10U_0603_6.3V6M

1

2

B

+APU_CORE_NB

VDDNB_CAP

+1.5V

C110

C110

180P_0402_50V8J

180P_0402_50V8J

1

1

2

2

VDDP Decoupling

C73

C73

C74

C74

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

2

2

+1.5V

C81

C81

C80

C80

22U_0805_6.3V6M

22U_0805_6.3V6M

C79

C79

1

2

VDDR Decoupling

C111

C111

C115

C115

1000P_0402_50V7K

1000P_0402_50V7K

180P_0402_50V8J

180P_0402_50V8J

1

1

2

2

C105

C105

C106

C106

180P_0402_50V8J

180P_0402_50V8J

180P_0402_50V8J

180P_0402_50V8J

1

1

2

2

C

C82

C82

C83

C83

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

2

C116

C116

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

1

2

2

C141

C141

180P_0402_50V8J

180P_0402_50V8J

1

2

C76

C76

10U_0603_6.3V6M

10U_0603_6.3V6M

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

1

1

2

2

C89

C89

C88

C88

22U_0805_6.3V6M

22U_0805_6.3V6M

1

2

C77

C77

10U_0603_6.3V6M

10U_0603_6.3V6M

1

2

22U_0805_6.3V6M

22U_0805_6.3V6M

+1.2VS

C78

C78

C90

C90

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

1

2

2

C102

C102

10U_0603_6.3V6M

10U_0603_6.3V6M

1

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

+1.5V

C92

C92

C91

C91

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

1

2

2

C103

C103

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

1

1

2

2

C94

C94

C95

C95

C96

C93

C93

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

C104

C104

1

1

2

2

C131

C131

180P_0402_50V8J

180P_0402_50V8J

180P_0402_50V8J

180P_0402_50V8J

1

1

2

2

C96

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

1

2

If the VSS plane is cut to

create a VDDIO plane,

place across the VDDIO

and VSS plane split

D

Co-layout with C100 on PVT

+1.5V

1

+

+

C147

C147

330U_D2_2V_Y

330U_D2_2V_Y

@

@

2

C130

C130

C99

C97

C97

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

1

1

2

2

C99

C98

C98

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

1

2

180P_0402_50V8J

180P_0402_50V8J

180P_0402_50V8J

180P_0402_50V8J

1

1

1

2

2

+

+

C100

C100

330U_2.5V_M_R17

330U_2.5V_M_R17

2

E

JAPUF

JAPUF

J20

VSS_1

L4

VSS_2

R7

VSS_3

W18

VSS_4

A15

VSS_5

AB17

VSS_6

AC22

VSS_7

AE21

VSS_8

AF24

VSS_9

AH23

VSS_10

AH25

VSS_11

B7

VSS_12

C14

VSS_13

C16

VSS_14

C2

VSS_15

C20

VSS_16

C22

VSS_17

C24

VSS_18

C26

VSS_19

C28

VSS_20

D13

VSS_21

D15

VSS_22

D17

VSS_23

D19

VSS_24

D23

VSS_25

D25

VSS_26

D27

VSS_27

E4

VSS_28

E9

VSS_29

F14

VSS_30

F16

VSS_31

F18

VSS_32

F20

VSS_33

F22

VSS_34

F26

VSS_35

F28

VSS_36

G13

VSS_37

G15

VSS_38

G17

VSS_39

G19

VSS_40

G21

VSS_41

G23

VSS_42

G25

VSS_43

G4

VSS_44

J22

VSS_45

J24

VSS_46

J4

VSS_47

J7

VSS_48

K11

VSS_49

K14

VSS_50

K9

VSS_51

AC11

VSS_52

L19

VSS_53

L7

VSS_54

M11

VSS_55

AF11

VSS_56

V19

VSS_57

V9

VSS_58

W16

VSS_59

W4

VSS_60

W7

VSS_61

Y11

VSS_62

Y20

VSS_63

Y22

VSS_64

Y9

VSS_65

A17

VSS_66

A13

VSS_67

K16

VSS_68

F24

VSS_69

G8

VSS_70

H7

VSS_71

J8

VSS_72

LOTES_ACA-ZIF-109-P12-A_FS1R2

LOTES_ACA-ZIF-109-P12-A_FS1R2

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

A19

A21

A23

A25

A7

AA4

AA7

AB13

AB15

AB19

AB21

AB23

AB25

AB27

AB9

AC14

AC16

AC18

AC20

AC24

AC26

AC28

AC4

AC7

AD9

AE13

AE15

AE17

M9

N10

N4

N7

R10

R4

T11

T9

U10

U18

U4

U7

V11

AE19

AE23

AE25

AE27

AE4

AE7

AF14

AF16

AF18

AF20

AF22

AF26

AF28

AF9

AG4

AG7

AH13

AH15

AH17

AH19

AH21

P9

C18

D21

W14

P11

C7

E8

K18

W12

@

@

Demo Board Capacitor

CORE_NB_CAP

22uF x 2

180pF x 1

VDDA

4.7uF x 1

0.22uF x 1

3.3nF x 1

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SCHEMATIC,MB LA-8864

SCHEMATIC,MB LA-8864

SCHEMATIC,MB LA-8864

4019IS

4019IS

4019IS

VDDIO_SUS

(CPU side)

22uF x 4

4.7uF x 4

0.22uF x 6 +2(split)

180pF x 1 + 2(split)

VDDIO_SUS

(DIMM x2)

100uF x 2

0.1uF x 12

E

840Monday, March 26, 2012

840Monday, March 26, 2012

840Monday, March 26, 2012

A

A

A

of

of

of

C108

C108

C75

C107

C107

1

2

C75

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

1000P_0402_50V7K

0.22U_0402_6.3V6K

0.22U_0402_6.3V6K

1000P_0402_50V7K

1

1

@

@

2

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/11/21 2011/12/11

2011/11/21 2011/12/11

2011/11/21 2011/12/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

APU_CORE

22uF x 10

0.22uF x 2

0.01uF x 3

180pF x 2

VDDP

0.22uF x 2

180pF x 2

D

CORE_NB

22uF x 2

10uF x 1

0.22uF x 2

180pF x 3

VDDR

0.22uF x 2

1nF x 1

180pF x 2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Page 9

5

4

3

2

1

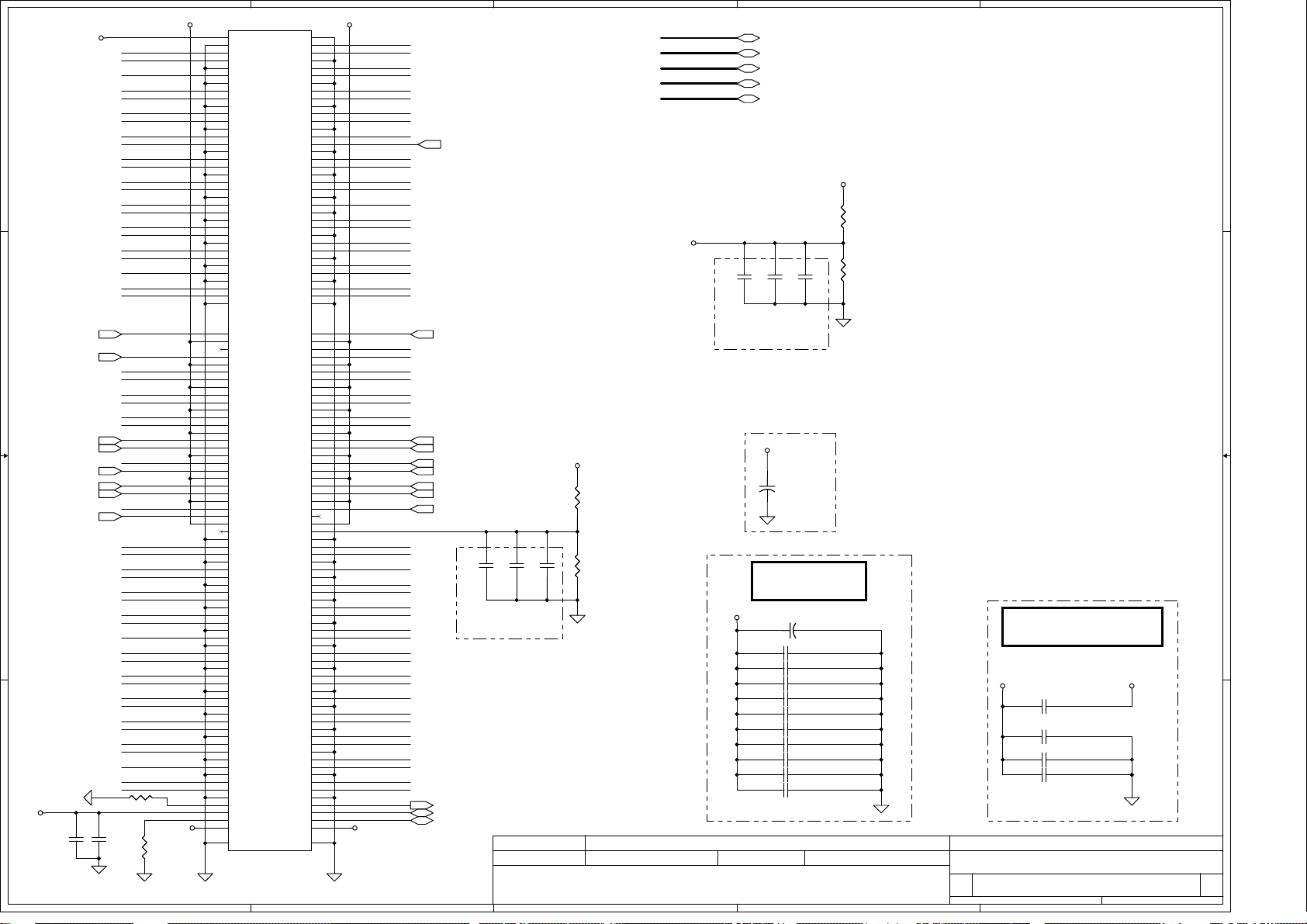

SB-TSI

BSH111, the Vgs is:

@

D D

R535

R535

1 2

+3VS

31.6K_0402_1%

31.6K_0402_1%

APU_SID<7>

APU_SIC<7>

C C

BSH111_SOT23-3

BSH111_SOT23-3

APU_SIC

BSH111_SOT23-3

BSH111_SOT23-3

@

C935 0.1U_0402_16V4Z

C935 0.1U_0402_16V4Z

1 2

R536

R536

1 2

30K_0402_1%

30K_0402_1%

Vg = 1.607 V

G

G

2

Q14

Q14

13

D

S

D

S

G

G

2

Q15

Q15

13

D

S

D

S

When APU High -> MOS OFF (Vgs < 0.4V )

APU Low -> MOS ON (Vgs > 1.3V)

EC_SMB_DA2APU_SID

EC_SMB_CK2

min = 0.4V

Max = 1.3V

EC_SMB_DA2 <27>

EC_SMB_CK2 <27>

Panel PWM

+3VS

12

B B

DP_INT_PWM<7>

A A

5

4

1 2

R89 2.2K_0402_5%R89 2.2K_0402_5%

12

R76

R76

4.7K_0402_5%

4.7K_0402_5%

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

R92

R92

47K_0402_5%

47K_0402_5%

C

C

Q21

Q21

2

B

B

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

E

E

3 1

2011/11/21 2011/12/11

2011/11/21 2011/12/11

2011/11/21 2011/12/11

3

12

R93

R93

4.7K_0402_5%

4.7K_0402_5%

61

Q25A

Q25A

2N7002KDWH_SOT363-6

2N7002KDWH_SOT363-6

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

APU_INVT_PWM <17>

Q25B in page30

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB LA-8864

SCHEMATIC,MB LA-8864

SCHEMATIC,MB LA-8864

4019IS

4019IS

4019IS

940Monday, March 26, 2012

940Monday, March 26, 2012

940Monday, March 26, 2012

of

of

1

of

A

A

A

Page 10

5

+VREF_DQA

D D

C C

B B

A A

+3VS

DDR_A_SCS1#<6>

C181

C181

DDR_A_BS2<6>

DDR_A_CLK0<6>

DDR_A_CLK0#<6>

DDR_A_BS0<6>

DDR_A_WE#<6>

DDR_A_CAS#<6>

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

1

C182

C182

2

DDR_A_D0

DDR_A_D1

DDR_A_DM0

DDR_A_D2

DDR_A_D3

DDR_A_D8

DDR_A_D9

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_D10

DDR_A_D11

DDR_A_D16

DDR_A_D17

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_D18

DDR_A_D19

DDR_A_D24

DDR_A_D25

DDR_A_DM3

DDR_A_D26

DDR_A_D27

DDR_A_CKE0

DDR_A_BS2

DDR_A_MA12

DDR_A_MA9

DDR_A_MA8

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1

DDR_A_CLK0

DDR_A_CLK0#

DDR_A_MA10

DDR_A_BS0

DDR_A_WE#

DDR_A_CAS#

DDR_A_MA13

DDR_A_SCS1#

DDR_A_D32

DDR_A_D33

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_D34

DDR_A_D35

DDR_A_D40

DDR_A_D41

DDR_A_DM5

DDR_A_D42

DDR_A_D43

DDR_A_D48

DDR_A_D49

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_D50

DDR_A_D51

DDR_A_D56

DDR_A_D57

DDR_A_DM7

DDR_A_D58

DDR_A_D59

R90

R90

1 2

10K_0402_5%

10K_0402_5%

1

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

5

+0.75VS

12

R91

R91

10K_0402_5%

10K_0402_5%

+1.5V

JDDR3H

JDDR3H

VREF_DQ1VSS1

3

VSS2

5

DQ0

7

DQ1

9

VSS4

11

DM0

13

VSS5

15

DQ2

17

DQ3

19

VSS7

21

DQ8

23

DQ9

25

VSS9

27

DQS#1

29

DQS1

31

VSS11

33

DQ10

35

DQ11

37

VSS13

39

DQ16

41

DQ17

43

VSS15

45

DQS#2

47

DQS2

49

VSS18

51

DQ18

53

DQ19

55

VSS20

57

DQ24

59

DQ25

61

VSS22

63

DM3

65

VSS23

67

DQ26

69

DQ27

71

VSS25

73

CKE0

75

VDD1

77

NC1

79

BA2

81

VDD3

83

A12/BC#

85

A9

87

VDD5

89

A8

91

A5

93

VDD7

95

A3

97

A1

99

VDD9

101

CK0

103

CK0#

105

VDD11

107

A10/AP

109

BA0

111

VDD13

113

WE#

115

CAS#

117

VDD15

119

A13

121

S1#

123

VDD17

125

NCTEST

127

VSS27

129

DQ32

131

DQ33

133

VSS29

135

DQS#4

137

DQS4

139

VSS32

141

DQ34

143

DQ35

145

VSS34

147

DQ40

149

DQ41

151

VSS36

153

DM5

155

VSS37

157

DQ42

159

DQ43

161

VSS39

163

DQ48

165

DQ49

167

VSS41

169

DQS#6

171

DQS6

173

VSS44

175

DQ50

177

DQ51

179

VSS46

181

DQ56

183

DQ57

185

VSS48

187

DM7

189

VSS49

191

DQ58

193

DQ59

195

VSS51

197

SA0

199

VDDSPD

201

SA1

203

VTT1

205

G1

LCN_DAN06-K4806-0102

LCN_DAN06-K4806-0102

@

@

DQ4

DQ5

VSS3

DQS#0

DQS0

VSS6

DQ6

DQ7

VSS8

DQ12

DQ13

VSS10

DM1

RESET#

VSS12

DQ14

DQ15

VSS14

DQ20

DQ21

VSS16

DM2

VSS17

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS#3

DQS3

VSS24

DQ30

DQ31

VSS26

CKE1

VDD2

VDD4

VDD6

VDD8

VDD10

CK1

CK1#

VDD12

RAS#

VDD14

ODT0

VDD16

ODT1

NC2

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

DM4

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

DM6

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

SDA

SCL

VTT2

BA1

S0#

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

A15

80

A14

82

84

A11

86

A7

88

90

A6

92

A4

94

96

A2

98

A0

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

206

G2

4

+1.5V

DDR_A_D4

DDR_A_D5

DDR_A_DQS#0

DDR_A_DQS0

DDR_A_D6

DDR_A_D7

DDR_A_D12

DDR_A_D13

DDR_A_DM1

MEM_MA_RST#

DDR_A_D14

DDR_A_D15

DDR_A_D20

DDR_A_D21

DDR_A_DM2

DDR_A_D22

DDR_A_D23