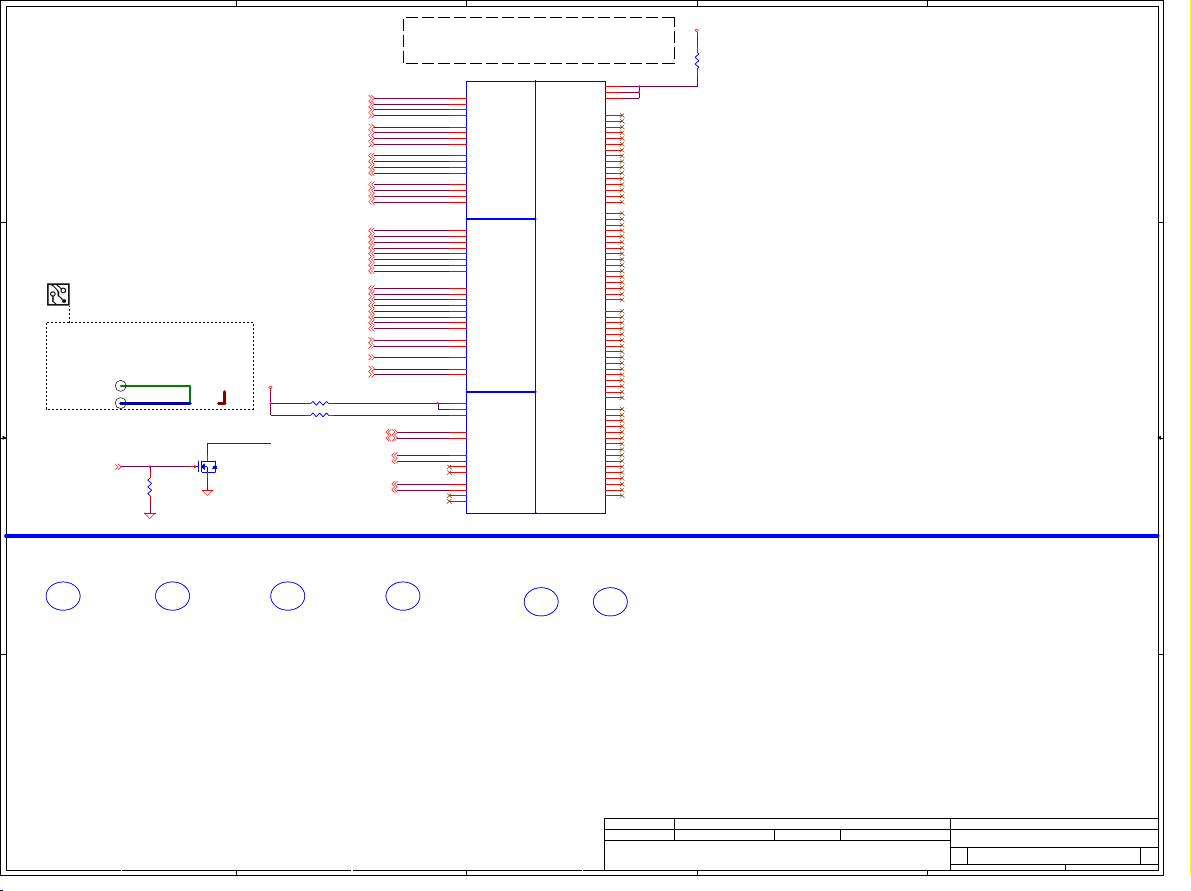

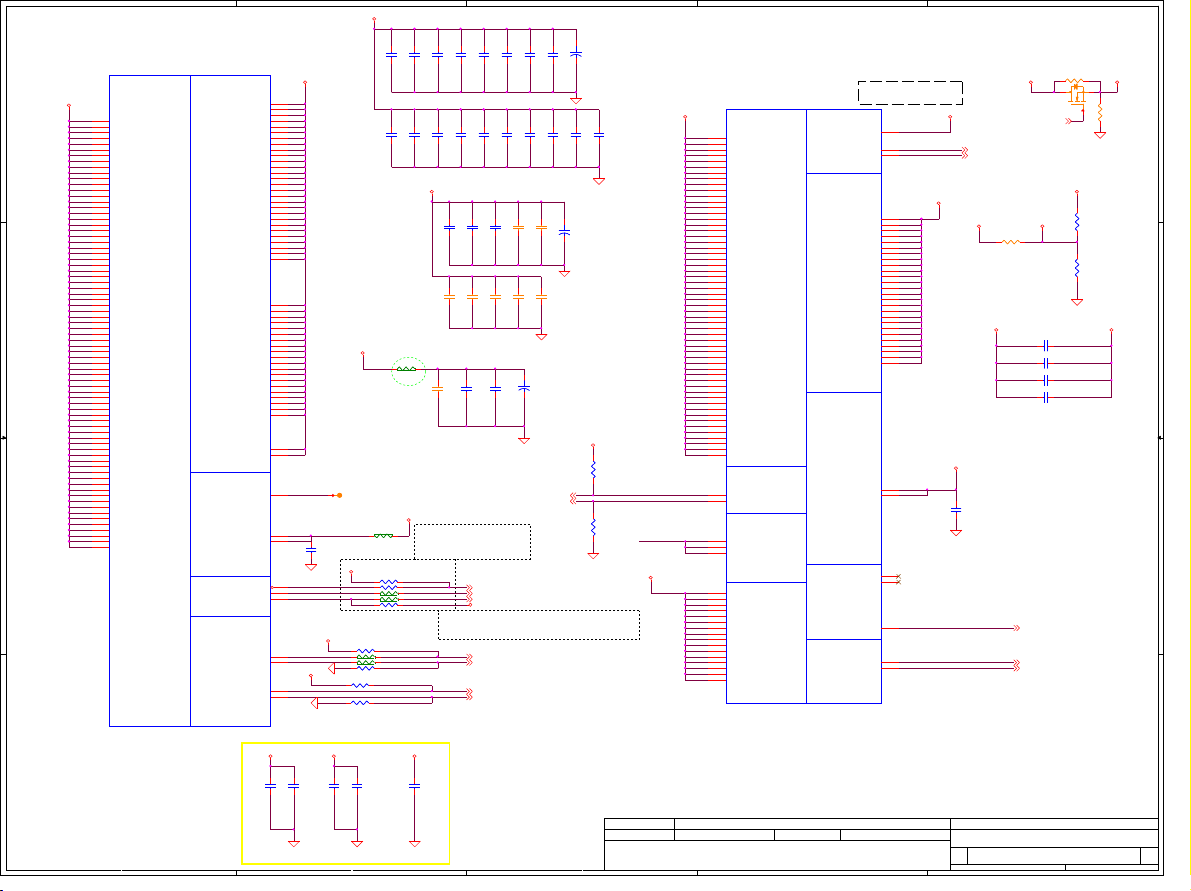

Page 1

A

MODEL NAME :

PCB NO :

1 1

BOM P/N :

QAZA0

LA-8821P ( DAB00000B00 )

ZZZ

ZZZ

MB_ PCB

MB_ PCB

B

C

D

E

4619J831L01 -> i5, 1.7G, DDR3L-4GB

4619J831L02 -> i5, 1.7G, DDR3L-8GB

4619J831L03 -> i7, 1.9G, DDR3L-4GB

4619J831L04 -> i7, 1.9G, DDR3L-8GB

4619J831L06 -> i5, 1.8G, DDR3L-4GB

4619J831L07 -> i5, 1.8G, DDR3L-8GB

4619J831L08 -> i7, 2.0G, DDR3L-4GB

4619J831L09 -> i7, 2.0G, DDR3L-8GB

4619J831L10 -> i5, 1.8G, DDR3L-4GB-NT

4619J831L11 -> i5, 1.8G, DDR3L-8GB-NT

4619J831L12 -> i7, 2.0G, DDR3L-4GB-NT

2 2

4619J831L13 -> i7, 2.0G, DDR3L-8GB-NT

Dell/Compal Confidential

4619J831L14 -> i5, 1.7G, DDR3L-4GB-NT

4619J831L15 -> i5, 1.7G, DDR3L-8GB-NT

4619J831L16 -> i7, 1.9G, DDR3L-4GB-NT

Schematic Document

4619J831L17 -> i7, 1.9G, DDR3L-8GB-NT

Murcielgo (Chief River SFF)

Ivy Bridge(BGA) + Panther Point(SFF, QS77)

3 3

2012-08-21

Rev: 1.0

Highlight the short pad for 0 ohm

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

A

B

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

2011/06/02 2013/10/28

2011/06/02 2013/10/28

2011/06/02 2013/10/28

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Tit le

Tit le

Tit le

P01-Cover Page

P01-Cover Page

P01-Cover Page

Size Docu me nt N umb er Rev

Size Docu me nt N umb er Rev

Size Docu me nt N umb er Rev

LA-8821P

LA-8821P

LA-8821P

Date : She et of

Date : She et of

Date : She et of

1 54Frida y, S ep tem ber 28, 20 12

1 54Frida y, S ep tem ber 28, 20 12

1 54Frida y, S ep tem ber 28, 20 12

E

1.0

1.0

1.0

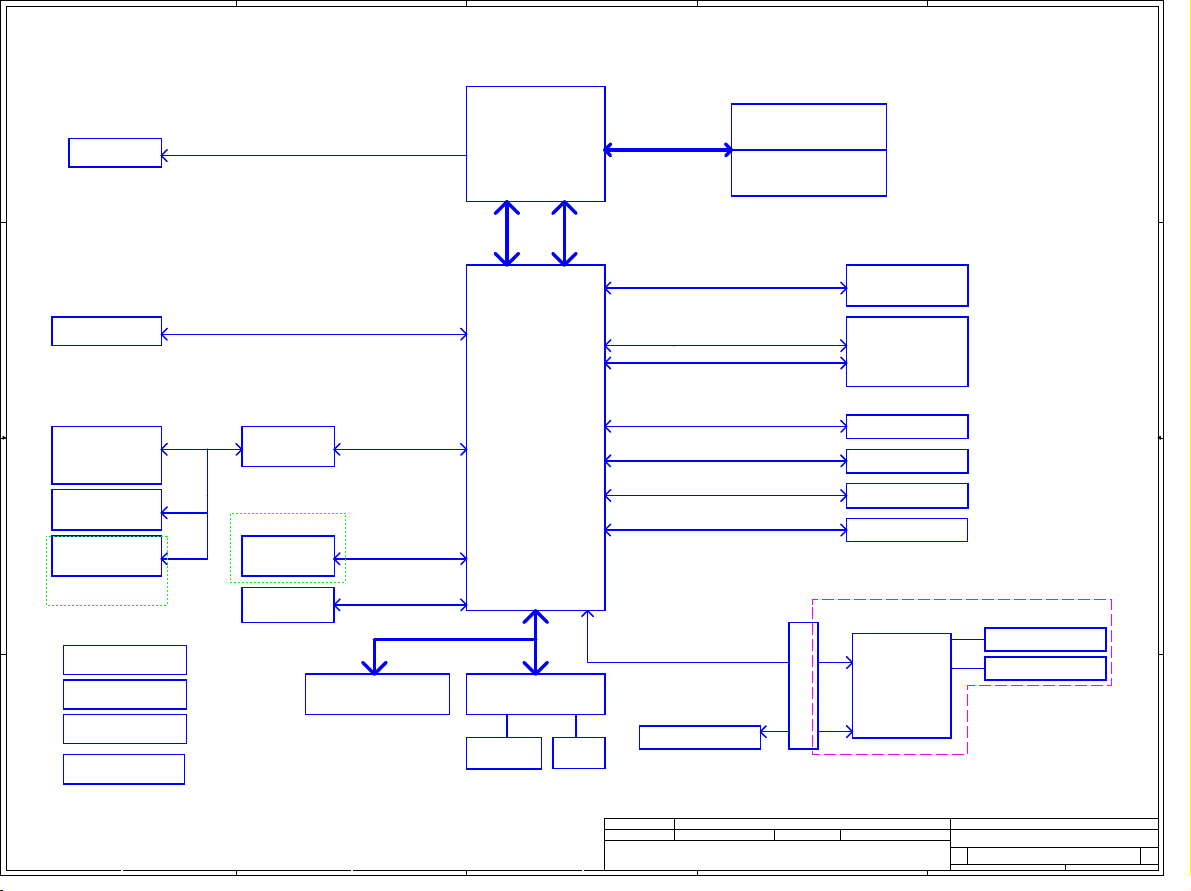

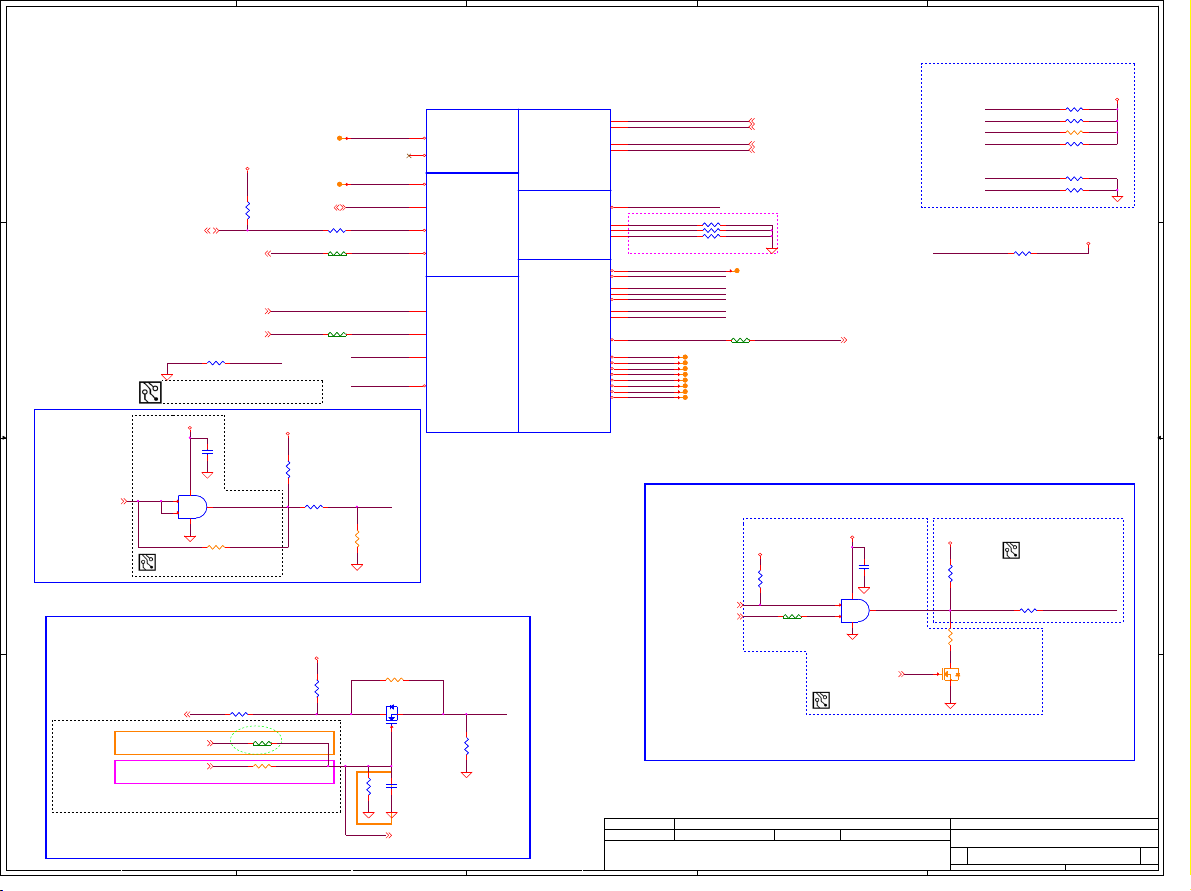

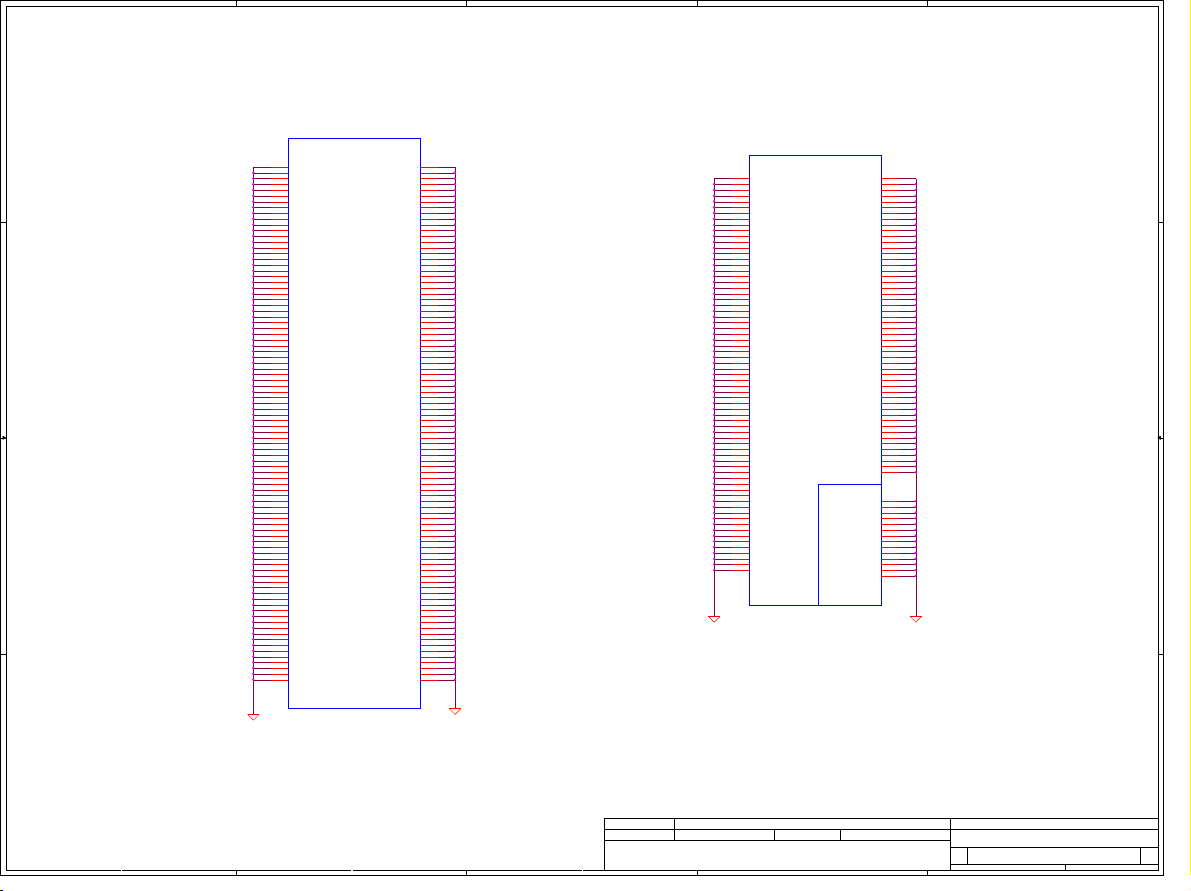

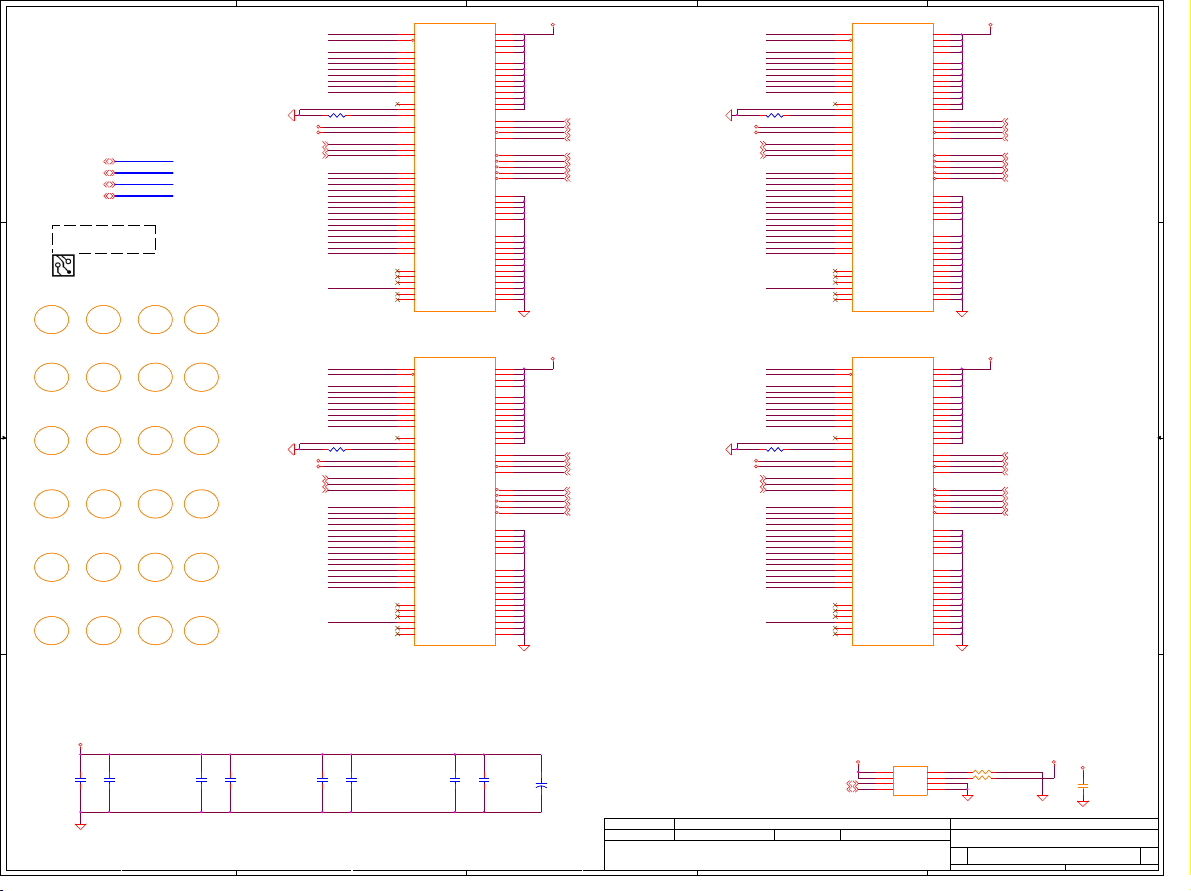

Page 2

A

B

C

D

E

1 1

eDP Panel

P.24

Conn x 2.

2 2

miniDP

Conn.

e-Compass +

Accelerometer

DE303DLHCTR

P.26

I2C

Sensor HUB

P.27

STM32F103RD

P.27

eDP

DP 1.1a

USB 2.0

Gyro Sensor

TX3GD20TR

3 3

Pressure Sensor

APS331APTR

RTC conn.

DC/DC Interface CKT.

Power Circuit DC/DC

4 4

PWM Fan Connector

De-pop

P.27

P.27

P.36 ~ 47

De-pop

NFC Module

Conn

P.33

P.32

P.34

SPI ROM

8M

TPM

AT97SC320 4-X2A14-AB

P.29

P.16

SMBus/I2C

SPI

P.27

Intel

Ivy Bridge

Processor

2C 17W

BGA 1023

Page 5, 6, 7, 8, 9, 10

100MHz 100MHz

2.7GT/s

DMI x4FDI x8

5GT/s

Intel

Panther Point SFF

PCH

QS77

BGA 1017 Balls

Page 16 ~ 23

LPC Bus

ENE KB9012BF

Touch Pad Int.KBD

P.34

Memory Bus (DDR3L)

Dual Channel

1.35V DDR3L 1333 MHz

SATA3.0

USB2.0

PCI-E 2.0

USB2.0

USB2.0

USB3.0/USB2.0

USB3.0/USB2.0

HD Audio

P.35

Digital MIC

P.33

Channel A

DDR3L 2Gb or 4Gb (x8 ) * 8

Channel B

DDR3L 2Gb or 4Gb (x8 ) * 8

P.11, 12

P.13,14

Mini Card (Full)

# mSATA

Mini Card (Half)

WLAN

WiGig

BT

Touch Screnn

Digital Camera

USB 3.0 Conn.

( USB Charger Port )

USB 3.0 Conn.

Daughter Board

IOL BTB Conn

P.25

P.24

Audio Codec

ALC3260

P.29

P.28

P.24

P.24

P.30

P.30

Headphone Jack

( iPhone & Nokia compatible)

Int. Speaker

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

A

B

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

2011/02/23 2013/10/28

2011/02/23 2013/10/28

2011/02/23 2013/10/28

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Tit le

Tit le

Tit le

P02-Block Diagram

P02-Block Diagram

P02-Block Diagram

Size Docu me nt N umb er Rev

Size Docu me nt N umb er Rev

Size Docu me nt N umb er Rev

LA-8821P

LA-8821P

LA-8821P

Date : She et of

Date : She et of

Date : She et of

2 54Frida y, S ep tem ber 28, 20 12

2 54Frida y, S ep tem ber 28, 20 12

2 54Frida y, S ep tem ber 28, 20 12

E

1.0

1.0

1.0

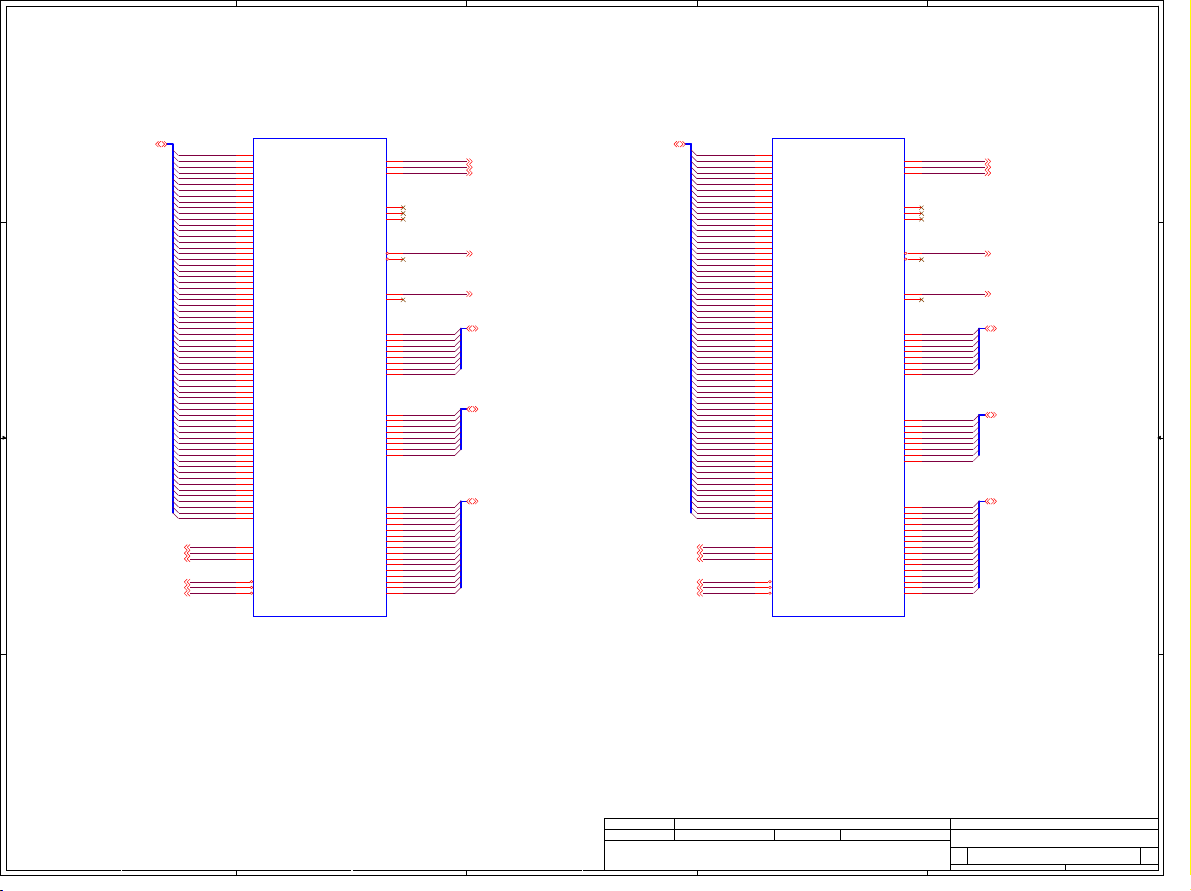

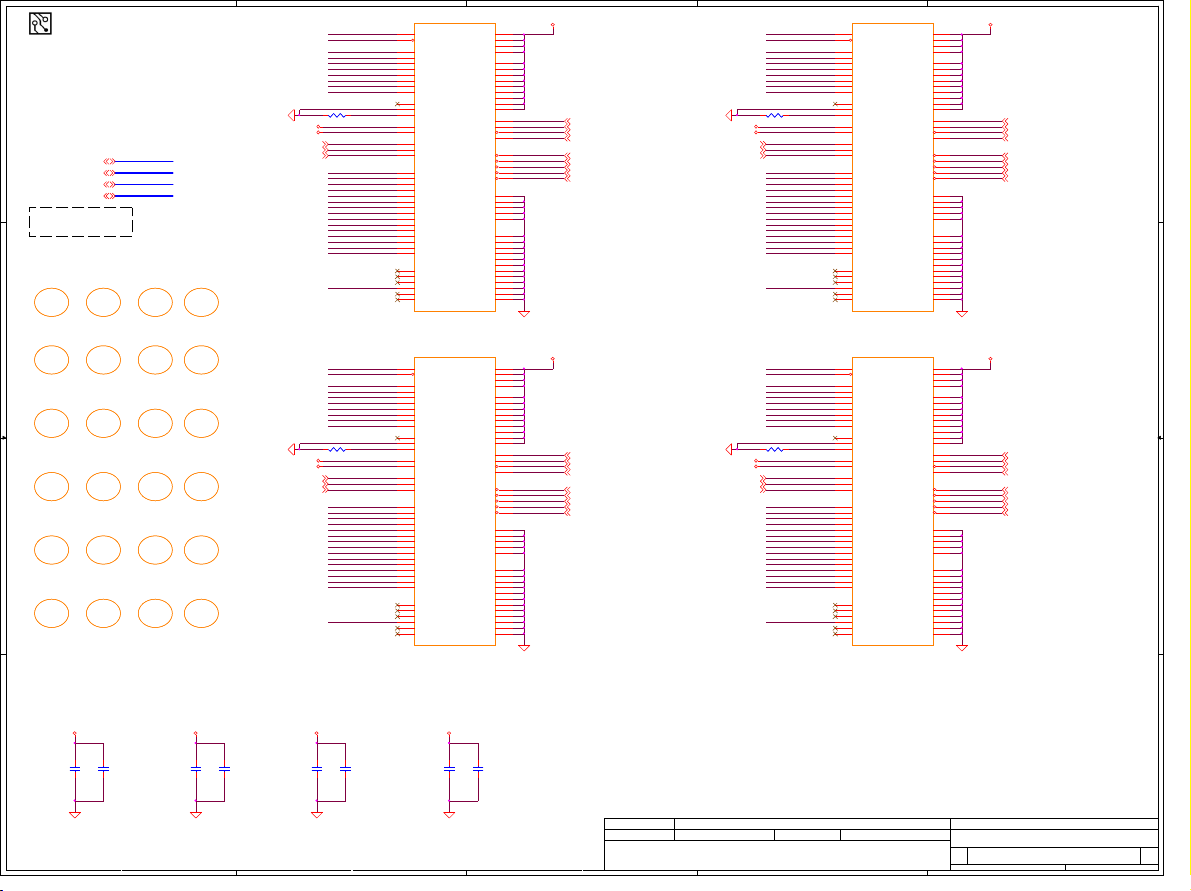

Page 3

A

B

C

D

E

Compal Confidential

Project Code : QAZA0

File Name : LA-88 21P

1 1

LS-8821P

Volume Up/Down , PWR, Rotation Button

2 2

Audio Jack

Keyboard

Keyboard Backlig ht

3 3

4 4

A

FPC

36 pin

FPC (main frame)

30 pin

FFC

4 pin

LA-8821P M/B

eDP Cable x 2

Coaxial and Wire

FFC

6 pin

Touch Pad

B

CABLE

9 pin

Battery Pack

FPC

16 pin to 15 pin

NFC Module

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

2011/06/02 2013/10/28

2011/06/02 2013/10/28

2011/06/02 2013/10/28

Deciphered Date

Deciphered Date

Deciphered Date

D

LS-8822P

Win8 Button

Hall S ensor

Camera

LCD Panel

Touch Panel Control Baord

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Tit le

Tit le

Tit le

P03-DaughterB block diagram

P03-DaughterB block diagram

P03-DaughterB block diagram

Size Docu me nt N umb er Rev

Size Docu me nt N umb er Rev

Size Docu me nt N umb er Rev

Date : She et of

Date : She et of

Date : She et of

E

3 54Frida y, S ep tem ber 28, 20 12

3 54Frida y, S ep tem ber 28, 20 12

3 54Frida y, S ep tem ber 28, 20 12

1.0

1.0

1.0

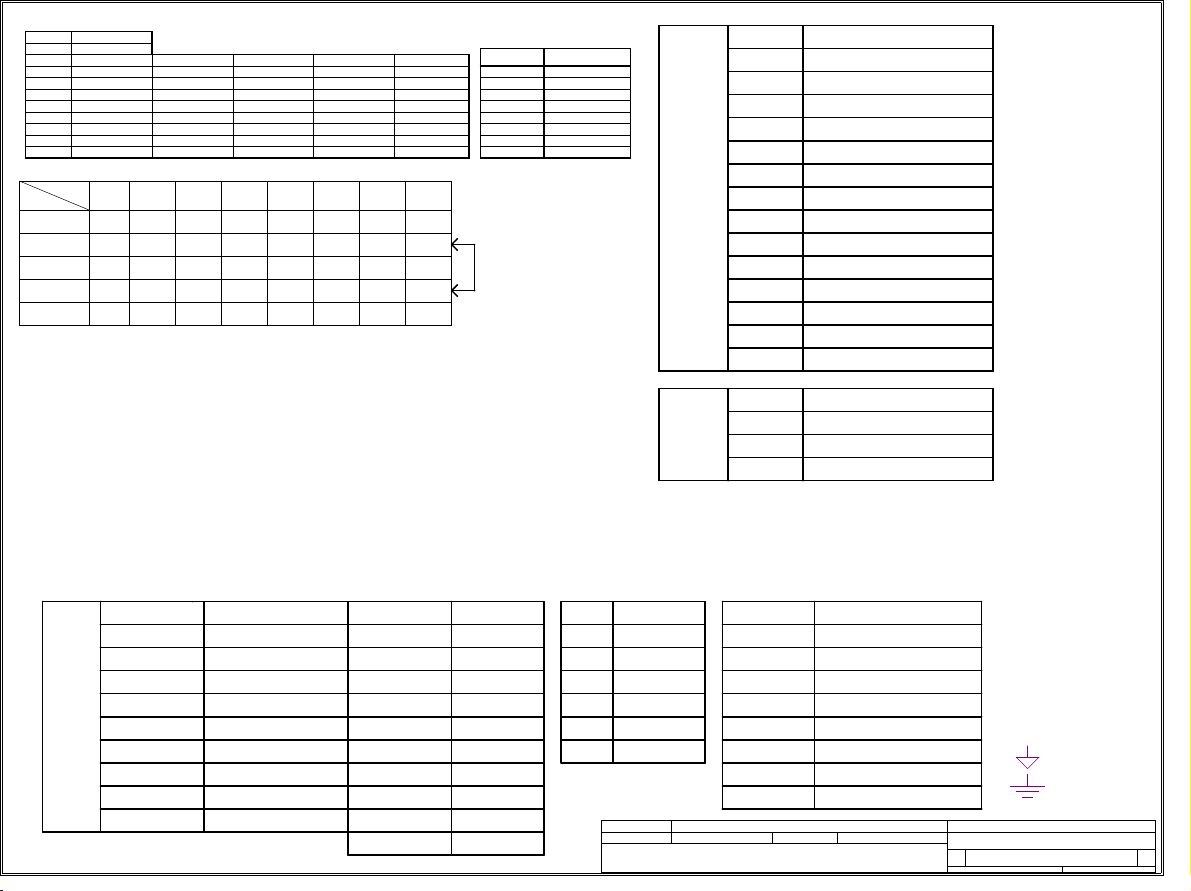

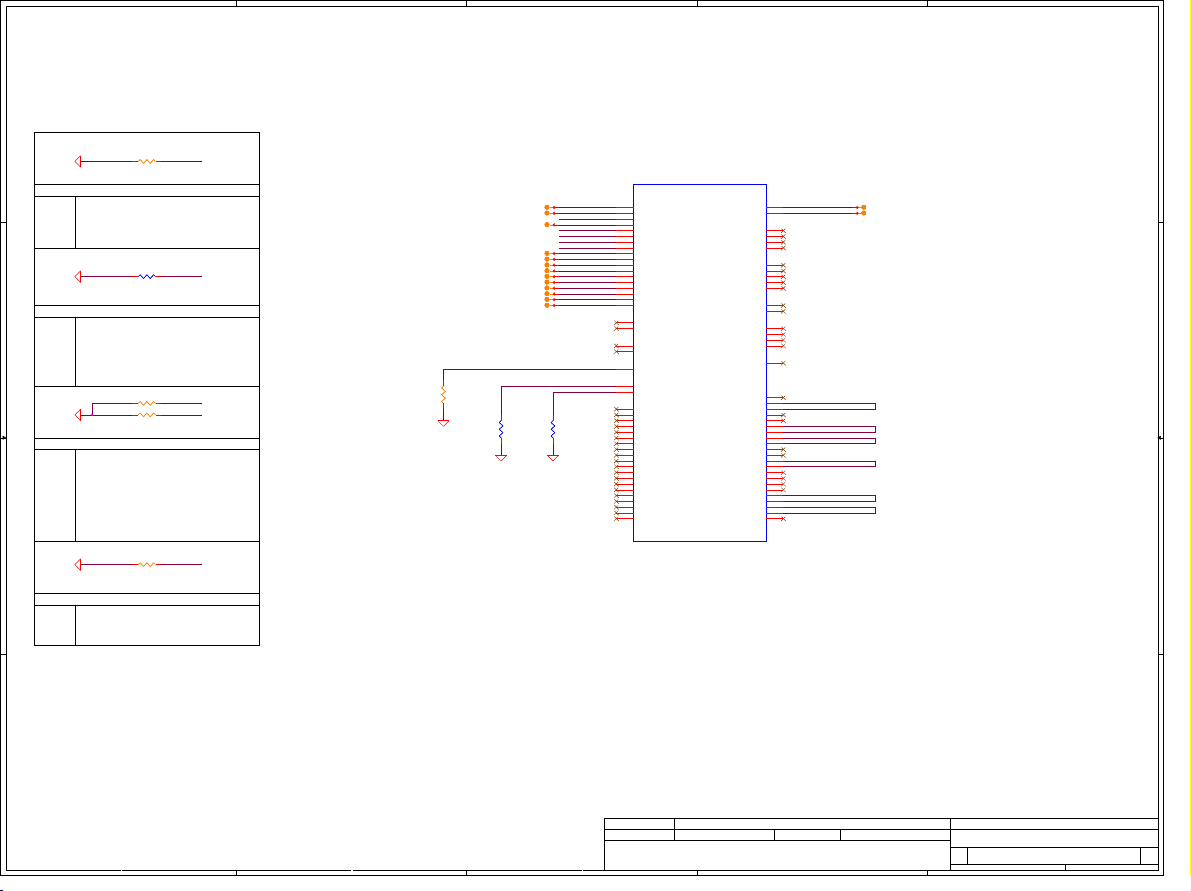

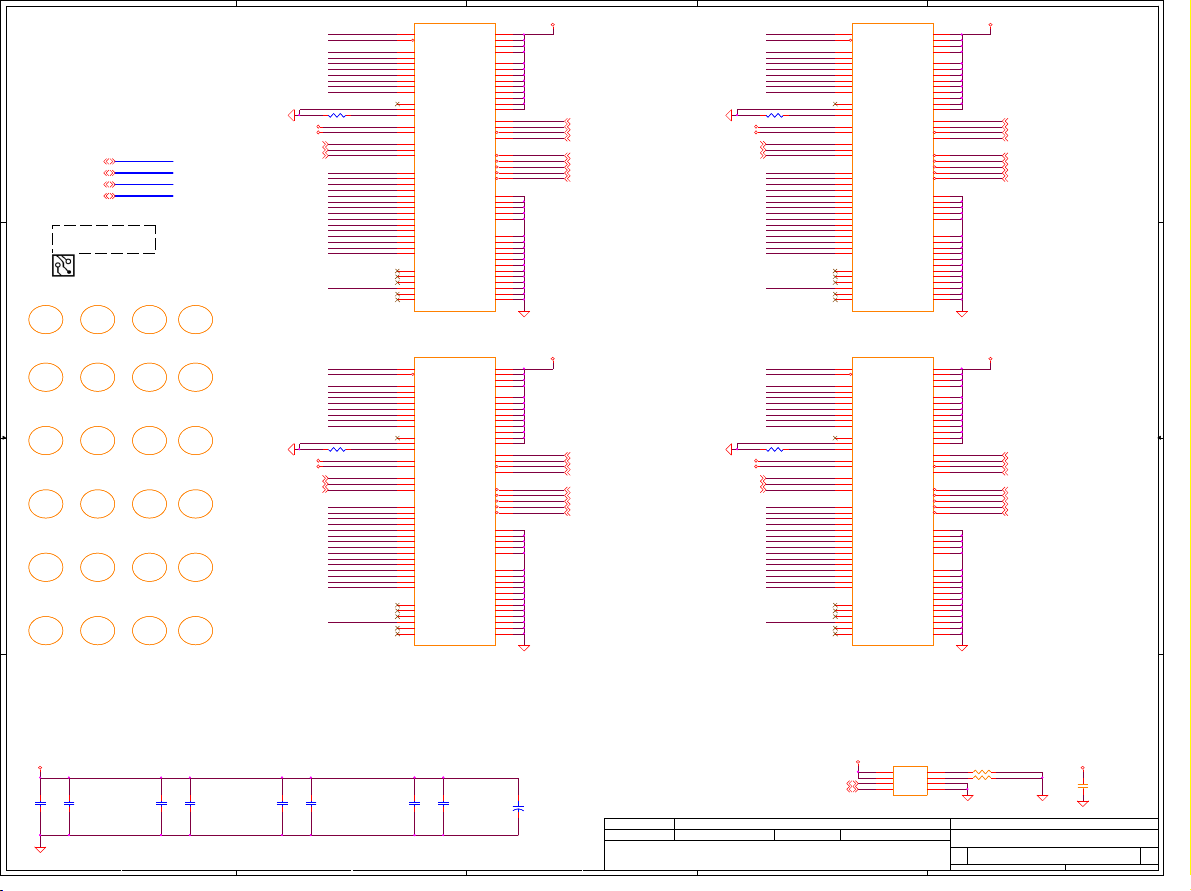

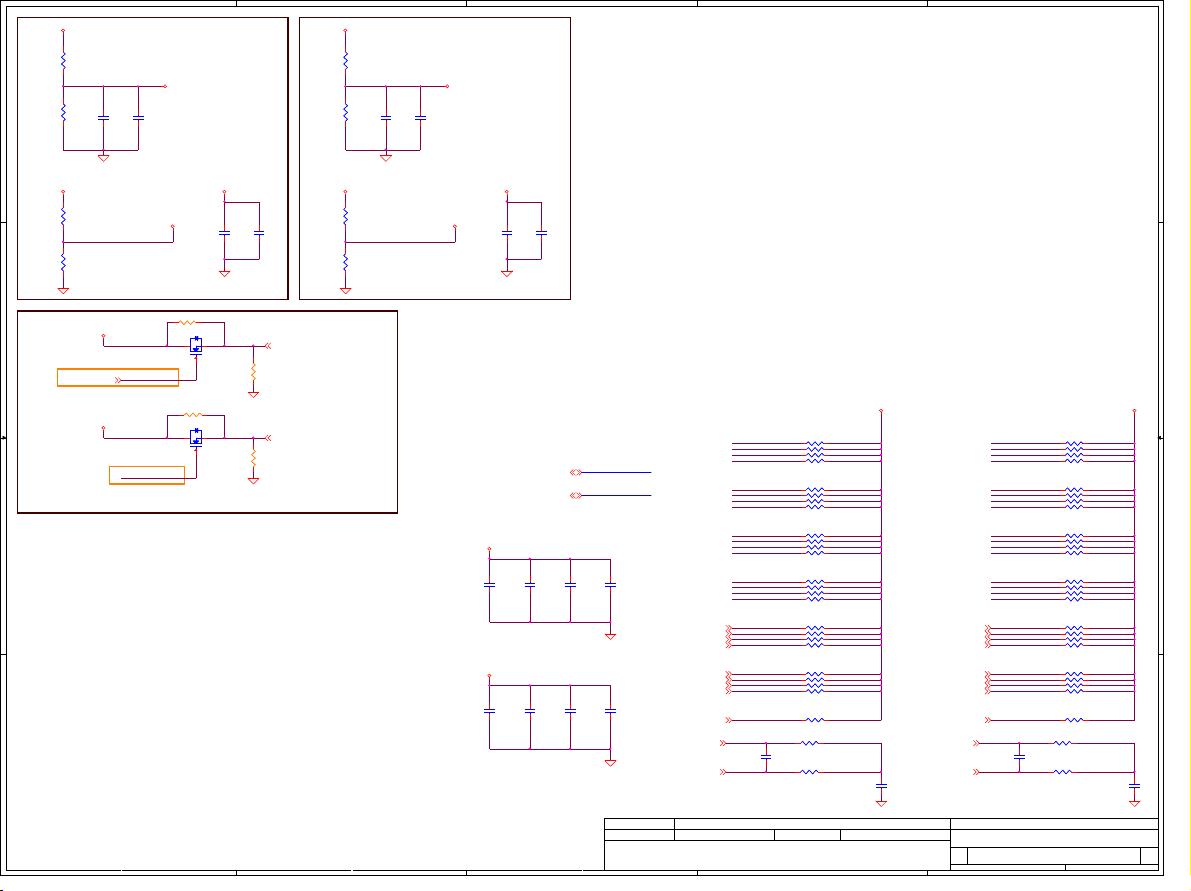

Page 4

Board ID Table for AD channel

Vcc 3.3V +/- 5%

100K +/- 5%Ra

Board ID Rb V min

1

2

3

4

5

6

7

SMBUS Control Table

EC_SMB_CK1

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_DA2

PCH_SML0CLK PCH

PCH_SML0DATA

PCH_SML1CLK

PCH_SML1DATA

MEM_SMBCLK

MEM_SMBDATA

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

NC

SOURCE

KB930

KB930

PCH

PCH

AD_BID V t ypAD_BID V AD_BID max

0 V0

0.168 V

0.375 V 0.503 V

0.634 V

0.958 V

1.372 V

1.851 V 2.200 V

2.433 V

WLAN BATT DDR3 SPD

V V V

V V

0 V 0.155 V

0.250 V

0.819 V

1.185 V

1.650 V

3.300 V

NFCCharger

Touch Pad

V

0.362 V

0.621 V

0.945 V

1.359 V

1.838 V

2.420 V

3.300 V

EC AD3

0x00-0x0C

0x0D-0x1C

0x1D-0x30

0x31-0x49

0x4A-0x69

0x6A-0x8E

0x8F-0xBB

0xBC-0xFF

ALS

V

BOARD ID Table

Board ID

0

1

2

3

4

5

6

7

Link

A

PCB Revision

0.1 Non Deep S3

0.1 Deep S 3

0.2 (X01)

0.4 (X02)

1.0 (A00)

PCH

USB

Port

Mapping

USB PORT#

0

1

2

3

4

5

6

7

8

9

10

11

12

13

DESTINATION

External USB3

External USB3

MINI CARD-1 WLAN

Touch Panel

Camera

Sensor HUB

PCH

1 1

DDI

Port

Mapping

DESTINATION

SATA

SATA0

m-SATA

SATA1

SATA2

SATA3

SATA4

SATA5

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

AND TRADE SECR ET INFORMATION. THI S SHEET MAY NOT BE TRAN SFERED FR OM THE CUSTODY OF THEC OMPETENTDI VISION OF R&D

AND TRADE SECR ET INFORMATION. THI S SHEET MAY NOT BE TRAN SFERED FR OM THE CUSTODY OF THEC OMPETENTDI VISION OF R&D

AND TRADE SECR ET INFORMATION. THI S SHEET MAY NOT BE TRAN SFERED FR OM THE CUSTODY OF THEC OMPETENTDI VISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONIC S, INC . NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONIC S, INC . NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONIC S, INC . NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

A

CLK

CLKOUT_PCIE1

CLKOUT_PCIE2

CLKOUT_PCIE3

CLKOUT_PCIE4

CLKOUT_PCIE5

CLKOUT_PCIE6

CLKOUT_PCIE7

CLKOUT_PEG_B

DESTINATIONDIFFERENTIAL

MINI CARD-1 WLAN

FLEX CLOCKS DESTINATION

CLKOUTFLEX0

TPM

CLKOUTFLEX1

CLKOUTFLEX2

CLKOUTFLEX3

PCI CLKOUT DESTINATION

PCI0

PCI1

PCH_LOOPBACK

EC LPC

PCI2

PCI3

PCI4

DDI PORT# DESTINATION

B

C

D mini-DP

PCI EXPRESS

DESTINATION

Lane 1CLKOUT_PCIE0

Lane 2

Lane 3

MINI CARD-1 WLAN

Lane 4

Lane 5

Lane 6

Lane 7

Lane 8

Compal Secret Data

Compal Secret Data

Compal Secret Data

2011/06/02 2013/10/28

2011/06/02 2013/10/28

2011/06/02 2013/10/28

Deciphered Date

Deciphered Date

Deciphered Date

Symbol Note :

: means Digital Ground

: means Analog Ground

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Tit le

Tit le

Tit le

P04-Notes List

P04-Notes List

P04-Notes List

Size Docu me nt N umb er Rev

Size Docu me nt N umb er Rev

Size Docu me nt N umb er Rev

LA-8821P

LA-8821P

LA-8821P

Date : She et of

Date : She et of

Date : She et of

4 54Frida y, S ep tem ber 28, 20 12

4 54Frida y, S ep tem ber 28, 20 12

4 54Frida y, S ep tem ber 28, 20 12

1.0

1.0

1.0

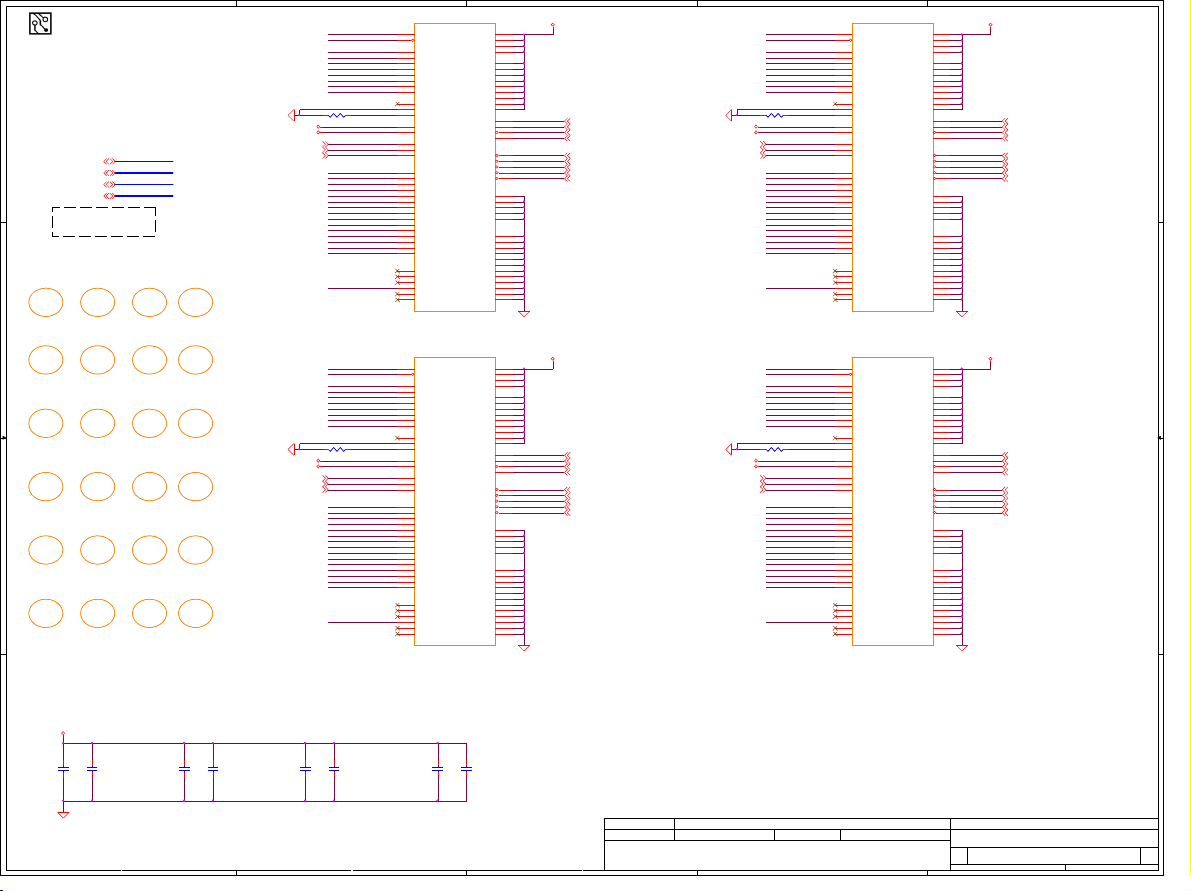

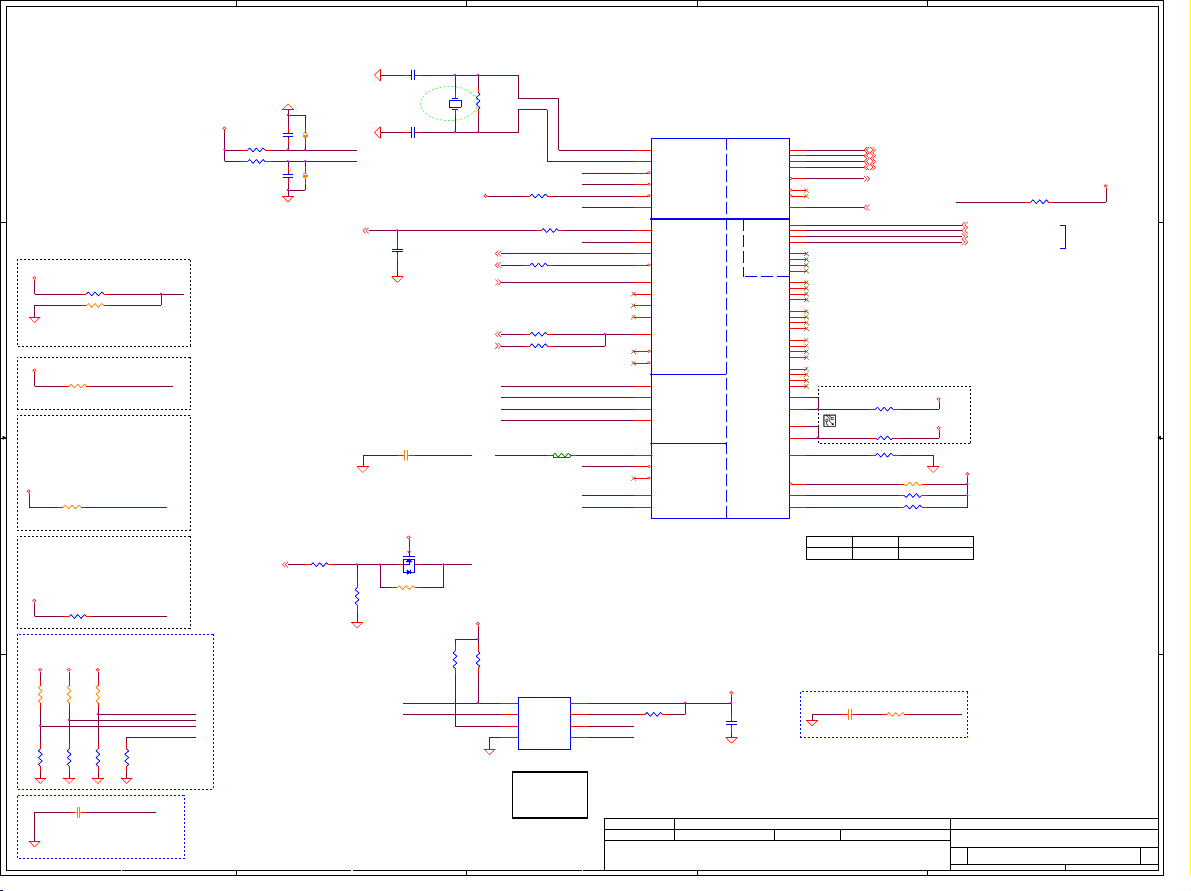

Page 5

5

D D

C C

B B

SA00005K63L for i5-3317U-1.7G SA00005L92L for i5-3427U- 1.8G

eDP_COMPIO (A1 8)

UCPU1

UCPU1

IVB1.7G

IVB1.7G

CPU_ IVB 1.7 G@

CPU_ IVB 1.7 G@

Trace le ngth Ma x is 500 mi ls

eDP_ HPD[24]

RC13 8

RC13 8

100 K_0 40 2_5 %~D

100 K_0 40 2_5 %~D

R_COMP pla ce close to CP U

width 4 m ils

width 12 mils

2

G

G

12

Ivy Bridge i5-1.8G

UCPU1

UCPU1

IVB1.8G

IVB1.8G

CPU_ IVB 1.8 G@

CPU_ IVB 1.8 G@

R_COMPeDP_ICOMPO (A1 7)

VCC_IO

CPU_ eDP _HPD #

13

D

D

QC5

QC5

DII-DM N65 D8L W-7~ D

DII-DM N65 D8L W-7~ D

S

S

+VCC P

RC36 24.9 _0 402 _1 %RC36 24.9 _0 402 _1 %

RC13 7 1K_ 040 2_ 5%~ DRC13 7 1K_ 040 2_ 5%~ D

Ivy Bridge i7-1.9GIvy Bridge i5-1.7G

UCPU1

UCPU1

IVB1.9G

IVB1.9G

CPU_ IVB 1.9 G@

CPU_ IVB 1.9 G@

SA00005K53L for i7-3517U-1.9G

DMI_ CRX _PT X_ N0[18]

DMI_ CRX _PT X_ N1[18]

DMI_ CRX _PT X_ N2[18]

DMI_ CRX _PT X_ N3[18]

DMI_ CRX _PT X_ P0[18 ]

DMI_ CRX _PT X_ P1[18 ]

DMI_ CRX _PT X_ P2[18 ]

DMI_ CRX _PT X_ P3[18 ]

DMI_ CT X_P RX_ N0[18]

DMI_ CT X_P RX_ N1[18]

DMI_ CT X_P RX_ N2[18]

DMI_ CT X_P RX_ N3[18]

DMI_ CT X_P RX_ P0[18 ]

DMI_ CT X_P RX_ P1[18 ]

DMI_ CT X_P RX_ P2[18 ]

DMI_ CT X_P RX_ P3[18 ]

FDI_C TX _PR X_N0[18]

FDI_C TX _PR X_N1[18]

FDI_C TX _PR X_N2[18]

FDI_C TX _PR X_N3[18]

FDI_C TX _PR X_N4[18]

FDI_C TX _PR X_N5[18]

FDI_C TX _PR X_N6[18]

FDI_C TX _PR X_N7[18]

FDI_C TX _PR X_P 0[ 18]

FDI_C TX _PR X_P 1[ 18]

FDI_C TX _PR X_P 2[ 18]

FDI_C TX _PR X_P 3[ 18]

FDI_C TX _PR X_P 4[ 18]

FDI_C TX _PR X_P 5[ 18]

FDI_C TX _PR X_P 6[ 18]

FDI_C TX _PR X_P 7[ 18]

FDI_F SYN C0[18]

FDI_F SYN C1[18]

FDI_I NT[18]

FDI_L SY NC0[18 ]

FDI_L SY NC1[18 ]

1 2

4

12

eDP_ AUX N[24]

eDP_ AUX P[24]

eDP_ TX N_P 0[24]

eDP_ TX N_P 1[24]

eDP_ TX P_ P0[24 ]

eDP_ TX P_ P1[24 ]

Ivy Bridge i7-2.0G

SA00005LA2L for i7-3667U-2.0G

3

PEG_ICOMPI and RCOMPO signals should be shor ted and routed

with - max leng th = 500 mils - typical imped ance = 43 mohm s

PEG_ICOMPO sign als should be routed with - m ax length = 50 0 mils

- typical imped ance = 14.5 mo hms

@

@

UCPU1 A

+EDP _CO M

CPU_ eDP _HPD #

UCPU1

UCPU1

IVB2.0G

IVB2.0G

CPU_ IVB 2.0 G@

CPU_ IVB 2.0 G@

UCPU1 A

M2

P6

P1

P10

N3

P7

P3

P11

K1

M8

N4

R2

K3

M7

P4

T3

U7

W11

W1

AA6

W6

V4

Y2

AC9

U6

W10

W3

AA7

W7

T4

AA3

AC8

AA11

AC12

U11

AA10

AG8

AF3

AD2

AG11

AG4

AF4

AC3

AC4

AE11

AE7

AC1

AA4

AE10

AE6

IVY-B RIDG E_ BGA 102 3

IVY-B RIDG E_ BGA 102 3

DMI_RX#[0]

DMI_RX#[1]

DMI_RX#[2]

DMI_RX#[3]

DMI_RX[0]

DMI_RX[1]

DMI_RX[2]

DMI_RX[3]

DMI_TX#[0]

DMI_TX#[1]

DMI_TX#[2]

DMI_TX#[3]

DMI_TX[0]

DMI_TX[1]

DMI_TX[2]

DMI_TX[3]

FDI0_TX#[0]

FDI0_TX#[1]

FDI0_TX#[2]

FDI0_TX#[3]

FDI1_TX#[0]

FDI1_TX#[1]

FDI1_TX#[2]

FDI1_TX#[3]

FDI0_TX[0]

FDI0_TX[1]

FDI0_TX[2]

FDI0_TX[3]

FDI1_TX[0]

FDI1_TX[1]

FDI1_TX[2]

FDI1_TX[3]

FDI0_FSYNC

FDI1_FSYNC

FDI_INT

FDI0_LSYNC

FDI1_LSYNC

eDP_COMPIO

eDP_ICOMPO

eDP_HPD#

eDP_AUX#

eDP_AUX

eDP_TX#[0]

eDP_TX#[1]

eDP_TX#[2]

eDP_TX#[3]

eDP_TX[0]

eDP_TX[1]

eDP_TX[2]

eDP_TX[3]

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

DMI Intel(R) FDI

DMI Intel(R) FDI

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

eDP

eDP

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

X76 4G

X76 4G

X7641131L01

X7641131L01

X76 _4G @

X76 _4G @

G3

G1

G4

H22

J21

B22

D21

A19

D17

B14

D13

A11

B10

G8

A8

B6

H8

E5

K7

K22

K19

C21

D19

C19

D16

C13

D12

C11

C9

F8

C8

C5

H6

F6

K6

G22

C23

D23

F21

H19

C17

K15

F17

F14

A15

J14

H13

M10

F10

D9

J4

F22

A23

D24

E21

G19

B18

K17

G17

E14

C15

K13

G13

K10

G10

D8

K4

X76 8G

X76 8G

X7641131L04

X7641131L04

X76 _8G @

X76 _8G @

PEG _CO MP

+VCC P

12

RC2

RC2

24.9 _0 402 _1 %

24.9 _0 402 _1 %

2

1

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

5

4

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

2011/06/02 2013/10/28

2011/06/02 2013/10/28

2011/06/02 2013/10/28

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Tit le

Tit le

Tit le

P05-CPU(1/6) DMI,FDI ,PEG

P05-CPU(1/6) DMI,FDI ,PEG

P05-CPU(1/6) DMI,FDI ,PEG

Size Docu me nt N umb er Rev

Size Docu me nt N umb er Rev

Size Docu me nt N umb er Rev

LA-8821P

LA-8821P

LA-8821P

Date : She et of

Date : She et of

Date : She et of

5 54Frida y, S ep tem ber 28, 20 12

5 54Frida y, S ep tem ber 28, 20 12

5 54Frida y, S ep tem ber 28, 20 12

1

1.0

1.0

1.0

Page 6

5

4

3

2

1

PM, XDP, CLK, S3 Reduce, PLTRST

PU/PD for JTAG signals

@

@

UCPU1 B

RC34

0_0 402 _5 %~D

0_0 402 _5 %~D

1 2

1 3

D

D

12

R1035

100K_0402_5%~D

R1035

100K_0402_5%~D

QC2

QC2

BSS 138 -G_ SOT 23 -3

BSS 138 -G_ SOT 23 -3

G

G

2

1

CC69

CC69

.047 U_0 40 2_1 6V7 K~D

.047 U_0 40 2_1 6V7 K~D

2

DRAM RST _C NTRL [ 15]

UCPU1 B

F49

PROC_SELECT#

C57

PROC_DETECT#

C49

CATERR#

A48

PECI

C45

PROCHOT#

D45

THERMTRIP#

C48

PM_SYNC

B46

UNCOREPWRGOOD

BE45

SM_DRAMPWROK

D44

RESET#

IVY-B RIDG E_ BGA 102 3

IVY-B RIDG E_ BGA 102 3

4.99 K_ 040 2_ 1%

4.99 K_ 040 2_ 1%

RC77

RC77

H_DRA MR ST #

12

S

S

Deep S3 Support

Non Deep S3(De-pop R1035)

MISC THERMAL PWR MANAGEMENT

MISC THERMAL PWR MANAGEMENT

BCLK

BCLK#

DPLL_REF_CLK

DPLL_REF_CLK#

CLOCKS

CLOCKS

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

DDR3

MISC

DDR3

MISC

PRDY#

PREQ#

TCK

TMS

TRST#

TDI

TDO

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

JTAG & BPM

JTAG & BPM

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

3

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

J3

H2

AG3

AG1

AT30

H_DRA MR ST #

BF44

SM_ RCO MP 0

BE43

SM_ RCO MP 1

BG43

SM_ RCO MP 2

DDR3 Compensation Signals

N53

XDP_ PRD Y#

N55

XDP_ PRE Q#

L56

XDP_ TC K

L55

XDP_ TM S

J58

XDP_ TR ST #

M60

XDP_ TD I

L59

XDP_ TD O

K58

XDP_ DBR ESE T# _R

G58

E55

E59

G55

G59

H60

J59

J61

POWEROK

Issued Date

Issued Date

Issued Date

CLK_ CPU _DM I [17]

CLK_ CPU _DM I# [17 ]

CLK_ CPU _DPL L [17 ]

CLK_ CPU _DPL L# [1 7]

1 2

RC55 1 40_ 04 02_ 1%R C55 1 40_ 040 2_ 1%

1 2

RC58 2 5.5 _.4 02_ 1%R C58 2 5.5_ .40 2_ 1%

1 2

RC60 2 00_ 04 02_ 1%R C60 2 00_ 040 2_ 1%

RC56 0 _04 02 _5% ~D

RC56 0 _04 02 _5% ~D

T22 4@ T2 24@

T22 5@ T2 25@

T22 6@ T2 26@

T22 7@ T2 27@

T22 8@ T2 28@

T22 9@ T2 29@

T23 0@ T2 30@

T23 1@ T2 31@

PM_ DRA M_ PWRG D[1 8]

CPU1 .5V _S3 _GA TE[32,3 5,4 2,9 ]

2011/06/02 2013/10/28

2011/06/02 2013/10/28

2011/06/02 2013/10/28

Width 20 mils, Spacing 13mils, Length < 500mil

T24 1@ T2 41@

SHORT

1 2

@

@

+3V _PCH

RC4

RC4

1K_ 040 2_ 5%~ D

1K_ 040 2_ 5%~ D

1 2

SHORT

1 2

RC11 0_04 02_ 5% ~D

RC11 0_04 02_ 5% ~D

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

XDP_ DBR ESE T#

@

@

2

XDP_ DBR ESE T# [18]

+3V _PCH

1

2

CC65

CC65

.1U_0402_16V7K~D

.1U_0402_16V7K~D

5

UC1

UC1

1

P

B

4

Y

2

A

G

74A HC1G 09 GW_T SS OP 5

74A HC1G 09 GW_T SS OP 5

3

RUN_O N_C PU1. 5VS 3#[32]

Place close to PCH or EC

D D

+VCC P

RC43

RC43

62_ 040 2_ 5%

62_ 040 2_ 5%

H_T HERM T RIP#[20]

H_PM _S YNC[18]

H_CP UPWR GD[20]

1 2

H_CP UPWR GD_R

1

2

CC68

CC68

.1U_0402_16V7K~D

.1U_0402_16V7K~D

5

UC2

UC2

P

4

BUFO _CP U_RS T#

Y

G

3

SN74 LV C1G 07DC KR_ SC7 0-5~ D

SN74 LV C1G 07DC KR_ SC7 0-5~ D

1 2

1 2

H_PR OCHO T#[35, 38]

C C

RC44 1 0K_ 040 2_ 5%~ DRC4 4 10K _04 02 _5% ~D

Avoid stub in the PWRGD path

while placing resistors RC44 & RC53

+3V S

PLT _RS T#[19, 27, 28, 35]

B B

1

NC

2

A

RC13 0 0_040 2_5 %~D@ RC13 0 0_040 2_5 %~ D@

Place close to PCH reset Logic Gate

For CPU S3 Power Reduce

10

1 2

DDR3_ DRA MRS T#[11, 12, 13, 14]

Deep S3 Support

A A

Non Deep S3

DRAM RST _C NTRL _E C[35]

DRAM RST _C NTRL _P CH[17]

DDR3_ DRA MRS T# _R

RC76 1 K_0 40 2_5 %~DRC76 1K _04 02_ 5% ~D

SHORT

1 2

RC14 5 0_0 402 _5 %~D

RC14 5 0_0 402 _5 %~D

1 2

RC72 0 _04 02 _5% ~D@R C72 0 _04 02_ 5% ~D@

@

@

H_PR OCHO T#

+VCC P

12

RC32

RC32

T24 8@ T2 48@

T1@ T1@

H_PE CI[2 0,35 ]

1 2

RC41 56_ 040 2_ 5%RC41 56_ 040 2_ 5%

SHORT

1 2

RC49 0_0 402 _5 %~D

RC49 0_0 402 _5 %~D

@

@

SHORT

1 2

RC53 0_0 402 _5 %~D

RC53 0_0 402 _5 %~D

@

@

75_0402_5%

75_0402_5%

1 2

RC33 4 3_0 40 2_1 %RC33 43_ 04 02_ 1%

+1.3 5V

12

RC75

RC75

1K_ 040 2_ 5%~ D

1K_ 040 2_ 5%~ D

H_CA TE RR#

H_PR OCHO T# _R

H_T HERM T RIP# _R

H_CP UPWR GD_R

VDDP WRGO OD_ R

BUF_ CPU_ RST #

BUF_ CPU_ RST #

12

@ RC34

@

RC74 0 _04 02 _5% ~D@RC7 4 0_ 040 2_5 %~ D@

DRAM RST _C NTRL

CPU DRAMRST# Control Option for Deep S3

5

4

XDP_ TM S

XDP_ TD I

XDP_ PRE Q#

XDP_ TD O

XDP_ TC K

XDP_ TR ST #

12

RC8

RC8

200 _04 02 _1%

200 _04 02 _1%

VDDP WRGO OD

RC19

@ RC19

@

39_ 040 2_ 1%

39_ 040 2_ 1%

1 2

13

D

D

@

@

S

S

QC1

QC1

DII-DM N65 D8L W-7~ D

DII-DM N65 D8L W-7~ D

1 2

RC42 1 K_0 402 _5 %~DRC42 1 K_0 402 _5 %~D

Place close to CPU

1 2

RC57 1 30_ 04 02_ 1%~ DRC57 13 0_0 402 _1 %~D

XDP_ DBR ESE T#

+1.3 5V_ CPU _VD DQ

2

G

G

1/17, Change P/N to SB0000 0UO00

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Tit le

Tit le

Tit le

P06-CPU(2/6) PM,XDP,CLK,S3, PLT

P06-CPU(2/6) PM,XDP,CLK,S3, PLT

P06-CPU(2/6) PM,XDP,CLK,S3, PLT

Size Docu me nt N umb er Rev

Size Docu me nt N umb er Rev

Size Docu me nt N umb er Rev

LA-8821P

LA-8821P

LA-8821P

Date : She et of

Date : She et of

Date : She et of

1

1 2

1 2

1 2

1 2

1 2

1 2

VDDP WRGO OD_ R

+VCC P

RC4551_ 040 2_ 5% RC4551_ 040 2_ 5%

RC4651_ 040 2_ 5% RC4651_ 040 2_ 5%

RC4751_ 040 2_ 5% @RC4751_04 02_ 5% @

RC4851_ 040 2_ 5% RC4851_ 040 2_ 5%

RC5251_ 040 2_ 5% RC5251_ 040 2_ 5%

RC5451_ 040 2_ 5% RC5451_ 040 2_ 5%

+3V S

1.0

1.0

1.0

6 54Frida y, S ep tem ber 28, 20 12

6 54Frida y, S ep tem ber 28, 20 12

6 54Frida y, S ep tem ber 28, 20 12

Page 7

5

4

3

2

1

D D

DDR_A _D[ 0..6 3][11,1 2]

C C

B B

DDR_A _D0

DDR_A _D1

DDR_A _D2

DDR_A _D3

DDR_A _D4

DDR_A _D5

DDR_A _D6

DDR_A _D7

DDR_A _D8

DDR_A _D9

DDR_A _D1 0

DDR_A _D1 1

DDR_A _D1 2

DDR_A _D1 3

DDR_A _D1 4

DDR_A _D1 5

DDR_A _D1 6

DDR_A _D1 7

DDR_A _D1 8

DDR_A _D1 9

DDR_A _D2 0

DDR_A _D2 1

DDR_A _D2 2

DDR_A _D2 3

DDR_A _D2 4

DDR_A _D2 5

DDR_A _D2 6

DDR_A _D2 7

DDR_A _D2 8

DDR_A _D2 9

DDR_A _D3 0

DDR_A _D3 1

DDR_A _D3 2

DDR_A _D3 3

DDR_A _D3 4

DDR_A _D3 5

DDR_A _D3 6

DDR_A _D3 7

DDR_A _D3 8

DDR_A _D3 9

DDR_A _D4 0

DDR_A _D4 1

DDR_A _D4 2

DDR_A _D4 3

DDR_A _D4 4

DDR_A _D4 5

DDR_A _D4 6

DDR_A _D4 7

DDR_A _D4 8

DDR_A _D4 9

DDR_A _D5 0

DDR_A _D5 1

DDR_A _D5 2

DDR_A _D5 3

DDR_A _D5 4

DDR_A _D5 5

DDR_A _D5 6

DDR_A _D5 7

DDR_A _D5 8

DDR_A _D5 9

DDR_A _D6 0

DDR_A _D6 1

DDR_A _D6 2

DDR_A _D6 3

DDR_A _B S0[1 1,1 2,15 ]

DDR_A _B S1[1 1,1 2,15 ]

DDR_A _B S2[1 1,1 2,15 ]

DDR_A _CA S#[1 1,1 2,1 5]

DDR_A _RA S#[1 1,1 2,1 5]

DDR_A _WE #[11,1 2,15 ]

@

@

UCPU1 C

UCPU1 C

AG6

AJ6

AP11

AL6

AJ10

AJ8

AL8

AL7

AR11

AP6

AU6

AV9

AR6

AP8

AT13

AU13

BC7

BB7

BA13

BB11

BA7

BA9

BB9

AY13

AV14

AR14

AY17

AR19

BA14

AU14

BB14

BB17

BA45

AR43

AW48

BC48

BC45

AR45

AT48

AY48

BA49

AV49

BB51

AY53

BB49

AU49

BA53

BB55

BA55

AV56

AP50

AP53

AV54

AT54

AP56

AP52

AN57

AN53

AG56

AG53

AN55

AN52

AG55

AK56

BD37

BF36

BA28

BE39

BD39

AT41

IVY-B RIDG E_ BGA 102 3

IVY-B RIDG E_ BGA 102 3

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

AU36

SA_CK[0]

AV36

SA_CK#[0]

AY26

SA_CKE[0]

AT40

SA_CK[1]

AU40

SA_CK#[1]

BB26

SA_CKE[1]

BB40

SA_CS#[0]

BC41

SA_CS#[1]

AY40

SA_ODT[0]

BA41

SA_ODT[1]

AL11

DDR_A _DQ S#0

SA_DQS#[0]

AR8

DDR_A _DQ S#1

SA_DQS#[1]

AV11

DDR_A _DQ S#2

SA_DQS#[2]

AT17

DDR_A _DQ S#3

SA_DQS#[3]

AV45

DDR_A _DQ S#4

SA_DQS#[4]

AY51

DDR_A _DQ S#5

SA_DQS#[5]

AT55

DDR_A _DQ S#6

SA_DQS#[6]

AK55

DDR_A _DQ S#7

SA_DQS#[7]

AJ11

DDR_A _DQ S0

SA_DQS[0]

AR10

DDR_A _DQ S1

SA_DQS[1]

AY11

DDR_A _DQ S2

SA_DQS[2]

AU17

DDR_A _DQ S3

SA_DQS[3]

AW45

DDR_A _DQ S4

SA_DQS[4]

AV51

DDR_A _DQ S5

SA_DQS[5]

AT56

DDR_A _DQ S6

SA_DQS[6]

AK54

DDR_A _DQ S7

SA_DQS[7]

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

BG35

DDR_A _M A0

BB34

DDR_A _M A1

BE35

DDR_A _M A2

BD35

DDR_A _M A3

AT34

DDR_A _M A4

AU34

DDR_A _M A5

BB32

DDR_A _M A6

AT32

DDR_A _M A7

AY32

DDR_A _M A8

AV32

DDR_A _M A9

BE37

DDR_A _M A1 0

BA30

DDR_A _M A1 1

BC30

DDR_A _M A1 2

AW41

DDR_A _M A1 3

AY28

DDR_A _M A1 4

AU26

DDR_A _M A1 5

M_C LK_ DDR0 [11 ,12 ,15 ]

M_C LK_ DDR# 0 [11,1 2,1 5]

DDR_A _CK E0 [1 1,1 2,1 5]

DDR_A _CS 0# [1 1,1 2,1 5]

M_O DT 0 [11, 12, 15]

DDR_A _DQ S#[ 0..7 ] [11,1 2]

DDR_A _DQ S[0 ..7] [11 ,12 ]

DDR_A _M A[0 ..15 ] [11 ,12 ,15 ]

DDR_B _D[ 0..6 3][13,1 4]

DDR_B _B S0[1 3,1 4,15 ]

DDR_B _B S1[1 3,1 4,15 ]

DDR_B _B S2[1 3,1 4,15 ]

DDR_B _CA S#[1 3,1 4,1 5]

DDR_B _RA S#[1 3,1 4,1 5]

DDR_B _WE #[13,1 4,15 ]

DDR_B _D0

DDR_B _D1

DDR_B _D2

DDR_B _D3

DDR_B _D4

DDR_B _D5

DDR_B _D6

DDR_B _D7

DDR_B _D8

DDR_B _D9

DDR_B _D1 0

DDR_B _D1 1

DDR_B _D1 2

DDR_B _D1 3

DDR_B _D1 4

DDR_B _D1 5

DDR_B _D1 6

DDR_B _D1 7

DDR_B _D1 8

DDR_B _D1 9

DDR_B _D2 0

DDR_B _D2 1

DDR_B _D2 2

DDR_B _D2 3

DDR_B _D2 4

DDR_B _D2 5

DDR_B _D2 6

DDR_B _D2 7

DDR_B _D2 8

DDR_B _D2 9

DDR_B _D3 0

DDR_B _D3 1

DDR_B _D3 2

DDR_B _D3 3

DDR_B _D3 4

DDR_B _D3 5

DDR_B _D3 6

DDR_B _D3 7

DDR_B _D3 8

DDR_B _D3 9

DDR_B _D4 0

DDR_B _D4 1

DDR_B _D4 2

DDR_B _D4 3

DDR_B _D4 4

DDR_B _D4 5

DDR_B _D4 6

DDR_B _D4 7

DDR_B _D4 8

DDR_B _D4 9

DDR_B _D5 0

DDR_B _D5 1

DDR_B _D5 2

DDR_B _D5 3

DDR_B _D5 4

DDR_B _D5 5

DDR_B _D5 6

DDR_B _D5 7

DDR_B _D5 8

DDR_B _D5 9

DDR_B _D6 0

DDR_B _D6 1

DDR_B _D6 2

DDR_B _D6 3

DDR structure 1R X 8

DDR structure 1R X 8

@

@

UCPU1 D

UCPU1 D

AL4

SB_DQ[0]

AL1

SB_DQ[1]

AN3

SB_DQ[2]

AR4

SB_DQ[3]

AK4

SB_DQ[4]

AK3

SB_DQ[5]

AN4

SB_DQ[6]

AR1

SB_DQ[7]

AU4

SB_DQ[8]

AT2

SB_DQ[9]

AV4

SB_DQ[10]

BA4

SB_DQ[11]

AU3

SB_DQ[12]

AR3

SB_DQ[13]

AY2

SB_DQ[14]

BA3

SB_DQ[15]

BE9

SB_DQ[16]

BD9

SB_DQ[17]

BD13

SB_DQ[18]

BF12

SB_DQ[19]

BF8

SB_DQ[20]

BD10

SB_DQ[21]

BD14

SB_DQ[22]

BE13

SB_DQ[23]

BF16

SB_DQ[24]

BE17

SB_DQ[25]

BE18

SB_DQ[26]

BE21

SB_DQ[27]

BE14

SB_DQ[28]

BG14

SB_DQ[29]

BG18

SB_DQ[30]

BF19

SB_DQ[31]

BD50

SB_DQ[32]

BF48

SB_DQ[33]

BD53

SB_DQ[34]

BF52

SB_DQ[35]

BD49

SB_DQ[36]

BE49

SB_DQ[37]

BD54

SB_DQ[38]

BE53

SB_DQ[39]

BF56

SB_DQ[40]

BE57

SB_DQ[41]

BC59

SB_DQ[42]

AY60

SB_DQ[43]

BE54

SB_DQ[44]

BG54

SB_DQ[45]

BA58

SB_DQ[46]

AW59

SB_DQ[47]

AW58

SB_DQ[48]

AU58

SB_DQ[49]

AN61

SB_DQ[50]

AN59

SB_DQ[51]

AU59

SB_DQ[52]

AU61

SB_DQ[53]

AN58

SB_DQ[54]

AR58

SB_DQ[55]

AK58

SB_DQ[56]

AL58

AG58

AG59

AM60

AL59

AF61

AH60

BG39

BD42

AT22

AV43

BF40

BD45

IVY-B RIDG E_ BGA 102 3

IVY-B RIDG E_ BGA 102 3

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_CK[0]

SB_CK#[0]

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

BA34

AY34

AR22

BA36

BB36

BF27

BE41

BE47

AT43

BG47

AL3

DDR_B _DQ S#0

AV3

DDR_B _DQ S#1

BG11

DDR_B _DQ S#2

BD17

DDR_B _DQ S#3

BG51

DDR_B _DQ S#4

BA59

DDR_B _DQ S#5

AT60

DDR_B _DQ S#6

AK59

DDR_B _DQ S#7

AM2

DDR_B _DQ S0

AV1

DDR_B _DQ S1

BE11

DDR_B _DQ S2

BD18

DDR_B _DQ S3

BE51

DDR_B _DQ S4

BA61

DDR_B _DQ S5

AR59

DDR_B _DQ S6

AK61

DDR_B _DQ S7

BF32

DDR_B _M A0

BE33

DDR_B _M A1

BD33

DDR_B _M A2

AU30

DDR_B _M A3

BD30

DDR_B _M A4

AV30

DDR_B _M A5

BG30

DDR_B _M A6

BD29

DDR_B _M A7

BE30

DDR_B _M A8

BE28

DDR_B _M A9

BD43

DDR_B _M A1 0

AT28

DDR_B _M A1 1

AV28

DDR_B _M A1 2

BD46

DDR_B _M A1 3

AT26

DDR_B _M A1 4

AU22

DDR_B _M A1 5

M_C LK_ DDR2 [13 ,14 ,15 ]

M_C LK_ DDR# 2 [13,1 4,1 5]

DDR_B _CK E0 [1 3,1 4,1 5]

DDR_B _CS 0# [1 3,1 4,1 5]

M_O DT 2 [13, 14, 15]

DDR_B _DQ S#[ 0..7 ] [13,1 4]

DDR_B _DQ S[0 ..7] [13 ,14 ]

DDR_B _M A[0 ..15 ] [13 ,14 ,15 ]

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

5

4

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

2011/06/02 2013/10/28

2011/06/02 2013/10/28

2011/06/02 2013/10/28

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Tit le

Tit le

Tit le

P07-CPU(3/6) DDRIII

P07-CPU(3/6) DDRIII

P07-CPU(3/6) DDRIII

Size Docu me nt N umb er Rev

Size Docu me nt N umb er Rev

Size Docu me nt N umb er Rev

LA-8821P

LA-8821P

LA-8821P

Date : She et of

Date : She et of

Date : She et of

7 54Frida y, S ep tem ber 28, 20 12

7 54Frida y, S ep tem ber 28, 20 12

7 54Frida y, S ep tem ber 28, 20 12

1

1.0

1.0

1.0

Page 8

5

D D

CFG Straps for Processor

12

CFG2

RC781K_ 040 2_1 %~ D @RC781K_ 040 2_1 %~ D @

PEG Static Lane Reversal - CFG2 is for the 16x

1:(Default) Normal Operation;

Lane # definition matches socket pin

map definition

CFG2

0:Lane Reversed

*

12

CFG4

RC811K_ 040 2_1 %~ D RC8 11K_04 02 _1% ~D

Display Port Presence Strap

C C

1 : Disabled; No Physical Display Port

attached to Embedded Display Port

CFG4

0 : Enabled; An external Display

*

Port device is connected to the

Embedded Display Port

12

RC871K_ 040 2_1 %~ D @RC871K_ 040 2_1 %~ D @

12

RC861K_ 040 2_1 %~ D @RC861K_ 040 2_1 %~ D @

CFG5

CFG6

PCIE Port Bifurcation Straps

11: (Default) x16 - Device 1 functions

*

1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled

;function 2 disabled

CFG[6:5]

01: Reserved - (Device 1 function 1

disabled ; function 2 enabled)

00: x8,x4,x4 - Device 1 functions 1

B B

and 2 enabled

12

RC891K_ 040 2_1 %~ D @RC891K_ 040 2_1 %~ D @

CFG7

4

VCC_ DIE_ SE NSE

RC14 2

@ RC14 2

@

0_0 402 _5 %~D

0_0 402 _5 %~D

1 2

12

RC14 3

RC14 3

1K_ 040 2_ 1%~ D

1K_ 040 2_ 1%~ D

3

@

@

UCPU1 E

UCPU1 E

B50

CFG0

T23 2@ T2 32@

CFG1

T20 8@ T2 08@

CFG2

CFG3

T20 9@ T2 09@

CFG4

CFG5

CFG6

CFG7

CFG8

T21 3@ T2 13@

CFG9

T21 0@ T2 10@

CFG1 0

T21 1@ T2 11@

CFG1 1

T21 2@ T2 12@

CFG1 2

T23 5@ T2 35@

CFG1 3

T23 6@ T2 36@

CFG1 4

T23 7@ T2 37@

CFG1 5

T23 8@ T2 38@

CFG1 6

T21 4@ T2 14@

CFG1 7

T21 5@ T2 15@

CPU_ RSV D6

CPU_ RSV D7

12

RC14 4

RC14 4

1K_ 040 2_ 1%~ D

1K_ 040 2_ 1%~ D

C51

B54

D53

A51

C53

C55

H49

A55

H51

K49

K53

F53

G53

L51

F51

D52

L53

H43

K43

H45

K45

F48

H48

K48

BA19

AV19

AT21

BB21

BB19

AY21

BA22

AY22

AU19

AU21

BD21

BD22

BD25

BD26

BG22

BE22

BG26

BE26

BF23

BE24

IVY-B RIDG E_ BGA 102 3

IVY-B RIDG E_ BGA 102 3

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

VCC_VAL_SENSE

VSS_VAL_SENSE

VAXG_VAL_SENSE

VSSAXG_VAL_SENSE

VCC_DIE_SENSE

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RESERVED

RESERVED

DC_TEST_A4

DC_TEST_C4

DC_TEST_D3

DC_TEST_D1

DC_TEST_A58

DC_TEST_A59

DC_TEST_C59

DC_TEST_A61

DC_TEST_C61

DC_TEST_D61

DC_TEST_BD61

DC_TEST_BE61

DC_TEST_BE59

DC_TEST_BG61

DC_TEST_BG59

DC_TEST_BG58

DC_TEST_BG4

DC_TEST_BG3

DC_TEST_BE3

DC_TEST_BG1

DC_TEST_BE1

DC_TEST_BD1

BCLK_ITP

BCLK_ITP#

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

N59

N58

N42

L42

L45

L47

M13

M14

U14

W14

P13

AT49

K24

AH2

AG13

AM14

AM15

N50

A4

C4

D3

D1

A58

A59

C59

A61

C61

D61

BD61

BE61

BE59

BG61

BG59

BG58

BG4

BG3

BE3

BG1

BE1

BD1

CLK_ RES _IT P

CLK_ RES _IT P#

DC_T ES T_ C4_D 3

DC_T ES T_ A59 _C5 9

DC_T ES T_ A61 _C6 1

DC_T ES T_ BE6 1_B E5 9

DC_T ES T_ BG3 _BE 3

DC_T ES T_ BG1 _BE 1

2

T23 3@ T2 33@

T23 4@ T2 34@

1

PEG DEFER TRAINING

1: (Default) PEG Train immediately

*

following xxRESETB de assertion

CFG7

0: PEG Wait for BIOS for training

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

5

4

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

2011/06/02 2013/10/28

2011/06/02 2013/10/28

2011/06/02 2013/10/28

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Tit le

Tit le

Tit le

P08-CPU(4/6) RSVD,CFG

P08-CPU(4/6) RSVD,CFG

P08-CPU(4/6) RSVD,CFG

Size Docu me nt N umb er Rev

Size Docu me nt N umb er Rev

Size Docu me nt N umb er Rev

LA-8821P

LA-8821P

LA-8821P

Date : She et of

Date : She et of

Date : She et of

8 54Frida y, S ep tem ber 28, 20 12

8 54Frida y, S ep tem ber 28, 20 12

8 54Frida y, S ep tem ber 28, 20 12

1

1.0

1.0

1.0

Page 9

5

ULV-DC Icc(max)=33A

D D

C C

B B

A A

+VCC _COR E

@

@

UCPU1 F

UCPU1 F

A26

VCC[1]

A29

VCC[2]

A31

VCC[3]

A34

VCC[4]

A35

VCC[5]

A38

VCC[6]

A39

VCC[7]

A42

VCC[8]

C26

VCC[9]

C27

VCC[10]

C32

VCC[11]

C34

VCC[12]

C37

VCC[13]

C39

VCC[14]

C42

VCC[15]

D27

VCC[16]

D32

VCC[17]

D34

VCC[18]

D37

VCC[19]

D39

VCC[20]

D42

VCC[21]

E26

VCC[22]

E28

VCC[23]

E32

VCC[24]

E34

VCC[25]

E37

VCC[26]

E38

VCC[27]

F25

VCC[28]

F26

VCC[29]

F28

VCC[30]

F32

VCC[31]

F34

VCC[32]

F37

VCC[33]

F38

VCC[34]

F42

VCC[35]

G42

VCC[36]

H25

VCC[37]

H26

VCC[38]

H28

VCC[39]

H29

VCC[40]

H32

VCC[41]

H34

VCC[42]

H35

VCC[43]

H37

VCC[44]

H38

VCC[45]

H40

VCC[46]

J25

VCC[47]

J26

VCC[48]

J28

VCC[49]

J29

VCC[50]

J32

VCC[51]

J34

VCC[52]

J35

VCC[53]

J37

VCC[54]

J38

VCC[55]

J40

VCC[56]

J42

VCC[57]

K26

VCC[58]

K27

VCC[59]

K29

VCC[60]

K32

VCC[61]

K34

VCC[62]

K35

VCC[63]

K37

VCC[64]

K39

VCC[66]

K42

VCC[67]

L25

VCC[68]

L28

VCC[69]

L33

VCC[70]

L36

VCC[71]

L40

VCC[72]

N26

VCC[73]

N30

VCC[74]

N34

VCC[75]

N38

VCC[76]

IVY-B RIDG E_ BGA 102 3

IVY-B RIDG E_ BGA 102 3

POWER

POWER

AF46

VCCIO[1]

AG48

VCCIO[3]

AG50

VCCIO[4]

AG51

VCCIO[5]

AJ17

VCCIO[6]

AJ21

VCCIO[7]

AJ25

VCCIO[8]

AJ43

VCCIO[9]

AJ47

VCCIO[10]

AK50

VCCIO[11]

AK51

VCCIO[12]

AL14

VCCIO[13]

AL15

VCCIO[14]

AL16

VCCIO[15]

AL20

VCCIO[16]

AL22

VCCIO[17]

AL26

VCCIO[18]

AL45

VCCIO[19]

AL48

VCCIO[20]

AM16

VCCIO[21]

AM17

VCCIO[22]

AM21

VCCIO[23]

AM43

VCCIO[24]

AM47

VCCIO[25]

AN20

VCCIO[26]

AN42

VCCIO[27]

AN45

VCCIO[28]

AN48

VCCIO[29]

AA14

VCCIO[30]

AA15

VCCIO[31]

AB17

VCCIO[32]

AB20

PEG IO AND DDR IO

PEG IO AND DDR IO

VCCIO[33]

AC13

CORE SUPPLY

CORE SUPPLY

5

VCCIO[34]

VCCIO[35]

VCCIO[36]

VCCIO[37]

VCCIO[38]

VCCIO[39]

VCCIO[40]

VCCIO[41]

VCCIO[42]

VCCIO[43]

VCCIO[44]

VCCIO[45]

VCCIO[46]

VCCIO[47]

VCCIO[48]

VCCIO[49]

VCCIO50

VCCIO51

VCCIO_SEL

VCCPQE[1]

VCCPQE[2]

RAILS

RAILS

VIDALERT#

VIDSCLK

VIDSOUT

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSS_SENSE_VCCIO

SENSE LINES SVID QUIET

SENSE LINES SVID QUIET

+VCC _COR E

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

CC219

CC219

1

2

AD16

AD18

AD21

AE14

AE15

AF16

AF18

AF20

AG15

AG16

AG17

AG20

AG21

AJ14

AJ15

W16

W17

BC22

AM25

AN22

A44

B43

C44

F43

G43

AN16

AN17

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

CC220

CC220

H_VC CP_ SEL

VCCS ENS E_R

+VCC P

8.5A

+1.0 5VS _V CCPQ

1

CC22 4

CC22 4

1U_0 40 2_6 .3V 6K~ D

1U_0 40 2_6 .3V 6K~ D

2

+VCC P

H_CP U_S VIDA LRT #

H_CP U_S VIDCL K

H_CP U_S VIDDA T

+VCC _COR E

RC97 1 00_ 04 02_ 1%~ DRC 97 10 0_ 040 2_1 %~D

RC98 0 _04 02 _5% ~D@RC9 8 0_ 040 2_5 %~ D@

RC99 0 _04 02 _5% ~D@RC9 9 0_ 040 2_5 %~ D@

RC10 0 100_0 402 _1 %~DRC100 100 _04 02 _1% ~D

+VCC P

1 2

RC12 6 10_ 040 2_ 5%~ DRC1 26 10 _04 02 _5% ~D

1 2

RC12 9 10_ 040 2_ 5%~ DRC1 29 10 _04 02 _5% ~D

Place the PU

resistors close to CPU

+VCC P

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

1

1

CC221

CC221

2

2

Close to JCPU1

4

+1.3 5V_ CPU _VD DQ

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1

CC160

CC160

2

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

CC233

CC233

1

2

+1.8 VS

11

@

@

1 2

RC10 9 0_0 805 _5 %~D

RC10 9 0_0 805 _5 %~D

SHORT

@

T22 3@T22 3

+VCC P

RH28 0

@RH280

@

0_0 603 _5 %~D

0_0 603 _5 %~D

12

SHORT

1 2

RC93 7 5_0 40 2_5 %RC93 7 5_0 40 2_5 %

1 2

RC94 4 3_0 40 2_5 %~DRC9 4 43_ 04 02_ 5%~ D

1 2

RC92 0 _04 02 _5% ~D@RC9 2 0_ 040 2_5 %~ D@

1 2

RC96 0 _04 02 _5% ~D@RC9 6 0_ 040 2_5 %~ D@

1 2

RC95 1 30_ 04 02_ 5%~ DRC 95 13 0_ 040 2_5 %~D

RC95 close to CPU

1 2

1 2

1 2

1 2

+1.3 5V_ CPU _VD DQ

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

1

CC222

CC222

CC223

CC223

2

4

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1

2

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

1

2

+VCC SA

VIDALERT#

Connect one end of s eries-resistor 43±5% close t o

processor and pull-up to VCCI O through 75±5% on

the other end of the series-resist or towards Int el MVP 7.

1

2

1

1

1

CC164

CC164

CC162

CC162

CC163

CC163

CC161

CC161

2

2

2

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

CC238

CC238

1U_0402_6.3V6K~D

CC239

CC239

CC234

CC234

CC240

CC240

1

1

1

2

2

2

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1

1

1

CC167

CC167

CC168

CC168

2

2

2

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

@ CC227

@

@ CC226

@

1

1

1

CC227

CC226

2

2

2

+1.8 VS_ VCC PLL

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

@ CC172

@

1

1

1

CC172

CC174

CC174

2

2

2

VR_S VID _AL RT# [4 4]

VR_S VID _CL K [44]

VR_S VID _DA T [44]

+VCC P

VIDSOUT:

Requires a pull-up t o VCCIO through a pull-up res istor of 130 ±5% c lose to t he processor, and a pull-up

to VCCIO through a pull-up res istor of 130 ±5% c lose to I ntel MVP 7.

VIDSCLK:

Required pull-up to VC CIO through 55 ±5% close to Intel IMVP 7.

VCCS ENS E [44]

VSS SEN SE [44]

VCCIO _S ENSE [ 41]

VSS IO_ SEN SE [41]

1

2

1

2

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

CC169

CC169

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

@ CC228

@

CC228

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

CC175

CC175

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1

CC165

CC165

2

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

CC235

CC235

1

2

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

@ CC170

@

1

CC170

2

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

@ CC229

@

1

CC229

2

1

+

+

CC17 6

CC17 6

330 U_D2 _2 .5VM _R 6M ~D

330 U_D2 _2 .5VM _R 6M ~D

2

VCC_ AXG _S ENSE[44]

VSS _AX G_ SENS E[4 4]

CC231

CC231

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

CC241

CC241

1

2

1

2

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1

CC232

CC232

2

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

CC236

CC236

1

2

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

@ CC225

@

1

CC225

+

+

2

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

@ CC230

@

CC230

+VCC _GFX COR E_A XG

1

+

+

2

1

2

CC17 1

CC17 1

330 U_B 2_2 VM _R1 5M

330 U_B 2_2 VM _R1 5M

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

3

330U_B2_2VM_R15M

330U_B2_2VM_R15M

CC166

CC166

ULV-DC GT2 29A

ULV-DC GT1 18A

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

CC242

CC242

12

12

3

+VCC _GFX COR E_A XG

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

CC237

CC237

1

2

RC13 5

RC13 5

100 _04 02 _5% ~D

100 _04 02 _5% ~D

RC13 6

RC13 6

100 _04 02 _5% ~D

100 _04 02 _5% ~D

1.2A

+1.8 VS_ VCC PLL

+VCC SA

4A (ULV-DC)

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

THIS SHEET OF ENGI NEERING D RAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC . AND CONTAINS CON FIDENTIAL

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

AND TRADE SECR ET INFORMATION. THIS SHEET MAY N OT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVI SION OF R&D

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

DEPARTMENTEXCEPT AS AUTHOR IZED BY COMPALELEC TRONICS, I NC. N EITHER THIS SH EET NOR THE IN FORMATION IT CON TAINS

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

MAY BE USED BY OR DISCLOSED TOANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPALELECTRON ICS, IN C.

@

@

UCPU1 G

UCPU1 G

AA46

VAXG[1]

AB47

VAXG[2]

AB50

VAXG[3]

AB51

VAXG[4]

AB52

VAXG[5]

AB53

VAXG[6]

AB55

VAXG[7]

AB56

VAXG[8]

AB58

VAXG[9]

AB59

VAXG[10]

AC61

VAXG[11]

AD47

VAXG[12]

AD48

VAXG[13]

AD50

VAXG[14]

AD51

VAXG[15]

AD52

VAXG[16]

AD53

VAXG[17]

AD55

VAXG[18]

AD56

VAXG[19]

AD58

VAXG[20]

AD59

VAXG[21]

AE46

VAXG[22]

N45

VAXG[23]

P47

VAXG[24]

P48

VAXG[25]

P50

VAXG[26]

P51

VAXG[27]

P52

VAXG[28]

P53

VAXG[29]

P55

VAXG[30]

P56

VAXG[31]

P61

VAXG[32]

T48

VAXG[33]

T58

VAXG[34]

T59

VAXG[35]

T61

VAXG[36]

U46

VAXG[37]

V47

VAXG[38]

V48

VAXG[39]

V50

VAXG[40]

V51

VAXG[41]

V52

VAXG[42]

V53

VAXG[43]

V55

VAXG[44]

V56

VAXG[45]

V58

VAXG[46]

V59

VAXG[47]

W50

VAXG[48]

W51

VAXG[49]

W52

VAXG[50]

W53

VAXG[51]

W55

VAXG[52]

W56

VAXG[53]

W61

VAXG[54]

Y48

VAXG[55]

Y61

VAXG[56]

F45

VAXG_SENSE

G45

VSSAXG_SENSE

BB3

VCCPLL[1]

BC1

VCCPLL[2]

BC4

VCCPLL[3]

L17

VCCSA[1]

L21

VCCSA[2]

N16

VCCSA[3]

N20

VCCSA[4]

N22

VCCSA[5]

P17

VCCSA[6]

P20

VCCSA[7]

R16

VCCSA[8]

R18

VCCSA[9]

R21

VCCSA[10]

U15

VCCSA[11]

V16

VCCSA[12]

V17

VCCSA[13]

V18

VCCSA[14]

V21

VCCSA[15]

W20

VCCSA[16]

IVY-B RIDG E_ BGA 102 3

IVY-B RIDG E_ BGA 102 3

2011/06/02 2013/10/28

2011/06/02 2013/10/28

2011/06/02 2013/10/28

POWER

POWER

GRAPHICS

GRAPHICS

SENSE

LINES

SENSE

LINES

1.8V RAIL

1.8V RAIL

SA RAIL

SA RAIL

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

SA_DIMM_VREFDQ

VREF

VREF

SB_DIMM_VREFDQ

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

QUIET RAILS

QUIET RAILS

VDDQ_SENSE

VSS_SENSE_VDDQ

VCCSA_SENSE

SENSE LINES

SENSE LINES

VCCSA_VID[0]

VCCSA_VID[1]

VCCSA VID

lines

VCCSA VID

lines

2

+V_SM_VREF should

have 10 mil trace width

AY43

SM_VREF

BE7

BG7

AJ28

VDDQ[1]

AJ33

VDDQ[2]

AJ36

VDDQ[3]

AJ40

VDDQ[4]

AL30

VDDQ[5]

AL34

VDDQ[6]

AL38

VDDQ[7]

AL42

VDDQ[8]

AM33

VDDQ[9]

AM36

VDDQ[10]

AM40

VDDQ[11]

AN30

VDDQ[12]

AN34

VDDQ[13]

AN38

VDDQ[14]

AR26

VDDQ[15]

AR28

VDDQ[16]

AR30

VDDQ[17]

AR32

VDDQ[18]

AR34

VDDQ[19]

AR36

VDDQ[20]

AR40

VDDQ[21]

AV41

VDDQ[22]

AW26

VDDQ[23]

BA40

VDDQ[24]

BB28

VDDQ[25]

BG33

VDDQ[26]

AM28

VCCDQ[1]

AN26

VCCDQ[2]

BC43

BA43

U10

D48

D49

1

0_0 402 _5 %~D

0_0 402 _5 %~D

+VRE FDQ_ A

QC6

@ QC 6

+V_ SM_ VRE F

V_DD R_RE FA_ R [15]

V_DD R_RE FB_ R [15]

+1.3 5V_ CPU _VD DQ

5A

+0.6 75V S

RC10 6 0_0 402 _5 %~D@ RC 106 0 _04 02_ 5% ~D@

+1.3 5V_ CPU _VD DQ +1.3 5V

+1.3 5V_ CPU _VD DQ

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

1

CC218

CC218

2

Tit le

Tit le

Tit le

P09-CPU(5/6) PWR,BYPASS

P09-CPU(5/6) PWR,BYPASS

P09-CPU(5/6) PWR,BYPASS

Size Docu me nt N umb er Rev

Size Docu me nt N umb er Rev

Size Docu me nt N umb er Rev

LA-8821P

LA-8821P

LA-8821P

Date : She et of

Date : She et of

Date : She et of

@

AP2 302 GN-H F_SO T2 3-3

AP2 302 GN-H F_SO T2 3-3

CPU1 .5V _S3 _GA TE[32,3 5,4 2,6 ]

+V_ SM_ VRE F

1 2

12

CC18 2 0 .1U_ 04 02_ 10V 7K ~DCC182 0.1U_0 40 2_1 0V 7K~ D

12

CC18 4 0 .1U_ 04 02_ 10V 7K ~DCC184 0.1U_0 40 2_1 0V 7K~ D

12

CC18 1 0 .1U_ 04 02_ 10V 7K ~DCC181 0.1U_0 40 2_1 0V 7K~ D

12

CC18 3 0 .1U_ 04 02_ 10V 7K ~DCC183 0.1U_0 40 2_1 0V 7K~ D

VCCS A_S ENS E [43 ]

VCCS A_V ID0 [4 3]

VCCS A_V ID1 [4 3]

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

1

RCU1

@ RCU 1

@

1 2

123

+1.3 5V_ CPU _VD DQ

12

RC11 2

RC11 2

1K_ 040 2_ 5%~ D

1K_ 040 2_ 5%~ D

12

RC11 6

RC11 6

1K_ 040 2_ 5%~ D

1K_ 040 2_ 5%~ D

+V_ SM_ VRE F

12

RC14 1

@ RC1 41

@

100 K_0 40 2_5 %~D

100 K_0 40 2_5 %~D

9 54Frida y, S ep tem ber 28, 20 12

9 54Frida y, S ep tem ber 28, 20 12

9 54Frida y, S ep tem ber 28, 20 12

1.0

1.0

1.0

Page 10

5

4

3

2

1

D D

C C

B B

@

@

UCPU1 H

UCPU1 H

A13

A17

A21

A25

A28

A33

A37

A40

A45

A49

A53

A9

AA1

AA13

AA50

AA51

AA52

AA53

AA55

AA56

AA8

AB16

AB18

AB21

AB48

AB61

AC10

AC14

AC46

AC6

AD17

AD20

AD4

AD61

AE13

AE8

AF1

AF17

AF21

AF47

AF48

AF50

AF51

AF52

AF53

AF55

AF56

AF58

AF59

AG10

AG14

AG18

AG47

AG52

AG61

AG7

AH4

AH58

AJ13

AJ16

AJ20

AJ22

AJ26

AJ30

AJ34

AJ38

AJ42

AJ45

AJ48

AJ7

AK1

AK52

AL10

AL13

AL17

AL21

AL25

AL28

AL33

AL36

AL40

AL43

AL47

AL61

AM13

AM20

AM22

AM26

AM30

AM34

IVY-B RIDG E_ BGA 102 3

IVY-B RIDG E_ BGA 102 3

VSS[1]

VSS[2]

VSS[3]

VSS[4]

VSS[5]

VSS[6]

VSS[7]

VSS[8]

VSS[9]

VSS[10]

VSS[11]

VSS[12]

VSS[13]

VSS[14]

VSS[15]

VSS[16]

VSS[17]

VSS[18]

VSS[19]

VSS[20]

VSS[21]

VSS[22]

VSS[23]

VSS[24]

VSS[25]

VSS[26]

VSS[27]

VSS[28]

VSS[29]

VSS[30]

VSS[31]

VSS[32]

VSS[33]

VSS[34]

VSS[35]

VSS[36]

VSS[37]

VSS[38]

VSS[39]

VSS[40]

VSS[41]

VSS[42]

VSS[43]

VSS[44]

VSS[45]

VSS[46]

VSS[47]

VSS[48]

VSS[49]

VSS[50]

VSS[51]

VSS[52]

VSS[53]

VSS[54]

VSS[55]

VSS[56]

VSS[57]

VSS[58]

VSS[59]

VSS[60]

VSS[61]

VSS[62]

VSS[63]

VSS[64]

VSS[65]

VSS[66]

VSS[67]

VSS[68]

VSS[69]

VSS[70]

VSS[71]

VSS[72]

VSS[73]

VSS[74]

VSS[75]

VSS[76]

VSS[77]

VSS[78]

VSS[79]

VSS[80]

VSS[81]

VSS[82]

VSS[83]

VSS[84]

VSS[85]

VSS[86]

VSS[87]

VSS[88]

VSS[89]

VSS[90]

VSS

VSS

VSS[91]

VSS[92]

VSS[93]

VSS[94]

VSS[95]

VSS[96]

VSS[97]

VSS[98]

VSS[99]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[162]

VSS[163]

VSS[164]

VSS[165]

VSS[166]

VSS[167]

VSS[168]

VSS[169]

VSS[170]

VSS[171]

VSS[172]

VSS[173]

VSS[174]

VSS[175]

VSS[176]

VSS[177]

VSS[178]

VSS[179]

VSS[180]

@

@

UCPU1 I

AM38

AM4

AM42

AM45

AM48

AM58

AN1

AN21

AN25

AN28

AN33

AN36

AN40

AN43

AN47

AN50

AN54

AP10

AP51

AP55

AP7

AR13

AR17

AR21

AR41

AR48

AR61

AR7

AT14

AT19

AT36

AT4

AT45

AT52

AT58

AU1

AU11

AU28

AU32

AU51

AU7

AV17

AV21

AV22

AV34

AV40

AV48

AV55

AW13

AW43

AW61

AW7

AY14

AY19

AY30

AY36

AY4

AY41

AY45

AY49

AY55

AY58

AY9

BA1

BA11

BA17

BA21

BA26

BA32

BA48

BA51

BB53

BC13

BC5

BC57

BD12

BD16

BD19

BD23

BD27

BD32

BD36

BD40

BD44

BD48

BD52

BD56

BD8

BE5

BG13

UCPU1 I

BG17

VSS[181]

BG21

VSS[182]

BG24

VSS[183]

BG28

VSS[184]

BG37

VSS[185]

BG41

VSS[186]

BG45

VSS[187]

BG49

VSS[188]

BG53

VSS[189]

BG9

VSS[190]

C29

VSS[191]

C35

VSS[192]

C40

VSS[193]

D10

VSS[194]

D14

VSS[195]

D18

VSS[196]

D22

VSS[197]

D26

VSS[198]

D29

VSS[199]

D35

VSS[200]

D4

VSS[201]

D40

VSS[202]

D43

VSS[203]

D46

VSS[204]

D50

VSS[205]

D54

VSS[206]

D58

VSS[207]

D6

VSS[208]

E25

VSS[209]

E29

VSS[210]

E3

VSS[211]

E35

VSS[212]

E40

VSS[213]

F13

VSS[214]

F15

VSS[215]

F19

VSS[216]

F29

VSS[217]

F35

VSS[218]

F40

VSS[219]

F55