Page 1

8

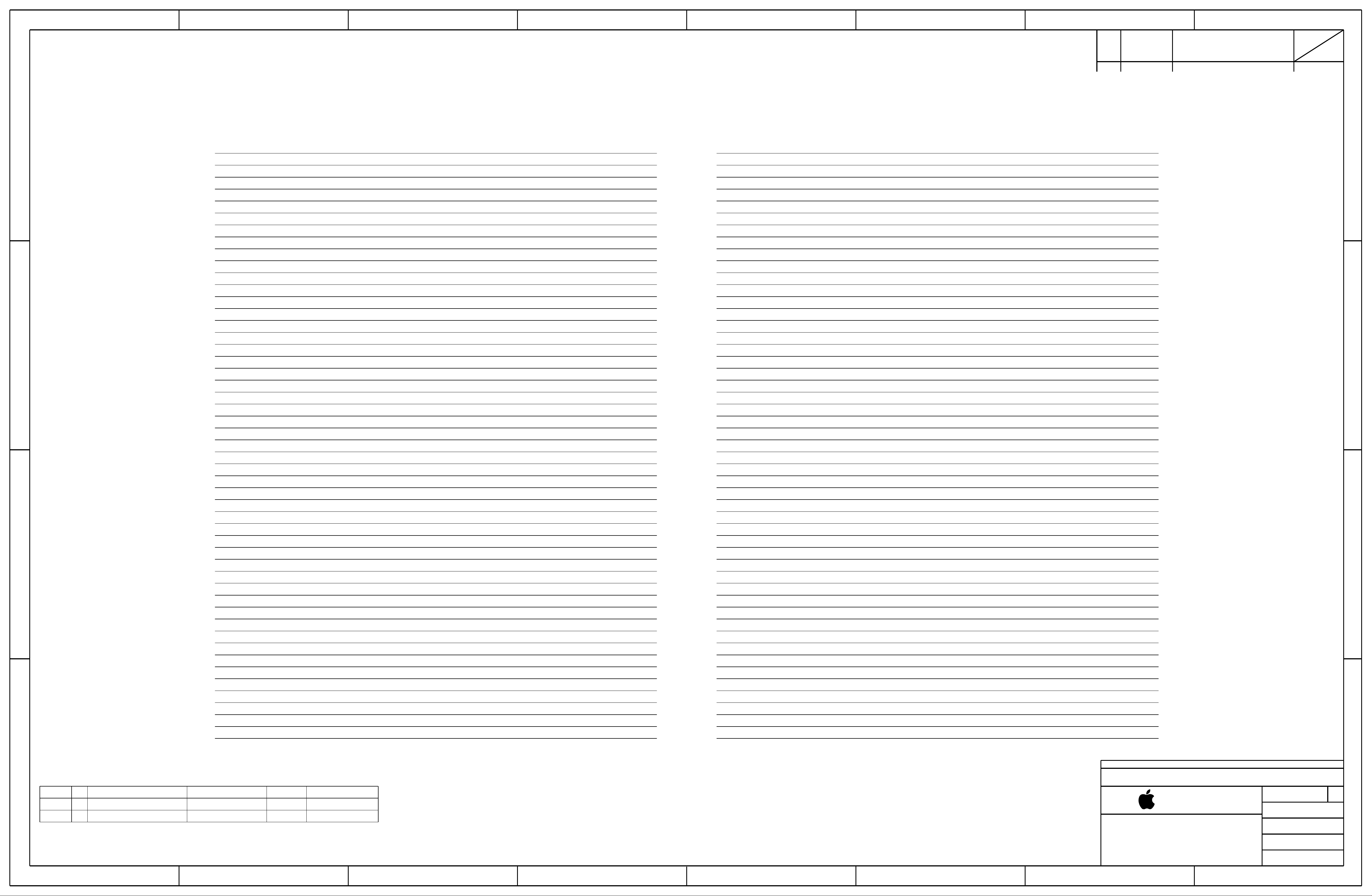

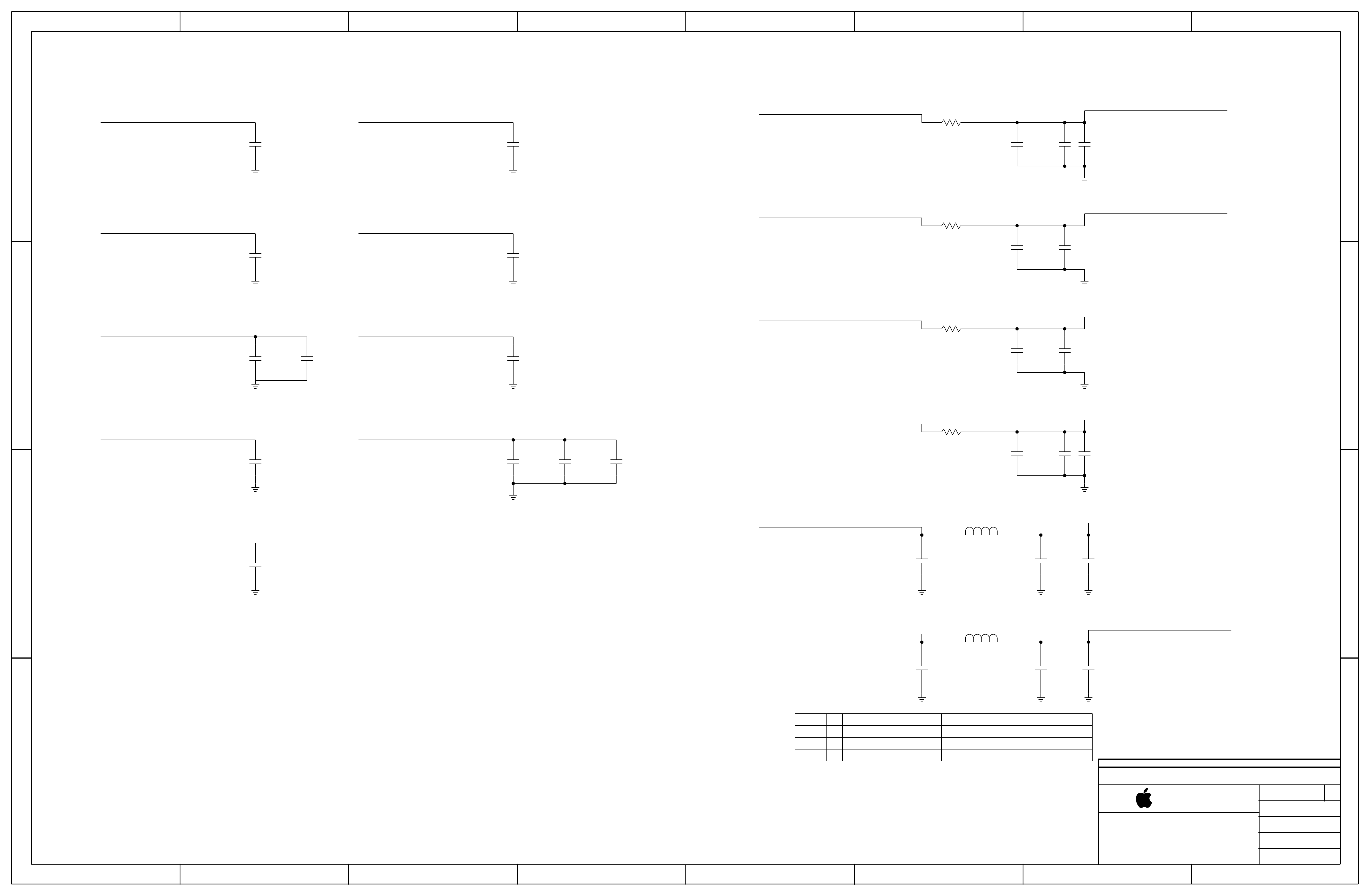

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

7

6 5 4 3

X1032 MLB BTTF

LAST_MODIFICATION=Thu Aug 9 14:09:34 2018

LAST_MODIFICATION=Thu Aug 9 14:09:34 2018

2 1

ECNREV DESCRIPTION OF REVISION

CK

APPD

DATE

2018-08-0900134733492 ENGINEERING RELEASED

D

1

2

3

1

2

3

44

5

5

6 6

7

8

9

10

11

12

13

8

9

10 03/30/2018

11

12

13

Table of Contents

BOM Configuration

BOM Configuration

PD Parts

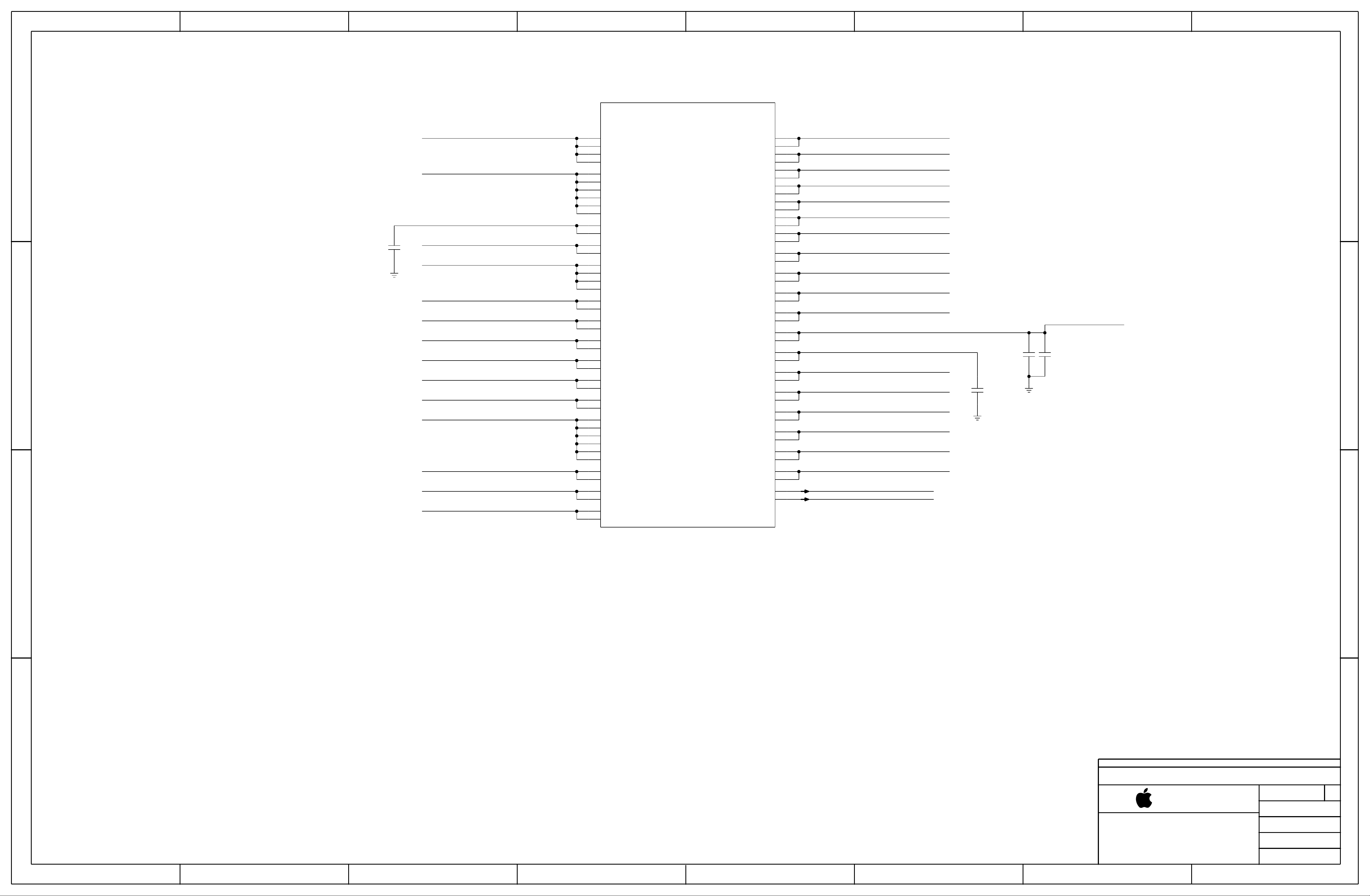

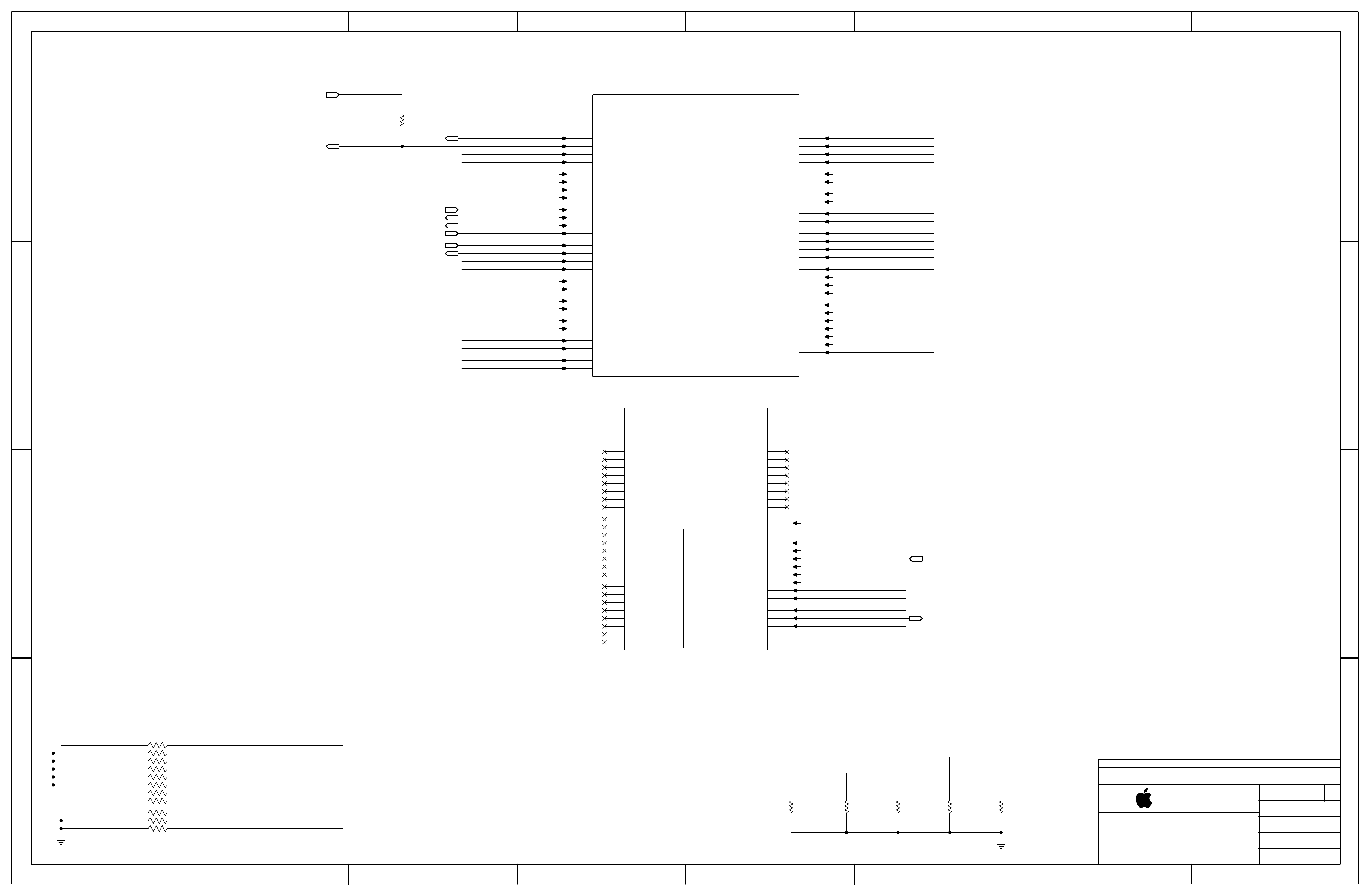

CPU GFX

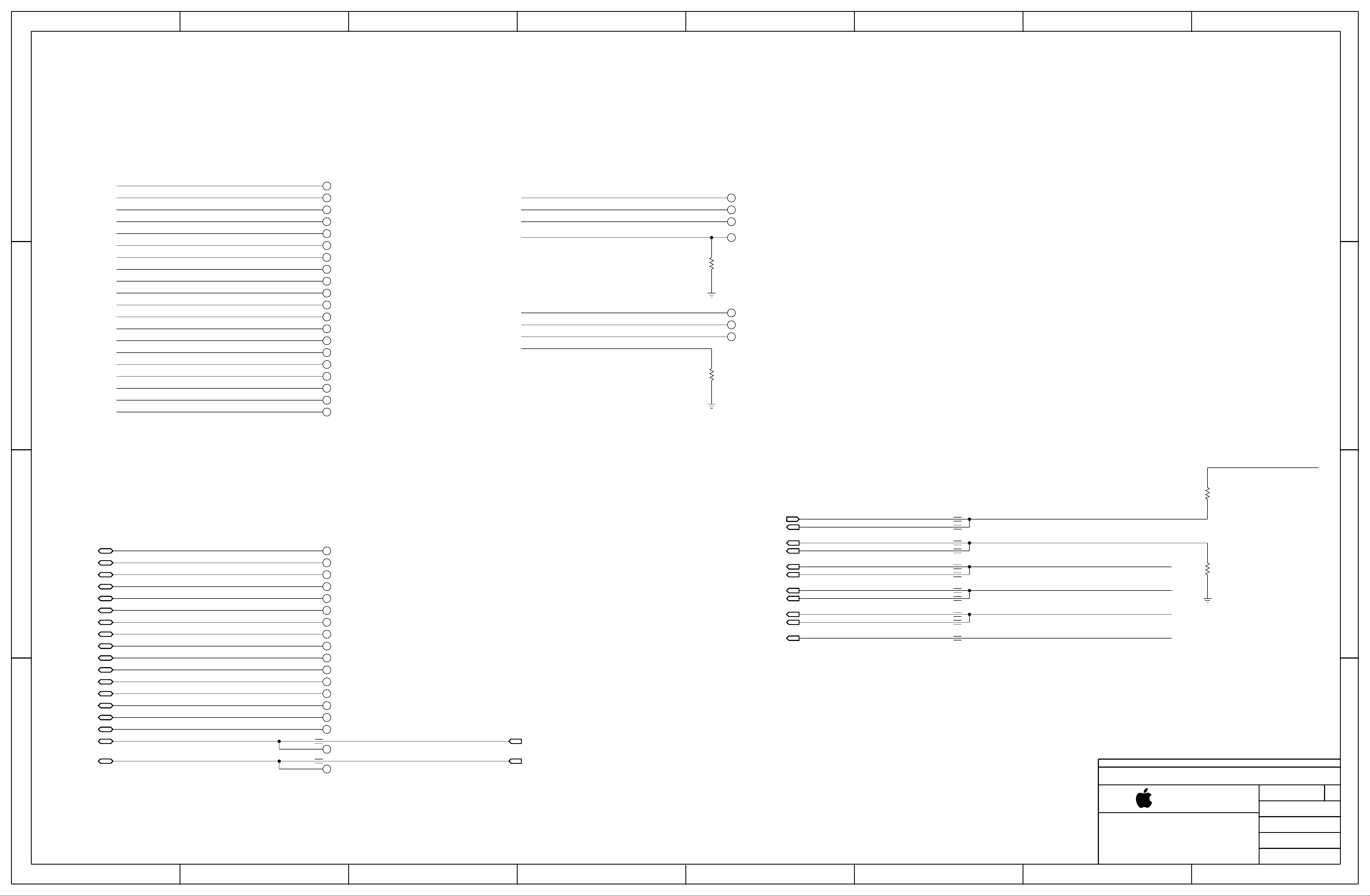

CPU Misc/JTAG/CFG/RSVD

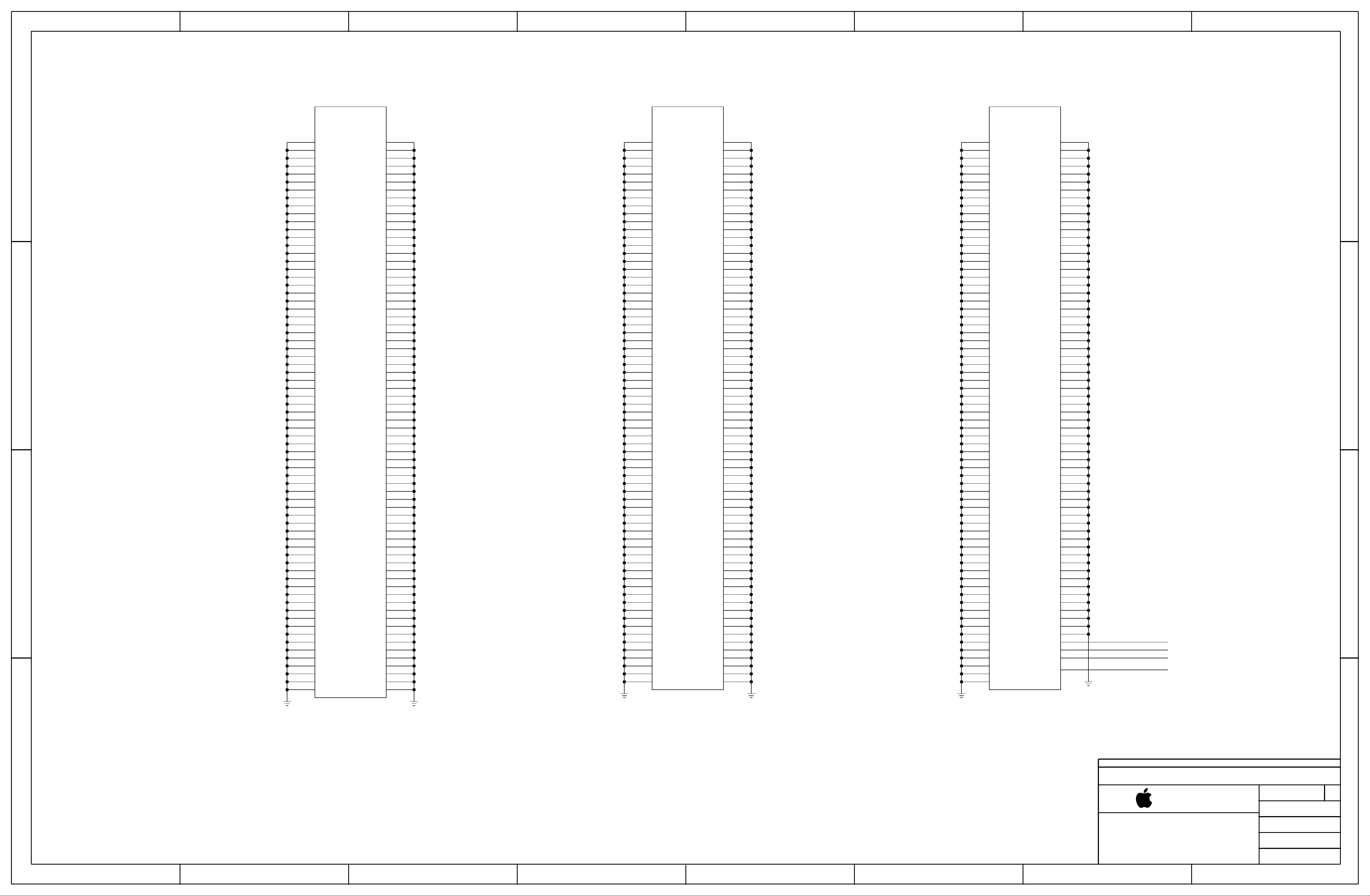

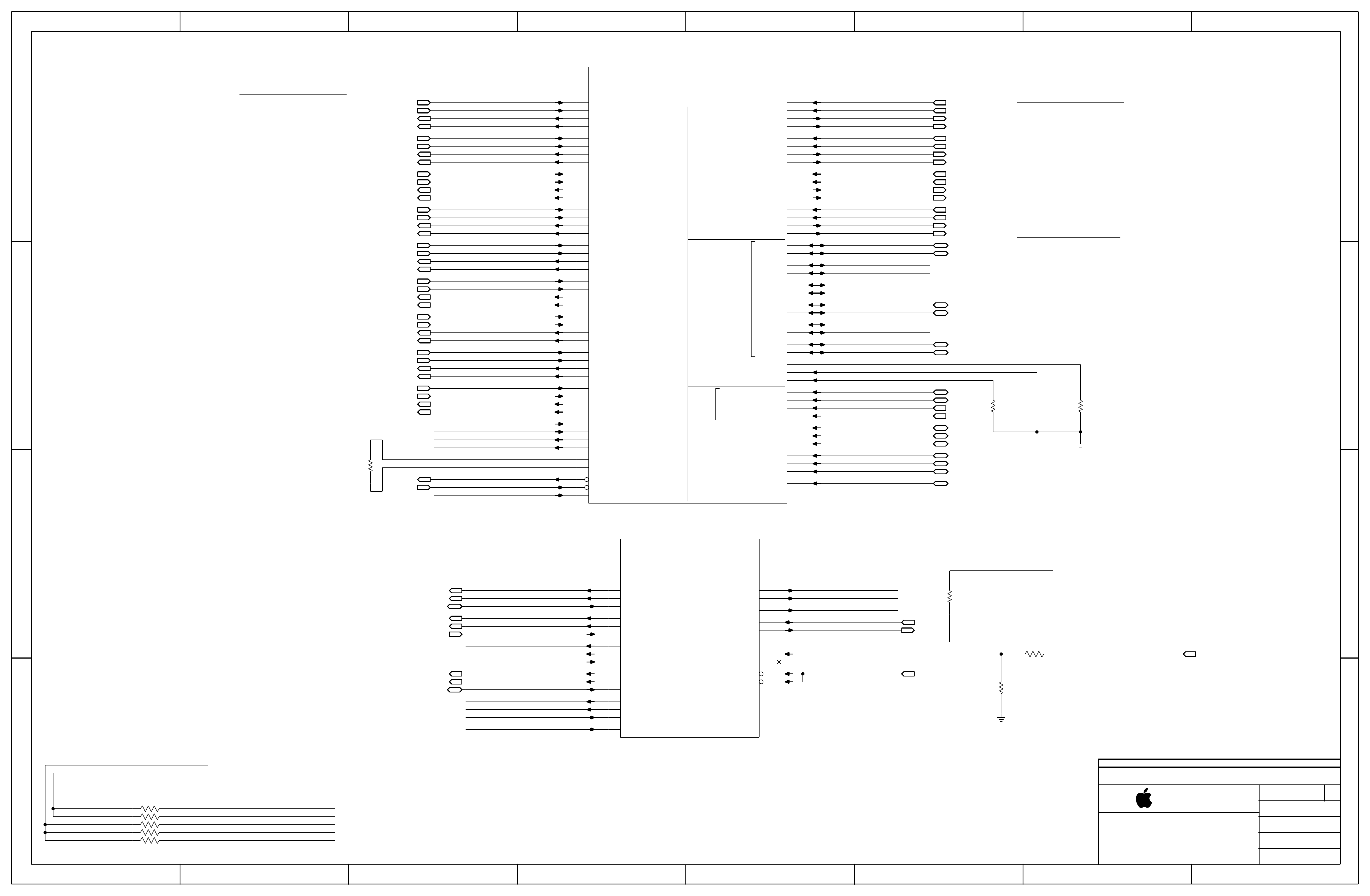

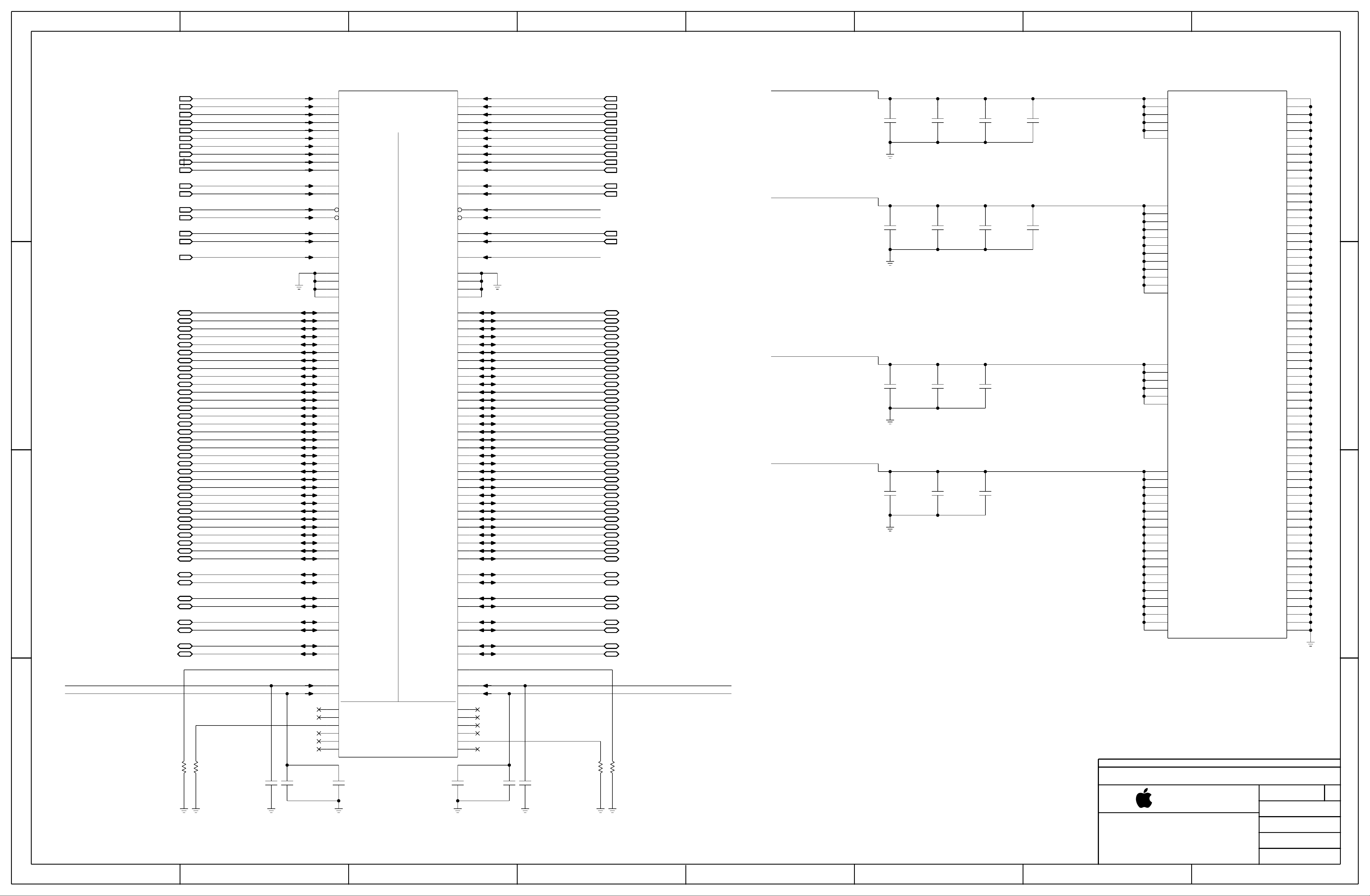

CPU LPDDR3 Interface7

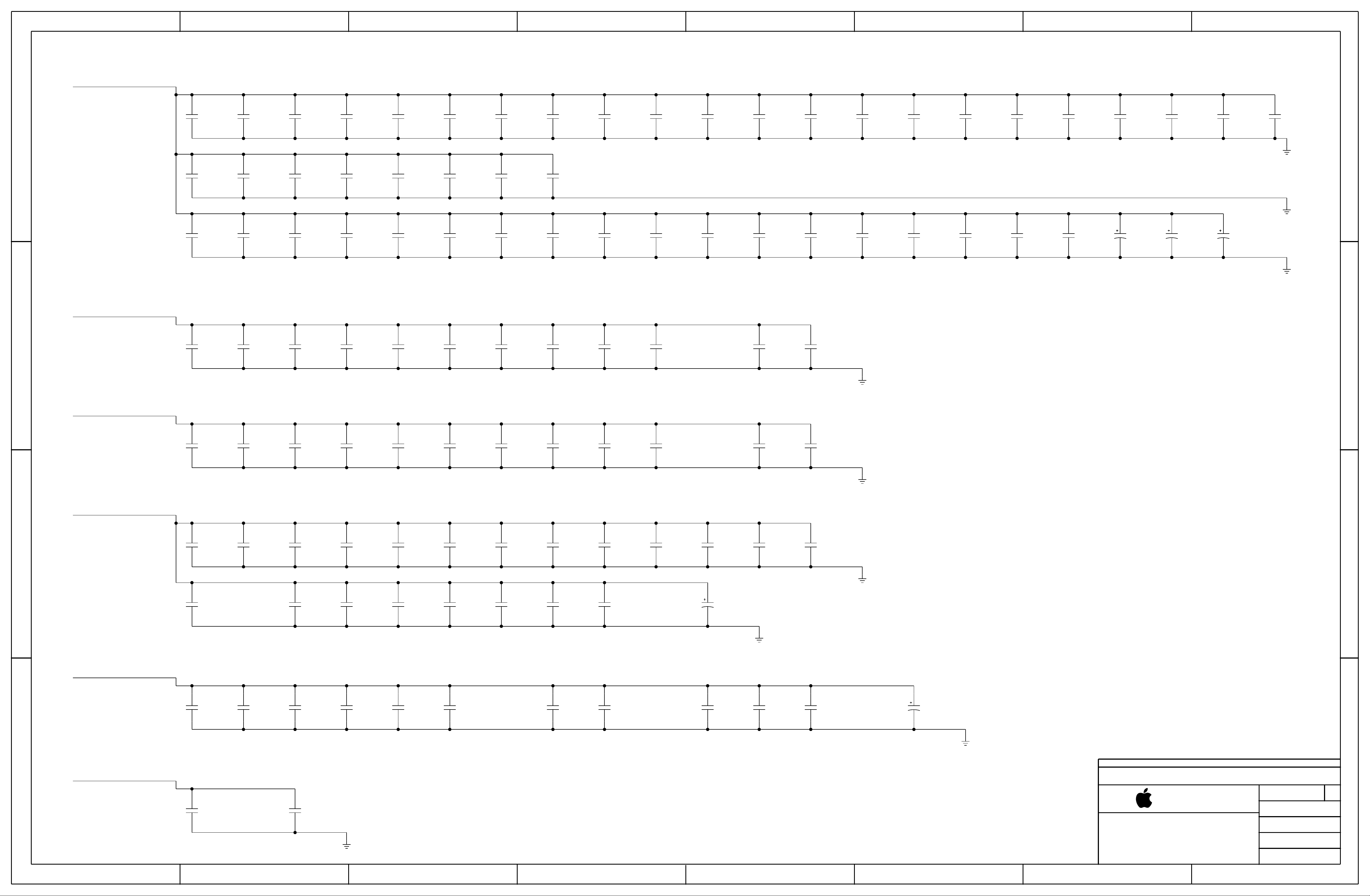

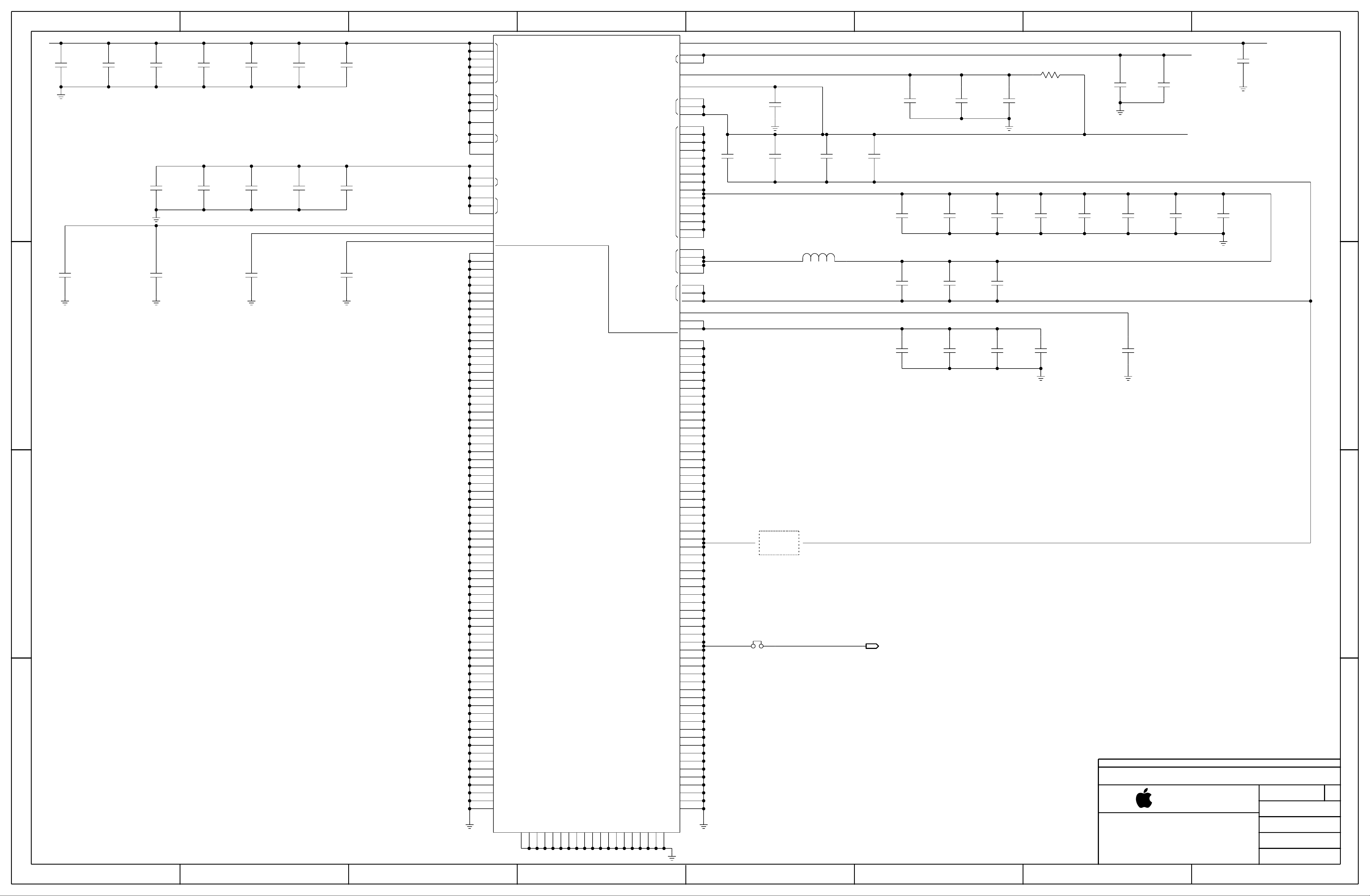

CPU Power

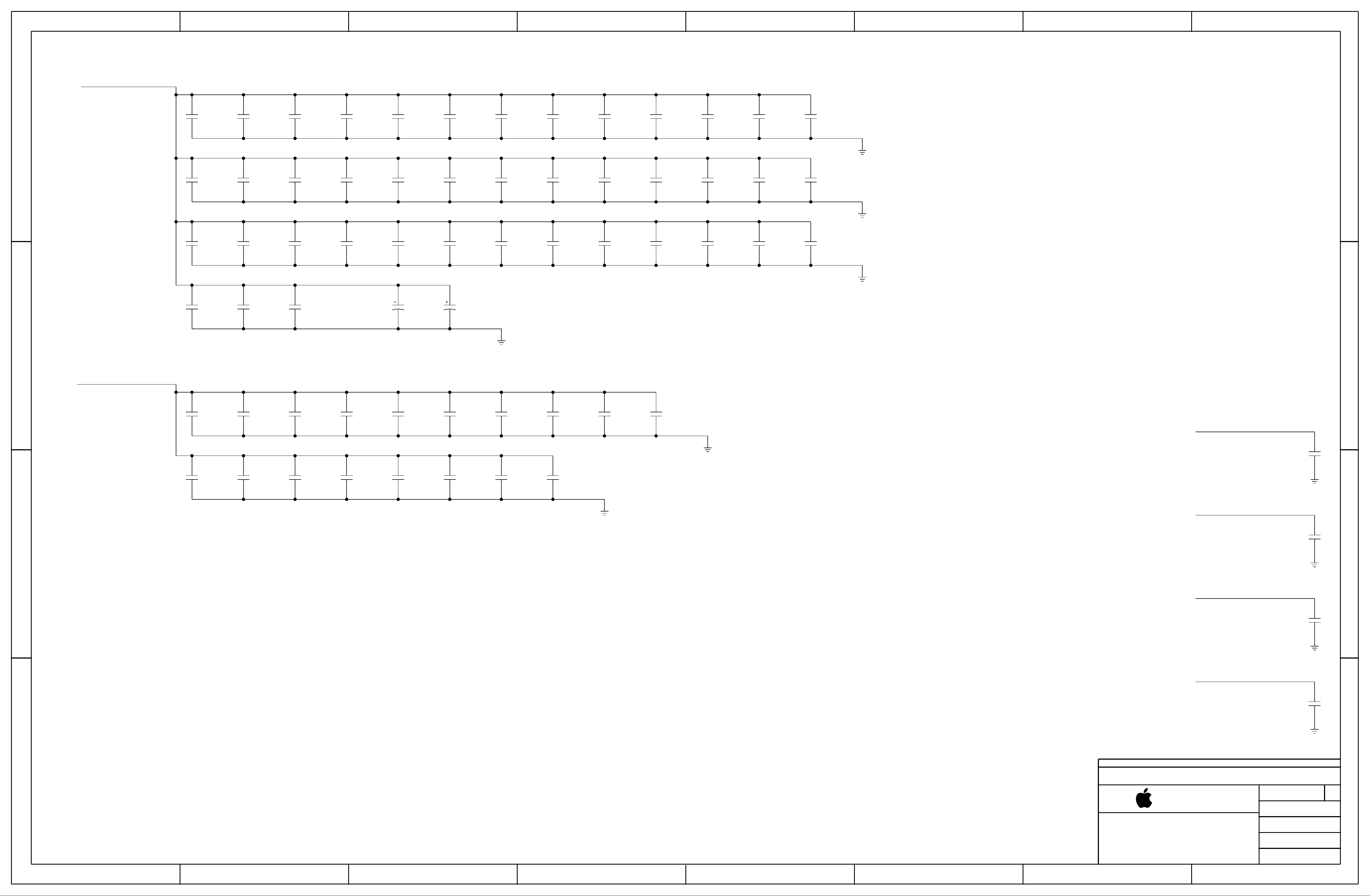

PCH Power

CPU & PCH Grounds

CPU Decoupling 1

CPU Decoupling 2

PCH Decoupling

J122_MLB

J122_MLB

J122_MLB

J122_MLB

J122_MLB

J122_MLB

J122_MLB

J122_MLB

J122_MLB

DATESYNCCONTENTSCSAPAGE

03/30/2018

03/30/2018

03/30/2018

03/30/2018

03/30/2018

03/30/2018

03/30/2018

03/30/2018

51

52

60

61

Fans

RIO Connector

Audio Speaker Amplifiers

54 66 Audio Connectors

67

68 02/16/2017

57

58

59

60

61

69

70

71

72

74

62 76

63

78 PMIC BUCKS AND SWs

Keyboard & Trackpad 155

Keyboard & Trackpad 256

DC-In & Battery Connectors

PBUS Supply & Battery Charger

CPU IMVP8 Regulator IC

CPU VCore/VccSA Power Stage

CPU VccGT Power Stage

VR - 5V, 3V3

X1032_MLB_P4BP

AHAAGE_AUD53 64

AHAAGE_AUD

X260_MLB

X589_CARD_IPD

X589_BIGSUR

X1032_MLB_P4BP

J122_MLB

J122_MLB

J122_MLB

X589_BIGSUR

X589_BIGSUR

DATESYNCCONTENTSCSAPAGE

02/13/2017

05/23/2017

04/19/2017

02/16/2017

02/15/2017

02/13/2017

03/30/2018

03/30/2018

03/30/2018

03/01/2017

03/16/2017

D

C

14

15

16

17

19

21

22

23

24

25

26

27

14 PCH Audio/LPC/SPI/SMBus

15 PCH Power Management

16

17

1818

19

2020

22

23

25

27

28

29

30

PCH PCIe/USB/CLK

PCH GPIO/LPSS

CPU/PCH Merged XDP

Chipset Shared Support

Chipset Project Support

LPDDR3 VREF MARGINING 03/30/2018

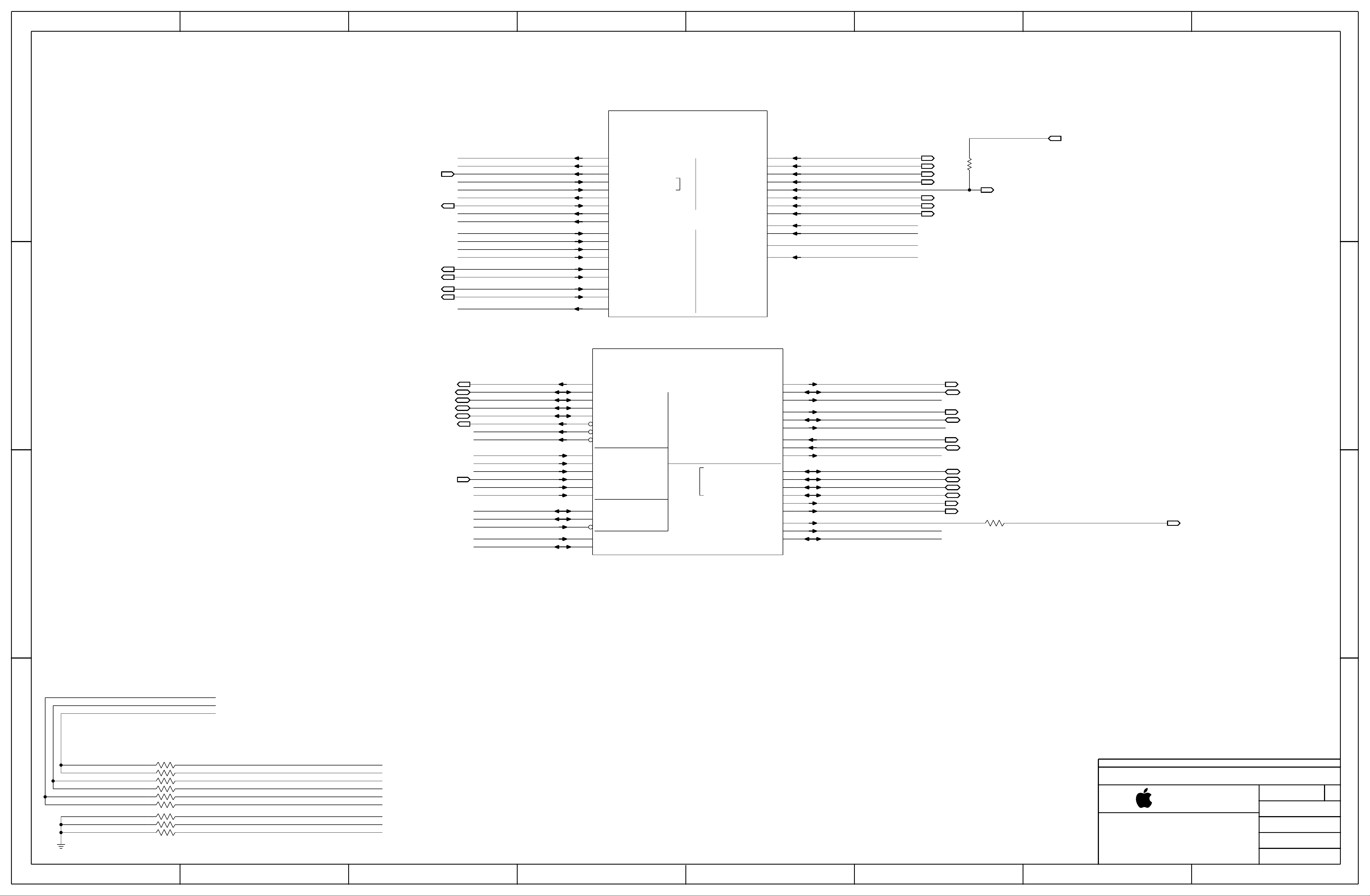

LPDDR3 DRAM Channel A (0-63)

LPDDR3 DRAM Channel B (0-63)

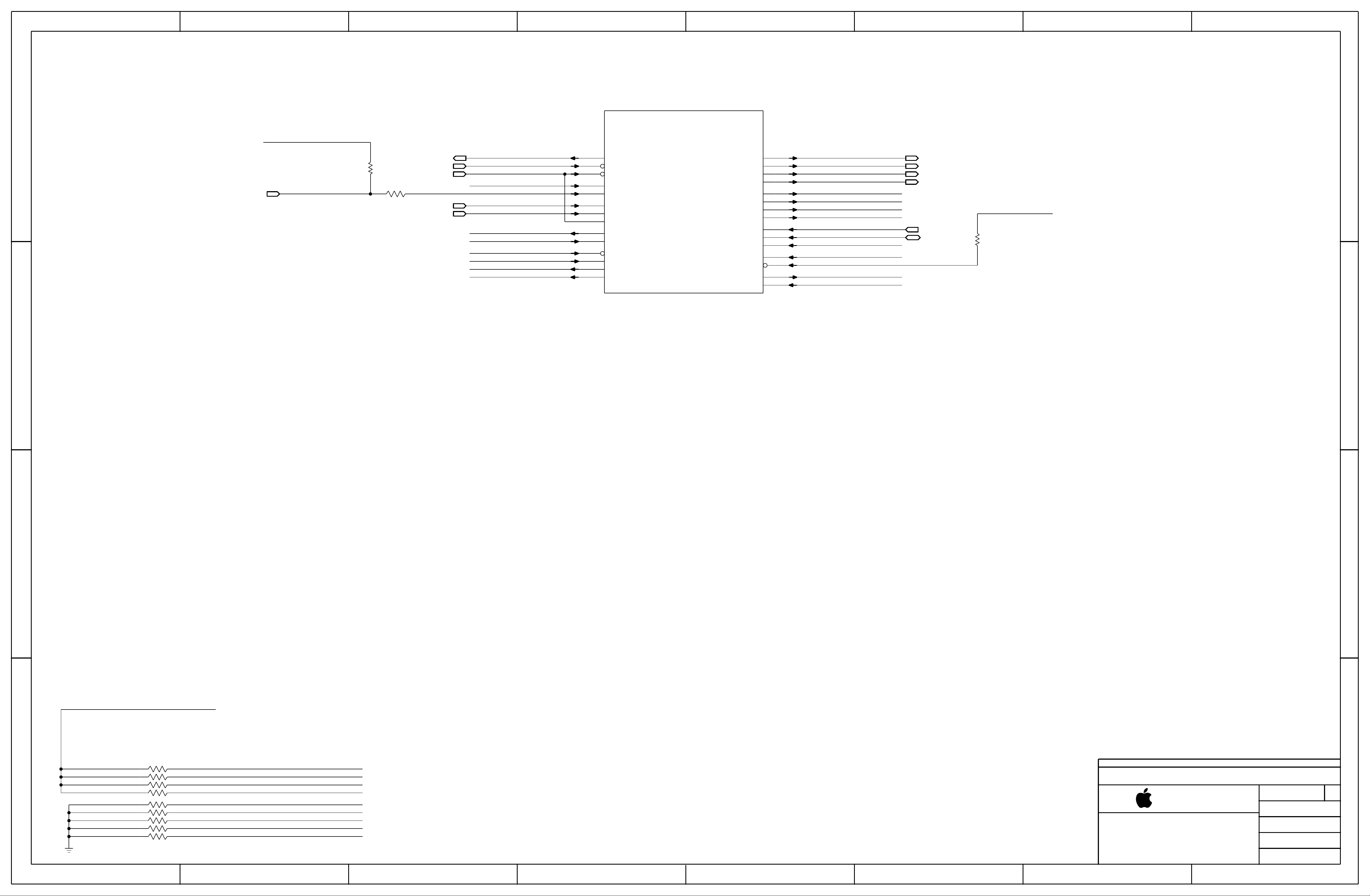

LPDDR3 DRAM Termination

USB-C HIGH SPEED 1

USB-C HIGH SPEED 2

USB-C SUPPORT

J122_MLB

J122_MLB

J122_MLB 03/30/2018

J122_MLB

X589_CPU_CNL_Y

X589_CPU_CNL_Y

X589_CPU_CNL_Y

J122_MLB

J122_MLB

J122_MLB

T290_CARD_CPU_U

X1032_MLB_P4BP

X1032_MLB_P4BP

X1032_MLB_P4BP

03/30/2018

03/30/2018

03/30/2018

03/13/2017

03/27/2017

03/07/2017

03/30/2018

03/30/2018

04/06/2018

02/13/2017

02/13/2017

02/13/2017

64

65

79

PMIC LDOs

PMIC GPIOs & Control80

POWER - VDDQ, VCCIO81

Power FETs

LCD Backlight Driver84

eDP Display Connector

68

69

8267

85

S4E<0>86

71

72 S4E<2>

73 02/13/2017

74

75 02/21/2017

76

77

87 S4E<1>

88

90

91

NAND VCC VR

SSD Support

Power Aliases - 1120

121

122

Power Aliases - 2

Signal Aliases

X589_BIGSUR

X589_BIGSUR

X589_CPU_CNL_Y66

X589_CPU_CNL_Y

X1032_MLB_P4BP

X1032_MLB_P4BP

X1032_MLB_P4BP

X1032_MLB_P4BP

X1032_MLB_P4BP

X1032

X589_CPU_CNL_Y

X589_CPU_CNL_Y

03/16/2017

03/16/2017

03/08/2017

02/22/2017

02/13/2017

02/13/2017

02/13/201770

02/13/2017

02/14/2017

02/21/2017

C

B

28

29

30

31

32

33

34

35

36

37

38

39

31

32

33

34

37

38

39

40

41

42 X589_BIGSUR

43

44

40 45

41

46

USB-C PORT CONTROLLER A

USB-C PORT CONTROLLER B

USB-C CONNECTOR

USB-C SUPPORT 2

WIFI/BT MODULE

WIFI/BT Module Support

SoC GPIO/SEP/USB/DDR/Test

SoC AOP/AON/SMC

SoC ISP/I2C/UART/SPI/I2S

SoC PCIe

SoC Power 1

SoC Power 2

SoC Power 3

SoC Ground

X1032_MLB_P4BP

X1032_MLB_P4BP

X1032_MLB_P4BP

MKARAKUCUK

X1032_MLB_P4BP

X589_BIGSUR

X589_BIGSUR

X589_BIGSUR

X589_BIGSUR

X589_BIGSUR

X589_BIGSUR

X589_BIGSUR

02/13/2017

02/13/2017

02/13/2017

03/22/2017

03/03/2017

03/15/2017

03/16/2017

03/15/2017

03/15/2017

02/13/2017

02/13/2017

02/13/2017

02/13/2017

78

79

80

81

123

124

127 Desense Caps 1

128

82 140 04/12/2017

83 BOM Variants 1

84

141

142

85 145

Memory Signal Swaps

ICT FCT

Desense Caps 2

Dev Support

BOM Variants 2

BOM Alternates

J122_MLB

X589_BIGSUR

04/13/2018

B

A

1 SCH CRITICAL SCHEM051-04039 SCH,MLB_BTTF,X1032

1 MLB CRITICAL PCBF820-01521 PCBF,MLB_BTTF,X1032

42

43

44

45

46

47

48

49

50

47

48

50

53

54

55

56

58

SoC Shared Support

SoC Project Support

Secure Element

I2C Connections 152

Power Sensors High Side

Power Sensors Load Side

Power Sensors Extended

Thermal Sensors

X589_BIGSUR

X589_BIGSUR

X941_MLB

X589_BIGSUR

X589_BIGSUR

X1032_MLB_P4BP

X1032_MLB_P4BP

X1032_MLB_P4BP

03/16/2017

02/13/2017

03/10/2017

02/13/2017

02/13/2017I2C Connections 2

02/14/2017

02/14/2017

02/14/2017

DRAWING TITLE

A

SYNC_DATE=07/25/2017SYNC_MASTER=CONSTRAINTS_ML

SCHEM,MLB-BTTF,X1032

TABLE_5_HEAD

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

BOM OPTIONCRITICAL

TABLE_5_ITEM

TABLE_5_ITEM

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

Apple Inc.

051-04039

REVISION

2.0.0

BRANCH

PAGE

1 OF 145

SHEET

1 OF 85

SIZEDRAWING NUMBER

D

8

3

124567

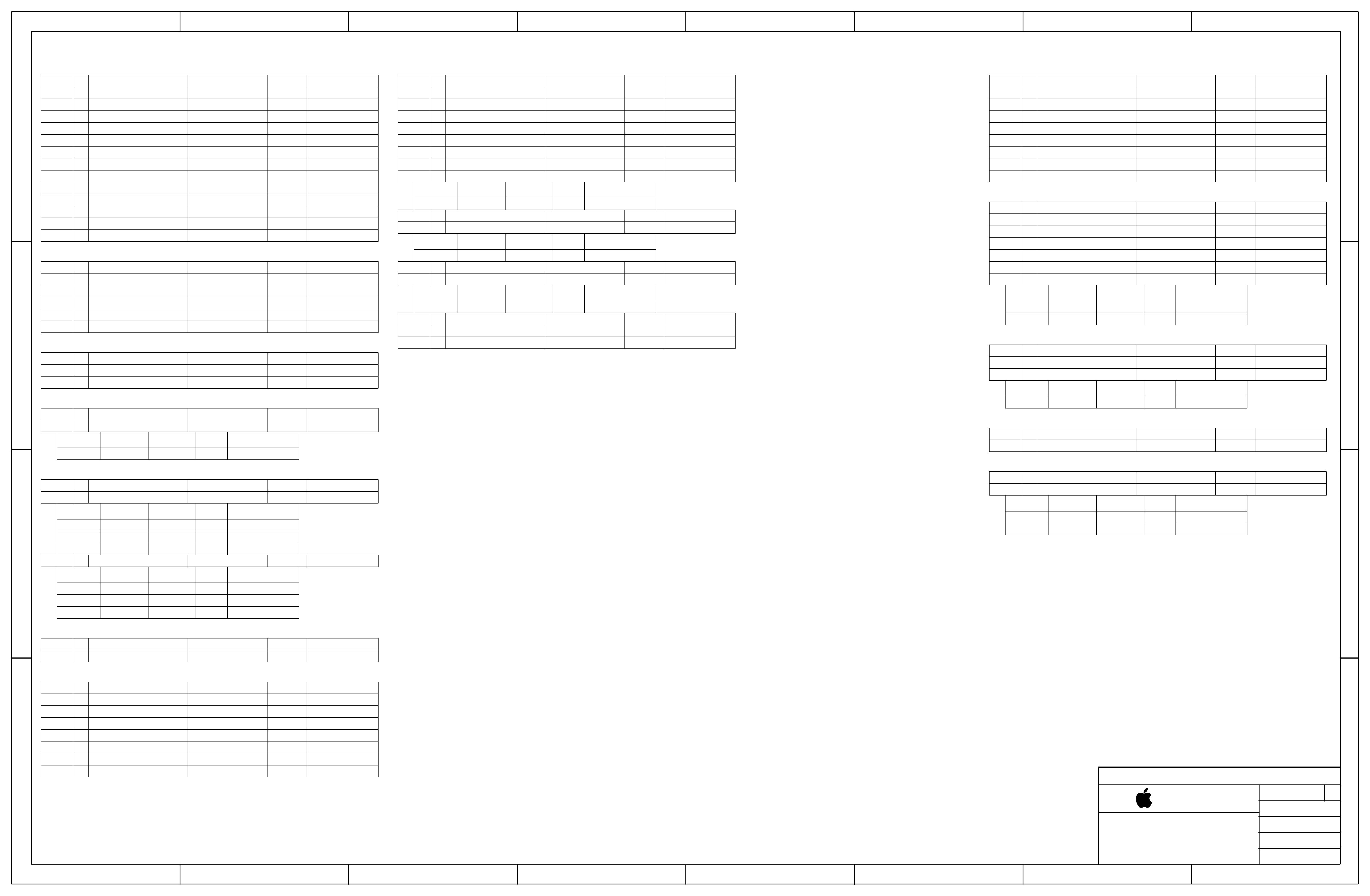

Page 2

678

3 245

1

D

C

Module Parts

CPU TBT ROMNAND

TABLE_5_HEAD

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

1

CPU,AML-Y,QQQE,PQS,1.8,1.15,BGA1515

337S00593 CPU_AMLY:QQQF

337S00614

337S00615 CRITICAL

998-15364 CRITICAL1

CPU,AML-Y,QQQF,PQS,1.6,1.05,BGA1515

CPU,AML-Y,QQQG,PQS,1.6,1.05,BGA1515

CPU,AML-Y,QQQM,PQS,H0,1.8,7W,1.15,B1515

CPU,AML-Y,QQQN,PQS,H0,1.6,7W,1.1,B1515

CPU,AML-Y,QQQP,PQS,H0,1.6,7W,1.05,B1515

1 U0500 CPU_AMLY:QQQQ337S00621 CRITICAL

CPU,AML-Y,QQQQ,PQS,H0,1.8,7W,1.15,B1515

1 U0500 CRITICAL337S00622

CPU,AML-Y,QQQR,PQS,H0,1.6,7W,1.1,B1515

CPU,AML-Y,QQQS,PQS,H0,1.6,7W,1.05,B1515

1 CRITICALU0500337S00623

CPU,AML-Y,SREKN,PRQ,1.8,7W,1.15,BGA1515

1 CRITICALU0500337S00624

CPU,AML-Y,SREKP,PRQ,1.6,7W,1.1,BGA1515

1 CRITICALU0500337S00625

CPU,AML-Y,SREKQ,PRQ,1.6,7W,1.05,BGA1515

INTERPOSER,VRTT ADAPTER,KBL-Y,BGA1515

CRITICALU05001

CRITICAL1337S00626 U0500

TBT Titan Ridge

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

338S00305

338S00356 TBT_TR:B01

338S00408 CRITICAL1 U2800

IC,TBT,TITAN RIDGE,QTJE,P-ES,A0,CSP337

IC,TBT,TITAN RIDGE DP,QTZZ,ES2,B0,CSP337

IC,TBT,TITAN RIDGE DP,QTZZ,ES2,C0,CSP337

1 U2800 TBT_TR:C0338S00399 CRITICAL

IC,TBT,TITAN RIDGE DP,QUJK,QS,C1,CSP337

IC,TBT,TITANRIDGE DP,SLMHS,PRQ,C1,CSP337

1338S00441

U28001 TBT_TR:A0CRITICAL

U2800 CRITICAL

U2800 CRITICAL TBT_TR:PRQ

Ace

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

IC,CD3215,ACE,C00,USB PWR SW,BLNK,BGA96

IC,CD3215,ACE,C00,USB PWRSW,BLNK,NFBGA96

CRITICAL

CRITICAL353S01442 U3100,U32002

Wireless

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

MODULE,WIFI,YEBISU CIDRE,U,ES4.8,LGA160

PART NUMBER

339S00446 339S00448 Murata ModuleALL

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

CRITICAL WIRELESS:USI1 U3700339S00448

TABLE_ALT_HEAD

TABLE_ALT_ITEM

BOM OPTIONCRITICAL

CPU_AMLY:QQQECRITICALU0500337S00592

CPU_AMLY:QQQG337S00594 CRITICALU05001

CPU_AMLY:QQQMCRITICALU05001337S00613

CPU_AMLY:QQQNCRITICALU05001

CPU_AMLY:QQQP1 U0500

CPU_AMLY:QQQR

CPU_AMLY:QQQS

CPU_AMLY:SREKN

CPU_AMLY:SREKP

CPU_AMLY:SREKQ

CPU_AMLY:INTERPOSERU0500

BOM OPTIONCRITICAL

TBT_TR:C1

BOM OPTIONCRITICAL

ACE:C0_BGA353S00961 2 U3100,U3200

ACE:C0_NFBGA

BOM OPTIONCRITICAL

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

335S00273 2 CRITICAL

335S00289 NAND:PMLC_128G_TO

335S00301 U8600,U8700,U88003 NAND:PMLC_128G_SD

335S00302 U8600,U8700,U8800 CRITICAL3

335S00292 NAND:PMLC_512G_TO3 U8600,U8700,U8800 CRITICAL

998-12416

335S00323 3 CRITICALU8600,U8700,U8800 NAND:PMLC_128G_SD_NM

998-12418 U8600,U8700,U8800 NAND:PMLC_256G_TO_NM

998-12423 ALL998-12422 TO 512G Substrate 2

335S00326 3 CRITICAL

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

NAND,1Z,128GBM,S4E,128G,SD,HPN1,ULGA110

NAND,3DV3,42GBP,XXX,S4E,170G,T,ULGA110

3 CRITICALU8600,U8700,U8800

NAND,3DV3,42GBP,XXX,S4E,170G,SD,ULGA110

NAND,3DV3,85GBP,XXX,S4E,170G,T,ULGA110

NAND,3DV3,85GBP,XXX,S4E,170G,SD,ULGA110

NAND,3DV3,170GBP,XXX,S4E,170G,T,ULGA110

NAND,3DV3,170GBP,XXX,S4E,170G,SD,ULGA110

NAND,3DV3,42GBP,S4E,170G,T,SUB X,ULGA110

PART NUMBER

NAND:PMLC_128G_TO_NM

NAND,3DV3,42GBP,XXX,S4E,170G,SD,ULGA110

3 CRITICAL

NAND,3DV3,85GBP,S4E,170G,T,SUB X,ULGA110

PART NUMBER

NAND:PMLC_256G_TO_NM

3335S00324 CRITICALU8600,U8700,U8800 NAND:PMLC_256G_SD_NM

NAND,3DV3,85GBP,XXX,S4E,170G,SD,ULGA110

NAND,3DV3,170GBP,S4E,170G,T,SUBX,ULGA110

3998-12422 CRITICAL

PART NUMBER

NAND:PMLC_512G_TO_NM

NAND,3DV3,170GBP,XXX,S4E,170G,SD,ULGA110

NAND,3DV4,512GBM,S4E,256G,SS,ULGA110

3 CRITICAL335S00322

NAND,3DV4,512GBM,S4E,256G,MG3,SS,ULGA110

U8600,U8700 NAND:HPN1_256G_2L

CRITICAL

U8600,U8700,U8800335S00290 3 CRITICAL

U8600,U8700,U8800 NAND:PMLC_512G_SD

CRITICAL3335S00304

U8600,U8700,U88003 CRITICAL NAND:PMLC_128G_TO_NM

TABLE_ALT_HEAD

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

TO 128G Substrate 2ALL998-12417 998-12416

TABLE_ALT_HEAD

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

ALL998-12418998-12419

TO 256G Substrate 2

U8600,U8700,U8800 NAND:PMLC_512G_TO_NM

TABLE_ALT_HEAD

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

U8600,U8700,U8800 NAND:PMLC_512G_SD_NM

BOM OPTIONCRITICAL

NAND:PMLC_256G_TO

NAND:PMLC_256G_SD

NAND:3DV4_1P5T_SSU8600,U8700,U8800

NAND:3DV4_1P5T_SS_MG3U8600,U8700,U8800 CRITICAL3335S00373

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

Programmables

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

IC,SPI SERIAL FLASH,8MBITS,3.0V,USON8

IC,NVM (V5.7) PROTO-0,X1032

1

IC,NVM (V1.1) NEW,PROTO-0,X1032

IC,NVM (V5.1) PROTO-1,X1032

1

341S00982 1 CRITICALU2890

IC,NVM (VXXX) PROTO-2,X1032

IC,NVM (VXXX) EVT,X1032

1

IC,NVM (VXXX) PROTO-3,X1032

IC,NVM (VXXX) EVT-2,X1032

U2890335S00133 1 CRITICAL TBT_ROM:BLANK

U2890341S00905 CRITICAL TBT_ROM:P0

U28901 CRITICAL341S00922 TBT_ROM:P0_B0

U2890 CRITICAL341S00942 TBT_ROM:P1

U2890

U28901341S01177

BT ROM

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

IC,SPI SERIAL FLASH,2MBIT,1.8V,DFN8

341S00745 BT_ROM:P0CRITICAL1

341S00939 U37701 CRITICAL BT_ROM:P1

341S01176

IC,BT ROM (V4) PROTO-0,X1032

BT SFLASH ROM (V22.33.40) PROTO-1,X1032

1341S00983

BT SFLASH ROM (VXXX) PROTO-2,X1032

1

BT SFLASH ROM (VXXX) EVT,X1032

BT SFLASH ROM (VXXX) EVT-2,X1032

1 U3770 CRITICAL BT_ROM:EVT2

PART NUMBER

U37701

U3770

U3770 CRITICAL341S01042 BT_ROM:EVT

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

CRITICAL335S00256 BT_ROM:BLANK

CRITICALU3770 BT_ROM:P2

TABLE_ALT_HEAD

TABLE_ALT_ITEM

ALL MacronixBT_ROM:BLANK335S00256335S00248

TABLE_ALT_ITEM

335S00256 BT_ROM:BLANK ALL335S00255 Adesto

Wifi ROM

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

335S00145 1

341S00744

IC,EEPROM,4KBIT,1.8V,SELECT ORG,TDFN8

WIFI ROM (P101) PROTO-0,WW1,X1032

PART NUMBER

CRITICALU3780 WIFI_ROM:P01

TABLE_ALT_HEAD

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

ALL335S00236 Rohm335S00145 WIFI_ROM:BLANK

SOC ROM

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

IC,FLASH,SERIAL,SPI,4MX8,1.8V,4X3MM,DFN8

U4770 SOC_ROM:BLANKCRITICAL1335S00203

BOM OPTIONCRITICAL

TBT_ROM:P2

TBT_ROM:EVT1 CRITICAL341S01046

TBT_ROM:P3U2890341S01150 CRITICAL

TBT_ROM:EVT2CRITICAL

BOM OPTIONCRITICAL

BOM OPTIONCRITICAL

WIFI_ROM:BLANKU3780 CRITICAL

BOM OPTIONCRITICAL

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

D

C

B

SOC

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

339S00370 1 U3900 SOC:B0_1GCRITICAL

POP,GIBRALTAR+1GB 20NM,M,B0,SCK,CSP1406

PART NUMBER

339S00370 ALL339S00375 Micron 1GB SCKSOC:B0_1G

339S00370 Hynix 1GB ATK339S00376 ALLSOC:B0_1G

POP,GIBRALTAR+2GB 20NM,M,B0,SCK,CSP1406

PART NUMBER

339S00372 SOC:B0_2G339S00378 Hynix 2GB ATKALL

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

ALLSOC:B0_1G Hynix 1GB SCK339S00370339S00371

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

ALL339S00372 Hynix 2GB SCKSOC:B0_2G339S00373

Micron 2GB ATK339S00372339S00377 SOC:B0_2G ALL

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

EFI ROM

TABLE_5_HEAD

TABLE_5_HEAD

BOM OPTIONCRITICAL

TABLE_5_ITEM

IC,SERIAL FLASH,128MBIT,1.8V,QE=1,WSON8

1 U2100 EFI_ROM:BLANK335S00371

PART NUMBER

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

CRITICAL

TABLE_ALT_HEAD

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

MacronixALL335S00370 335S00371

TABLE_ALT_ITEM

335S00371335S00376 AdestoALL

TABLE_5_ITEM

SOC:B0_2G339S00372 CRITICALU39001

BOM OPTIONCRITICAL

TABLE_5_ITEM

B

A

PMU

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

IC,PMU,CALPE,D2249A0,OTP-AI,CSP324,0.4P

DRAM

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

IC,SDRAM,LPDDR3-1866,32GBIT,20NM,BGA253

2 CRITICAL333S00052 DRAM:SAMSUNG_8GBU2300,U2500

2 CRITICALU2300,U2500333S00130 DRAM:SAMSUNG_16GB

IC,LPDDR3-1866,64GBIT,18NM,S,BGA253

2 U2300,U2500333S00110 CRITICAL DRAM:HYNIX_8GB

IC,LPDDR3-1866,32GBIT,21NM,BGA253

IC,LPDDR3-1866,64GBIT,21NM,BGA253

333S00082 CRITICAL2 DRAM:MICRON_8GB_1866U2300,U2500

IC,LPDDR3-1866,32GBIT,20NM,BGA253

IC,LPDDR3-1866,64GBIT,20NM,M,BGA253

2 CRITICAL333S00113 U2300,U2500 DRAM:MICRON_16GB

IC,LPDDR3-2133,32GBIT,20NM,BGA253

U2300,U25002 CRITICAL333S00111

U2300,U25002 CRITICAL333S00199 DRAM:MICRON_8GB

TABLE_5_HEAD

BOM OPTIONCRITICAL

TABLE_5_ITEM

CRITICALU78001 PMU:A0_A338S00267

TABLE_5_HEAD

BOM OPTIONCRITICAL

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

DRAM:HYNIX_16GB

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

PAGE TITLE

A

BOM Configuration

SIZE

D

Apple Inc.

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

DRAWING NUMBER

051-04039

REVISION

2.0.0

BRANCH

PAGE

2 OF 145

SHEET

2 OF 85

8

67

35 4

2

1

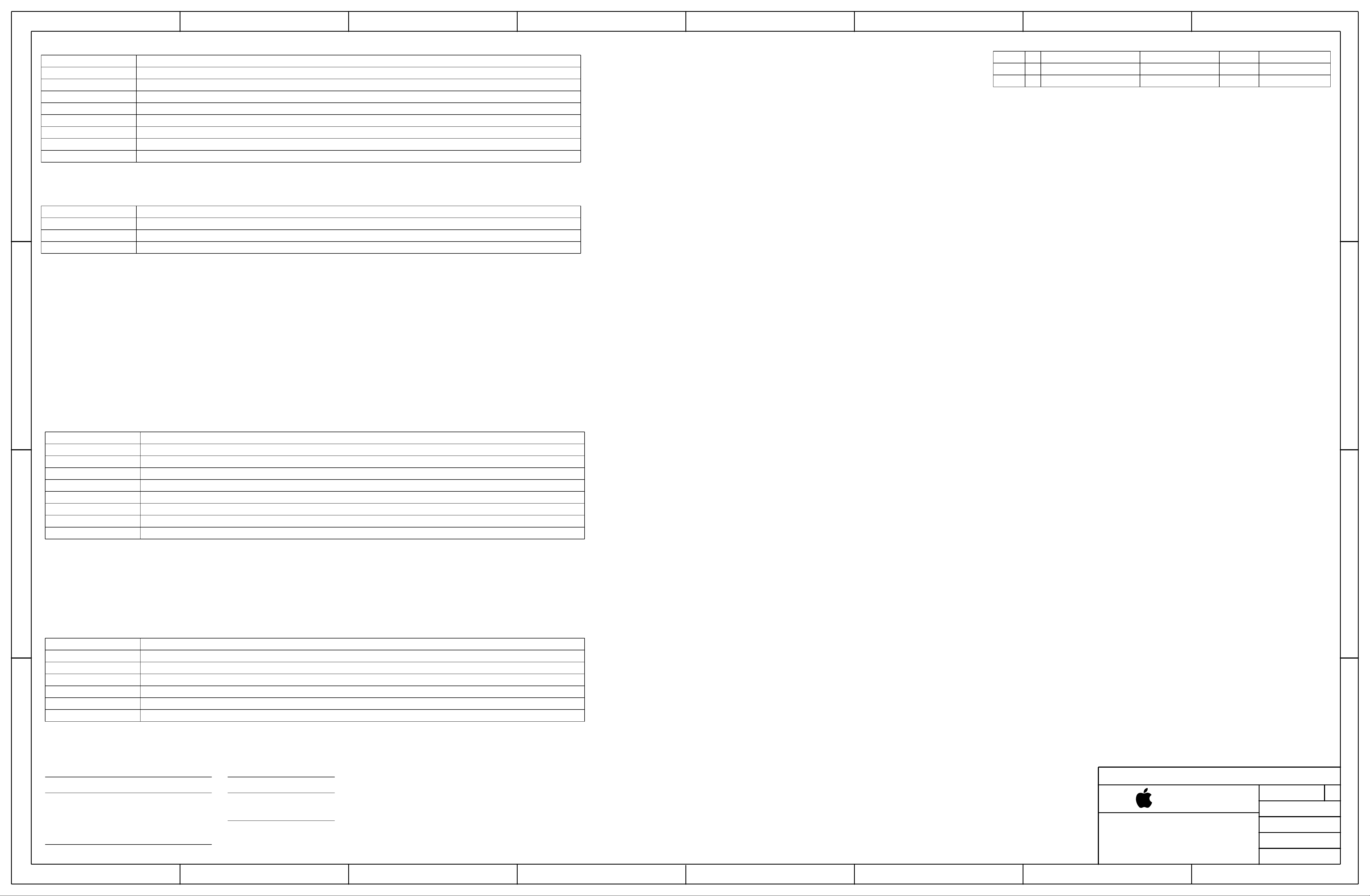

Page 3

678

3 245

1

D

BOM Groups

BOM GROUP BOM OPTIONS

MLB_COMMON

MLB_USBC

MLB_PROGPARTS

SCHEM,PCBF,ALTERNATE,COMMON,MLB_PROGPARTS,MLB_USBC,MLB_POWER,MLB_WIRELESS,MLB_MECH1,MLB_MECH2,MLB_MISC,PVT

TBT_PCIE_4LANES,TBT_TR:PRQ,ACE:C0_BGA

BT_ROM:EVT2,SOC_ROM:BLANK,TBT_ROM:EVT2,WIFI_ROM:P0,SE:PROD_2017

MLB_POWER PMU:A0_A

WIRELESS:USIMLB_WIRELESS

MLB_MECH1

MLB_MECH2

MLB_MISC

BRACKET,BUSBARLONG,BUSBARTOP,BUSBARBOTTOM

SHLD_CAN_DRAM,SHLD_FNC_NAND,SHLD_CAN_TR,SHLD_FNC_SOC,SHLD_CAN_DPLXR

BOARDID0,BOARDID1,BOARDID2,BOARDID4,SYSDET:FET,NAND_VCC:2V5,BOOTCFG0

See <rdar://problem/39661910> for BOARDID straps

Build Specific Groups

BOM GROUP BOM OPTIONS

PROTO3

PREEVT2

PVT

MAF,EFI_ROM:BLANK

BOARDREV0,SAF,PCHFLTR:FERRITE

BOARDREV1,SAF,PCHFLTR:FERRITE

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_5_HEAD

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

DEV PARTS,MLB_BTTF,X1032 DEV_PARTS_BOMDEV11 CRITICAL985-00733

BOM OPTIONCRITICAL

TABLE_5_ITEM

CMN_PARTS_BOMCOMMON PARTS,MLB_BTTF,X10321 CRITICALCBOM685-00251

TABLE_5_ITEM

D

C

NAND Configs

BOM GROUP BOM OPTIONS

NANDCFG:HPN1_256G_2L

NANDCFG:PMLC_128G_TO

NANDCFG:PMLC_128G_SD

NANDCFG:PMLC_256G_TO

NANDCFG:PMLC_256G_SD

NANDCFG:PMLC_512G_TO

NANDCFG:PMLC_512G_SD

NANDCFG:3DV4_1P5T_SS

C

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

NAND:HPN1_256G_2L,SSDJTAG:2L,SOC:B0_1G

TABLE_BOMGROUP_ITEM

NAND:PMLC_128G_TO_NM,SOC:B0_1G

TABLE_BOMGROUP_ITEM

NAND:PMLC_128G_SD_NM,SOC:B0_1G

TABLE_BOMGROUP_ITEM

NAND:PMLC_256G_TO_NM,SOC:B0_1G

TABLE_BOMGROUP_ITEM

NAND:PMLC_256G_SD_NM,SOC:B0_1G

TABLE_BOMGROUP_ITEM

NAND:PMLC_512G_TO_NM,SOC:B0_1G

TABLE_BOMGROUP_ITEM

NAND:PMLC_512G_SD_NM,SOC:B0_1G

TABLE_BOMGROUP_ITEM

NAND:3DV4_1P5T_SS_MG3,SOC:B0_2G

B

CPU DRAM SPD Straps

BOM GROUP BOM OPTIONS

DRAMCFG:SAMSUNG_8GB

DRAMCFG:SAMSUNG_16GB

DRAMCFG:HYNIX_8GB

DRAMCFG:HYNIX_16GB

DRAMCFG:MICRON_8GB

DRAMCFG:MICRON_16GB

DRAM:SAMSUNG_8GB,RAMCFG0_L

DRAM:SAMSUNG_16GB,RAMCFG0_L,RAMCFG2_L,RAM_16GB

DRAM:HYNIX_8GB,RAMCFG0_L,RAMCFG1_L

DRAM:HYNIX_16GB,RAMCFG0_L,RAMCFG1_L,RAMCFG2_L,RAM_16GB

DRAM:MICRON_8GB

DRAM:MICRON_16GB,RAMCFG2_L,RAM_16GB

B

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

A

RAMCFGx strap is low if in table.

CPU DRAM CFG Chart

Vendor

Hynix

Samsung

Unused

Micron

CFG 1

0

1

0

1

8

CFG 0

0

0

1

1

Vendor

8GB

16GB

CFG 2

1

0

A

PAGE TITLE

BOM Configuration

DRAWING NUMBER

051-04039

Apple Inc.

REVISION

2.0.0

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

67

35 4

2

BRANCH

PAGE

3 OF 145

SHEET

3 OF 85

1

SIZE

D

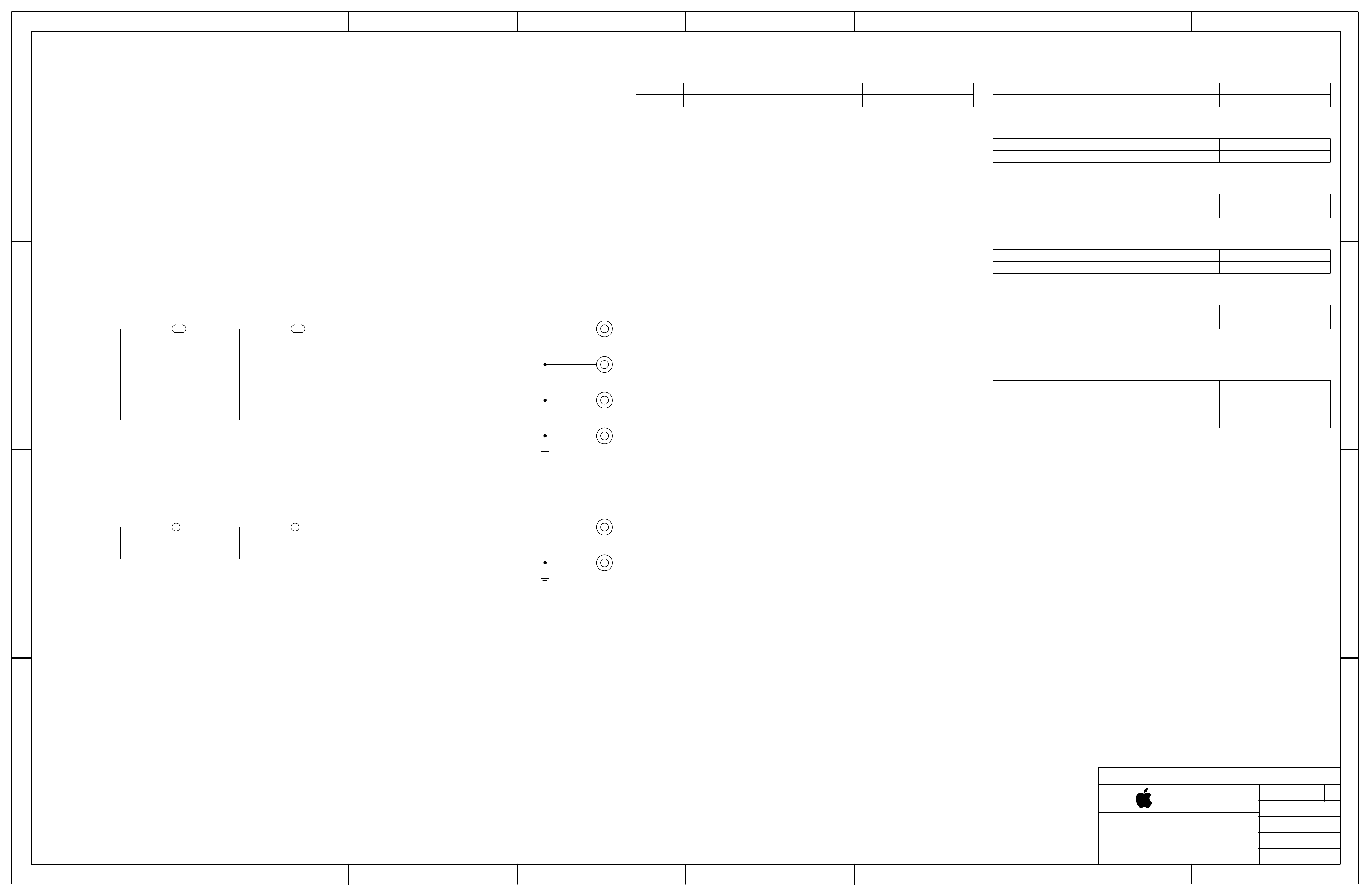

Page 4

678

3 245

1

Shield Cans

D

Mounting Bracket

806-12895 CRITICAL1

BRKT,MOUNTING,MLB,X1030

DRAM Shield Can

TABLE_5_HEAD

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

BOM OPTIONCRITICAL

TABLE_5_ITEM

SHIELD CAN,DRAM,X1030

BRACKETBRKT1

806-12387

1 CRITICALSHLD1 SHLD_CAN_DRAM

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

BOM OPTIONCRITICAL

TABLE_5_HEAD

TABLE_5_ITEM

NAND Shield Fence

D

SHIELD FENCE,MEMORY,SINGLE,X1030

TABLE_5_HEAD

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

BOM OPTIONCRITICAL

TABLE_5_ITEM

SHLD_FNC_NANDSHLD2806-12384 1 CRITICAL

TR Shield Can

TABLE_5_HEAD

SHIELD CAN,TITAN RIDGE,X1030

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

SHLD3806-12386 1 CRITICAL

BOM OPTIONCRITICAL

TABLE_5_ITEM

SHLD_CAN_TR

C

Mounting Holes

998-03823

SH0400

TH-NSP

1

SL-3.36X2.1-5.86X4.6

SH0401

TH-NSP

1

SL-3.36X2.1-5.86X4.6

Heatsink Mounting Bosses

860-01043

SH0410

5.0OD1.85ID-1.5H-SM1

1

SH0411

5.0OD1.85ID-1.5H-SM1

1

SH0412

5.0OD1.85ID-1.5H-SM1

1

SH0413

5.0OD1.85ID-1.5H-SM1

1

SOC/NAND Shield Fence

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

806-12385 SHLD4 SHLD_FNC_SOCCRITICAL1

SHIELD FENCE,GIBRALTOR AND MEMORY,X1030

Diplexer Shield Can

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

SHIELD CAN,DIPLEX,SUS,X1030

CRITICAL1 SHLD_CAN_DPLXRSHLD5806-12650

Bus Bars

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

806-16920 2 BUSBARLONGCRITICAL

BUSBAR,MLB,LONG,BOTTOM,X1032

BUSBAR,MLB,TOP,X1032

BUSBAR,MLB,LONG,BOTTOM,X1032

BB0400,BB0403

CRITICAL

TABLE_5_HEAD

BOM OPTIONCRITICAL

TABLE_5_ITEM

TABLE_5_HEAD

BOM OPTIONCRITICAL

TABLE_5_ITEM

C

TABLE_5_HEAD

BOM OPTIONCRITICAL

TABLE_5_ITEM

TABLE_5_ITEM

BUSBARTOPBB04011806-16921 CRITICAL

TABLE_5_ITEM

BUSBARBOTTOMBB04021806-16922

B

998-11113 998-11114

SH0402

4.6R1.7-NSP 4.6X5.2R1.7X2.3-NSP

1

SH0403

1

Antenna Cowling Bosses

860-00974

SH0420

2.7X1.8R-1.4ID-0.91H-SM-X1030

1

SH0421

2.7X1.8R-1.4ID-0.91H-SM-X1030

1

B

A

8

A

PAGE TITLE

PD Parts

DRAWING NUMBER

051-04039

Apple Inc.

REVISION

2.0.0

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

BOM_COST_GROUP=MECHANICALS

67

35 4

IV ALL RIGHTS RESERVED

2

BRANCH

PAGE

4 OF 145

SHEET

4 OF 85

1

SIZE

D

Page 5

D

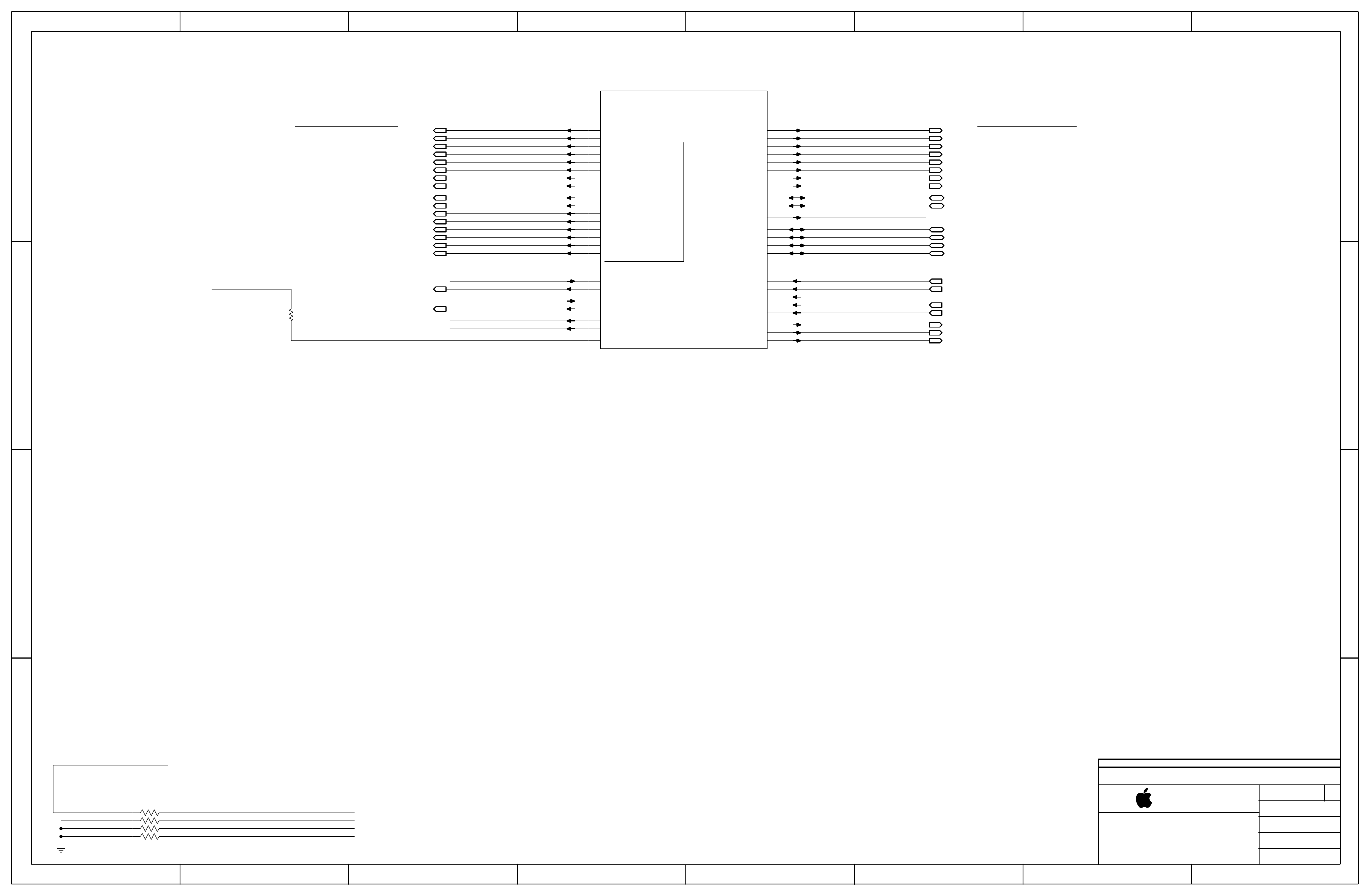

DDI Port Assignments:

USBC Sink 0

USBC Sink 1

27

27

27

27

27

27

27

27

27

27

27

27

27

27

27

27

678

3 245

1

CRITICAL

OMIT_TABLE

U0500

KBL-PCH-Y-QKKR

BGA

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

947915

DP_X_SNK0_ML_C_N<0>

DP_X_SNK0_ML_C_P<0>

DP_X_SNK0_ML_C_N<1>

DP_X_SNK0_ML_C_P<1>

DP_X_SNK0_ML_C_N<2>

DP_X_SNK0_ML_C_P<2>

DP_X_SNK0_ML_C_N<3>

DP_X_SNK0_ML_C_P<3>

DP_X_SNK1_ML_C_N<0>

DP_X_SNK1_ML_C_P<0>

DP_X_SNK1_ML_C_N<1>

DP_X_SNK1_ML_C_P<1>

DP_X_SNK1_ML_C_N<2> DP_X_SNK0_AUXCH_C_N

DP_X_SNK1_ML_C_P<2>

DP_X_SNK1_ML_C_N<3>

DP_X_SNK1_ML_C_P<3>

A46

C46

C48

A48

B45

D45

B47

D47

A42

C42

A44

C44

B41

D41

B43

D43

DDI1_TXN0

DDI1_TXP0

DDI1_TXN1

DDI1_TXP1

DDI1_TXN2

DDI1_TXP2

DDI1_TXN3

DDI1_TXP3

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

SYM 1 OF 20

DDI

DISPLAY

EDP

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

H45

F45

J44

G44

J46

G46

H43

F43

J42

G42

A40

H41

F41

J40

G40

DP_INT_ML_C_N<0>

DP_INT_ML_C_P<0>

DP_INT_ML_C_N<1>

DP_INT_ML_C_P<1>

DP_INT_ML_C_N<2>

DP_INT_ML_C_P<2>

DP_INT_ML_C_N<3>

DP_INT_ML_C_P<3>

DP_INT_AUXCH_C_N

DP_INT_AUXCH_C_P

TP_EDP_DISP_UTIL

DP_X_SNK0_AUXCH_C_P

DP_X_SNK1_AUXCH_C_N

DP_X_SNK1_AUXCH_C_P

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

BI

BI

BI

BI

BI

69

69

69

69

69

69

69

69

69

69

27

27

27

27

eDP Port Assignment:

D

Internal panel

C

PPVCCIO_S0_CPU

8 11 76

PLACE_NEAR=U0500.A50:15.24mm

R0520

24.9

1%

1/20W

MF

201

DISPLAY SIDEBANDS

TP_PCH_GPP_E18

20

OUT

1

20

OUT

PCH_DDPB_CTRLDATA

TP_PCH_GPP_E20

PCH_DDPC_CTRLDATA

TP_PCH_GPP_E22

2

TP_PCH_GPP_E23

MCP_EDP_RCOMP

L6

GPP_E18/DDPB_CTRLCLK

H6

GPP_E19/DDPB_CTRLDATA

H4

GPP_E20/DDPC_CTRLCLK

F4

GPP_E21/DDPC_CTRLDATA

M5

GPP_E22

L4

GPP_E23

A50

EDP_RCOMP

(IPD-PLTRST#)

(IPD-PLTRST#)

(IPD-PLTRST#)

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_BKLEN

EDP_BKLCTL

EDP_VDDEN

C11

L10

M7

F6

A7

D4

B6

D3

DP_X_SNK0_HPD

DP_X_SNK1_HPD

TP_PCH_GPP_E15

TBT_X_PLUG_EVENT_L

DP_INT_HPD

EDP_BKLT_EN

EDP_BKLT_PWM

EDP_PANEL_PWR_EN

OUT

OUT

OUT

IN

IN

IN

IN

27

27

27 25 5

69 5

79 68 5

79 69

69 5

C

B

B

A

PM_SLP_S3_L

R0530

R0560

R0562

R0563

100K

100K

100K

100K

8

21

21

21

21

1/20W

5% 2011/20W MF

5% MF

1/20W 201

79 25 20 15 14

PAGE TITLE

SYNC_DATE=03/30/2018SYNC_MASTER=J122_MLB

A

CPU GFX

DRAWING NUMBER

051-04039

Apple Inc.

TBT_X_PLUG_EVENT_L

2015% MF

EDP_BKLT_EN

EDP_PANEL_PWR_EN

DP_INT_HPD

MF5%

2011/20W

27 25 5

79 68 5

69 5

69 5

BOM_COST_GROUP=CPU & CHIPSET

67

35 4

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

2

REVISION

2.0.0

BRANCH

PAGE

5 OF 145

SHEET

5 OF 85

1

SIZE

D

Page 6

D

PP1V_S0SW

8 12 18 75

42

79 42 20 17 15

33 32

BI

OUT

678

PP1V_S3

8 12 15 59 75

R0610

1/20W

CPU_PROCHOT_L

IN

1K

5%

MF

201

1

2

1

R0614

100K

5%

1/20W

MF

201

2

R0611

499

2 1

1%

1/20W

MF

201

R0612

65 42

1K

5%

1/20W

MF

201

OUT

3 245

1

CRITICAL

OMIT_TABLE

U0500

1

65

2

42

OUT

BI

CPU_CATERR_L

CPU_PECI

CPU_PROCHOT_R_L

42

PM_THRMTRIP_L

NC

18

18

18

18

18

18

BI

BI

BI

BI

OUT

BI

(IFDIM trigger)

XDP_BPM_L<0>PLT_RST_L

XDP_BPM_L<1>

XDP_BPM_L<2>

XDP_BPM_L<3>

XDP_PCH_OBSFN_C1

XDP_PCH_OBSDATA_A3

PCH_WLAN_PERST_L

33 32

OUT

PCH_WLAN_DEV_WAKE

IPD in module

CPU_OPI_RCOMP

PCH_OPI_COMP

H49

F49

J48

H47

B62

H51

J50

F51

G50

E11

M9

BD8

BC11

BN17

BP16

CATERR*

PECI

PROCHOT*

THERMTRIP*

SKTOCC*

BPM0*

BPM1*

BPM2*

BPM3*

GPP_E3/CPU_GP0

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

KBL-PCH-Y-QKKR

BGA

947915

SYM 4 OF 20

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPD)

(IPU)

JTAG

(IPU)

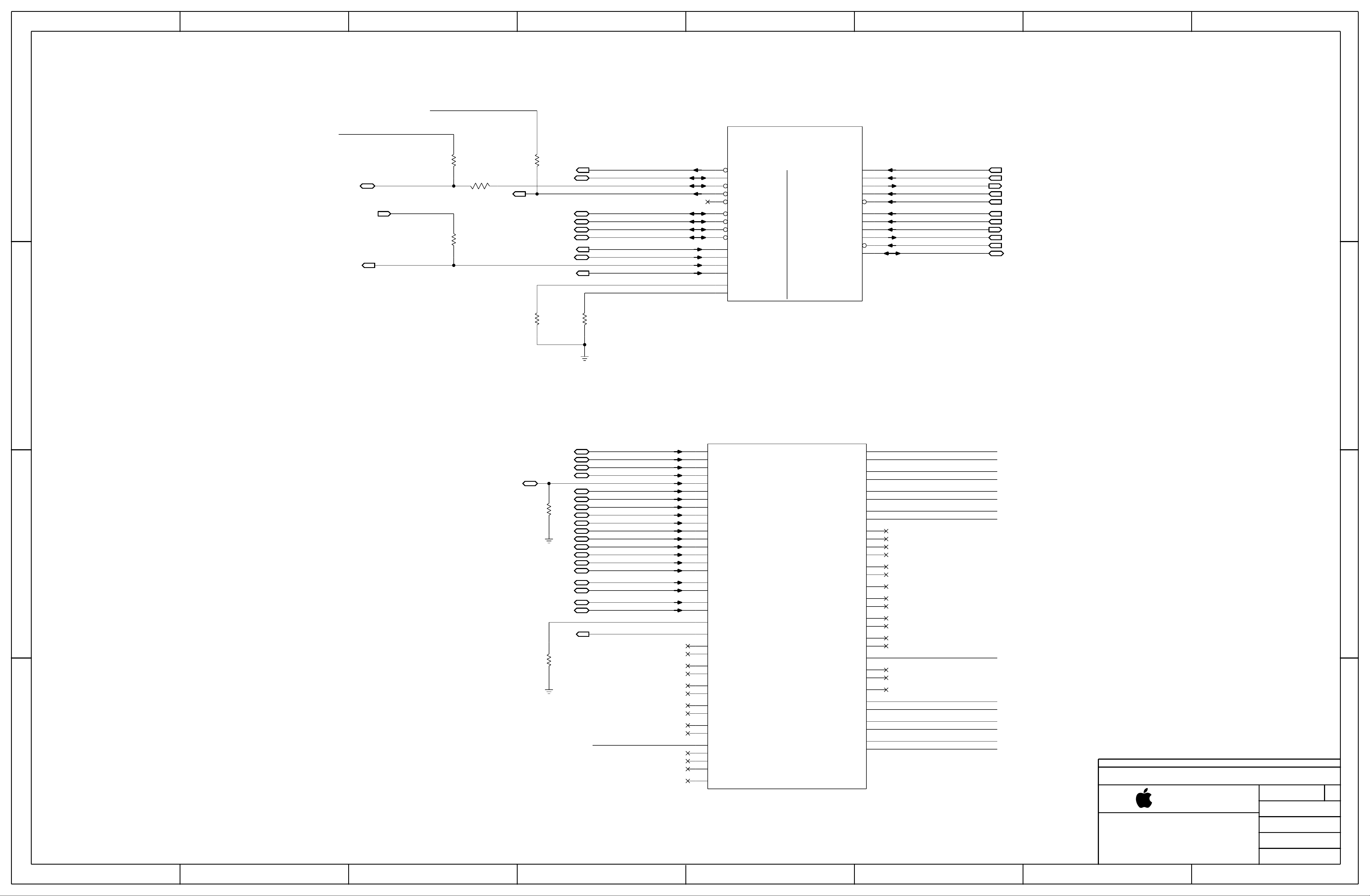

CPU MISC

(IPD)

(IPD)

(IPU)

(IPU)

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST*

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST*

JTAGX

D53

C54

G48

C59

F47

B53

C50

B51

A52

C52

B49

XDP_CPUPCH_TCK

XDP_CPUPCH_TDI

XDP_CPUPCH_TDO

XDP_CPUPCH_TMS

XDP_CPUPCH_TRST_L

TP_XDP_PCH_TCK

XDP_CPUPCH_TDI

XDP_CPUPCH_TDO

XDP_CPUPCH_TMS

XDP_CPUPCH_TRST_L

XDP_CPUPCH_TCK

OUT

OUT

IN

IN

IN

IN

IN

IN

IN

IN

BI

18

18

18

18

18

18

18

18

18

18

18

D

C

B

A

R0620

49.9

PLACE_NEAR=U0500.BN17:2.54mm

PLACE_NEAR=U0500.BP16:2.54mm

1

1%

1/20W

MF

201

2

18

BI

R0634

1K

5%

1/20W

MF

201

R0680

49.9

1%

1/20W

MF

201

1

2

1

2

R0621

49.9

1%

1/20W

MF

201

18

18

18

18

18

18

18

18

18

18

18

18

18

18

18

18

18

18

18

18

1

2

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

OUT

CPU_CFG<0>

CPU_CFG<1>

CPU_CFG<2>

CPU_CFG<3>

CPU_CFG<4>

CPU_CFG<5>

CPU_CFG<6>

CPU_CFG<7>

CPU_CFG<8>

CPU_CFG<9>

CPU_CFG<10>

CPU_CFG<11>

CPU_CFG<12>

CPU_CFG<13>

CPU_CFG<14>

CPU_CFG<15>

CPU_CFG<16>

CPU_CFG<17>

CPU_CFG<18>

CPU_CFG<19>

CPU_CFG_RCOMP

ITP_PMODE

TP_MCP_RSVD_D49

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

G52

F53

J52

H53

H55

D55

C56

F55

D61

G58

D57

F61

J60

J58

H61

H59

J54

G54

G56

J56

A54

A60

B4

B3

F3

F1

L36

L38

BA19

BB18

BC19

BD18

D49

M21

L20

M19

L26

CRITICAL

OMIT_TABLE

U0500

KBL-PCH-Y-QKKR

BGA

947915

(IPU)

BL64

BG47

BA17

AY18

BF18

BE19

BA23

AY22

R12

P13

M15

L16

L18

M17

AH7

K12

H12

BN3

BP3

L22

M23

BN1

AY20

BA21

BB14

M25

L24

L28

M27

BJ15

BJ17

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

TP_MCP_RSVD_BL64

TP_MCP_RSVD_BG47

TP_MCP_RSVD_BA17

TP_MCP_RSVD_AY18

TP_MCP_RSVD_BF18

TP_MCP_RSVD_BE19

TP_MCP_RSVD_BA23

TP_MCP_RSVD_AY22

TP_MCP_RSVD_BN1

TP_MCP_RSVD_M25

TP_MCP_RSVD_L24

TP_MCP_RSVD_L28

TP_MCP_RSVD_M27

TP_MCP_RSVD_BJ15

TP_MCP_RSVD_BJ17

SYNC_MASTER=J122_MLB SYNC_DATE=03/30/2018

PAGE TITLE

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

BOM_COST_GROUP=CPU & CHIPSET

IV ALL RIGHTS RESERVED

CPU Misc/JTAG/CFG/RSVD

DRAWING NUMBER

051-04039

Apple Inc.

REVISION

2.0.0

BRANCH

PAGE

6 OF 145

SHEET

6 OF 85

C

B

A

SIZE

D

8

67

35 4

2

.

1

Page 7

678

3 245

1

D

C

B

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

MEM_A_DQ<0>

MEM_A_DQ<1>

MEM_A_DQ<2>

MEM_A_DQ<3>

MEM_A_DQ<4>

MEM_A_DQ<5>

MEM_A_DQ<6>

MEM_A_DQ<7>

MEM_A_DQ<8>

MEM_A_DQ<9>

MEM_A_DQ<10>

MEM_A_DQ<11>

MEM_A_DQ<12>

MEM_A_DQ<13>

MEM_A_DQ<14>

MEM_A_DQ<15>

MEM_A_DQ<16>

MEM_A_DQ<17>

MEM_A_DQ<18>

MEM_A_DQ<19>

MEM_A_DQ<20>

MEM_A_DQ<21>

MEM_A_DQ<22>

MEM_A_DQ<23>

MEM_A_DQ<24>

MEM_A_DQ<25>

MEM_A_DQ<26>

MEM_A_DQ<27>

MEM_A_DQ<28>

MEM_A_DQ<29>

MEM_A_DQ<30>

MEM_A_DQ<31>

MEM_A_DQ<32>

MEM_A_DQ<33>

MEM_A_DQ<34>

MEM_A_DQ<35>

MEM_A_DQ<36>

MEM_A_DQ<37>

MEM_A_DQ<38>

MEM_A_DQ<39>

MEM_A_DQ<40>

MEM_A_DQ<41>

MEM_A_DQ<42>

MEM_A_DQ<43>

MEM_A_DQ<44>

MEM_A_DQ<45>

MEM_A_DQ<46>

MEM_A_DQ<47>

MEM_A_DQ<48>

MEM_A_DQ<49>

MEM_A_DQ<50>

MEM_A_DQ<51>

MEM_A_DQ<52>

MEM_A_DQ<53>

MEM_A_DQ<54>

MEM_A_DQ<55>

MEM_A_DQ<56>

MEM_A_DQ<57>

MEM_A_DQ<58>

MEM_A_DQ<59>

MEM_A_DQ<60>

MEM_A_DQ<61>

MEM_A_DQ<62>

MEM_A_DQ<63>

AG61

AH60

AK62

AK60

AH62

AG63

AL61

AL63

AM60

AM62

AT60

AR61

AN61

AN63

AR63

AT62

AT56

AR55

AN57

AN55

AR57

AT58

AM58

AM56

AL55

AL57

AH58

AH56

AK58

AK56

AG55

AG57

BE55

BC55

BG53

BE53

BC53

BG55

BD52

BF52

BC51

BE51

BC49

BE49

BG51

BG49

BF48

BD48

BJ55

BL55

BJ53

BL53

BN55

BN53

BM52

BK52

BL51

BJ51

BL49

BJ49

BN49

BN51

BK48

BM48

DDR0_DQ0

DDR0_DQ1

DDR0_DQ2

DDR0_DQ3

DDR0_DQ4

DDR0_DQ5

DDR0_DQ6

DDR0_DQ7

DDR0_DQ8

DDR0_DQ9

DDR0_DQ10

DDR0_DQ11

DDR0_DQ12

DDR0_DQ13

DDR0_DQ14

DDR0_DQ15

DDR1_DQ0/DDR0_DQ16

DDR1_DQ1/DDR0_DQ17

DDR1_DQ2/DDR0_DQ18

DDR1_DQ3/DDR0_DQ19

DDR1_DQ4/DDR0_DQ20

DDR1_DQ5/DDR0_DQ21

DDR1_DQ6/DDR0_DQ22

DDR1_DQ7/DDR0_DQ23

DDR1_DQ8/DDR0_DQ24

DDR1_DQ9/DDR0_DQ25

DDR1_DQ10/DDR0_DQ26

DDR1_DQ11/DDR0_DQ27

DDR1_DQ12/DDR0_DQ28

DDR1_DQ13/DDR0_DQ29

DDR1_DQ14/DDR0_DQ30

DDR1_DQ15/DDR0_DQ31

DDR0_DQ16/DDR0_DQ32

DDR0_DQ17/DDR0_DQ33

DDR0_DQ18/DDR0_DQ34

DDR0_DQ19/DDR0_DQ35

DDR0_DQ20/DDR0_DQ36

DDR0_DQ21/DDR0_DQ37

DDR0_DQ22/DDR0_DQ38

DDR0_DQ23/DDR0_DQ39

DDR0_DQ24/DDR0_DQ40

DDR0_DQ25/DDR0_DQ41

DDR0_DQ26/DDR0_DQ42

DDR0_DQ27/DDR0_DQ43

DDR0_DQ28/DDR0_DQ44

DDR0_DQ29/DDR0_DQ45

DDR0_DQ30/DDR0_DQ46

DDR0_DQ31/DDR0_DQ47

DDR1_DQ16/DDR0_DQ48

DDR1_DQ17/DDR0_DQ49

DDR1_DQ18/DDR0_DQ50

DDR1_DQ19/DDR0_DQ51

DDR1_DQ20/DDR0_DQ52

DDR1_DQ21/DDR0_DQ53

DDR1_DQ22/DDR0_DQ54

DDR1_DQ23/DDR0_DQ55

DDR1_DQ24/DDR0_DQ56

DDR1_DQ25/DDR0_DQ57

DDR1_DQ26/DDR0_DQ58

DDR1_DQ27/DDR0_DQ59

DDR1_DQ28/DDR0_DQ60

DDR1_DQ29/DDR0_DQ61

DDR1_DQ30/DDR0_DQ62

DDR1_DQ31/DDR0_DQ63

CRITICAL

OMIT_TABLE

U0500

KBL-PCH-Y-QKKR

BGA

947915

SYM 2 OF 20

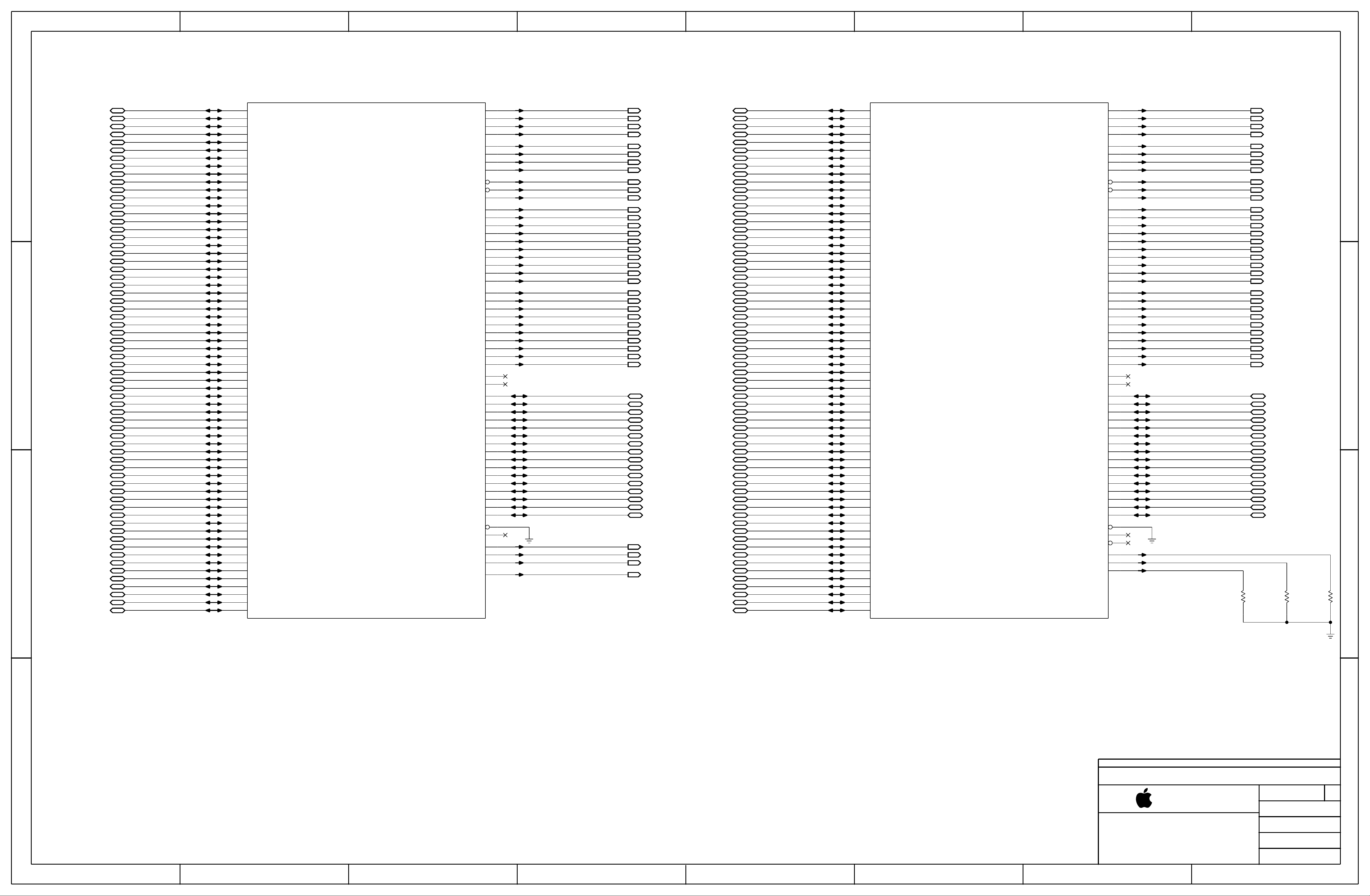

DDR CH - A

DDR0_CKN0

DDR0_CKP0

DDR0_CKN1

DDR0_CKP1

DDR0_CKE0

DDR0_CKE1

DDR0_CKE2

DDR0_CKE3

DDR0_CS0*

DDR0_CS1*

DDR0_ODT0

DDR0_CAA0

DDR0_CAA1

DDR0_CAA2

DDR0_CAA3

DDR0_CAA4

DDR0_CAA5

DDR0_CAA6

DDR0_CAA7

DDR0_CAA8

DDR0_CAA9

DDR0_CAB0

DDR0_CAB1

DDR0_CAB2

DDR0_CAB3

DDR0_CAB4

DDR0_CAB5

DDR0_CAB6

DDR0_CAB7

DDR0_CAB8

DDR0_CAB9

DDR0_MA3

DDR0_MA4

DDR0_DQSN0

DDR0_DQSP0

DDR0_DQSN1

DDR0_DQSP1

DDR1_DQSN0/DDR0_DQSN2

DDR1_DQSP0/DDR0_DQSP2

DDR1_DQSN1/DDR0_DQSN3

DDR1_DQSP1/DDR0_DQSP3

DDR0_DQSN2/DDR0_DQSN4

DDR0_DQSP2/DDR0_DQSP4

DDR0_DQSN3/DDR0_DQSN5

DDR0_DQSP3/DDR0_DQSP5

DDR1_DQSN2/DDR0_DQSN6

DDR1_DQSP2/DDR0_DQSP6

DDR1_DQSN3/DDR0_DQSN7

DDR1_DQSP3/DDR0_DQSP7

DDR0_ALERT*

DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

BC62

BC60

BA60

BA62

BB57

BC58

BE57

AW61

AW63

BJ57

BN61

AW59

AW55

BF62

AV56

AW57

AV58

BA56

BD59

BD61

BG61

BK59

BL62

BJ61

AV60

BN62

BB61

BL61

BM59

BN58

AV62

BB63

BL57

AJ61

AJ63

AP62

AP60

AP56

AP58

AJ57

AJ55

BD54

BF54

BF50

BD50

BM54

BK54

BK50

BM50

BG57

BM56

AR53

AN53

AW53

BN47

NC

NC

MEM_A_CLK_N<0>

MEM_A_CLK_P<0>

MEM_A_CLK_N<1>

MEM_A_CLK_P<1>

MEM_A_CKE<0>

MEM_A_CKE<1>

MEM_A_CKE<2>

MEM_A_CKE<3>

MEM_A_CS_L<0>

MEM_A_CS_L<1>

MEM_A_ODT<0>

MEM_A_CAA<0>

MEM_A_CAA<1>

MEM_A_CAA<2>

MEM_A_CAA<3>

MEM_A_CAA<4>

MEM_A_CAA<5>

MEM_A_CAA<6>

MEM_A_CAA<7>

MEM_A_CAA<8>

MEM_A_CAA<9>

MEM_A_CAB<0>

MEM_A_CAB<1>

MEM_A_CAB<2>

MEM_A_CAB<3>

MEM_A_CAB<4>

MEM_A_CAB<5>

MEM_A_CAB<6>

MEM_A_CAB<7>

MEM_A_CAB<8>

MEM_A_CAB<9>

MEM_A_DQS_N<0>

MEM_A_DQS_P<0>

MEM_A_DQS_N<1>

MEM_A_DQS_P<1>

MEM_A_DQS_N<2>

MEM_A_DQS_P<2>

MEM_A_DQS_N<3>

MEM_A_DQS_P<3>

MEM_A_DQS_N<4>

MEM_A_DQS_P<4>

MEM_A_DQS_N<5>

MEM_A_DQS_P<5>

MEM_A_DQS_N<6>

MEM_A_DQS_P<6>

MEM_A_DQS_N<7>

MEM_A_DQS_P<7>

CPU_DIMM_VREFCA

CPU_DIMMA_VREFDQ

CPU_DIMMB_VREFDQ

PM_MEMVTT_EN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

21

21

21

66

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

CRITICAL

OMIT_TABLE

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

24 22

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

MEM_B_DQ<0>

MEM_B_DQ<1>

MEM_B_DQ<2>

MEM_B_DQ<3>

MEM_B_DQ<4>

MEM_B_DQ<5>

MEM_B_DQ<6>

MEM_B_DQ<7>

MEM_B_DQ<8>

MEM_B_DQ<9>

MEM_B_DQ<10>

MEM_B_DQ<11>

MEM_B_DQ<12>

MEM_B_DQ<13>

MEM_B_DQ<14>

MEM_B_DQ<15>

MEM_B_DQ<16>

MEM_B_DQ<17>

MEM_B_DQ<18>

MEM_B_DQ<19>

MEM_B_DQ<20>

MEM_B_DQ<21>

MEM_B_DQ<22>

MEM_B_DQ<23>

MEM_B_DQ<24>

MEM_B_DQ<25>

MEM_B_DQ<26>

MEM_B_DQ<27>

MEM_B_DQ<28>

MEM_B_DQ<29>

MEM_B_DQ<30>

MEM_B_DQ<31>

MEM_B_DQ<32>

MEM_B_DQ<33>

MEM_B_DQ<34>

MEM_B_DQ<35>

MEM_B_DQ<36>

MEM_B_DQ<37>

MEM_B_DQ<38>

MEM_B_DQ<39>

MEM_B_DQ<40>

MEM_B_DQ<41>

MEM_B_DQ<42>

MEM_B_DQ<43>

MEM_B_DQ<44>

MEM_B_DQ<45>

MEM_B_DQ<46>

MEM_B_DQ<47>

MEM_B_DQ<48>

MEM_B_DQ<49>

MEM_B_DQ<50>

MEM_B_DQ<51>

MEM_B_DQ<52>

MEM_B_DQ<53>

MEM_B_DQ<54>

MEM_B_DQ<55>

MEM_B_DQ<56>

MEM_B_DQ<57>

MEM_B_DQ<58>

MEM_B_DQ<59>

MEM_B_DQ<60>

MEM_B_DQ<61>

MEM_B_DQ<62>

MEM_B_DQ<63>

BC41

BC39

BG41

BE39

BF42

BD42

BG39

BE41

BC43

BD46

BG43

BG45

BC45

BE43

BE45

BF46

BM28

BN27

BK28

BL25

BN25

BL27

BJ25

BJ27

BM24

BK24

BN21

BJ23

BL23

BN23

BJ21

BL21

BN45

BM46

BL43

BK46

BN43

BL45

BJ45

BJ43

BM42

BN41

BJ41

BN39

BK42

BL41

BL39

BJ39

BF28

BD28

BG25

BC27

BG27

BE27

BE25

BC25

BF24

BD24

BG21

BC23

BE23

BG23

BC21

BE21

DDR0_DQ32/DDR1_DQ0

DDR0_DQ33/DDR1_DQ1

DDR0_DQ34/DDR1_DQ2

DDR0_DQ35/DDR1_DQ3

DDR0_DQ36/DDR1_DQ4

DDR0_DQ37/DDR1_DQ5

DDR0_DQ38/DDR1_DQ6

DDR0_DQ39/DDR1_DQ7

DDR0_DQ40/DDR1_DQ8

DDR0_DQ41/DDR1_DQ9

DDR0_DQ42/DDR1_DQ10

DDR0_DQ43/DDR1_DQ11

DDR0_DQ44/DDR1_DQ12

DDR0_DQ45/DDR1_DQ13

DDR0_DQ46/DDR1_DQ14

DDR0_DQ47/DDR1_DQ15

DDR1_DQ32/DDR1_DQ16

DDR1_DQ33/DDR1_DQ17

DDR1_DQ34/DDR1_DQ18

DDR1_DQ35/DDR1_DQ19

DDR1_DQ36/DDR1_DQ20

DDR1_DQ37/DDR1_DQ21

DDR1_DQ38/DDR1_DQ22

DDR1_DQ39/DDR1_DQ23

DDR1_DQ40/DDR1_DQ24

DDR1_DQ41/DDR1_DQ25

DDR1_DQ42/DDR1_DQ26

DDR1_DQ43/DDR1_DQ27

DDR1_DQ44/DDR1_DQ28

DDR1_DQ45/DDR1_DQ29

DDR1_DQ46/DDR1_DQ30

DDR1_DQ47/DDR1_DQ31

DDR0_DQ48/DDR1_DQ32

DDR0_DQ49/DDR1_DQ33

DDR0_DQ50/DDR1_DQ34

DDR0_DQ51/DDR1_DQ35

DDR0_DQ52/DDR1_DQ36

DDR0_DQ53/DDR1_DQ37

DDR0_DQ54/DDR1_DQ38

DDR0_DQ55/DDR1_DQ39

DDR0_DQ56/DDR1_DQ40

DDR0_DQ57/DDR1_DQ41

DDR0_DQ58/DDR1_DQ42

DDR0_DQ59/DDR1_DQ43

DDR0_DQ60/DDR1_DQ44

DDR0_DQ61/DDR1_DQ45

DDR0_DQ62/DDR1_DQ46

DDR0_DQ63/DDR1_DQ47

DDR1_DQ48

DDR1_DQ49

DDR1_DQ50

DDR1_DQ51

DDR1_DQ52

DDR1_DQ53

DDR1_DQ54

DDR1_DQ55

DDR1_DQ56

DDR1_DQ57

DDR1_DQ58

DDR1_DQ59

DDR1_DQ60

DDR1_DQ61

DDR1_DQ62

DDR1_DQ63

U0500

KBL-PCH-Y-QKKR

BGA

947915

SYM 3 OF 20

DDR CH - B

DDR1_CKN0

DDR1_CKP0

DDR1_CKN1

DDR1_CKP1

DDR1_CKE0

DDR1_CKE1

DDR1_CKE2

DDR1_CKE3

DDR1_CS0*

DDR1_CS1*

DDR1_ODT0

DDR1_CAA0

DDR1_CAA1

DDR1_CAA2

DDR1_CAA3

DDR1_CAA4

DDR1_CAA5

DDR1_CAA6

DDR1_CAA7

DDR1_CAA8

DDR1_CAA9

DDR1_CAB0

DDR1_CAB1

DDR1_CAB2

DDR1_CAB3

DDR1_CAB4

DDR1_CAB5

DDR1_CAB6

DDR1_CAB7

DDR1_CAB8

DDR1_CAB9

DDR1_MA3

DDR1_MA4

DDR0_DQSN4/DDR1_DQSN0

DDR0_DQSP4/DDR1_DQSP0

DDR0_DQSN5/DDR1_DQSN1

DDR0_DQSP5/DDR1_DQSP1

DDR1_DQSN4/DDR1_DQSN2

DDR1_DQSP4/DDR1_DQSP2

DDR1_DQSN5/DDR1_DQSN3

DDR1_DQSP5/DDR1_DQSP3

DDR0_DQSN6/DDR1_DQSN4

DDR0_DQSP6/DDR1_DQSP4

DDR0_DQSN7/DDR1_DQSN5

DDR0_DQSP7/DDR1_DQSP5

DDR1_DQSN6

DDR1_DQSP6

DDR1_DQSN7

DDR1_DQSP7

DDR1_ALERT*

DDR1_PAR

DRAM_RESET*

DDR_RCOMP0

DDR_RCOMP1

DDR_RCOMP2

BK36

BM36

BD32

BF32

BN33

BK32

BG33

BH30

BM30

BJ33

BC35

BK30

BN31

BM32

BL37

BG31

BN37

BJ37

BJ35

BM34

BN35

BG37

BE37

BC37

BF34

BC33

BF30

BD36

BG35

BC31

BF36

BJ31

BK34

BD40

BF40

BD44

BF44

BK26

BM26

BM22

BK22

BK44

BM44

BM40

BK40

BD26

BF26

BF22

BD22

BD34

BD30

BP20

BF64

BJ64

BC64

NC

NC

NCNC

NC

MEM_B_CLK_N<0>

MEM_B_CLK_P<0>

MEM_B_CLK_N<1>

MEM_B_CLK_P<1>

MEM_B_CKE<0>

MEM_B_CKE<1>

MEM_B_CKE<2>

MEM_B_CKE<3>

MEM_B_CS_L<0>

MEM_B_CS_L<1>

MEM_B_ODT<0>

MEM_B_CAA<0>

MEM_B_CAA<1>

MEM_B_CAA<2>

MEM_B_CAA<3>

MEM_B_CAA<4>

MEM_B_CAA<5>

MEM_B_CAA<6>

MEM_B_CAA<7>

MEM_B_CAA<8>

MEM_B_CAA<9>

MEM_B_CAB<0>

MEM_B_CAB<1>

MEM_B_CAB<2>

MEM_B_CAB<3>

MEM_B_CAB<4>

MEM_B_CAB<5>

MEM_B_CAB<6>

MEM_B_CAB<7>

MEM_B_CAB<8>

MEM_B_CAB<9>

MEM_B_DQS_N<0>

MEM_B_DQS_P<0>

MEM_B_DQS_N<1>

MEM_B_DQS_P<1>

MEM_B_DQS_N<2>

MEM_B_DQS_P<2>

MEM_B_DQS_N<3>

MEM_B_DQS_P<3>

MEM_B_DQS_N<4>

MEM_B_DQS_P<4>

MEM_B_DQS_N<5>

MEM_B_DQS_P<5>

MEM_B_DQS_N<6>

MEM_B_DQS_P<6>

MEM_B_DQS_N<7>

MEM_B_DQS_P<7>

CPU_SM_RCOMP<0>

CPU_SM_RCOMP<1>

CPU_SM_RCOMP<2>

R0752

162

1%

1/20W

MF

201

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

78

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

24 23

D

C

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

B

1%

1/20W

MF

201

1

2

R0750

1

R0751

80.6

2

200

1%

1/20W

MF

201

1

2

A

PAGE TITLE

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

BOM_COST_GROUP=CPU & CHIPSET

IV ALL RIGHTS RESERVED

PLACE_NEAR=U0500.BC64:12.7mm

PLACE_NEAR=U0500.BJ64:12.7mm

PLACE_NEAR=U0500.BF64:12.7mm

SYNC_DATE=03/30/2018SYNC_MASTER=J122_MLB

CPU LPDDR3 Interface

DRAWING NUMBER

051-04039

Apple Inc.

REVISION

2.0.0

BRANCH

PAGE

7 OF 145

SHEET

7 OF 85

A

SIZE

D

8

67

35 4

2

1

Page 8

678

3 245

1

D

C

B

A

SKL-ULX current estimates from Skylake Processor EDS vol 1, doc #544924, v0.94

VCCIO breakdown per 4/20/15 email from Srini

CRITICAL

OMIT_TABLE

U0500

KBL-PCH-Y-QKKR

BGA

PPVCCGT_S0_CPU

8 12 76

24A Max

AA53

AB62

AC47

AC55

AD54

AD64

AE61

AF47

AJ53

AK49

AN46

AT43

AT50

N50

T46

T54

U61

V60

W57

Y44

Y51

Y62

AB54

AB64

AC49

AC57

AD56

AE53

AE63

AF49

AK43

AK50

AN47

AT44

AT51

R51

T47

U53

U63

V62

W59

Y46

Y54

Y64

AB58

AC44

AC51

AC61

AD60

AE57

AF44

AF51

AK46

AB60

AC46

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

947915

SYM 14 OF 20

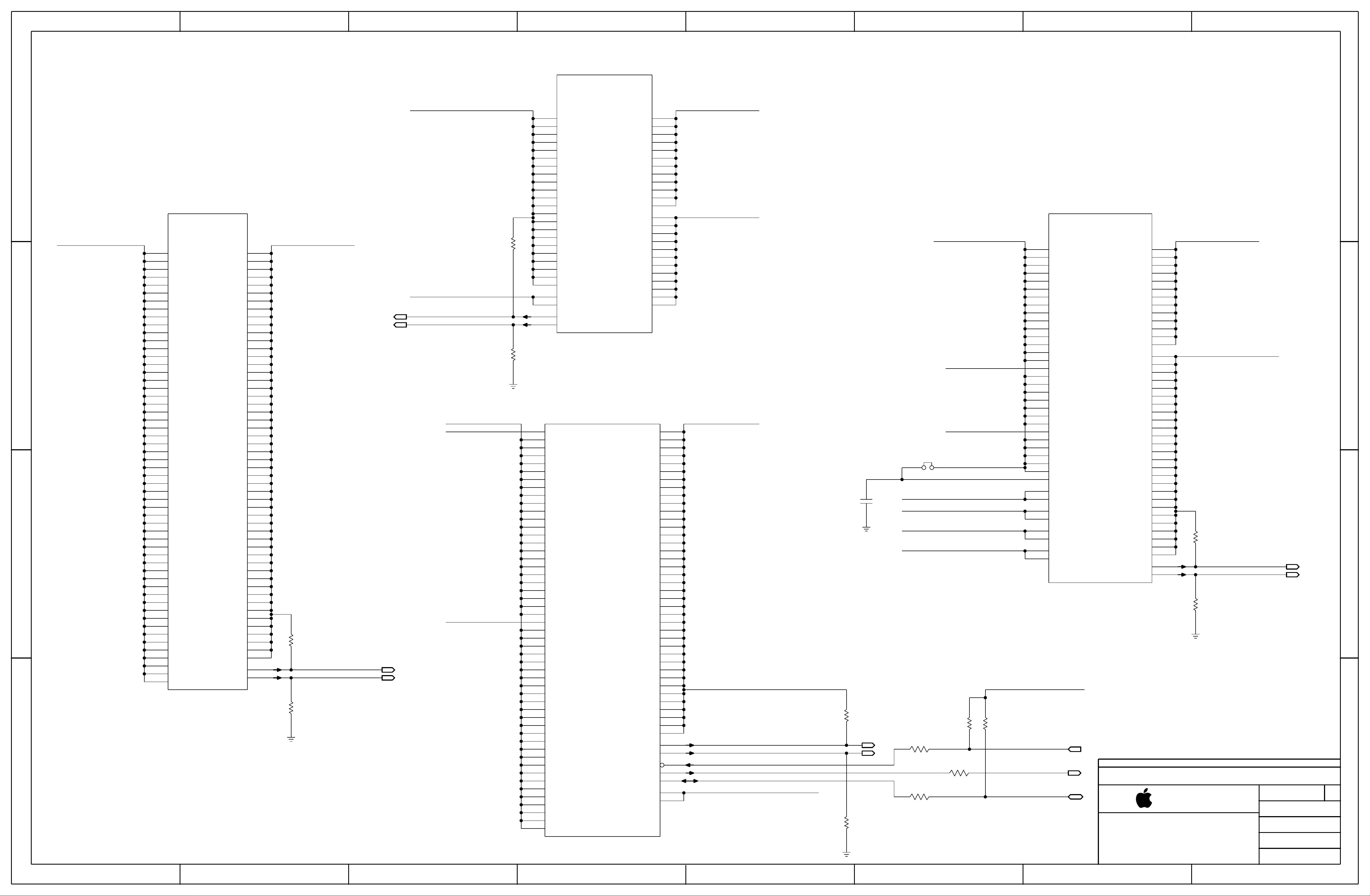

CPU POWER 2 OF 4

VCCGT_SENSE

VSSGT_SENSE

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

AC53

AC63

AD62

AE59

AF46

AG53

AK47

AN44

AN51

AT49

N48

T44

T51

U59

V58

W55

Y43

Y50

Y60

AB56

AC43

AC50

AC59

AD58

AE55

AF43

AF50

AK44

AK51

AN49

AT46

N44

R53

T49

U55

V54

V64

W61

Y47

Y56

AN50

AT47

N46

T43

T50

U57

V56

W53

W63

Y49

Y58

AN43

N52

P52

PPVCCGT_S0_CPU

PLACE_NEAR=U0500.N52:50.8mm

1

R0830

100

5%

1/20W

MF

201

2

CPU_VCCGTSENSE_P

CPU_VCCGTSENSE_N

PLACE_NEAR=U0500.P52:50.8mm

1

R0831

100

5%

1/20W

MF

201

2

8 12 76

OUT

OUT

PPVCCSA_S0_CPU

11 76

3.78A Max

PLACE_NEAR=U0500.N30:50.8mm

VCCSA & VCCSA_DDR must

be isolated from VR

output to BGA pads

PPVCCSA_S0_CPUDDR

11 76

320mA Max

59

59

OUT

OUT

CPU_VCCSASENSE_P

CPU_VCCSASENSE_N

PLACE_NEAR=U0500.R30:50.8mm

24A Max

PPVCC_S0_CPU

8 11 49 76

TP_MCP_DC_A64

TP_MCP_DC_B64

59

59

R0860

100

5%

1/20W

MF

201

R0861

100

5%

1/20W

MF

201

NOTE: Aliases not used on CPU supply outputs

to avoid any extraneous connections.

CRITICAL

OMIT_TABLE

U0500

KBL-PCH-Y-QKKR

BGA

947915

SYM 16 OF 20

AA29

AF30

AN29

AC29

AH29

AN30

AC30

AK29

AR29

1

2

1

2

AE29

AK30

AF29

AL29

AT29

AT30

VCCSA

VCCSA

VCCSA

L30

VCCSA

T30

VCCSA

VCCSA

VCCSA

VCCSA

M31

VCCSA

V29

VCCSA

VCCSA

VCCSA

VCCSA

N30

VCCSA

Y29

VCCSA

VCCSA

VCCSA

R29

VCCSA

Y30

VCCSA

VCCSA

VCCSA

T29

VCCSA

VCCSA_DDR

VCCSA_DDR

M29

VCCSA_SENSE

N28

VSSSA_SENSE

VCCG0

VCCG0

VCCG0

VCCG0

VCCG0

VCCG0

VCCG0

CPU POWER 4 OF 4

VCCG0

VCCG0

VCCG0

VCCG0

VCCG0

VCCG1

VCCG1

VCCG1

VCCG1

VCCG1

VCCG1

VCCG1

VCCG1

VCCG1

VCCG1

VCCG1

VCCG1

AA35

R38

Y35

AA38

T35

Y38

AC35

T38

AC38

V35

R35

V38

AF35

AK38

AR35

AF38

AL35

AR38

AH35

AL38

AH38

AN35

AK35

AN38

CRITICAL

OMIT_TABLE

A64

AE32

AE40

AH41

AN32

AT33

AT41

J64

L48

M33

M43

M53

M64

N40

N59

P60

R57

T41

AA32

AE33

AE41

AK32

AN41

AT35

B64

L40

L50

M35

M45

M56

N32

N42

N61

P62

R59

V32

AA41

AE35

AF32

AK41

AR32

AT36

D64

L42

L52

M37

M47

R63

P56

R32

Y32

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

U0500

KBL-PCH-Y-QKKR

BGA

947915

SYM 13 OF 20

CPU POWER 1 OF 4

VCC_SENSE

VSS_SENSE

VIDALERT*

VIDSCK

VIDSOUT

VCCSTG

VCCSTG

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCVCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

M58

N34

N54

N63

P64

R61

V41

AC41

AE38

AH32

AL41

AT32

AT40

H63

L46

L63

M41

M51

M62

N38

N57

P58

R41

T32

Y41

AC32

AE36

AF41

AL32

AR41

AT38

F64

L44

L54

M39

M49

M60

N36

N55

L34

L32

B58

A56

A58

AA26

AC26

PPVCCG0_S0_CPU

MIN_LINE_WIDTH=0.1500

MIN_NECK_WIDTH=0.1500

VOLTAGE=1.5V

PPVCCG1_S0_CPU

MIN_LINE_WIDTH=0.1500

MIN_NECK_WIDTH=0.1500

VOLTAGE=1.5V

PPVCC_S0_CPU

CPU_VCCSENSE_P

CPU_VCCSENSE_N

CPU_VIDALERT_R_L

CPU_VIDSCLK_R

CPU_VIDSOUT_R

PP1V_S0SW

11

11

8 11 49 76

VDDQC must implement

1nH trace filter

BYPASS=U0500.BA39::0.59mm

C0850

0.1UF

X5R-CERM

PLACE_NEAR=U0500.L34:50.8mm

100

5%

1/20W

MF

201

100

5%

1/20W

MF

201

1

2

1

2

R0820

6 8 12 18

75

PLACE_NEAR=U0500.L32:50.8mm

R0821

10%

10V

0201

1

2

OUT

OUT

59

59

PP1V2_S3

12 76

2A Max

TP_MCP_DC_BN64

TP_MCP_DC_BP64

XW0850

SM

21

PP1V2_S0_CPU_VDDQC

MIN_LINE_WIDTH=0.2000

MIN_NECK_WIDTH=0.2000

VOLTAGE=1.2V

PP1V_S3

6 8 12 15

59 75

PP1V_S0SW

6 8 12 18 75

PP1V2_S0SW

12 76

PP1V_S3

12 75

R0800

56

1%

1/20W

MF

R0810

220

21

1%

1/20W

MF

201

R0812

0

21

5%

1/20W

MF

0201

201

R0811

0

5%

1/20W

MF

0201

R0800.2:

R0802.2:

R0811.1:

AH64

BA27

BA37

BA49

BP32

BP50

AK64

BA29

BA41

BA51

BP34

BP56

AT64

BA31

BA43

BN64

BP40

BP58

AV64

BA33

BA45

BP24

BP42

BP64

BA25

BA35

BA47

BP26

BP48

BA39

V26

Y26

R26

T26

AE27

AF27

R27

T27

PP1V_S3

1

2

1

R0802

100

1%

1/20W

MF

201

2

CPU_VIDALERT_L

21

CPU_VIDSCLK

CPU_VIDSOUT

PLACE_NEAR=U0500.B58:12.7mm

PLACE_NEAR=U0500.A58:12.7mm

PLACE_NEAR=U0500.A56:12.7mm

BOM_COST_GROUP=CPU & CHIPSET

KBL-PCH-Y-QKKR

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQC

VCCST

VCCST

VCCSTG

VCCSTG

VCCPLL_OC

VCCPLL_OC

VCCPLL

VCCPLL

IN

OUT

BI

CRITICAL

OMIT_TABLE

U0500

BGA

947915

SYM 15 OF 20

CPU POWER 3 OF 4

VCCIO_SENSE

VSSIO_SENSE

6 8 12 15 59 75

59

SYNC_MASTER=J122_MLB SYNC_DATE=03/30/2018

PAGE TITLE

59

59

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

PPVCCIO_S0_CPU

AC23

AF24

AN26

AC24

AF26

AR26

AE23

AH26

AT26

AE24

AK26

AE26

AL26

AV26

AV36

AV46

AW31

AW41

AW51

AV28

AV38

AV48

AW33

AW43

AV30

AV40

AV50

AW35

AW45

AV32

AV42

AW27

AW37

AW47

AV34

AV44

AW29

AW39

AW49

AT24

AR24

VCCIO & VCCIO_DDR must

be isolated from local

plane to BGA pads

PPVCCIO_S0_CPU

PLACE_NEAR=U0500.AT26:50.8mm

1

R0840

100

5%

1/20W

MF

201

2

CPU_VCCIOSENSE_P

CPU_VCCIOSENSE_N

PLACE_NEAR=U0500.AN24:50.8mm

1

R0841

100

5%

1/20W

MF

201

2

CPU Power

Apple Inc.

1.185A Max

1.75A Max

5 11 76

76

OUT

OUT

DRAWING NUMBER

051-04039

REVISION

2.0.0

BRANCH

PAGE

8 OF 145

SHEET

8 OF 85

D

C

B

66

66

A

SIZE

D

8

67

35 4

2

1

Page 9

D

C

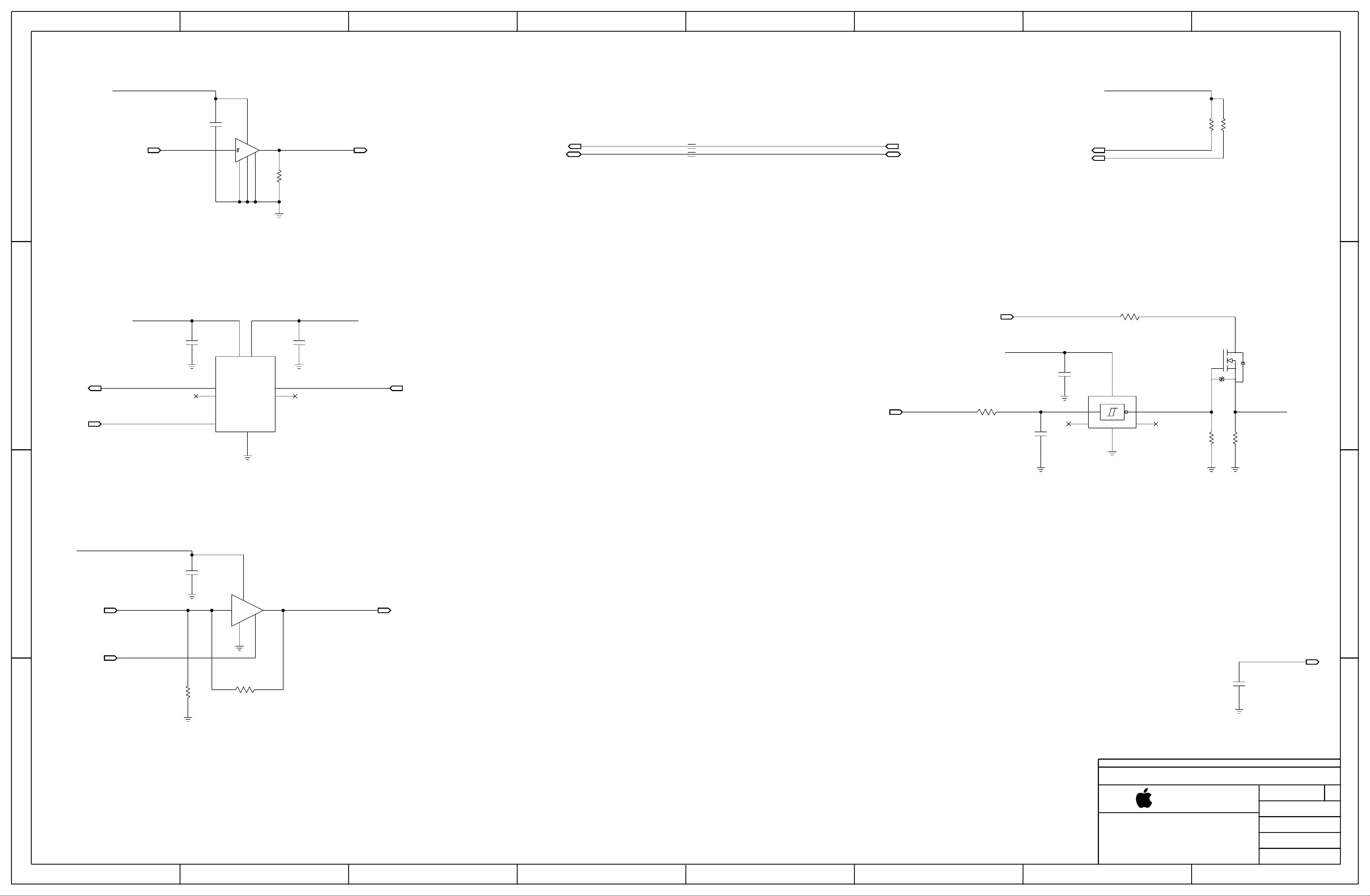

VCCAMPHYPLL_1P0 and VCCPRIM_1P0 / VCCPRIM_3P3 breakdowns from Srini email 4/13/15

BYPASS=U0500.AL2::5.32mm

20%

6.3V

X5R

1

2

C0920

1.0UF

0201-1

678

PP1V_PRIM

75

370mA Max

PPVCC_PRIM_CORE

75

1.1A Max

PP1V_S5_PCH_DCPDSW

MIN_LINE_WIDTH=0.2000

MIN_NECK_WIDTH=0.2000

VOLTAGE=1.0V

PP1V_PRIM

13 75

22mA Max

PP1V_PRIM

13 75

See EDS Table 10-5

PP1V_SUSSW_PCH_VCCAMPHYPLL

13

88mA Max

PP1V_SUS_PCH_VCCAPLL

13

26mA Max

PP1V_PRIM

13 75

168mA Max

PP3V3_S5

13 75

71mA Max

PP3V3R1V8R1V5_S0_PCH_VCCHDA

13

68/36/33mA @ 3.3/1.8/1.5V Max

PP1V8_S5

13 75

11/7mA @ 3.3/1.8V Max

PP1V_PRIM

75

0.565A Max

AH18

AH19

AK18

AL18

AE18

AE19

AF18

AF19

AR16

AT16

AL2

AM1

V1

W2

T1

T15

T16

U2

V15

V16

AA18

AA19

AH13

AH15

AL15

AM13

AT23

AV22

AT15

AV15

AA21

AA23

AK23

AL23

AN23

AR23

VCCPRIM_1P0

VCCPRIM_1P0

VCCPRIM_1P0

VCCPRIM_1P0

VCCPRIM_CORE

VCCPRIM_CORE

VCCPRIM_CORE

VCCPRIM_CORE

VCCPRIM_CORE

VCCPRIM_CORE

DCPDSW_1P0

DCPDSW_1P0

VCCMPHYAON_1P0

VCCMPHYAON_1P0

VCCMPHYGT_1P0

VCCMPHYGT_1P0

VCCMPHYGT_1P0

VCCMPHYGT_1P0

VCCAMPHYPLL_1P0

VCCAMPHYPLL_1P0

VCCAPLL_1P0

VCCAPLL_1P0

VCCPRIM_1P0

VCCPRIM_1P0

VCCDSW_3P3

VCCDSW_3P3

VCCHDA

VCCHDA

VCCSPI

VCCSPI

VCCSRAM_1P0

VCCSRAM_1P0

VCCSRAM_1P0

VCCSRAM_1P0

VCCSRAM_1P0

VCCSRAM_1P0

CRITICAL

OMIT_TABLE

U0500

KBL-PCH-Y-QKKR

BGA

947915

SYM 17 OF 20

PCH POWER

VCCPGPPA

VCCPGPPA

VCCPGPPB

VCCPGPPB

VCCPGPPC

VCCPGPPC

VCCPGPPD

VCCPGPPD

VCCPGPPE

VCCPGPPE

VCCPGPPF

VCCPGPPF

VCCPGPPG

VCCPGPPG

VCCPRIM_3P3

VCCPRIM_3P3

VCCPRIM_1P0

VCCPRIM_1P0

VCCATS

VCCATS

VCCRTCPRIM_3P3

VCCRTCPRIM_3P3

VCCRTC

VCCRTC

DCPRTC

DCPRTC

VCCCLK1

VCCCLK1

VCCCLK2

VCCCLK2

VCCCLK3

VCCCLK3

VCCCLK4

VCCCLK4

VCCCLK5

VCCCLK5

AT1

AU2

AV1

AW2

AH1

AJ2

AF1

AG2

AA2

AB1

AN2

AP1

AN15

AP13

AC2

AD1

AA15

AA16

AE15

AE16

AK19

AL19

AR19

AT19

AT18

AV18

V18

Y18

V19

Y19

V23

Y23

V21

Y21

R21

R23

PP1V8_S5

20/9mA @ 3.3/1.8V Max

PP1V8_S5

4/2mA @ 3.3/1.8V Max

PP1V8_S5

6/3mA @ 3.3/1.8V Max

PP1V8_S5

8/3mA @ 3.3/1.8V Max

PP3V3_S5

6/2mA @ 3.3/1.8V Max

PP1V8_S5

33/161mA @ 3.3/1.8V Max

PP3V3_S5

41/56mA @ 3.3/1.8V Max

PP3V3_S5

PP1V_PRIM

PP1V8_S5

PP3V3_S5

PPVOUT_S0_PCH_DCPRTC

MIN_LINE_WIDTH=0.2000

MIN_NECK_WIDTH=0.2000

VOLTAGE=1.0V

PP1V_PRIM

PP1V_PRIM

PP1V_SUS_PCH_VCCCLK3

PP1V_SUS_PCH_VCCCLK4

PP1V_SUS_PCH_VCCCLK5

3 245

1mA Max

6mA Max

6mA Max

<1mA Max

<1mA Max

35mA Max

29mA Max

24mA Max

33mA Max

4mA Max

75

17 75

14 17 75

75

13 75

17 75

14 75

75

75

13 75

13 75

75

75

13

13

13

Must not exceed

PP3V_G3H

1

C0901

1.0UF

20%

6.3V

2

X5R

0201-1

BYPASS=U0500.AR19::2.10mm

BYPASS=U0500.AT19::2.10mm

10%

10V

0201

1

2

C0900

0.1UF

X5R-CERM

1

C0910

0.1UF

10%

10V

2

X5R-CERM

0201

BYPASS=U0500.AT18::1.08mm

1

NOTE: Aliases not used on CPU supply outputsSPT-LP current estimates from Sunrise Point-LP PCH EDS vol 1, doc #545659, v1.2.

to avoid any extraneous connections.

D

3.2V max

15 75

C

B

PP3V3_S5

75

74mA Max

PP1V_PRIM

75

55mA Max

PP1V_PRIM

13 75

33mA Max

AH21

AK21

AR21

AT21

R15

R16

VCCPRIM_3P3

VCCPRIM_3P3

VCCPRIM_1P0

VCCPRIM_1P0

VCCAPLLEBB_1P0

VCCAPLLEBB_1P0

VCCCLK6

VCCCLK6

GPP_B0/CORE_VID0

GPP_B1/CORE_VID1

R19

T19

BA13

BB12

PP1V_PRIM

TP_PCH_CORE_VID<0>

TP_PCH_CORE_VID<1>

75

10mA Max

B

A

8

SYNC_DATE=03/30/2018SYNC_MASTER=J122_MLB

PAGE TITLE

A

PCH Power

DRAWING NUMBER

051-04039

Apple Inc.

REVISION

2.0.0

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

BOM_COST_GROUP=CPU & CHIPSET

67

35 4

IV ALL RIGHTS RESERVED

2

BRANCH

PAGE

9 OF 145

SHEET

9 OF 85

1

SIZE

D

Page 10

678

3 245

1

D

C

B

A14

AA36

AA47

AA57

AC15

AC27

AE10

AE43

AE50

AF16

AF40

AF62

AH24

AH40

AH49

AK1

AK24

AK40

AL16

AL33

AL46

AL53

AN18

AN33

AP64

AR2

AR4

AR47

AR6

AU55

AV16

AW17

AY16

AY32

AY42

AY52

BA5

BA9

BB28

BB38

BB48

BC17

BD56

BE33

BF56

BG2

BG8

BH28

BH40

BH50

BJ29

BK56

BL35

BM16

BP36

BP54

D10

E14

E24

E34

E44

E54

J14

J9

AH47

AJ59

AK16

AK36

AK9

V24

CRITICAL

OMIT_TABLE

U0500

KBL-PCH-Y-QKKR

BGA

947915

K23

K33

K43

K53

L61

N20

R10

R24

R40

R49

T13

T33

T60

V27

V43

V50

Y15

Y33

Y9

AA24

AA40

AA49

AA59

AC16

AC33

AE2

AE44

AE51

AF21

AF54

AF64

AH27

AH43

AH50

AK11

AK27

AK5

AL21

AL36

AL47

AL59

AN19

AN36

AR10

AR27

AR40

AR49

AR8

AU57

AV20

AW19

AY24

AY34

AY44

BA53

BB20

BB30

BB40

BB50

BC29

BD63

BE35

BF59

BG29

AL30

AL44

AL51

AN16

AN27

BA7

BH20

BH32

BH42

BH52

BJ47

BL1

BL47

BM18

BN6

BP38

BP60

E16

E26

E36

R43

E46

E56

J3

K15

K25

K35

K45

K55

M3

N22

R30

R50

T18

T36

T62

V30

V44

V51

Y16

Y36

Y7

AA27

AA43

AA50

AA61

AC18

AC36

AE21

AE46

AE8

AF23

AF56

AG59

AH30

AH44

AH51

AK13

AK3

AK54

AL24

AL40

AL49

AM54

AN21

AN40

AR12

AR30

AR43

AP54

AR18

AR36

AR46

AR59

BA3

CRITICAL

OMIT_TABLE

U0500

KBL-PCH-Y-QKKR

BGA

947915

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SYM 19 OF 20

GND 2 OF 3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AR50

AT27

AU59

AV24

AY26

AW21

AY36

AY46

BA1

BB22

BA58

BB32

BB42

BB52

BE12

BC47

BE47

BG12

BG4

BH34

BH22

BH44

BH54

BJ62

BL29

BM20

BL8

BP22

BP44

E18

E28

D6