Page 1

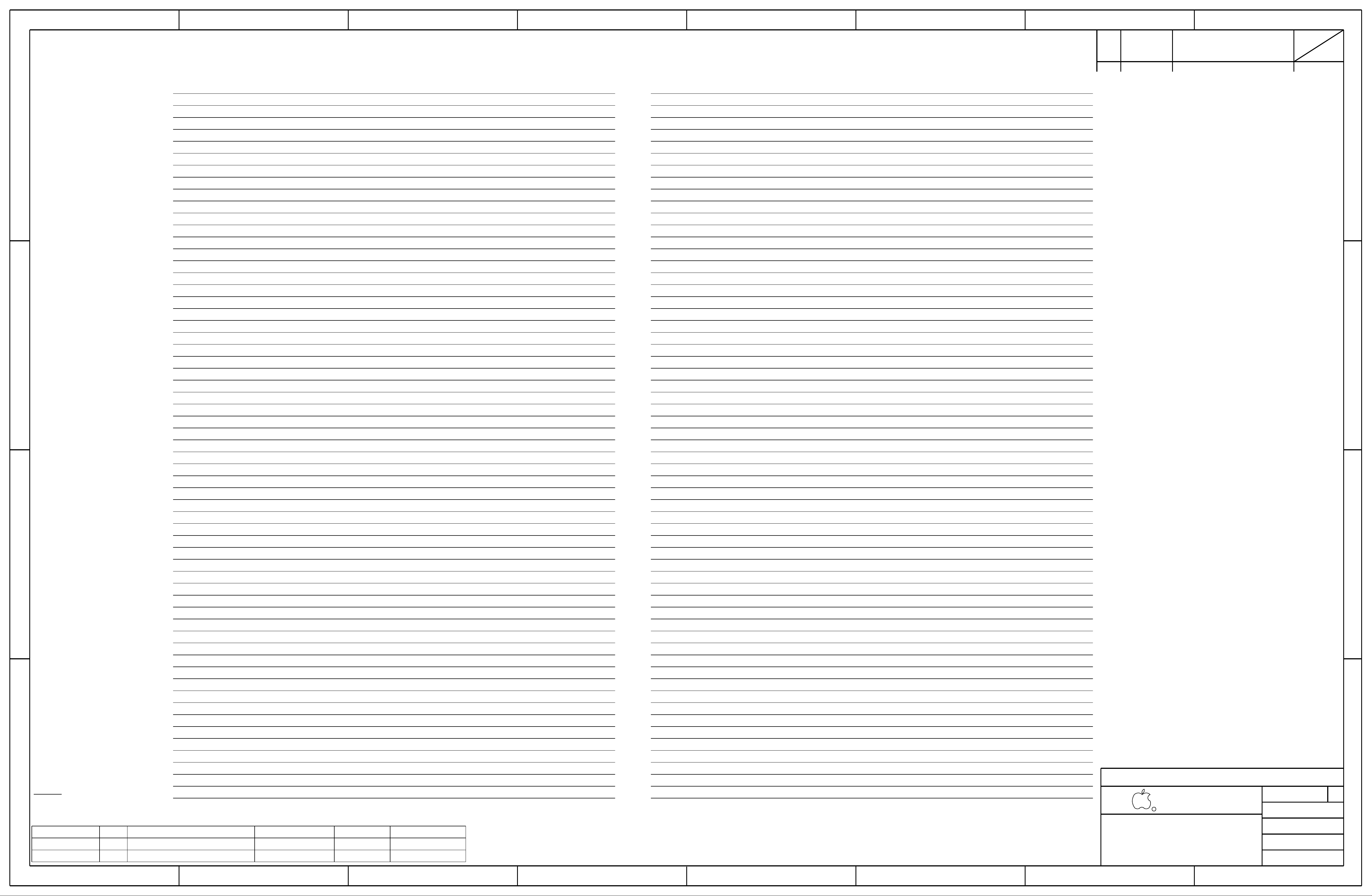

8

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

7

6 5 4 3

SCHEM,MLB_BAFFIN,X363G

2 1

CK

ECNREV DESCRIPTION OF REVISION

DATESYNCCONTENTSCSAPAGEDATESYNCCONTENTSCSAPAGE

APPD

DATE

2016-08-24000689728910 ENGINEERING RELEASED

D

1

2

3

4

5

1

2

3

4

5

6 6

7

8

9

7

8

9

10

11

12

13

14

11

12

13

14

MLB_BAFFIN

BOM Configuration

BOM Configuration

PD Parts

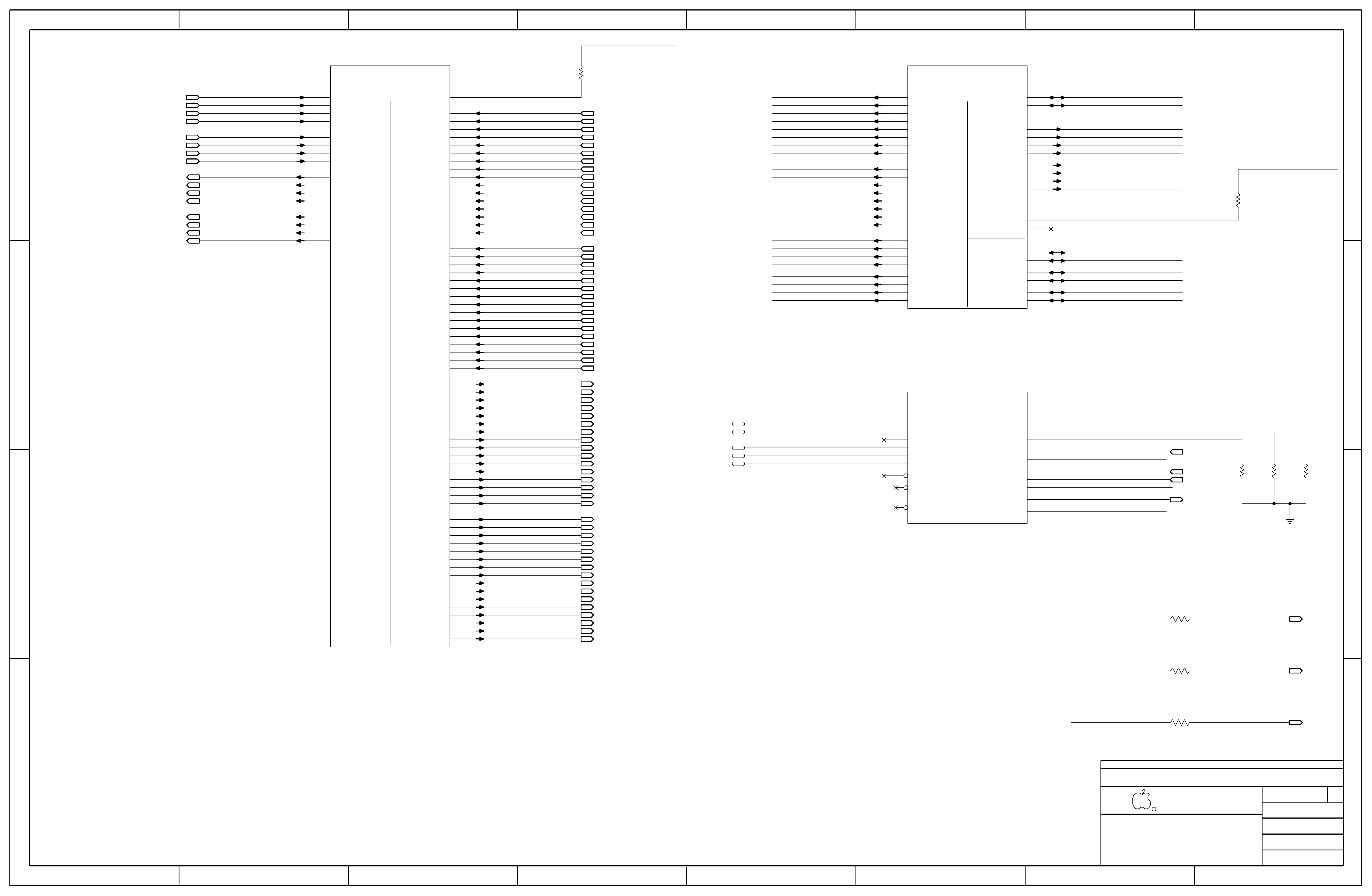

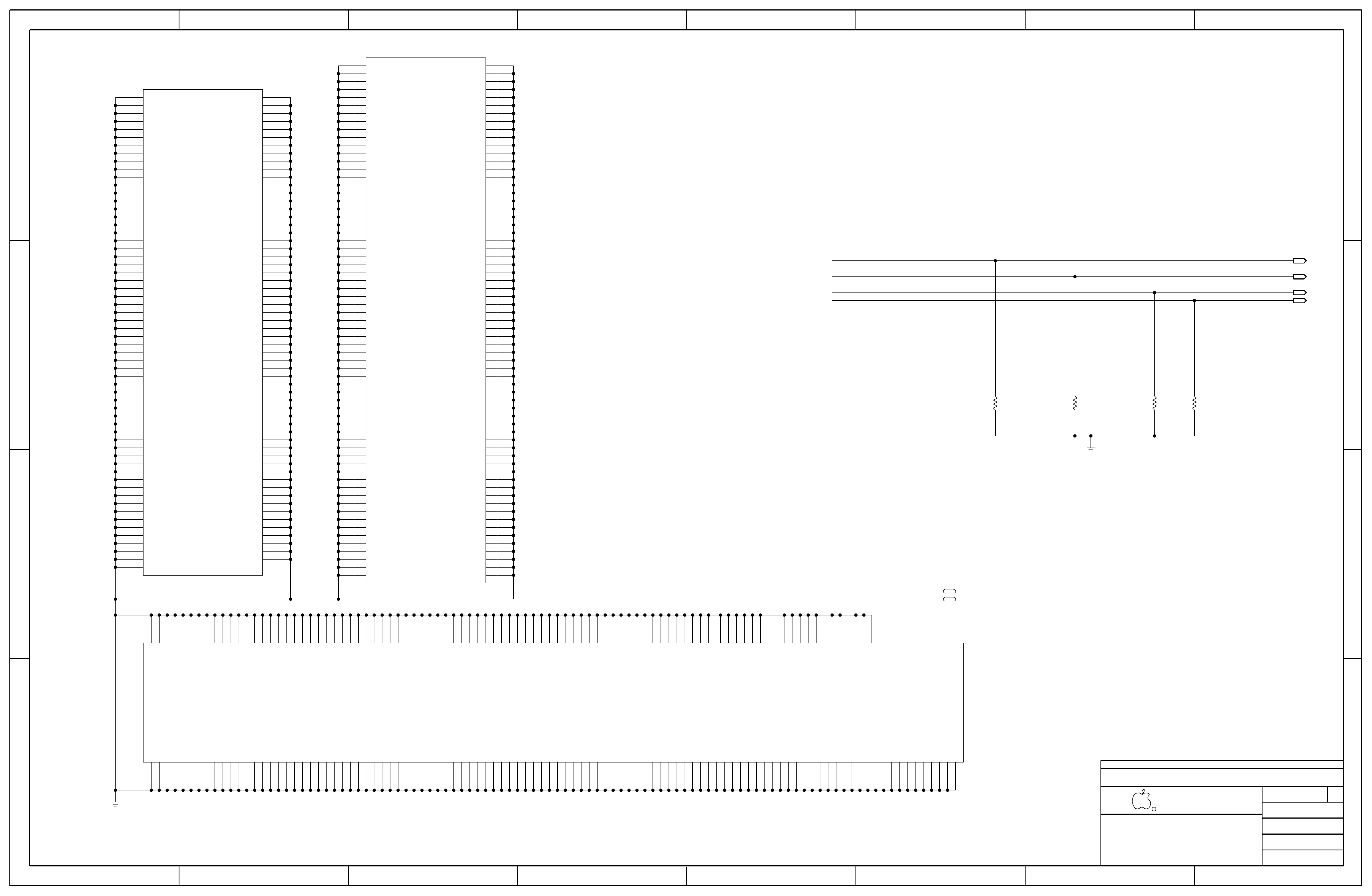

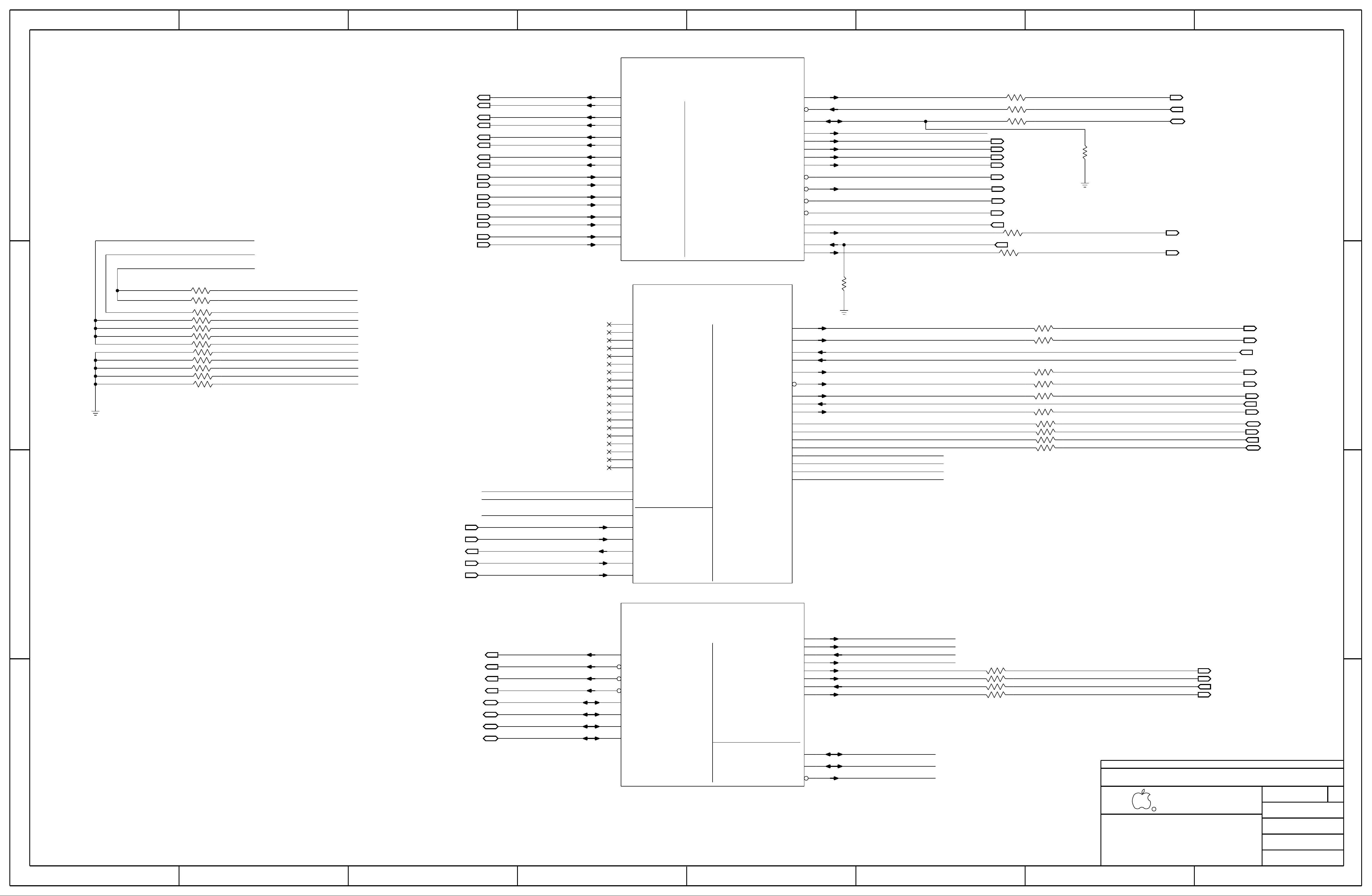

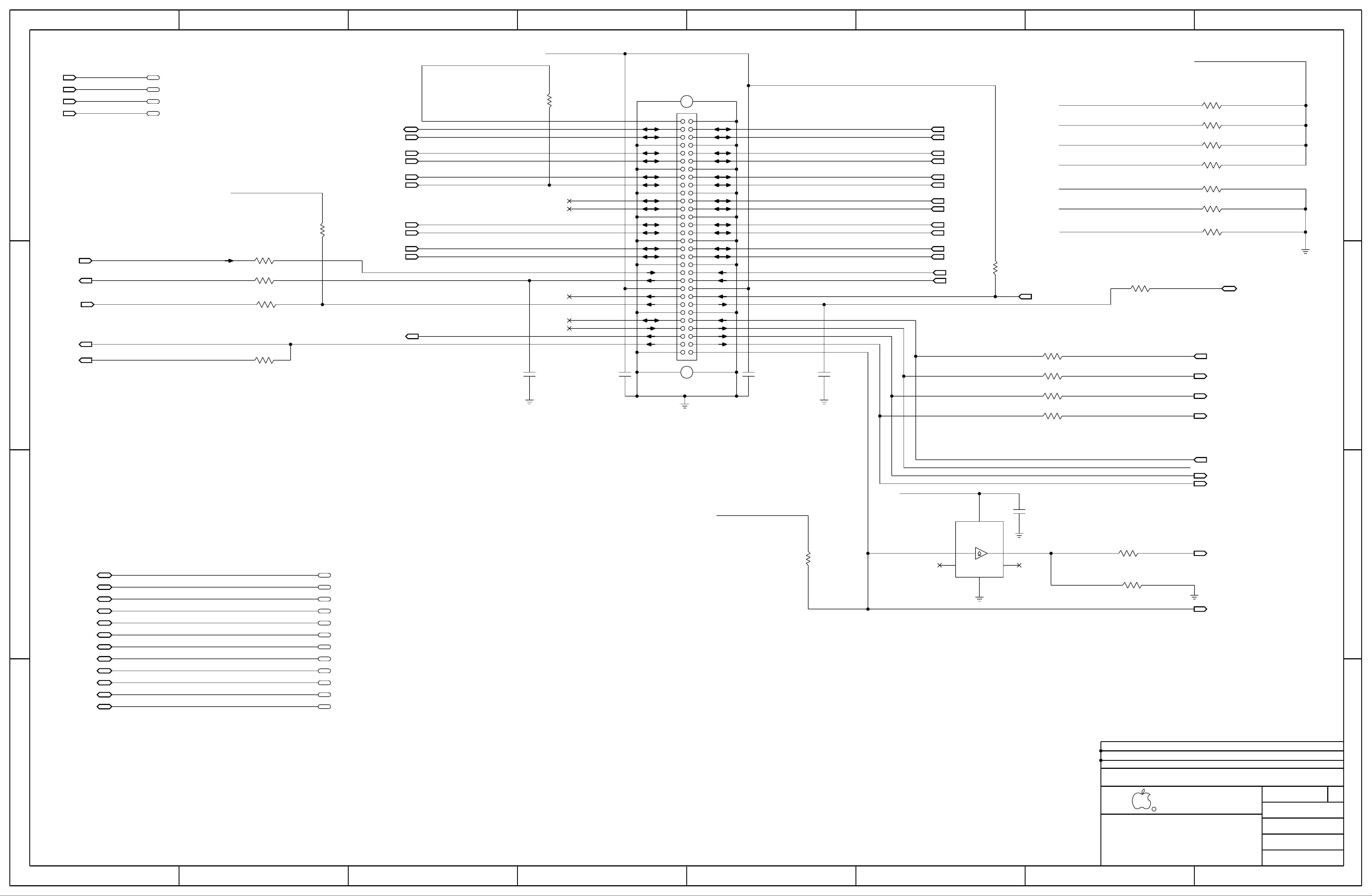

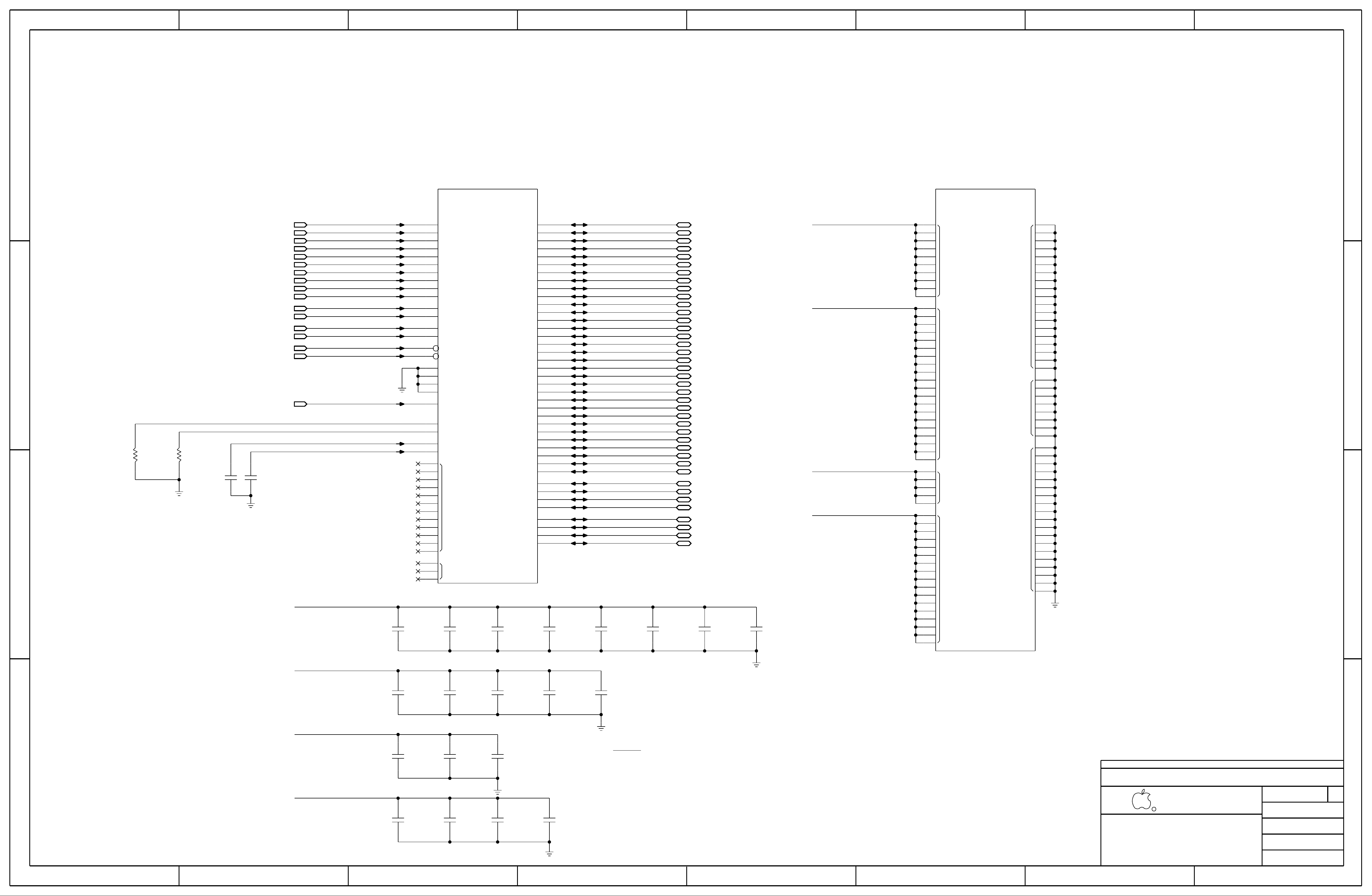

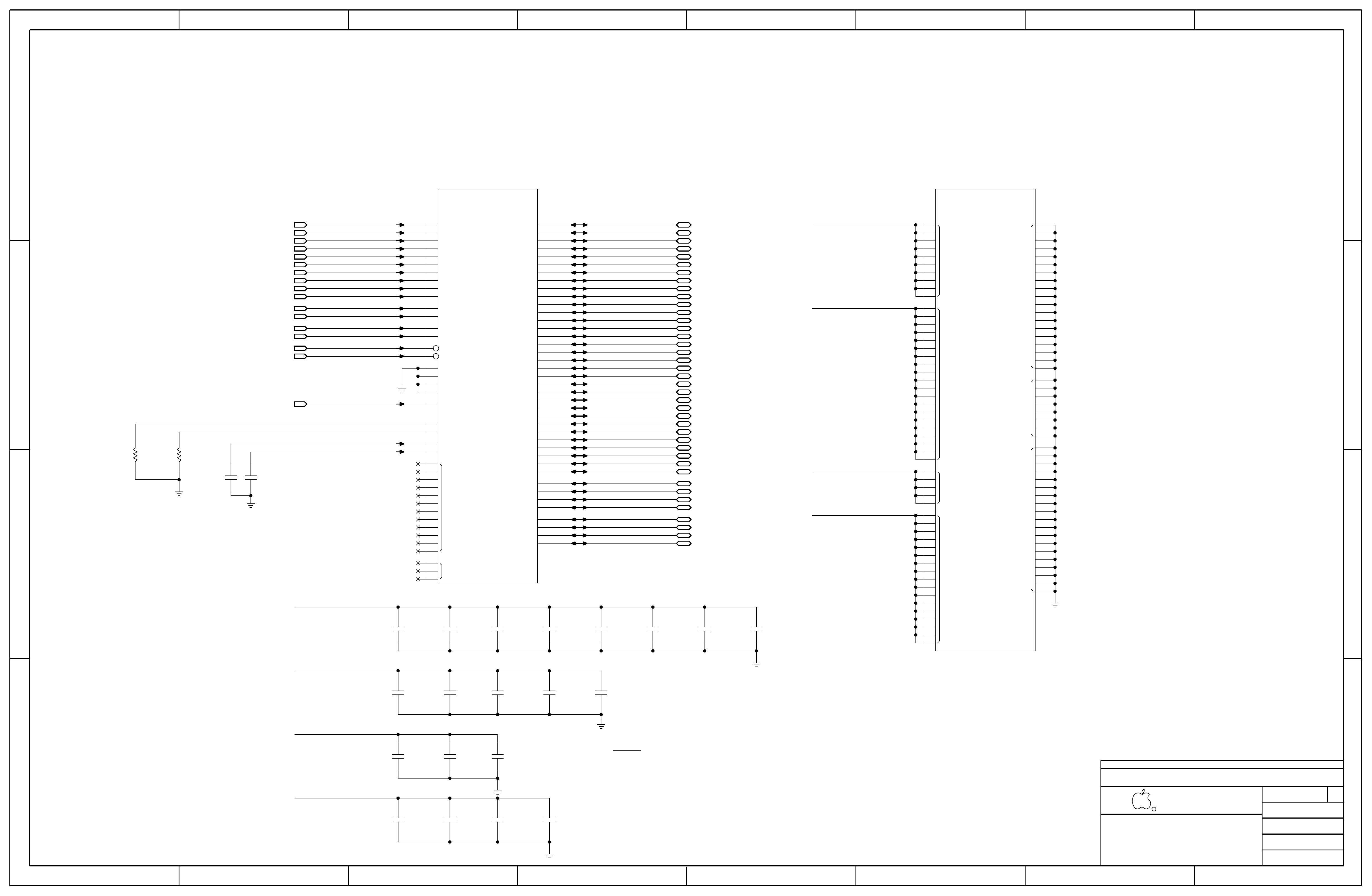

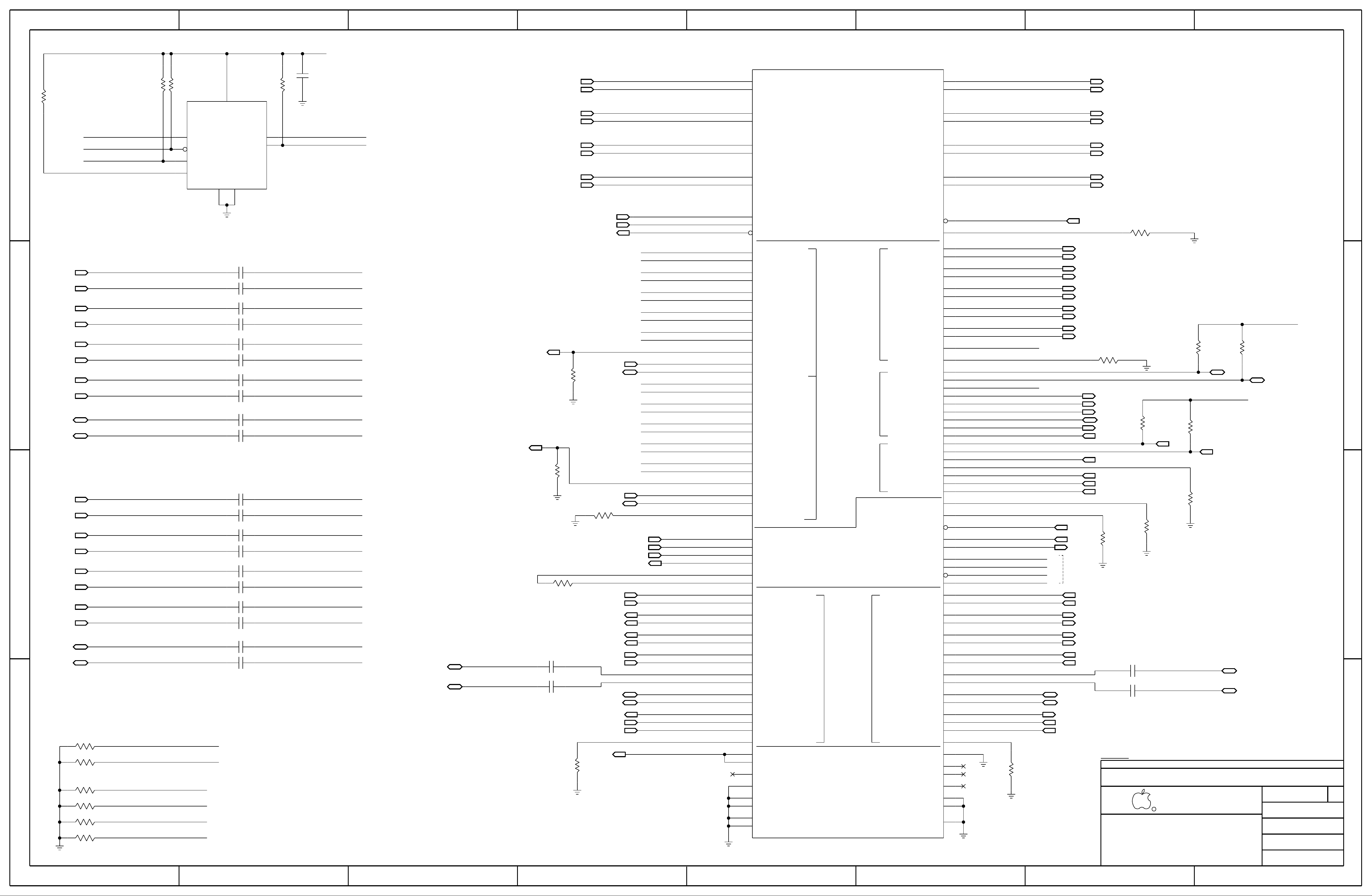

CPU DMI/PEG/FDI/RSVD

CPU Clock/Misc/JTAG/CFG

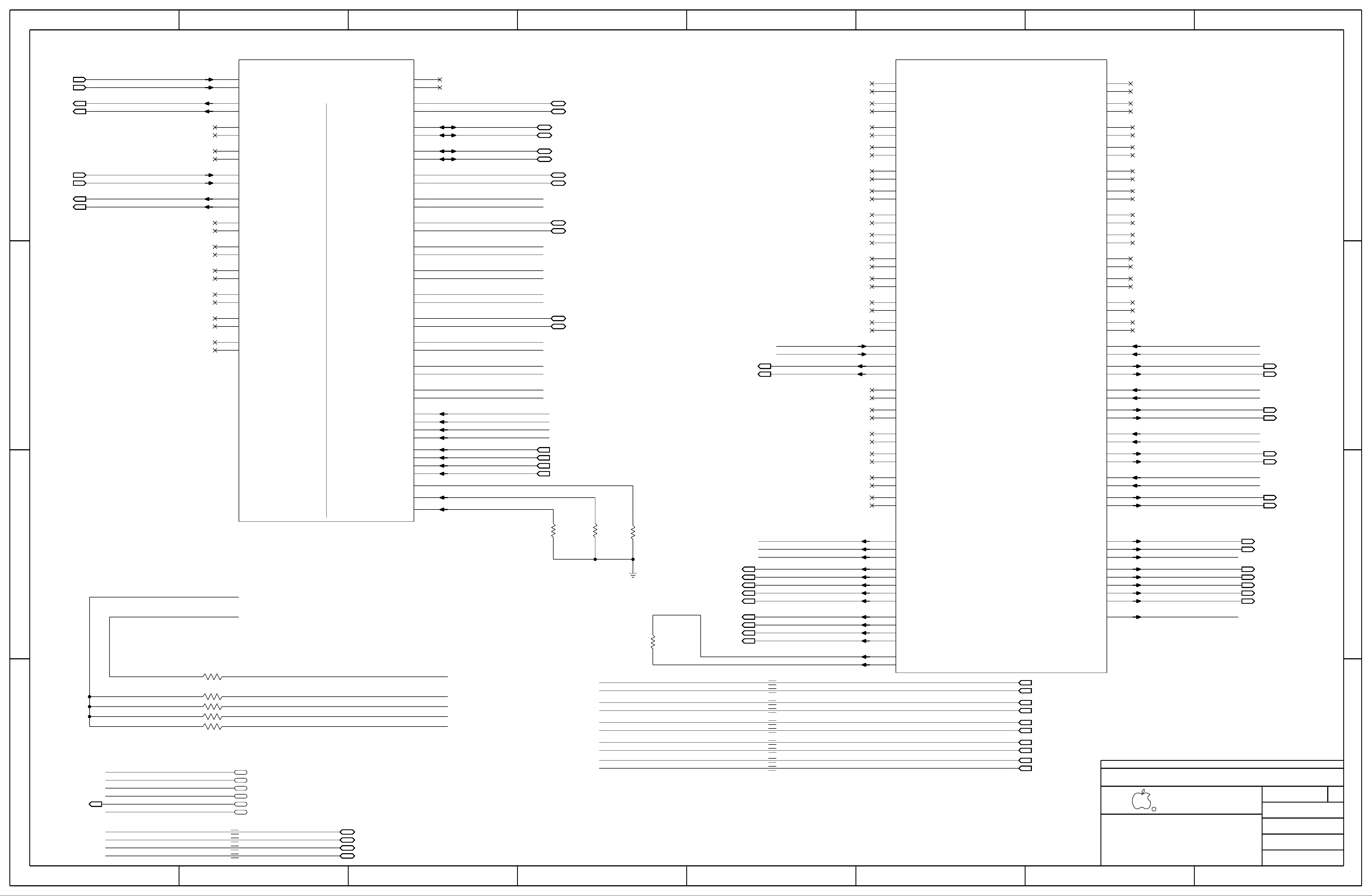

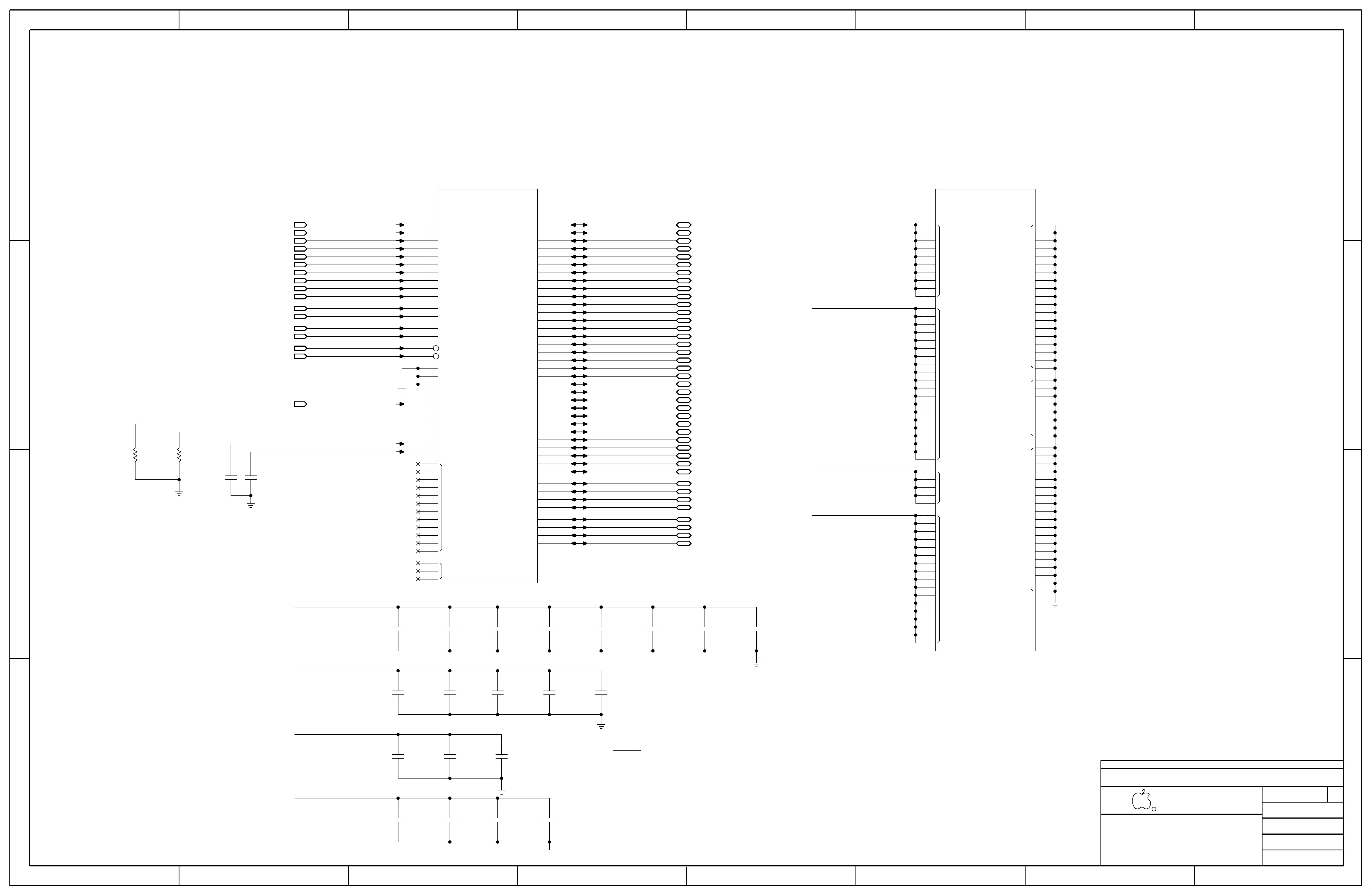

CPU DDR3 Interfaces

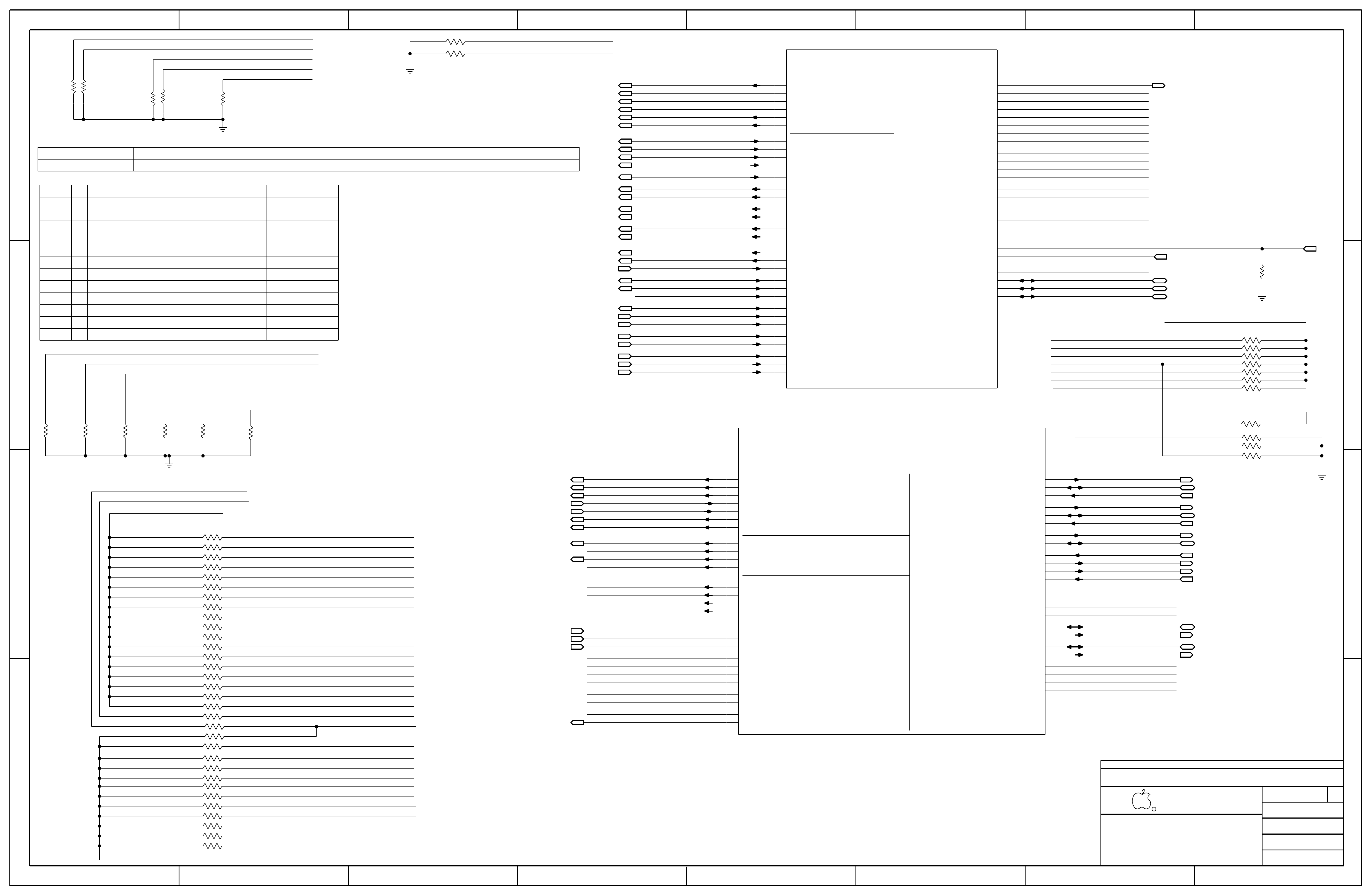

CPU Power

CPU Ground

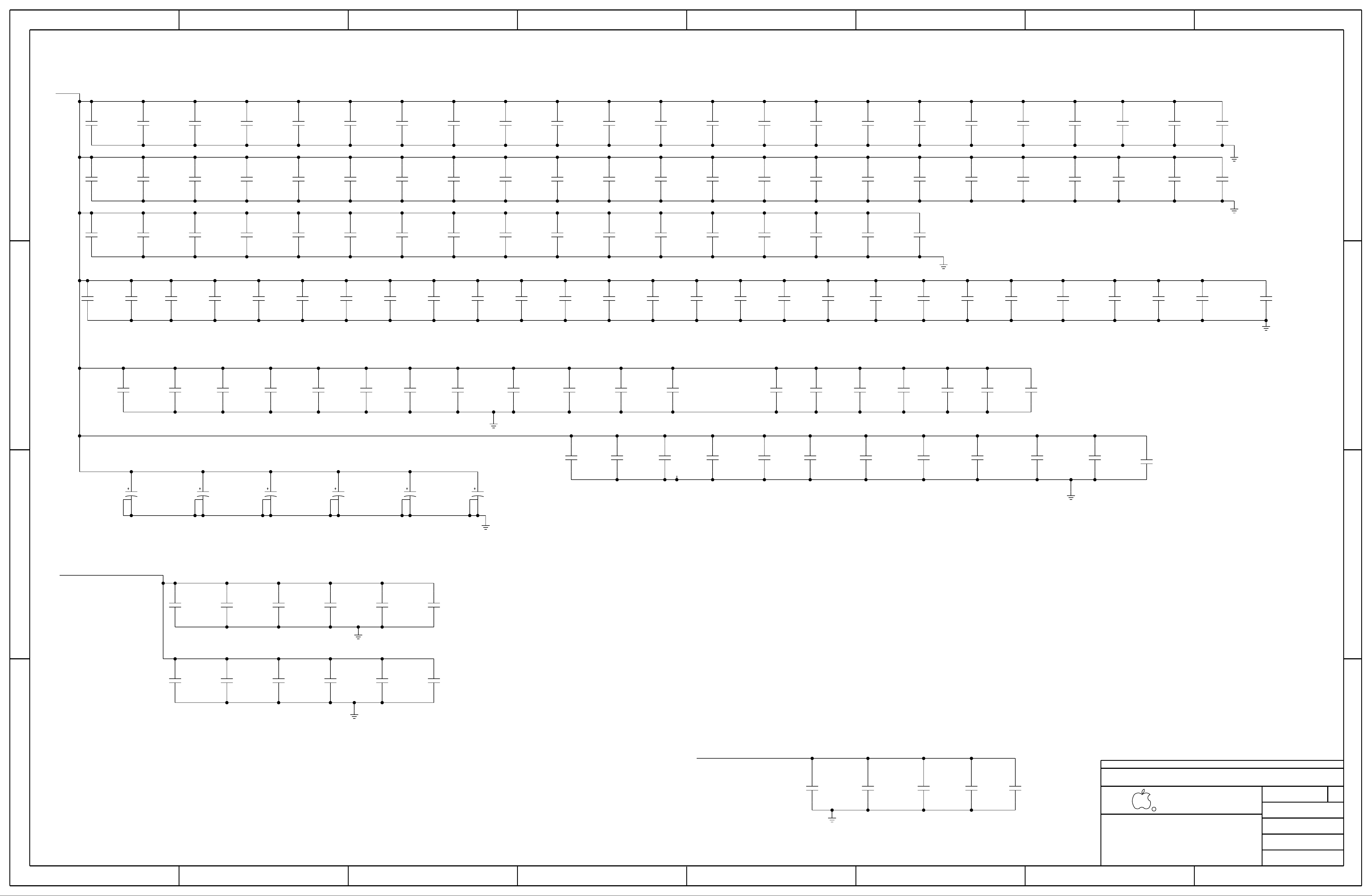

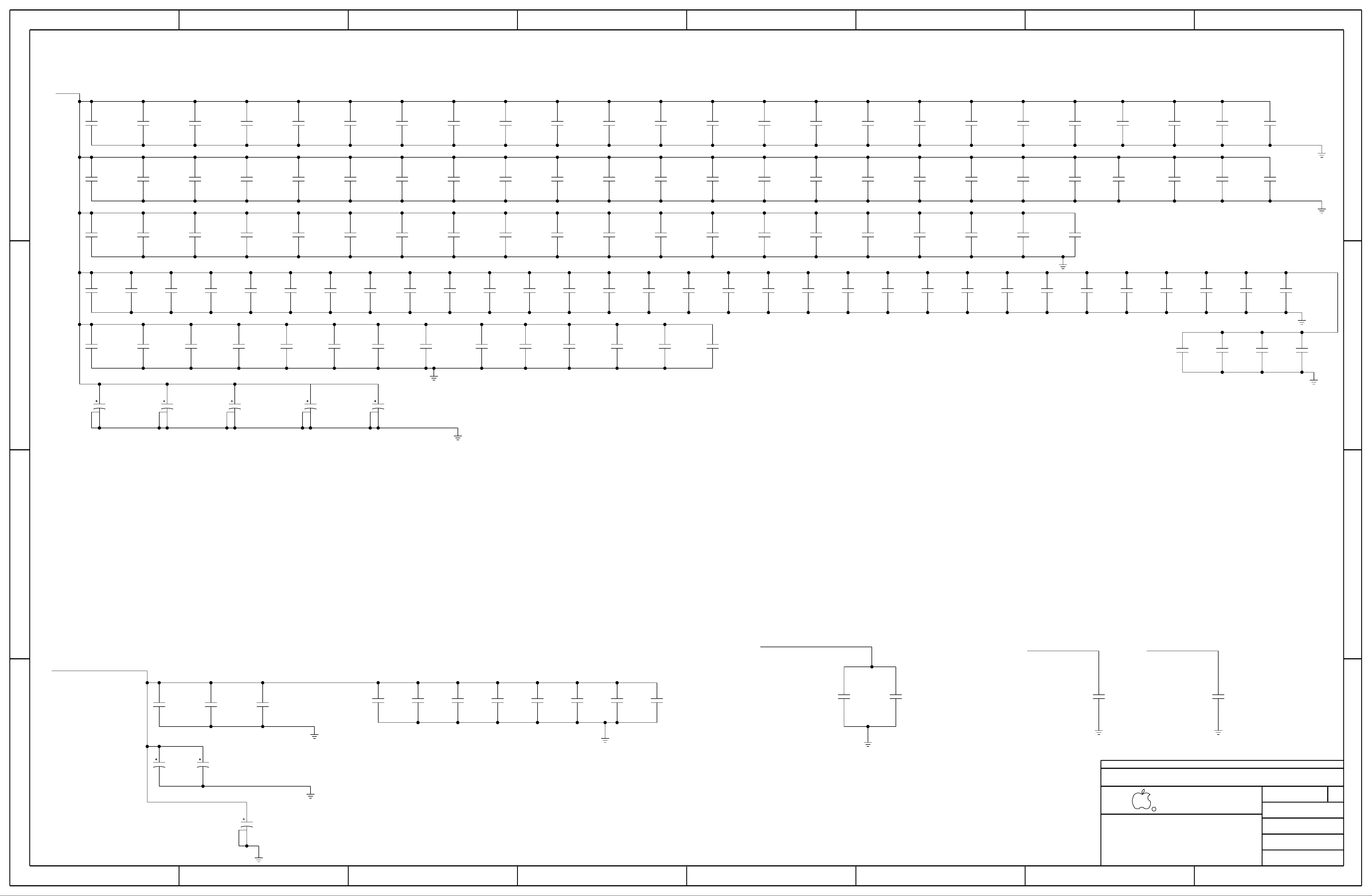

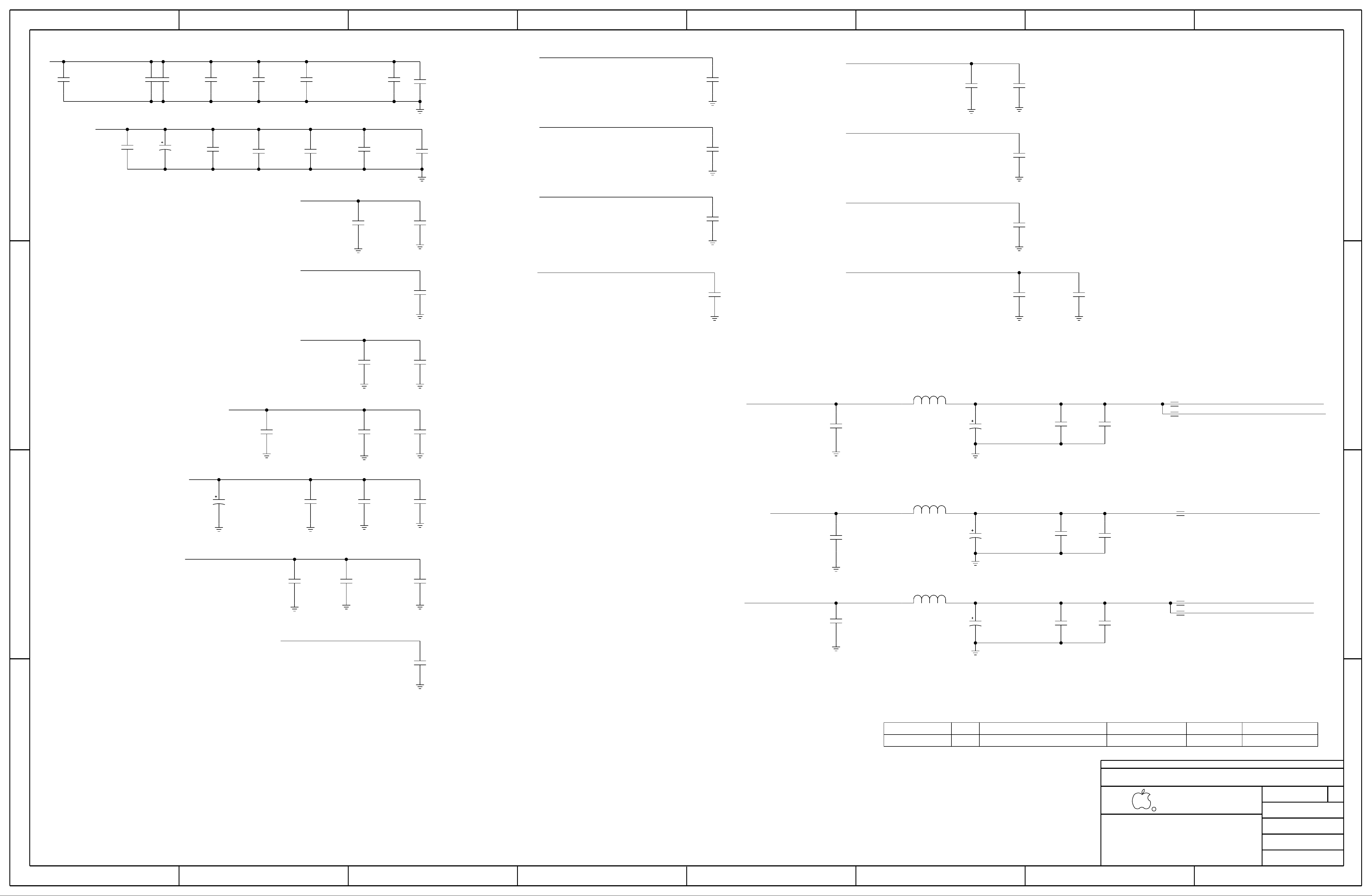

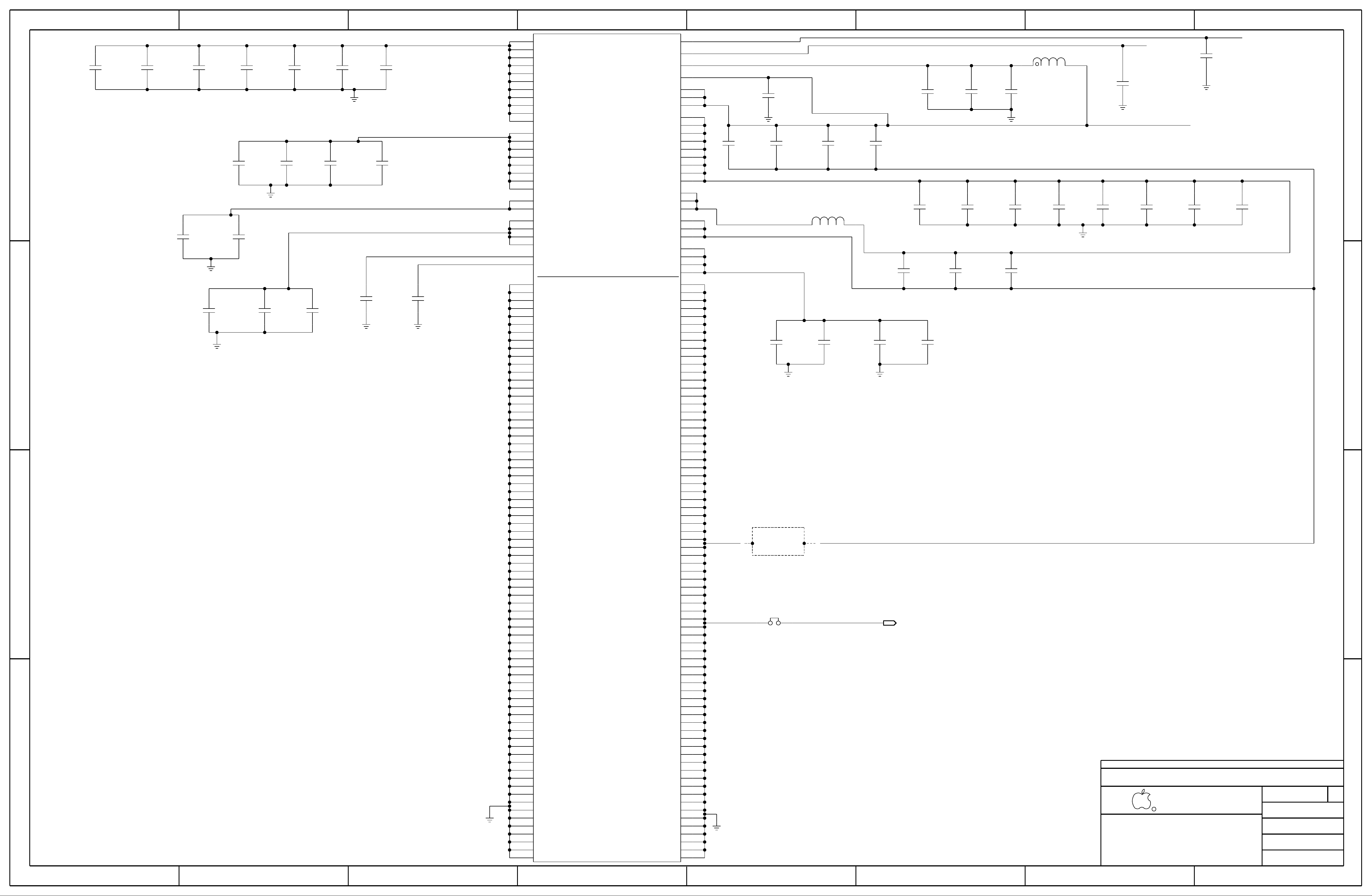

CPU Decoupling 1 [10]

CPU Decoupling 2 [11]

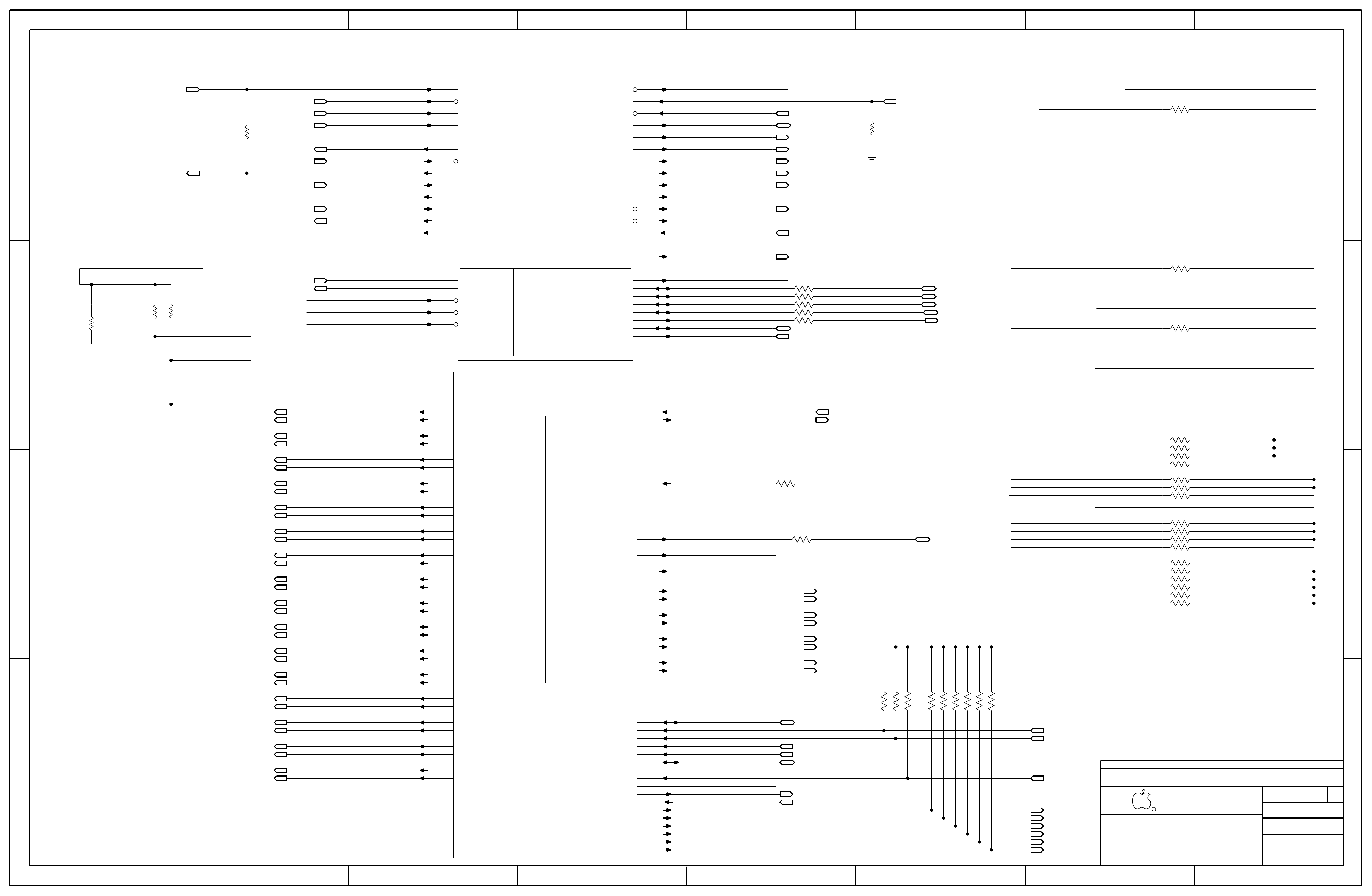

PCH RTC/HDA/JTAG/SATA/CLK

PCH DMI/FDI/PM/GFX/PCI

PCH PCI-E/USB

J80_MLB

J80_MLB_BAFFIN_CLEAN

J80_MLB

X363_AGOTETI

J80_MLB

J80_MLB

J80_MLB

J80_MLB

J80_DTUZMAN_MLB_BAFFIN

X363_SEAN

X363_SAKKOC

J80_MLB

X363_SAKKOC

07/07/2015

12/02/2015

11/16/2015

01/21/2016

11/06/2015

11/06/2015

08/16/2015

08/17/2015

11/22/2015

02/01/2016

04/14/2016

11/06/2015

04/14/2016

61

65

66

63

64

65

69

70

71

66 72

7367

68

69

7010

71

72

73

74

76

78

79

80

81

74 82

AUDIO Speaker Amps & Conn

AUDIO JACK CONNECTOR62

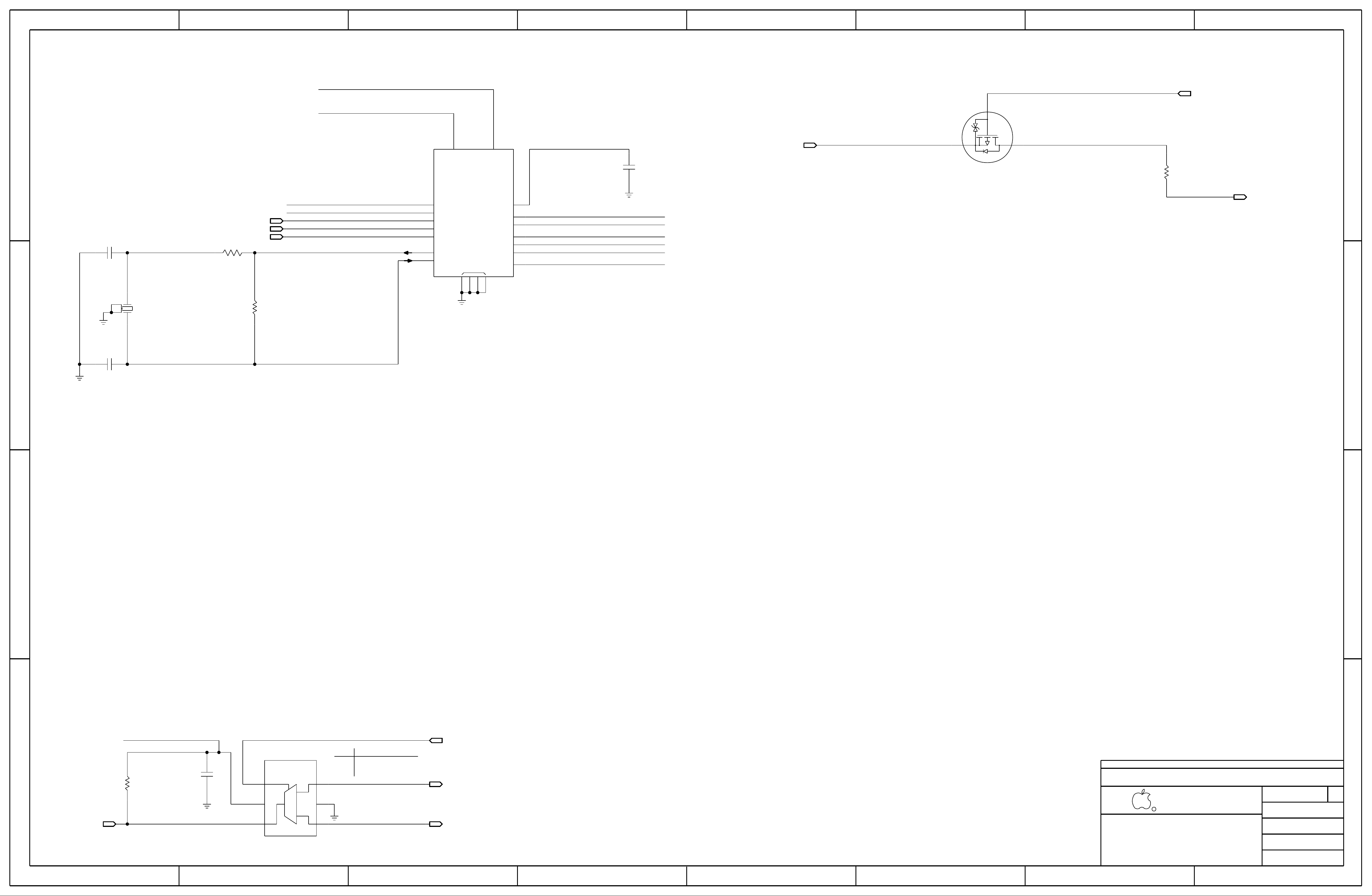

DC-In & Battery Connectors

PBUS Supply & Battery Charger

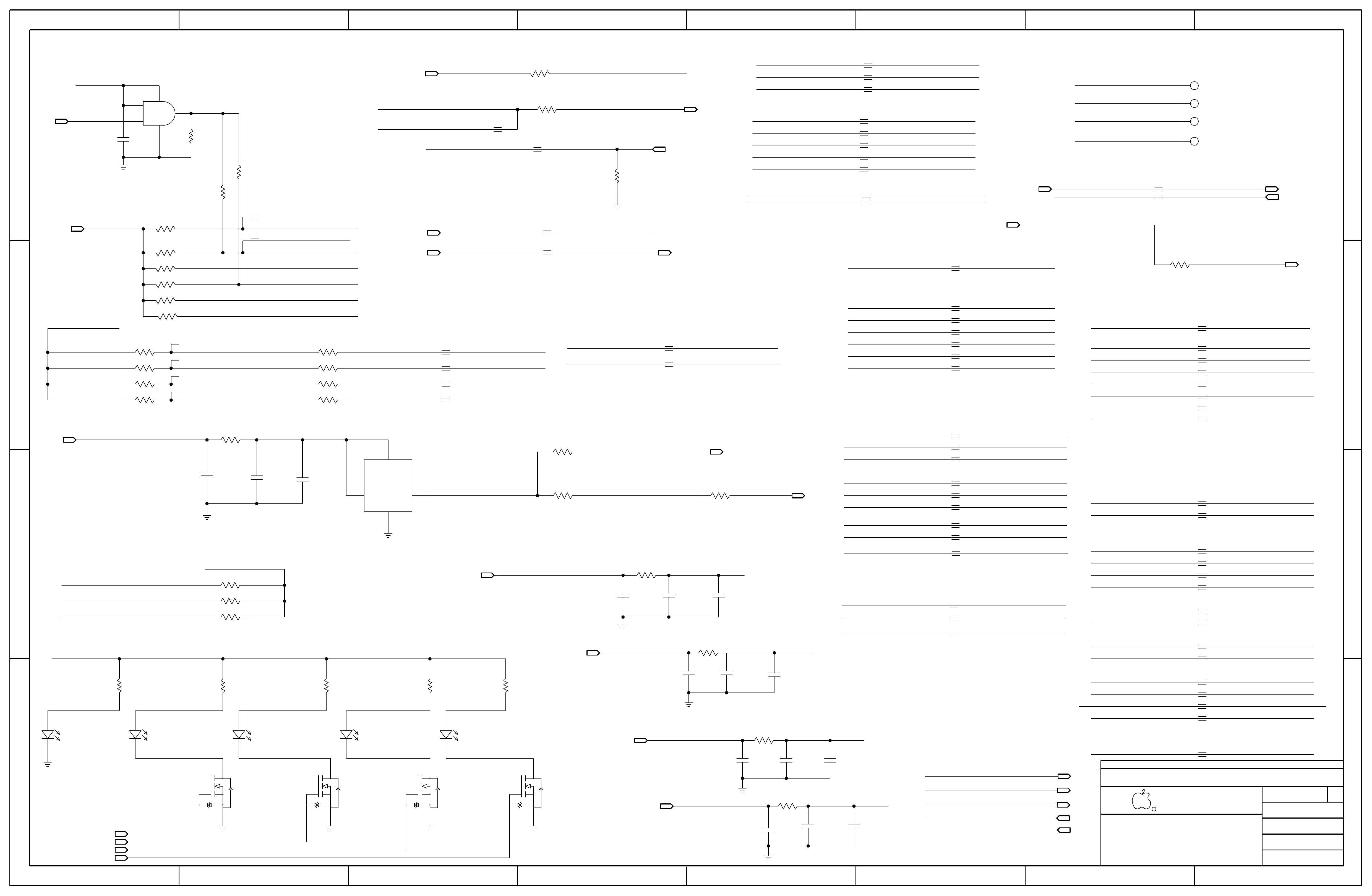

CORE & SA IMVP IC

CORE IMVP POWER BLOCK

SA IMVP IC

GT & GTX IMVP POWER BLOCK

Power - 5V 3.3V Supply

PMIC-1 & Power Control

PMIC-1 1.2V 0.6V VCCIO

PMIC-1 1V 1.8V VCCPCH

PMIC-1 Aliases & TPs

Power FETs

X363_AUDIO

J80_MLB

J80_MLB

J80_MLB

J80_DTUZMAN_MLB_BAFFIN

J80_DTUZMAN_MLB_BAFFIN

J80_DTUZMAN_MLB_BAFFIN

J80_DTUZMAN_MLB_BAFFIN

J80_DTUZMAN_MLB_BAFFIN

J80_MLB

J80_MLB

X363_ZIFENGSHEN

J80_SILUCHEN_MLB_BAFFIN

J80_SAKKOC_MLB_BAFFIN

01/25/2016

11/06/2015

11/06/2015

11/06/2015

12/10/2015

09/03/2015

11/18/2015

09/03/2015

12/09/2015

12/08/2015

11/06/2015

04/14/2016

12/08/2015

12/11/2015

D

C

15

16

17

18

19

20

21

22

23

24

25

26

27

15

PCH GPIO/MISC/NCTF

16 PCH Power

17

18

19

20

22

23

24

25

26

27

28

PCH DECOUPLING

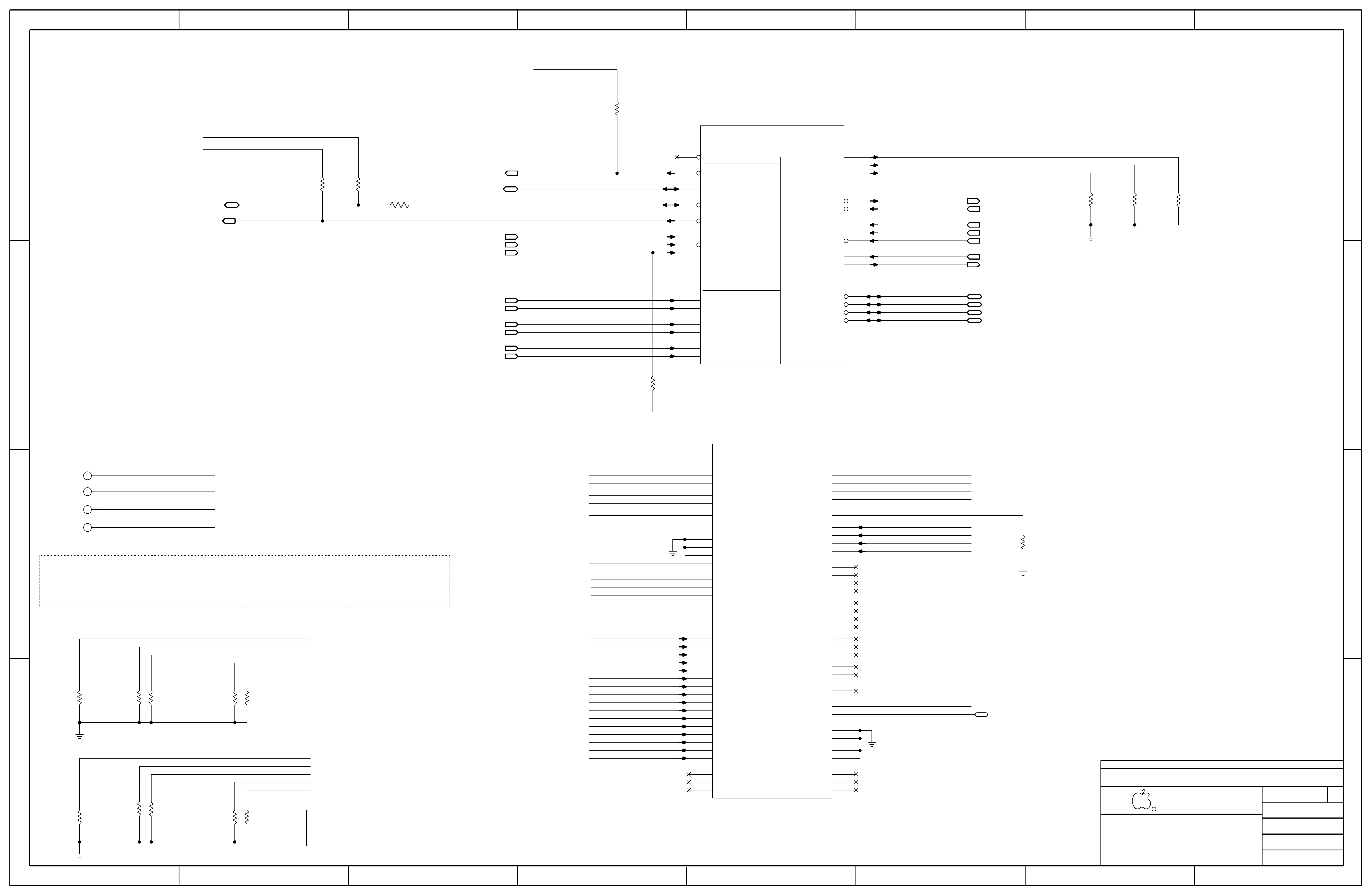

CPU/PCH Merged XDP

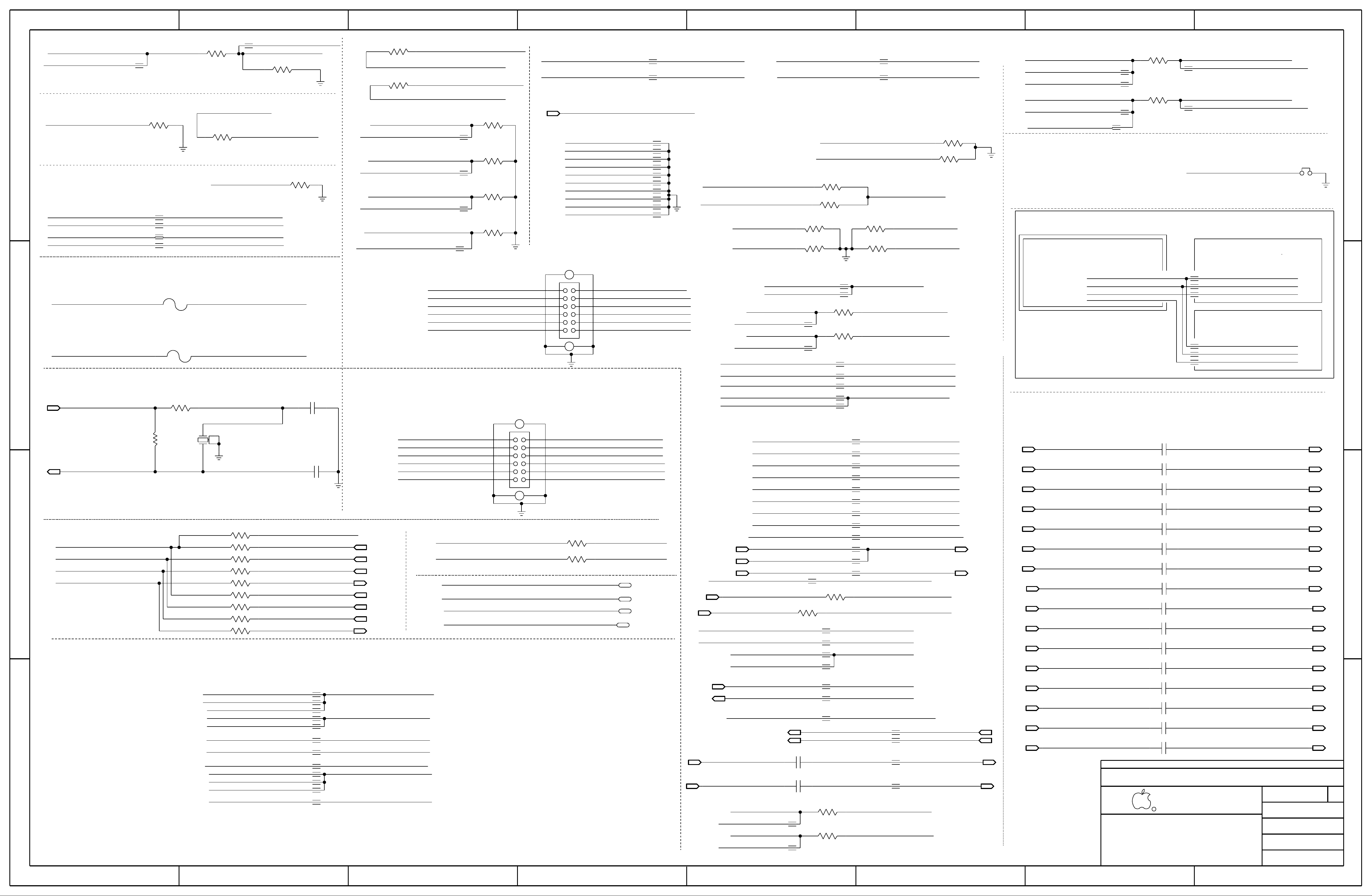

Chipset Support 1

Chipset Support 2

LPDDR3 VREF MARGINING

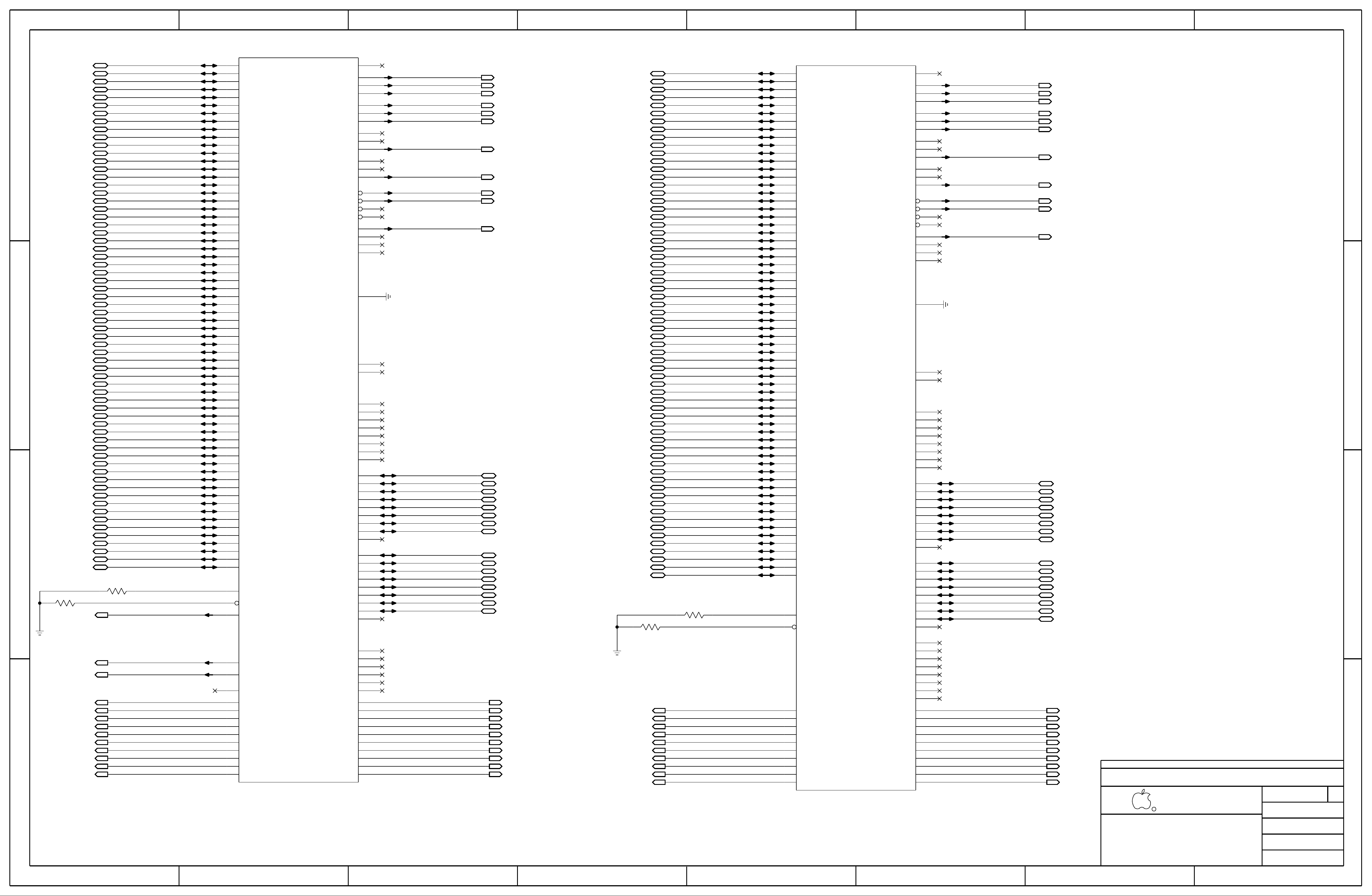

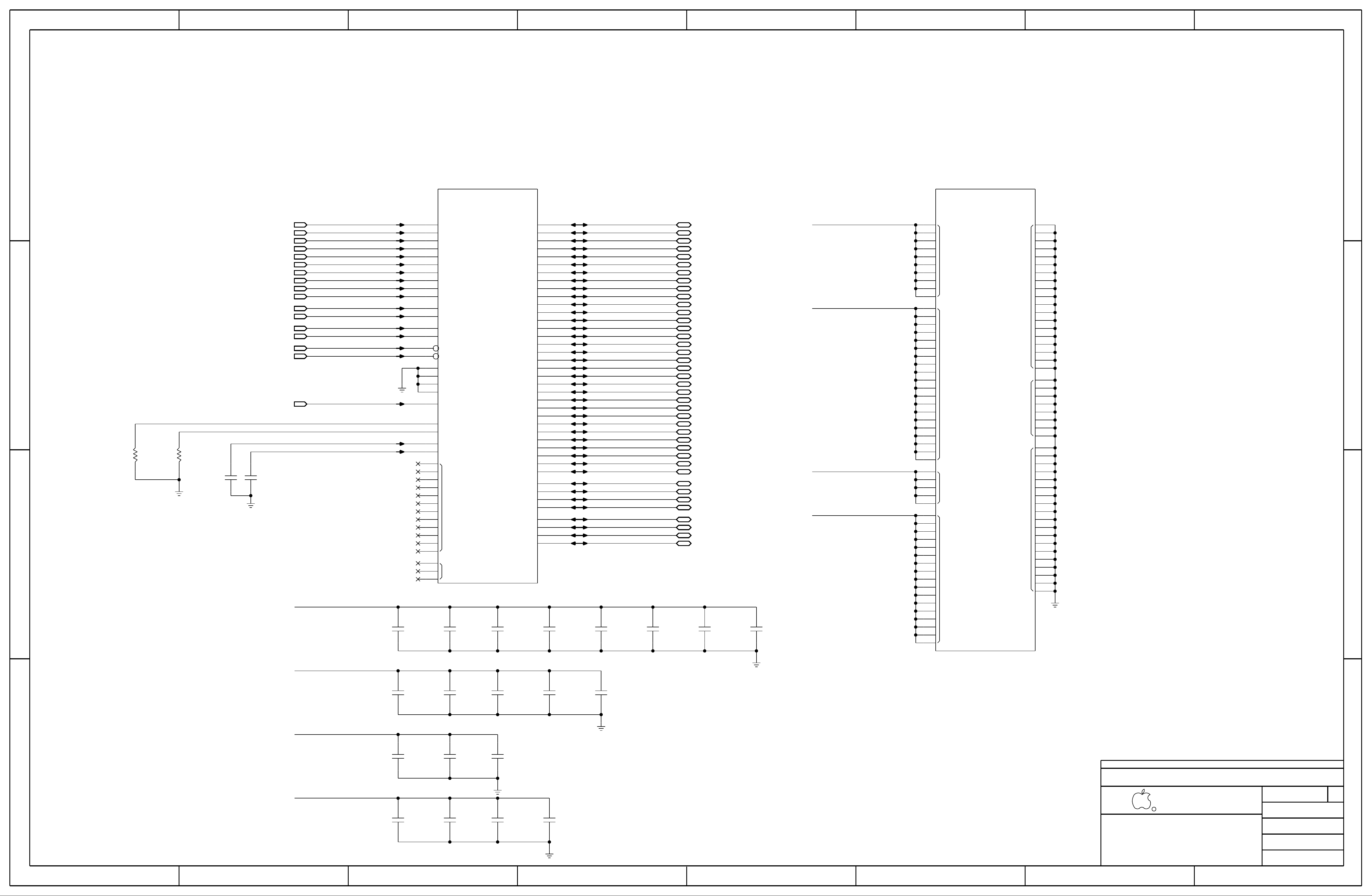

LPDDR3 DRAM Channel A (0-31)

LPDDR3 DRAM Channel A (32-63)

LPDDR3 DRAM Channel B (0-31)

LPDDR3 DRAM Channel B (32-63)

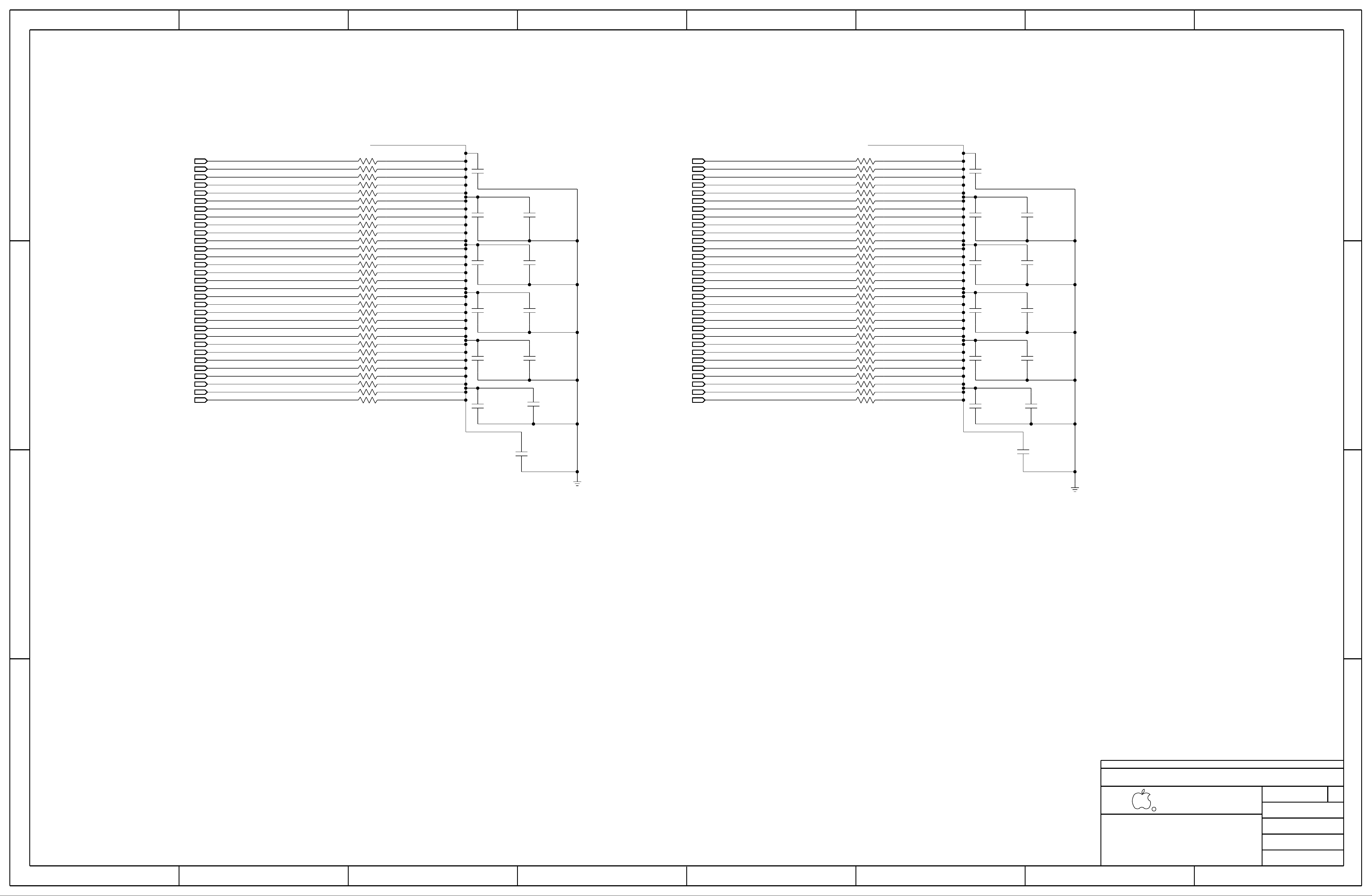

LPDDR3 DRAM Termination

USB-C HIGH SPEED 1

USB-C HIGH SPEED 22928

X363_SAKKOC

X363_SAKKOC

J80_MLB

X363_SAKKOC

X363_SAKKOC

X363_SAKKOC

J80_MLB

J80_MLB

J80_MLB

J80_MLB

J80_MLB

J80_MLB

J80_MLB

J80_MLB

04/29/2016

01/25/2016

11/06/2015

01/25/2016

04/29/2016

01/14/2016

11/06/2015

11/06/2015

11/06/2015

11/06/2015

11/06/2015

11/06/2015

11/06/2015

75

76

77

78

79

84

85

86

87

88

80 89

81

82

83

84

85

86

90

91

92

93

94

95

968711/06/2015

88

97

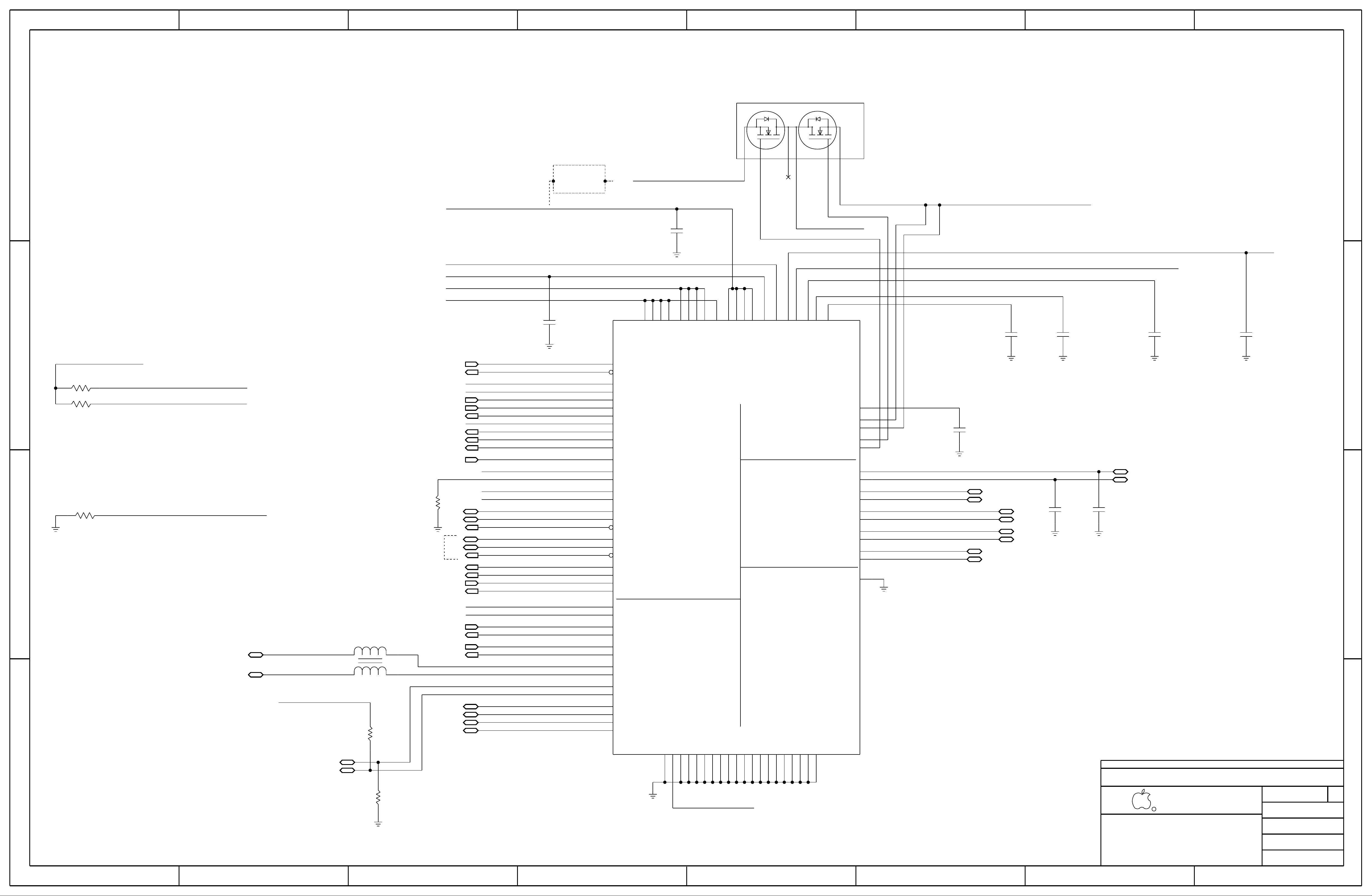

LCD Backlight Driver

eDP Display Connector

POLARIS_CONTROLLER

POLARIS POWER

POLARIS GND

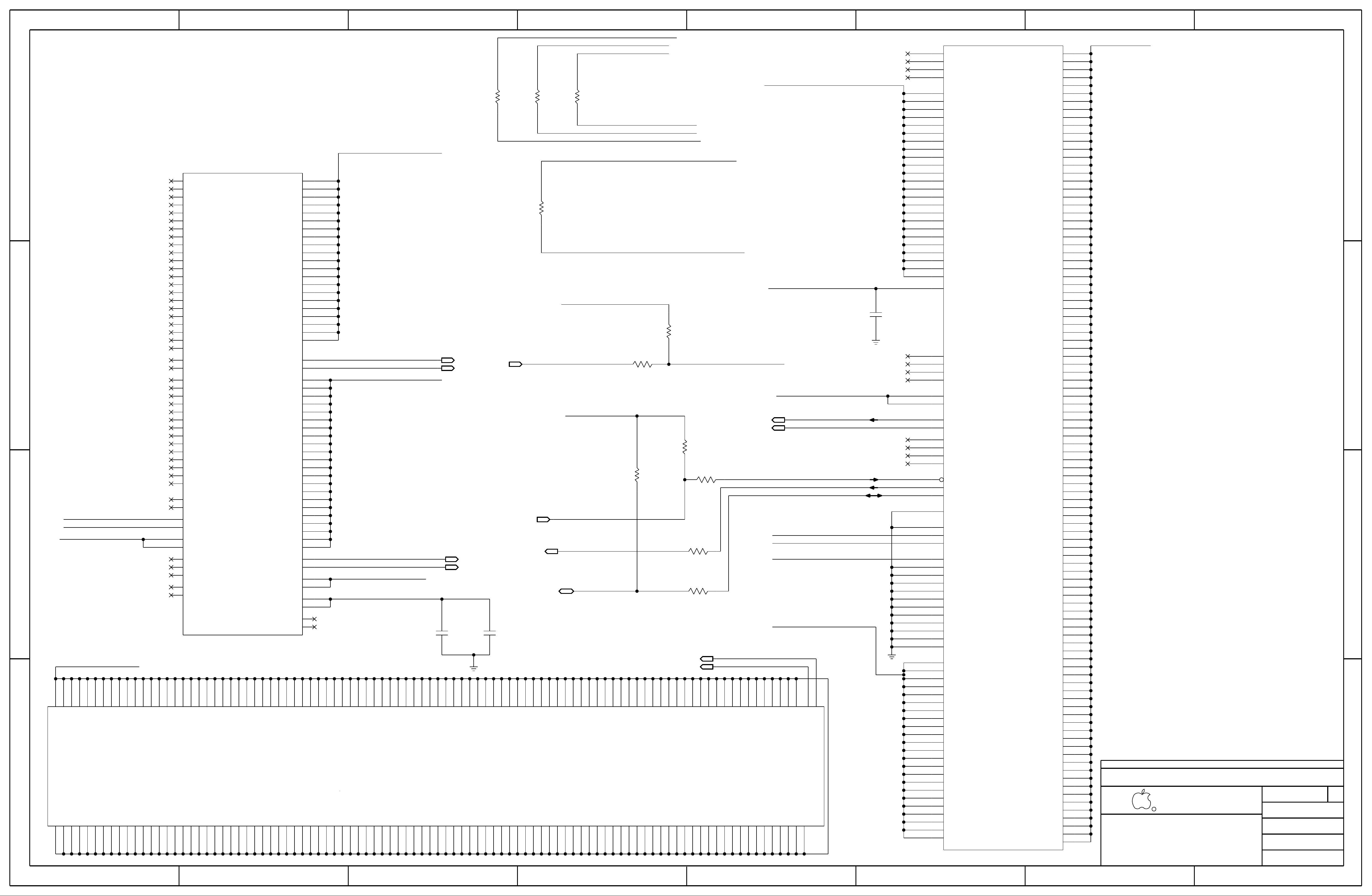

Connector

TEMP SENSORS

NAND 1/2

NAND 2/2

POLARIS PMIC

SSD NAND VR

SSD SUPPORT

Lifeboat

Constraints

J80_DTUZMAN_MLB_BAFFIN

J80_ZIFENGSHEN_MLB_BAFFIN

X363_JSAMUELS

X363_JSAMUELS

X363_JSAMUELS

X363_JSAMUELS

J80_MLB

X363_JSAMUELS

X363_JSAMUELS

X363_JSAMUELS

X363_JSAMUELS

X363_ZIFENGSHEN

X363_BBABADI

Constraints

12/03/2015

12/03/2015

04/01/2016

05/18/2016

04/01/2016

04/01/2016

11/06/2015

08/09/2016

08/09/2016

08/09/2016

04/01/2016

04/15/2016

01/20/2016

05/18/2016

C

B

29

30

31

32

33

34

35

36

37

38

39

40

41

42

30

31

32

33

34

35

37

38

39

40

41

42

43

44

USB-C Support

USB-C PORT CONTROLLER A

USB-C PORT CONTROLLER B

USB-C CONNECTOR A

USB-C CONNECTOR B

TBT 5V REGULATOR

WIFI/BT: MODULE 1

WIFI/BT: MODULE 2

Camera/DFR 1

Camera/DFR 2

Camera/DFR 3

Berkelium - 1

Berkelium - 2

T208 Support

X363_AGOTETI

X362_GKOO

J80_MLB

X362_MLB

X362_MLB

J80_ZIFENGSHEN_MLB_BAFFIN

X363_SAKKOC

J80_MLB

X363_SAKKOC

X362_T208

X362_T208

X362_T208

X362_T208

X362_T208

08/08/2016

08/08/2016

11/06/2015

03/30/2016

03/29/2016

12/04/2015

04/29/2016

11/06/2015

04/29/2016

03/22/2016

04/25/2016

01/27/2016

03/15/2016

06/30/2016

89

90

91

92

93

94

98

99

100

101

102

103

95 104

96

97

98

99

100

101

102

105

106

107

108

109

110

111

eDP Mux

GPU PCC

BAFFIN PCI-E

Baffin CORE/FB POWER

Baffin FRAME BUFFER I/F

Baffin 1V05 GPU / 1V35 FB Power Supply

GDDR5 Frame Buffer A

GDDR5 Frame Buffer B

GFX IMVP VCore Regulator [106]

Baffin GPIOs,CLK & Straps

Baffin DP/GPIO

Baffin VSS & MISC

USB-C HIGH SPEED 1

USB-C HIGH SPEED 2

dpmux

X363_SEAN

X363_SEAN

X363_SEAN

J80_SEAN

J80_DTUZMAN_MLB_BAFFIN

J80_SEAN

J80_SEAN

J80_DTUZMAN_MLB_BAFFIN

X363_SEAN

X363_SEAN

X363_SEAN

J80_MLB

J80_MLB

08/22/2015

01/27/2016

01/27/2016

02/01/2016

04/29/2015

12/08/2015

04/29/2015

04/29/2015

12/08/2015

01/28/2016

01/27/2016

01/27/2016

11/06/2015

11/06/2015

B

43

44

45

46

47

48

49

50

51

52

53

54

55

56

45

47

49

50

51

52

53

54

55

56

57

58

59

60

Connectors&ESD

External A USB3 Connector

MESA

SMC

SMC Shared Support

SMC Project Support

SMBus Connections

Power Sensors: High Side

Power Sensors: Load Side

Power Sensors: Extended

Power Sensors: Extended 2

Thermal Sensors

Sensor Extended 3

Fans

X363_SAMANTHA

J80_MLB

X362_P49

X363_ZIFENGSHEN

J80_ZIFENGSHEN_MLB_BAFFIN

X363_ZIFENGSHEN

X363_ZIFENGSHEN

X363_ZIFENGSHEN

X363_ZIFENGSHEN

X363_ZIFENGSHEN

X363_ZIFENGSHEN

X363_ZIFENGSHEN

X363_ZIFENGSHEN

X363_ZIFENGSHEN

01/08/2016

08/26/2015

01/08/2016

04/14/2016

11/19/2015

04/14/2016

04/14/2016

04/14/2016

04/14/2016

04/14/2016

04/14/2016

04/14/2016

05/19/2016

04/14/2016

103

104

105

106

112

113

114

115

107 116

108

109

110

111

112

113

114

115

116

117

120

121

122

123

124

125

126

127

USB-C Support

USB-C PORT CONTROLLER A

USB-C PORT CONTROLLER B

USB-C CONNECTOR A

USB-C CONNECTOR B

TBT 5V REGULATOR

Power Aliases - 1

Power Aliases - 2

Signal Aliases

Memory Bit/Byte Swizzle

ICT & FCT 1

ICT & FCT 2

NC & No Test

Desense Caps

J80_AGOTETI_MLB_BAFFIN

J80_MLB

J80_MLB

X362_MLB

X362_MLB

J80_ZIFENGSHEN_MLB_BAFFIN

J80_MLB

X363_SAKKOC

X363_SAKKOC

J80_MLB

X363_SAKKOC

J80_BBABADI_MLB_BAFFIN

X363_BBABADI

X363_ZIFENGSHEN

12/07/2015

11/06/2015

11/06/2015

03/30/2016

03/29/2016

12/04/2015

08/16/2015

01/14/2016

01/13/2016

11/06/2015

04/14/2016

12/10/2015

01/26/2016

04/15/2016

A

DRAWING

TITLE=MLB_BAFFIN

ABBREV=ABBREV

LAST_MODIFIED=Wed Aug 24 09:57:44 2016

Schematic / PCB #'s

051-00647 1

820-00281 1

57

58

59

60

SCHEM,MLB-BAFFIN,X363G

PCBF,MLB-BAFFIN,X363G

61

62

63

64

SPI Debug Connector

HDA Bridge

AUDIO JACK CODEC

AUDIO Speaker Amps & Conn

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

CRITICALSCH

CRITICALPCB

J80_MLB

X363_AUDIO

X363_AUDIO

X363_AUDIO

11/06/2015

01/11/2016

01/25/2016

01/25/2016

This is the PVT design

117

118

119

120

128

130

141

142

Desense Caps

Project Specific Constraints

639 BOM Configuration

639 BOM Configuration 2

LAST_MODIFICATION=Wed Aug 24 09:57:44 2016

3

DESENSE

X363_ZIFENGSHEN

J80_MLB

J80_MLB

05/18/2016

06/02/2016

07/23/2015

07/23/2015

DRAWING TITLE

SCHEM,MLB-BAFFIN,X363

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

051-00647

REVISION

10.0.0

BRANCH

dvt-fab10

PAGE

1 OF 145

SHEET

1 OF 121

1245678

A

SIZEDRAWING NUMBER

D

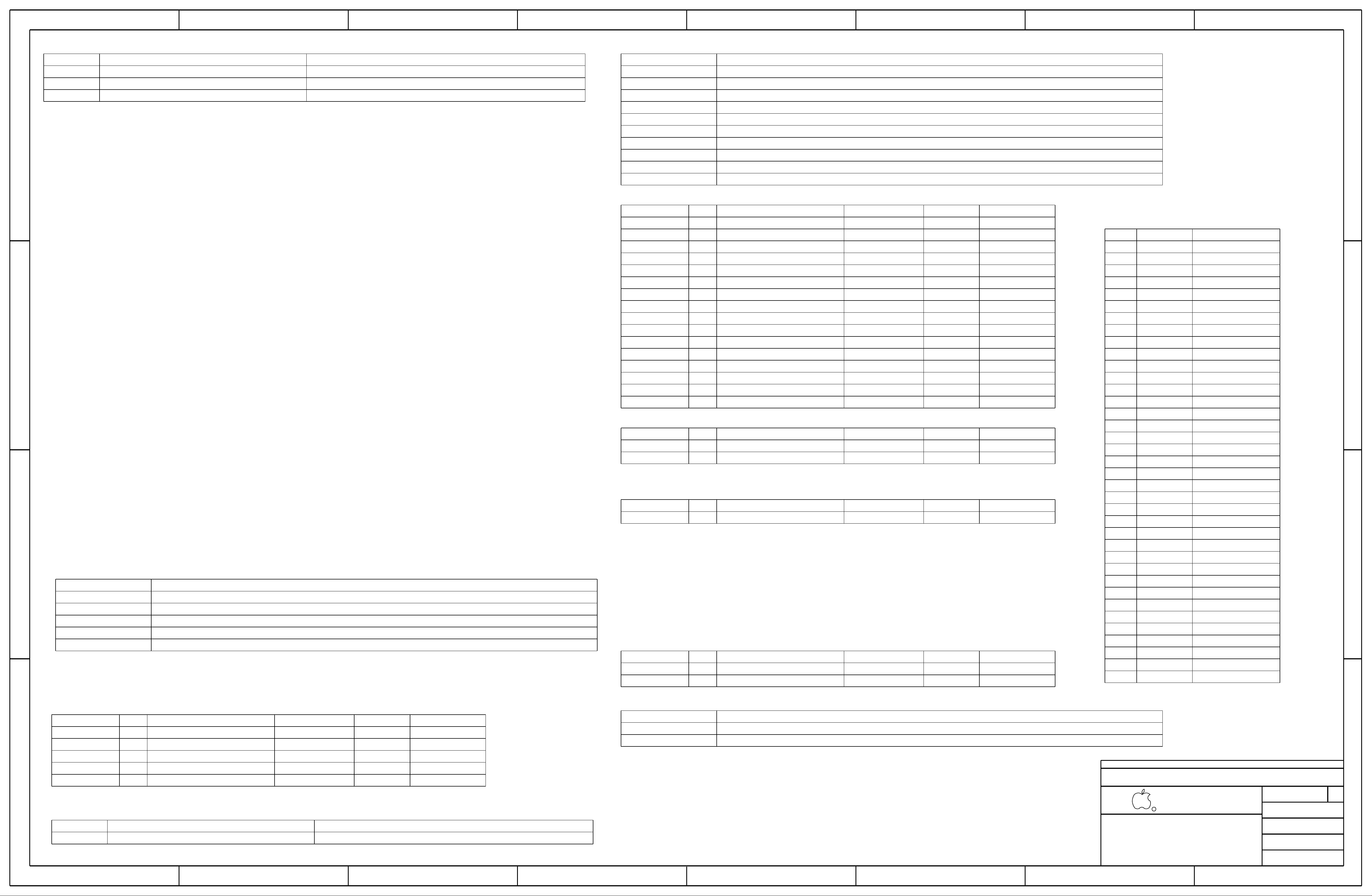

Page 2

345678

2 1

D

BOM Variants

BOM NUMBER BOM NAME BOM OPTIONS

685-00076 COMMON PARTS,MLB-BAFFIN,X363 X363_COMMON

985-00126

DEV,MLB-BAFFIN,X363

X363_DEVEL:PVT

985-00232 X363_DEVEL:PVTDEV,MLB-BAFFIN,PVT,X363

639 BOMs have been moved to the end of the schematic

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

X363 BOM Groups

BOM GROUP BOM OPTIONS

X363_COMMON

X363_COMMON1

X363_COMMON2

X363_COMMON3

X363_COMMON4

X363_PROGPARTS

X363_DEVEL:ENG

X363_DEVEL:DVT

X363_DEVEL:PVT

ENGISNS

ALTERNATE,COMMON,X363_COMMON1,X363_COMMON2,X363_COMMON3,X363_COMMON4,X363_PROGPARTS

SOC:HYNIX,SE:PROD,SKIP_5V3V3:AUDIBLE,DIPLEXER:MURATA,T208_PROG:REV5,BOARD_ID:17,VCCHDA:S0

XDP:YES,SAMCONN,SOC_BOOT:SPI,DPMUX_XTAL:NO,GPUCLK:OSC,BAFFIN,AP_TEMP,VCCPLLOC:S3,WIFI_SAK:NO

CPUTHRM:ALRT,TBTTHRM:ALRT,LOADRC:NO,OTHERRC:YES,DDRRC:YES,TBTRC:YES,TPADRC:YES,LID_FEATURE_ON

EDP:YES,CPUPEG:X8X4X4,TBTTHRM_SNS,GPUTHRM_SNS,S3_STATE:YES,GPU_ROM:YES,SVID_PU:CORE

BOOTROM_PROG:DVT,BT_PROG:DVT,WIFI_PROG:DVT,UPCROM_PROG:DVT,SMC_PROG:PVT,DPMUXMCU:PROG,PCC:NO

ALTERNATE,ENGISNS,DBGLED,XDP_CONN,USBC_DBG,DBG_BTN,DBG_FAN,DBG_XTAL,DPMUX_DEBUG,WIFI_DBG,SSD_DEBUG,GPUROM:BLANK,PCC:YES

ALTERNATE,ENGISNS,DBGLED,XDP_CONN,USBC_DBG,DBG_BTN,DBG_FAN,DBG_XTAL,DPMUX_DEBUG,WIFI_DBG,SSD_DEBUG

ALTERNATE,XDP_CONN,USBC_DBG

TBTISNS,LOADISNS,TPADISNS,DDRISNS,OTHERISNS

Module Parts

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

D

C

B

GPU Options

BOM GROUP BOM OPTIONS

2GB_MC_BAFFIN FB_2GB_MICRON,VRAM:GRP1

2GB_HY_BAFFIN FB_2GB_HYNIX,VRAM:GRP1

2GB_SM_BAFFIN FB_2GB_SAMSUNG,VRAM:GRP2

4GB_SM_BAFFIN FB_4GB_SAMSUNG,VRAM:GRP1

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

337S00227 U05001 CRITICAL

337S00228 U0500

337S00229

998-04701

1

1 U0500

1 CRITICAL

1 CRITICAL337S00258

4

338S00254 CRITICAL2

1 U7000 CRITICAL353S01016

338S00221

338S00142

337S00330

1

1

337S00332 CRITICALUA000

1

998-04866

1 UA000998-04867

2677-04532 CRITICALJ5250,J5260

CPU,SKY,SR2FT,R1,PRQ,4/2,2.9,BGA1440

CPU,SKY,SR2FU,R1,PRQ,4/2,2.7,BGA1440

CPU,SKY,SR2FQ,R1,PRQ,4/2,2.6,BGA1440

INTERPOSER,INTEL,BGA1440,MM940989

IC,SKL PCH-H,SFF,SR2NH,PRQ,D1,BGA939

IC,CD3215,ACE,C0,USB PWR SW,BLNK,BGA96

IC,TBT,ALPINE RIDGE DP,QT5S,QS,C1,BGA337

IC,ISL9239HIZ,PMU,TUBA,WCSP40,2.1X3.3MM

IC,PMU,P650839,7X7MM.BGA168

IC,CODEC,CLIFDEN,CS42L83A,B0,WLCSP49

IC,GPU,BAFFIN,ULA,A1,PS,BGA769

IC,GPU,BAFFIN,PROA,A1,PS,BGA769

IC,GPU,BAFFIN,LEA,A1,PS,BGA769

INTERPOSER,AMD,C988,BGA769,VDDC

SUBASSY (T&R) PCBA, AMR, INTERPOSER, X363

U0500

U1100

U3100,U3200,UB300,UB400

U2800,UB000

U63001

UA000

UA0001 CRITICALINTERPOSER,AMD,C989,BGA769,VDDCI/MVDD

CRITICAL

CRITICAL

CRITICAL353S00961

CRITICAL1 U7800

CRITICAL

CRITICALUA000

CRITICAL337S00331

CRITICAL

CPU_SKL:2.9

CPU_SKL:2.7

CPU_SKL:2.6

CPU_SKL:SOCKET

BAFFIN_ULA

BAFFIN_PROA

BAFFIN_LEA

STARDUST:VDDCI_MVDD

STARDUST:VDDC

Development/Base BOMs

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

1 BASE685-00076 COMMON PARTS,MLB-BAF,X363 BASE_BOMCRITICAL

985-00126

WIFI/BT Diplexers

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

FLTR,DIPLEXER,2.45/5.54GHZ,0805

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

FB_4GB_MICRON,VRAM:GRP14GB_MC_BAFFIN

Main DRAM Parts

333S00050

333S00070

4

4

IC,SDRAM,LPDDR3-2133,32GBIT,20NM,BGA178

IC,SDRAM,LPDDR3-2133,32GBIT,20NM,BGA178

U2300,U2400,U2500,U2600

U2300,U2400,U2500,U2600

CRITICAL3155S0979 U3810,U3820,U3830 DIPLEXER:MURATA

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

CRITICAL

CRITICAL

DEVEL_BOM1 CRITICALDEVELDEV,MLB-BAF,X363

16G_SAMSUNG_2133

16G_MICRON_2133

Strategic Silicon

PART# COMMENT

337S00229

333S00050

333S00070 07

335S00149

335S00204 02

335S00205 02

335S00219 02

339S00154 02

339S00155 02

338S00166

337S00225

337S00285

337S00286

333S00044

333S00043

333S00078

333S00074

333S00075

343S00135

343S00136

343S00137

338S00138

353S3978 02

338S00097

353S00961 09

338S00142

359S00006

STRATEGIC VALUE

08337S00227

08337S00228

08

07

02

02

08

08

08

07

07

07

07

07

10

10

10

10

09338S00193

02

08338S00254

09

07353S00604

08353S4316

08338S00221

09353S00853

05339S00056

08

09353S00795

CPU

CPU

CPU

MAIN MEMORY

MAIN MEMORY

SSD NAND

SSD NAND

SSD NAND

SSD NAND

SSD CONTROLLER

SSD CONTROLLER

SSD PMIC

GPU

GPU

GPU

VIDEO MEMORY

VIDEO MEMORY

VIDEO MEMORY

VIDEO MEMORY

VIDEO MEMORY

T208

T208

T208

T208

BERKELIUM

MOJAVE

SECURE ELEMENT

ALPINE RIDGE

ACE

CLIFDEN

AUDIO AMP

BAYSIDE

BANJO

TUBA

ICEBOCK

GREEN CLOCK

DEBUG MUX

TABLE_STRATEGIC_HEAD

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

TABLE_STRATEGIC__ITEM

C

B

A

FB VDRAM Parts

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

333S00044

333S00043

333S00078

333S00074

333S00075

4

4

4

4

4

IC,GDDR5,4Gb,7Gbps,1.5V,25NM,A,170 BGA UA400,UA450,UA500,UA550

UA400,UA450,UA500,UA550IC,GDDR5,4Gb,7Gbps,1.5V,25NM,A,170 BGA

IC,GDDR5,8Gb,7Gbps,1.5V,25NM,B,170 BGA

IC,GDDR5,8Gb,7Gbps,1.5V,25NM,A,170 BGA

UA400,UA450,UA500,UA550

UA400,UA450,UA500,UA550IC,GDDR5,8Gb,7Gbps,1.5V,25NM,B,170 BGA

UA400,UA450,UA500,UA550

CRITICAL

CRITICAL

CRITICAL

CRITICAL

Sub-BOM DIPLEXER

BOM NUMBER BOM NAME BOM OPTIONS

685-00085 DIPLEXERS,MURATA,X363G DIPLEXER:MURATA

FB_2GB_MICRON

FB_2GB_HYNIX

FB_2GB_SAMSUNGCRITICAL

FB_4GB_SAMSUNG

FB_4GB_MICRON

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

Main DRAM SPD Straps

BOM GROUP BOM OPTIONS

16G_SAMSUNG_2133,RAMCFG4:L,RAMCFG3:L,RAMCFG0:LRAM_16G_SAMSUNG_2133

16G_MICRON_2133,RAMCFG4:L,RAMCFG3:L,RAMCFG1:LRAM_16G_MICRON_2133

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

PAGE TITLE

BOM Configuration

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

SYNC_DATE=07/07/2015SYNC_MASTER=J80_MLB

DRAWING NUMBER SIZE

051-00647

REVISION

D

10.0.0

BRANCH

dvt-fab10

PAGE

2 OF 145

SHEET

2 OF 121

A

8 7 5 4 2 1

36

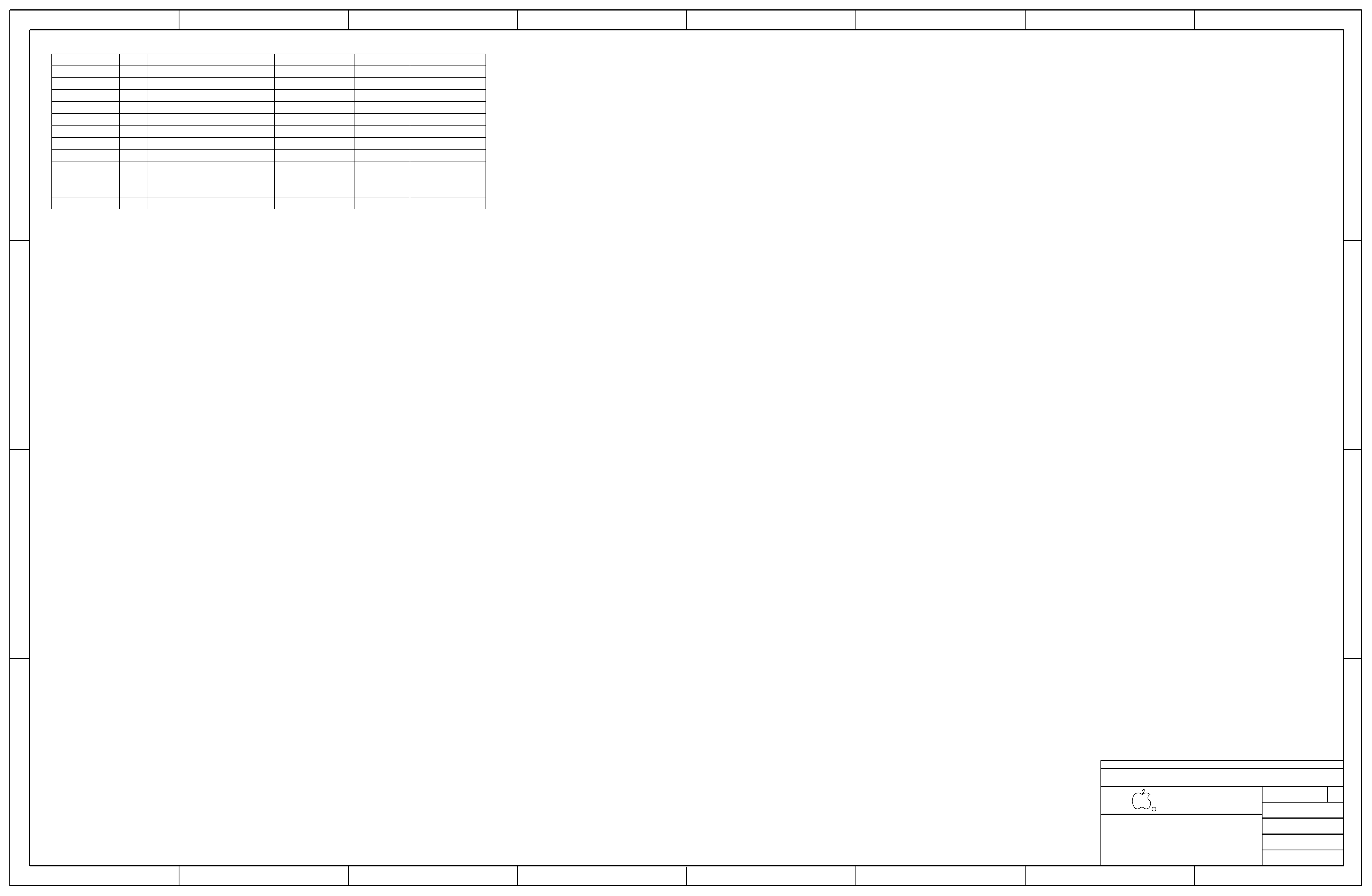

Page 3

Programmable Parts

345678

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

2 1

D

338S1231

341S00701

335S00013

341S00699

353S00926

341S00707

341S00708

335S00024

341S00709

341S3565

335S0724 1 UA701

1

1

1

1

2

1

1

1

1341S00695

1

1 U9800

IC,SMC12,40MHZ/50DMIPS MCU,7X7,168BGA

IC,SMC-B1,EXT (v2.37F7) PVT,X363G

IC,SPI SERIAL FLASH,64M BITS,3V,8P SOIC,QE=1

IC,EFI ROM (V0193), DVT, X363G

IC,CD3215,ACE,B03,BLNK,BGA96

T29,AR1 (V10.5) PVT, X363G

T29,AR2 (V10.5) PVT, X363G

IC,SERIAL-FLASH,2MBIT,4V,8-USON,2x3x,6MM

IC,BT ROM (V28), DVT, X362/X363

WIFI ROM (P107) DVT,NEW,WW1,X362/X363

IC, EDP MUX-95C, (RENESAS) V3.2.8,DVB,D2

IC,1Mbit SERIAL FLASH 2X3X0.6MM UFDFPN8 PKG

U5000

U5000

U6100

U6100

U2890,UB090

U2890

UB090

U3750

U3750

U3710

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

SMC_PROG:BLANK

SMC_PROG:PVT

BOOTROM_PROG:BLANK

BOOTROM_PROG:DVT

UPCROM_PROG:BLANK

UPCROM_PROG:DVT

UPCROM_PROG:DVT

BT_PROG:BLANK

BT_PROG:DVT

WIFI_PROG:DVT

DPMUXMCU:PROG

GPUROM:BLANK

Blank

TI

Blank

Macronix/Winbond

Blank

Winbond

Winbond

Blank

Macronix/Winbond

Rohm/On Semi

Blank

D

C

C

B

B

A

SYNC_MASTER=J80_MLB_BAFFIN_CLEAN SYNC_DATE=12/02/2015

PAGE TITLE

BOM Configuration

DRAWING NUMBER SIZE

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

8 7 5 4 2 1

36

REVISION

BRANCH

PAGE

SHEET

051-00647

10.0.0

dvt-fab10

3 OF 145

3 OF 121

A

D

Page 4

345678

2 1

D

C

B

Pogo Pins

APN 870-01771

PG0410

POGO-2.3OD-4.63H-SM

SM

1

PG0411

POGO-2.3OD-4.63H-SM

SM

1

PG0420

POGO-2.3OD-4.63H-SM

SM

1

PG0421

POGO-2.3OD-4.63H-SM

SM

1

PG0430

POGO-2.3OD-4.63H-SM

SM

1

PG0471

POGO-2.3OD-4.63H-SM

SM

1

PG0470

POGO-2.3OD-4.63H-SM

SM

1

APN 870-01772

PG0400

POGO-2.3OD-4.06H-SM

SM

1

PG0401

POGO-2.3OD-4.06H-SM

SM

1

APN 860-00392

BS0400

3.4OD1.75ID-1.12H-SM

1

BS0410

3.4OD1.75ID-1.12H-SM

1

APN 806-06520

BS0420

3.4OD1.75ID-1.45H-SM

1

APN 806-06521

BS0430

3.4OD1.75ID-1.9H-SM

1

BS0440

3.4OD1.75ID-1.9H-SM

1

BS0450

3.4OD1.75ID-1.9H-SM

1

APN 860-00413

BS0460

3.4OD1.75ID-1.57H-SM

1

APN 860-00469

BS0470

2.7X1.8R-1.4ID-0.91H-SM

1

SMT Bosses

USB-C Left

BOT side - North

USB-C Right

BOT side - North

DFR Touch

BOT side

DFR Display

BOT side - Left

Keyboard

BOT side - Left

Trackpad

BOT side - Left

Lifeboat

BOT side - North

eDP

TOP side - Left

BS0401

3.4OD1.75ID-1.12H-SM

1

USB-C Left

BOT side - South

BS0411

3.4OD1.75ID-1.12H-SM

1

USB-C Right

BOT side - South

APN 806-06600

BS0480

3.4OD1.75ID-2.12H-SM

1

BS0431

3.4OD1.75ID-1.9H-SM

1

DFR Display

BOT side - Right

BS0441

3.4OD1.75ID-1.9H-SM

1

Keyboard

BOT side - Right

BS0451

3.4OD1.75ID-1.9H-SM

1

Trackpad

BOT side - Right

BS0461

3.4OD1.75ID-1.57H-SM

1

Lifeboat

BOT side - South

BS0701

2.7X1.8R-1.4ID-0.91H-SM

1

eDP

TOP side - Right

USB-C Right

BOT side - Left

Rubber Mount

Standoffs

APN 860-00452

BM0400

3.09OD1.4ID-3.25H-SM

1

2

APN 860-00435

BM0401

2.8OD1.2ID-1.55H-SM

1

2

BM0402

2.8OD1.2ID-1.55H-SM

1

2

BM0403

2.8OD1.2ID-1.55H-SM

1

2

BM0404

2.8OD1.2ID-1.55H-SM

1

2

BM0405

2.8OD1.2ID-1.55H-SM

1

2

BM0406

2.8OD1.2ID-1.55H-SM

1

2

BM0407

2.8OD1.2ID-1.55H-SM

1

2

BM0408

2.8OD1.2ID-1.55H-SM

1

2

BM0409

2.8OD1.2ID-1.55H-SM

1

Shield Can TH

APN 998-2691

TH0400

TH-NSP

1

SL-1.1X0.4-1.4X0.7

TH0401

TH-NSP

1

SL-1.1X0.4-1.4X0.7

TH0410

TH-NSP

1

SL-1.1X0.4-1.4X0.7

TH0411

TH-NSP

1

SL-1.1X0.4-1.4X0.7

TH0420

TH-NSP

1

SL-1.1X0.4-1.4X0.7

TH0421

TH-NSP

1

SL-1.1X0.4-1.4X0.7

T208 through holes are non-plated... for now

TH0440

TH-NSP

1

SL-1.1X0.4-1.4X0.7

TH0441

TH-NSP

1

SL-1.1X0.4-1.4X0.7

TH0450

TH-NSP

1

SL-1.1X0.4-1.4X0.7

TH0451

TH-NSP

1

SL-1.1X0.4-1.4X0.7

TH0460

TH-NSP

1

SL-1.1X0.4-1.4X0.7

TH0461

TH-NSP

1

SL-1.1X0.4-1.4X0.7

System Memory - BOT side - Left

System Memory - BOT side - Right

TBT Left - BOT side - North

TBT Left - BOT side - South

TBT Right - BOT side - North

TBT Right - BOT side - South

T208 - TOP side - North

T208 - TOP side - South

SSD - BOT side - North

SSD - BOT side - South

SSD - TOP side - North

SSD - TOP side - South

Frame Buffer Memory - BOT side - Left

Frame Buffer Memory - BOT side - Right

Shield Can Fence

1

SH0400

SM

SHLD-FENCE-MLB-M8-X379

1

SH0410

SM

SHLD-FENCE-MLB-M8-X379

1

SH0420

SM

SHLD-FENCE-MLB-M8-X379

1

SH0430

SM

SHLD-FENCE-M8-X379

1

SH0440

SM

SHLD-FENCE-MLB-M8-X379

1

SH0450

SM

SHLD-FENCE-MLB-M8-X379

1

SH0460

SM

SHLD-FENCE-MLB-M8-X379

1

SH0470

SM

SHLD-FENCE-MLB-M8-X379

OMIT_TABLE

DRAM - BOT side

APN 806-06590

OMIT_TABLE

AR Right - BOT side

APN 806-06586

OMIT_TABLE

AR Left - BOT side

APN 806-06588

T208 - TOP side

APN 806-07814

OMIT_TABLE

SSD - TOP side

APN 806-06584

OMIT_TABLE

SSD - BOT side

APN 806-06585

OMIT_TABLE

Diplexer - BOT side

APN 806-06591

OMIT_TABLE

VRAM - BOT side

APN 806-08026

D

C

B

A

APN 806-07958

TOUCH-COWLING-HOOK-X378

1

BS0704

SM

DFR Touch - TOP side

2

BM0410

2.8OD1.2ID-1.55H-SM

1

2

BM0411

2.8OD1.2ID-1.55H-SM

1

2

BM0483

2.8OD1.2ID-1.55H-SM

1

2

APN 860-00500

BM0484

2.8OD1.2ID-3.5H-SM

1

2

APN 860-00500

BM0485

2.8OD1.2ID-3.5H-SM

1

2

BM0486

2.8OD1.2ID-3.5H-SM

1

2

BM0487

2.8OD1.2ID-3.5H-SM

1

2

Shield Can Omit Table

806-08023 1 SH0400 CRITICAL

1 CRITICALSH0410806-08019

1 CRITICALSH0420806-08021

806-07918

1 SH0450 CRITICAL806-07917

806-08024 CRITICALSH04601

BOM_COST_GROUP=MECHANICALS

SHIELD,FENCE,DRAM,X378

SHIELD,FENCE,ALPINE RIDGE,RIGHT,X378

SHIELD,FENCE,ALPINE RIDGE,LEFT,X378

SHIELD,NAND,TOP,ALT,X363

SHIELD,NAND,BOTTOM,ALT,X363

SHIELD,DIPLEX,EG,X378

FENCE,VRAM,EG,X378

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

SH0440 CRITICAL1

SH0470 CRITICAL1806-08026

PAGE TITLE

PD Parts

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

SYNC_DATE=11/16/2015SYNC_MASTER=J80_MLB

DRAWING NUMBER SIZE

051-00647

REVISION

D

10.0.0

BRANCH

dvt-fab10

PAGE

4 OF 145

SHEET

4 OF 121

A

8 7 5 4 2 1

36

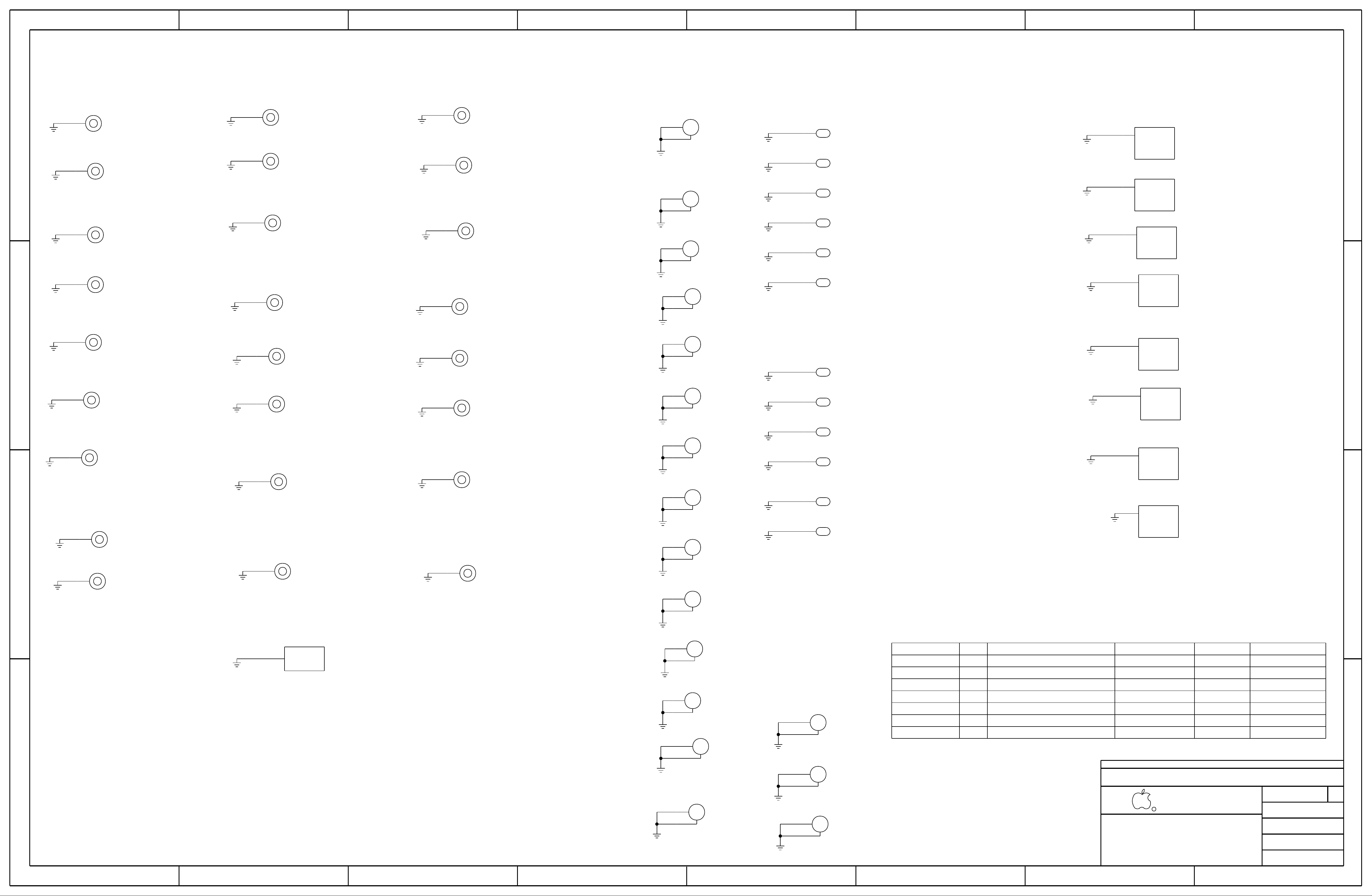

Page 5

345678

2 1

D

C

113 13

113 13

113 13

113 13

113 13

113 13

113 13

113 13

113 13

113 13

113 13

113 13

113 13

113 13

113 13

113 13

IN

IN

IN

IN

IN

IN

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

DMI_S2N_N<0>

DMI_S2N_N<1>

DMI_S2N_N<2>

DMI_S2N_N<3>

DMI_S2N_P<0>

DMI_S2N_P<1>

DMI_S2N_P<2>

DMI_S2N_P<3>

DMI_N2S_N<0>

DMI_N2S_N<1>

DMI_N2S_N<2>

DMI_N2S_N<3>

DMI_N2S_P<0>

DMI_N2S_P<1>

DMI_N2S_P<2>

DMI_N2S_P<3>

E8

DMI_RXN0

F6

DMI_RXN1

E5

DMI_RXN2

J9

DMI_RXN3

D8

DMI_RXP0

E6

DMI_RXP1

D5

DMI_RXP2

J8

DMI_RXP3

A8

DMI_TXN0

B6

DMI_TXN1

A5

DMI_TXN2

B4

DMI_TXN3

B8

DMI_TXP0

C6

DMI_TXP1

B5

DMI_TXP2

D4

DMI_TXP3

OMIT_TABLE

U0500

SKYLAKE-4+4E

BGA

SYM 1 OF 13

DMI

PEG_RCOMP

PEG_RXN0

PEG_RXN1

PEG_RXN2

PEG_RXN3

PEG_RXN4

PEG_RXN5

PEG_RXN6

PEG_RXN7

PEG_RXN8

PEG_RXN9

PEG_RXN10

PEG_RXN11

PEG_RXN12

PEG_RXN13

PEG_RXN14

PEG_RXN15

PEG_RXP0

PEG_RXP1

PEG_RXP2

PEG_RXP3

PEG_RXP4

PEG_RXP5

PEG_RXP6

PEG_RXP7

PEG_RXP8

PEG_RXP9

PEG_RXP10

PEG_RXP11

PEG_RXP12

PEG_RXP13

PEG_RXP14

PEG_RXP15

G2

D25

F24

D23

F22

D21

F20

D19

F18

E17

E16

E15

E14

E13

E12

E11

E10

E25

E24

E23

E22

E21

E20

E19

E18

D17

F16

D15

F14

D13

F12

D11

F10

CPU_PEG_RCOMP

PEG_GPU_D2R_N<0>

PEG_GPU_D2R_N<1>

PEG_GPU_D2R_N<2>

PEG_GPU_D2R_N<3>

PEG_GPU_D2R_N<4>

PEG_GPU_D2R_N<5>

PEG_GPU_D2R_N<6>

PEG_GPU_D2R_N<7>

PCIE_TBT_X_D2R_N<0>

PCIE_TBT_X_D2R_N<1>

PCIE_TBT_X_D2R_N<2>

PCIE_TBT_X_D2R_N<3>

PCIE_TBT_T_D2R_N<0>

PCIE_TBT_T_D2R_N<1>

PCIE_TBT_T_D2R_N<2>

PCIE_TBT_T_D2R_N<3>

PEG_GPU_D2R_P<0>

PEG_GPU_D2R_P<1>

PEG_GPU_D2R_P<2>

PEG_GPU_D2R_P<3>

PEG_GPU_D2R_P<4>

PEG_GPU_D2R_P<5>

PEG_GPU_D2R_P<6>

PEG_GPU_D2R_P<7>

PCIE_TBT_X_D2R_P<0>

PCIE_TBT_X_D2R_P<1>

PCIE_TBT_X_D2R_P<2>

PCIE_TBT_X_D2R_P<3>

PCIE_TBT_T_D2R_P<0>

PCIE_TBT_T_D2R_P<1>

PCIE_TBT_T_D2R_P<2>

PCIE_TBT_T_D2R_P<3>

PPVCCIO_S0_CPU

1

R0510

24.9

1%

1/16W

MF-LF

402

2

PLACE_NEAR=U0500.G2:5mm

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

111

IN

5 8 109

NC_DDI1_ML_C_N<0>

111

NC_DDI1_ML_C_P<0>

111

NC_DDI1_ML_C_N<1>

111

NC_DDI1_ML_C_P<1>

111

NC_DDI1_ML_C_N<2>

111

NC_DDI1_ML_C_P<2>

111

NC_DDI1_ML_C_N<3>

111

NC_DDI1_ML_C_P<3>

111

NC_DDI2_ML_C_N<0>

111

NC_DDI2_ML_C_P<0>

111

NC_DDI2_ML_C_N<1>

111

NC_DDI2_ML_C_P<1>

111

NC_DDI2_ML_C_N<2>

111

NC_DDI2_ML_C_P<2>

111

NC_DDI2_ML_C_N<3>

111

NC_DDI2_ML_C_P<3>

111

NC_DDI3_ML_N<2>

111

NC_DDI3_ML_P<2>

111

NC_DDI3_ML_N<3>

111

NC_DDI3_ML_P<3>

111

NC_DDI3_ML_N<0>

111

NC_DDI3_ML_P<0>

111

NC_DDI3_ML_N<1>

111

NC_DDI3_ML_P<1>

111

Port D pins out of order

to match Intel symbol.

K37

K36

J34

J35

H36

H37

J38

J37

H33

H34

G38

F37

F35

F34

E36

E37

E33

F33

B33

C33

D34

C34

B34

B36

DDI1_TXN0

DDI1_TXP0

DDI1_TXN1

DDI1_TXP1

DDI1_TXN2

DDI1_TXP2

DDI1_TXN3

DDI1_TXP3

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

DDI3_TXN2

DDI3_TXP2

DDI3_TXN3

DDI3_TXP3

DDI3_TXN0

DDI3_TXP0

DDI3_TXN1

DDI3_TXP1

OMIT_TABLE

U0500

SKYLAKE-4+4E

BGA

SYM 11 OF 13

EDP

EDP_DISP_UTIL

DIGITAL DISPLAY INTERFACES

EDP_AUXN

EDP_AUXP

EDP_TXN0

EDP_TXN1

EDP_TXN2

EDP_TXN3

EDP_TXP0

EDP_TXP1

EDP_TXP2

EDP_TXP3

EDP_RCOMP

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

B26

C26

E29

E28

B29

B28

D29

F28

A29

C28

D37

A33

E27

D27

E26

F26

B27

A27

NC

DP_INT_IG_AUX_N

DP_INT_IG_AUX_P

DP_INT_IG_ML_N<0>

DP_INT_IG_ML_N<1>

DP_INT_IG_ML_N<2>

DP_INT_IG_ML_N<3>

DP_INT_IG_ML_P<0>

DP_INT_IG_ML_P<1>

DP_INT_IG_ML_P<2>

DP_INT_IG_ML_P<3>

CPU_EDP_RCOMP

NC_DDI1_AUXCH_C_N

NC_DDI1_AUXCH_C_P

NC_DDI2_AUXCH_C_N

NC_DDI2_AUXCH_C_P

NC_DDI3_AUXCH_N

NC_DDI3_AUXCH_P

111

111

111

111

111

111

113 89

113 89

113 89

113 89

113 89

113 89

113 89

113 89

113 89

113 89

PPVCCIO_S0_CPU

1

R0530

24.9

1%

1/16W

MF-LF

402

2

D

5 8 109

PLACE_NEAR=U0500.D37:5mm

C

B

PEG_TXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3

PEG_TXN4

PEG_TXN5

PCI EXPRESS BASED INTERFACE SIGNALS

PEG_TXN6

PEG_TXN7

PEG_TXN8

PEG_TXN9

PEG_TXN10

PEG_TXN11

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4

PEG_TXP5

PEG_TXP6

PEG_TXP7

PEG_TXP8

PEG_TXP9

PEG_TXP10

PEG_TXP11

PEG_TXP12

PEG_TXP13

PEG_TXP14

PEG_TXP15

A25

C24

A23

C22

A21

C20

A19

C18

B17

B16

B15

B14

B13

B12

B11

B10

B25

B24

B23

B22

B21

B20

B19

B18

A17

C16

A15

C14

A13

C12

A11

C10

PEG_GPU_R2D_C_N<0>

PEG_GPU_R2D_C_N<1>

PEG_GPU_R2D_C_N<2>

PEG_GPU_R2D_C_N<3>

PEG_GPU_R2D_C_N<4>

PEG_GPU_R2D_C_N<5>

PEG_GPU_R2D_C_N<6>

PEG_GPU_R2D_C_N<7>

PCIE_TBT_X_R2D_C_N<0>

PCIE_TBT_X_R2D_C_N<1>

PCIE_TBT_X_R2D_C_N<2>

PCIE_TBT_X_R2D_C_N<3>

PCIE_TBT_T_R2D_C_N<0>

PCIE_TBT_T_R2D_C_N<1>

PCIE_TBT_T_R2D_C_N<2>

PCIE_TBT_T_R2D_C_N<3>

PEG_GPU_R2D_C_P<0>

PEG_GPU_R2D_C_P<1>

PEG_GPU_R2D_C_P<2>

PEG_GPU_R2D_C_P<3>

PEG_GPU_R2D_C_P<4>

PEG_GPU_R2D_C_P<5>

PEG_GPU_R2D_C_P<6>

PEG_GPU_R2D_C_P<7>

PCIE_TBT_X_R2D_C_P<0>

PCIE_TBT_X_R2D_C_P<1>

PCIE_TBT_X_R2D_C_P<2>

PCIE_TBT_X_R2D_C_P<3>

PCIE_TBT_T_R2D_C_P<0>

PCIE_TBT_T_R2D_C_P<1>

PCIE_TBT_T_R2D_C_P<2>

PCIE_TBT_T_R2D_C_P<3>

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

111

111

111

111

111

111

111

111

111

111

111

111

111

111

111

111

111

111

111

111

111

111

111

111

111

111

111

111

111

111

111

111

TP-P5

TP-P5

TP-P5

TP-P5

TP-P5

TP0501

TP0502

TP0503

TP0504

TP0505

TP

TP

TP

TP

TP

OMIT_TABLE

U0500

SKYLAKE-4+4E

BGA

SYM 13 OF 13

OPC_RCOMP

OPCE_RCOMP

OPCE_RCOMP2

PROC_TRIGIN

PROC_TRIGOUT

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

DDR_VTT_CNTL

PM_DOWN

BT29

BR25

BP25

H23

J23

G27

G25

G29

BT13

BP31

CPU_EOPIO_RCOMP

CPU_OPC_OPIO_RCOMP

CPU_OPC_OPIO_RCOMP_ED2

PCH_CPU_TRIGGER

CPU_PCH_TRIGGER_R

PCH_DISPA_BCLK

PCH_DISPA_SDO

CPU_PROC_AUD_SDO_R

PM_MEMVTT_EN

CPU_PCH_PM_DOWN_R

IN

5

IN

IN

5

OUT

5

13

20

20

71

1

R0521

49.9

1%

1/20W

MF

201

2

1

R0522

49.9

1%

1/20W

MF

201

2

1

R0523

49.9

1%

1/20W

MF

201

2

NC

NC

B2

B38

BP1

BR2

C1

C38

BR33

AT13

AW13

NCTF

NCTF

NCTF

NCTF

NCTF

NCTF

SKTOCC*

ZVM*

MSM*

1

1

1

1

1

CPU_DC_B2_C1

CPU_DC_B38_C38

NC

CPU_DC_BR2_BR1

CPU_DC_C1_B2

CPU_DC_C38_B38

NC

CPU Daisy-Chain Strategy:

Each corner of CPU has two testpoints.

Other corner test signals connected in

daisy-chain fashion. Continuity should

exist between both TP's on each corner.

R0524

30

5

1 2

5%

1/20W

MF

201

CPU_PCH_TRIGGERCPU_PCH_TRIGGER_R

OUT

13

B

A

5

5

BOM_COST_GROUP=CPU & CHIPSET

CPU_PCH_PM_DOWN_R

CPU_PROC_AUD_SDO_R

SYNC_MASTER=X363_AGOTETI SYNC_DATE=01/21/2016

PAGE TITLE

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

R0525

20

1 2

5%

1/20W

MF

201

CPU_PCH_PM_DOWN

OUT

13

R0526

20

1 2

5%

1/20W

MF

201

PCH_DISPA_SDI

OUT

20

CPU DMI/PEG/FDI/RSVD

DRAWING NUMBER SIZE

Apple Inc.

R

051-00647

REVISION

10.0.0

BRANCH

dvt-fab10

PAGE

5 OF 145

SHEET

5 OF 121

A

D

8 7 5 4 2 1

36

Page 6

PP1V0_S3

6 8 11 110

PLACE_NEAR=U0500.BM30:10mm

1

R0604

49.9

1%

1/20W

MF

201

2

OMIT_TABLE

345678

2 1

D

PP1V0_S0SW

8 11 18 110

PP1V0_S3

6 8 11 110

65 47 46

48 47 46 13

OUT

U0500

Note: Confirm values for 0603 and 0601. Different for J145

NC

1

R0605

1K

1%

1/16W

MF-LF

402

BI

CPU_PROCHOT_L

2

1

R0601

1K

1%

1/16W

MF-LF

402

2

PLACE_NEAR=U0500.BR30:5mm

R0603

499

1 2

1%

402

1/16W

MF-LF

46

47 13

13

13

13

OUT

BI

IN

IN

IN

CPU_CATERR_L

CPU_PECI

CPU_PROCHOT_R_L

PM_THRMTRIP_L

PM_SYNC

CPU_RESET_L

CPU_PWRGD

BN1

BM30

BT34

BR30

BM34

BP35

BT31

PROC_SELECT*

CATERR*

PECI

PROCHOT*

J31

THERMTRIP*

PM_SYNC

RESET*

PROCPWRGD

SKYLAKE-4+4E

BGA

SYM 2 OF 13

(IPU)

(IPU)

(IPD)

(IPU)

(IPU)

(IPU)

JTAG DDR3

DDR_RCOMP0

DDR_RCOMP1

DDR_RCOMP2

PROC_PRDY*

PROC_PREQ*

PROC_TCK

PROC_TMS

PROC_TRST*

PROC_TDI

PROC_TDO

G1

H1

J2

BP27

BL30

BR28

BP28

BP30

BL32

BT28

CPU_SM_RCOMP<0>

CPU_SM_RCOMP<1>

CPU_SM_RCOMP<2>

XDP_CPU_PRDY_L

XDP_CPU_PREQ_L

XDP_CPU_TCK

XDP_CPU_TMS

XDP_CPU_TRST_L

XDP_CPU_TDI

XDP_CPU_TDO

OUT

IN

IN

IN

IN

IN

OUT

1

R0614

162

115 18 13

115 18 13

115 18

115 18

115 18 13

115 18

115 18

1%

1/16W

MF-LF

402

2

1

R0613

121

1%

1/16W

MF-LF

402

2

1

R0612

200

1%

1/16W

MF-LF

402

2

D

C

B

A

P2MM

SM

1

PP0600

PP0601

PP0602

PP0603

CFG [7] :PEG DEFER TRAINING 1 = (DEFAULT) IMMEDIATELY AFTER xxRESETB 0 = WAIT FOR BIOS

CFG [6:5] :PCIE BIFURCATION 11 = 1 X16 (DEFAULT) 10 = 2 X8 01 = RSVD 00 = X8, X4, X4

CFG [4] :eDP ENABLE/DISABLE 1 = DISABLED 0 = ENABLED

CFG [3] :PCIE x4 LANE REVERSAL 1 = NORMAL OPERATION 0 = LANES REVERSED

CFG [2] :PCIE x16 LANE REVERSAL 1 = NORMAL OPERATION 0 = LANES REVERSED

PP

P2MM

SM

PP

P2MM

SM

PP

P2MM

SM

PP

TP_CPU_RSVD_R14

1

TP_CPU_RSVD_N29

1

TP_CPU_RSVD_AE29

1

TP_CPU_RSVD_AA14

6

6

6

6

These can be placed close to

J1800 and only for debug access

NOSTUFF

R0649

1K

5%

1/20W

MF

201

NOSTUFF

R0647

1K

5%

1/20W

MF

201

CPU_CFG<16>

CPU_CFG<9>

CPU_CFG<3>

CPU_CFG<1>

CPU_CFG<0>

NOSTUFF

1K

5%

1/20W

MF

201

1

2

1

2

R0648

NOSTUFF

1

R0643

1K

5%

1/20W

MF

201

2

NOSTUFF

R0641

1K

5%

1/20W

MF

201

1

2

NOSTUFF

1

R0640

1K

5%

1/20W

MF

201

2

CPU_CFG<7>

CPU_CFG<6>

CPU_CFG<5>

CPU_CFG<4>

CPUCFG6_PD

1K

5%

1/20W

MF

201

1

2

1

2

R0646

CPUCFG5_PD

1

R0645

1K

5%

1/20W

MF

201

2

EDP:YES

R0644

1K

5%

1/20W

MF

201

1

2

CPU_CFG<2>

NOSTUFF

1

R0642

1K

5%

1/20W

MF

201

2

18 6

18 6

115 18 6

18 6

18 6

18 6

18 6

18 6

18 6

18 6

BOM GROUP BOM OPTIONS

CPUPEG:X8X4X4 CPUCFG6_PD,CPUCFG5_PD

To use PEG X16 configuration, simply remove CPUPEG:X8X8 and CPUPEG:X8X4X4 from BOMs.

113 12

113 12

113 12

113 12

113 12

113 12

IN

IN

IN

IN

IN

IN

CPU_CLK24M_NSSC_CLK_N

CPU_CLK24M_NSSC_CLK_P

CPU_CLK100M_PCIBCLK_N

CPU_CLK100M_PCIBCLK_P

CPU_CLK100M_BCLK_N

CPU_CLK100M_BCLK_P

PLACE_NEAR=U0500.BT31:157mm

R0611

10K

5%

1/16W

MF-LF

402

1

2

D31

E31

C36

D35

A32

B31

CLK24N

CLK24P

PCI_BCLKN

PCI_BCLKP

BCLKN

BCLKP

CLOCK PWR THERMAL

(IPU)

(IPU)

(IPU)

(IPU)

BPM0*

BPM1*

BPM2*

BPM3*

BR27

BT27

BM31

BT30

XDP_BPM_L<0>

XDP_BPM_L<1>

XDP_BPM_L<2>

XDP_BPM_L<3>

18

BI

18

BI

18

BI

18

BI

C

OMIT_TABLE

U0500

SKYLAKE-4+4E

BGA

SYM 12 OF 13

RESERVED

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

CFG_RCOMP

(IPU)

(IPU)

RSVD_TP

RSVD_TP

CFG16

CFG18

CFG17

CFG19

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VSS

VSS

VSS

VSS

RSVD

RSVD

RSVD

BK24

BK16

BJ16

BJ24

BT25

BP23

BN22

BN23

BP22

AU13

AY13

J24

J3

BR17

BN33

BP16

BR16

BP17

BR35

BR31

BN35

BT17

C30

BT2

BR1

W3

W2

V6

W1

H24

E30

F30

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TP_CPU_RSVD_TP_BK24

TP_CPU_RSVD_TP_BK16

TP_CPU_RSVD_TP_BJ16

TP_CPU_RSVD_TP_BJ24

CPU_CFG_RCOMP

CPU_CFG<16>

CPU_CFG<18>

CPU_CFG<17>

CPU_CFG<19>

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

TP_CPU_RSVD_TP_BT2

CPU_DC_BR1_BR2

NC

NC

NC

18 6

18

18

18

1

TP

TP-P5

TP0610

1

R0690

49.9

1%

1/16W

MF-LF

402

2

BOM_COST_GROUP=CPU & CHIPSET

SYNC_MASTER=J80_MLB SYNC_DATE=11/06/2015

PAGE TITLE

CPU Clock/Misc/JTAG/CFG

DRAWING NUMBER SIZE

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

051-00647

REVISION

10.0.0

BRANCH

dvt-fab10

PAGE

6 OF 145

SHEET

6 OF 121

D

B

A

18 6

18 6

18 6

115 18 6

18 6

18 6

18 6

18 6

18

18 6

18

18

18

18

18

18

TP_CPU_RSVD_TP_BJ34

TP_CPU_RSVD_TP_BJ33

TP_CPU_RSVD_TP_BL33

TP_CPU_RSVD_TP_BM33

TP_CPU_RSVD_TP_D1

PPVCC_S0_CPU

8 55 109

TP_CPU_RSVD_R14

6

TP_CPU_RSVD_N29

6

TP_CPU_RSVD_AE29

6

TP_CPU_RSVD_AA14

6

CPU_CFG<0>

CPU_CFG<1>

CPU_CFG<2>

CPU_CFG<3>

CPU_CFG<4>

CPU_CFG<5>

CPU_CFG<6>

CPU_CFG<7>

CPU_CFG<8>

CPU_CFG<9>

CPU_CFG<10>

CPU_CFG<11>

CPU_CFG<12>

CPU_CFG<13>

CPU_CFG<14>

CPU_CFG<15>

CPUCFG5_PDCPUPEG:X8X8

NC

NC

NC

BJ34

BJ33

BL33

BM33

D1

V30

V12

V29

Y35

R14

N29

AE29

AA14

BN25

BN27

BN26

BN28

BR20

BM20

BT20

BP20

BR23

BR22

BT23

BT22

BM19

BR19

BP19

BT19

G3

G13

BT16

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

VSS

VSS

VSS

VCC

RSVD

RSVD

RSVD

RSVD

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

RSVD

RSVD

RSVD

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

8 7 5 4 2 1

36

Page 7

D

C

B

A

0

1 2

5%

1/20W

MF

201

113 26 22

113 26 22

113 26 22

113 26 22

113 26 22

113 26 22

113 26 22

113 26 22

113 26 22

113 26 22

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

R0701

21

21

21

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

MEM_A_DQ<0>

MEM_A_DQ<1>

MEM_A_DQ<2>

MEM_A_DQ<3>

MEM_A_DQ<4>

MEM_A_DQ<5>

MEM_A_DQ<6>

MEM_A_DQ<7>

MEM_A_DQ<8>

MEM_A_DQ<9>

MEM_A_DQ<10>

MEM_A_DQ<11>

MEM_A_DQ<12>

MEM_A_DQ<13>

MEM_A_DQ<14>

MEM_A_DQ<15>

MEM_A_DQ<16>

MEM_A_DQ<17>

MEM_A_DQ<18>

MEM_A_DQ<19>

MEM_A_DQ<20>

MEM_A_DQ<21>

MEM_A_DQ<22>

MEM_A_DQ<23>

MEM_A_DQ<24>

MEM_A_DQ<25>

MEM_A_DQ<26>

MEM_A_DQ<27>

MEM_A_DQ<28>

MEM_A_DQ<29>

MEM_A_DQ<30>

MEM_A_DQ<31>

MEM_A_DQ<32>

MEM_A_DQ<33>

MEM_A_DQ<34>

MEM_A_DQ<35>

MEM_A_DQ<36>

MEM_A_DQ<37>

MEM_A_DQ<38>

MEM_A_DQ<39>

MEM_A_DQ<40>

MEM_A_DQ<41>

MEM_A_DQ<42>

MEM_A_DQ<43>

MEM_A_DQ<44>

MEM_A_DQ<45>

MEM_A_DQ<46>

MEM_A_DQ<47>

MEM_A_DQ<48>

MEM_A_DQ<49>

MEM_A_DQ<50>

MEM_A_DQ<51>

MEM_A_DQ<52>

MEM_A_DQ<53>

MEM_A_DQ<54>

MEM_A_DQ<55>

MEM_A_DQ<56>

MEM_A_DQ<57>

MEM_A_DQ<58>

MEM_A_DQ<59>

MEM_A_DQ<60>

MEM_A_DQ<61>

MEM_A_DQ<62>

MEM_A_DQ<63>

NOSTUFF

1 2

5%

1/20W

MF

201

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

CPU_DIMMA_VREFDQ

CPU_DIMMB_VREFDQ

0

R0703

DDR0_PAR

MEM_A_ALERT

CPU_DIMM_VREFCA

MEM_A_CAA<0>

MEM_A_CAA<1>

MEM_A_CAA<2>

MEM_A_CAA<3>

MEM_A_CAA<4>

MEM_A_CAA<5>

MEM_A_CAA<6>

MEM_A_CAA<7>

MEM_A_CAA<8>

MEM_A_CAA<9>

BR6

BT6

BP3

BR3

BN5

BP6

BP2

BN3

BL4

BL5

BL2

BM1

BK4

BK5

BK1

BK2

BT11

BR11

BT8

BR8

BP11

BN11

BP8

BN8

BL12

BL11

BL8

BJ8

BJ11

BJ10

BL7

BJ7

BG4

BG5

BF4

BF5

BG2

BG1

BF1

BF2

BD2

BD1

BC4

BC5

BD5

BD4

BC1

BC2

BG11

BG10

BG8

BF8

BF11

BF10

BG7

BF7

BB11

BC11

BB8

BC8

BC10

BB10

BC7

BB7

AG3

AU5

BN13

BP13

BR13

BJ26

AP1

AT4

AP3

AN3

AN1

AU1

AU4

AN2

AU3

AU2

DDR0_DQ0

DDR0_DQ1

SKYLAKE-4+4E

DDR0_DQ2

DDR0_DQ3

DDR0_DQ4

DDR0_DQ5

DDR0_DQ6

DDR0_DQ7

DDR0_DQ8

DDR0_DQ9

DDR0_DQ10

DDR0_DQ11

DDR0_DQ12

DDR0_DQ13

DDR0_DQ14

DDR0_DQ15

DDR0_DQ16

DDR0_DQ17

DDR0_DQ18

DDR0_DQ19

DDR0_DQ20

DDR0_DQ21

DDR0_DQ22

DDR0_DQ23

DDR0_DQ24

DDR0_DQ25

DDR0_DQ26

DDR0_DQ27

DDR0_DQ28

DDR0_DQ29

DDR0_DQ30

DDR0_DQ31

DDR0_DQ32

DDR0_DQ33

DDR0_DQ34

DDR0_DQ35

DDR0_DQ36

DDR0_DQ37

DDR0_DQ38

DDR0_DQ39

DDR0_DQ40

DDR0_DQ41

DDR0_DQ42

DDR0_DQ43

DDR0_DQ44

DDR0_DQ45

DDR0_DQ46

DDR0_DQ47

DDR0_DQ48

DDR0_DQ49

DDR0_DQ50

DDR0_DQ51

DDR0_DQ52

DDR0_DQ53

DDR0_DQ54

DDR0_DQ55

DDR0_DQ56

DDR0_DQ57

DDR0_DQ58

DDR0_DQ59

DDR0_DQ60

DDR0_DQ61

DDR0_DQ62

DDR0_DQ63

DDR0_PAR

DDR0_ALERT*

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

RSVD

DDR0_CAA0

DDR0_CAA1

DDR0_CAA2

DDR0_CAA3

DDR0_CAA4

DDR0_CAA5

DDR0_CAA6

DDR0_CAA7

DDR0_CAA8

DDR0_CAA9

OMIT_TABLE

U0500

BGA

SYM 3 OF 13

MEMORY CHANNEL DDR0

DDR0_DQSN0

DDR0_DQSN1

DDR0_DQSN2

DDR0_DQSN3

DDR0_DQSN4

DDR0_DQSN5

DDR0_DQSN6

DDR0_DQSN7

DDR0_DQSN8

DDR0_DQSP0

DDR0_DQSP1

DDR0_DQSP2

DDR0_DQSP3

DDR0_DQSP4

DDR0_DQSP5

DDR0_DQSP6

DDR0_DQSP7

DDR0_DQSP8

RSVD

DDR0_CKN0

DDR0_CKP0

DDR0_CKE0

DDR0_CKN1

DDR0_CKP1

DDR0_CKE1

DDR0_CLKN2

DDR0_CLKP2

DDR0_CKE2

DDR0_CLKN3

DDR0_CLKP3

DDR0_CKE3

DDR0_CS0*

DDR0_CS1*

DDR0_CS2*

DDR0_CS3*

DDR0_ODT0

DDR0_ODT1

DDR0_ODT2

DDR0_ODT3

VSS

DDR0_MA3

DDR0_MA4

DDR0_ECC0

DDR0_ECC1

DDR0_ECC2

DDR0_ECC3

DDR0_ECC4

DDR0_ECC5

DDR0_ECC6

DDR0_ECC7

RSVD

RSVD

RSVD

RSVD_TP

RSVD_TP

RSVD

DDR0_CAB0

DDR0_CAB1

DDR0_CAB2

DDR0_CAB3

DDR0_CAB4

DDR0_CAB5

DDR0_CAB6

DDR0_CAB7

DDR0_CAB8

DDR0_CAB9

BJ23

AG2

AG1

AT1

AK1

AK2

AT2

AK3

AL3

AT3

AL1

AL2

AT5

AD5

AE2

AD2

AE5

AD3

AE4

AE1

AD4

U38

AP5

AP2

BA2

BA1

AY4

AY5

BA5

BA4

AY1

AY2

BR5

BL3

BP9

BL9

BG3

BD3

BG9

BC9

BA3

BP5

BK3

BR9

BJ9

BF3

BC3

BF9

BB9

AY3

AJ8

B30

BH30

BJ13

BJ14

BJ21

AE3

AD1

AG4

AH4

AH5

AN4

AH1

AH2

AP4

AH3

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NCNC

MEM_A_CLK_N<0>

MEM_A_CLK_P<0>

MEM_A_CKE<0>

MEM_A_CLK_N<1>

MEM_A_CLK_P<1>

MEM_A_CKE<1>

MEM_A_CKE<2>

MEM_A_CKE<3>

MEM_A_CS_L<0>

MEM_A_CS_L<1>

MEM_A_ODT<0>

MEM_A_DQS_N<0>

MEM_A_DQS_N<1>

MEM_A_DQS_N<2>

MEM_A_DQS_N<3>

MEM_A_DQS_N<4>

MEM_A_DQS_N<5>

MEM_A_DQS_N<6>

MEM_A_DQS_N<7>

MEM_A_DQS_P<0>

MEM_A_DQS_P<1>

MEM_A_DQS_P<2>

MEM_A_DQS_P<3>

MEM_A_DQS_P<4>

MEM_A_DQS_P<5>

MEM_A_DQS_P<6>

MEM_A_DQS_P<7>

MEM_A_CAB<0>

MEM_A_CAB<1>

MEM_A_CAB<2>

MEM_A_CAB<3>

MEM_A_CAB<4>

MEM_A_CAB<5>

MEM_A_CAB<6>

MEM_A_CAB<7>

MEM_A_CAB<8>

MEM_A_CAB<9>

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

345678

2 1

OMIT_TABLE

113 26 22

113 26 22

26 22

113 26 23

113 26 23

26 22

26 23

26 23

26 23 22

26 23 22

26 23 22

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

1 2

112

0

5%

1/20W

MF

201

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

MEM_B_DQ<0>

MEM_B_DQ<1>

MEM_B_DQ<2>

MEM_B_DQ<3>

MEM_B_DQ<4>

MEM_B_DQ<5>

MEM_B_DQ<6>

MEM_B_DQ<7>

MEM_B_DQ<8>

MEM_B_DQ<9>

MEM_B_DQ<10>

MEM_B_DQ<11>

MEM_B_DQ<12>

MEM_B_DQ<13>

MEM_B_DQ<14>

MEM_B_DQ<15>

MEM_B_DQ<16>

MEM_B_DQ<17>

MEM_B_DQ<18>

MEM_B_DQ<19>

MEM_B_DQ<20>

MEM_B_DQ<21>

MEM_B_DQ<22>

MEM_B_DQ<23>

MEM_B_DQ<24>

MEM_B_DQ<25>

MEM_B_DQ<26>

MEM_B_DQ<27>

MEM_B_DQ<28>

MEM_B_DQ<29>

MEM_B_DQ<30>

MEM_B_DQ<31>

MEM_B_DQ<32>

MEM_B_DQ<33>

MEM_B_DQ<34>

MEM_B_DQ<35>

MEM_B_DQ<36>

MEM_B_DQ<37>

MEM_B_DQ<38>

MEM_B_DQ<39>

MEM_B_DQ<40>

MEM_B_DQ<41>

MEM_B_DQ<42>

MEM_B_DQ<43>

MEM_B_DQ<44>

MEM_B_DQ<45>

MEM_B_DQ<46>

MEM_B_DQ<47>

MEM_B_DQ<48>

MEM_B_DQ<49>

MEM_B_DQ<50>

MEM_B_DQ<51>

MEM_B_DQ<52>

MEM_B_DQ<53>

MEM_B_DQ<54>

MEM_B_DQ<55>

MEM_B_DQ<56>

MEM_B_DQ<57>

MEM_B_DQ<58>

MEM_B_DQ<59>

MEM_B_DQ<60>

MEM_B_DQ<61>

MEM_B_DQ<62>

MEM_B_DQ<63>

0

1 2

R0702

5%

1/20W

MF

201

R0704

DDR1_PAR

MEM_B_ALERT

AB1

AB2

AA4

AA5

AB5

AB4

AA2

AA1

V5

V2

U1

U2

V1

V4

U5

U4

AA11

AA10

AC11

AC10

AA7

AA8

AC8

AC7

W8

W7

V10

V11

W11

W10

V7

V8

R2

P5

R4

P4

R5

P2

R1

P1

M4

M1

L4

L2

M5

M2

L5

L1

R11

P11

P7

R8

R10

P10

R7

P8

L11

M11

L7

M8

L10

M10

M7

L8

AJ7

AR8

DDR1_DQ0

DDR1_DQ1

DDR1_DQ2

DDR1_DQ3

DDR1_DQ4

DDR1_DQ5

DDR1_DQ6

DDR1_DQ7

DDR1_DQ8

DDR1_DQ9

DDR1_DQ10

DDR1_DQ11

DDR1_DQ12

DDR1_DQ13

DDR1_DQ14

DDR1_DQ15

DDR1_DQ16

DDR1_DQ17

DDR1_DQ18

DDR1_DQ19

DDR1_DQ20

DDR1_DQ21

DDR1_DQ22

DDR1_DQ23

DDR1_DQ24

DDR1_DQ25

DDR1_DQ26

DDR1_DQ27

DDR1_DQ28

DDR1_DQ29

DDR1_DQ30

DDR1_DQ31

DDR1_DQ32

DDR1_DQ33

DDR1_DQ34

DDR1_DQ35

DDR1_DQ36

DDR1_DQ37

DDR1_DQ38

DDR1_DQ39

DDR1_DQ40

DDR1_DQ41

DDR1_DQ42

DDR1_DQ43

DDR1_DQ44

DDR1_DQ45

DDR1_DQ46

DDR1_DQ47

DDR1_DQ48

DDR1_DQ49

DDR1_DQ50

DDR1_DQ51

DDR1_DQ52

DDR1_DQ53

DDR1_DQ54

DDR1_DQ55

DDR1_DQ56

DDR1_DQ57

DDR1_DQ58

DDR1_DQ59

DDR1_DQ60

DDR1_DQ61

DDR1_DQ62

DDR1_DQ63

DDR1_PAR

DDR1_ALERT*

U0500

SKYLAKE-4+4E

BGA

SYM 4 OF 13

MEMORY CHANNEL DDR1

RSVD

DDR1_CKN0

DDR1_CKP0

DDR1_CKE0

DDR1_CKN1

DDR1_CKP1

DDR1_CKE1

DDR1_CLKN2

DDR1_CLKP2

DDR1_CKE2

DDR1_CLKN3

DDR1_CLKP3

DDR1_CKE3

DDR1_CS0*

DDR1_CS1*

DDR1_CS2*

DDR1_CS3*

DDR1_ODT0

DDR1_ODT1

DDR1_ODT2

DDR1_ODT3

VSS

DDR1_MA3

DDR1_MA4

DDR1_ECC0

DDR1_ECC1

DDR1_ECC2

DDR1_ECC3

DDR1_ECC4

DDR1_ECC5

DDR1_ECC6

DDR1_ECC7

DDR1_DQSN0

DDR1_DQSN1

DDR1_DQSN2

DDR1_DQSN3

DDR1_DQSN4

DDR1_DQSN5

DDR1_DQSN6

DDR1_DQSN7

DDR1_DQSN8

DDR1_DQSP0

DDR1_DQSP1

DDR1_DQSP2

DDR1_DQSP3

DDR1_DQSP4

DDR1_DQSP5

DDR1_DQSP6

DDR1_DQSP7

DDR1_DQSP8

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

113 26 23

113 26 23

113 26 23

113 26 23

113 26 23

113 26 23

113 26 23

113 26 23

113 26 23

113 26 23

113 26 24

113 26 24

113 26 24

113 26 24

113 26 24

113 26 24

113 26 24

113 26 24

113 26 24

113 26 24

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

MEM_B_CAA<0>

MEM_B_CAA<1>

MEM_B_CAA<2>

MEM_B_CAA<3>

MEM_B_CAA<4>

MEM_B_CAA<5>

MEM_B_CAA<6>

MEM_B_CAA<7>

MEM_B_CAA<8>

MEM_B_CAA<9>

AM6

AR11

AN7

AN8

AN10

AR9

AR10

AN11

AT9

AR7

DDR1_CAA0

DDR1_CAA1

DDR1_CAA2

DDR1_CAA3

DDR1_CAA4

DDR1_CAA5

DDR1_CAA6

DDR1_CAA7

DDR1_CAA8

DDR1_CAA9

RSVD

DDR1_CAB0

DDR1_CAB1

DDR1_CAB2

DDR1_CAB3

DDR1_CAB4

DDR1_CAB5

DDR1_CAB6

DDR1_CAB7

DDR1_CAB8

DDR1_CAB9

BJ27

AN9

AM9

AT8

AM8

AM7

AT10

AM10

AM11

AT7

AJ11

AJ10

AT11

AF11

AE7

AF10

AE10

AF7

AE8

AE9

AE11

Y38

AL5

AL6

AW11

AY11

AY8

AW8

AY10

AW10

AY7

AW7

AA3

U3

AC9

W9

P3

L3

R9

M9

AY9

AB3

V3

AA9

V9

R3

M3

P9

L9

AW9

BK28

BK26

BK27

BK23

BK21

BJ35

BJ28

BJ36

AF9

AF8

AH11

AH10

AH8

AK5

AH9

AH7

AK6

AJ9

NC

MEM_B_CLK_N<0>

MEM_B_CLK_P<0>

MEM_B_CKE<0>

MEM_B_CLK_N<1>

MEM_B_CLK_P<1>

MEM_B_CKE<1>

OUT

OUT

OUT

OUT

OUT

OUT

NC

NC

MEM_B_CKE<2>

OUT

NC

NC

MEM_B_CKE<3>

MEM_B_CS_L<0>

MEM_B_CS_L<1>

OUT

OUT

OUT

NC

NC

MEM_B_ODT<0>

OUT

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

MEM_B_DQS_N<0>

MEM_B_DQS_N<1>

MEM_B_DQS_N<2>

MEM_B_DQS_N<3>

MEM_B_DQS_N<4>

MEM_B_DQS_N<5>

MEM_B_DQS_N<6>

MEM_B_DQS_N<7>

BI

BI

BI

BI

BI

BI

BI

BI

NC

MEM_B_DQS_P<0>

MEM_B_DQS_P<1>

MEM_B_DQS_P<2>

MEM_B_DQS_P<3>

MEM_B_DQS_P<4>

MEM_B_DQS_P<5>

MEM_B_DQS_P<6>

MEM_B_DQS_P<7>

BI

BI

BI

BI

BI

BI

BI

BI

NC

NC

NCNC

NC

NC

NC

NC

NC

NC

MEM_B_CAB<0>

MEM_B_CAB<1>

MEM_B_CAB<2>

MEM_B_CAB<3>

MEM_B_CAB<4>

MEM_B_CAB<5>

MEM_B_CAB<6>

MEM_B_CAB<7>

MEM_B_CAB<8>

MEM_B_CAB<9>

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BOM_COST_GROUP=CPU & CHIPSET

113 26 24

113 26 24

26 24

113 26 25

113 26 25

26 24

D

26 25

26 25

26 25 24

26 25 24

26 25 24

C

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

B

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 112

113 26 25

113 26 25

113 26 25

113 26 25

113 26 25

113 26 25

113 26 25

113 26 25

113 26 25

113 26 25

PAGE TITLE

CPU DDR3 Interfaces

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

DRAWING NUMBER SIZE

051-00647

051-00647

REVISION

BRANCH

dvt-fab10

dvt-fab10

PAGE

SHEET

SYNC_DATE=11/06/2015SYNC_MASTER=J80_MLB

10.0.0

10.0.0

7 OF 145

7 OF 145

7 OF 1217 OF 121

A

D

8 7 5 4 2 1

36

Page 8

345678

2 1

D

C

B

A

PP1V0_S3

6 8 11 110

CPU_VCCST_PWRGD_R

8

PP1V0_S0SW

6 11 18 110

PPVCCGT_S0_CPU

AW36

AW37

AW38

AY29

VCCGT

VCCGT

VCCGT

U0500

OMIT_TABLE

VCCGT

BGA

SYM 7 OF 13

SKYLAKE-4+4E

VCCGT

VCCGT

AJ31

AJ32

VCCGT

VCCGT

AJ29

AJ30

AY30

AY31

VCCGT

VCCGT

POWER

VCCGT

VCCGT

AJ33

AJ34

AY32

AY35

VCCGT

VCCGT

VCCGT

VCCGT

AJ35

AJ36

AY36

AY37

VCCGT

VCCGT

VCCGT

VCCGT

AK31

AK32

8 55 109

AY38

BA13

VCCGT

VCCGT

VCCGT

VCCGT

AK33

AK34

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

BA14

BA29

VCCGT

VCCGT

VCCGT

VCCGT

AK35

AK36

OMIT_TABLE

AF29

AF30

AF31

AF32

AF33

AF34

AG13

AG14

AG31

AG32

AG33

AG34

AG35

AG36

AH13

AH14

AH29

AH30

AH31

AH32

AH36

AH35 J14

BK17

BK19

BK20

BL16

BL17

BL18

BL19

BL20

BL21

BM17

BN17

BL15

BM16

BP15

BR15

BT15

BN15

BM15

BA30

VCCGT

VCCGT

AK37

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

AJ13

VCCGTX

AJ14

VCCGTX

VCCGTX_SENSE

VSSGTX_SENSE

BJ17

VCCOPC

BJ19

VCCOPC

BJ20

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC_SENSE

VSSOPC_SENSE

H30

VCCST

H13

VCCST_PWRGD

G30

VCCSTG

H29

VCCSTG

VCCEOPIO

VCCEOPIO

VCCEOPIO

VCCEOPIO_SENSE

VSSEOPIO_SENSE

BA31

BA32

BA33

BA34

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

AL13

AL29

AK38

AL30

U0500

SKYLAKE-4+4E

SYM 6 OF 13

POWER

BA35

BA36

BB13

BB14

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

AL35

AL36

VCCGT

AL37

VCCGT

AL31

AL32

BGA

BB31

BB32

VCCGT

VCCGT

VCCGT

VCCGT

AL38

VCCIO_SENSE

VSSIO_SENSE

VCCSA_SENSE

VSSSA_SENSE

VCCPLL_OC

VCCPLL_OC

VCC_OPC_1P8

VCC_OPC_1P8

BB33

BB34

BB35

BB36

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

AM13

AM14

AM29

AM30

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCPLL

VCCPLL

BB37

BB38

VCCGT

VCCGT

VCCGT

VCCGT

AM31

AM32

BC29

VCCGT

VCCGT

VCCGT

VCCGT

AM33

AG12

G15

G17

G19

G21

H15

H16

H17

H19

H20

H21

H26

H27

J15

J16

J17

J19

J20

J21

J26

J27

H14

J30

K29

K30

K31

K32

K33

K34

K35

L31

L32

L35

L36

L37

L38

M29

M30

M31

M32

M33

M34

M35

M36

M38

M37

H28

J28

BH13

G11

BL14

BM14

BC30

BC31

VCCGT

VCCGT

AM34

AM35

PPVCCIO_S0_CPU

CPU_VCCIOSENSE_P

CPU_VCCIOSENSE_N

PPVCCSA_S0_CPU

CPU_VCCSASENSE_P

CPU_VCCSASENSE_N

PP1V0_S3

PP1V2_S0SW

109

NC

NC

BC32

BC35

BC36

BC37

BC38

BD13

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

AN32

AN33

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

AN13

AM36

VCCGT

VCCGT

VCCGT

AN14

AN31

BD14

BD29

VCCGT

VCCGT

VCCGT

VCCGT

AN34

AN35

BD30

BD31

VCCGT

VCCGT

VCCGT

VCCGT

AN36

AN37

BD32

BD33

VCCGT

VCCGT

VCCGT

VCCGT

AP13

AN38

11 110

BD34

BD35

VCCGT

VCCGT

VCCGT

VCCGT

AP14

AP29

5 8 109

OUT

OUT

8 53 109

OUT

OUT

1

C0802

2

BD36

BE31

VCCGT

VCCGT

VCCGT

VCCGT

AP30

AP31

71 8

71 9

65 8

65 9

1UF

20%

6.3V

X6S-CERM

0201

BE32

BE33

BE34

VCCGT

VCCGT

VCCGT

VCCGT

AP32

AP35

AP36

BE35

BE36

VCCGT

VCCGT

VCCGT

VCCGT

AP37

AP38

1

2

1

C0803

1UF

20%

6.3V

2

X6S-CERM

0201

BE37

BE38

VCCGT

VCCGT

VCCGT

VCCGT

AR29

AR30

R0864

100

5%

1/20W

MF

201

70

IN

BF13

BF14

BF29

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

AR31

AR32

AR33

PPVCC_S0_CPU

1

R0865

100

5%

1/20W

MF

201

2

PPVCCGT_S0_CPU

PPVCCSA_S0_CPU

PLACE_NEAR=U0500.AG37:50.8mm

PLACE_NEAR=U0500.AH38:50.8mm

PLACE_NEAR=U0500.M38:50.4mm

1

R0866

100

5%

1/20W

MF

201

2

8 55 109

8 53 109

CPU_VCCSASENSE_P

CPU_VCCGTSENSE_P

CPU_VCCSENSE_P

PPVCCIO_S0_CPU

PLACE_NEAR=U0500.H14:50.8mm

1

R0861

100

5%

1/20W

MF

201

2

CPU_VCCIOSENSE_P

PULL-UPS FOR SENSE LINES

PP1V0_S3

6 8 11 110

1

R0840

1K

1%

1/16W

MF-LF

402

2

R0841

60.4

BG33

BG34

VCCGT

VCCGT

VCCGT

VCCGT

AT38

AU14

1 2

1%

1/20W

MF

201

1

R0802

100

5%

1/20W

MF

201

2

BG35

BG36

BH33

VCCGT

VCCGT

VCCGT

VCCGT