ANPEC APA2030, APA2031 Datasheet

APA2030/2031

Stereo 2.6W Audio Amplifier(With Gain Control)

Features General Description

••

• Low operating current with 6mA

••

••

• Improved depop circuitry to eliminate turn-on

••

transients in outputs

••

• High PSRR

••

••

• Internal gain control, eliminate external components.

••

••

• 2.6W per channel output power into 3Ω load at 5V,

••

BTL mode

••

• Multiple input modes allowable selected by HP

••

/LINE pin (APA2030)

••

• Two output modes allowable with BTL and SE

••

modes selected by SE/BTL pin (for APA2030 only)

••

• Low current consumption in shutdown mode (50µ

••

A)

••

• Short Circuit Protection

••

••

• TSSOP-24-P (APA2030) and TSSOP-20-P

••

(APA2031) with thermal pad package.

Applications

••

• NoteBook PC

••

••

• LCD Monitor

••

APA2030/1 is a monolithic integrated circuit, which

provides internal gain control, and a stereo bridged

audio power amplifiers capable of producing 2.6W

(1.9W) into 3Ω with less than 10% (1.0%) THD+N.

By control the two gain setting pins, Gain0 and Gain1,

The amplifier can provide 6dB, 10dB, 15.6dB, and

21.6dB gain settings. The advantage of internal gain

setting can be less components and PCB area. Both

of the depop circuitry and the thermal shutdown pro-

tection circuitry are integrated in APA2030/1, that

reduces pops and clicks noise during power up or

shutdown mode operation. It also improved the power

off pop noise and protects the chip from being de-

stroyed by over temperature and short current failure.

To simplify the audio system design APA2030 com-

bines a stereo bridge-tied loads (BTL) mode for

speaker drive and a stereo single-end (SE) mode for

headphone drive into a single chip, where both modes

are easily switched by the SE/BTL input control pin

signal. Besides the multiple input selections is used

for portable audio system. APA2031 eliminates both

input selection and single-end (SE) mode function to

simplifying the design and save the PCB space.

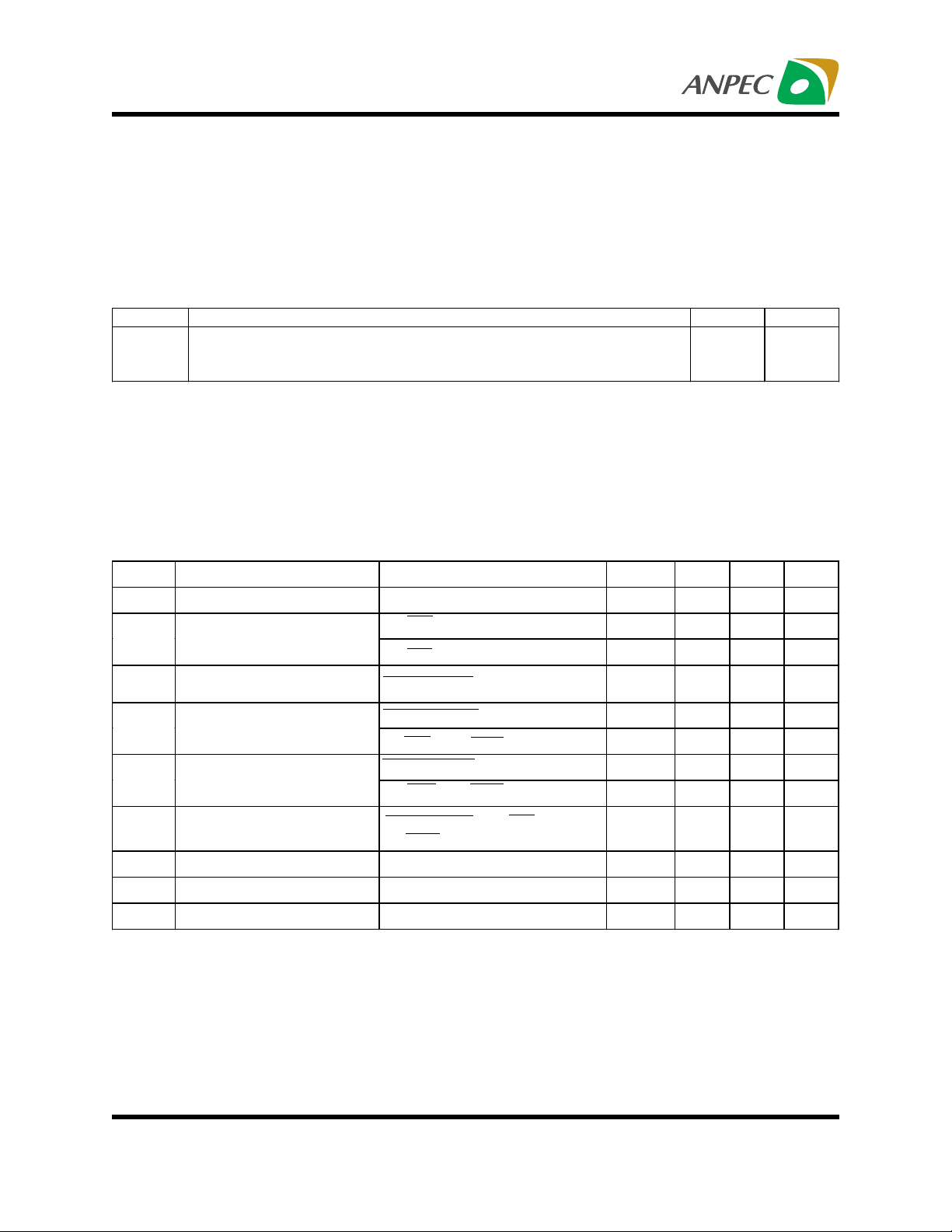

Ordering and Marking Information

APA2030/1

Lead Free Code

Handling Code

Temp. Range

Package Code

APA2030/1 R :

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise

customers to obtain the latest version of relevant information to verify before placing orders.

Copyright ANPEC Electronics Corp.

Rev. A.2 -Apr., 2004

APA2030/1

XXXXX

Package Code

R : TSSOP-P *

Temp. Range

I : - 40 to 85 C

Handling Code

TU : Tu be TR : Tape & R eel

TY : Tra y

Lead Free Code

L : Lead Free Device Blank : O riginal Device

XXXXX - Date Code

°

www.anpec.com.tw1

APA2030/2031

Pin Assignment

GND 1

GA IN0 2

LOUT+ 4

LLINEIN 5

LHPIN 6

PVDD 7

RIN+ 8

LOUT- 9

LIN+ 10

BYPASS 11

GND 12

TOP View

(APA2030)

Block Diagram

LLINEIN

LHPIN

LIN+

BYPASS

AP A 2030_P i nOut

24 GND

23 RLINEIN

22 SHUTDOWNGA IN1 3

21 ROUT+

20 RHPIN

19 V

18 PV

17 HP/LINE

16 ROUT-

15 SE/BTL

14 PCB EEP

13 GND

MUX

DD

DD

GND 1

GAIN0 2

LOUT+ 4

LIN- 5

6

PV

DD

LOUT- 8

LIN+ 9

BYPA SS 10

Vbias

TOP View

(APA2031)

LOUT+

20 GND

19 SHUTDO WN

18 ROUT+GAIN1 3

17 RIN-

16 V

DD

15 PV

DD

14 ROUT-RIN+ 7

13 GND

12 NC

11 GND

GAIN0

GIAN1

RLINEIN

RHPIN

RIN+

HP/LINE

SE/BTL

SHUTDO W N

PCB EEP

Copyright ANPEC Electronics Corp.

Rev. A.2 - Apr., 2004

Gain

selectable

MUX

H P/L INE

SE/BTL

Shutdown

ckt

PC- BEEP

ckt

LOUT-

ROUT+

Vbias

ROUT-

AP A2030_B lock

APA2030

www.anpec.com.tw2

APA2030/2031

Block Diagram

LIN-

LIN+

BYPASS

SHUTDOW N

GAIN0

GAIN1

RIN-

RIN+

Shu tdo wn

ckt

Gain

selectab le

LOUT+

Vbias

LOUT-

ROUT+

Vbias

ROUT-

APA2031_Block

APA2031

Absolute Maximum Ratings

(Over operating free-air temperature range unless otherwise noted.)

Parameter Rating

Supply voltage range, VDD, PVDD -0.3V to 6V

Input voltage range at SE/BTL, HP/LINE, SHUTDOWN, -0.3V to VDD

Operating ambient temperature range, TA -40°C to 85°C

Maximum junction temperature, TJ Internal Limited

ESD

STG

-65°C to 150°C

-3000 to 3000*1

-200 to 200*2

www.anpec.com.tw3

Storage temperature range, T

Soldering Temperature, 10 seconds, TS 260°C

Electrostatic Discharge, V

Power dissipation, PD Internal Limited

Note:

*1. Human body model: C=100pF, R=1500Ω, 3 positives pulse plus 3 negative pulses

*2. Machine model: C=200pF, L=0.5mH, 3 positive pulses plus 3 negative pulses

Copyright ANPEC Electronics Corp.

Rev. A.2 - Apr., 2004

APA2030/2031

Recommended Operating Conditions

Supply Voltage, VDD………………………………………………………………………….…………..4.5V to 5.5V

Thermal Characteristics

Symbol Parameter Value Unit

Thermal Resistance from Junction to Ambient in Free Air

R

* 5 in2 printed circuit board with 2oz trace and copper pad through 9 25mil diameter vias.

The thermal pad on the TSSOP_P package with solder on the printed circuit board.

THJA

TSSOP-P24*

TSSOP-P20*

Electrical Characteristics

(VDD=5V,-20°C<TA<85°C, unless otherwise noted.)

45

48

°C/W

Symbol Parameter Test Condition Min. Typ. Max. Unit

VDD Supply Voltage

IDD Supply current

Supply current in shutdown

ISD

mode

VIH High level threshold Voltage

VIL Low level threshold Voltage

II Input current

ICM

V

Common mode Input voltage

VOS Output differential voltage

PC_beep trigger level

SE/BTL = 0V 6 12 mA

SE/BTL = 5V

SHUTDOWN = 0V 50 300

SHUTDOWN, GAIN0, GAIN1 2 V

SE/BTL, HP/LINE

SHUTDOWN, GAIN0, GAIN1 0.8 V

SE/BTL, HP/LINE 3 V

SHUTDOWN, SE/BTL,

HP/LINE, GAIN0, GAIN1

3.3 5.5 V

4 8 mA

µA

4 V

5 nA

VDD-1.0 V

5 mV

1 Vp.p

Copyright ANPEC Electronics Corp.

Rev. A.2 - Apr., 2004

www.anpec.com.tw4

APA2030/2031

Electical Characteristics (Cont.)

Operating Characteristics, BTL mode

Vdd=5V, T

A=25°C, Rl=4

ΩΩ

, Gain=6dB, (Unless otherwise noted)

Ω

ΩΩ

Symbol Parameter Test Condition

THD=10%, Fin=1khz, RL=3Ω

THD=10%, Fin=1khz, RL=4Ω

PO Maximum output power

THD=10%, Fin=1khz, RL=8Ω

THD=1%, Fin=1khz, RL=3Ω

THD=1%, Fin=1khz, RL=4Ω

in

=1khz, RL=8Ω

THD+N

Total harmonic distortion plus

noise

PSRR Power ripple rejection ratio

xtalk Channel separation

HP/LINE input separation

S/N Signal to noise ratio

THD=1%, F

Po=1.1W, RL=4Ω Fin=1khz

Po=0.7W, RL=8Ω, Fin=1khz

Vin=0.2Vrms, Rl=8Ω,

Cb=0.47µf, f=120Hz

f=1khz, Cb=0.47µf,

f=1khz, Cb=0.47µf,

Po=1.1W, Rl=8Ω , A_weight

Operating Characteristics, SE mode ( for APA2030 only)

Vdd=5V, T

A=25°C, Rl=32

ΩΩ

Ω, Gain=4, 1dB, (Unless otherwise noted)

ΩΩ

Min. Typ. Max. Unit

2.6 W

2.3 W

1.5 W

1.9 W

1.7 W

1 1.1 W

0.05 %

0.04 %

85 dB

95 dB

80 dB

105 dB

Symbol Parameter Test Condition Min. Typ. Max. Unit

P

THD+N

Maximum output power

O

Total harmonic distortion plus

noise

PSRR Power ripple rejection ratio

THD=10%, Fin=1khz, RL=32Ω

THD=1%, Fin=1khz, RL=32Ω

Po=75mW, RL=32Ω .Fin=1khz

Vin=0.2Vrms, Rl=32Ω,

Cb=0.47µf, f=120,

110 mW

90 mW

0.03 %

55 dB

SE/BTL attenuation 80 dB

xtalk Channel separation

HP/LINE input separation

S/N Signal to noise ratio

Copyright ANPEC Electronics Corp.

Rev. A.2 - Apr., 2004

f=1khz, Cb=0.47µf,

f=1khz, Cb=0.47µf, BTL

Po=75mW, Rl=32Ω, A_weight,

65 dB

80 dB

100 dB

www.anpec.com.tw5

APA2030/2031

Pin Descriptions

APA2030

Pin name

GND

GAIN0 2 I/P

GAIN1 3 I/P

LOUT+ 4 O/P

LLINEIN 5 I/P

RLIN EIN 23 I/P

LHPIN 6 O/P

PVDD

RIN+ 8 I/P

LOUT- 9 O/P

LIN+ 10 I/P

BYPASS 11 -

PCBEEP 14 I/P PC-beep signal input

SE/BTL

ROUT- 16 O/P

HP/LINE 17 I/P

VDD 19 -

RHPIN 20 I/P

ROUT+ 21 O/P

SHUTDOWN

RLINEIN

APA2031

Pin name

GND

GAIN0 2 I/P

GAIN1 3 I/P

LOUT+ 4 O/P

LIN- 5 I/P

PVDD 6,15 -

RIN+ 7 I/P

LOUT- 8 O/P

LIN+ 9 I/P

BYPASS 10 -

NC 12 -

ROUT- 14 O/P

VDD 16 -

Copyright ANPEC Electronics Corp.

Rev. A.2 - Apr., 2004

Pin

Config. Function Description

no.

1,

12,

13,

24

7,

18

15 I/P

22 I/P

23 I/P

Pin

Config. Function Description

no.

1, 11,

13, 20

- Ground connection, Connected to thermal pad.

Input signal for internal gain setting

Input signal for internal gain setting

Left channel positive output in BTL mode and SE mode

Left channel line input terminal, selected when HP/LINE is held low.

Right channel line input terminal, selected when HP/LINE is held low.

Left channel headphone input terminal, selected when HP/LINE is held high.

- Supply voltage only for power amplifier

Right channel positive signal input, when differential signal is accepted.

Left channel negative output in BTL mode and high impedance in SE mode

Left channel positive signal input, when differential signal is accepted.

Bypass voltage

Output mode control input pin, high for SE output mode and low for BTL

mode

Right channel negative output in BTL mode and high impedance in SE

mode

Multi-input selection input, headphone mode when held high, line-in mode

when held low

Supply voltage for internal circuit excepting power amplifier.

Right channel headphone input terminal, selected when HP/LINE is held

high.

Right channel positive output in BTL mode and SE mode

It will be into shutdown m od e when pull low

Right channel line input terminal, selected when HP/LINE is held low

- Ground connection, Connected to thermal pad.

Input signal for internal gain setting

Input signal for internal gain setting

Left channel positive output

Left channel negative audio signal input

Supply voltage only for power amplifier

Right channel positive audio signal input

Left channel negative output

Left channel positive audio signal input

Bypass voltage

No connection

Right channel negative output

Supply voltage for internal circuit excepting power amplifier

www.anpec.com.tw6

APA2030/2031

Pin Description

APA2031

Pin name

RIN+ 17 I/P

ROUT+ 18 O/P

SHUTDOWN

Pin

Config. Function Description

no.

Right channel negative audio signal input

Right channel positive output

19 I/P It will be into shutdown mode when pull low

Control Input Table ( for APA2030 only)

HP/ LINE

X

L

H

L

H

X

SE/BTL

X L Disable Shutdown mode

L H Disable Line input, BTL out

L H Disable HP input, BTL out

H H Disable Line input, SE out

H H Disable HP input, SE out

X X Enable PCBEEP input, BTL out

SHUTDOWN

PCBEEP Operating mode

Gain Setting Table (for both APA2030 and APA2031)

GAIN0 GAIN1 Ri Rf Av

0 0

0 1

1 0

1 1

25.7KΩ 154.3KΩ

90KΩ 90KΩ

69KΩ 111KΩ

42KΩ 138KΩ

6dB

10dB

15.6dB

21.6dB

Copyright ANPEC Electronics Corp.

Rev. A.2 - Apr., 2004

www.anpec.com.tw7

APA2030/2031

Typical Application Circuit

(f

(for APA2030 using SE input signal)

L-LI NE

R-L INE

HP/LINE

Control Signal

SE/BTL Si gnal

L-HP

R-HP

0.47µF

0.47µF

100k

Ω

0.47µF

0.47µF

0.47µF

0.47µF

0.47µF

VDD

100kΩ

LLINEIN

LHPIN

LIN+

BYPASS

GAI N0

GAI N1

RLI NEI N

RHPI N

RIN+

HP/LINE

SE/BTL

DD

V

MUX

Gai n

selectable

MUX

HP/L INE

SE/BTL

VDD

0.1µF

GND

0Ω

100µF

PV

DD

Vbia s

Vbia s

LOUT+

LOUT-

ROUT+

4

4Ω

220µF

Ω

SE/BTL

Signal

220µF

1kΩ

Cont r ol

1kΩ

Ri ng

Pin

Tip

Headphone

Jack

Sle eve

Shutdown Signal

BEEP Signal

SHUTDOWN

PCBEEP

0.47µF

Copyright ANPEC Electronics Corp.

Rev. A.2 - Apr., 2004

Shutdown

ckt

PC-BEEP

ckt

ROUT-

APA2030AppCkt

APA 2030

www.anpec.com.tw8

APA2030/2031

Typical Application Circuit

(for APA2031 using SE input signal)

L-INPUT

R-INPUT

0.47µF

0.47µF

0.47µF

0.47µF

0.47µF

LIN-

LIN+

BYPASS

GAIN0

GAIN1

RIN-

RIN+

VDD

µ

0.1

VDD PVDDGND

Gain

selectable

Ω

0

F

100

µ

F

LOUT+

Vbias

Ω

4

LOUT-

ROUT +

Vbias

Ω

4

Shutdown

Signal

SHUTDOWN

Copyright ANPEC Electronics Corp.

Rev. A.2 - Apr., 2004

Shutdown

ckt

ROUT -

APA 2031

www.anpec.com.tw9

Loading...

Loading...