Evaluation Board User Guide

UG-393

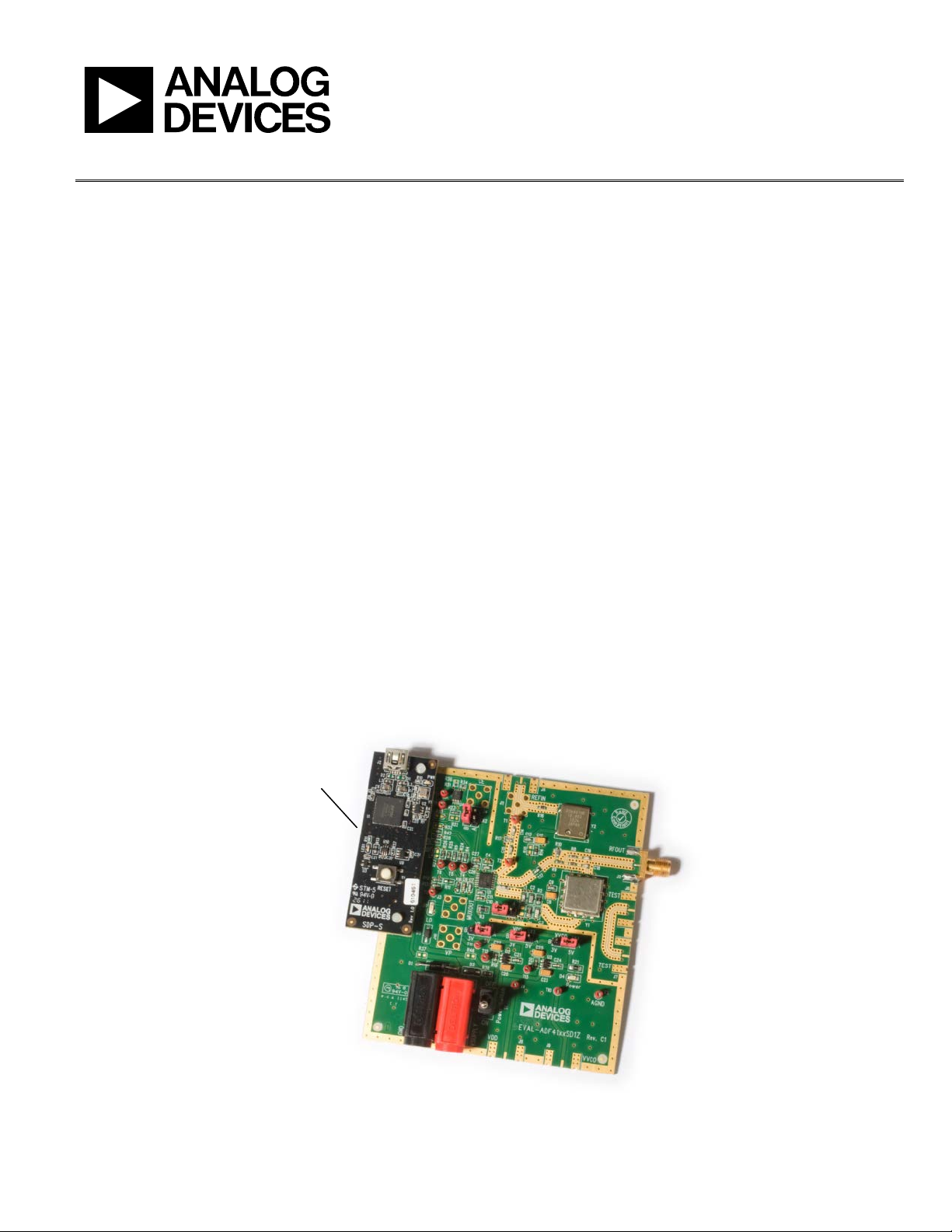

10621-001

SDP-S

(TO BE PURCHAS E D

SEPARATELY)

One Technology Way • P. O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

Evaluation Board for the ADF4157 Fractional-N PLL Frequency Synthesizer

FEATURES

Self-contained evaluation board, including frequency

synthesizer, VCO, TCXO for reference frequency, and

loop filter

Designed for 10 MHz PFD frequency, minimum charge pump

current, and a 20 kHz loop bandwidth

Accompanying software allows complete control of

synthesizer functions from a PC

EVALUATION KIT CONTENTS

EV-ADF4157SD1Z board

CD that includes

Self-installing software that allows users to control the

board and exercise all functions of the device

Electronic version of the ADF4157 data sheet

Electronic version of the UG-393 user guide

ADDITIONAL EQUIPMENT

PC running Windows XP or more recent version

SDP-S board (system demonstration platform, serial only)

Spectrum analyzer

Oscilloscope (optional)

DOCUMENTS NEEDED

ADF4157 data sheet

UG-393 user guide

REQUIRED SOFTWARE

Analog Devices Frac-N PLL software (Version 4 or higher)

ADIsimPLL

GENERAL DESCRIPTION

This evaluation board allows the user to evaluate the performance

of the ADF4157 frequency synthesizer for phase-locked loops

(PLLs). The SDP-S controller board allows software programming

of the frequency synthesizer. Figure 1 shows the board, which

contains the ADF4157 synthesizer, the power supplies, a TCXO

reference, and an RF output signal. There is also a loop filter

(20 kHz), a VCO (Z-Communications, Inc., V940ME03-LF),

and an external reference SMA input. The evaluation board is

set up for a 10 MHz PFD frequency.

Figure 1 shows the board with all necessary components inserted.

PLEASE SEE THE LAST PAGE FOR AN IMPORTANT

WARNING AND LEGAL TERMS AND CONDITIONS.

EVALUATION BOARD

Figure 1. EV-ADF4157SD1Z with SDP-S

Rev. 0 | Page 1 of 24

UG-393 Evaluation Board User Guide

TABLE OF CONTENTS

Features .............................................................................................. 1

Evaluation Kit Contents ................................................................... 1

Additional Equipment ..................................................................... 1

Documents Needed .......................................................................... 1

Required Software ............................................................................ 1

General Description ......................................................................... 1

Evaluation Board .............................................................................. 1

Revision History ............................................................................... 2

Quick Start Guide ............................................................................. 3

Evaluation Board Hardware ............................................................ 4

Power Supplies .............................................................................. 4

REVISION HISTORY

7/12—Revision 0: Initial Version

Input Signals...................................................................................4

Output Signals ...............................................................................4

Default Operation and Jumper Selection Settings ....................5

System Demonstration Platform (SDP) .....................................5

Evaluation Board Setup Procedure .................................................6

Installing the Frac-N PLL Software ............................................6

Evaluation Board Software ............................................................ 10

Evaluation and Test ........................................................................ 12

Evaluation Board Schematics and Artwork ................................ 13

Bill of Materials ............................................................................... 20

Related Links ................................................................................... 21

Rev. 0 | Page 2 of 24

Evaluation Board User Guide UG-393

QUICK START GUIDE

Follow these steps to evaluate the ADF4157 frequency synthesizer

after ensuring that the on-board links are correct with reference

to Table 1:

1. Install the Analog Devices Frac-N PLL software.

2. Connect the SDP-S motherboard to the PC and to the

EV-ADF4157SD1Z.

3. Follow the hardware driver installation procedure that

appears if you are using Windows® XP.

4. Connect the power supplies to banana connectors (6 V

to 12 V).

5. Run the Frac-N PLL software.

6. Select the SDP board and the ADF4157 device in the Select

Device and Connection tab of the main wi ndow.

7. Click the Main Controls tab, and then update all registers.

8. Connect the spectrum analyzer to J2.

9. Measure the results.

Rev. 0 | Page 3 of 24

UG-393 Evaluation Board User Guide

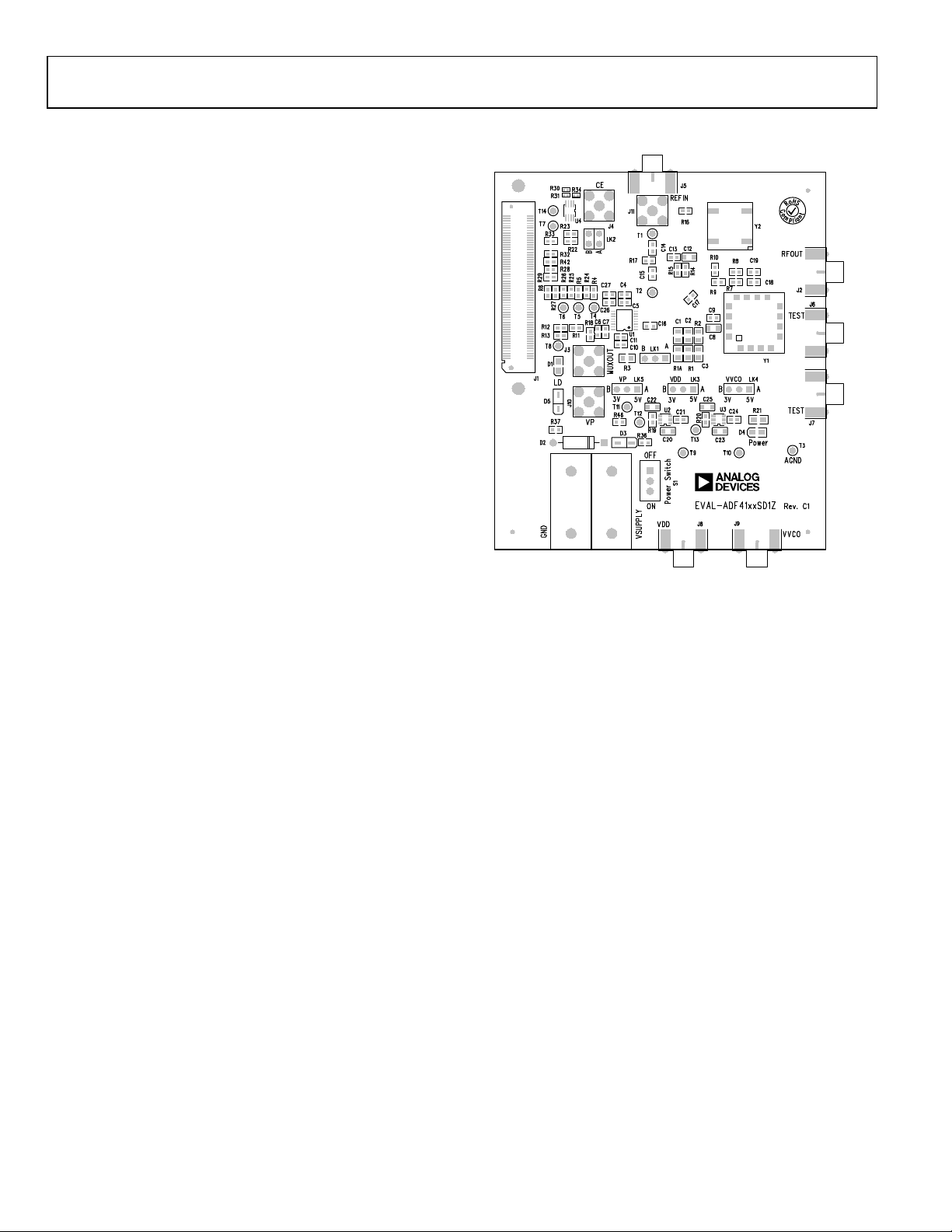

10621-002

EVALUATION BOARD HARDWARE

The evaluation board requires the use of an SDP-S motherboard to

program the device. The SDP-S is not included with the evaluation

board. The EV-ADF4157SD1Z schematics are shown in Figure 21

to Figure 23.

POWER SUPPLIES

The board is powered from external banana connectors. The

voltage can vary between 6 V and 12 V. The power supply circuit

provides 3.0 V to the V

to choose either 3.0 V or 5 V for the V

synthesizer. The default settings for V

respectively. Note that V

exceeding this voltage level may damage the device.

External power supplies can be used to directly drive the ADF4157

frequency synthesizer. In this case, the user must insert SMA

connectors as shown in Figure 2.

INPUT SIGNALS

A 10 MHz TCXO reference source from Fox Electronics is fitted

as the default option. An external reference generator can also be

used as the reference input. A low noise, high slew rate reference

source is required to achieve the specified performance of the

ADF4157 frequency synthesizer. An SMA connector fitted to

J11 can be connected to an external reference generator and

used as the reference source. Alternatively, the edge mount

connector, J5, can be inserted and used instead of J11. To use

any external reference option, remove the 0 Ω R16 and R14 links.

Digital SPI signals are supplied through the SDP connector, J1.

The SDP-S board is recommended. The SDP-Blackfin (SDP-B)

board can also be used, but Resistor R57 must be removed from

the SDP-B board. Some additional spurious low frequencies may

appear if the SDP-B connector is used.

of the ADF4157 and allows the user

DD

of the ADF4157 frequency

P

and VP are 3.0 V and 5 V,

DD

should never exceed 3.3 V because

DD

Figure 2. Evaluation Board Silkscreen

OUTPUT SIGNALS

All components necessary for local oscillator (LO) generation

are on the board. The PLL comprises the ADF4157 frequency

synthesizer, a passive loop filter, and the VCO. A 5.8 GHz VCO

from Z-Communications is supplied with the evaluation board.

A 20 kHz low-pass filter is inserted between the charge pump

output and the VCO input. The 0.31 mA charge pump current

setting is used. The VCO output is available at RFOUT through

a standard SMA connector, J2. The MUXOUT signal can be

monitored at Test Point T8 or at SMA Connector J3.

Rev. 0 | Page 4 of 24

Evaluation Board User Guide UG-393

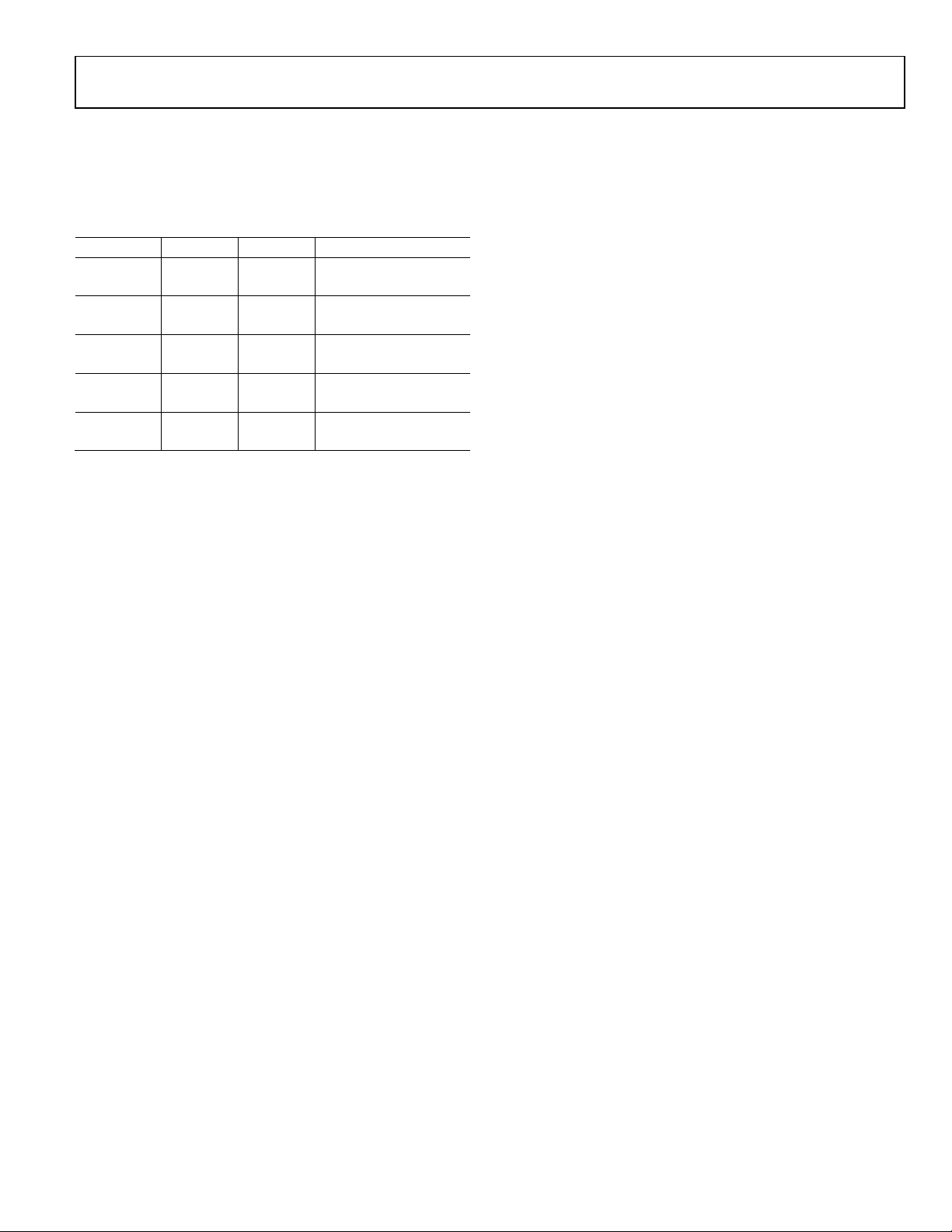

DEFAULT OPERATION AND JUMPER SELECTION SETTINGS

Link positions and their respective functions are outlined in

Table 1.

Table 1. Link Positions and Functions

Link Position Options Description

LK1 A R1A Not used

B RSET Normal operation

LK2 A GND Hardware power-down

B VDD Normal operation

LK3 (VDD) A 5 V Not used

B 3 V Normal operation

LK4 (V

B 3 V VCO supply (3 V)

LK5 (VP) A 5 V VP supply (5 V)

B 3 V VP supply (3 V)

) A 5 V VCO supply (5 V)

VCO

SYSTEM DEMONSTRATION PLATFORM (SDP)

The system demonstration platform (SDP) is a series of controller

boards, interposer boards, and daughter boards that can be

used for easy, low cost evaluation of Analog Devices, Inc.,

components and reference circuits. It is a reusable platform

whereby a single controller board can be reused in various

daughter board evaluation systems.

Controller boards connect to a PC via a USB 2.0 high speed port

and provide a range of communication interfaces on a 120-pin

connector. The pinout for this connector is strictly defined. A

receptacle for this 120-pin connector is included on all SDP

daughter boards, component evaluation boards, and Circuits

from the Lab® reference circuit boards. There are two controller

boards in the platform: the SDP-B, which is based on the Blackfin®

ADSP-BF527, and the SDP-S, which is a serial interface only

controller board. The SDP-S has a subset of the SDP-B functionality.

Interposer boards route signals between the SDP 120-pin connector and a second connector. When the second connector is

also a 120-pin connector, the interposer can be used for signal

monitoring of the 120-pin connector signals. Alternatively, the

second connector allows SDP platform elements to be integrated

into a second platform, for example, the BeMicro SDK. More

information on the SDP can be found at www.analog.com/sdp.

Rev. 0 | Page 5 of 24

UG-393 Evaluation Board User Guide

10621-003

10621-004

10621-005

EVALUATION BOARD SETUP PROCEDURE

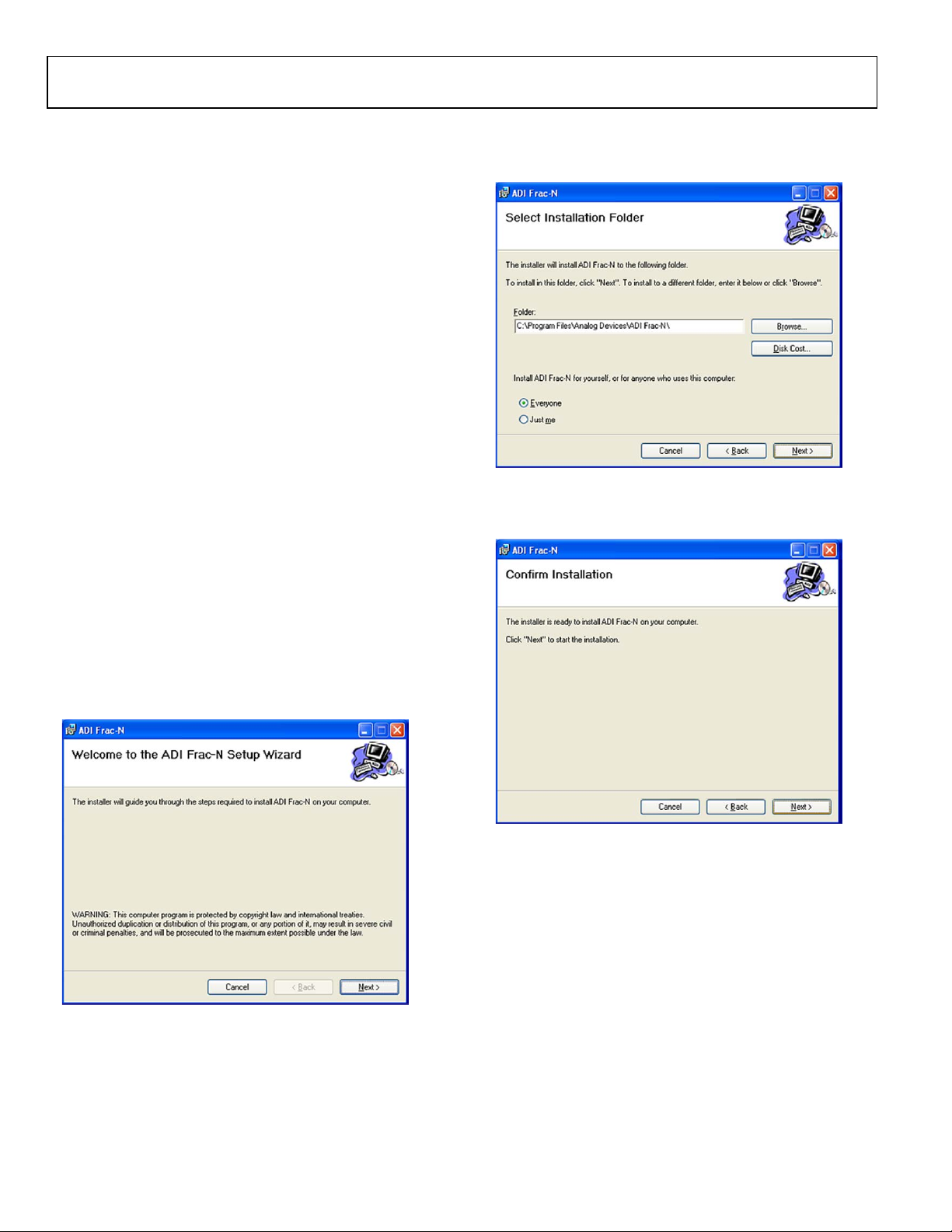

INSTALLING THE FRAC-N PLL SOFTWARE

Use the following steps to install the SDP drivers and the Analog

Devices Frac-N PLL software.

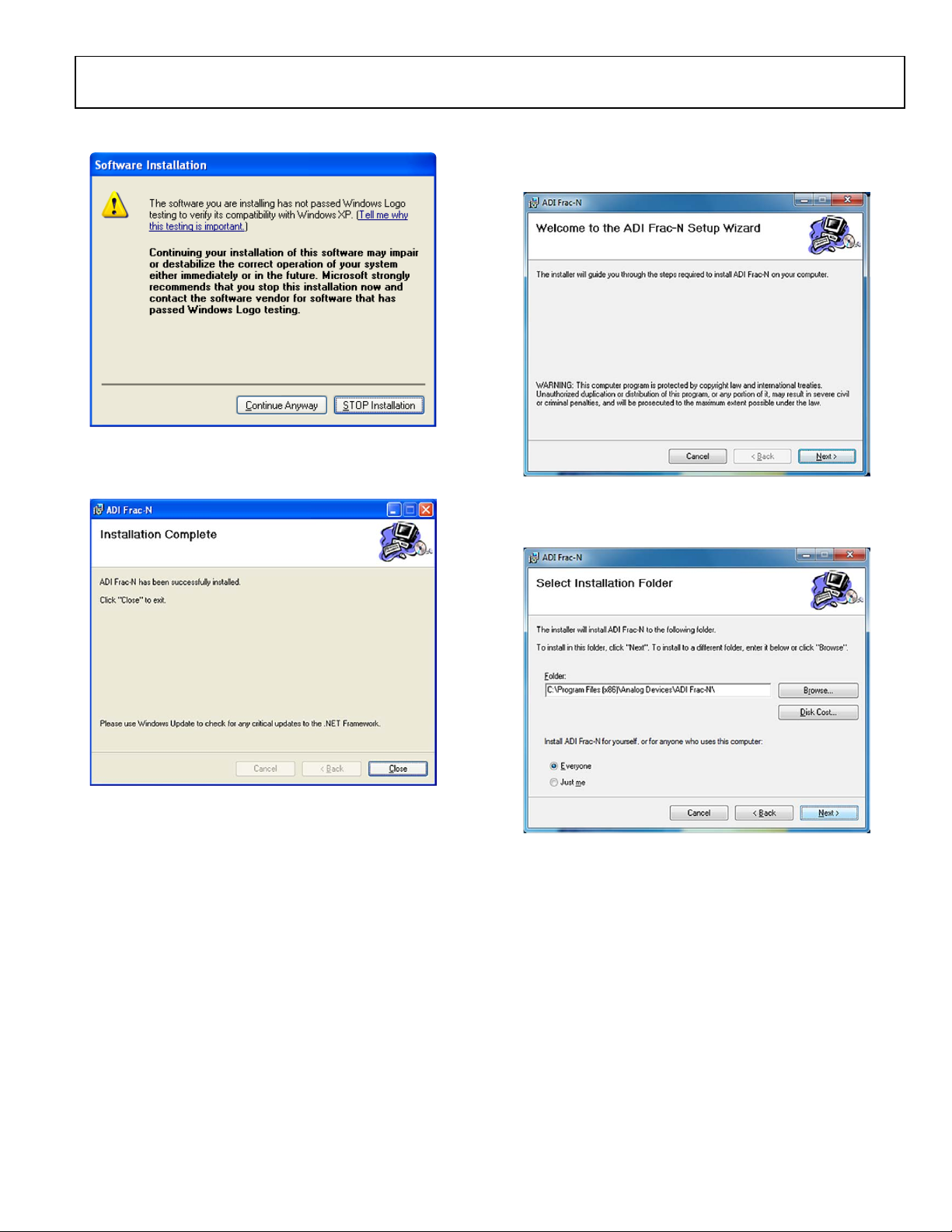

1. Install the Frac-N PLL software by double-clicking

ADI_PLL_Frac-N_Setup.msi.

If you are using Windows XP, follow the instructions in

the Windows XP Frac-N PLL Software Installation Guide

section (see Figure 3 to Figure 7).

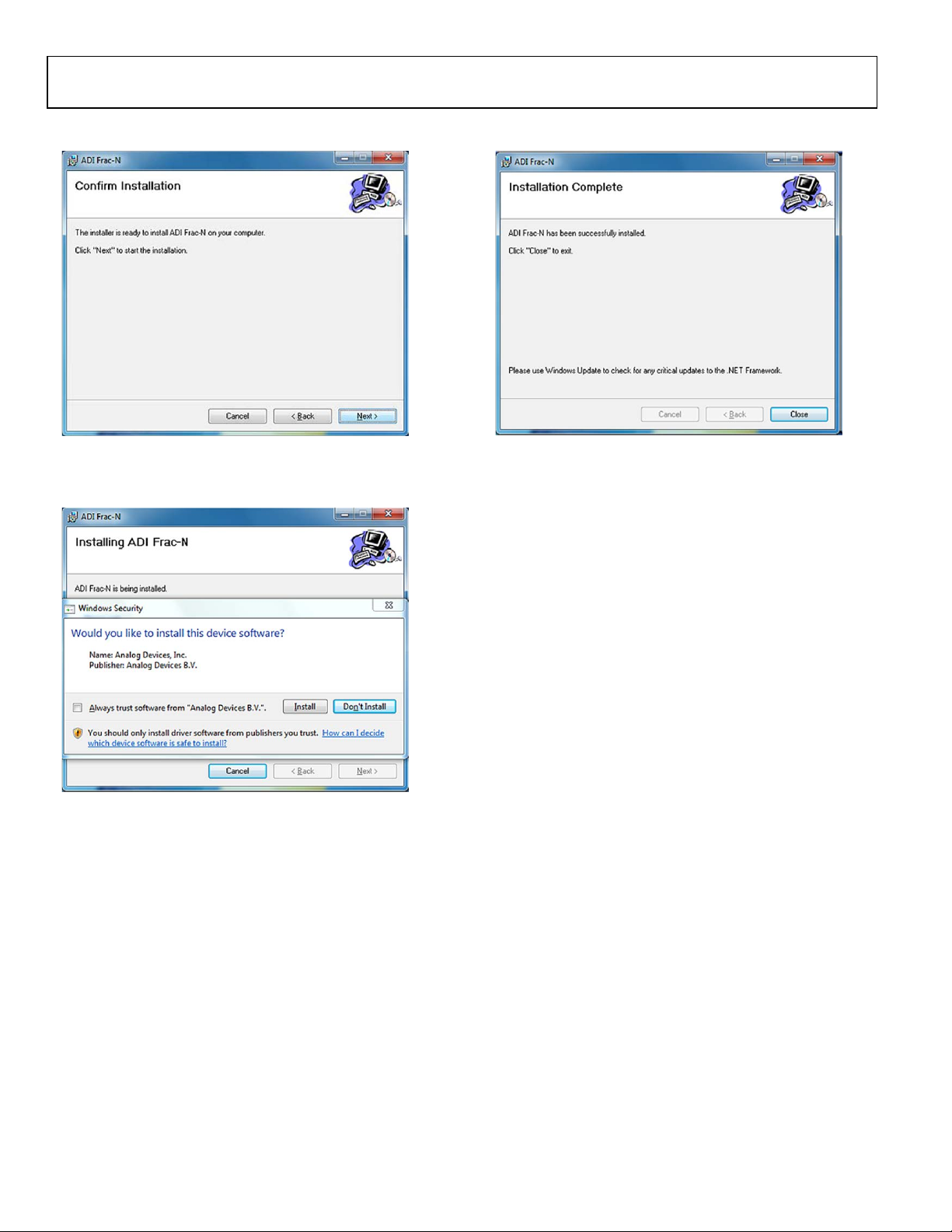

If you are using Windows Vista or Windows 7, follow the

instructions in the Windows Vista and Windows 7 Frac-N

PLL Software Installation Guide section (see Figure 8 to

Figure 12).

Note that the software requires Microsoft Windows

Installer and Microsoft .NET Framework 3.5 (or higher).

The installer connects to the Internet and downloads

Microsoft .NET Framework automatically. Alternatively,

before running ADI_PLL_Frac-N_Setup.msi, both the

installer and .NET Framework can be installed from the

CD provided in the evaluation board kit.

2. Connect your SDP board (black) to a PC using the supplied

USB cable.

If you are using Windows XP, follow the steps in the Windows

XP SDP-S Board Driver Installation Guide section (see

Figure 13 to Figure 16).

If you are using Windows Vista or Windows 7, the drivers

install automatically.

2. Choose an installation directory and click Next.

Figure 4. Windows XP Frac-N PLL Software Installation,

Select Installation Folder

3. Click Next.

Windows XP Frac-N PLL Software Installation Guide

1. Click Next.

Figure 3. Windows XP Frac-N PLL Software Installation,

Setup Wizard

Figure 5. Windows XP Frac-N PLL Software Installation,

Confirm Installation

Rev. 0 | Page 6 of 24

Evaluation Board User Guide UG-393

10621-006

10621-007

10621-008

10621-009

4. Click Continue Anyway.

Windows Vista and Windows 7 Frac-N PLL Software Installation Guide

1. Click Next.

Figure 6. Windows XP Frac-N PLL Software Installation,

5. Click Close.

Figure 7. Windows XP Frac-N PLL Software Installation,

Logo Testing

Figure 8. Windows Vista/Windows 7 Frac-N PLL Software Installation,

Setup Wizard

2. Choose an installation directory and click Next.

Installation Complete

Figure 9. Windows Vista/Windows 7 Frac-N PLL Software Installation,

Select Installation Folder

Rev. 0 | Page 7 of 24

UG-393 Evaluation Board User Guide

10621-010

10621-011

10621-012

3. Click Next.

5. Click Close.

Figure 10. Windows Vista/Windows 7 Frac-N PLL Software Installation,

Confirm Installation

4. Click Install.

Figure 11. Windows Vista/Windows 7 Frac-N PLL Software Installation,

Start Installation

Figure 12. Windows Vista/Windows 7 Frac-N PLL Software Installation,

Installation Complete

Rev. 0 | Page 8 of 24