Quick Start Guide

V

V

UG-378

One Technology Way • P. O . Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel : 781.329.4700 • Fax : 781.461.3113 • www.analog.com

Overview of AD5110/AD5112/AD5114 Connections and Functionality

GENERAL DESCRIPTION

This quick start guide provides a general overview of AD5110/

AD5112/AD5114 connections and functionality and should be

reviewed in conjunction with the AD5110/AD5112/AD5114

data sheet.

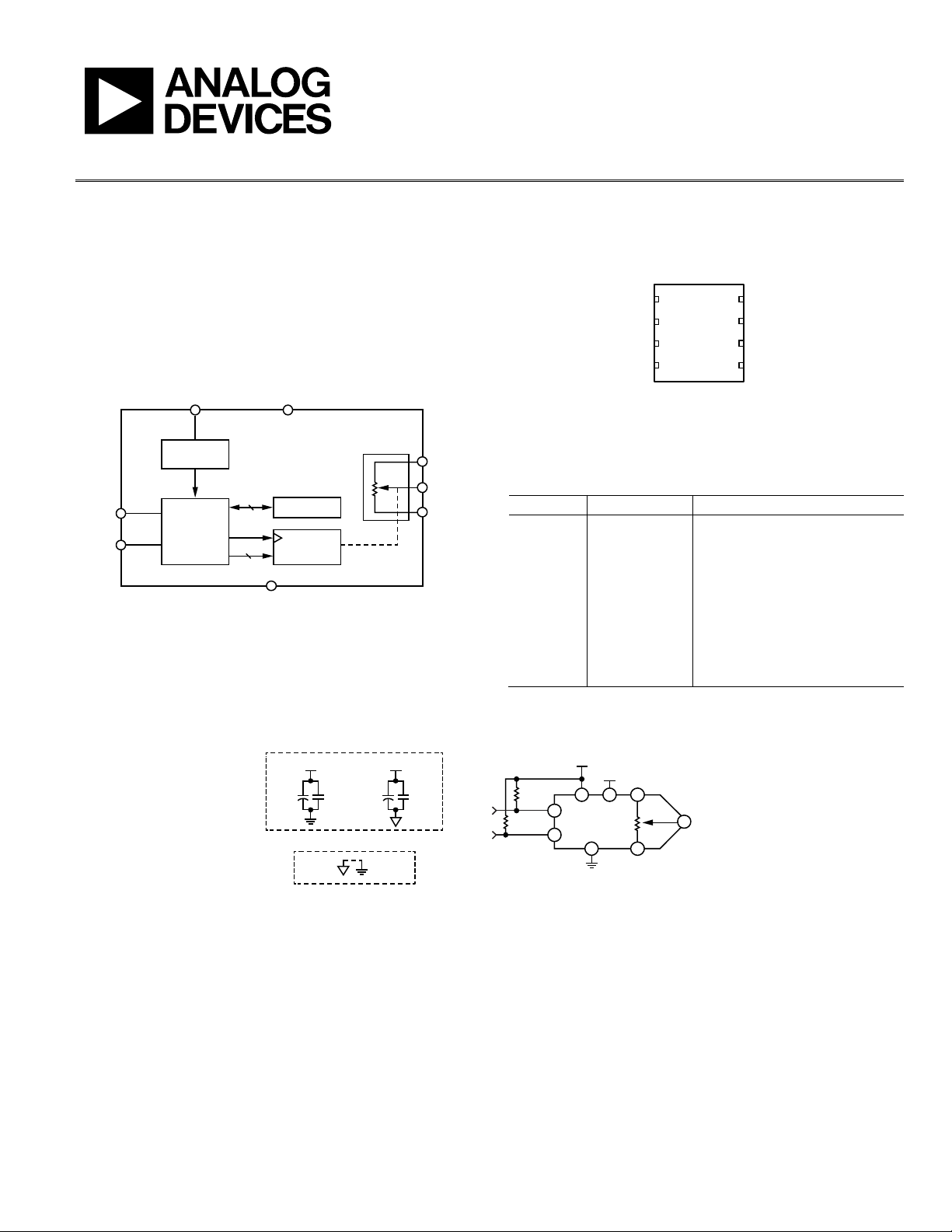

FUNCTIONAL BLOCK DIAGRAM

LOGIC

POWER-ON

RESET

SDA

SCL

2

I

SERIAL

INTERFACE

DATA

C

DATA

DD

AD5110/AD5112/AD5114

EEPROM

RDAC

REGISTER

GND

Figure 1.

TYPICAL EXTERNAL CONNECTIONS

SUPPLIES

V

DD

++

GROUNDS

DIGITAL

GND

V

LOGIC

ANALOG

GND

A

W

B

0.1µF0.1µF10µF 10µF

10547-001

SCL

SDA

Figure 3.

PIN CONFIGURATION

1V

DD

NOTES

1. THE EXPOSED PAD IS INTERNALLY FLOATING.

2A

3W

4B

AD5110/

AD5112/

AD5114

TOP VIEW

(Not to Scale)

Figure 2.

8V

LOGIC

7SDA

6SCL

5GND

PIN FUNCTION DESCRIPTIONS

Table 1.

Pin No. Mnemonic Description

1 VDD Positive power supply.

2 A Terminal A of RDAC.

3 W Wiper terminal of RDAC.

4 B Terminal B of RDAC.

5 GND Ground pin.

6 SCL Serial clock line.

7 SDA Serial data line.

8 V

EPAD Internally floating exposed pad.

V

LOGIC

2.2kΩ

6

2.2kΩ

7

Logic power supply.

LOGI C

V

DD

A

2

18

3

w

4

5

B

10547-003

10547-002

PLEASE SEE THE LAST PAGE FOR AN IMPORTANT

WARNING AND LEGAL TERMS AND CONDITIONS.

Rev. 0 | Page 1 of 4

UG-378 Quick Start Guide

OPERATIONAL CONDITIONS

Table 2. Specifications

Parameter Specification

VDD to GND 2.3 V to 5.5 V

V

to GND 1.8 V to VDD

LOGI C

VA, VW, VB to GND GND to VDD

Maximum Continuous IA, IW, IB

RAW = 5 kΩ and 10 kΩ ±6 mA

RAW = 80 kΩ ±1.5 mA

Maximum Clock (SCL) 400 kHz

Table 3. Device Address Selection

Model 7-Bit I2C Device Address

AD511X1 BCPZ Y2 0101111

AD511X1 BCPZ Y2-1 0101100

1

Model.

2

Resistance.

SHIFT REGISTER AND TIMING DIAGRAM

191 9 91

SCL

SDA

START BY

MASTER

111A1A0 C2C1

FRAME 1

SERIAL BUS ADDRESS BYTE

R/W0 000000

ACK. BY

AD5110

MOST SIGNIFICANT DATA BYTE

FRAME 2

C0 D7 D6 D5 D4 D3 D2 D1 D0

ACK. BY

AD5110

LEAST SIGNIFICANT DATA BYTE

FRAME 3

ACK. BY STOP BY

AD5110 MASTER

Figure 4. Write Sequence

COMMANDS

Table 4. Command Operation Truth Table

Command Data

Command

Number

DB10 DB8 DB7 DB0

C2 C1 C0 D7 D6 D5 D4 D3 D2 D1 D0

0 0 0 0 X X X X X X X X No operation

1 0 0 1 X X X X X X X X Write contents of RDAC register to EEPROM

2 0 1 0 0

6

5 4 3 2 1

MSB

1 0 0 0 0 0 0 0 Top scale

1 1 1 1 1 1 1 1 Bottom scale

3 0 1 1 X X X X X X X A0 Software shutdown

4 1 0 0 X X X X X X X X Software reset: refresh RDAC register with EEPROM

5 1 0 1 X X X X X X X X Read contents of RDAC register

6 1 1 0 X X X X X X A1 A0 Read contents of EEPROM

1

X is a don’t care.

2

In the AD5114, this bit is a don’t care.

3

In the AD5112, this bit is a don’t care.

1

Operation

2

2, 3

Write contents of serial register data to RDAC

0

LSB

Shutdown off

Shutdown on

A1 A0 Data

0 0 Wiper position saved

0 1 Resistor tolerance

10547-004

Rev. 0 | Page 2 of 4

Loading...

Loading...