Next Generation OP07 Ultralow

V

V

FEATURES

Outstanding gain linearity

Ultrahigh gain, 5000 V/mV min

Low V

Excellent TCV

High PSRR, 3 μV/V max

Low power consumption, 60 mW max

Fits OP07, 725,108A/308A, 741 sockets

Available in die form

over temperature, 55 μV max

OS

, 0.3 μV/°C max

OS

Offset Voltage Operational Amplifier

OP77

PIN CONNECTIONS

1

OS

TRIM

–IN

+IN

V–

OP77

2

3

TOP VIEW

4

(Not to S cale)

NC = NO CONNECT

Figure 1. 8-Pin Hermetic

DIP_Q-8 (Z Suffix)

OS

TRIM V+

V

OS

1

OP77

–IN OUT

3

+IN NC

4V– (CASE)

TOP VIEW

(Not to Scale)

NC = NO CONNECT

Figure 2. TO-99

(J Suffix)

TRIM

8

4

8

7

6

5

7

5

VOS TRIM

V+

OUT

NC

62

00320-001

00320-002

GENERAL DESCRIPTION

The OP77 significantly advances the state-of-the-art in

precision op amps. The outstanding gain of 10,000,000 or more

for the OP77 is maintained over the full 10 V output range. This

exceptional gain-linearity eliminates incorrectable system

nonlinearities common in previous monolithic op amps and

provides superior performance in high closed-loop gain

applications. Low initial V

combined with only 50 mW of power consumption, are

significant improvements over previous designs. These

characteristics, plus the exceptional TCV

maximum and the low V

drift and rapid stabilization time,

OS

of 0.3 μV/°C

OS

of 25 μV maximum, eliminates the

OS

need for V

adjustment and increases system accuracy over

OS

temperature.

A PSRR of 3 μV/V (110 dB) and CMRR of 1.0 μV/V maximum

virtually eliminate errors caused by power supply drifts and

common-mode signals. This combination of outstanding

characteristics makes the OP77 ideally suited for high resolution

instrumentation and other tight error budget systems.

Rev. E

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2002–2010 Analog Devices, Inc. All rights reserved.

OP77

TABLE OF CONTENTS

Features .............................................................................................. 1

Pin Connections ............................................................................... 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Electrical Specifications ............................................................... 3

Wafer Test Limits .......................................................................... 4

Typical Electrical Characteristics ............................................... 5

Absolute Maximum Ratings ............................................................ 6

REVISION HISTORY

4/10—Rev. D to Rev. E

Removed Figure 33 and Two Subsequent Paragraphs ............... 12

6/09—Rev. C to Rev. D

Changes to Figure 1 and Figure 2 ................................................... 1

Changes to Table 1 ............................................................................ 3

Removed Endnote 1 and Endnote 2 in Table 3 ............................ 4

Changes to Figure 16 ........................................................................ 9

Changes to Figure 31 and Figure 32 ............................................. 12

Changes to Figure 38 ...................................................................... 14

Moved Figure 39 ............................................................................. 14

10/02—Rev. B to Rev. C

Edits to Specifications ...................................................................... 2

Figure 2 Caption Changed ............................................................ 10

Figure 3 Caption Changed ............................................................ 10

Edits to Figure 10 ............................................................................ 11

Updated Outline Dimensions ....................................................... 15

2/02—Rev. A to Rev. B

Remove 8-Lead SO PIN Connection Diagrams ........................... 1

Changes to Absolute Maximum Rating ......................................... 2

Remove OP77B column from Specifications ................................ 2

Remove OP77B column from Electrical Characteristics ........ 3, 5

Remove OP77G column from Wafer Test Limits ......................... 6

Remove OP77G column from Typical Electrical Characteristics6

Thermal Resistance .......................................................................6

ESD Caution...................................................................................6

Typical Performance Characteristics ..............................................7

Test Circuits ..................................................................................... 10

Applications ..................................................................................... 11

Precision Current Sinks ............................................................. 12

Outline Dimensions ....................................................................... 15

Ordering Guide .......................................................................... 16

Rev. E | Page 2 of 16

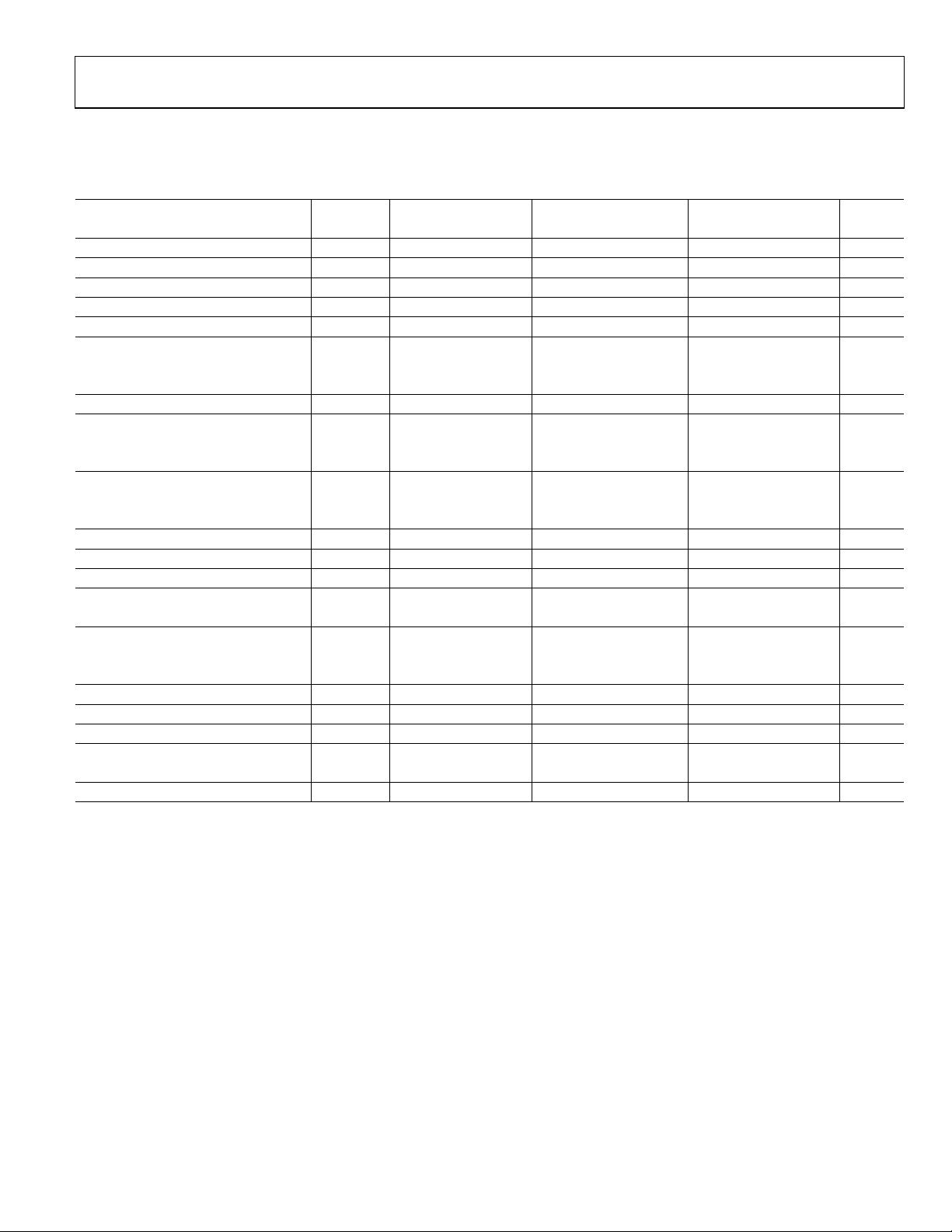

OP77

ELECTRICAL SPECIFICATIONS

@ VS = ±15 V, TA = 25°C, unless otherwise noted.

Table 1.

OP77E OP77F

Parameter Symbol Conditions Min Typ Max Min Typ Max Unit

INPUT OFFSET VOLTAGE VOS 10 25 20 60 μV

LONG-TERM STABILITY1 V

INPUT OFFSET CURRENT IOS 0.3 1.5 0.3 2.8 nA

INPUT BIAS CURRENT IB −0.2 +1.2 +2.0 −0.2 +1.2 +2.8 nA

INPUT NOISE VOLTAGE2 e

INPUT NOISE VOLTAGE DENSITY en fO = 10 Hz 10.3 18.0 10.5 20.0 nV/√Hz

f

f

INPUT NOISE CURRENT2 i

INPUT NOISE CURRENT DENSITY in fO = 10 Hz 0.32 0.80 0.35 0.90 pA√Hz

f

f

INPUT RESISTANCE

Differential Mode3 R

Common Mode R

INPUT VOLTAGE RANGE IVR ±13 ±14 ±13 ±14 V

COMMON-MODE REJECTION RATIO CMRR VCM = ±13 V 0.1 1.0 0.1 1.6 μV/V

POWER SUPPLY REJECTION RATIO PSRR VS = ±3 V to ±18 V 0.7 3.0 0.7 3.0 μV/V

LARGE-SIGNAL VOLTAGE GAIN AVO RL ≥ 2 kΩ 5000 12,000 2000 6000 V/mV

V

OUTPUT VOLTAGE SWING VO RL ≥ 10 kΩ ±13.5 ±14.0 ±13.5 ±14.0 V

R

R

SLEW RATE2 SR RL ≥ 2 kΩ 0.1 0.3 0.1 0.3 V/μs

CLOSED-LOOP BANDWIDTH2 BW A

OPEN-LOOP OUTPUT RESISTANCE RO 60 60 Ω

POWER CONSUMPTION Pd VS = ±15 V, no load 50 60 50 60 mW

V

OFFSET ADJUSTMENT RANGE Rp = 20 kn ±3 ±3 mV

1

Long-term input offset voltage stability refers to the averaged trend line of VOS vs. time over extended periods after the first 30 days of operation. Excluding the initial

hour of operation, changes in V

2

Sample tested.

3

Guaranteed by design.

during the first 30 operating days are typically 2.5 μV.

OS

/time 0.3 0.4 μV/Mo

OS

0.1 Hz to 10 Hz 0.35 0.6 0.38 0.65 μV

np-p

= 100 Hz2 10.0 13.0 10.2 13.5

O

= 1000 Hz 9.6 11.0 9.8 11.5

O

0.1 Hz to 10 Hz 14 30 15 35 pA

np-p

= 100 Hz2 0.14 0.23 0.15 0.27

O

= 1000 Hz 0.12 0.17 0.13 0.18

O

26 45 18.5 45 MΩ

IN

200 200 GΩ

INCM

= ±10 V

O

≥ 2 kΩ ±12.5 ±13.0 ±12.5 ±13.0

L

≥ 1 kΩ ±12.0 ±12.5 ±12.0 ±12.5

L

+ 1 0.4 0.6 0.4 0.6 MHz

VCL

= ±3 V, no load 3.5 4.5 3.5 4.5

S

p-p

p-p

Rev. E | Page 3 of 16

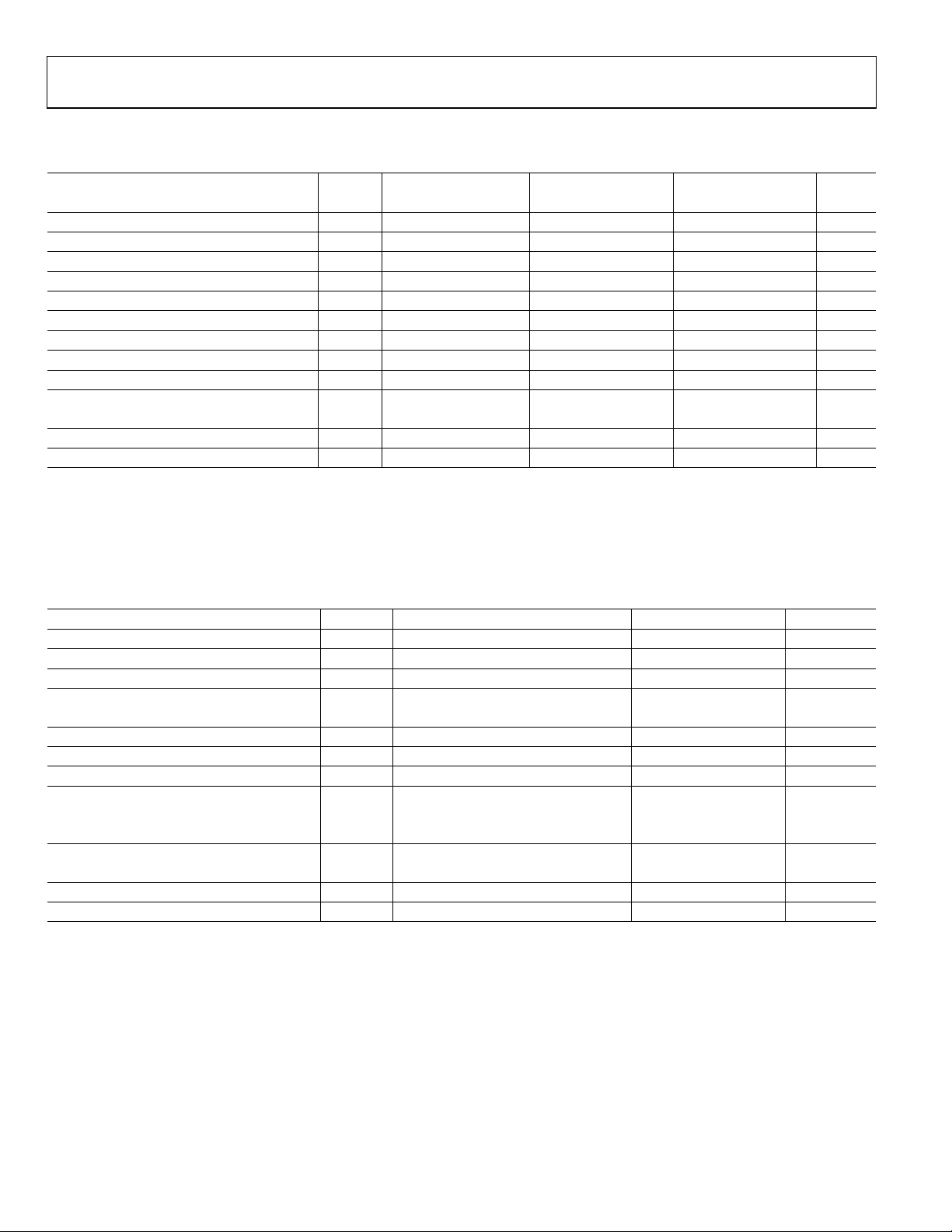

OP77

@ VS = ±15 V, −25°C ≤ TA ≤ +85°C for OP77FJ and OP77E/OP77F, unless otherwise noted.

Table 2.

OP77E OP77F

Parameter Symbol Conditions Min Typ Max Min Typ Max Unit

INPUT OFFSET VOLTAGE VOS 10 45 20 100 μV

AVERAGE INPUT OFFSET VOLTAGE DRIFT1 TCVOS 0.1 0.3 0.2 0.6 μV/°C

INPUT OFFSET CURRENT IOS 0.5 2.2 0.5 4.5 nA

AVERAGE INPUT OFFSET CURRENT DRIFT2 TCI

INPUT BIAS CURRENT IB −0.2 +2.4 +4.0 −0.2 +2.4 +6.0 nA

AVERAGE INPUT BIAS CURRENT DRIFT2 TCIB 8 40 15 60 pA/°C

INPUT VOLTAGE RANGE IVR ±13.0 ±13.5 ±13.0 ±13.5 V

COMMON-MODE REJECTION RATIO CMRR VCM = ±13 V 0.1 1.0 0.1 3.0 pV/V

POWER SUPPLY REJECTION RATIO PSRR VS = ±3 V to ±18 V 1.0 3.0 1.0 5.0 μV/V

LARGE-SIGNAL VOLTAGE GAIN A

V

OUTPUT VOLTAGE SWING VO RL ≥ 2 kΩ ±12 ±13.0 ±12 ±13.0 V

POWER CONSUMPTION Pd VS = ±15 V, no load 60 75 60 75 mW

1

OP77E: TCVOS is 100% tested on J and Z packages.

2

Guaranteed by end-point limits.

1.5 4.0 1.5 85 pA/°C

OS

R

VO

≥ 2 kΩ 2000 6000 1000 4000 V/mV

L

= ±10 V

O

WAFER TEST LIMITS

@ VS = ±15 V, TA = 25°C, for OP77NBC devices, unless otherwise noted.

Table 3.

Parameter Symbol Conditions OP77NBC Limit Unit

INPUT OFFSET VOLTAGE V

INPUT OFFSET CURRENT I

INPUT BIAS CURRENT IB ±2 nA max

INPUT RESISTANCE

Differential Mode RIN 26 MΩ min

INPUT VOLTAGE RANGE IVR ±13 V min

COMMON-MODE REJECTION RATIO CMRR VCM = ±13 V 1 μV/V max

POWER SUPPLY REJECTION RATIO PSRR VS = ±3 V to ±18 V 3 μV/V max

OUTPUT VOLTAGE SWING VO RL = 10 kΩ ±13.5 V min

R

R

LARGE-SIGNAL VOLTAGE GAIN AVO RL = 2 kΩ 2000 V/mV min

V

DIFFERENTIAL INPUT VOLTAGE ±30 V max

POWER CONSUMPTION Pd VO = 0 V 60 mW max

40 μV max

OS

2.0 nA max

OS

= 2 kΩ ±12.5

L

= 1 kΩ ±12.0

L

= ±10 V

O

Rev. E | Page 4 of 16

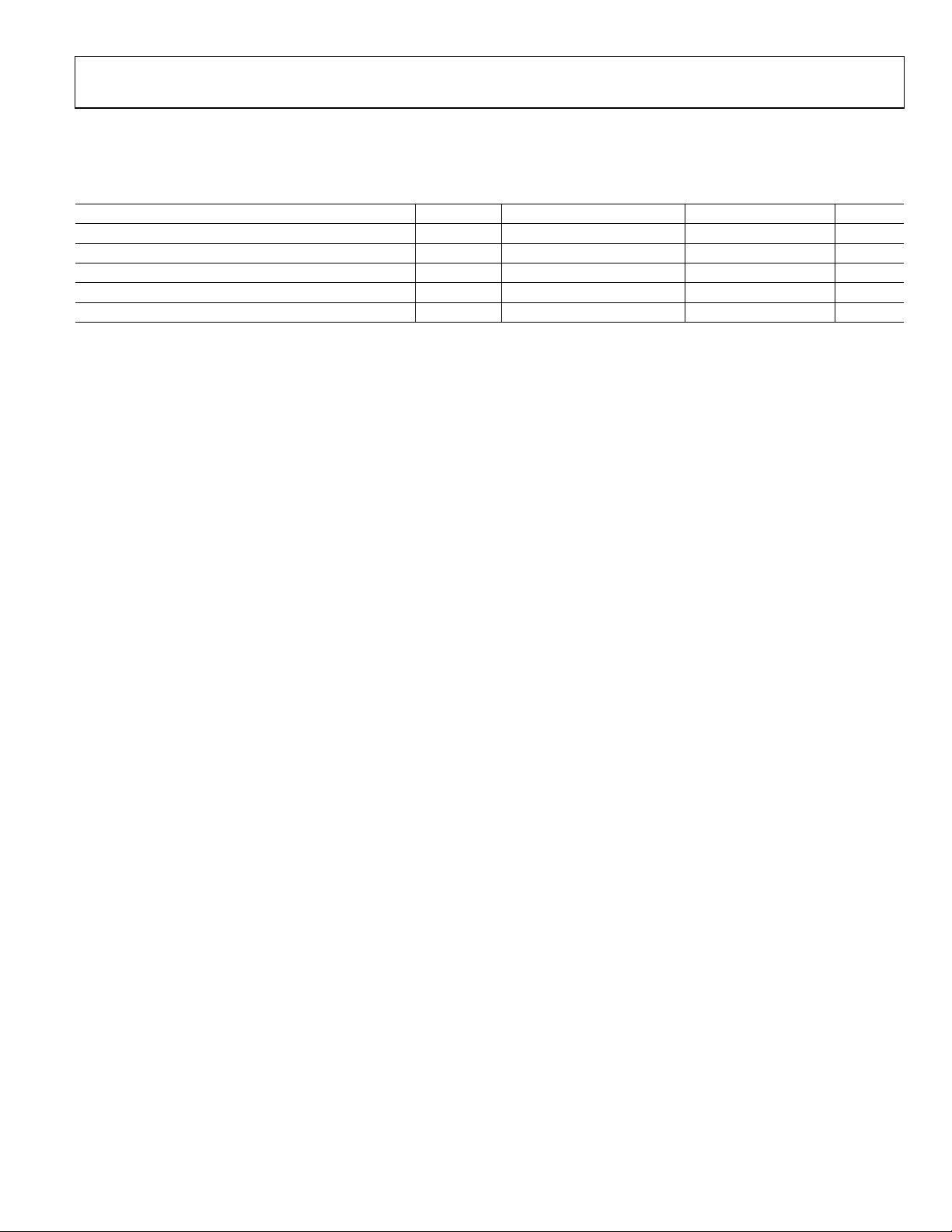

OP77

TYPICAL ELECTRICAL CHARACTERISTICS

@ VS = ±15 V, TA = 25°C, unless otherwise noted.

Table 4.

Parameter Symbol Conditions OP77NBC Limit Unit

AVERAGE INPUT OFFSET VOLTAGE DRIFT TCVOS RS = 50 Ω 0.1 μV/°C

NULLED INPUT OFFSET VOLTAGE DRIFT TCV

AVERAGE INPUT OFFSET CURRENT DRIFT TCIOS 0.5 pA/°C

SLEW RATE SR RL ≥ 2 kΩ 0.3 V/μs

BANDWIDTH BW A

RS = 50 Ω, RP = 20 kΩ 0.1 μV/°C

OSn

+ 1 0.6 MHz

VCL

Rev. E | Page 5 of 16

Loading...

Loading...