Analog Devices OP491, OP291, OP191 Datasheet

Micropower Single-Supply

NC = NO CONNECT

1

2

3

4

8

7

6

5

OP191

OUTA

V+

NC

NC

NC

–INA

+INA

–V

1

2

3

4

8

7

6

5

OP191

1

2

3

4

5

6

7

14

13

12

11

10

9

8

OP491

OUTD

–IND

+IND

–V

+INC

–INC

OUTC

OUTA

–INA

+INA

+V

+INB

–INB

OUTB

1

2

3

4

5

6

7

14

13

12

11

10

9

8

OP491

OUTD

–IND

+IND

–V

+INC

–INC

OUTC

OUTA

–INA

+INA

+V

+INB

–INB

OUTB

1

2

5

6

7

3

4

14

13

10

9

8

12

11

OP491

a

Rail-to-Rail Input/Output Op Amps

FEATURES

Single-Supply Operation: 2.7 V to 12 V

Wide Input Voltage Range

Rail-to-Rail Output Swing

Low Supply Current: 300 µA/Amp

Wide Bandwidth: 3 MHz

Slew Rate: 0.5 V/µs

Low Offset Voltage: 700 µV

No Phase Reversal

APPLICATIONS

Industrial Process Control

Battery Powered Instrumentation

Power Supply Control and Protection

Telecom

Remote Sensors

Low Voltage Strain Gage Amplifiers

DAC Output Amplifier

GENERAL DESCRIPTION

The OP191, OP291 and OP491 are single, dual and quad

micropower, single-supply, 3 MHz bandwidth amplifiers featuring rail-to-rail inputs and outputs. All are guaranteed to

operate from a 3 volt single supply as well as ± 5 volt dual

supplies.

Fabricated on Analog Devices’ CBCMOS process, the OP191

family has a unique input stage that allows the input voltage to

safely extend 10 volts beyond either supply without any phase

inversion or latch-up. The output voltage swings to within

millivolts of the supplies and continues to sink or source

current all the way to the supplies.

Applications for these amplifiers include portable telecom

equipment, power supply control and protection, and interface

for transducers with wide output ranges. Sensors requiring a

rail-to-rail input amplifier include Hall effect, piezo electric,

and resistive transducers.

The ability to swing rail-to-rail at both the input and output

enables designers to build multistage filters in single-supply

systems and maintain high signal-to-noise ratios.

The OP191/OP291/OP491 are specified over the extended

industrial (–40°C to +125°C) temperature range. The OP191

single and OP291 dual amplifiers are available in 8-pin plastic

DIPs and SO surface mount packages. The OP491 quad is

available in 14-pin DIPs and narrow 14-pin SO packages.

Consult factory for OP491 TSSOP availability.

OP191/OP291/OP491

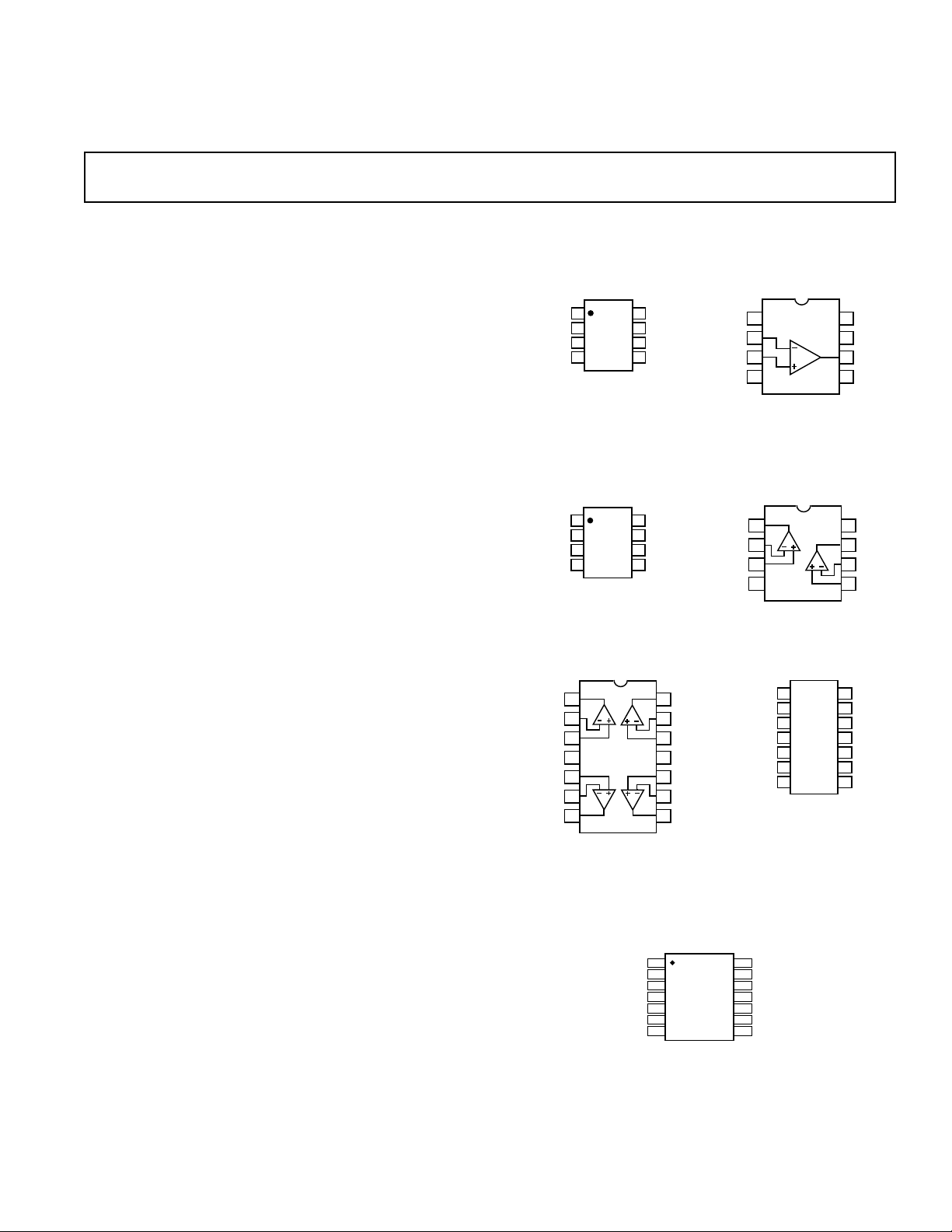

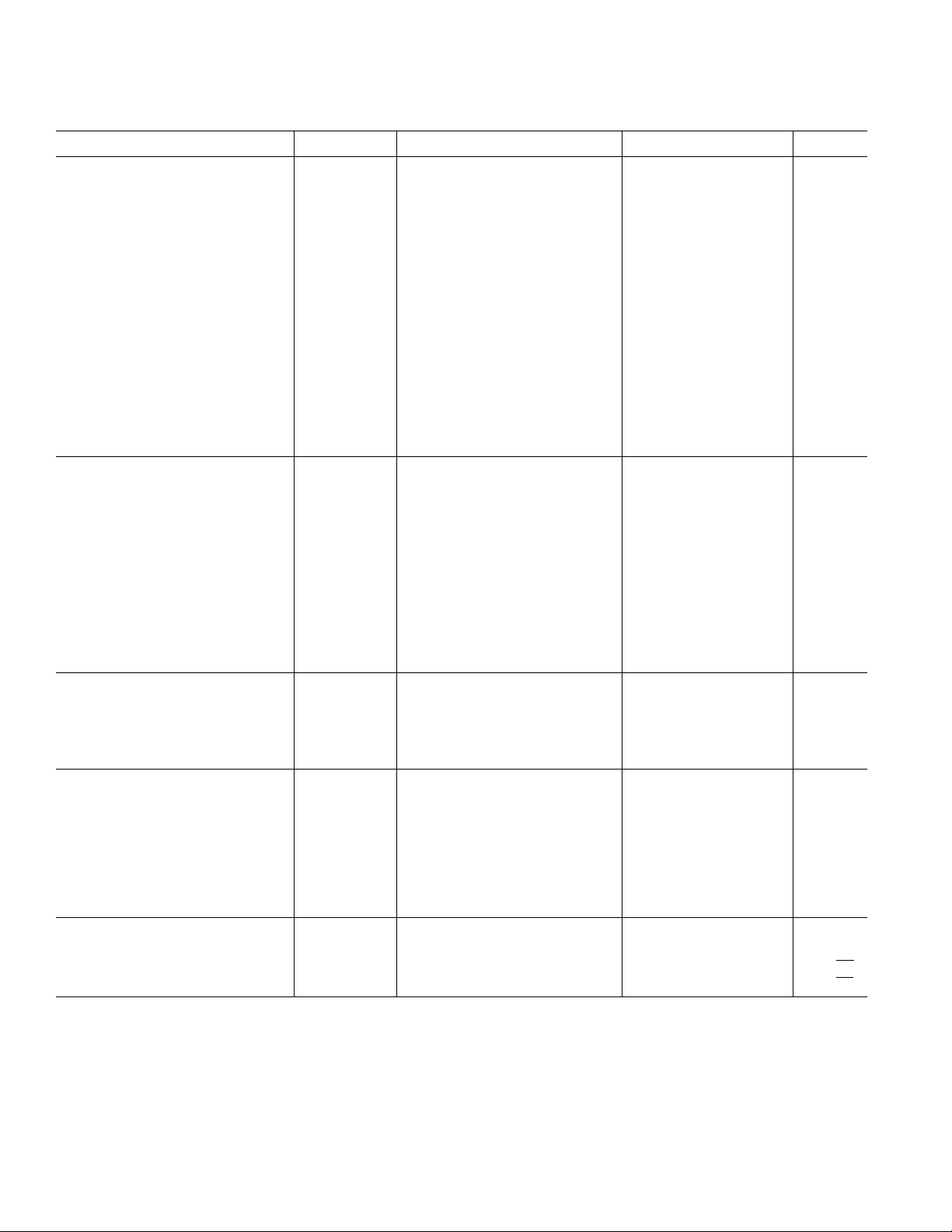

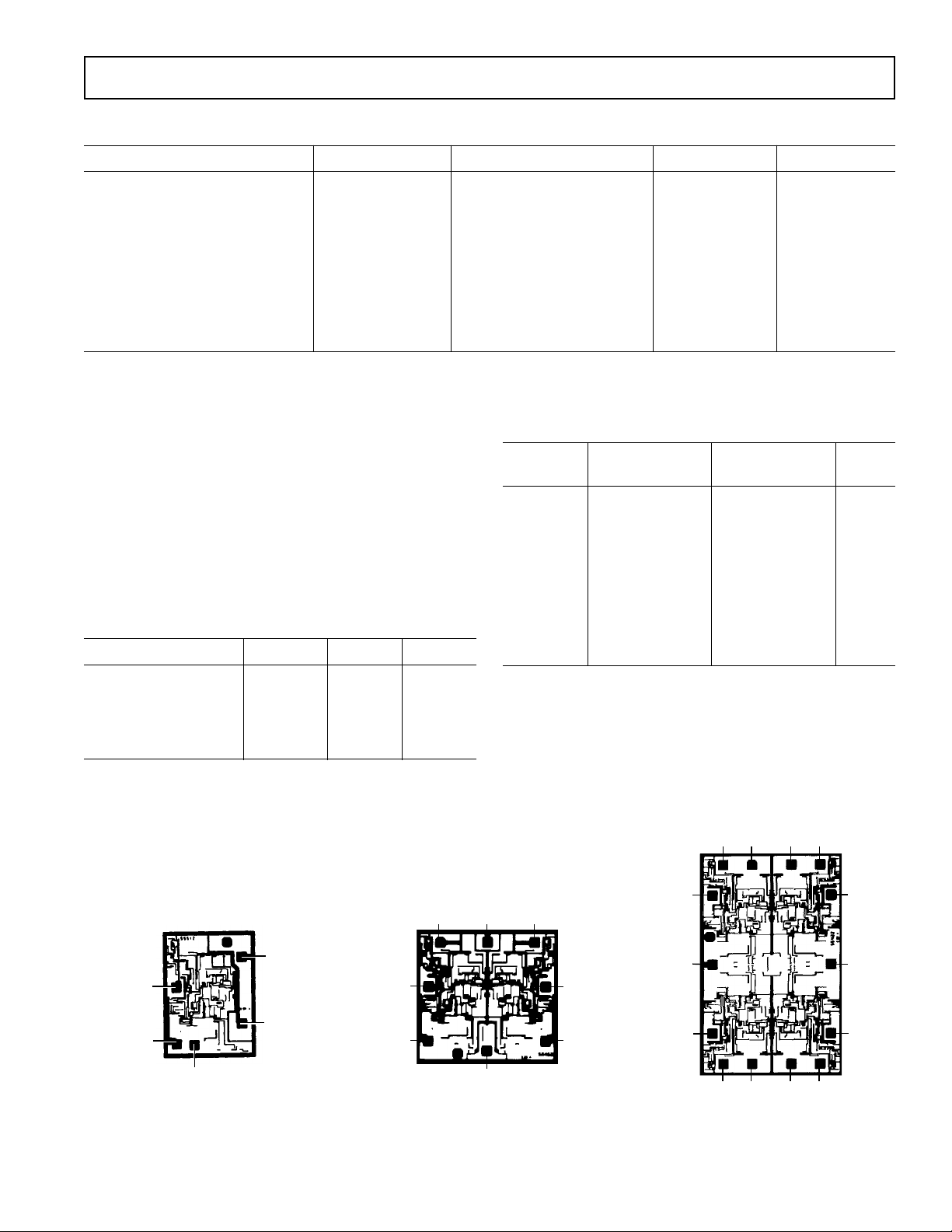

OP191/OP291/OP491 PIN CONFIGURATIONS

8-Lead Narrow-Body SO 8-Lead Epoxy DIP

(S Suffix) (P Suffix)

8-Lead Narrow-Body SO 8-Lead Epoxy DIP

(S Suffix) (P Suffix)

1

2

OP291

3

4

14-Lead Epoxy DIP 14-Lead SO

(P Suffix) (S Suffix)

8

7

6

5

14-Lead

TSSOP

(RU Suffix)

OUTA

–INA

+INA

1

OP291

2

3

4

–V

+V

8

OUTB

7

–INB

6

+INB

5

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood. MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

OP191/OP291/OP491–SPECIFICA TIONS

ELECTRICAL SPECIFICATIONS

(@ VS = +3.0 V, VCM = 0.1 V, VO = 1.4 V, TA = +25°C unless otherwise noted)

Parameter Symbol Conditions Min Typ Max Units

INPUT CHARACTERISTICS

Offset Voltage OP191G V

OP291/OP491G V

Input Bias Current I

Input Offset Current I

B

OS

OS

OS

–40 ≤ T

–40 ≤ T

–40 ≤ T

–40 ≤ T

≤ +125°C1mV

A

≤ +125°C 1.25 mV

A

≤ +125°C70nA

A

≤ +125°C16nA

A

80 500 µV

80 700 µV

30 50 nA

0.1 8 nA

Input Voltage Range 0 3 V

Common-Mode Rejection Ratio CMRR V

Large Signal Voltage Gain A

Offset Voltage Drift ∆V

Bias Current Drift ∆I

VO

/∆T 1.1 µV/°C

OS

/∆T 100 pA/°C

B

= 0 V to 2.9 V 70 90 dB

CM

–40 ≤ T

≤ +125°C6587dB

A

RL = 10 kΩ , VO = 0.3 V to 2.7 V 25 70 V/mV

–40 ≤ T

≤ +125°C 50 V/mV

A

Offset Current Drift ∆IOS/∆T 20 pA/°C

OUTPUT CHARACTERISTICS

Output Voltage High V

OH

RL = 100 kΩ to GND 2.95 2.99 V

–40°C to +125°C 2.90 2.98 V

R

= 2 kΩ to GND 2.8 2.9 V

L

–40°C to +125°C 2.70 2.8 V

Output Voltage Low V

OL

RL = 100 kΩ to V+ 4.5 10 mV

–40°C to +125°C35mV

R

= 2 kΩ to V+ 40 75 mV

L

–40°C to +125°C 130 mV

Short Circuit Limit I

SC

Sink/Source ± 8.75 ±13.5 mA

–40°C to +125°C ±6.0 ±10.5 mA

Open Loop Impedance Z

OUT

f = 1 MHz, AV = 1 200 Ω

POWER SUPPLY

Power Supply Rejection Ratio PSRR V

Supply Current/Amplifier I

SY

= 2.7 V to 12 V 80 110 dB

S

–40°C ≤ T

≤ +125°C 75 110 dB

A

VO = 0 V 200 350 µA

–40°C ≤ TA ≤ +125°C 330 480 µA

DYNAMIC PERFORMANCE

Slew Rate +SR R

Slew Rate –SR R

Full-Power Bandwidth BW

Settling Time t

P

S

= 10 kΩ 0.4 V/µs

L

= 10 kΩ 0.4 V/µs

L

1% Distortion 1.2 kHz

To 0.01% 22 µs

Gain Bandwidth Product GBP 3 MHz

Phase Margin θ

O

45 Degrees

Channel Separation CS f = 1 kHz, RL = 10 kΩ 145 dB

NOISE PERFORMANCE

Voltage Noise e

Voltage Noise Density e

Current Noise Density i

Specifications subject to change without notice.

p-p 0.1 Hz to 10 Hz 2 µV p-p

n

n

n

f = 1 kHz 35 nV/√Hz

0.8 pA/√Hz

–2–

REV. 0

OP191/OP291/OP491

ELECTRICAL SPECIFICATIONS

(@ VS = +5.0 V, VCM = 0.1 V, VO = 1.4 V, TA = +25°C unless otherwise noted)

Parameter Symbol Conditions Min Typ Max Units

INPUT CHARACTERISTICS

Offset Voltage OP191 V

OP291/OP491 V

Input Bias Current I

Input Offset Current I

B

OS

OS

OS

–40 ≤ T

–40 ≤ T

–40 ≤ T

–40 ≤ T

≤ +125°C 1.0 mV

A

≤ +125°C 1.25 mV

A

≤ +125°C60nA

A

≤ +125°C16nA

A

80 500 µV

80 700 µV

30 50 nA

0.1 8 nA

Input Voltage Range 0 5 V

Common-Mode Rejection Ratio CMRR V

Large Signal Voltage Gain A

Offset Voltage Drift ∆V

Bias Current Drift ∆I

VO

/∆T –40 ≤ TA ≤ +125°C 1.1 µV/°C

OS

/∆T 100 pA/°C

B

= 0 V to 4.9 V 70 93 dB

CM

–40 ≤ T

≤ +125°C6590dB

A

RL = 10 kΩ , VO = 0.3 V to 4.7 V 25 70 V/mV

–40 ≤ T

≤ +125°C 50 V/mV

A

Offset Current Drift ∆IOS/∆T 20 pA/°C

OUTPUT CHARACTERISTICS

Output Voltage High V

OH

RL = 100 kΩ to GND 4.95 4.99 V

–40°C to +125°C 4.90 4.98 V

R

= 2 kΩ to GND 4.8 4.85 V

L

–40°C to +125°C 4.65 4.75 V

Output Voltage Low V

OL

RL = 100 kΩ to V+ 4.5 10 mV

–40°C to +125°C35mV

R

= 2 kΩ to V+ 40 75 mV

L

–40°C to +125°C 155 mV

Short Circuit Limit I

SC

Sink/Source ± 8.75 ±13.5 mA

–40°C to +125°C ±6.0 ±10.5 mA

Open Loop Impedance Z

OUT

f = 1 MHz, AV = 1 200 Ω

POWER SUPPLY

Power Supply Rejection Ratio PSRR V

Supply Current/Amplifier I

SY

= 2.7 V to 12 V 80 110 dB

S

–40 ≤ T

≤ +125°C 75 110 dB

A

VO = 0 V 220 400 µA

–40 ≤ TA ≤ +125°C 350 500 µA

DYNAMIC PERFORMANCE

Slew Rate +SR R

Slew Rate –SR R

Full-Power Bandwidth BW

Settling Time t

P

S

= 10 kΩ 0.4 V/µs

L

= 10 kΩ 0.4 V/µs

L

1% Distortion 1.2 kHz

To 0.01% 22 µs

Gain Bandwidth Product GBP 3 MHz

Phase Margin θ

O

45 Degrees

Channel Separation CS f = 1 kHz, RL = 10 kΩ 145 dB

NOISE PERFORMANCE

Voltage Noise e

Voltage Noise Density e

Current Noise Density i

NOTES

+5 V specifications are guaranteed by +3 V and ±5 V testing.

Specifications subject to change without notice.

REV. 0

p-p 0.1 Hz to 10 Hz 2 µV p-p

n

n

n

f = 1 kHz 35 nV/√Hz

0.8 pA/√Hz

–3–

OP191/OP291/OP491

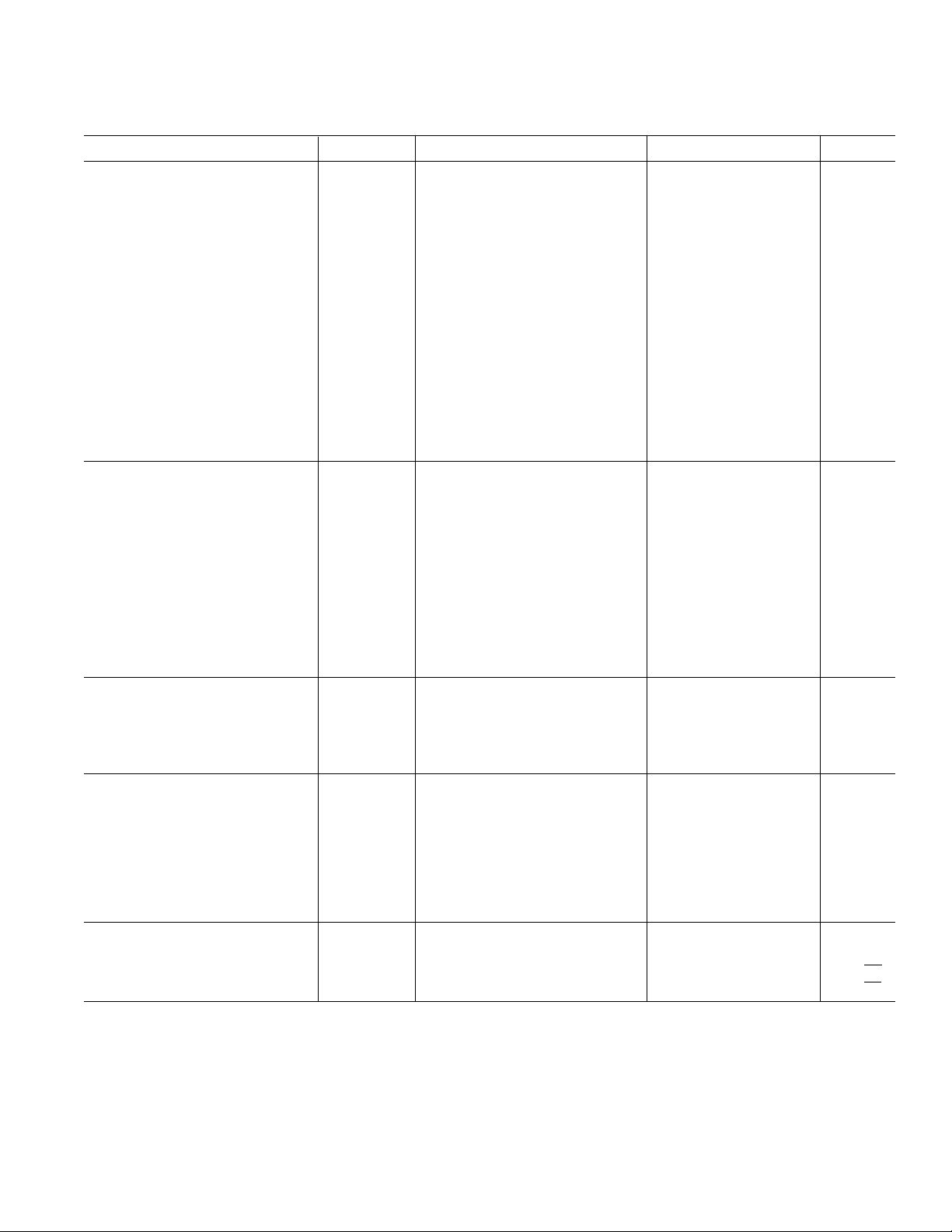

ELECTRICAL SPECIFICATIONS

(@ VO = ±5.0 V, –4.9 V ≤ VCM ≤ +4.9 V, TA = +25°C unless otherwise noted)

Parameter Symbol Conditions Min Typ Max Units

INPUT CHARACTERISTICS

Offset Voltage OP191 V

OP291/OP491 V

Input Bias Current I

Input Offset Current I

B

OS

OS

OS

–40 ≤ T

–40 ≤ T

–40 ≤ T

–40 ≤ T

≤ +125°C1mV

A

≤ +125°C 1.25 mV

A

≤ +125°C70nA

A

≤ +125°C16nA

A

80 500 µV

80 700 µV

30 50 nA

0.1 8 nA

Input Voltage Range –5 +5 V

Common-Mode Rejection CMR V

Large Signal Voltage Gain A

Offset Voltage Drift ∆V

Bias Current Drift ∆I

VO

/∆T 1.1 µV/°C

OS

/∆T 100 pA/°C

B

= ±5 V 75 100 dB

CM

–40 ≤ T

≤ +125°C6797dB

A

RL = 10 kΩ, VO = ±4.7 V, 25 70

–40 ≤ T

≤ +125°C 50 V/mV

A

Offset Current Drift ∆IOS/∆T 20 pA/°C

OUTPUT CHARACTERISTICS

Output Voltage Swing V

O

RL = 100 kΩ to GND ±4.93 ±4.99 V

–40°C to +125°C ±4.90 ±4.98 V

R

= 2 kΩ to GND ±4.80 ±4.95 V

L

Short Circuit Limit I

SC

–40 ≤ T

Sink/Source ± 8.75 ±16 mA

≤ +125°C ±4.65 ±4.75 V

A

–40°C to +125°C ±6 ±13 mA

Open Loop Impedance Z

OUT

f = 1 MHz, AV = 1 200 Ω

POWER SUPPLY

Power Supply Rejection Ratio PSRR V

Supply Current/Amplifier I

SY

= ±5 V 80 110 dB

S

–40 ≤ T

≤ +125°C 70 100 dB

A

VO = 0 V 260 420 µA

–40 ≤ TA ≤ +125°C 390 550 µA

DYNAMIC PERFORMANCE

Slew Rate ±SR R

Full-Power Bandwidth BW

Settling Time t

P

S

=10 kΩ 0.5 V/µs

L

1% Distortion 1.2 kHz

To 0.01% 22 µs

Gain Bandwidth Product GBP 3 MHz

Phase Margin θ

O

45 Degrees

Channel Separation CS f = 1 kHz 145 dB

NOISE PERFORMANCE

Voltage Noise e

Voltage Noise Density e

Current Noise Density i

Specifications subject to change without notice.

p-p 0.1 Hz to 10 Hz 2 µV p-p

n

n

n

INPUT

OUTPUT

f = 1 kHz 35 nV/√Hz

0.8 pA/√Hz

5V

100

90

10

0%

5V

VS = ±5V

R

= 2kΩ

L

A

= +1

V

V

= 20Vp-p

I

N

200µs

Figure 1. Input and Output with Inputs Overdriven by 5 V

–4–

REV. 0

OP191/OP291/OP491

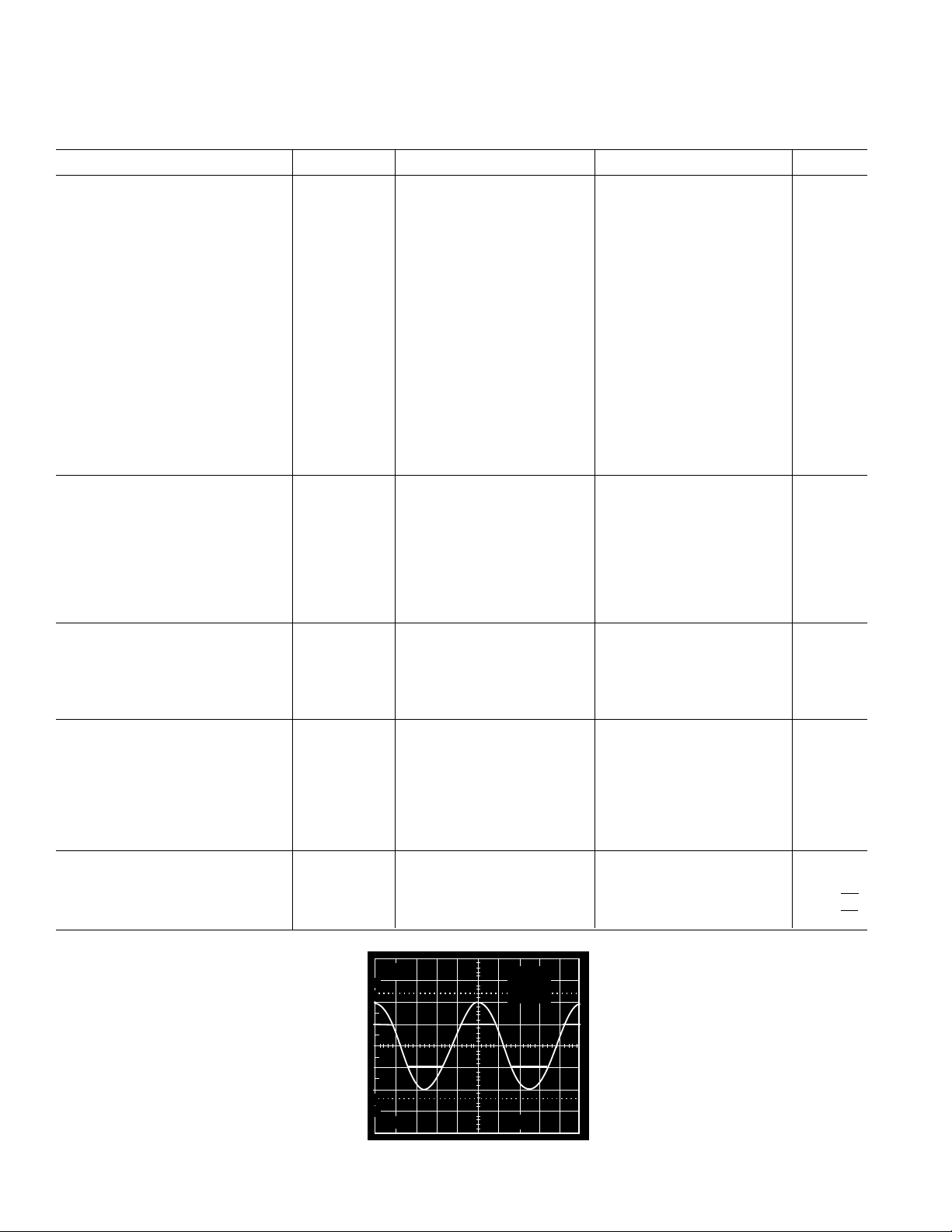

W AFER TEST LIMITS

(@ VS = +3.0 V, VCM = 0.1 V, TA = +25°C unless otherwise noted)

Parameter Symbol Conditions Limit Units

Offset Voltage V

Input Bias Current I

Input Offset Current I

Input Voltage Range V

OS

B

OS

CM

Common-Mode Rejection Ratio CMRR V

= 0 V to +2.9 V 70 dB min

CM

±300 µV max

50 nA max

8nA

V– to V+ V min

Power Supply Rejection Ratio PSRR V = 2.7 V to +12 V 80 dB min

Large Signal Voltage Gain A

Output Voltage High V

Output Voltage Low V

Supply Current/Amplifier I

NOTE

Electrical tests and wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard

product dice. Consult factory to negotiate specifications based on dice lot qualifications through sample lot assembly and testing.

ABSOLUTE MAXIMUM RATINGS

VO

OH

OL

SY

1

RL = 10 kΩ 50 V/mV min

RL = 2 kΩ to GND 2.8 V min

RL = 2 kΩ to V+ 75 mV max

VO = 0 V, RL = ∞ 350 µA max

ORDERING GUIDE

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +16 V

Input Voltage . . . . . . . . . . . . . . . . . . . . . . . .GND to V

+ 10 V

S

Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . .7 V

Output Short-Circuit Duration to GND . . . . . . . . . .Indefinite

Storage Temperature Range

P, S, RU Packages . . . . . . . . . . . . . . . . . . .–65°C to +150°C

Operating Temperature Range

OP191/OP291/OP491G . . . . . . . . . . . . . . .–40°C to +125°C

Junction Temperature Range

P, S, RU Packages . . . . . . . . . . . . . . . . . . .–65°C to +150°C

Lead Temperature Range (Soldering60sec) . . . . . . . . +300°C

Package Type θ

2

JA

θ

JC

Units

Model Range Description Option

OP191GP –40°C to +125°C 8-Pin Plastic DIP N-8

OP191GS –40°C to +125°C 8-Pin SOIC SO-8

OP191GBC +25°C DICE

OP291GP –40°C to +125°C 8-Pin Plastic DIP N-8

OP291GS –40°C to +125°C 8-Pin SOIC SO-8

OP291GBC +25°C DICE

OP491GP –40°C to +125°C 14-Pin Plastic DIP N-14

OP491GS –40°C to +125°C 14-Pin SOIC SO-14

OP491HRU –40°C to +125°C 14-Pin TSSOP RU-14

OP491GBC +25°C DICE

Temperature Package Package

8-Pin Plastic DIP (P) 103 43 °C/W

8-Pin SOIC (S) 158 43 °C/W

14-Pin Plastic DIP (P) 76 33 °C/W

14-Pin SOIC (S) 120 36 °C/W

14-Pin TSSOP (RU) 180 35 °C/W

NOTES

1

Absolute maximum ratings apply to both DICE and packaged parts, unless

otherwise noted.

2

θJA is specified for the worst case conditions; i.e., θ

for P-DIP packages; θ

and SOIC packages.

is specified for device soldered in circuit board for TSSOP

JA

is specified for device in socket

JA

2

14 13

1

DICE CHARACTERISTICS

7

2

6

3

4

OP191 Die Size 0.047 × 0.066 Inch,

3,102 Sq. Mils. Substrate (Die Backside) Is Connected to V+.

Transistor Count, 74.

REV. 0

1

1

212

2

3

3

3

8

8

8

7

7

7

6

6

6

5

5

5

4

4

4

OP291 Die Size 0.070 × 0.070 Inch,

4,900 Sq. Mils. Substrate (Die Backside) Is Connected to V+.

Transistor Count, 146

–5–

3

4

5

6

87

12

11

10

9

OP491 Die Size 0.070 × 0.110 Inch,

7,700 Sq. Mils. Substrate (Die Backside) Is Connected to V+.

Transistor Count, 290.

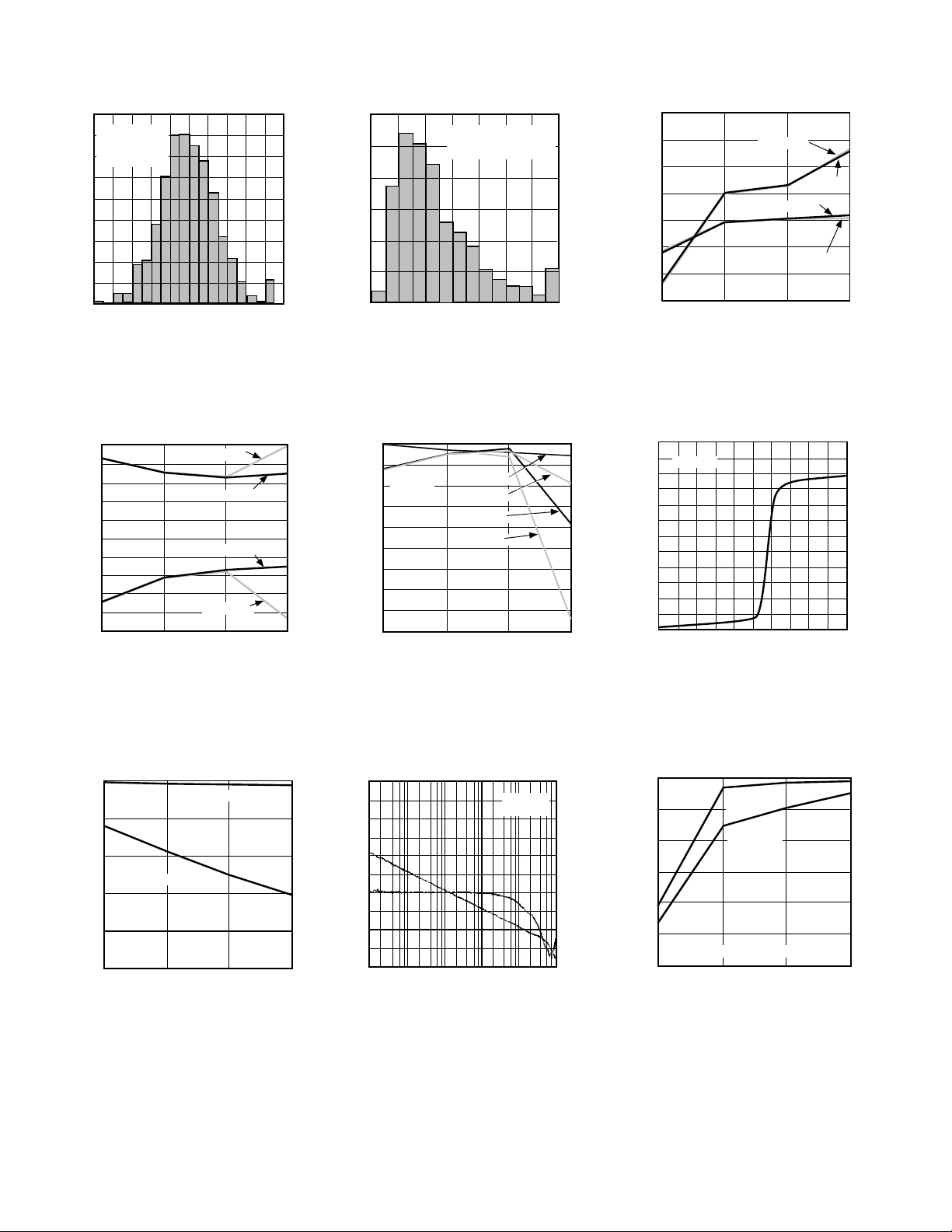

OP191/OP291/OP491–T ypical Performance Characteristics

36

–36

3.0

–18

–30

0.30

–24

0

0

–12

–6

6

12

18

30

24

2.72.42.11.81.51.20.900.60

INPUT COMMON MODE VOLTAGE – Volts

INPUT BIAS CURRENT – nA

VS = +3V

1200

1000

800

600

400

200

0

12525–40

85

TEMPERATURE – °C

OPEN-LOOP GAIN –V/mV

VS = 3V, VO = 0.3V / 2.7V

RL = 100kΩ,

V

CM

= 2.9V

RL = 100kΩ,

V

CM

= 0.1V

180

VS = +3V

160

T

= +25°C

A

BASED ON 1200

140

OP AMPS

120

100

80

UNITS

60

40

20

0

–0.18

INPUT OFFSET VOLTAGE – mV

0.14

0.06–0.02–0.10

0.22

Figure 2. OP291 Input Offset Voltage

Distribution, V

40

30

20

10

0

–10

–20

–30

INPUT BIAS CURRENT – nA

–40

–50

–60

S

VS = +3V

TEMPERATURE – °C

= +3 V

V

= 3V

CM

V

= 2.9V

CM

V

= 0.1V

CM

V

= 0V

CM

12525–40 85

120

100

80

60

UNITS

20

0

1400

V

= +3V

S

–40°C < T

< +125°C

A

BASED ON 600 OP AMPS

INPUT OFFSET VOLTAGE – µV/ °C

64325

7

Figure 3. OP291 Input Offset Voltage Drift Distribution, V

0

–0.2

VS = +3V

–0.4

–0.6

–0.8

–1.0

–1.2

–1.4

INPUT OFFSET CURRENT – nA

–1.6

–1.8

VCM = 0.1V

VCM = 2.9V

VCM = 3V

VCM = 0V

TEMPERATURE – °C

= +3 V

S

85

12525–40

0

VS = +3V

–0.02

–0.04

–0.06

–0.08

–0.1

INPUT OFFSET VOLTAGE – mV

–0.12

–0.14

VCM = 0.1V

VCM = 3V

TEMPERATURE – °C

85

VCM = 0V

VCM = 2.9V

Figure 4. Input Offset Voltage vs.

Temperature, V

= +3 V

S

12525–40

Figure 5. Input Bias Current vs.

Temperature, V

3.00

2.95

2.90

2.85

OUTPUT SWING – Volts

2.80

VS = +3V

2.75

–40

Figure 8. Output Voltage Swing

vs. Temperature, V

= +3 V

S

+VO @ RL = 100k

+VO @ RL = 2k

25

TEMPERATURE – °C

85

= +3 V

S

125

Figure 6. Input Offset Current

vs. Temperature, V

160

140

120

100

80

40

20

OPEN-LOOP GAIN – dB

0

–20

–40

100601k 10k 100k 1M 10M

FREQUENCY – Hz

= +3 V

S

VS = +3V

T

= +25°C

A

0

45

90

135

180

225

270

Figure 9. Open-Loop Gain & Phase

vs. Frequency, V

= +3 V

S

–6–

Figure 7. Input Bias Current vs.

Common-Mode Voltage, V

PHASE SHIFT – Degrees

Figure 10. Open-Loop Gain vs.

Temperature, VS = +3 V

= +3 V

S

REV. 0

Loading...

Loading...