Analog Devices DAC8426 Datasheet

Quad 8-Bit Voltage Out CMOS DAC

a

FEATURES

No Adjustments Required, Total Error 61 LSB Max

Over Temperature

Four Voltage-Output DACs on a Single Chip

Internal 10 V Bandgap Reference

Operates from Single 115 V Supply

Fast 50 ns Data Load Time, All Temperatures

Pin-for-Pin Replacement for PM-7226 and AD7226,

Eliminates External Reference

APPLICATIONS

Process Controls

Multichannel Microprocessor Controlled:

System Calibration

Op Amp Offset and Gain Adjust

Level and Threshold Setting

GENERAL DESCRIPTION

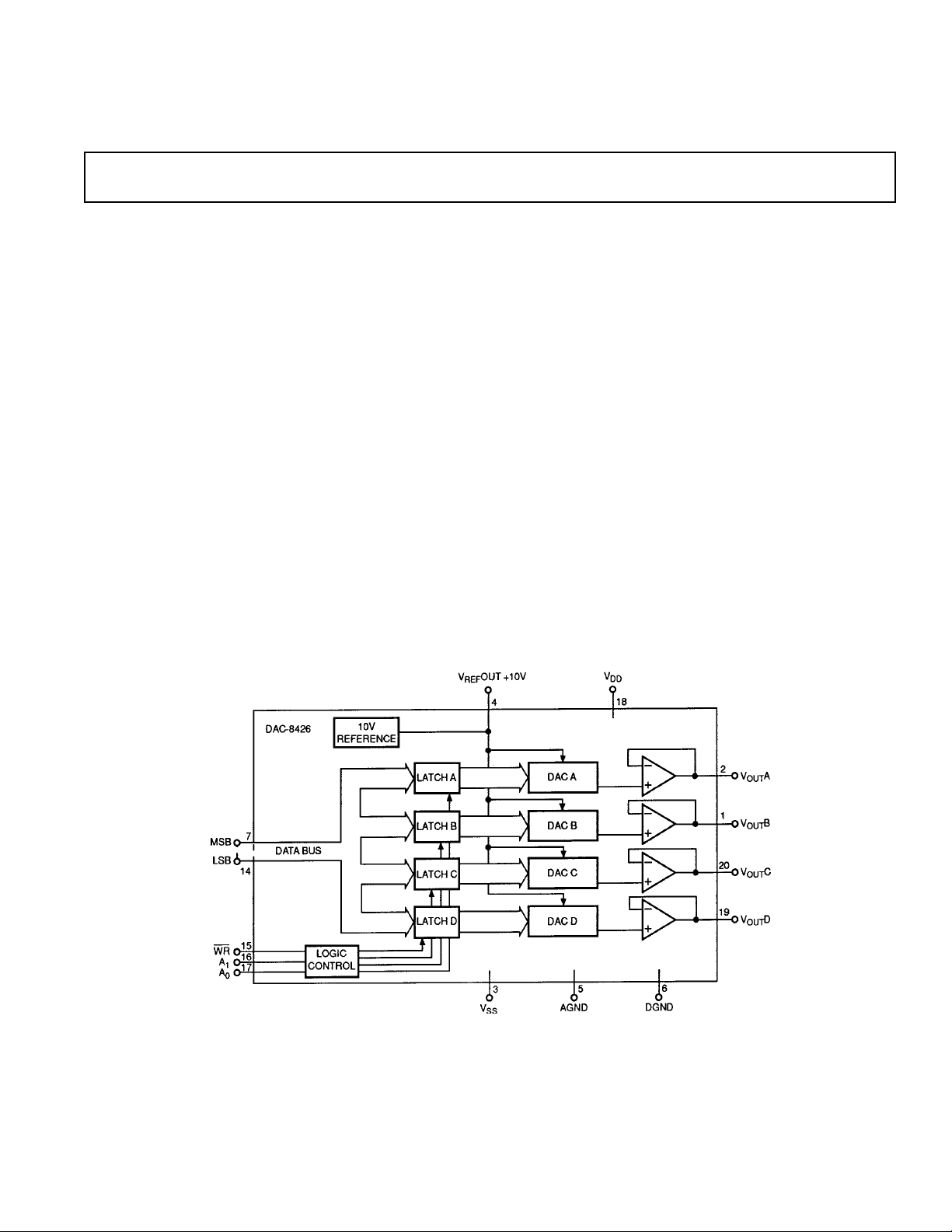

The DAC8426 is a complete quad voltage output D/A converter

with internal reference. This product fits directly into any existing 7226 socket where the user currently has a 10 V external

reference. The external reference is no longer necessary. The

internal reference of the DAC8426 is laser-trimmed to ±0.4%

Complete with Internal 10 V Reference

DAC8426

offering a 25 ppm/°C temperature coefficient and 5 mA of external load driving capability.

The DAC8426 contains four 8-bit voltage-output CMOS D/A

converters on a single chip. A 10 V output bandgap reference

sets the output full-scale voltage. The circuit also includes four

input latches and interface control logic.

One of the four latches, selected by the address inputs, is loaded

from the 8-bit data bus input when the write strobe is active

low. All digital inputs are TTL/CMOS (5 V) compatible. The

on-board amplifiers can drive up to 10 mA from either a single

or dual supply. The on-board reference that is always connected

to the internal DACs has 5 mA available to drive external devices.

Its compact size, low power, and economical cost-per-channel,

make the DAC8426 attractive for applications requiring multiple D/A converters without sacrificing circuit-board space. System reliability is also increased due to reduced parts count.

PMI’s advanced oxide-based, silicon-gate, CMOS process allows the DAC8426’s analog and digital circuitry to be manufactured on the same chip. This, coupled with PMI’s highly stable

thin-film R-2R resistor ladder, aids in matching and temperature tracking between DACs.

FUNCTIONAL BLOCK DIAGRAM

REV. C

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

DAC8426–SPECIFICA TIONS

(VDD = +15 V 6 10%, AGND = DGND = 0 V, VSS = 0 V, TA = –558C to +1258C

applies for DAC8426AR/BR, TA = –408C to +858C applies for DAC8426ER/EP/FR/FP/FS, unless otherwise noted.)

Parameter Symbol Conditions Min Typ Max Units

STATIC PERFORMANCE

Resolution N 8 Bits

Total Unadjusted Error

Relative Accuracy INL A, E ±1/2 LSB

Differential Nonlinearity

Full-Scale Temperature Coefficient TCG

Zero Scale Error V

Zero Scale Error

Temperature Coefficient TCV

REFERENCE OUTPUT

Output Voltage V

Temperature Coefficient TCV

Load Regulation LD

Line Regulation LN

Output Noise

3

Output Current I

DIGITAL INPUTS

Logic Input “0” V

Logic Input “1” V

Input Current I

Input Capacitance

POWER SUPPLIES

Positive Supply Current

Negative Supply Current

Power Dissipation

Power Supply Sensitivity P

1

TUE Includes Reference A, E ±1 LSB

B, F ±2 LSB

2

DNL ±1 LSB

FS

ZSE

ZS

OUT No Load A, E 9.96 10.04 V

REF

Includes Reference 25 ppm/°C

Dual Supply VSS = –5 V 10 µV/°C

B, F ±1 LSB

20 mV

B, F 9.92 10.08 V

OUT 20 ppm/°C

REF

REG

REG

∆IL = 5 mA 0.02 0.1 %/mA

∆VDD ±10% 0.008 0.04 %/V

en rms f = 0.1 Hz to 10 Hz 3 10 µV p-p

OUT ∆V

REF

INL

INH

3

4

4

5

C

I

I

P

IN

IN

DD

SS

DISS

SS

OUT < 40 mV 5 7 mA

REF

0.8 V

2.4 V

VIN = 0 V or V

DD

0.1 10 µA

48pF

614mA

Dual Supply VSS = –5 V 4 10 mA

90 210 mW

∆VDD = ±5% 0.0002 0.01 %/%

ELECTRICAL CHARACTERISTICS

VDD = +15 V 6 10%, AGND = DGND = 0 V, VSS = 0 V, TA = –558C to +1258C applies for

DAC8426AR/BR, TA = –408C to +858C applies for DAC8426ER/EP/FR/FP/FS, unless otherwise noted.

Parameter Symbol Conditions Min Typ6Max Units

DAC OUTPUT

Output Current (Source)

Output Current (Sink)

Minimum Load Resistance R

DYNAMIC PERFORMANCE

V

Slew Rate SR 4 V/µs

OUT

V

Settling Time t

OUT

(Positive or Negative)

Digital Crosstalk Q 10 nVs

SWITCHING CHARACTERISTICS

Address To Write Setup Time t

Address To Write Hold Time t

Data Valid To Write Setup Time t

Data Valid To Write Hold Time t

Write Pulse Width t

NOTES

1

Includes Full-Scale Error, Relative Accuracy, and Zero Code Error. Note ± 1 LSB = ±0.39% error.

2

All devices guaranteed monotonic over the full operating temperature range.

3

Guaranteed and not subject to production test.

4

Digital inputs VIN = V

5

P

calculated by IDD × VDD.

DISS

6

Typicals represent measured characteristics at TA = +25°C.

Specifications subject to change without notice.

INL

or V

3

3

3

; V

OUT

and V

INH

I

OUT

I

OUT

S

3

AS

AH

DS

DH

WR

OUT unloaded.

REF

SOURCE Digital In = All Ones 10 mA

SINK Digital In = All Zeroes VSS = –5 V 350 450 µA

L(MIN)

Digital In = All Ones 2 kΩ

To ±1/2 LSB, RL = 2 kΩ 3 µs

0ns

0ns

70 ns

10 ns

50 ns

–2–

REV. C

DAC8426

ABSOLUTE MAXIMUM RATINGS

VDD to AGND or DGND . . . . . . . . . . . . . . . . .–0.3 V, +17 V

V

to AGND or DGND . . . . . . . . . . . . . . . . . . . . .–7 V, V

SS

DD

VDD to VSS . . . . . . . . . . . . . . . . . . . . . . . . . . . .–0.3 V, +24 V

AGND to DGND . . . . . . . . . . . . . . . . . . . . . . . .–0.3 V, +5 V

Digital Input Voltage to DGND . . . . . . . . . . . . . –0.3 V, V

V

OUT to AGND1 . . . . . . . . . . . . . . . . . . . . . –0.3 V, V

REF

V

to AGND1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . VSS, V

OUT

DD

DD

DD

Operating Temperature

Military AR/BR . . . . . . . . . . . . . . . . . . . . –55°C to +125°C

Extended Industrial ER/EP/FR/FP/FS . . . . –40°C to +85°C

Maximum Junction Temperature . . . . . . . . . . . . . . . . +150°C

Storage Temperature . . . . . . . . . . . . . . . . . . –65°C to +150°C

Lead Temperature (Soldering, 60 sec) . . . . . . . . . . . . +300°C

THERMAL RESISTANCE

Package Type u

2

JA

u

JC

Units

20-Pin Cerdip (R) 70 7 °C/W

20-Pin Plastic DIP (P) 61 24 °C/W

20-Pin SOL(S) 80 22 °C/W

NOTES

1

Outputs may be shorted to any terminal provided the package power dissipation

is not exceeded. Typical output short-circuit current to AGND is 50 mA.

2

θJA is specified for worst case mounting conditions, i.e., θJA is specified for de-

vice in socket for cerdip and P-DIP packages; θJA is specified for device soldered to printed circuit board for SOL package.

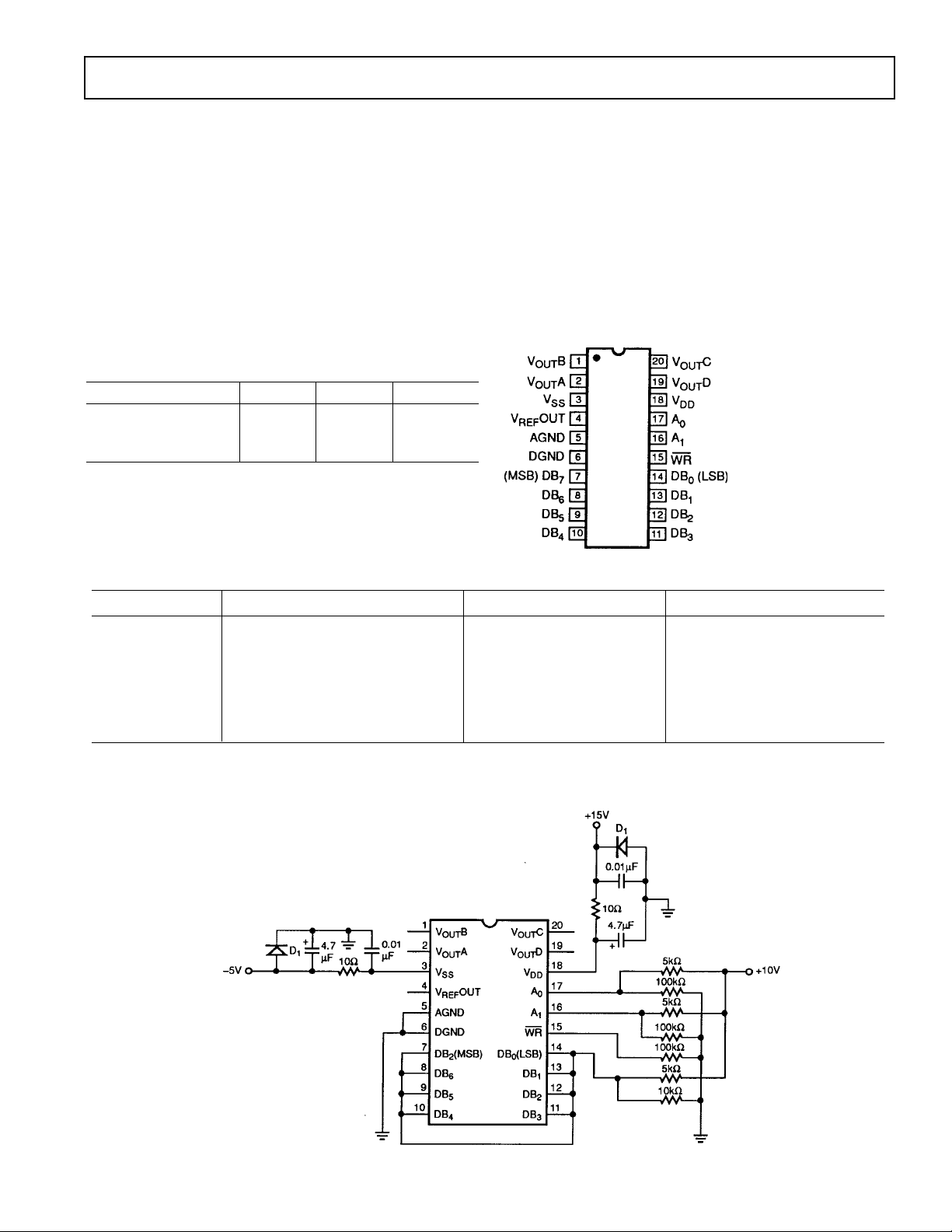

ORDERING GUIDE

CAUTION

1. Do not apply voltages higher than VDD or less than VSS potential on any terminal.

2. The digital control inputs are zener-protected; however,

permanent damage may occur on unprotected units from

high-energy electrostatic fields. Keep units in conductive

foam at all times until ready to use.

3. Do not insert this device into powered sockets. Remove

power before insertion or removal.

4. Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to device.

PIN CONNECTIONS

20-Pin Cerdip

(R Suffix)

20-Pin Epoxy DIP

(P Suffix)

20-Pin SOL

(S Suffix)

1

Model Total Unadjusted Error Temperature Range Package Description

DAC8426AR

2

±1 LSB –55°C to +125°C 20-Pin Cerdip (Q-20)

DAC8426ER ±1 LSB –40°C to +85°C 20-Pin Cerdip (Q-20)

DAC8426EP ±1 LSB –40°C to +85°C 20-Pin Plastic DIP (N-20)

DAC8426BR

2

±2 LSB –55°C to +125°C 20-Pin Cerdip (Q-20)

DAC8426FR ±2 LSB –40°C to +85°C 20-Pin Cerdip (Q-20)

DAC8426FP ±2 LSB –40°C to +85°C 20-Pin Plastic DIP (N-20)

DAC8426FS

NOTES

1

Burn-in is available on commercial and industrial temperature range parts in cerdip, plastic DIP, and TO-can packages.

2

For devices processed in total compliance to MIL-STD-883, add /883 after part number. Consult factory for 883 data sheet.

3

For availability and burn-in information on SO and PLCC packages, contact your local sales office.

3

±2 LSB –40°C to +85°C 20-Lead SOL (R-20)

REV. C

Burn-In Circuit

–3–

DAC8426

WARNING!

ESD SENSITIVE DEVICE

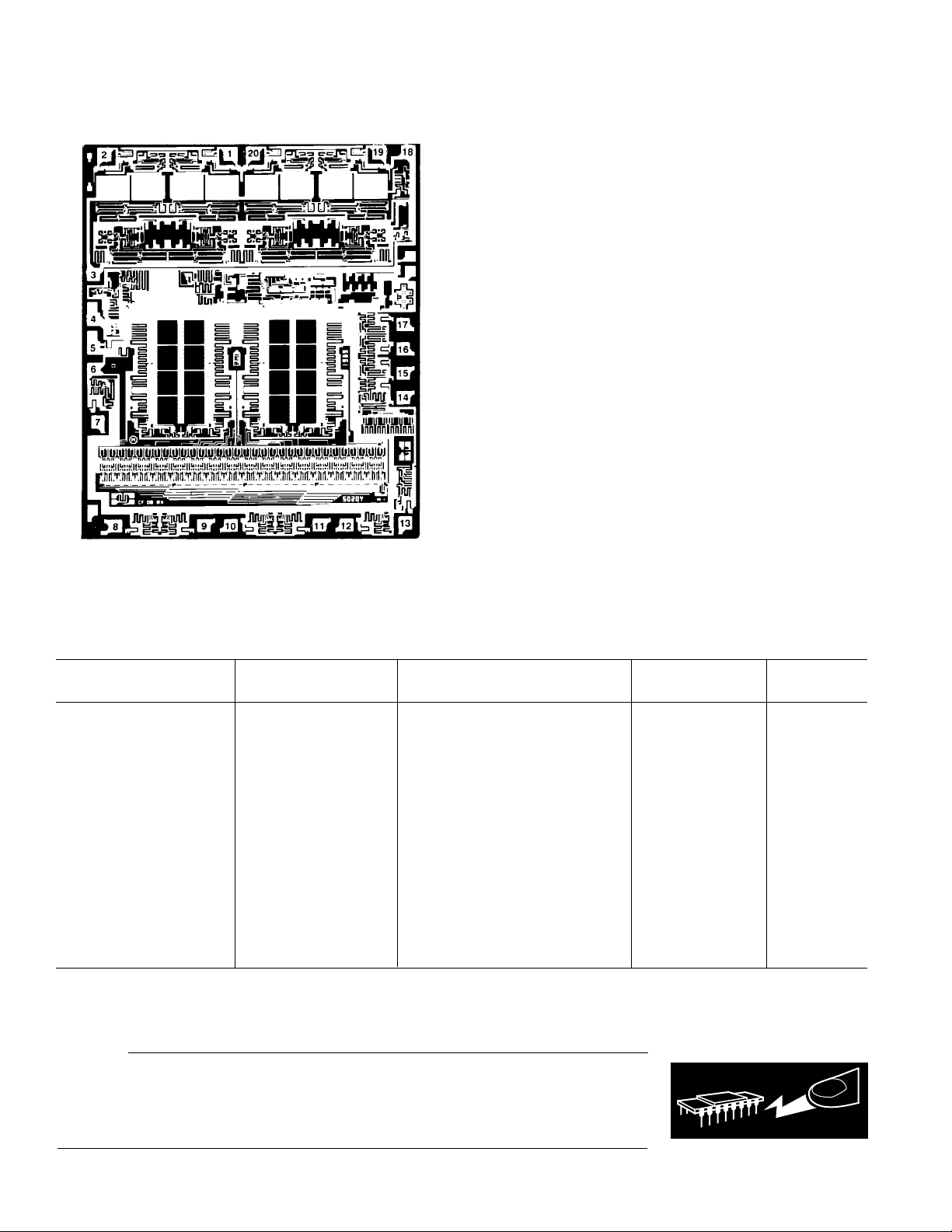

DICE CHARACTERISTICS

1. V

OUT B

2. V

OUT A

3. V

SS

4. V

OUT 14. DB0 (LSB)

REF

11. DB

12. DB

13. DB

3

2

1

5. AGND 15. WR

6. DGND 16. A

7. DB7 (MSB) 17. A

8. DB

6

9. DB

5

10. DB

4

18. V

19. V

20. V

1

0

DD

OUT D

OUT C

DIE SIZE 0.129 × 0.152 inch, 19,608 sq. mils

×

3.86 mm, 12.65 sq. mm)

(3.28

WAFER TEST LIMITS

at VDD = +15 V 6 5%; VSS = AGND = DGND = 0 V; unless otherwise specified. TA = +258C. All specifications

apply for DACs A, B, C, and D.

DAC8426GBC

Parameter Symbol Conditions Limits Units

Total Unadjusted Error TUE ±2 LSB max

Relative Accuracy INL ±1 LSB max

Differential Nonlinearity DNL ± 1 LSB max

Full-Scale Error G

Zero Code Error V

DAC Output Current I

Reference Output Voltage V

Load Regulation LD

Line Regulation LN

Reference Output Current I

Logic Inputs High V

Logic Inputs Low V

Logic Input Current I

Positive Supply Current I

Negative Supply Current I

NOTE

Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed

for standard product dice. Consult factory to negotiate specifications based on dice lot qualifications through sample lot assembly and testing.

FSE

ZSE

SOURCE Digital In = All Ones 10 mA min

OUT

OUT No Load 10.04 V max

REF

REG

REG

OUT ∆V

REF

INH

INL

IN

DD

SS

∆IL = 5 mA 0.1 %/mA max

∆VDD = ±10 V 0.04 %/V max

OUT < 40 mV 5 mA min

REF

V

= 0 V or V

IN

VIN = V

VIN = V

INL

INL

or V

or V

DD

INH

INH’ VSS

= –5 V 10 mA max

±1 LSB max

±20 mV max

2.4 V min

0.8 V max

±1 µA max

14 mA max

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the DAC8426 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

–4–

REV. C

Loading...

Loading...