Analog Devices AD7839 Datasheet

Octal 13-Bit, Parallel Input,

a

FEATURES

Eight 13-Bit DACs in One Package

Voltage Outputs

Offset Adjust for Each DAC Pair

Reference Range of ⴞ5 V

Maximum Output Voltage Range of ⴞ10 V

Clear Function to User-Defined Voltage

44-Lead MQFP Package

APPLICATIONS

Automatic Test Equipment

Process Control

General Purpose Instrumentation

V

CCVSSVDD

GENERAL DESCRIPTION

The AD7839 contains eight 13-bit DACs on one monolithic

chip. It has output voltages with a full-scale range of ±10 V

from reference voltages of ±5 V.

The AD7839 accepts 13-bit parallel loaded data from the external bus into one of the input registers under the control of the

WR, CS and DAC channel address pins, A0–A2.

The DAC outputs are updated on reception of new data into

the DAC registers. All the outputs may be updated simultaneously by taking the LDAC input low.

Each DAC output is buffered with a gain-of-two amplifier into

which an external DAC offset voltage can be inserted via the

DUTGNDx pins.

The AD7839 is available in a 44-lead MQFP package.

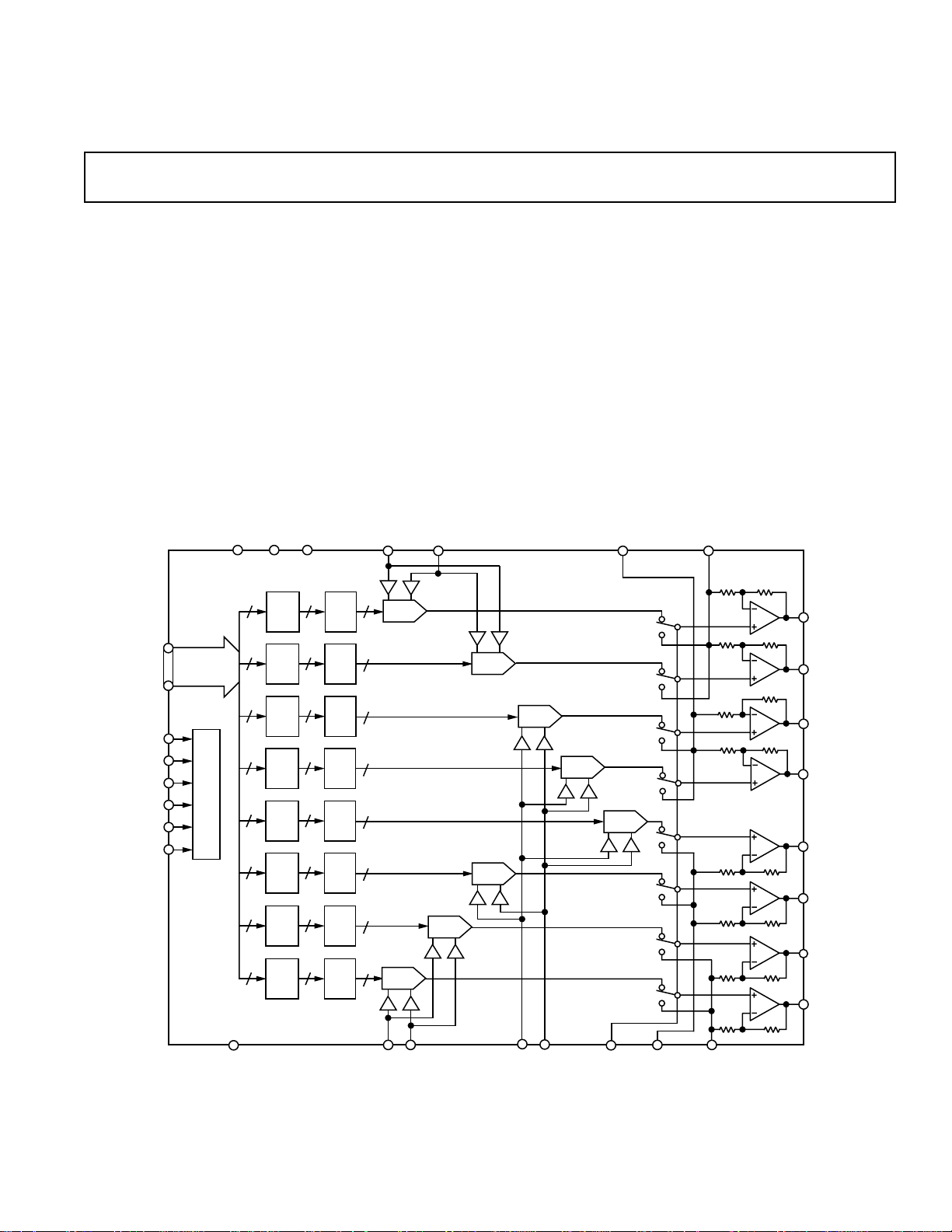

FUNCTIONAL BLOCK DIAGRAM

V

REF

(+)ABV

REF

(–)

AB

DUTGND

CD

Voltage-Output DAC

AD7839

DUTGND

AB

DB12

DB0

WR

CS

A0

LDAC

AD7839

13

13 13

13 13

13 13

A1

A2

DECODE

ADDRESS

13 13

13 13

13 13

13 13

INPUT

REG

A

INPUT

REG

B

INPUT

REG

C

INPUT

REG

D

INPUT

REG

E

INPUT

REG

F

INPUT

REG

G

INPUT

REG

H

13 13

DAC

REG

A

DAC

REG

B

DAC

REG

C

DAC

REG

D

DAC

REG

E

DAC

REG

F

DAC

REG

G

DAC

REG

H

DAC A

13

13

13

13

13

13

13

DAC H

DAC B

DAC C

DAC D

DAC E

DAC F

DAC G

RR

RR

R

R

R

R

R

R

R

R

R

R

R

R

A

V

OUT

B

V

OUT

C

V

OUT

D

V

OUT

E

V

OUT

F

V

OUT

G

V

OUT

H

V

OUT

V

GND

V

REF

GH

(–)

(+)

REF

GH

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

V

REF

CDEF

(–)

(+)

V

REF

CDEF

CLR

DUTGND

DUTGND

EF

GH

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

(VCC = +5 V ⴞ 5%; VDD = +15 V ⴞ 5%; VSS = –15 V ⴞ 5%; GND = DUTGND = 0 V;

AD7839–SPECIFICATIONS

RL = 5 k⍀ and CL = 50 pF to GND, T

A

1

= T

MIN

to T

, unless otherwise noted.)

MAX

Parameter A Version Units Test Conditions/Comments

ACCURACY

Resolution 13 Bits

Relative Accuracy ±2 LSB max Typically ±0.5 LSB

Differential Nonlinearity ±0.9 LSB max Guaranteed Monotonic Over Temperature

Zero-Scale Error ±4LSB maxV

Full-Scale Error ±4LSB maxV

Gain Error ±1 LSB typ V

Gain Temperature Coefficient

DC Crosstalk

REFERENCE INPUTS

2

2

2

0.5 ppm FSR/°C typ

10 ppm FSR/°C max

120 µV max See Terminology. Typically 75 µV

(+) = +5 V, V

REF

(+) = +5 V, V

REF

(+) = +5 V, V

REF

(–) = –5 V. Typically within ±1 LSB

REF

(–) = –5 V. Typically within ±1 LSB

REF

(–) = –5 V

REF

DC Input Impedance 100 MΩ typ

Input Current ±1 µA max Per Input. Typically ±0.03 µA

V

(+) Range 0/+5 V min/max

REF

(–) Range –5/0 V min/max

V

REF

[V

REF

(+) – V

(–)] +2/+10 V min/max For Specified Performance. Can Go as Low as 0 V, but

REF

Performance Not Guaranteed

DUTGND INPUTS

2

DC Input Impedance 60 kΩ typ

Max Input Current ±0.3 mA typ Per Input

Input Range –2/+2 V min/max

OUTPUT CHARACTERISTICS

Output Voltage Swing ±10 V min 2 × (V

2

(–) + [V

REF

REF

(+) – V

(–)] × D) – V

REF

DUTGND

Short Circuit Current 15 mA max

Resistive Load 5 kΩ min To 0 V

Capacitive Load 50 pF max To 0 V

DC Output Impedance 0.5 Ω max

DIGITAL INPUTS

V

, Input High Voltage 2.4 V min

INH

V

, Input Low Voltage 0.8 V max

INL

I

, Input Current Total for All Pins

INH

2

@ +25°C1µA max

to T

T

MIN

MAX

±10 µA max

CIN, Input Capacitance 10 pF max

POWER REQUIREMENTS

V

CC

V

DD

V

SS

Power Supply Sensitivity

␣␣ ∆Full Scale/∆V

␣␣ ∆Full Scale/∆V

I

CC

I

DD

I

SS

NOTES

1

Temperature range for A Version: –40°C to +85°C

2

Guaranteed by characterization. Not production tested.

3

The AD7839 is functional with power supplies of ±12 V ± 10% with reduced output range. At 12 V it is recommended to restrict reference range to ±4 V due to

output amplifier headroom limitations

Specifications subject to change without notice.

DD

SS

3

+4.75/+5.25 V min/max For Specified Performance

+14.25/+15.75 V min/max For Specified Performance

2

–14.25/–15.75 V min/max For Specified Performance

90 dB typ

90 dB typ

0.5 mA max V

= VCC, V

INH

= GND. Dynamic Current

INL

10 mA max Outputs Unloaded. Typically 8 mA

10 mA max Outputs Unloaded. Typically 8 mA

–2–

REV. 0

AD7839

(These characteristics are included for Design Guidance and are not subject

AC PERFORMANCE CHARACTERISTICS

Parameter A Units Test Conditions/Comments

DYNAMIC PERFORMANCE

Output Voltage Settling Time 30 µs typ Full-Scale Change to ±1/2 LSB. DAC Latch Contents Alternately

40 µs max Loaded with All 0s and All 1s

Slew Rate 0.7 V/µs typ

Digital-to-Analog Glitch Impulse 230 nV-s typ Measured with V

Channel-to-Channel Isolation 99 dB typ See Terminology

DAC-to-DAC Crosstalk 40 nV-s typ See Terminology

Digital Crosstalk 0.2 nV-s typ Feedthrough to DAC Output Under Test Due to Change in Digital

Digital Feedthrough 0.1 nV-s typ Effect of Input Bus Activity on DAC Output Under Test

Output Noise Spectral Density

␣ ␣ @ 1 kHz 200 nV/√Hz

Specifications subject to change without notice.

1, 2

TIMING SPECIFICATIONS

(VCC = +5 V ⴞ 5%; VDD = +15 V ⴞ 5%; VSS = –15 V ⴞ 5%; GND = DUTGND = 0 V)

to production testing.)

(+) = +5 V, V

REF

Alternately Loaded with 0FFF Hex and 1000 Hex. Not Dependent

on Load Conditions

Input Code to Another Converter

typ All 1s Loaded to DAC. V

(+) = V

REF

(–) = –5 V. DAC Latch

REF

(–) = 0 V

REF

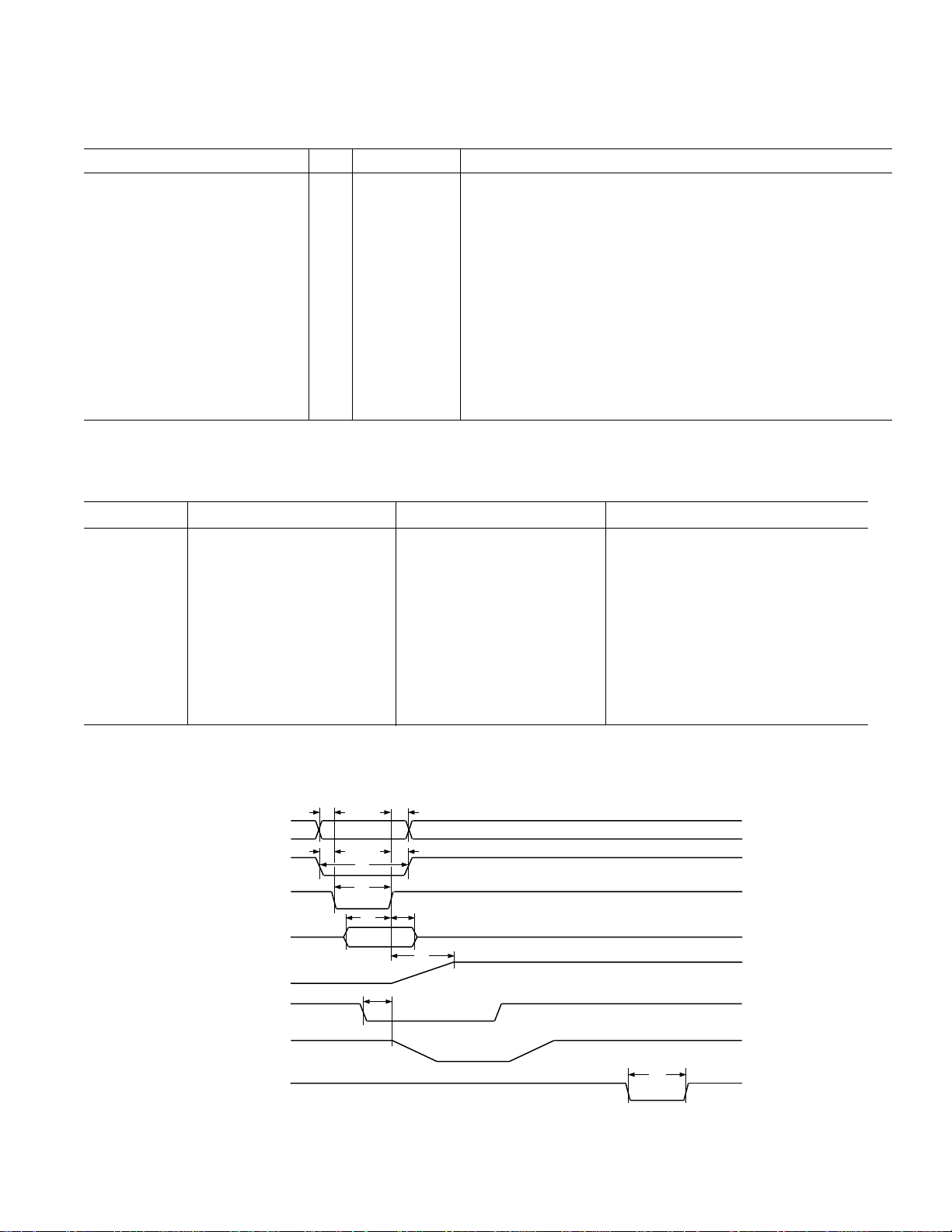

Parameter Limit at T

t

1

t

2

t

3

t

4

t

5

t

6

t

7

t

8

t

9

t

10

t

11

NOTES

1

All input signals are specified with tr = tf = 5 ns (10% to 90% of 5 V) and timed from a voltage level of 1.6 V.

2

Rise and fall times should be no longer than 50 ns.

Specifications subject to change without notice.

15 ns min Address to WR Setup Time

0 ns min Address to WR Hold Time

50 ns min CS Pulsewidth Low

50 ns min WR Pulsewidth Low

0 ns min CS to WR Setup Time

0 ns min WR to CS Hold Time

20 ns min Data Setup Time

0 ns min Data Hold Time

30 µs typ Settling Time

300 ns max CLR Pulse Activation Time

50 ns min LDAC Pulsewidth Low

A0, A1, A2

CS

WR

DATA

V

OUT

CLR

MIN, TMAX

t

1

t

5

t

2

t

6

t

3

t

4

t

8

t

7

t

9

t

10

Units Description

V

OUT

LDAC

Figure 1. Timing Diagram

–3–REV. 0

t

11

AD7839

ABSOLUTE MAXIMUM RATINGS

(T

= +25°C unless otherwise noted)

A

VCC to GND3 . . . . . . . . . . . . . . .–0.3 V, +7 V or V

1, 2

+ 0.3 V

DD

(Whichever Is Lower)

to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V, +17 V

V

DD

V

to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . +0.3 V, –17 V

SS

Digital Inputs to GND . . . . . . . . . . . . . . –0.3 V, V

(+) to V

V

REF

V

(+) to GND . . . . . . . . . . . . . . . VSS – 0.3 V, VDD + 0.3 V

REF

V

(–) to GND . . . . . . . . . . . . . . . VSS – 0.3 V, VDD + 0.3 V

REF

DUTGND to GND . . . . . . . . . . . . . V

V

(A–H) to GND . . . . . . . . . . . . VSS – 0.3 V, VDD + 0.3 V

OUT

(–) . . . . . . . . . . . . . . . . . . . . . . –0.3 V, +18 V

REF

– 0.3 V, VDD + 0.3 V

SS

+ 0.3 V

CC

Operating Temperature Range

Industrial (A Version) . . . . . . . . . . . . . . . . –40°C to +85°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Junction Temperature (T

max) . . . . . . . . . . . . . . . . . .+150°C

J

MQFP Package

Power Dissipation . . . . . . . . . . . . . . . . . . (T

max – T

J

)/θ

A

θJA Thermal Impedance . . . . . . . . . . . . . . . . . . . . . 95°C/W

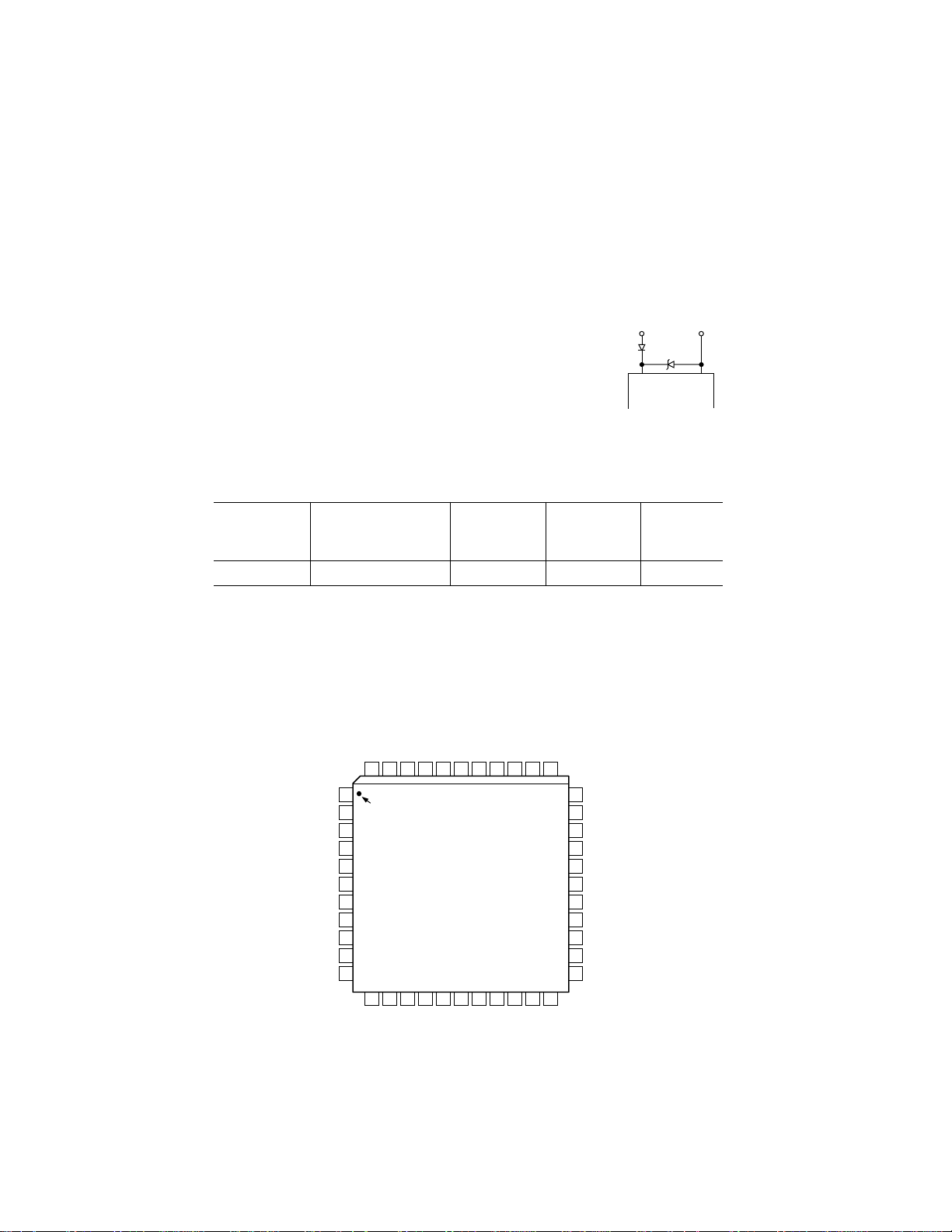

ORDERING GUIDE

Temperature Error DNL Package

Model Range (LSBs) (LSBs) Option*

AD7839AS –40°C to +85°C ±2 ±1 S-44

*S = Plastic Quad Flatpack (MQFP).

Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . . . +215°C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . .+220°C

ESD Rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . >4000 V

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2

Transient currents of up to 100 mA will not cause SCR latch-up.

3

VCC must not exceed VDD by more than 0.3 V. If it is possible for this to happen

during power supply sequencing, the following diode protection scheme will ensure

protection.

JA

IN4148

V

DD

HP5082-2811

V

DD

AD7839

V

CC

V

CC

Linearity

DUTGND_AB

V

OUT

V

(–)AB

REF

V

(+)AB

REF

V

V

LDAC

CS

PIN CONFIGURATION

C

OUT

V

DUTGND_CD

CC

V

GND

D

(–)CDEF

OUT

REF

V

V

40 39 3841424344 36 35 3437

AD7839

TOP VIEW

(Not to Scale)

DB1

DB0

B

OUT

V

1

PIN 1

IDENTIFIER

2

A

3

4

5

DD

6

SS

7

8

A2

9

A1

A0

10

11

12 13 14 15 16 17 18 19 20 21 22

WR

(+)CDEF

DD

REF

V

V

DB3

DB2

E

OUT

V

DUTGND_EF

DB5

DB4

F

OUT

V

DB6

G

OUT

V

DB7

33

DUTGND_GH

32

V

OUT

31

V

REF

30

V

REF

29

V

SS

28

CLR

27

DB12

26

DB11

25

DB10

24

DB9

23

DB8

H

(–)GH

(+)GH

–4–

REV. 0

Loading...

Loading...