LC2MOS

a

FEATURES

Four 14-Bit DACs in One Package

AD7834—Serial Loading

AD7835—Parallel 8-/14-Bit Loading

Voltage Outputs

Power-On Reset Function

Max/Min Output Voltage Range of 8.192 V

Maximum Output Voltage Span of 14 V

Common Voltage Reference Inputs

User Assigned Device Addressing

Clear Function to User-Defined Voltage

Surface-Mount Packages

AD7834—28-Lead SOIC and PDIP

AD7835—44-Lead MQFP and PLCC

APPLICATIONS

Process Control

Automatic Test Equipment

General Purpose Instrumentation

GENERAL DESCRIPTION

The AD7834 and AD7835 contain four 14-bit DACs on one

monolithic chip. The AD7834 and AD7835 have output

voltages in the range of ±8.192 V with a maximum span

of 14 V.

Quad 14-Bit DACs

AD7834/AD7835

The AD7834 is a serial input device. Data is loaded in 16-bit

format from the external serial bus, MSB first after two leading 0s,

into one via DIN, SCLK and FSYNC. The AD7834 has five

dedicated package address pins, PA0–PA4, that can be wired to

AGND or V

addressed in a multipackage application.

The AD7835 can accept either 14-bit parallel loading or doublebyte loading, where right-justified data is loaded in one 8-bit and

one 6-bit byte. Data is loaded from the external bus into one of

the input latches under the control of the WR, CS, BYSHF,

and DAC channel address pins, A0–A2.

With either device, the LDAC signal can be used to update either

all four DAC outputs simultaneously or individually on reception

of new data. In addition, for either device, the asynchronous

CLR input can be used to set all signal outputs, V

to the user-defined voltage level on the Device Sense Ground pin,

DSG. On power-on, before the power supplies have stabilized,

internal circuitry holds the DAC output voltage levels to within

±2 V of the DSG potential. As the supplies stabilize, the DAC

output levels move to the exact DSG potential (assuming

CLR is exercised).

The AD7834 is available in 28-lead 0.3" SOIC and 0.6" PDIP

packages, and the AD7835 is available in a 44-lead MQFP

package and a 44-lead PLCC package.

to permit up to 32 AD7834s to be individually

CC

1–V

OUT

OUT

(continued on page 10)

4,

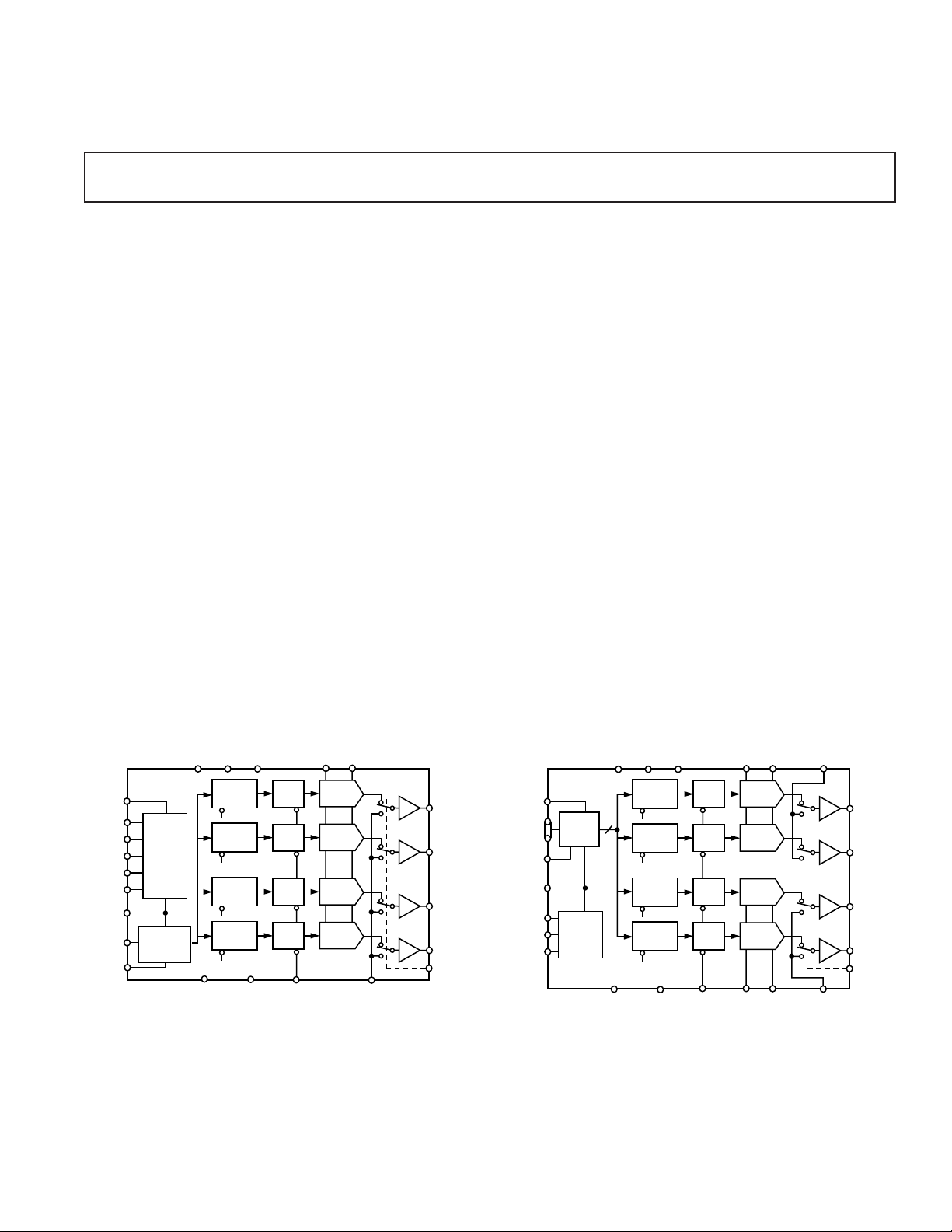

AD7834 FUNCTIONAL BLOCK DIAGRAM

PAEN

PA0

PA1

PA2

PA3

PA4

FSYNC

DIN

SCLK

AD7834

CONTROL

LOGIC

&

ADDRESS

DECODE

SERIAL-TO-

PARALLEL

CONVERTER

V

CC

AGND

VDDV

INPUT

REGISTER

1

INPUT

REGISTER

2

INPUT

REGISTER

3

INPUT

REGISTER

4

DGND

SS

DAC 1

LATCH

DAC 2

LATCH

DAC 3

LATCH

DAC 4

LATCH

LDAC

V

(–)

(+)

V

REF

REF

DAC 1

DAC 2

DAC 3

DAC 4

DSG

X1

V

1

OUT

X1

V

2

OUT

V

OUT

V

OUT

CLR

3

4

X1

X1

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

AD7835 FUNCTIONAL BLOCK DIAGRAM

V

VDDV

CC

BYSHF

DB13

DB0

WR

CS

AD7835

INPUT

BUFFER

A0

ADDRESS

A1

DECODE

A2

14

AGND

INPUT

REGISTER

1

INPUT

REGISTER

2

INPUT

REGISTER

3

INPUT

REGISTER

4

DGND

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

SS

DAC 1

LATCH

DAC 2

LATCH

DAC 3

LATCH

DAC 4

LATCH

LDAC

V

(–)A

(+)A

V

V

REF

REF

DAC 1

DAC 2

DAC 3

DAC 4

(–)B

DSG A

REF

X1

V

1

OUT

X1

V

2

OUT

X1

X1

DSG B

V

(+)B

REF

V

V

CLR

OUT

OUT

3

4

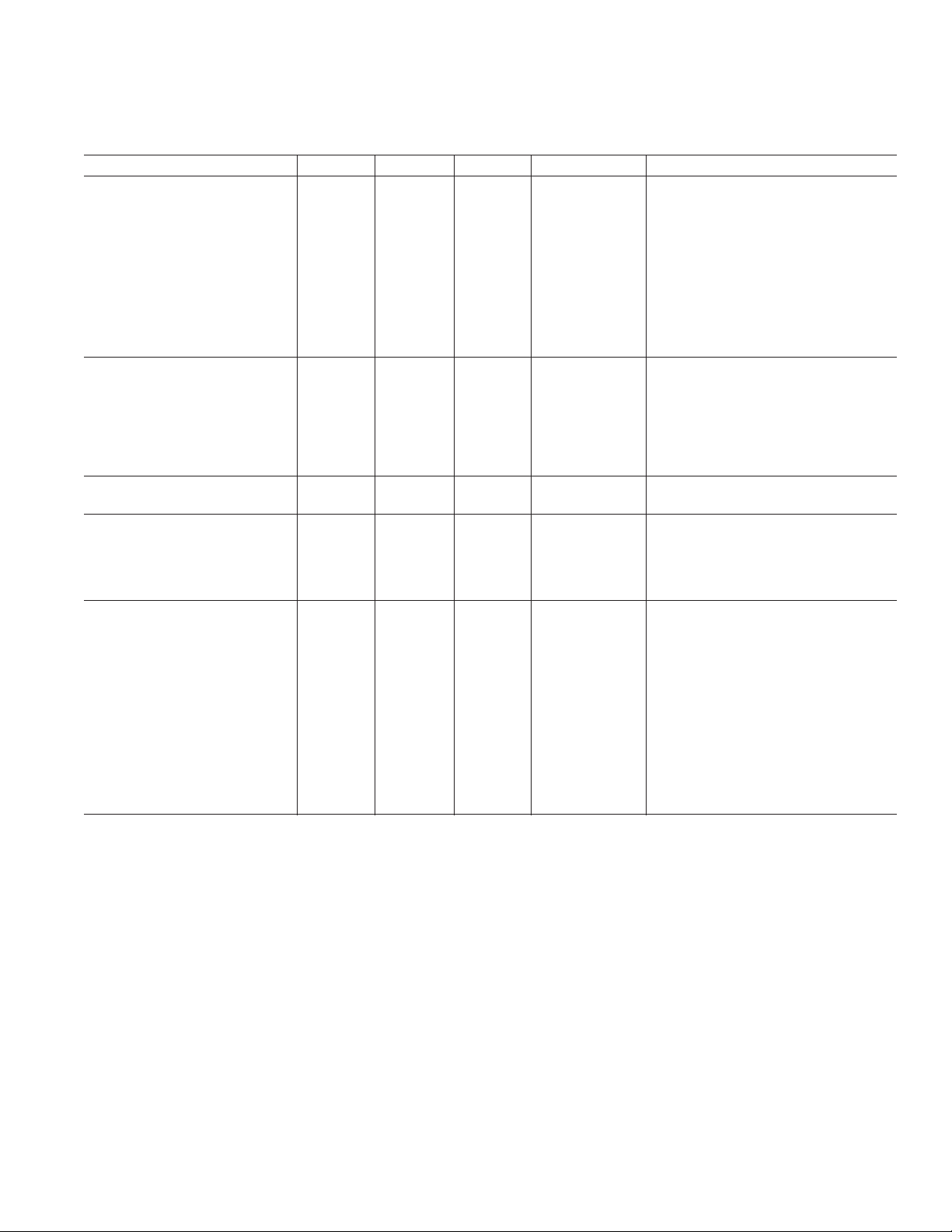

(VCC = +5 V 5%; VDD = +15 V 5%; VSS = –15 V 5%;

AD7834/AD7835

AD7834/AD7835–SPECIFICATIONS

P

arameter A B S Unit Test Conditions/Comments

AGND = DGND = 0 V; T

ACCURACY

Resolution 14 14 14 Bits

Relative Accuracy ±2 ±1 ±2 LSB max

Differential Nonlinearity ±0.9 ±0.9 ±0.9 LSB max Guaranteed Monotonic over Temperature

Full-Scale Error V

to T

T

MIN

MAX

±5 ±5 ±8 mV max

Zero-Scale Error ±4 ±4 ±5 mV max V

Gain Error ±0.5 ±0.5 ±0.5 mV typ V

Gain Temperature Coefficient

DC Crosstalk

2

2

444ppm FSR/∞C typ

20 20 20 ppm FSR/∞C max

50 50 50 mV max See Terminology. RL = 10 kW

REFERENCE INPUTS

DC Input Resistance 30 30 30 MW typ

Input Current ±1 ±1 ±1 mA max Per Input

(+) Range 0/+8.192 0/+8.192 0/+8.192 V min/max

V

REF

(–) Range –8.192/0 –8.192/0 –8.192/0 V min/max

V

REF

[V

REF

(+) – V

(–)] +5/+14 +7/+14 +5/+14 V min/max For Specified Performance. Can go as low as

REF

DEVICE SENSE GROUND INPUTS

Input Current ±2 ±2 ±2 mA max Per Input. V

DIGITAL INPUTS

, Input High Voltage 2.4 2.4 2.4 V min

V

INH

V

, Input Low Voltage 0.8 0.8 0.8 V max

INL

, Input Current ±10 ±10 ±10 mA max

I

INH

CIN, Input Capacitance 10 10 10 pF max

POWER REQUIREMENTS

V

CC

V

DD

V

SS

+5.0 +5.0 +5.0 V nom ±5% for Specified Performance

+15.0 +15.0 +15.0 V nom ±5% for Specified Performance

–15.0 –15.0 –15.0 V nom ±5% for Specified Performance

Power Supply Sensitivity

DFull Scale/DV

DFull Scale/DV

I

CC

DD

SS

110 110 110 dB typ

100 100 100 dB typ

0.2 0.2 0.5 mA max V

333mA max AD7834: V

666mA max AD7835: V

I

DD

13 13 15 mA max AD7834: Outputs Unloaded

15 15 15 mA max AD7835: Outputs Unloaded

I

SS

NOTES

1

Temperature range is as follows: A Version: –40∞C to +85∞C; B Version: –40∞C to +85∞ C.

2

Guaranteed by design.

Specifications subject to change without notice.

13 13 15 mA max Outputs Unloaded

1

= T

to T

A

MIN

(+) = +7 V, V

REF

(+) = +7 V, V

REF

(+) = +7 V, V

REF

, unless otherwise noted.)

MAX

(–) = –7 V

REF

(–) = –7 V

REF

(–) = –7 V

REF

0 V, but performance not guaranteed.

= –2 V to +2 V

DSG

= VCC, V

INH

= DGND

INL

= 2.4 V min, V

INH

= 2.4 V min, V

INH

= 0.8 V max

INL

= 0.8 V max

INL

(These characteristics are included for design guidance and are not

AC PERFORMANCE CHARACTERISTICS

P

arameter A B S Unit Test Conditions/Comments

DYNAMIC PERFORMANCE

Output Voltage Settling Time 10 10 10 ms typ Full-Scale Change to ± 1/2 LSB. DAC latch contents

Digital-to-Analog Glitch Impulse 120 120 120 nV-s typ Measured with V

DC Output Impedance 0.5 0.5 0.5 W typ See Terminology

Channel-to-Channel Isolation 100 100 100 dB typ See Terminology; applies to the AD7835 only

DAC to DAC Crosstalk 25 25 25 nV-s typ See Terminology

Digital Crosstalk 3 3 3 nV-s typ Feedthrough to DAC Output under test due to

Digital Feedthrough – AD7834 0.2 0.2 0.2 nV-s typ Effect of Input Bus Activity on DAC Output Under Test

Digital Feedthrough – AD7835 1.0 1.0 1.0 nV-s typ

Output Noise Spectral Density

@ 1 kHz 40 40 40 nV/÷Hz typ All 1s Loaded to DAC. V

subject to production testing. )

alternately loaded with all 0s and all 1s

alternately loaded with all 0s and all 1s

change in digital input code to another converter.

–2–

REF

(+) = V

REF

(–) = 0 V. DAC latch

REF

(+) = V

(–) = 0 V

REF

REV. B

AD7834/AD7835

(VCC = +5 V 5%; VDD = +12 V 5%; VSS = –12 V 5%;

SPECIFICATIONS

P

arameter A B S Unit Test Conditions/Comments

AGND = DGND = 0 V; T

ACCURACY

Resolution 14 14 14 Bits

Relative Accuracy ±2 ± 1 ±2 LSB max

Differential Nonlinearity ±0.9 ± 0.9 ± 0.9 LSB max Guaranteed Monotonic over Temperature

Full-Scale Error V

to T

T

MIN

MAX

±5 ± 5 ±8 mV max

Zero-Scale Error ± 4 ± 4 ± 5 mV max V

Gain Error ±0.5 ± 0.5 ±0.5 mV typ V

Gain Temperature Coefficient

DC Crosstalk

2

2

444ppm FSR/∞C typ

20 20 20 ppm FSR/∞C max

50 50 50 mV max See Terminology. RL = 10 kW

REFERENCE INPUTS

DC Input Resistance 30 30 30 MW typ

Input Current ±1 ± 1 ±1 mA max Per Input

(+) Range 0/+8.192 0/+8.192 0/+8.192 V min/max

V

REF

(–) Range –5/0 –5/0 –5/0 V min/max

V

REF

[V

REF

(+) – V

(–)] +5/+13.192 +7/+13.192 +5/+13.192 V min/max For Specified Performance. Can Go as Low

REF

DEVICE SENSE GROUND INPUTS

Input Current ±2 ± 2 ±2 mA max Per Input. V

DIGITAL INPUTS

V

, Input High Voltage 2.4 2.4 2.4 V min

INH

, Input Low Voltage 0.8 0.8 0.8 V max

V

INL

, Input Current ±10 ±10 ± 10 mA max

I

INH

CIN, Input Capacitance 10 10 10 pF max

POWER REQUIREMENTS

V

CC

V

DD

V

SS

+5.0 +5.0 +5.0 V nom ±5% for Specified Performance

+15.0 +15.0 +15.0 V nom ± 5% for Specified Performance

–15.0 –15.0 –15.0 V nom ±5% for Specified Performance

Power Supply Sensitivity

DFull Scale/DV

DFull Scale/DV

I

CC

DD

SS

110 110 110 dB typ

100 100 100 dB typ

0.2 0.2 0.5 mA max V

333mA max AD7834: V

666mA max AD7835: V

I

DD

13 13 15 mA max AD7834: Outputs Unloaded

15 15 15 mA max AD7835: Outputs Unloaded

I

SS

NOTES

1

Temperature range is as follows: A Version: –40∞C to +85∞C; B Version: –40∞C to +85∞ C.

2

Guaranteed by design.

Specifications subject to change without notice.

13 13 15 mA max Outputs Unloaded

A

1

= T

MIN

to T

, unless otherwise noted.)

MAX

(+) = +5 V, V

REF

(+) = +5 V, V

REF

(+) = +5 V, V

REF

(–) = –5 V

REF

(–) = –5 V

REF

(–) = –5 V

REF

as 0 V, but Performance Not Guaranteed

= –2 V to +2 V

DSG

= VCC, V

INH

= DGND

INL

= 2.4 V min, V

INH

= 2.4 V min, V

INH

= 0.8 V max

INL

= 0.8 V max

INL

REV. B

–3–

AD7834/AD7835

)

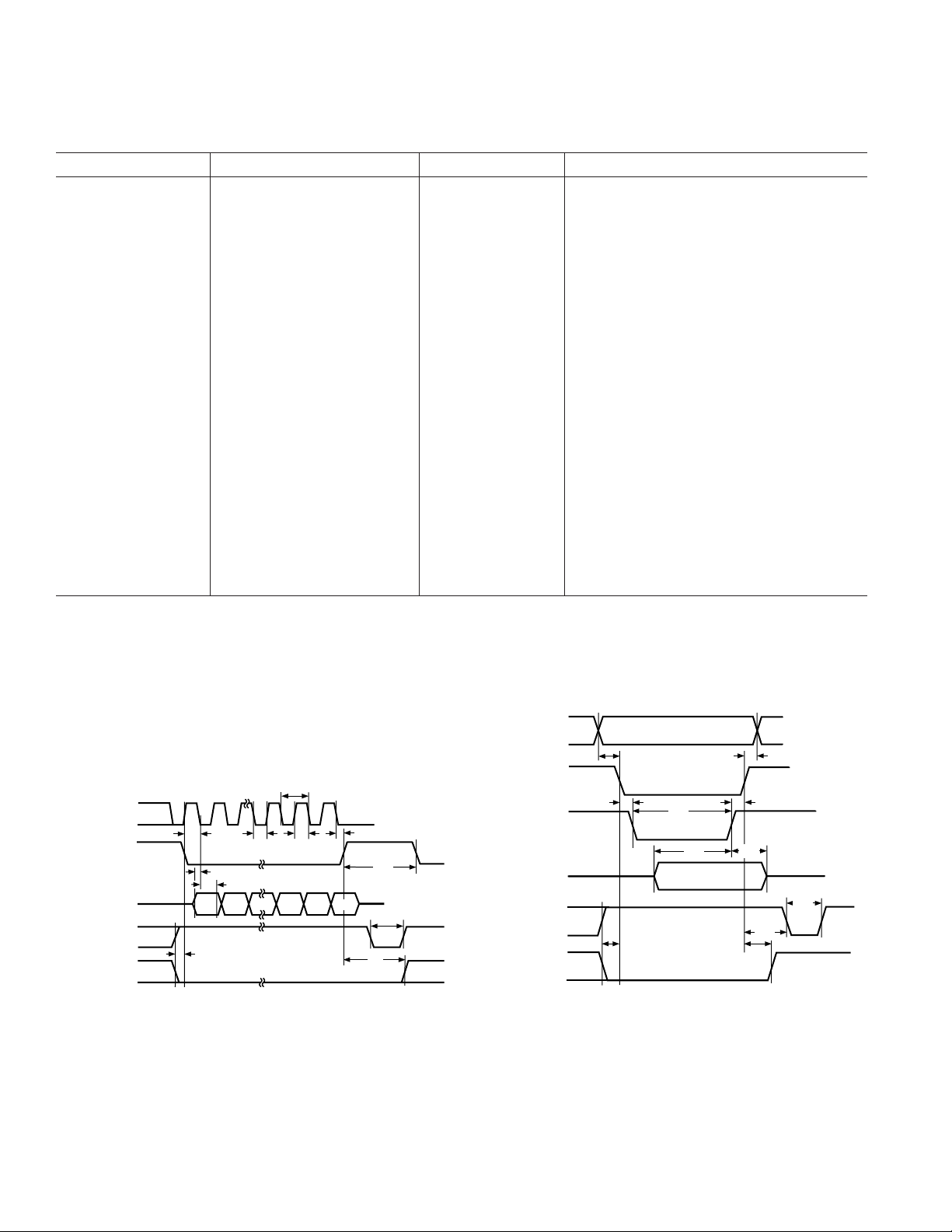

TIMING SPECIFICATIONS

Parameter Limit at T

AD7834 Specific

2

t

1

2

t

2

2

t

3

t

4

t

5

t

6

t

7

t

8

t

9

t

21

1

(VCC = +5 V 5%; VDD = +11.4 V to +15.75 V; VSS = –11.4 V to –15.75 V; AGND = DGND = 0 V)

MIN, TMAX

Unit Description

100 ns min SCLK Cycle Time

50 ns min SCLK Low

30 ns min SCLK High Time

30 ns min FSYNC, PAEN Setup Time

40 ns min FSYNC, PAEN Hold Time

30 ns min Data Setup Time

10 ns min Data Hold Time

0 ns min LDAC to FSYNC Setup Time

40 ns min LDAC to FSYNC Hold Time

20 ns min Delay Between Write Operations

AD7835 Specific

t

11

t

12

t

13

t

14

t

15

t

16

t

17

t

18

t

19

t

20

15 ns min A0, A1, A2, BYSHF to CS Setup Time

15 ns min A0, A1, A2, BYSHF to CS Hold Time

0 ns min CS to WR Setup Time

0 ns min CS to WR Hold Time

40 ns min WR Pulsewidth

40 ns min Data Setup Time

10 ns min Data Hold Time

0 ns min LDAC to CS Setup Time

0 ns min CS to LDAC Setup Time

0 ns min LDAC to CS Hold Time

General

t

10

NOTES

1

All input signals are specified with tr = tf = 5 ns (10% to 90% of 5 V) and timed from a voltage level of 1.6 V.

2

Rise and fall times should be no longer than 50 ns.

Specifications subject to change without notice.

40 ns min LDAC, CLR Pulsewidth

SCLK

FSYNC

DIN

(SIMULTANEOUS

LDAC

UPDATE)

LDAC

(PER-CHANNEL

UPDATE

1ST

2ND

CLK

CLK

t

4

t

7

MSB LSB

D23 D22

t

8

t

2

t

6

24TH

t

1

CLK

D1

t

D0

t

3

Figure 1. AD7834 Timing Diagram

A0 A1 A2

BYSHF

t

11

CS

t

13

5

t

21

t

10

t

9

(SIMULTANEOUS

(PER-CHANNEL

WR

DATA

LDAC

UPDATE)

LDAC

UPDATE)

t

t

15

t

16

18

t

12

t

14

t

17

t

10

t

19

t

20

Figure 2. AD7835 Timing Diagram

–4–

REV. B

AD7834/AD7835

ABSOLUTE MAXIMUM RATINGS

(TA = 25∞C unless otherwise noted.)

VCC to DGND3 . . . . . . . . . . . . . . –0.3 V, +7 V or V

1, 2

+ 0.3 V

DD

(Whichever Is Lower)

to AGND . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V, +17 V

V

DD

V

to AGND . . . . . . . . . . . . . . . . . . . . . . . . . . +0.3 V, –17 V

SS

AGND to DGND . . . . . . . . . . . . . . . . . . . . . . . –0.3 V, +0.3 V

Digital Inputs to DGND . . . . . . . . . . . . . . –0.3 V, V

(+) to V

V

REF

V

(+) to AGND . . . . . . . . . . . . . . . V

REF

(–) to AGND . . . . . . . . . . . . . . . V

V

REF

DSG to AGND . . . . . . . . . . . . . . . . . V

V

(1–4) to AGND . . . . . . . . . . . . V

OUT

(–) . . . . . . . . . . . . . . . . . . . . . . –0.3 V, +18 V

REF

– 0.3 V, VDD + 0.3 V

SS

– 0.3 V, VDD + 0.3 V

SS

– 0.3 V, VDD + 0.3 V

SS

– 0.3 V, VDD + 0.3 V

SS

+ 0.3 V

CC

Operating Temperature Range

Industrial (A Version) . . . . . . . . . . . . . . . . . . .–40∞C to +85∞C

Storage Temperature Range . . . . . . . . . . . . . –65∞C to +150∞C

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . 150∞C

Plastic Package

Thermal Impedance . . . . . . . . . . . . . . . . . . . . . . 75∞C/W

JA

Lead Temperature, Soldering (10 sec) . . . . . . . . . . . . 260∞C

SOIC Package

Thermal Impedance . . . . . . . . . . . . . . . . . . . . . . 75∞C/W

JA

Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . . 215∞C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . 220∞C

MQFP Package

JA Thermal Impedance . . . . . . . . . . . . . . . . . . . . . . 95∞C/W

Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . . 215∞C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . 220∞C

PLCC Package

Thermal Impedance. . . . . . . . . . . . . . . . . . . . . . 55∞C/W

JA

Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . . 215∞C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . 220∞C

Power Dissipation (Any Package) . . . . . . . . . . . . . . . . 480 mW

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2

Transient currents of up to 100 mA will not cause SCR latch up.

3

VCC must not exceed VDD by more than 0.3 V. If it is possible for this to happen

during power supply sequencing, the following diode protection scheme will

ensure protection.

V

V

DD

CC

IN4148

SD103C

V

V

DD

CC

AD7834/

AD7835

ORDERING GUIDE

Temperature Linearity DNL Package

Model Range Error (LSBs) (LSBs) Option

AD7834AR –40∞C to +85∞C ± 2 ± 0.9 R-28

AD7834AR-REEL –40∞C to +85∞C ± 2 ± 0.9 R-28

AD7834BR –40∞C to +85∞C ± 1 ± 0.9 R-28

AD7834BR-REEL –40∞C to +85∞C ± 1 ± 0.9 R-28

AD7834AN –40∞C to +85∞C ± 2 ± 0.9 N-28

AD7834BN –40∞C to +85∞C ± 1 ± 0.9 N-28

AD7835AP

AD7835AP-REEL

AD7835AS

AD7835AS-REEL

NOTES

1

R = SOIC; N = Plastic DIP; S = Plastic Quad Flatpack (MQFP); P = Plastic Leaded Chip Carrier (PLCC).

2

Contact Sales Office for availability.

2

2

2

2

–40∞C to +85∞C ± 2 ± 0.9 P-44A

–40∞C to +85∞C ± 2 ± 0.9 P-44A

–40∞C to +85∞C ± 2 ± 0.9 S-44

–40∞C to +85∞C ± 2 ± 0.9 S-44

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD7834/AD7835 feature proprietary ESD protection circuitry, permanent damage

may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

1

WARNING!

ESD SENSITIVE DEVICE

REV. B

–5–

AD7834/AD7835

AD7834 PIN FUNCTION DESCRIPTIONS

Pin Mnemonic Description

V

CC

V

SS

V

DD

DGND Digital Ground

AGND Analog Ground

V

(+) Positive Reference Input. The positive reference voltage is referred to AGND.

REF

V

(–)Negative Reference Input. The negative reference voltage is referred to AGND.

REF

V

1 to V

OUT

OUT

DSG Device Sense Ground Input. Used in conjunction with the CLR input for power-on protection of the DACs.

DIN Serial Data Input

SCLK Clock Input for writing data to the device. Data is clocked into the input register on the falling edge of SCLK.

FSYNC Frame Sync Input. Active low logic input used, in conjunction with DIN and SCLK, to write data to the device

PA0 to PA4 Package Address Inputs. These inputs are hardwired high (V

PAEN Package Address Enable Input. When low, this input allows normal operation of the device. When it is high, the

LDAC Load DAC Input (level sensitive). This input signal, in conjunction with the FSYNC input signal, determines

CLR Asynchronous Clear Input (level sensitive, active low). When this input is brought low, all analog outputs are

Logic Power Supply; +5 V ± 5%

Negative Analog Power Supply; –15 V ± 5% or –12 V ± 5%

Positive Analog Power Supply; +15 V ± 5% or +12 V ± 5%

4 DAC Outputs

When CLR is low, the DAC outputs are forced to the potential on the DSG pin.

with serial data expected after the falling edge of this signal. The contents of the 24-bit serial-to-parallel input

register are transferred on the rising edge of this signal.

) or low (DGND) to assign dedicated package

CC

addresses in a multipackage environment.

device ignores the package address (but not the channel address) in the serial data stream and loads the serial

data into the input registers. This feature is useful in a multipackage application where it can be used to load the

same data into the same channel in each package.

how the analog outputs are updated. If LDAC is maintained high while new data is being loaded into the

device’s input registers, no change occurs on the analog outputs. Subsequently, when LDAC is brought low, the

contents of all four input registers are transferred into their respective DAC latches, updating the analog outputs.

Alternatively, if LDAC is kept low while new data is shifted into the device, then the addressed DAC latch (and

corresponding analog output) is updated immediately on the rising edge of FSYNC.

switched to the externally set potential on the DSG pin. When CLR is brought high, the signal outputs remain at

the DSG potential until LDAC is brought low. When LDAC is brought low, the analog outputs are switched

back to reflect their individual DAC output levels. As long as CLR remains low, the LDAC signals are ignored

and the signal outputs remain switched to the potential on the DSG pin.

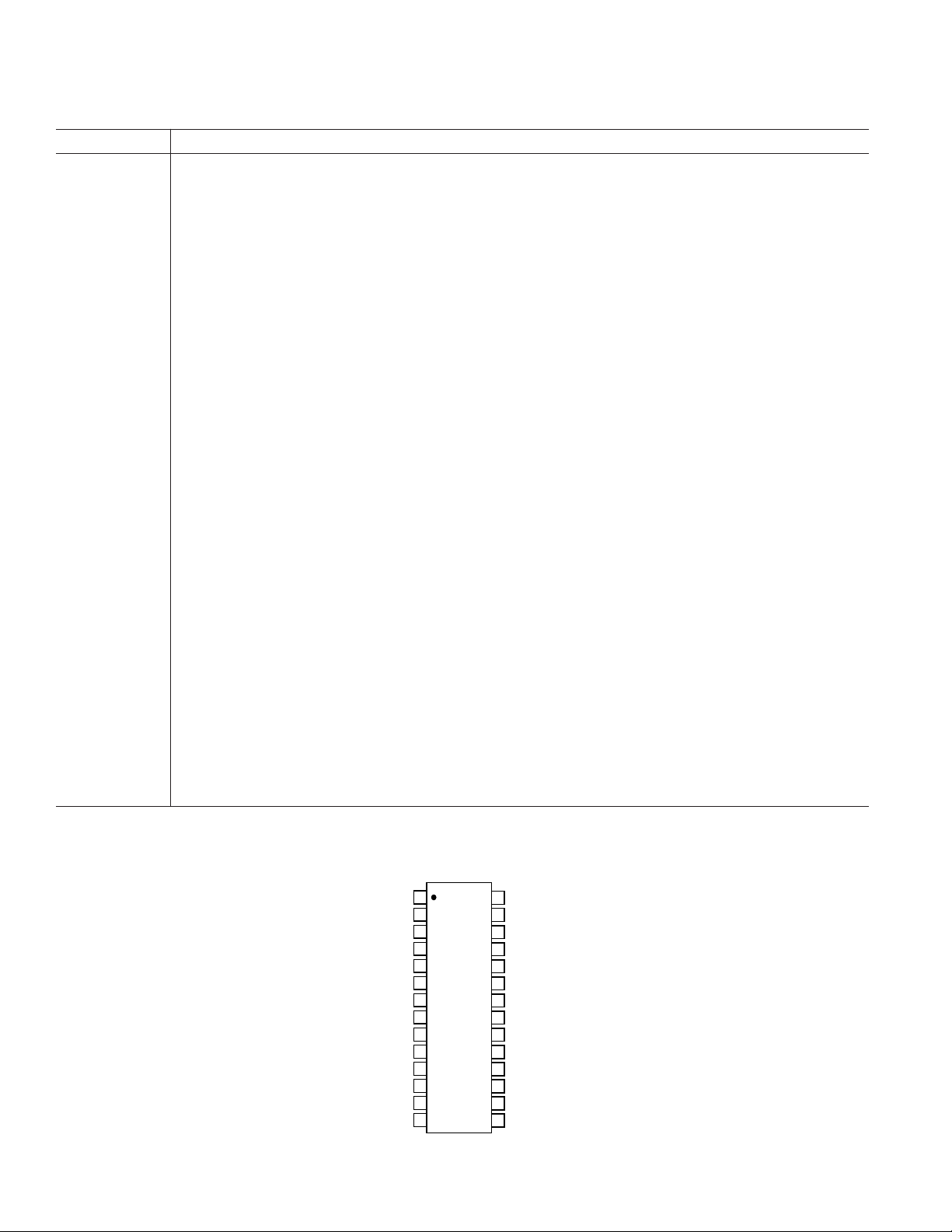

PIN CONFIGURATIONS

PDIP AND SOIC

28

27

26

25

24

23

22

21

20

19

18

17

16

15

AGND

NC

NC

NC

NC

V

DD

V

OUT

V

OUT

CLR

LDAC

FSYNC

PAEN

PA4

PA3

1

3

V

REF

V

REF

V

V

DGND

V

DSG

NC

OUT

OUT

V

SCLK

DIN

PA0

PA1

PA2

SS

(–)

(+)

2

4

CC

1

2

3

4

5

AD7834

6

TOP VIEW

(Not to Scale)

7

8

9

10

11

12

13

14

NC = NO CONNECT

–6–

REV. B

Loading...

Loading...