V

V

V

V

V

V

V

V

V

FEATURES

8-bit half-flash ADC with 420 ns conversion time

Eight single-ended analog input channels

Available with input offset adjust

On-chip track-and-hold

SNR performance given for input frequencies

up to10 MHz

On-chip reference (2.5 V)

Automatic power-down at the end of conversion

Wide operating supply range

3 V ± 10% and 5 V ± 10%

Input ranges

0 V to 2 V p-p, V

0 V to 2.5 V p-p, V

Flexible parallel interface with

stand-alone operation

APPLICATIONS

Data acquisition systems, DSP front ends

Disk drives

Mobile communication systems, subsampling

applications

GENERAL DESCRIPTION

= 3 V ± 10%

DD

= 5 V ± 10%

DD

EOC

pulse to allow

3 V/5 V, 2 MSPS, 8-Bit, 8-Channel ADC

AD7829-1

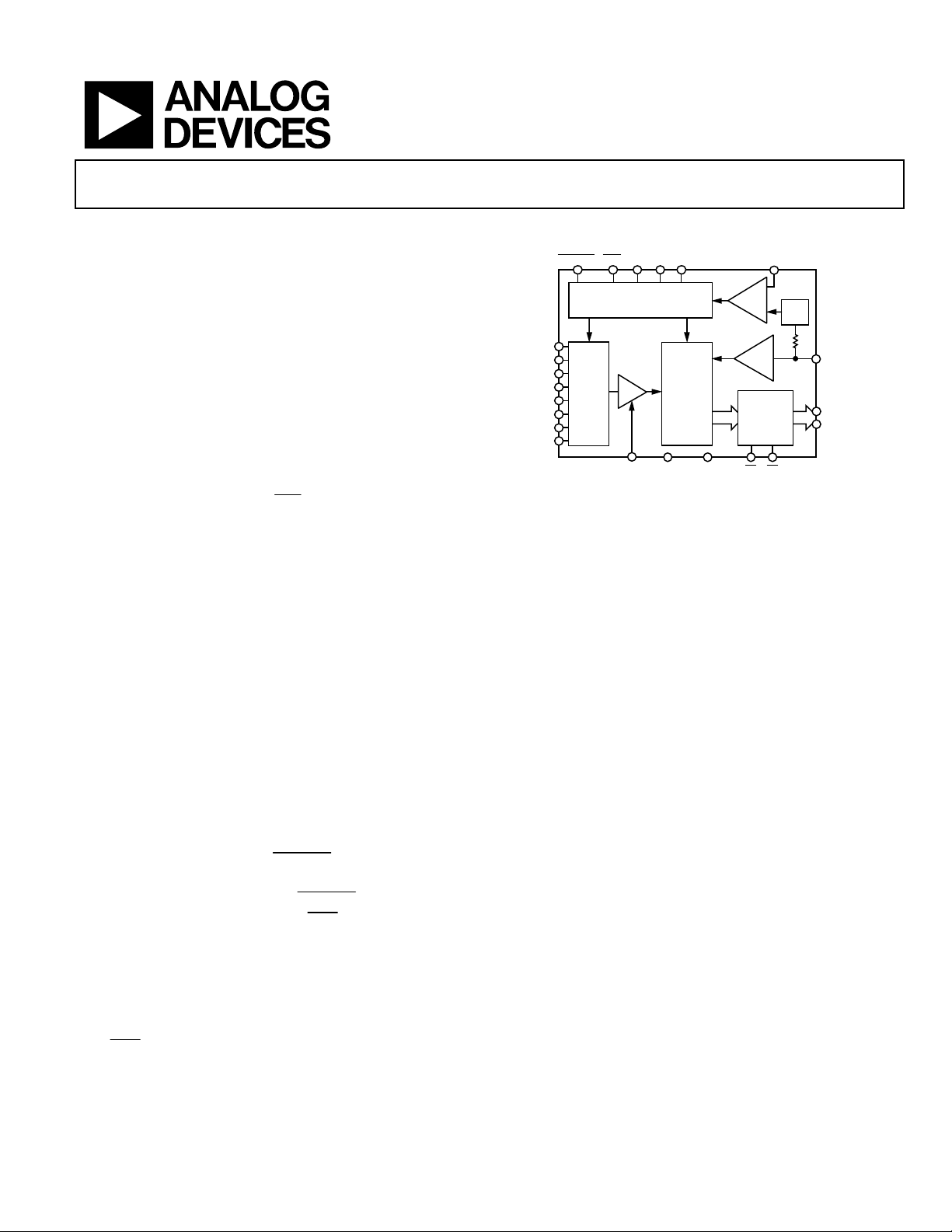

FUNCTIONAL BLOCK DIAGRAM

COMP

BUF

PARALLEL

PORT

RD

CS

DD

2.5V

REF

V

REF IN/OUT

DB7

DB0

06179-001

CONVST

EOC

A0 A1 A2

CONTROL

LOGIC

IN1

IN2

IN3

INPUT

IN4

IN5

IN6

IN7

IN8

MUX

T/H

V

MID

AGND

8-BIT

HALF

FLASH

ADC

Figure 1.

DGND

The AD7829-1 is a high speed 8-channel, microprocessorcompatible, 8-bit analog-to-digital converter with a maximum

throughput of 2 MSPS. The AD7829-1 contains an on-chip

reference of 2.5 V (2% tolerance); a track-and-hold amplifier;

a 420 ns, 8-bit half-flash ADC; and a high speed parallel

interface. The converter can operate from a single 3 V ± 10%

and 5 V ± 10% supply.

The AD7829-1 combines the convert start and power-down

functions at one pin, that is, the

CONVST

pin. This allows a

unique automatic power-down at the end of a conversion to be

implemented. The logic level on the

after the end of a conversion when an

CONVST

EOC

pin is sampled

(end of conversion)

signal goes high, and if it is logic low at that point, the ADC is

powered down. The parallel interface is designed to allow easy

interfacing to microprocessors and DSPs. Using only address

decoding logic, the parts are easily mapped into the microprocessor

address space.

EOC

The

pulse allows the ADCs to be used in a stand-alone

manner (see the Parallel Interface section).

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

The AD7829-1 is available in a 28-lead, wide body, small outline

IC (SOIC_W) and a 28-lead thin shrink small outline package

(TSSOP).

PRODUCT HIGHLIGHTS

1. Fast Conversion Time. The AD7829-1 has a conversion

time of 420 ns. Faster conversion times maximize the DSP

processing time in a real-time system.

2. Analog Input Span Adjustment. The V

user to offset the input span. This feature can reduce the

requirements of single-supply op amps and take into

account any system offsets.

3. FPBW (Full Power Bandwidth) of Track-and-Hold. The

track-and-hold amplifier has excellent high frequency

performance. The AD7829-1 is capable of converting fullscale input signals up to a frequency of 10 MHz, making

the parts ideally suited to subsampling applications.

4. Channel Selection. Channel selection is made without the

necessity of writing to the part.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2006 Analog Devices, Inc. All rights reserved.

pin allows the

MID

AD7829-1

TABLE OF CONTENTS

Features.............................................................................................. 1

Typical Connection Diagram ................................................... 10

Applications....................................................................................... 1

General Description ......................................................................... 1

Functional Block Diagram .............................................................. 1

Product Highlights ........................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Timing Characteristics ................................................................ 5

Timing Diagram........................................................................... 5

Absolute Maximum Ratings............................................................ 6

ESD Caution.................................................................................. 6

Pin Configuration and Function Descriptions............................. 7

Terminology ...................................................................................... 8

Circuit Information........................................................................ 10

Circuit Description..................................................................... 10

ADC Transfer Function............................................................. 11

Analog Input............................................................................... 11

Power-Up Times......................................................................... 14

Power vs. Throughput................................................................ 14

Operating Modes........................................................................ 15

Parallel Interface......................................................................... 17

Microprocessor Interfacing........................................................... 18

AD7829-1 to 8051 ...................................................................... 18

AD7829-1 to PIC16C6x/PIC16C7x......................................... 18

AD7829-1 to ADSP-21xx.......................................................... 18

Interfacing Multiplexer Address Inputs .................................. 18

Outline Dimensions....................................................................... 20

Ordering Guide .......................................................................... 20

REVISION HISTORY

7/06—Revision 0: Initial Version

Rev. 0 | Page 2 of 20

AD7829-1

SPECIFICATIONS

VDD = 3 V ± 10%, VDD = 5 V ± 10%, GND = 0 V, V

REF IN/OUT

Table 1.

Parameter Version B Unit Test Conditions/Comments

DYNAMIC PERFORMANCE fIN = 30 kHz, f

Signal to (Noise + Distortion) Ratio

Total Harmonic Distortion

1

Peak Harmonic or Spurious Noise

Intermodulation Distortion

1

1

1

2nd Order Terms −65 dB typ

3rd Order Terms −65 dB typ

Channel-to-Channel Isolation

1

DC ACCURACY

Resolution 8 Bits

Minimum Resolution for Which

No Missing Codes Are Guaranteed

Integral Nonlinearity (INL)

Differential Nonlinearity (DNL)

Gain Error

Gain Error Match

Offset Error

1

1

1

Offset Error Match

ANALOG INPUTS

2

1

1

1

VDD = 5 V ± 10% Input voltage span = 2.5 V

V

to V

IN1

Input Voltage VDD V max

IN8

0 V min

V

Input Voltage VDD − 1.25 V max Default V

MID

1.25 V min

VDD = 3 V ± 10% Input voltage span = 2 V

V

to V

IN1

Input Voltage VDD V max

IN8

0 V min

V

Input Voltage VDD − 1 V max Default V

MID

1 V min

VIN Input Leakage Current ±1 µA max

VIN Input Capacitance 15 pF max

V

Input Impedance 6 kΩ typ

MID

REFERENCE INPUT

V

Input Voltage Range 2.55 V max 2.5 V + 2%

REF IN/OUT

2.45 V min 2.5 V − 2%

Input Current 1 A typ

100 A max

ON-CHIP REFERENCE Nominal 2.5 V

Reference Error ±50 mV max

Temperature Coefficient 50 ppm/°C typ

LOGIC INPUTS

Input High Voltage, V

Input Low Voltage, V

Input High Voltage, V

Input Low Voltage, V

2.4 V min VDD = 5 V ± 10%

INH

0.8 V max VDD = 5 V ± 10%

INL

2 V min VDD = 3 V ± 10%

INH

0.4 V max VDD = 3 V ± 10%

INL

Input Current, IIN ±1 A max Typically 10 nA, VIN = 0 V to VDD

Input Capacitance, CIN 10 pF max

= 2.5 V. All specifications −40°C to +85°C, unless otherwise noted.

= 2 MHz

SAMPLE

48 dB min

−55 dB max

−55 dB max

fa = 27.3 kHz, fb = 28.3 kHz

−70 dB typ fIN = 20 kHz

8 Bits

±0.75 LSB max

±0.75 LSB max

±2 LSB max

±0.1 LSB typ

±1 LSB max

±0.1 LSB typ

See Analog Input section

= 1.25 V

MID

= 1 V

MID

Rev. 0 | Page 3 of 20

AD7829-1

Parameter Version B Unit Test Conditions/Comments

LOGIC OUTPUTS

Output High Voltage, VOH I

4 V min VDD = 5 V ± 10%

2.4 V min VDD = 3 V ± 10%

Output Low Voltage, VOL I

0.4 V max VDD = 5 V ± 10%

0.2 V max VDD = 3 V ± 10%

High Impedance Leakage Current ±1 A max

High Impedance Capacitance 10 pF max

CONVERSION RATE

Track/Hold Acquisition Time 200 ns max See Circuit Description section

Conversion Time 420 ns max

POWER SUPPLY REJECTION

VDD ± 10% ±1 LSB max

POWER REQUIREMENTS

VDD 4.5 V min 5 V ± 10%; for specified performance

5.5 V max

VDD 2.7 V min 3 V ± 10%; for specified performance

3.3 V max

IDD

Normal Operation 12 mA max 8 mA typically

Power-Down 5 A max Logic inputs = 0 V or VDD

0.2 A typ

Power Dissipation VDD = 3 V

Normal Operation 36 mW max Typically 24 mW

Power-Down

200 kSPS 9.58 mW typ

500 kSPS 23.94 mW typ

1

See the Terminology section of this data sheet.

2

Refer to the Analog Input section for an explanation of the analog input(s).

= 200 A

SOURCE

= 200 A

SINK

Rev. 0 | Page 4 of 20

AD7829-1

TIMING CHARACTERISTICS

V

Table 2.

Parameter

t1 420 420 ns max Conversion time

t2 20 20 ns min

t3 30 30 ns min

t4 110 110 ns max

70 70 ns min

t5 10 10 ns max

t6 0 0 ns min

t7 0 0 ns min

t8 30 30 ns min

3

t

9

t

10

20 20 ns max

t11 10 10 ns min

t12 15 15 ns min

t13 200 200 ns min Minimum time between new channel selection and convert start

t

POWER UP

t

POWER UP

1

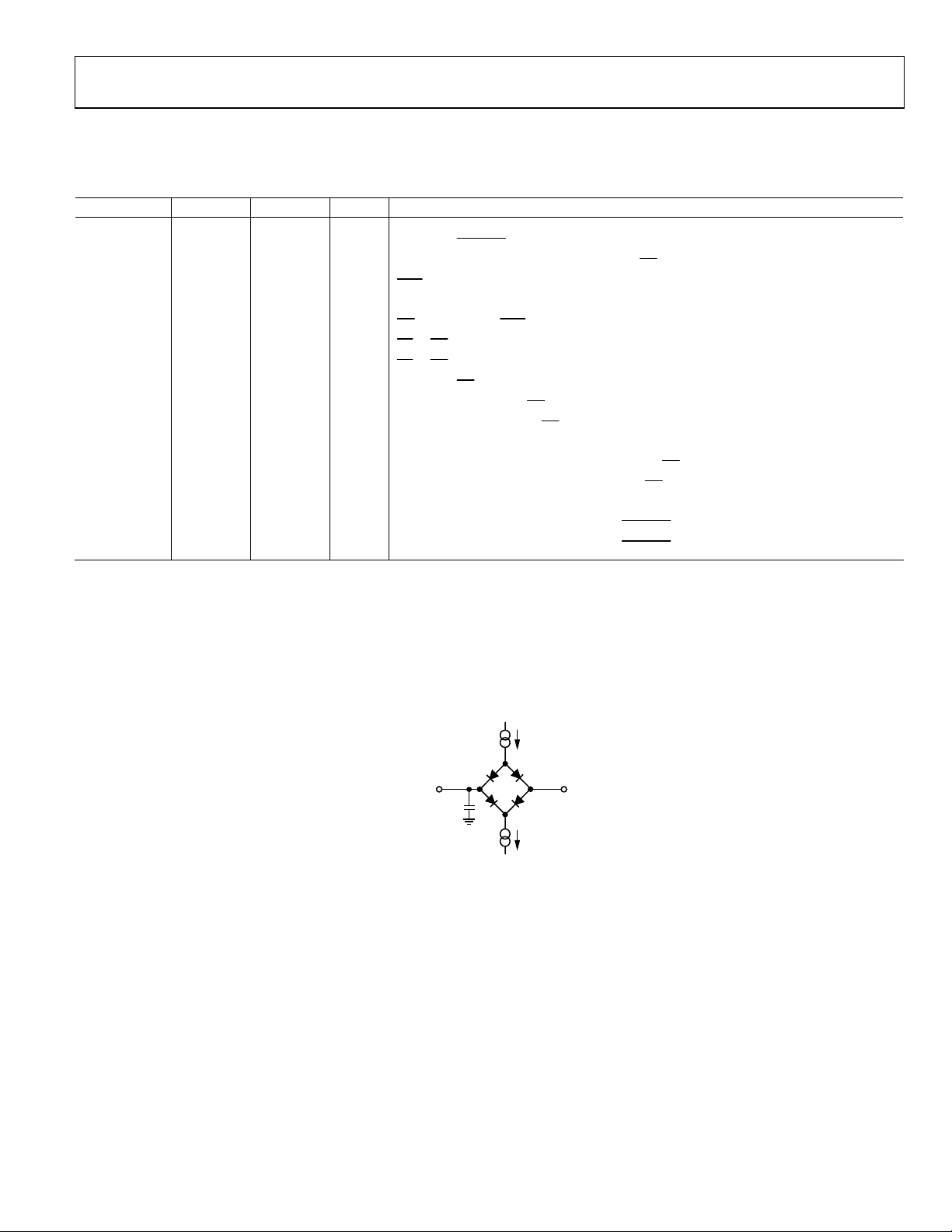

Sample tested to ensure compliance.

2

See Figure 21, Figure 22, and Figure 23.

3

Measured with the load circuit of Figure 2 and defined as the time required for an output to cross 0.8 V or 2.4 V with VDD = 5 V ± 10%, and the time required for an

output to cross 0.4 V or 2.0 V with VDD = 3 V ± 10%.

4

Derived from the measured time taken by the data outputs to change 0.5 V when loaded with the circuit of Figure 2. The measured number is then extrapolated back

to remove the effects of charging or discharging the 50 pF capacitor. This means that the time, t10, quoted in the timing characteristics is the true bus relinquish time

of the part and, as such, is independent of external bus loading capacitances.

= 2.5 V. All specifications −40°C to +85°C, unless otherwise noted.

REF IN/OUT

1, 2

5 V ± 10% 3 V ± 10% Unit Description

Minimum CONVST

Minimum time between the rising edge of RD

pulse width

EOC

rising edge to EOC pulse high

RD

to RD setup time

CS

to RD hold time

CS

Minimum RD

10 20 ns max

4

5 5 ns min

Data access time after RD

Bus relinquish time after RD

Address setup time before the falling edge of RD

Address hold time after the falling edge of RD

25 25 μs typ

1 1 μs max

Power-up time from the rising edge of CONVST

Power-up time from the rising edge of CONVST

pulse width

and the next falling edge of convert start

pulse width

low

high

using on-chip reference

using external 2.5 V reference

TIMING DIAGRAM

200µA I

TO OUTPUT

PIN

C

L

50pF

200µA I

Figure 2. Load Circuit for Access Time and Bus Relinquish Time

OL

2.1V

OH

06179-002

Rev. 0 | Page 5 of 20

AD7829-1

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted.

Table 3.

Parameter Rating

V

to AGND −0.3 V to +7 V

DD

V

to DGND −0.3 V to +7 V

DD

Analog Input Voltage to AGND

V

to V

IN1

−0.3 V to V

IN8

−0.3 V to V

V

Input Voltage to AGND −0.3 V to VDD + 0.3 V

MID

−0.3 V to V

−0.3 V to V

+ 0.3 V

DD

+ 0.3 V Reference Input Voltage to AGND

DD

+ 0.3 V Digital Input Voltage to DGND

DD

+ 0.3 V Digital Output Voltage to DGND

DD

Operating Temperature Range

−40°C to +85°C Industrial (B Version)

−65°C to +150°C Storage Temperature Range

150°C Junction Temperature

SOIC Package, Power Dissipation 450 mW

θ

Thermal Impedance 75°C/W

JA

Lead Temperature, Soldering

215°C Vapor Phase (60 sec)

220°C Infrared (15 sec)

TSSOP Package, Power Dissipation 450 mW

θ

Thermal Impedance 128°C/W

JA

Lead Temperature, Soldering

215°C Vapor Phase (60 sec)

220°C Infrared (15 sec)

ESD 1 kV

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. 0 | Page 6 of 20

Loading...

Loading...