CMOS

a

FEATURES

Single +5 V Supply

Receive Channel

Differential or Single-Ended Analog Inputs

Auxiliary Set of Analog I & Q Inputs

Two Sigma-Delta A/D Converters

Choice of Two Digital FIR Filters

Root-Raised-Cosine Rx Filters, α = 0.35

Brick Wall FIR Rx Filters

On-Chip or User Rx Offset Calibration

ADC Sampling Vernier

Three Auxiliary DACs

On-Chip Voltage Reference

Low Active Power Dissipation, Typical 45 mW

Low Sleep Mode Power Dissipation, <50 µW

28-Pin SSOP

APPLICATIONS

American TIA Digital Cellular Telephony

American Analog Cellular Telephony

Digital Baseband Receivers

GENERAL DESCRIPTION

The AD7013 is a complete low power, CMOS, TIA IS-54 baseband receive port with single +5 V power supply. The part is

TIA IS-54 Baseband Receive Port

AD7013

designed to perform the baseband conversion of I and Q

waveforms in accordance with the American (TIA IS-54)

Digital Cellular Telephone system.

The receive path consists of two high performance sigma-delta

ADCs, each followed by a FIR digital filter. A primary and

auxiliary set of IQ differential analog inputs are provided,

where either can be selected as inputs to the sigma-delta

ADCs. Also, a choice of two frequency responses are available

for the receive FIR filters; a Root-Raised-Cosine filter for

digital mode or a brick wall response for analog mode.

Differential analog inputs are provided for both I and Q

channels. On-chip calibration logic is also provided to remove

either on-chip offsets or remove system offsets. A 16-bit serial

interface is provided, interfacing easily to most DSPs. The

receive path also provides a means to vary the sampling

instant, giving a resolution to 1/32 of a symbol interval.

The auxiliary section provides two 8-bit DACs and one 10-bit

DAC for functions such as automatic gain control (AGC),

automatic frequency control (AFC) and power amplifier

control.

As it is a necessity for all digital mobile systems to use the

lowest possible power, the device has receive and auxiliary

power down options. The AD7013 is housed in a space

efficient 28-pin SSOP (Shrink Small Outline Package).

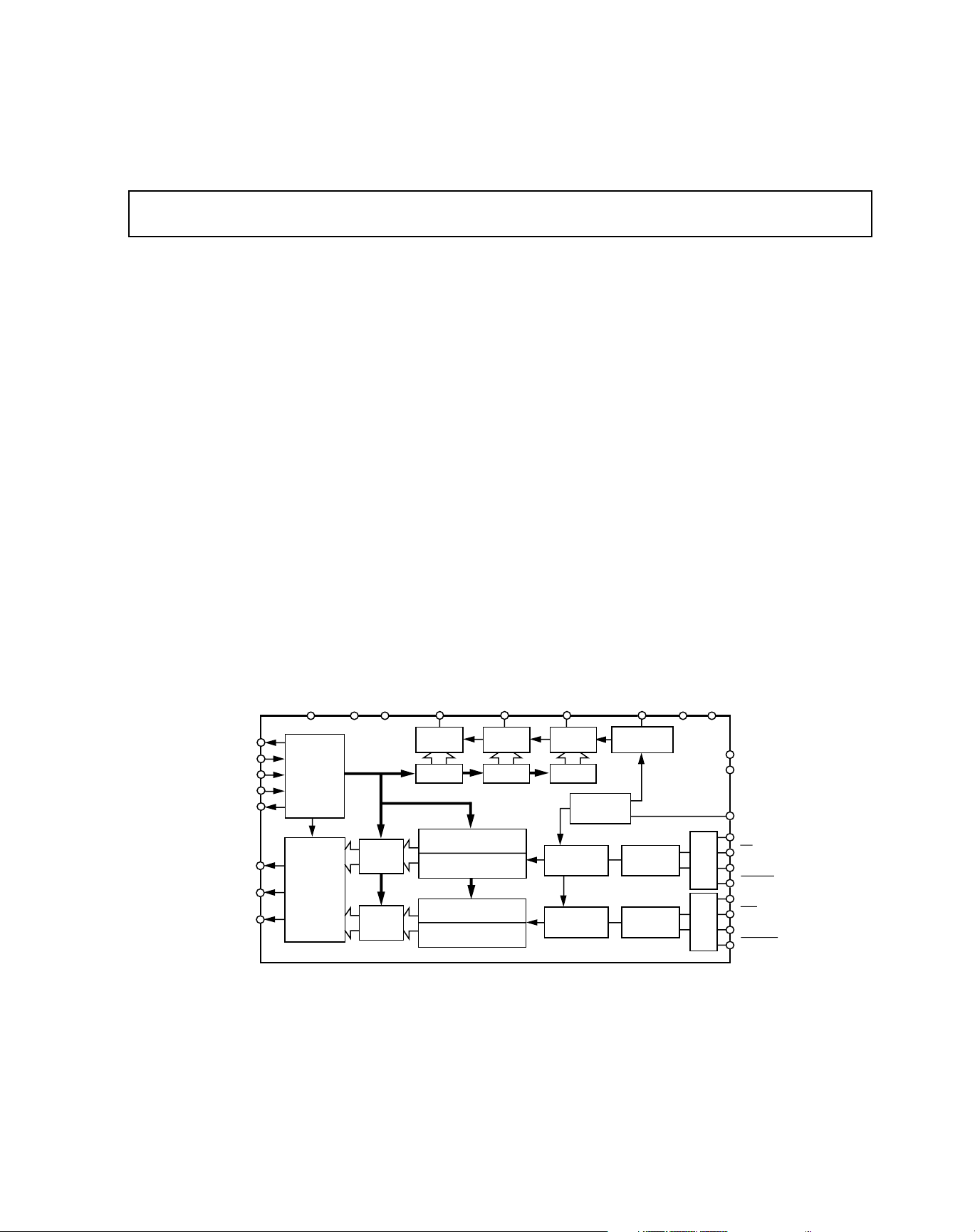

FUNCTIONAL BLOCK DIAGRAM

DxCLK

DATA IN

FRAME IN

MODE1

FRAME OUT

Rx CLK

Rx DATA

Rx FRAME

MCLK

INTERFACE

RECEIVE

CHANNEL

INTERFACE

SERIAL

SERIAL

DGND V

OFFSET

ADJUST

OFFSET

ADJUST

AUX DAC1 AUX DAC2 AUX DAC3

DD

10-BIT

AUX DAC

LATCH

ANALOG MODE

FIR DIGITAL FILTER

ROOT RAISED COSINE

FIR DIGITAL FILTER

ANALOG MODE

FIR DIGITAL FILTER

ROOT RAISED COSINE

FIR DIGITAL FILTER

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

V

FS ADJUST

8-BIT

AUX DAC

LATCH

One Technology Way, P.O. Box 9106, Norwood. MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

8-BIT

AUX DAC

LATCH

1.23V

REFERENCE

∆Σ–∆

MODULATOR

∆Σ–∆

MODULATOR

FULL-SCALE

ADJUST

SWITCHED

CAP FILTER

SWITCHED

CAP FILTER

AGND

AA

AD7013

MUX

MUX

AGND

AGND

BYPASS

IRx

IRx

AUX IRx

AUX IRx

QRx

QRx

AUX QRx

AUX QRx

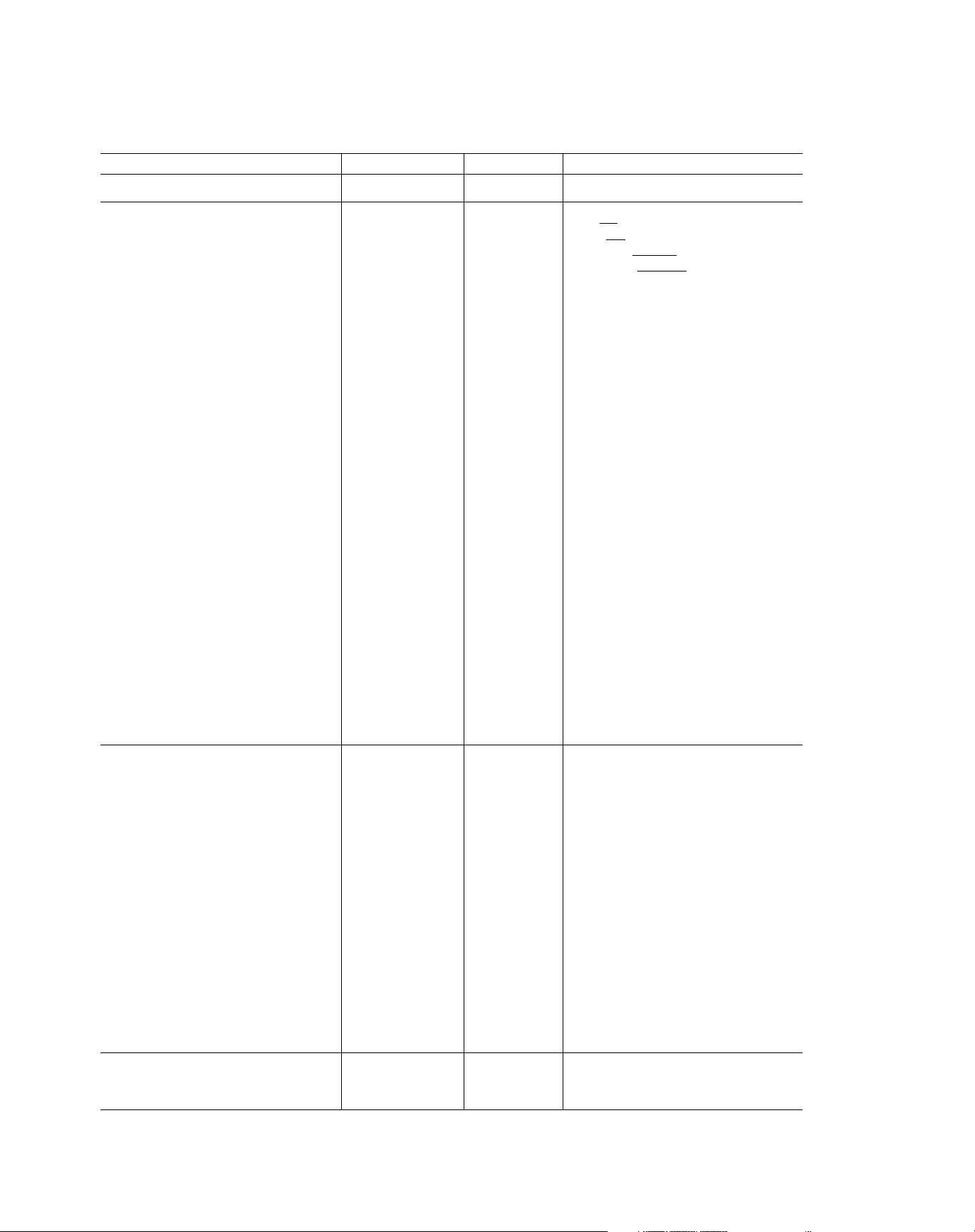

AD7013–SPECIFICATIONS

(VAA = VDD = +5 V ± 10%; AGND = DGND = 0 V; f

1

= T

to T

T

A

MIN

, unless otherwise noted)

MAX

= 6.2208 MHz;

MCLK

Parameter AD7013A Units Test Conditions/Comments

RECEIVE SECTION

ADC SPECIFICATION

Number of Input Channels 4 (IRx–IRx) and

QRx–QRx); CR12 = 0

(AUX IRx–AUX IRx) and

(AUX QRx–AUX QRx); CR12 = 1

Number of ADC Channels 2

Resolution 15 Bits

ADC Signal Range 2.6 Volts p-p Measured Using an Input Sine Wave of 3 kHz

Differential Signal Range V

± 0.65 Volts For Both Noninverting and

BIAS

Inverting Analog Inputs

Single-Ended Signal Range V

V

BIAS

± 1.3 Volts For Noninverting Analog Inputs;

BIAS

Inverting Analog Inputs = V

0.65 to (VAA–0.65) Volts min/max Differential

BIAS

1.3 to (VAA–1.3) Volts min/max Single-Ended

Input Range Accuracy ±7.5 %

Accuracy

Bias Offset Error ±7.5 mV Autocalibration; V

= min/max

BIAS

±55 mV User Calibration; I & Q Offset

Adjust Registers Equal to Zero

Dynamic Specifications

CMRR –40 dB typ Measured Using an Input Sine Wave of

3 kHz with Both Noninverting and

Inverting Inputs Tied Together

Dynamic Range 70 dB typ Digital Mode Filter; CR11 = 0

65 dB typ Analog Mode Filter; CR11 = 1

SNR

2

65 dB min Digital Mode Filter; CR11 = 0

68 dB typ

60 dB min Analog Mode Filter; CR11 = 1

63 dB typ

Input Sampling Rate 1.5552/1.28 MHz MCLK = 6.2208 MHz/5.12 MHz; MCLK/4

Output Word Rate 97.2/80 kHz MCLK = 6.2208 MHz/5.12 MHz;

4 × Sampling of the Symbol Rate, MCLK/64

48.6/40 kHz MCLK = 6.2208 MHz/5.12 MHz;

2 × Sampling of the Symbol Rate, MCLK/128

RECEIVE DIGITAL FILTERS

Digital Mode MCLK = 6.2208 MHz

Root-Raised-Cosine α = 0.35

Settling Time 329.2 µs

Absolute Group Delay 164.6 µs

Frequency Response

0–7.8975 kHz ±0.05 dB max

11.9 kHz –3.0 dB

16.4025 kHz –19 dB

> 30 kHz –66 dB max

Analog Mode MCLK = 5.12 MHz

Brick Wall Filter

Settling Time 400 µs

Absolute Group Delay 200 µs

Frequency Response

0–8 kHz 0 to –0.5 dB max

11.4 kHz –3.0 dB

15 kHz –24 dB

>17 kHz –68 dB max

TIA IS-54 RECEIVE SPECIFICATIONS

Error Vector Magnitude

Error Offset Magnitude

3

3

2 % rms typ Measured Using a Full-Scale Input

1 % rms typ

–2–

REV. A

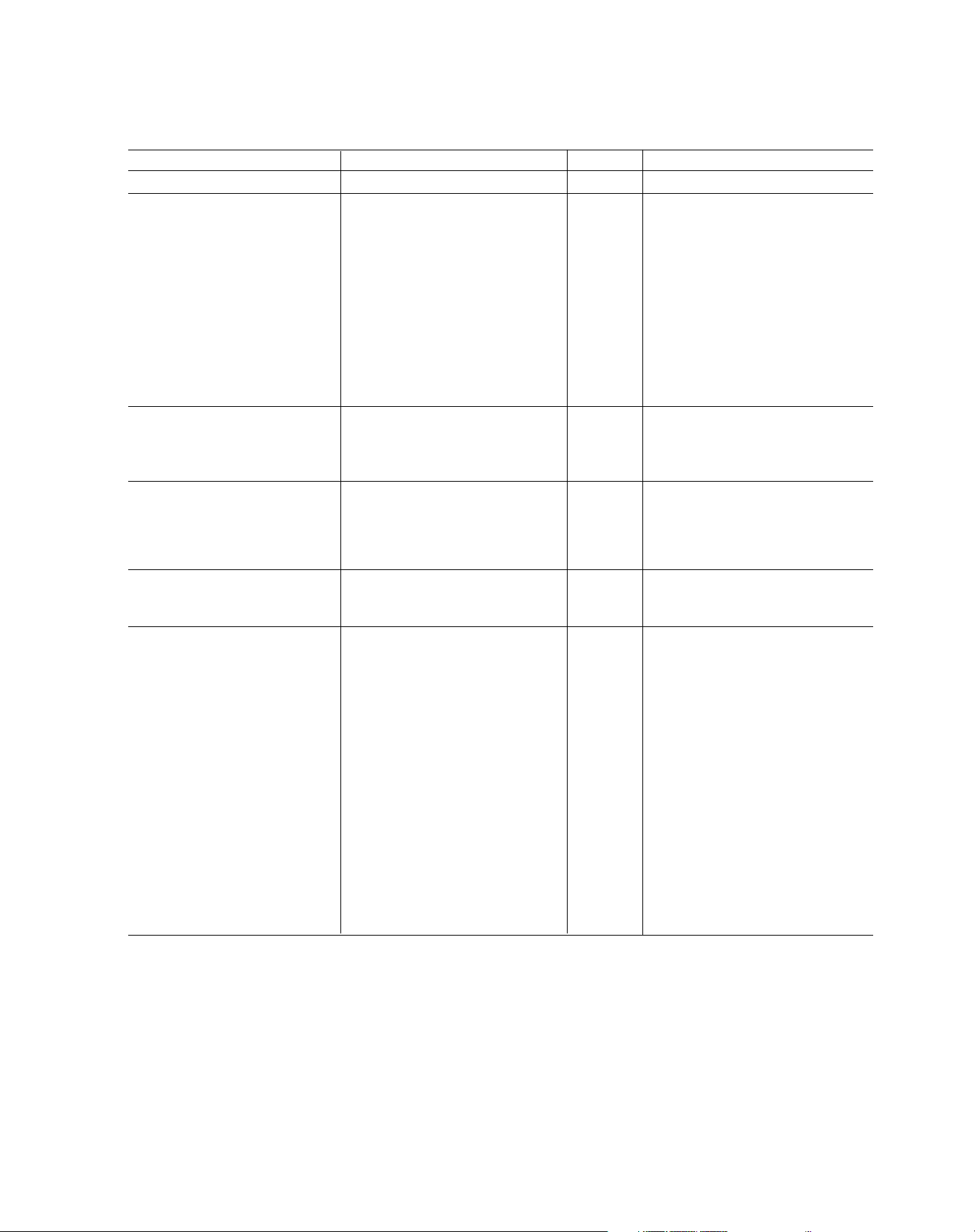

Parameter AD7013A Units Test Conditions/Comments

AUXILIARY SECTION

AUX DAC1 AUX DAC2 AUX DAC3

Resolution 10 8 8 Bits

DC Accuracy

Integral ±3 ± 1 ±1 LSBs max

Differential –1.5/+4 ±1 ± 1 LSBs max AUX DAC2 & AUX DAC3 Guaranteed

Monotonic

Zero Code Leakage ±500 ±500 ±500 nA max

Gain Error ±7.5 ±7.5 ±7.5 % max

Output Full-Scale Current 566 280 280 µAR

Output Impedance

4

2MΩ typ

= 18 kΩ

SET

Output Voltage Compliance 2.6 Volts max

Coding Binary

Power Down Option Yes

REFERENCE SPECIFICATIONS

V

REF

1.23 Volts typ

Reference Accuracy ±5 % max

Reference Impedance 20 kΩ typ

LOGIC INPUTS

, Input High Voltage VDD–0.9 V min

V

INH

V

, Input Low Voltage 0.9 V max

INL

, Input Current 10 µA max

I

INH

CIN, Input Capacitance 10 pF max

AD7013

LOGIC OUTPUTS

V

, Output High Voltage VDD–0.4 V min |I

OH

VOL, Output Low Voltage 0.4 V max |I

| ≤ 40 µA

OUT

| ≤ 1.6 mA

OUT

POWER SUPPLIES

V

DD

5

I

DD

4.5/5.5 V

MIN/VMAX

All Sections Active 10.5 mA max CR14 = CR15 = CR16 = CR17 = 1

9 mA typ MCLK = 6.2208 MHz; 80 pF

Load on DxCLK

ADCs Active Only 8.6 mA max CR14 = 1; CR15 = CR16 = CR17 = 0

MCLK = 6.2208 MHz; 80 pF

Load on DxCLK

AUX DACs Active Only 2.2 mA max CR14 = 0; CR15 = CR16 = CR17 = 1;

MCLK Inactive, MCLK = 0 V

10-Bit AUX DAC Active 1.6 mA max CR14 = CR15 = CR16 = 0; CR17 = 1;

MCLK Inactive, MCLK = 0 V

All Sections Powered Down

6

2 mA max CR14 = CR15 = CR16 = CR17 = 0

MCLK = 6.2208 MHz; 80 pF

Load on DxCLK

30 µA typ MCLK =100 kHz; 80 pF

Load on DxCLK

10 µA max MCLK Inactive, MCLK = 0 V

NOTES

1

Operating temperature ranges as follows: A version: –40°C to +85°C.

2

SNR calculation includes noise and distortion components.

3

See Terminology.

4

Sampled tested only.

5

Measured while the digital inputs are static and equal to 0 V or VDD.

6

With all sections powered down, IDD is proportional to the capacitive load on DxCLK. For example, IDD is typically 1.7 mA with 80 pF load and 600 µA with

10 pF load.

Specifications subject to change without notice.

REV. A

–3–

AD7013

TERMINOLOGY

Sampling Rate

This is the rate at which the modulators on the receive channels

sample the analog input.

Output Rate

This is the rate at which data words are made available at the

RxDATA pin.

Integral Nonlinearity

This is the maximum deviation from a straight line passing through

the endpoints of the DAC or ADC transfer function.

Differential Nonlinearity

This is the difference between the measured and the ideal 1 LSB

change between any two adjacent codes in the DAC or ADC.

Dynamic Range

Dynamic Range is the ratio of the maximum rms input signal to the

rms noise of the converter, expressed logarithmically, in decibels

(dB = 20 log

[ratio]).

10

Signal to (Noise + Distortion) Ratio

This is the measured ratio of signal to (noise + distortion) at the

output of the receive channel. The signal is the rms amplitude of

the fundamental. Noise is the rms sum of all nonfundamental

signals up to half the sampling frequency (f

/2), excluding dc. The

S

ratio is dependent upon the number of quantization levels in the

digitization process; the more levels, the smaller the quantization

noise. The theoretical signal to (noise + distortion) ratio for a sine

wave is given by:

Signal to (Noise + Distortion) = (6.02N + 1.76) dB

Settling Time

This is the digital filter settling time in the AD7013 receive section.

Bias Offset Error

This is the amount of offset in the receive channel ADC when the

differential inputs are tied together.

Receive Error Vector Magnitude

This is a measure of the rms signal error vector introduced by the

receive Root-Raised Cosine digital filter. This is measured by

applying an ideal transmit signal (i.e., an ideal π/4 DQPSK

modulator and an ideal transmit Root-Raised Cosine filter) to the

receive channel and measuring the resulting rms error vector.

Offset Vector Magnitude

This is a measure of the offset vector introduced by the AD7013 as

illustrated in the figure below. The offset vector is calculated so as to

minimize the rms error vector for each of the constellation points.

ERROR

Q

VECTOR

ABSOLUTE MAXIMUM RATINGS

(TA = +25°C unless otherwise noted)

1

VAA, VDD to GND ......................... –0.3 V to +7 V

AGND to DGND ........................–0.3 V to +0.3 V

Digital I/O Voltage to DGND ........... –0.3 V to V

+0.3 V

DD

Analog I/O Voltage to AGND ........... –0.3 V to VDD +0.3 V

Operating Temperature Range

Industrial (A Version) ................... –40°C to +85°C

Storage Temperature Range ............... –65°C to +150°C

Maximum Junction Temperature ...................+150°C

SSOP θ

Thermal Impedance ....................+122°C/W

JA

Lead Temperature Soldering

Vapor Phase (60 sec) ...........................+215°C

Infrared (15 sec) ..............................+220°C

NOTES

1

Stresses above those listed under “Absolute Maximum Ratings” may cause perma-

nent damage to the device. This is a stress rating only and functional operation of

the device at these or any other conditions above those listed in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions extended periods may affect device reliability.

PIN CONFIGURATION

V

1

AA

IRx

2

IRx

QRx

QRx

AGND

3

4

5

6

AD7013

7

TOP VIEW

8

(Not to Scale)

9

10

11

12

13

14

AUX IRx

AUX IRx

AUX QRx

AUX QRx

MODE1 DATA IN

Rx FRAME

Rx DATA DGND

Rx CLK FRAME OUT

BYPASS

28

AGND

27

FS ADJUST

26

AGND

25

AUX DAC1

24

AUX DAC2

23

AUX DAC3

22

V

21

MCLK

20

DxCLK

19

18

FRAME IN

17

16

15

DD

ORDERING GUIDE

Model Temperature Range Package Option*

AD7013ARS –40°C to +85°C RS-28

*RS = SSOP.

SIGNAL

OFFSET

VECTOR

VECTOR

I

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

this device features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

–4–

WARNING!

ESD SENSITIVE DEVICE

REV. A

AD7013

PIN FUNCTION DESCRIPTIONS

SSOP Pin

Number Mnemonic Function

POWER SUPPLY

1V

21 V

AA

DD

10, 25, 27 AGND Analog Ground.

16 DGND Digital Ground. Both AGND and DGND should be externally tied together.

ANALOG SIGNAL AND REFERENCE

28 BYPASS Reference Decoupling Output. A 10 nF decoupling capacitor should be connected

2, 4 IRx, IRx Differential Analog Inputs for the I receive channel. These are the primary receive

6, 8 QRx, QRx Differential Analog Inputs for the Q receive channel. These are the primary receive

3, 5 AUX IRx,

7, 9 AUX QRx,

AUX IRx Auxiliary Differential Analog Inputs for the I receive channel. The Auxiliary inputs

AUX QRx Auxiliary Differential Analog Inputs for the Q receive channel. The Auxiliary inputs

24 AUX DAC1 Analog output from the 10-bit auxiliary DAC.

3, 22 AUX DAC2, AUX DAC3 Analog outputs from the 8-bit auxiliary DACs.

26 FS ADJUST An external resistor is connected from this pin to ground to determine the full-

Positive Power Supply for Analog section. A 0.1 µF decoupling capacitor should be

connected between this pin and AGND.

Positive Power Supply for Digital section. A 0.1 µF decoupling capacitor should be

connected between this pin and DGND. Both V

and VDD should be externally

AA

tied together.

between this pin and AGND.

analog inputs and are selected by setting CR12 to a zero in the command register.

analog inputs and are selected by setting CR12 to a zero in the command register.

are selected by setting CR12 to a one in the command register.

are selected by setting CR12 to a one in the command register.

scale current for AUX DAC1, AUX DAC2, and AUX DAC3.

SERIAL INTERFACE AND CONTROL

20 MCLK Master Clock, Digital Input. When operating in IS-54 Digital mode this pin should

be driven by a 6.2208 MHz CMOS compatible clock source and 5.12 MHz clock

source for Analog Mode.

19 DxCLK Transmit Clock, Digital Output. This is a continuous clock equal to MCLK/2 which

can be used to clock the serial port of a DSP.

17 FRAME IN Digital Input. This is used to frame the clocking in of 16-bit words for the control

registers serial interface.

18 DATA IN Digital Input. Transmit Serial Data, digital input. This pin is used to clock in

data for the serial interface on the rising edge of DxCLK.

15 FRAME OUT Digital Output. This output represents a buffered version of FRAME IN and is

controlled by the MODE1 pin. This pin can be used to daisy chain the

FRAME IN signal.

11 MODE1 Digital Input. This pin determines the state of FRAME OUT. When MODE1 is high,

FRAME IN is buffered and made available on FRAME OUT.

When MODE1 is low, FRAME OUT is in 3-STATE.

RECEIVE INTERFACE AND CONTROL

14 RxCLK Output Clock for the receive section interface.

12 RxFRAME Synchronization output for framing I and Q data at the receive interface.

13 RxDATA Receive Data, digital output. I and Q data are available at this pin via a 16-bit serial

interface. Data is valid on the falling edge of RxCLK. I and Q data are clocked out

as two 16-bits words, with the I word being clocked first. The last bit in each 16-bit

word is a I/Q flag bit, indicating whether that word is an I word or a Q word.

REV. A

–5–

AD7013

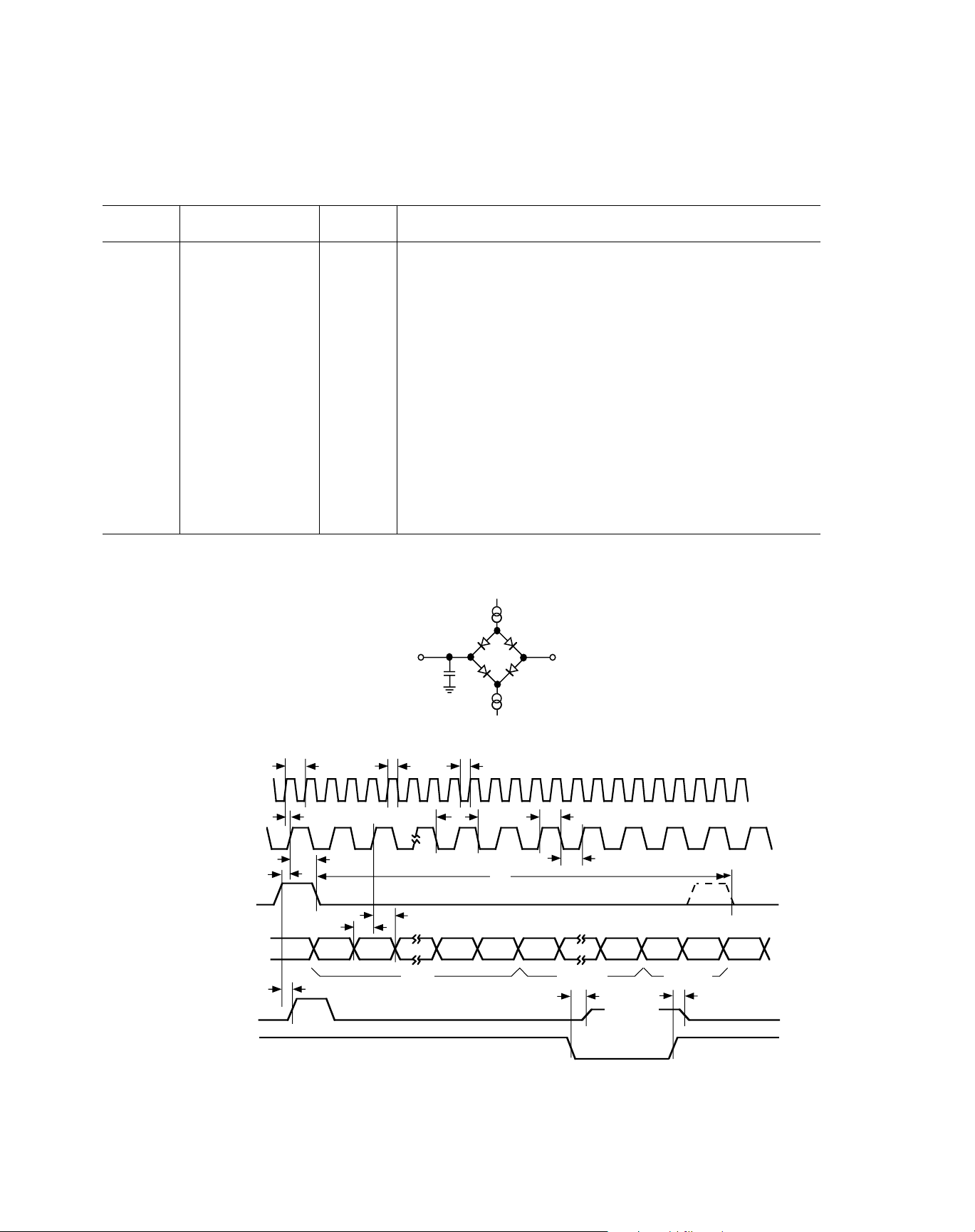

(VAA = +5 V ± 10%; VDD = +5 V ± 10%; AGND = DGND =0 V,

1

= 6.2208 MHz; TA = T

CONTROL SERIAL INTERFACE TIMING

Limit at

Parameter TA = –40°C to +85°C Units Description

f

MCLK

MIN

to T

, unless otherwise noted)

MAX

t

1

t

2

t

3

t

4

160 ns min MCLK Cycle Time

65 ns min MCLK High Time

65 ns min MCLK Low Time

20 ns min MCLK Rising Edge to DxCLK Rising Edge Propagation Delay

60 ns max

t

5

t

6

t

7

t

8

t

9

t

10

t

11

t

12

t

13

2t

1

ns DxCLK Cycle Time

t1–20 ns min DxCLK Minimum High Time

t1–20 ns min DxCLK Minimum Low Time

25 ns min DxCLK Rising Edge to FRAME IN Setup Time

10 ns min DxCLK Rising Edge to FRAME IN Hold Time

16t

5

ns min FRAME IN Cycle Time

25 ns min DxCLK Rising Edge to DATA IN Setup Time

10 ns min DxCLK Rising Edge to DATA IN Hold Time

0 ns min FRAME IN Rising Edge to FRAME OUT Rising Edge Propagation Delay

25 ns max

t

14

t

15

NOTE

1

t14 is derived from the measured time taken by the FRAME OUT pin to change 0.5 V when loaded with the circuit of Figure 1. The measured number is then

extrapolated back to remove the effects of charging or discharging the 80 pF capacitor. This means that the time quoted in the Timing Characteristics is the

25 ns max MODE1 Low to FRAME OUT 3-STATE

25 ns max MODE1 High to FRAME OUT Active

I

OL

+2.1V

I

OH

TO OUTPUT PIN

50pF

1.6mA

C

L

200µA

MxCLK (I)

DxCLK (O)

FRAME IN (I)

DATA IN (I)

FRAME OUT (O)

MODE1 (I)

Figure 1. Load Circuit for Digital Outputs

t

1

t

4

t

t

t

13

NOTE: (O) INDICATES AN OUTPUT, (I) INDICATES AN INPUT, MODE1 = LOGIC HIGH

9

8

t

2

t

12

t

11

DB9 DB8 DB1 DB0 A3 A0 S1 S0

DATA

t

3

t

5

t

10

t

6

t

7

ADDRESS IGNORED

t

14

3 – STATE

t

15

Figure 2. 16-Bit Serial Interface for Writing to the AD7013 Internal Registers

–6–

REV. A

Loading...

Loading...