+

–

+

–

+

–

+

–

+

–

50

50

10k

10k

10k

10k

V

B

–INPUT

–GAIN

SENSE

+INPUT

–GAIN

DRIVE

+GAIN

SENSE

+GAIN

DRIVE

SENSE

OUTPUT

REFERENCE

AD625

Programmable Gain

a

FEATURES

User Programmed Gains of 1 to 10,000

Low Gain Error: 0.02% Max

Low Gain TC: 5 ppm/C Max

Low Nonlinearity: 0.001% Max

Low Offset Voltage: 25 V

Low Noise 4 nV/√Hz (at 1 kHz) RTI

Gain Bandwidth Product: 25 MHz

16-Lead Ceramic or Plastic DIP Package,

20-Terminal LCC Package

Standard Military Drawing Available

MlL-Standard Parts Available

Low Cost

PRODUCT DESCRIPTION

The AD625 is a precision instrumentation amplifier specifically

designed to fulfill two major areas of application: 1) Circuits requiring nonstandard gains (i.e., gains not easily achievable with

devices such as the AD524 and AD624). 2) Circuits requiring a

low cost, precision software programmable gain amplifier.

For low noise, high CMRR, and low drift the AD625JN is the

most cost effective instrumentation amplifier solution available.

An additional three resistors allow the user to set any gain from

1 to 10,000. The error contribution of the AD625JN is less than

0.05% gain error and under 5 ppm/°C gain TC; performance

limitations are primarily determined by the external resistors.

Common-mode rejection is independent of the feedback resistor

matching.

A software programmable gain amplifier (SPGA) can be configured with the addition of a CMOS multiplexer (or other switch

network), and a suitable resistor network. Because the ON

resistance of the switches is removed from the signal path, an

AD625 based SPGA will deliver 12-bit precision, and can be

programmed for any set of gains between 1 and 10,000, with

completely user selected gain steps.

For the highest precision the AD625C offers an input offset

voltage drift of less than 0.25 µV/°C, output offset drift below

15 µV/°C, and a maximum nonlinearity of 0.001% at G = 1. All

grades exhibit excellent ac performance; a 25 MHz gain bandwidth product, 5 V/µs slew rate and 15 µs settling time.

The AD625 is available in three accuracy grades (A, B, C) for

industrial (–40°C to +85°C) temperature range, two grades (J,

K) for commercial (0°C to +70°C) temperature range, and one

(S) grade rated over the extended (–55°C to +125°C) temperature range.

REV. D

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

Instrumentation Amplifier

AD625

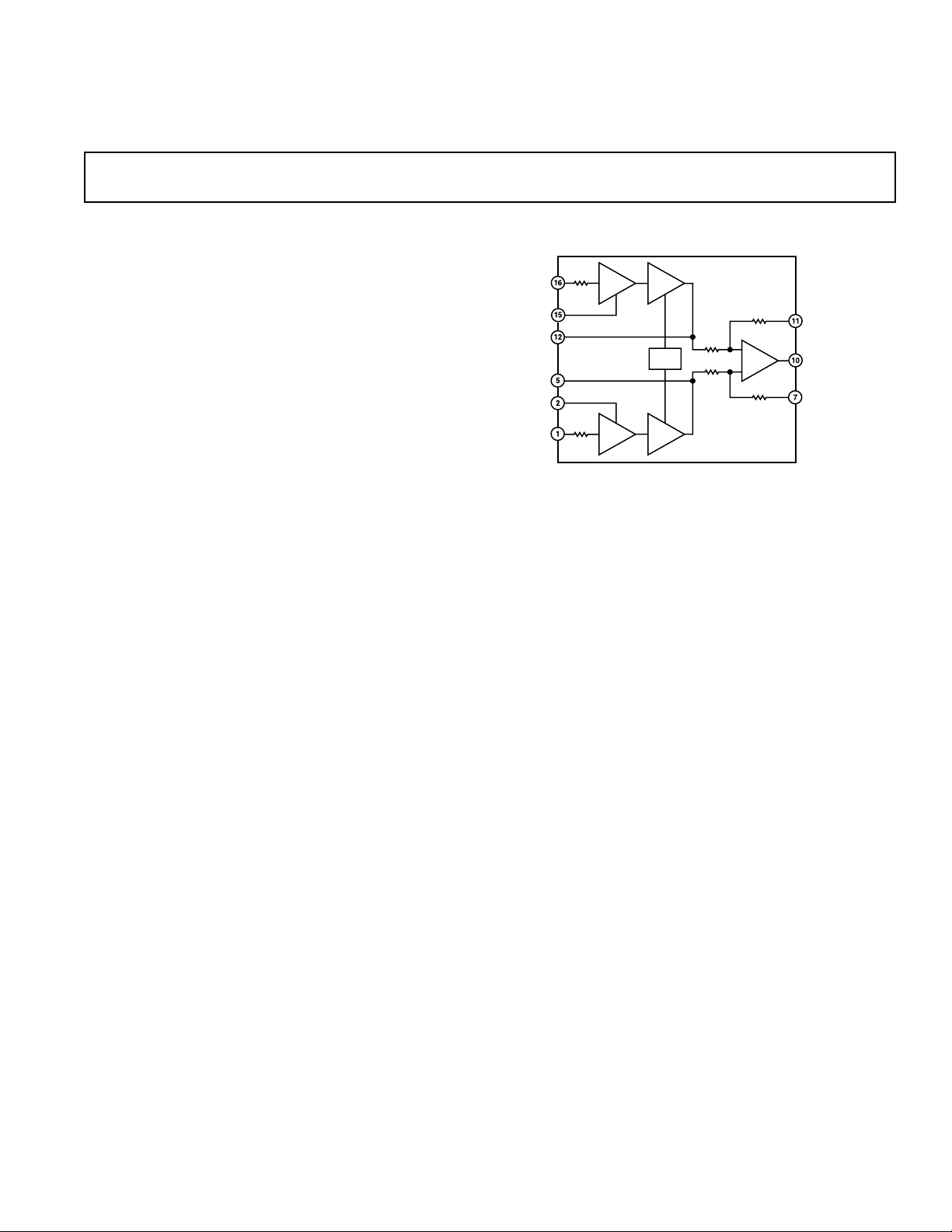

FUNCTIONAL BLOCK DIAGRAM

PRODUCT HIGHLIGHTS

1. The AD625 affords up to 16-bit precision for user selected

fixed gains from 1 to 10,000. Any gain in this range can be

programmed by 3 external resistors.

2. A 12-bit software programmable gain amplifier can be configured using the AD625, a CMOS multiplexer and a resistor

network. Unlike previous instrumentation amplifier designs,

the ON resistance of a CMOS switch does not affect the gain

accuracy.

3. The gain accuracy and gain temperature coefficient of the

amplifier circuit are primarily dependent on the user selected

external resistors.

4. The AD625 provides totally independent input and output

offset nulling terminals for high precision applications. This

minimizes the effects of offset voltage in gain-ranging

applications.

5. The proprietary design of the AD625 provides input voltage

noise of 4 nV/√Hz at 1 kHz.

6. External resistor matching is not required to maintain high

common-mode rejection.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2000

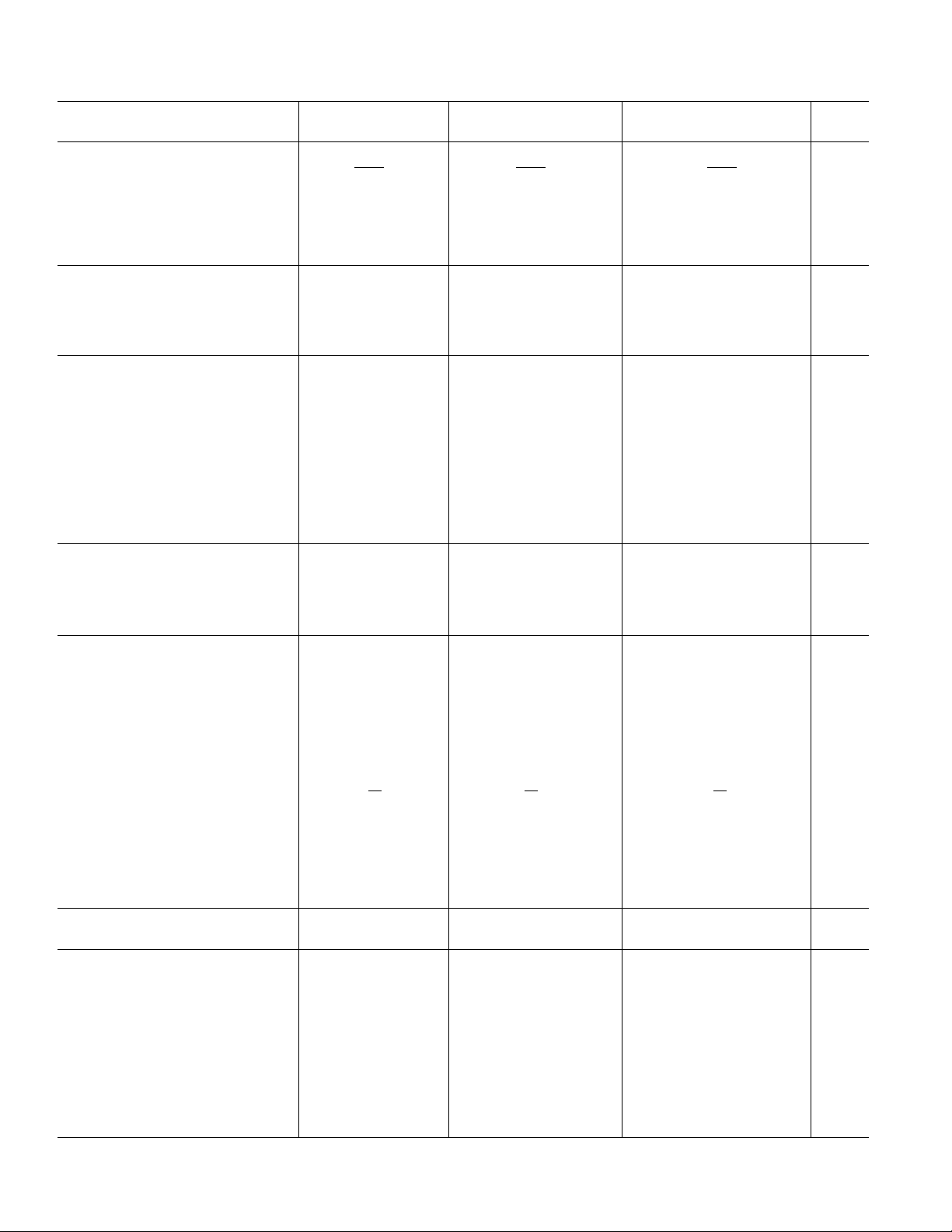

AD625–SPECIFICATIONS

AD625A/J/S AD625B/K AD625C

Model Min Typ Max Min Typ Max Min Typ Max Unit

GAIN

Gain Equation

Gain Range 1 10,000 1 10,000 1 110,000

Gain Error

Nonlinearity, Gain = 1-256 ±0.005 ± 0.002 ±0.001 %

Gain vs. Temp. Gain<1000

GAIN SENSE INPUT

Gain Sense Current 300 500 150 250 50 100 nA

vs. Temperature 5 20 2 15 2 10 nA/°C

Gain Sense Offset Current 150 500 75 250 50 100 nA

vs. Temperature 2 15 1 10 2 10 nA/°C

VOLTAGE OFFSET (May be Nulled)

Input Offset Voltage 50 200 25 50 10 25 µV

vs. Temperature 1 2/2 0.25 0.50/1 0.1 0.25 µV/°C

Output Offset Voltage 4 5 2 3 1 2 mV

vs. Temperature 20 50/50 10 25/40 10 15 µV/°C

Offset Referred to the

Input vs. Supply

INPUT CURRENT

Input Bias Current ±30

vs. Temperature ±50 ±50 ± 50 pA/°C

Input Offset Current ±2

vs. Temperature ±20 ±20 ± 20 pA/°C

INPUT

Input Impedance

Differential Resistance 1 1 1 GΩ

Differential Capacitance 4 4 4 pF

Common-Mode Resistance 1 1 1 GΩ

Common-Mode Capacitance 4 4 4 pF

Input Voltage Range

Differ. Input Linear (V

Common-Mode Linear (V

Common-Mode Rejection Ratio dc to

60 Hz with 1 kΩ Source Imbalance

OUTPUT RATING ± 10 V ±10 V ±10 V

DYNAMIC RESPONSE

Small Signal –3 dB

G = 1 (RF = 20 kΩ) 650 650 650 kHz

G = 10 400 400 400 kHz

G = 100 150 150 150 kHz

G = 1000 25 25 25 kHz

Slew Rate 5.0 5.0 5.0 V/µs

Settling Time to 0.01%, 20 V Step

G = 1 to 200 15 15 15 µs

G = 500 35 35 35 µs

G = 1000 75 75 75 µs

1

Gain>256 ±0.01 ±0.008 ±0.005 %

G = 1 70 75 75 85 80 90 dB

G = 10 85 95 90 100 95 105 dB

G = 100 95 100 105 110 110 120 dB

G = 1000 100 110 110 120 115 140 dB

G = 1 70 75 75 85 80 90 dB

G = 10 90 95 90 105 100 115 dB

G = 100 100 105 105 115 110 125 dB

G = 1000 110 115 110 125 120 140 dB

1

2

)

DL

)

CM

12 V –

(typical @ VS = 15 V, RL = 2 k and TA = + 25C, unless otherwise noted)

2 R

F

+ 1

R

G

±.0350.05 ±0.02

5 5 5 ppm/°C

50 ±20

35 ±1

±10 ±10 ± 10 V

G

×V

D

(

2

@ 5 mA @ 5 mA @ 5 mA

)

12 V –

2 R

F

+ 1

R

G

0.03 ±0.01

25 ±10

15 ±1

G

×V

D

(

)

2

12 V –

2 R

F

+ 1

R

G

G

×V

D

(

2

0.02 %

15 nA

5 nA

)

–2–

REV. D

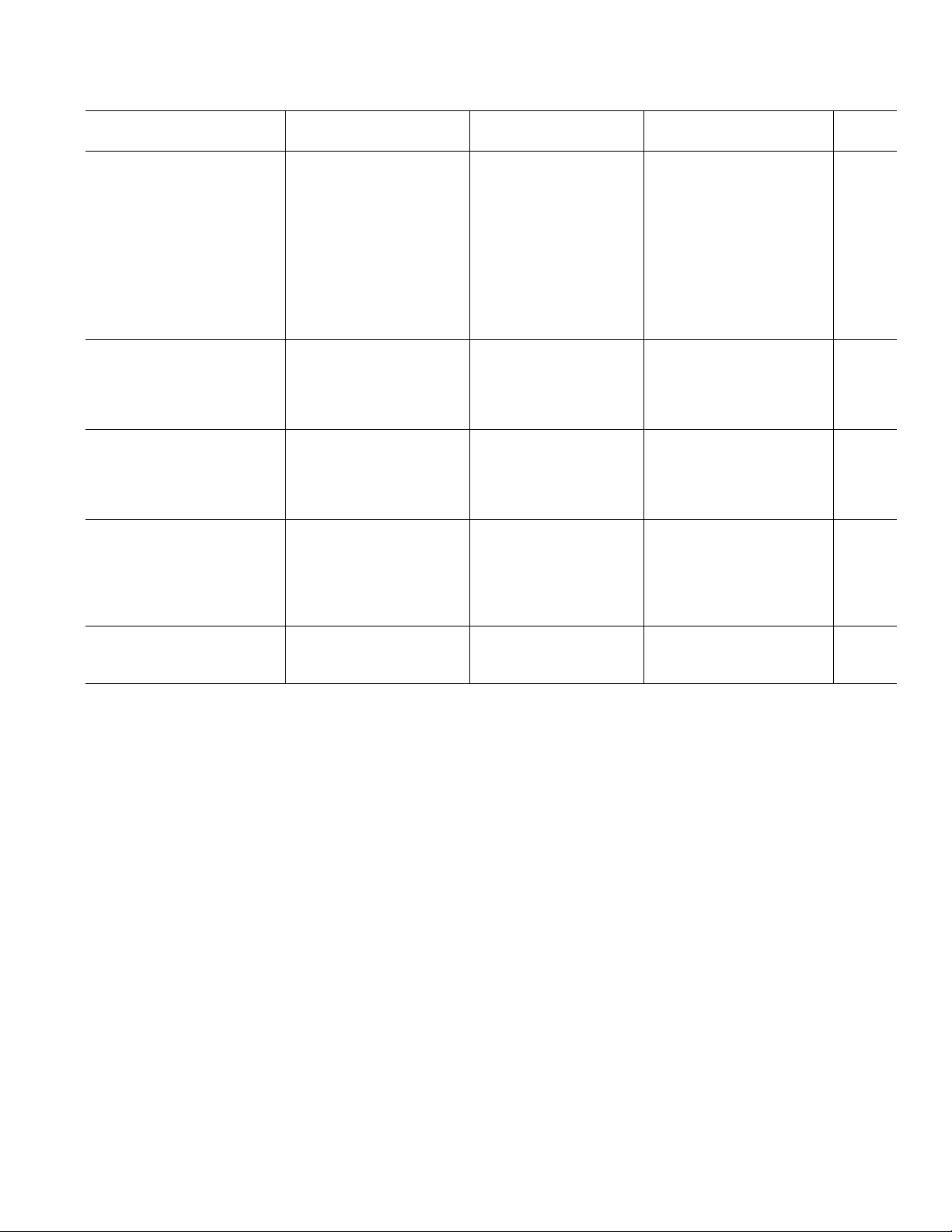

AD625

AD625A/J/S AD625B/K AD625C

Model Min Typ Max Min Typ Max Min Typ Max Unit

NOISE

Voltage Noise, 1 kHz

R.T.I. 4 4 4 nV/√Hz

R.T.O. 75 75 75 nV/√Hz

R.T.I., 0.1 Hz to 10 Hz

G = 1 10 10 10 µV p-p

G = 10 1.0 1.0 1.0 µV p-p

G = 100 0.3 0.3 0.3 µV p-p

G = 1000 0.2 0.2 0.2 µV p-p

Current Noise

0.1 Hz to 10 Hz 60 60 60 pA p-p

SENSE INPUT

R

IN

I

IN

Voltage Range ± 10 ±10 ± 10 V

Gain to Output 1 ± 0.01 1 ± 0.01 1 ± 0.01 %

REFERENCE INPUT

R

IN

I

IN

Voltage Range ± 10 ±10 ± 10 V

Gain to Output 1 ± 0.01 1 ± 0.01 1 ± 0.01 %

TEMPERATURE RANGE

Specified Performance

J/K Grades 0 +70 0 +70 °C

A/B/C Grades –40 +85 –40 +85 –40 +85 °C

S Grade –55 +125 °C

Storage –65 +150 –65 +150 –65 +150 °C

POWER SUPPLY

Power Supply Range ±6 to ± 18 ±6 to ±18 ± 6 to ± 18 V

Quiescent Current 3.5 5 3.5 5 3.5 5 mA

NOTES

1

Gain Error and Gain TC are for the AD625 only. Resistor Network errors will add to the specified errors.

2

VDL is the maximum differential input voltage at G = 1 for specified nonlinearity. VDL at other gains = 10 V/G. VD = actual differential input voltage.

Example: G = 10, VD = 0.50; VCM = 12 V – (10/2 × 0.50 V) = 9.5 V.

Specifications subject to change without notice.

All min and max specifications are guaranteed. Specifications shown in boldface are tested on all production units at final electrical test. Results from those tests are

used to calculate outgoing quality levels.

10 10 10 kΩ

30 30 30 µA

20 20 20 kΩ

30 30 30 µA

REV. D

–3–

AD625

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS*

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 18 V

Internal Power Dissipation . . . . . . . . . . . . . . . . . . . . . . 450 mW

Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±V

Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . ±V

Output Short Circuit Duration . . . . . . . . . . . . . . . . Indefinite

Storage Temperature Range (D, E) . . . . . . . . –65°C to +150°C

Storage Temperature Range (N) . . . . . . . . . . –65°C to +125°C

Operating Temperature Range

AD625J/K . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0°C to +70°C

AD625A/B/C . . . . . . . . . . . . . . . . . . . . . . . . –40°C to +85°C

S

S

AD625S . . . . . . . . . . . . . . . . . . . . . . . . . . . –55°C to +125°C

Lead Temperature Range (Soldering 10 sec) . . . . . . . . +300°C

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

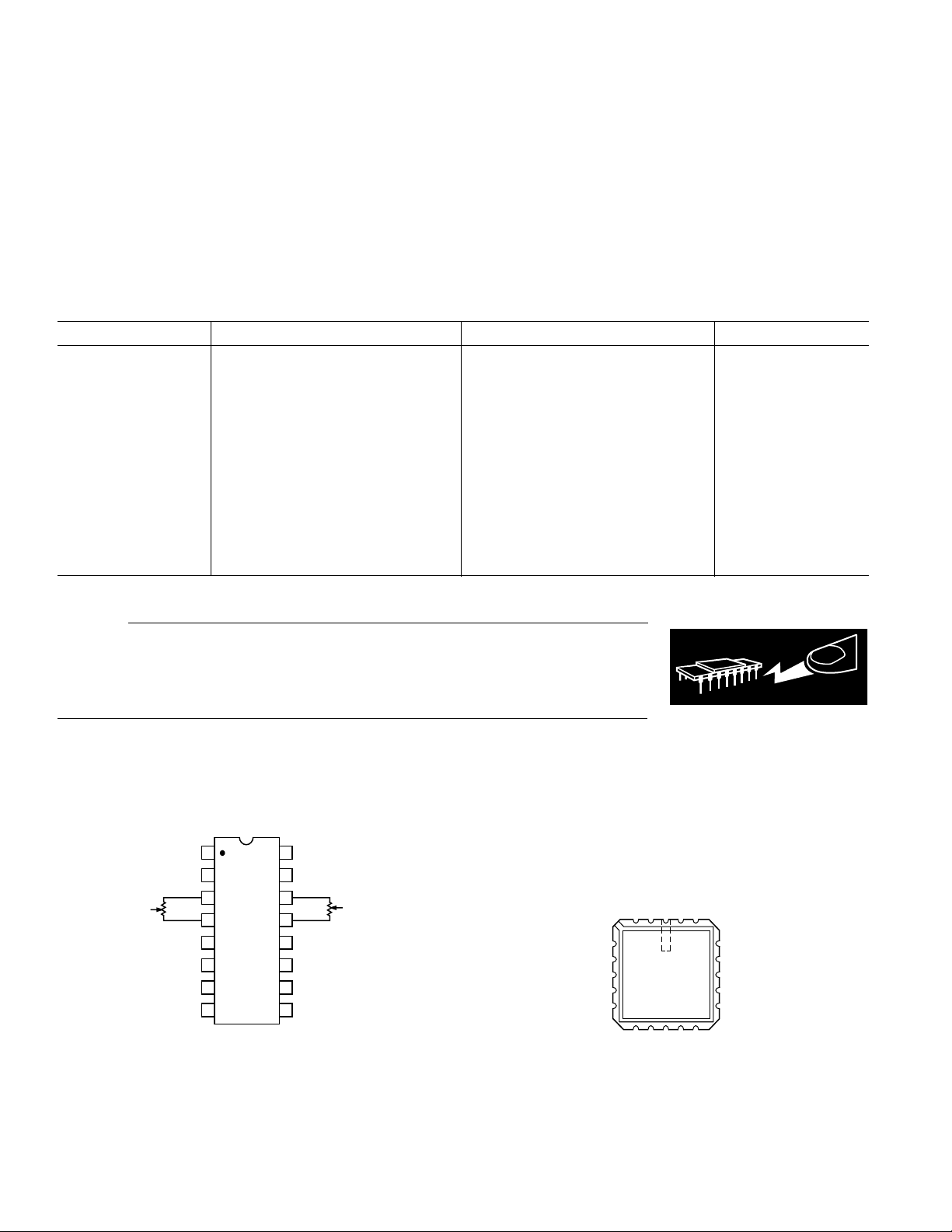

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD625AD –40°C to +85°C 16-Lead Ceramic DIP D-16

AD625BD –40°C to +85°C 16-Lead Ceramic DIP D-16

AD625BD/+ –40°C to +85°C 16-Lead Ceramic DIP D-16

AD625CD –40°C to +85°C 16-Lead Ceramic DIP D-16

AD625SD –55°C to +125°C 16-Lead Ceramic DIP D-16

AD625SD/883B –55°C to +125°C 16-Lead Ceramic DIP D-16

AD625SE/883B –55°C to +125°C 20-Terminal Leadless Chip Carrier E-20A

AD625JN 0°C to +70°C 16-Lead Plastic DIP N-16

AD625KN 0°C to +70°C 16-Lead Plastic DIP N-16

AD625ACHIPS –40°C to +85°CDie

AD625SCHIPS –55°C to +125°CDie

5962-87719012A* –55°C to +125°C 20-Terminal Leadless Chip Carrier E-20A

5962-8771901EA* –55°C to +125°C 16-Lead Ceramic DIP D-16

*Standard Military Drawing Available

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD625 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

PIN CONNECTIONS

Ceramic DIP (D) and Plastic DIP (N) Packages

1

+INPUT –INPUT

+GAIN SENSE –GAIN SENSE

RTI NULL RTO NULL

S

RTI NULL RTO NULL

+GAIN DRIVE

REFERENCE V

2

3

10k 10k+V

–V

AD625

4

TOP VIEW

5

(Not to Scale)

NC SENSE

6

7

8

S

NC = NO CONNECT

16

15

14

13

–GAIN DRIVE

12

11

10

OUT

+V

9

S

–V

S

Leadless Chip Carrier (E) Package

+INPUT

+GAIN SENSE

4

RTI NULL

5

RTI NULL

NC

+GAIN DRIVE

NC

6

(Not to Scale)

7

8

910111213

AD625

TOP VIEW

–V

S

NC

NC

20 19123

–INPUT

–GAIN SENSE

S

OUT

+V

V

18

RTO NULL

17

RTO NULL

16

NC

15

–GAIN NULL

14

SENSE

REFERENCE

NC = NO CONNECT

REV. D–4–

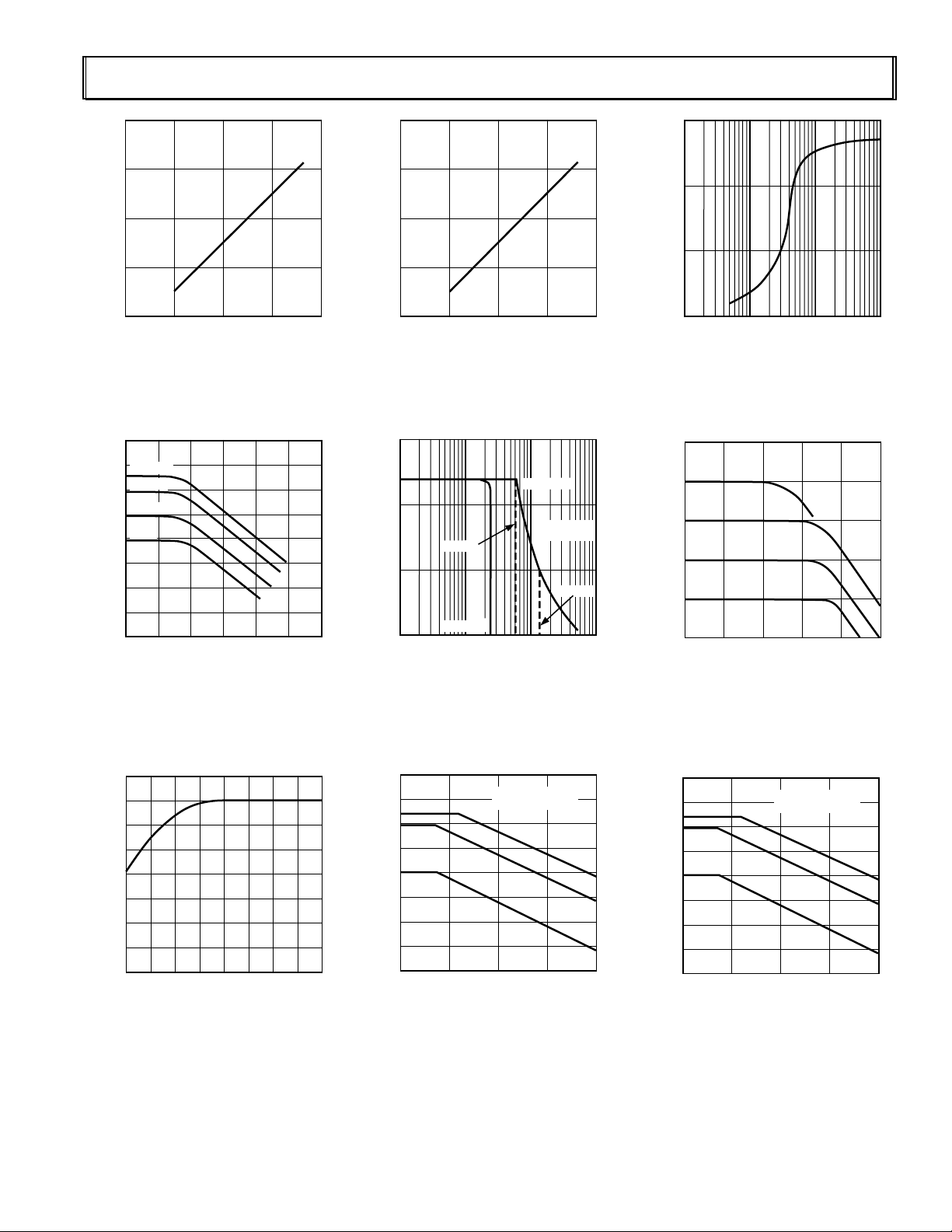

Typical Performance Characteristics–A

D625

20

15

10

25C

5

INPUT VOLTAGE RANGE – V

0

0

5101520

SUPPLY VOLTAGE – V

Figure 1. Input Voltage Range vs.

Supply Voltage, G = 1

–160

–140

G = 1000

G = 100

–120

G = 10

–100

G = 1

–80

CMRR – dM

–60

–40

–20

0

0

10 100 1k 10k 100k 10M

FREQUENCY – Hz

Figure 4. CMRR vs. Frequency

RTI, Zero to 1 k

Ω

Source Imbal-

ance

20

15

10

5

OUTPUT VOLTAGE SWING – V

0

0

5101520

SUPPLY VOLTAGE – V

Figure 2. Output Voltage Swing

vs. Supply Voltage

30

G = 1, 100

20

BANDWIDTH

LIMITED

G = 100

10

FULL POWER RESPONSE – V p-p

0

G = 500

G = 1000

1k

10k 100k 1M

FREQUENCY – Hz

Figure 5. Large Signal Frequency

Response

30

20

10

OUTPUT VOLTAGE SWING – V p-p

0

10

100 1k 10k

LOAD RESISTANCE –

Figure 3. Output Voltage Swing

vs. Load Resistance

1000

100

GAIN

10

1

1k 10k 100k 1M 10M

100

FREQUENCY – Hz

Figure 6. Gain vs. Frequency

–1

0

1

2

3

4

FROM FINAL VALUE – V

5

OS

V

6

7

0

1.0 2.0 3.0 4.0 5.0 6.0 7.0 8.0

WARM-UP TIME – Minutes

Figure 7. Offset Voltage, RTI, Turn

On Drift

REV. D

160

–VS = –15V dc+

1V p-p SINEWAVE

FREQUENCY – Hz

POWER SUPPLY REJECTION – dB

140

120

100

80

60

40

20

0

10

G = 500

G = 100

G = 1

100 1k 10k 100k

Figure 8. Negative PSRR vs.

Frequency

–5–

160

140

G = 500

120

G = 100

100

G = 1

80

60

40

20

POWER SUPPLY REJECTION – dB

0

10

100 1k 10k 100k

1V p-p SINEWAVE

FREQUENCY – Hz

Figure 9. Positive PSRR vs.

Frequency

+VS = +15V dc+

Loading...

Loading...