16-Bit Monotonic

a

FEATURES

Guaranteed 16-Bit Monotonicity

Monolithic BiMOS II Construction

60.01% Typical Nonlinearity

8- and 16-Bit Bus Compatibility

3 ms Settling to 16 Bits

Low Drift

Low Power

Low Noise

APPLICATIONS

Robotics

Closed-Loop Positioning

High-Resolution ADCs

Microprocessor-Based Process Control

MIL-STD-883 Compliant Versions Available

PRODUCT DESCRIPTION

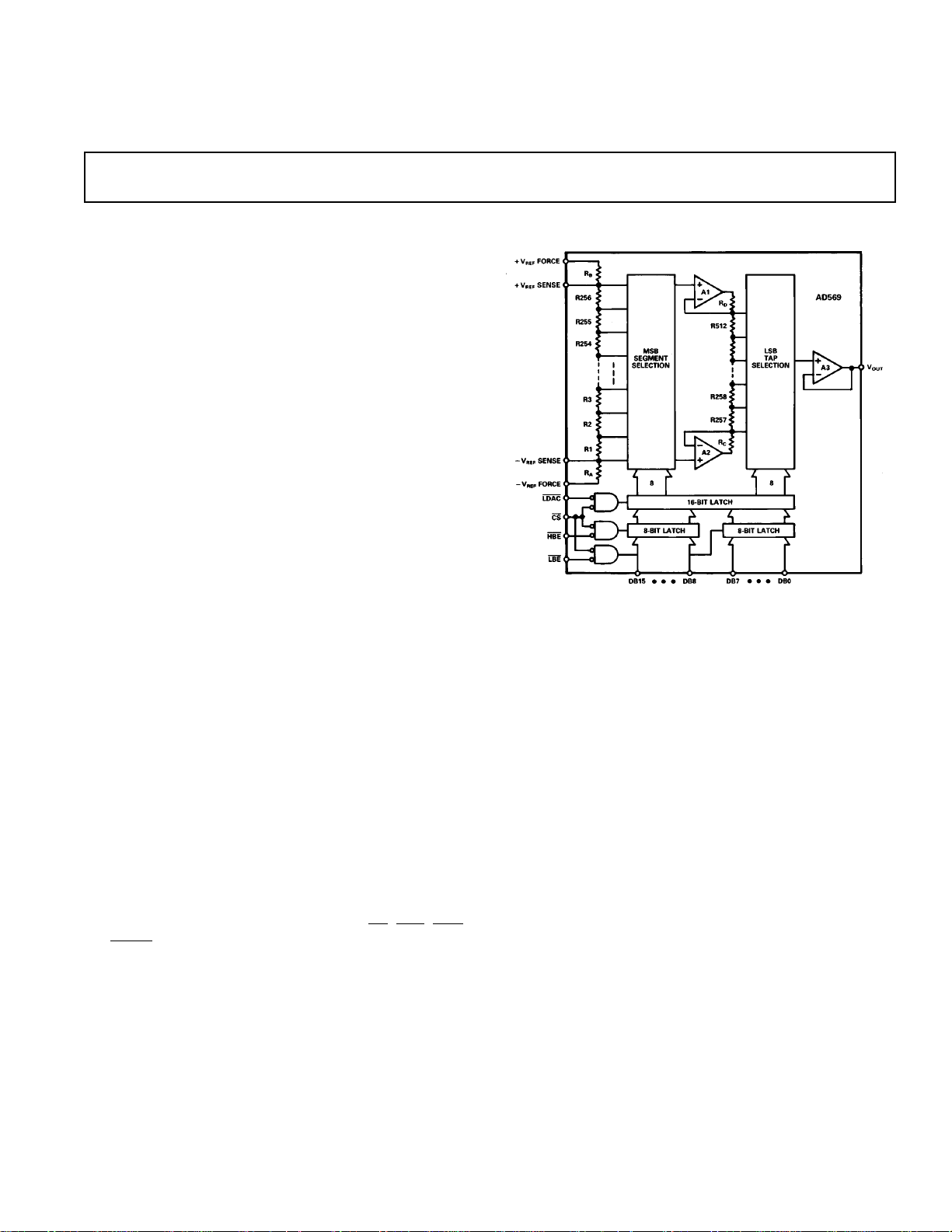

The AD569 is a monolithic 16-bit digital-to-analog converter

(DAC) manufactured in Analog Devices’ BiMOS II process.

BiMOS II allows the fabrication of low power CMOS logic

functions on the same chip as high precision bipolar linear circuitry. The AD569 chip includes two resistor strings, selector

switches decoding logic, buffer amplifiers, and double-buffered

input latches.

The AD569’s voltage-segmented architecture insures 16-bit

monotonicity over time and temperature. Integral nonlinearity is

maintained at ±0.01%, while differential nonlinearity is

±0.0004%. The on-chip, high-speed buffer amplifiers provide a

voltage output settling time of 3 µs to within ±0.001% for a

full-scale step.

The reference input voltage which determines the output range

can be either unipolar or bipolar. Nominal reference range is

±5 V and separate reference force and sense connections are

provided for high accuracy applications. The AD569 can operate with an ac reference in multiplying applications.

Data may be loaded into the AD569’s input latches from 8- and

16-bit buses. The double-buffered structure simplifies 8-bit bus

interfacing and allows multiple DACs to be loaded asynchronously and updated simultaneously. Four TTL/LSTTL/5 V

CMOS-compatible signals control the latches:

and

LDAC

The AD569 is available in five grades: J and K versions are

specified from 0°C to +70°C and are packaged in a 28-pin plastic DIP and 28-pin PLCC package; AD and BD versions are

specified from –25°C to +85°C and are packaged in a 28-pin

ceramic DIP. The SD version, also in a 28-pin ceramic DIP, is

specified from –55°C to +125°C.

CS, LBE, HBE,

Voltage Output D/A Converter

AD569

FUNCTIONAL BLOCK DIAGRAM

PRODUCT HIGHLIGHTS

1. Monotonicity to 16 bits is insured by the AD569’s voltagesegmented architecture.

2. The output range is ratiometric to an external reference or ac

signal. Gain error and gain drift of the AD569 are negligible.

3. The AD569’s versatile data input structure allows loading

from 8- and 16-bit buses.

4. The on-chip output buffer amplifier can supply ± 5 V into a

1 kΩ load, and can drive capacitive loads of up to 1000 pF.

5. Kelvin connections to the reference inputs preserve the gain

and offset accuracy of the transfer function in the presence of

wiring resistances and ground currents.

6. The AD569 is available in versions compliant with MIL-STD-

883. Refer to the Analog Devices Military Products Databook or current AD569/883B data sheet for detailed

specifications.

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

AD569–SPECIFICATIONS

(TA = +258C, +VS = +12 V, –VS = –12 V, +V

otherwise noted.)

= +5 V, –V

REF

= –5 V, unless

REF

Model AD569JN/JP/AD AD569KN/KP/BD AD569SD

Parameter Min Typ Max Min Typ Max Min Typ Max Units

RESOLUTION 16 16 16 Bits

LOGIC INPUTS

V

(Logic “l”) 2.0 5.5 2.0 5.5 2.0 5.5 Volts

IH

V

(Logic “0”) 0 0.8 0 0.8 0 0.8 Volts

IL

I

(VIH = 5.5 V) 10 10 10 µA

IH

IIL (VIL = 0 V) 10 10 10 µA

TRANSFER FUNCTION

CHARACTERISTICS

Integral Nonlinearity ±0.02

T

MIN

to T

MAX

±0.02

Differential Nonlinearity ±1/2

T

to T

MIN

MAX

MAX

MAX

MAX

2

MAX

3

2

2

2

–5 +5 –5 +5 –5 +5 Volts

Unipolar Offset

T

to T

MIN

Bipolar Offset

T

to T

MIN

Full Scale Error

T

to T

MIN

Bipolar Zero

T

to T

MIN

REFERENCE INPUT

+V

Range

REF

–V

Range –5 +5 –5 +5 –5 +5 Volts

REF

±1/2

Resistance 15 20 25 15 20 25 15 20 25 kΩ

6

0.04 ±0.01

6

0.04 ±0.02060.024

6

1 ±1/4

6

1 ±1/2

6

500

6

750

6

500

6

750

6

350

6

750

6

0.04

6

0.04

6

0.024

6

1/2

6

1

6

350

6

450

6

350

6

450

6

350

6

750

6

0.024

6

0.024

6

0.04 % FSR

6

0.04 % FSR

6

1 LSB

6

1 LSB

6

500 µV

6

750 µV

6

500 µV

6

750 µV

6

350 µV

6

750 µV

6

0.04 % FSR

6

0.04 % FSR

4

1

OUTPUT CHARACTERISTICS

Voltage –5 +5 –5 +5 –5 +5 Volts

Capacitive Load 1000 1000 1000 pF

Resistive Load 1 1 1 kΩ

Short Circuit Current 10 10 10 mA

POWER SUPPLIES

Voltage

+V

–V

S

S

+10.8 +12 +13.2 +10.8 +12 +13.2 +10.8 +12 +13.2 Volts

–10.8 –12 –13.2 –10.8 –12 –13.2 –10.8 –12 –13.2 Volts

Current

+I

S

–I

S

Power Supply Sensitivity

5

+9 +13 +9 +13 +9 +13 mA

–9 –13 –9 –13 –9 –13 mA

+10.8 V ≤ +VS ≤ +13.2 V ±0.5 62 ±0.5 62 ±0.5 62 ppm/%

–10.8 V ≥ –VS ≥ –13.2 V ±1 63 ±1 63 ±1 63 ppm/%

TEMPERATURE RANGE

Specified

JN, KN, JP, KP 0 +70 0 +70 °C

AD, BD –25 +85 –25 +85 °C

SD –55 +125 °C

Storage

JN, KN, JP, KP –65 +150 –65 +150 °C

AD, BD, SD –65 +150 –65 +150 –65 +150 °C

NOTES

1

FSR stands for Full-Scale Range, and is 10 V for a –5 V to +5 V span.

2

Refer to Definitions section.

3

For operation with supplies other than ±12 V, refer to the Power Supply and Reference Voltage Range Section.

4

Measured between +V

5

Sensitivity of Full-Scale Error due to changes in +VS and sensitivity of Offset to changes in –VS.

Specifications subject to change without notice.

Specifications shown in boldface are tested on all production units at final electrical test. Results from those tests are used to calculate outgoing quality levels. All min

and max specifications are guaranteed, although only those shown in boldface are tested on all production units.

Force and –V

REF

REF

Force.

–2–

REV. A

AC PERFORMANCE CHARACTERISTICS

These characteristics are included for Design Guidance Only and are not subject to test.

+VS = +12 V; –VS = –12 V; +V

Parameter Limit Units Test Conditions/Comments

Output Voltage Settling 5 µs max No Load Applied

(Time to ±0.001% FS 3 µs typ (DAC output measured from falling edge of

For FS Step) 6 µs max V

= +5 V; –V

REF

= –5 V excepts where stated.

REF

Load = 1 kΩ, C

OUT

= 1000 pF.

LOAD

4 µs typ (DAC output measured from falling edge of LDAC. )

AD569

LDAC.)

Digital-to-Analog Glitch 500 nV-sec typ Measured with V

= 0 V. DAC registers alternatively loaded

REF

Impulse with input codes of 8000

transition). Load = 1 kΩ.

Multiplying Feedthrough –100 dB max +V

= 1 V rms 10 kHz sine wave,

REF

–V

= 0 V

REF

Output Noise Voltage 40 nV/ÏHz typ Measured between V

Density (1 kHz-1 MHz)

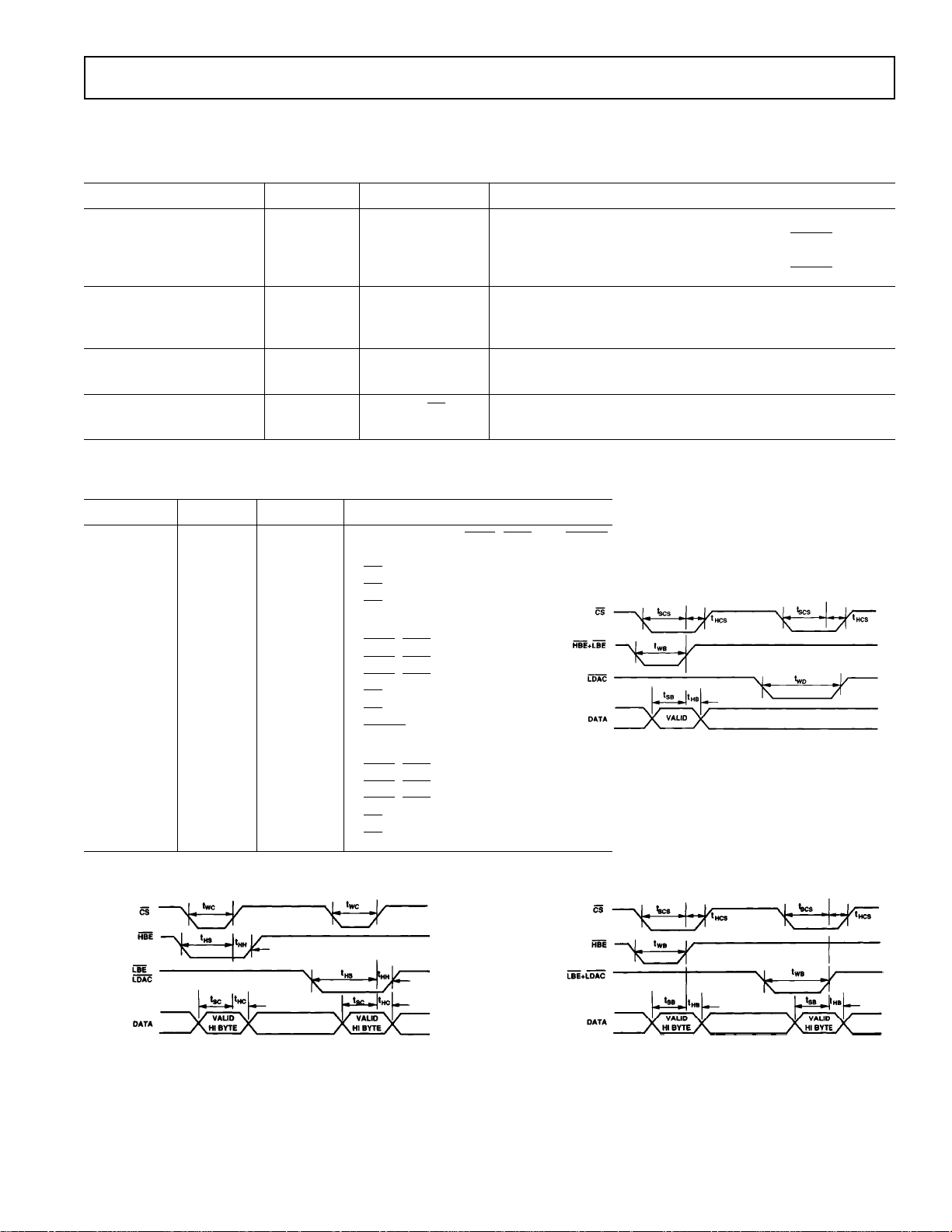

TIMING CHARACTERISTICS

(+VS = +12 V, –VS = –12 V, VIH = 2.4 V, VIL = 0.4 V,T

Parameter Limit Units Test Conditions/Comments

Case A 150 ns Pulse on HBE, LBE, and LDAC

T

= 140 ns min, THH = 10 ns min

t

t

t

WC

SC

HC

120 ns min CS Pulse Width

60 ns min CS Data Setup Time

20 ns min CS Data Hold Time

HS

Case B None

t

WB

t

SB

t

HB

t

SCS

t

HCS

t

WD

Case C None

t

WB

t

SB

t

HB

t

SCS

t

HCS

70 ns min HBE, LBE Pulse Width

80 ns min HBE, LBE Data Setup Time

20 ns min HBE, LBE Data Hold Time

120 ns min CS Setup Time

10 ns min CS Hold Time

120 ns min LDAC Pulse Width

Figure 2a. AD569 Timing Diagram – Case B

120 ns min HBE, LBE Pulse Width

80 ns min HBE, LBE Data Setup Time

20 ns min HBE, LBE Data Hold Time

120 ns min CS Setup Time

10 ns min CS Hold Time

and 0FFFH (worst-case

H

and –V

OUT

MIN

to T

MAX

REF

)

REV. A

Figure 1. AD569 Timing Diagram – Case A

Figure 2b. AD569 Timing Diagram – Case C

–3–

AD569

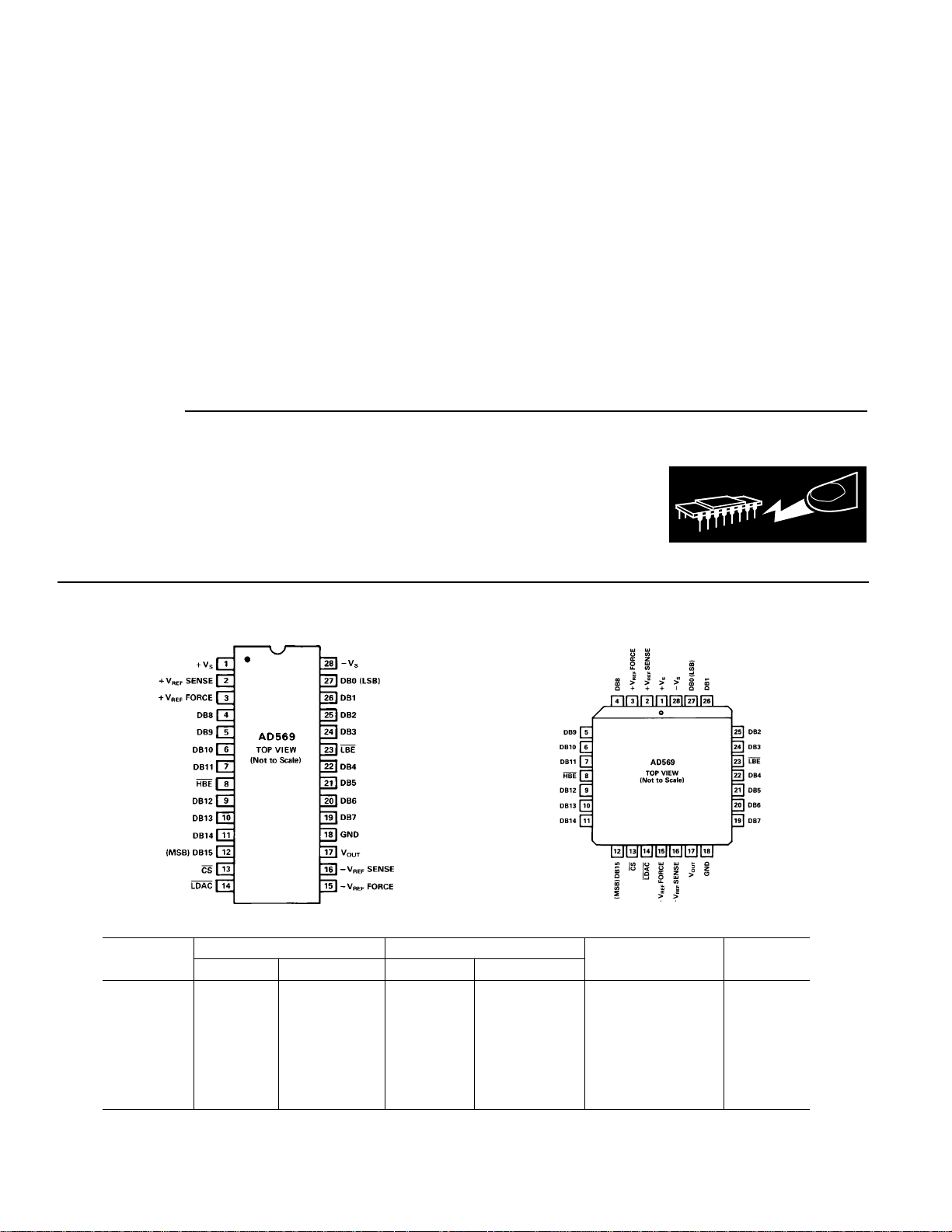

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS*

(TA = +25°C unless otherwise noted)

+VS (Pin 1) to GND (Pin 18) . . . . . . . . . . . . . . +18 V, –0.3 V

–V

(Pin 28) to GND (Pin 18) . . . . . . . . . . . . . . –18 V, +0.3 V

S

+V

(Pin 1) to –VS (Pin 28) . . . . . . . . . . . . . . . +26.4 V, –0.3 V

S

Digital Inputs

(Pins 4-14, 19-27) to GND (Pin 18) . . . . . . . . . +V

+V

Force (Pin 3) to +V

REF

–V

Force (Pin 15) to –V

REF

V

Force (Pins 3, 15) to GND (Pin 18) . . . . . . . . . . . . . ±V

REF

V

Sense (Pins 2, 16) to GND (Pin 18) . . . . . . . . . . . . . ±V

REF

V

(Pin 17) . . . . . . . . . . . . . . . . . . Indefinite Short to GND

OUT

Sense (Pin 2) . . . . . . . . ±16.5 V

REF

Sense (Pin 16) . . . . . . . ±16.5 V

REF

. . . . . . . . . . . . . . . . . . . . . . . . Momentary Short to +V

, –0.3 V

S

–V

S,

Power Dissipation (Any Package) . . . . . . . . . . . . . . . 1000 mW

Operating Temperature Range

Commercial Plastic (JN, KN, JP, KP Versions) 0°C to +70°C

Industrial Ceramic (AD, BD Versions) . . . . –25°C to +85°C

Extended Ceramic (SD Versions) . . . . . . . –55°C to +125°C

Storage Temperature . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Lead Temperature Range (Soldering, 10 secs) . . . . . . . +300°C

*Stresses above those listed under “Absolute Maximum Ratings” may cause

permanent damage to the device. This is a stress rating only and functional

S

operation of the device at these or any other conditions above those indicated in the

S

operational sections of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

S

ESD SENSITIVITY

The AD569 features input protection circuitry consisting of large “distributed” diodes and polysilicon

series resistors to dissipate both high-energy discharges (Human Body Model) and fast, low-energy

pulses (Charged Device Model). Per Method 3015.2 of MIL-STD-883C, the AD569 has been

classified as a Category A device.

Proper ESD precautions are strongly recommended to avoid functional damage or performance

degradation. Charges as high as 4000 volts readily accumulate on the human body and test equipment

and discharge without detection. Unused devices must be stored in conductive foam or shunts, and

the foam should be discharged to the destination socket before devices are removed. For further

information on ESD precautions, refer to Analog Devices’ ESD Prevention Manual.

PIN DESIGNATIONS

ORDERING GUIDE

Integral Nonlinearity Differential Nonlinearity Temperature Package

+258CT

MIN–TMAX

+258CT

MIN–TMAX

Range Option

2

Model

1

AD569JN ±0.04% ±0.04% ±1 LSB ±1 LSB 0°C to +70°C N-28

AD569JP ±0.04% ±0.04% ±1 LSB ±1 LSB 0°C to +70°C P-28A

AD569KN ±0.024% ±0.024% ±1/2 LSB ±1 LSB 0°C to +70°C N-28

AD569KP ±0.024% ±0.024% ±1/2 LSB ±1 LSB 0°C to +70°C P-28A

AD569AD ±0.04% ±0.04% ±1 LSB ±1 LSB –25°C to +85°C D-28

AD569BD ±0.024% ±0.024% ±1/2 LSB ±1 LSB –25°C to +85°C D-28

AD569SD ±0.04% ±0.04% ±1 LSB ±1 LSB –55°C to +125°C D-28

NOTES

1

For details on grade and package offerings screened in accordance with MIL-STD-883, refer to the Analog Devices Military Products Databook

or current AD569/883B data sheet.

2

D = Ceramic DIP; N = Plastic DIP; P = Plastic Leaded Chip Carrier.

–4–

REV. A

Loading...

Loading...