Serial Input, Voltage Output

VDDV

12-/14-Bit Digital-to-Analog Converters

FEATURES

Pin-compatible 12-, 14-bit digital-to-analog converters

Serial input, voltage output

Maximum output voltage range of ±10 V

Data readback

3-wire serial interface

Clear function to a user-defined voltage

Power-down function

Serial data output for daisy-chaining

16-lead TSSOP

APPLICATIONS

Industrial automation

Automatic test equipment

Process control

General-purpose instrumentation

GENERAL DESCRIPTION

The AD5530/AD5531 are single 12- and 14-bit (respectively)

serial input, voltage output digital-to-analog converters (DAC).

They utilize a versatile 3-wire interface that is compatible with

SPI®, QSPI™, MICROWIRE™, and DSP interface standards. Data

is presented to the part in a 16-bit serial word format. Serial

data is available on the SDO pin for daisy-chaining purposes.

Data readback allows the user to read the contents of the DAC

register via the SDO pin.

AD5530/AD5531

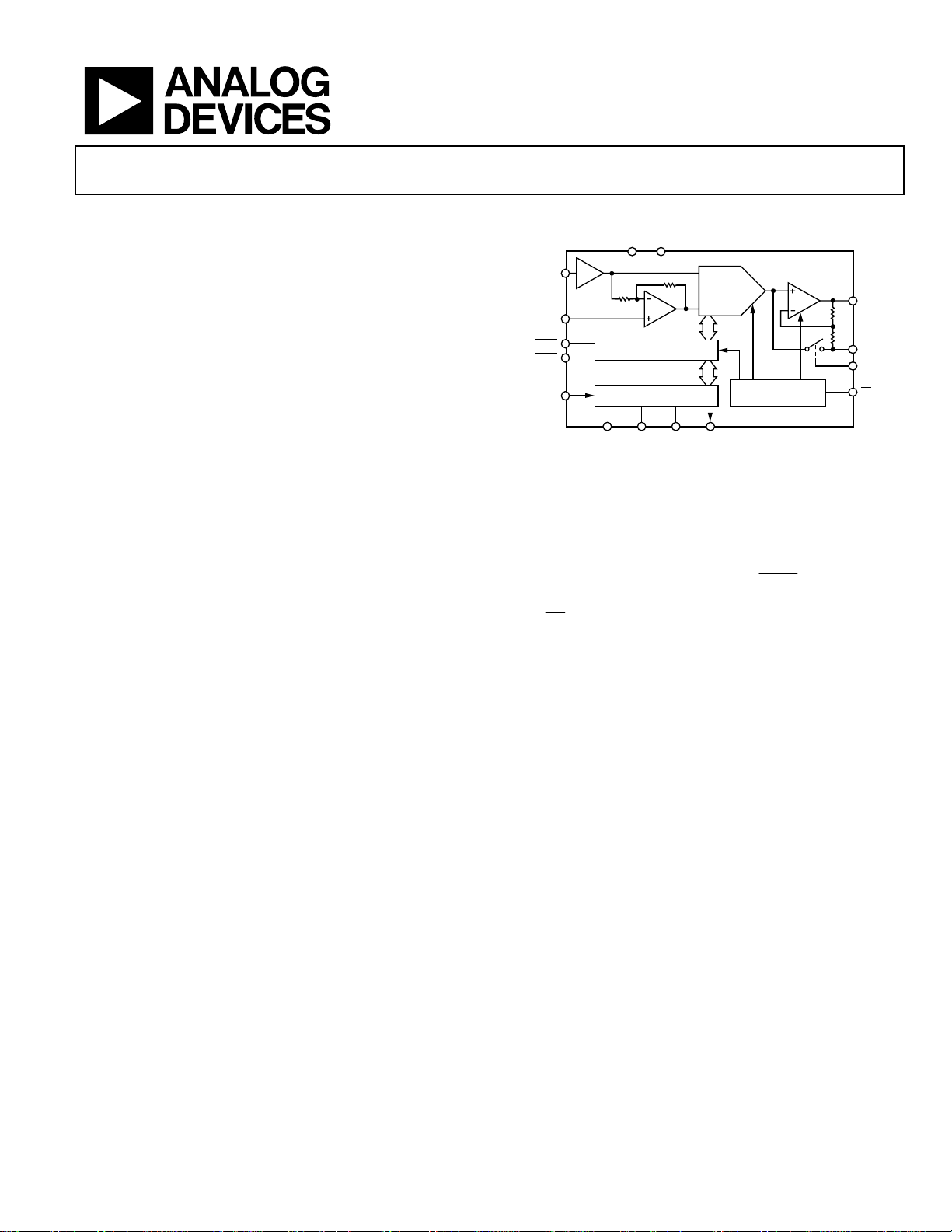

FUNCTIONAL BLOCK DIAGRAM

SS

DAC

CONTROL LOGIC

AD5530/AD5531

POWER-DOWN

LDAC

can be used to

V

OUT

R

R

DUTGND

CLR

PD

REFIN

REFAGND

LDAC

RBEN

SDIN

R

DAC REGIS TER

SHIFT REGISTER

GND

SCLK SYNC SDO

R

12-/14-BIT

Figure 1.

The DAC output is buffered by a gain of two amplifier and

referenced to the potential at DUTGND.

update the output of the DAC asynchronously. A power-down

PD

pin (

a

) allows the DAC to be put into a low power state, and

CLR

pin allows the output to be cleared to a user-defined

voltage, the potential at DUTGND.

The AD5530/AD5531 are available in 16-lead TSSOP.

0938-001

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2007 Analog Devices, Inc. All rights reserved.

AD5530/AD5531

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

AC Performance Characteristics ................................................ 5

Standalone Timing Characteristics............................................ 5

Daisy-Chaining and Readback Timing Characteristics.......... 6

Absolute Maximum Ratings............................................................ 7

ESD Caution.................................................................................. 7

Pin Configuration and Function Descriptions............................. 8

Typical Performance Characteristics ............................................. 9

Terminology .................................................................................... 12

Theory of Operation ...................................................................... 13

DAC Architecture....................................................................... 13

Serial Interface ............................................................................ 13

PD

Function................................................................................ 13

Readback Function .................................................................... 13

CLR

Function.............................................................................. 13

Output Voltage............................................................................ 14

Bipolar Configuration................................................................ 14

Microprocessor Interfacing........................................................... 15

AD5530/AD5531 to ADSP-21xx.............................................. 15

AD5530/AD5531 to 8051 Interface......................................... 15

AD5530/AD5531 to MC68HC11 Interface............................ 15

Applications Information.............................................................. 17

Optocoupler Interface................................................................ 17

Serial Interface to Multiple AD5530s or AD5531s ................ 17

Daisy-Chaining Interface with Multiple AD5530s or

AD5531s ...................................................................................... 17

Outline Dimensions....................................................................... 18

Ordering Guide .......................................................................... 18

REVISION HISTORY

1/07—Rev. A to Rev. B

Updated Format..................................................................Universal

Changes to Figure 28...................................................................... 17

3/06—Rev. 0 to Rev. A

Change to Table 3 ............................................................................. 5

Change to Figure 4 ........................................................................... 8

Change to Output Voltage Section ............................................... 14

Change to Ordering Guide............................................................ 18

5/02—Revision 0: Initial Version

Rev. B | Page 2 of 20

AD5530/AD5531

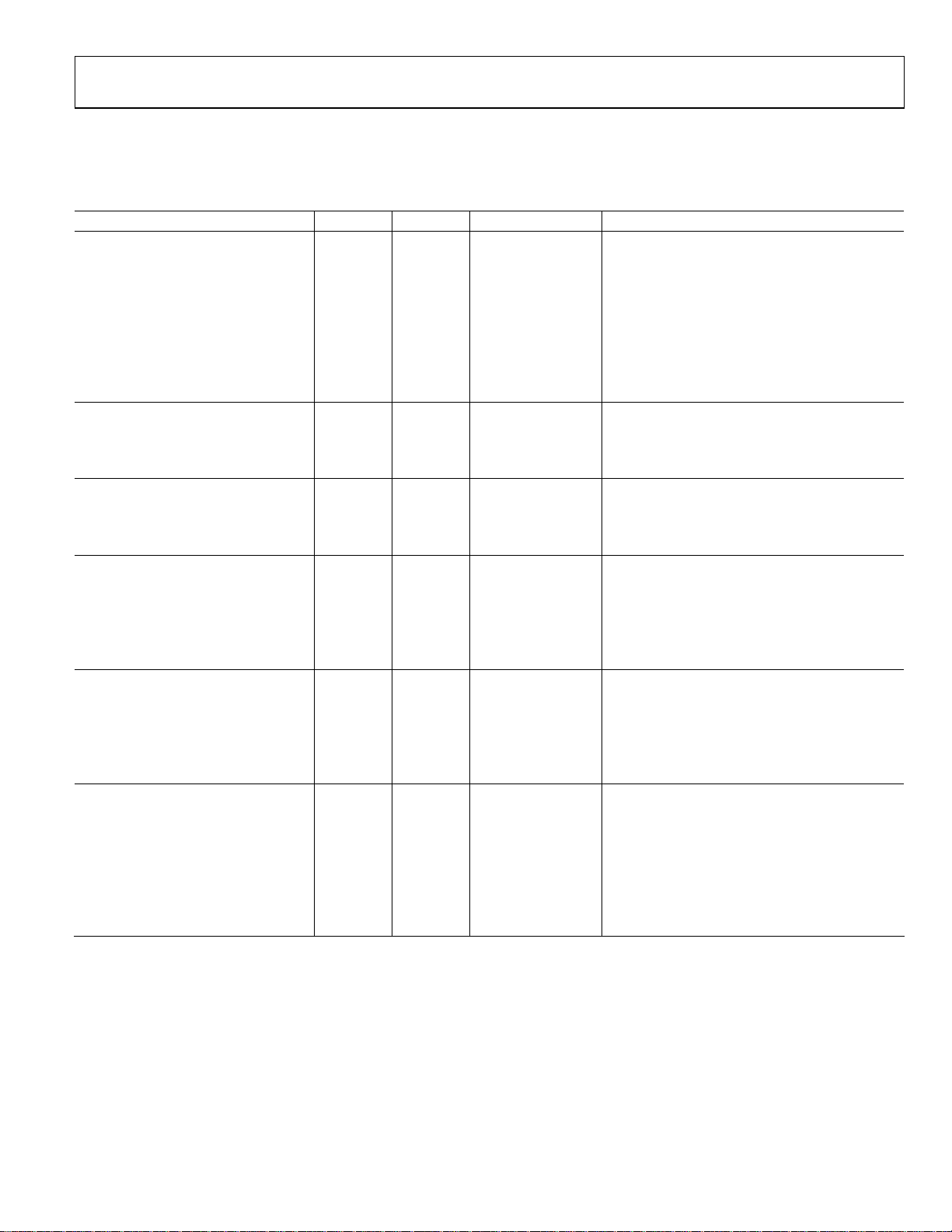

SPECIFICATIONS

VDD = 15 V ± 10%; VSS = −15 V ± 10%; GND = 0 V; RL = 5 kΩ and CL = 220 pF to GND. All specifications T

MIN

to T

, unless otherwise noted.

MAX

Table 1.

Parameter

1

AD5530 AD5531 Unit Test Conditions/Comments

ACCURACY

Resolution 12 14 Bits

Relative Accuracy ±1 ±2 LSB max

Differential Nonlinearity ±1 ±1 LSB max Guaranteed monotonic over temperature

Zero-Scale Error ±2 ±8 LSB max Typically within ±1 LSB

Full-Scale Error ±2 ±8 LSB max Typically within ±1 LSB

Gain Error ±1 ±4 LSB typ

Gain Temperature Coefficient2 0.5 0.5 ppm FSR/°C typ

10 10 ppm FSR/°C max

REFERENCE INPUTS2

Reference Input Range 0 to 5 0 to 5 V min to V max Max output range ±10 V

DC Input Resistance 100 100 MΩ typ

Input Current ±1 ±1 μA max Per input, typically ±20 nA

DUTGND INPUT2

DC Input Impedance 60 60 kΩ typ

Max Input Current ±0.3 ±0.3 mA typ

Input Range −4 to +4 −4 to +4 V min to V max Max output range ±10 V

O/P CHARACTERISTICS2

Output Voltage Swing ±10 ±10 V max

Short-Circuit Current 15 15 mA max

Resistive Load 5 5 kΩ min To 0 V

Capacitive Load 1200 1200 pF max To 0 V

DC Output Impedance 0.5 0.5 Ω max

DIGITAL I/O

V

, Input High Voltage 2.4 2.4 V min

INH

V

, Input Low Voltage 0.8 0.8 V max

INL

I

, Input Current ±10 ±10 μA max Total for all pins

INH

CIN, Input Capacitance

SDO VOL, Output Low Voltage 0.4 0.4 V max I

2

10 10 pF max 3 pF typical

= 1 mA

SINK

POWER REQUIREMENTS

VDD/VSS +15/−15 +15/−15 V nom ±10% for specified performance

Power Supply Sensitivity

ΔFull Scale/ΔVDD 110 110 dB typ

ΔFull Scale/ΔVSS 100 100 dB typ

IDD 2 2 mA max Outputs unloaded

ISS 2 2 mA max Outputs unloaded

IDD in Power-Down 150 150 μA max Typically 50 μA

1

Temperature range for B Version: −40°C to +85°C.

2

Guaranteed by design, not subject to production test.

Rev. B | Page 3 of 20

AD5530/AD5531

VDD = 12 V ± 10%; VSS = −12 V ± 10%; GND = 0 V; RL = 5 kΩ and CL = 220 pF to GND; TA = T

MIN

to T

, unless otherwise noted.

MAX

Table 2.

Parameter

1

AD5530 AD5531 Unit Test Conditions/Comments

ACCURACY

Resolution 12 14 Bits

Relative Accuracy ±1 ±2 LSB max

Differential Nonlinearity ±1 ±1 LSB max Guaranteed monotonic over temperature

Zero-Scale Error ±2 ±8 LSB max Typically within ±1 LSB

Full-Scale Error ±2 ±8 LSB max Typically within ±1 LSB

Gain Error ±1 ±4 LSB typ

Gain Temperature Coefficient2 0.5 0.5 ppm FSR/°C typ

10 10 ppm FSR/°C max

REFERENCE INPUTS2

Reference Input Range 0 to 4.096 0 to 4.096 V min to V max Max output range ±8.192 V

DC Input Resistance 100 100 MΩ typ

Input Current ±1 ±1 μA max Per input, typically ±20 nA

DUTGND INPUT2

DC Input Impedance 60 60 kΩ typ

Max Input Current ±0.3 ±0.3 mA typ

Input Range −3 to +3 −3 to +3 V min to V max Max output range ±8.192 V

O/P CHARACTERISTICS2

Output Voltage Swing ±8.192 ±8.192 V max

Short-Circuit Current 15 15 mA max

Resistive Load 5 5 kΩ min To 0 V

Capacitive Load 1200 1200 pF max To 0 V

DC Output Impedance 0.5 0.5 Ω max

DIGITAL I/O

V

, Input High Voltage 2.4 2.4 V min

INH

V

, Input Low Voltage 0.8 0.8 V max

INL

I

, Input Current ±10 ±10 μA max Total for all pins

INH

CIN, Input Capacitance2 10 10 pF max 3 pF typical

SDO VOL, Output Low Voltage 0.4 0.4 V max I

= 1 mA

SINK

POWER REQUIREMENTS

VDD/VSS +12/−12 +12/−12 V nom ±10% for specified performance

Power Supply Sensitivity

ΔFull Scale/ΔVDD 110 110 dB typ

ΔFull Scale/ΔVSS 100 100 dB typ

IDD 2 2 mA max Outputs unloaded

ISS 2 2 mA max Outputs unloaded

IDD in Power-Down 150 150 μA max Typically 50 μA

1

Temperature range for B Version: −40°C to +85°C.

2

Guaranteed by design, not subject to production test.

Rev. B | Page 4 of 20

AD5530/AD5531

AC PERFORMANCE CHARACTERISTICS

VDD = 10.8 V to 16.5 V, VSS = −10.8 V to −16.5 V; GND = 0 V; RL = 5 kΩ and CL = 220 pF to GND. All specifications T

otherwise noted.

Table 3.

Parameter B Version Unit Test Conditions/Comments

DYNAMIC PERFORMANCE

Output Voltage Settling Time 20 μs typ

Full-scale change to ±½ LSB. DAC latch contents alternately

loaded with all 0s and all 1s.

Slew Rate 1.3 V/μs typ

Digital-to-Analog Glitch Impulse 120 nV-s typ

DAC latch alternately loaded with 0x0FFF and 0x1000. Not

dependent on load conditions.

Digital Feedthrough 0.5 nV-s typ Effect of input bus activity on DAC output under test.

Output Noise Spectral Density @ 1 kHz 100 nV/√Hz typ All 1s loaded to DAC.

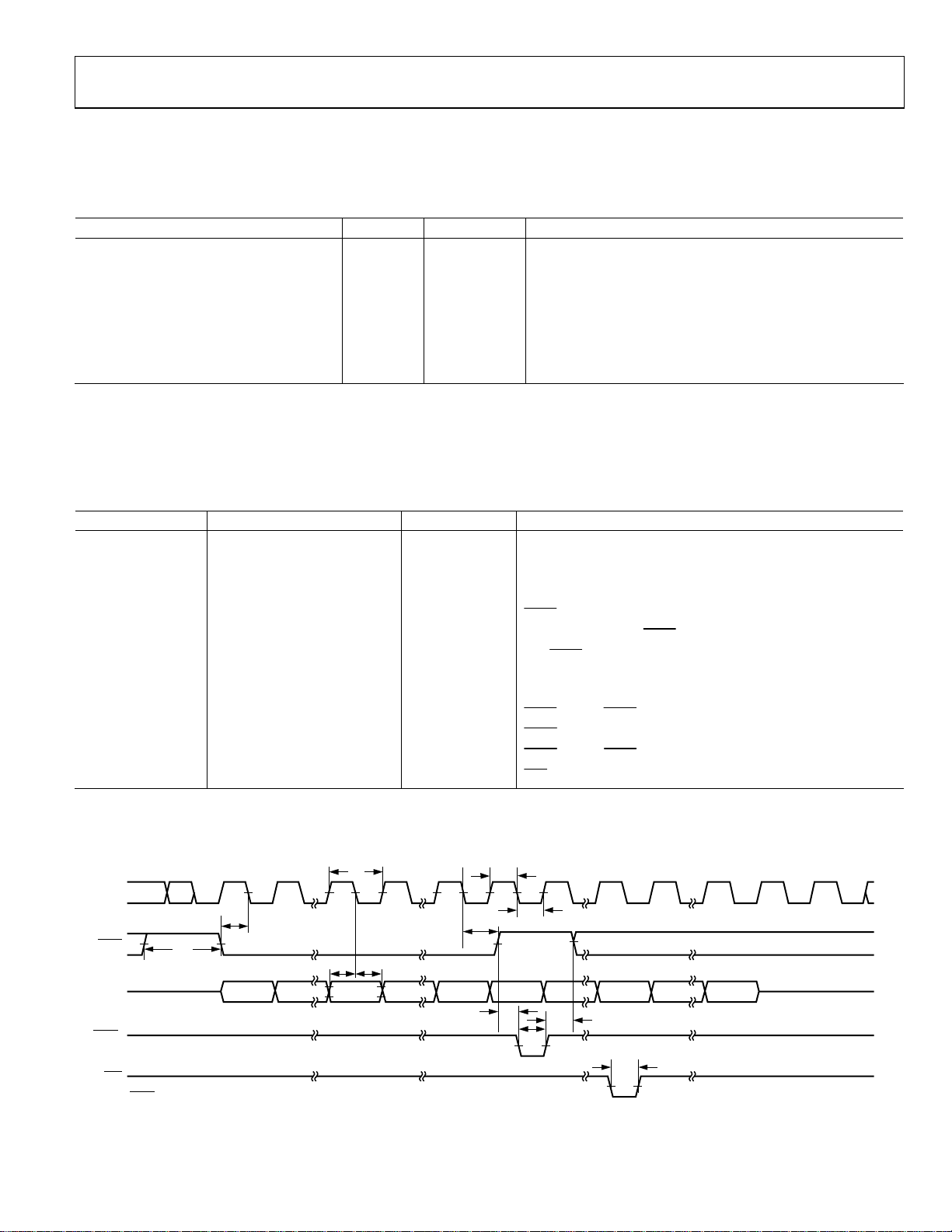

STANDALONE TIMING CHARACTERISTICS

VDD = 10.8 V to 16.5 V, VSS = −10.8 V to −16.5 V; GND = 0 V; RL = 5 kΩ and CL = 220 pF to GND. All specifications T

otherwise noted.

MIN

MIN

to T

to T

MAX

MAX

, unless

, unless

Table 4.

Parameter Limit at T

f

MAX

1, 2

MIN

, T

Unit Description

MAX

7 MHz max SCLK frequency

t1 140 ns min SCLK cycle time

t2 60 ns min SCLK low time

t3 60 ns min SCLK high time

t4 50 ns min

t5 40 ns min

t6 50 ns min

SYNC to SCLK falling edge setup time

SCLK falling edge to

SYNC high time

Min

SYNC rising edge

t7 40 ns min Data setup time

t8 15 ns min Data hold time

t9 5 ns min

t10 50 ns min

t11 5 ns min

t12 50 ns min

1

Guaranteed by design, not subject to production test.

2

Sample tested during initial release and after any redesign or process change that can affect this parameter. All input signals are measured with tR = tF = 5 ns (10% to

90% of VDD) and timed from a voltage level of (VIL + VIH)/2.

SYNC high to LDAC low

LDAC pulse width

LDAC high to SYNC low

CLR

pulse width

SCLK

t

4

SYNC

SDIN

1

LDAC

CLR

1

LDAC CAN BE TIED PERMANENTLY LO W, IF REQUIRED.

t

6

MSB

DB15 DB14 DB11 DB0

t

1

t7t

8

Figure 2. Timing Diagram for Standalone Mode

LSB

t

3

t

t

5

2

t

9

t

11

t

10

t

12

0938-002

Rev. B | Page 5 of 20

AD5530/AD5531

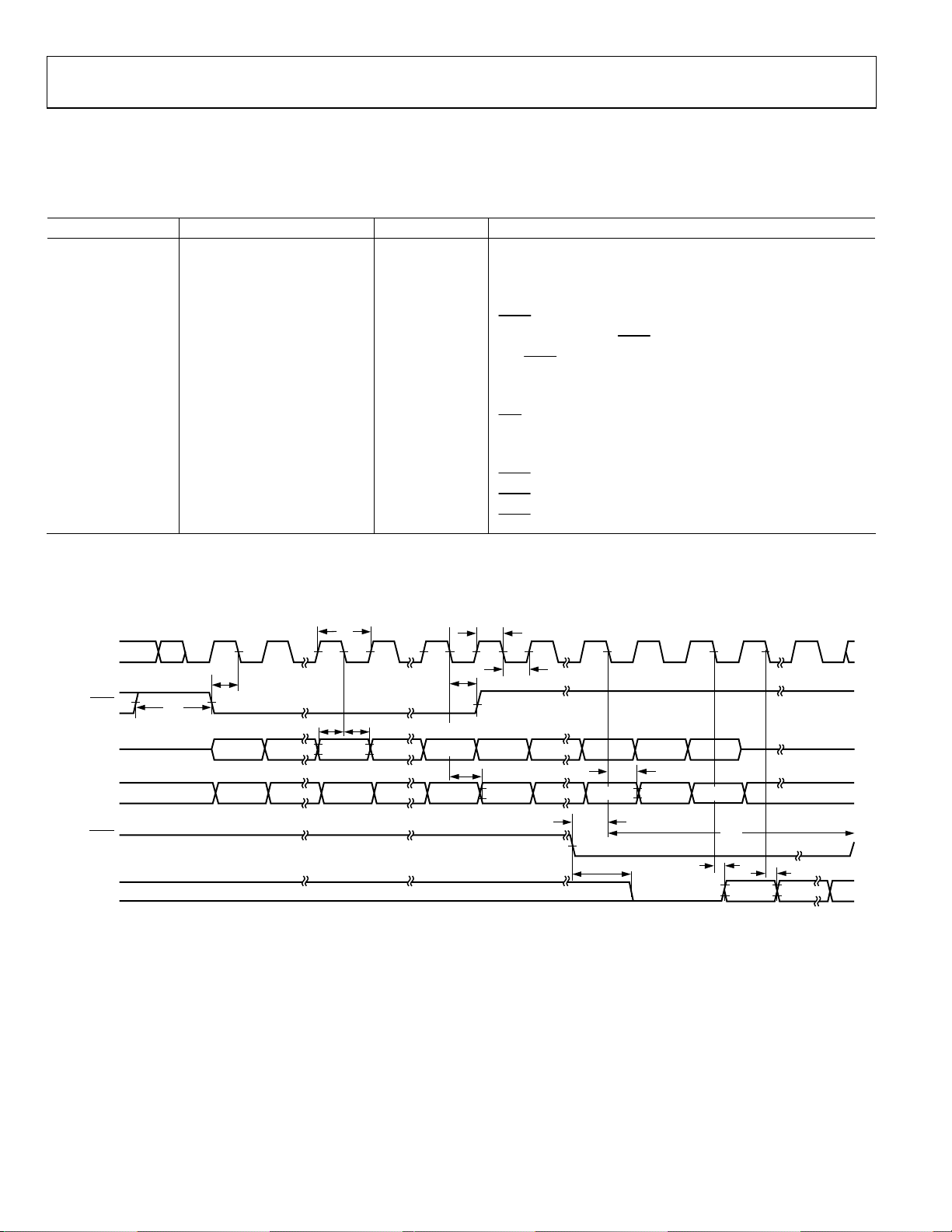

DAISY-CHAINING AND READBACK TIMING CHARACTERISTICS

VDD = 10.8 V to 16.5 V, VSS = −10.8 V to −16.5 V; GND = 0 V; RL = 5 kΩ and CL = 220 pF to GND. All specifications T

otherwise noted.

MIN

to T

MAX

, unless

Table 5.

Parameter Limit at T

f

MAX

1, 2, 3

MIN

, T

Unit Description

MAX

2 MHz max SCLK frequency

t1 500 ns min SCLK cycle time

t2 200 ns min SCLK low time

t3 200 ns min SCLK high time

t4 50 ns min

t5 40 ns min

t6 50 ns min

SYNC to SCLK falling edge setup time

SCLK falling edge to

SYNC high time

Min

SYNC rising edge

t7 40 ns min Data setup time

t8 15 ns min Data hold time

t12 50 ns min

CLR pulse width

t13 130 ns min SCLK falling edge to SDO valid

t14 50 ns max SCLK falling edge to SDO invalid

t15 50 ns min

t16 50 ns min

t17 100 ns min

1

Guaranteed by design, not subject to production test.

2

Sample tested during initial release and after any redesign or process change that can affect this parameter. All input signals are measured with tR = tF = 5 ns (10% to

90% of VDD) and timed from a voltage level of (VIL + VIH)/2.

3

SDO; R

= 5 kΩ, CL = 15 pF

PULLUP

RBEN to SCLK falling edge setup time

RBEN hold time

RBEN falling edge to SDO valid

SCLK

SYNC

SDIN

SDO

(DAISY-

CHAINING)

RBEN

t

1

t

4

t

6

MSB

DB15 DB14 DB11 DB0

t7t

8

t

3

t

2

t

MSB LSB

DB15 DB11 DB0

14

t

15

LSB

t

5

t

13

t

16

SDO

(READBACK)

t

17

Figure 3. Timing Diagram for Daisy-Chaining and Readback Mode

Rev. B | Page 6 of 20

t

13

MSB LSB

t

14

RB0RB1300

00938-003

Loading...

Loading...