Quad Parametric Measurement Unit with

www.BDTIC.com/ADI

FEATURES

Quad parametric measurement unit (PMU)

FV, FI, FN (high-Z), MV, MI functions

4 programmable current ranges (internal R

±5 μA, ±20 μA, ±200 μA, and ±2 mA

1 programmable current range up to ±80 mA (external R

22.5 V FV range with asymmetrical operation

Integrated 16-bit DACs provide programmable levels

Gain and offset correction on chip

Low capacitance outputs suited to relayless systems

On-chip comparators per channel

FI voltage clamps and FV current clamps

Guard drive amplifier

System PMU connections

Programmable temperature shutdown

SPI- and LVDS-compatible interfaces

Compact 80-lead TQFP with exposed pad (top or bottom)

VREF

REFGND

MEASOUT[0:3]

AGND

AGND

POWER-ON

RESET

RESET BUSY

AVSS AVDD

16

X1 REG

16

M REG

16

C REG

16

16

16

16

16

16

16

16

16

16

16

16

×2

X1 REG

M REG

C REG

×6

X1 REG

M REG

C REG

×2

SW12

×6

X1 REG

M REG

C REG

×6

X1 REG

M REG

C REG

16-BIT

16

OFFSET

DAC

16

SDI

SCLK SYNC

SDO CPOL0/

X2 REG

X2 REG

X2 REG

MEASOU T

MUXAND GAIN

×1/×0.2

X2 REG

X2 REG

TOALL DAC

OUTPU T

AMPLIFIERS

SERIAL

INTERFACE

DVCC

16

×2

OFFSET DAC

×6

16

×2

×6

16

×6

16

LOAD

)

SENSE

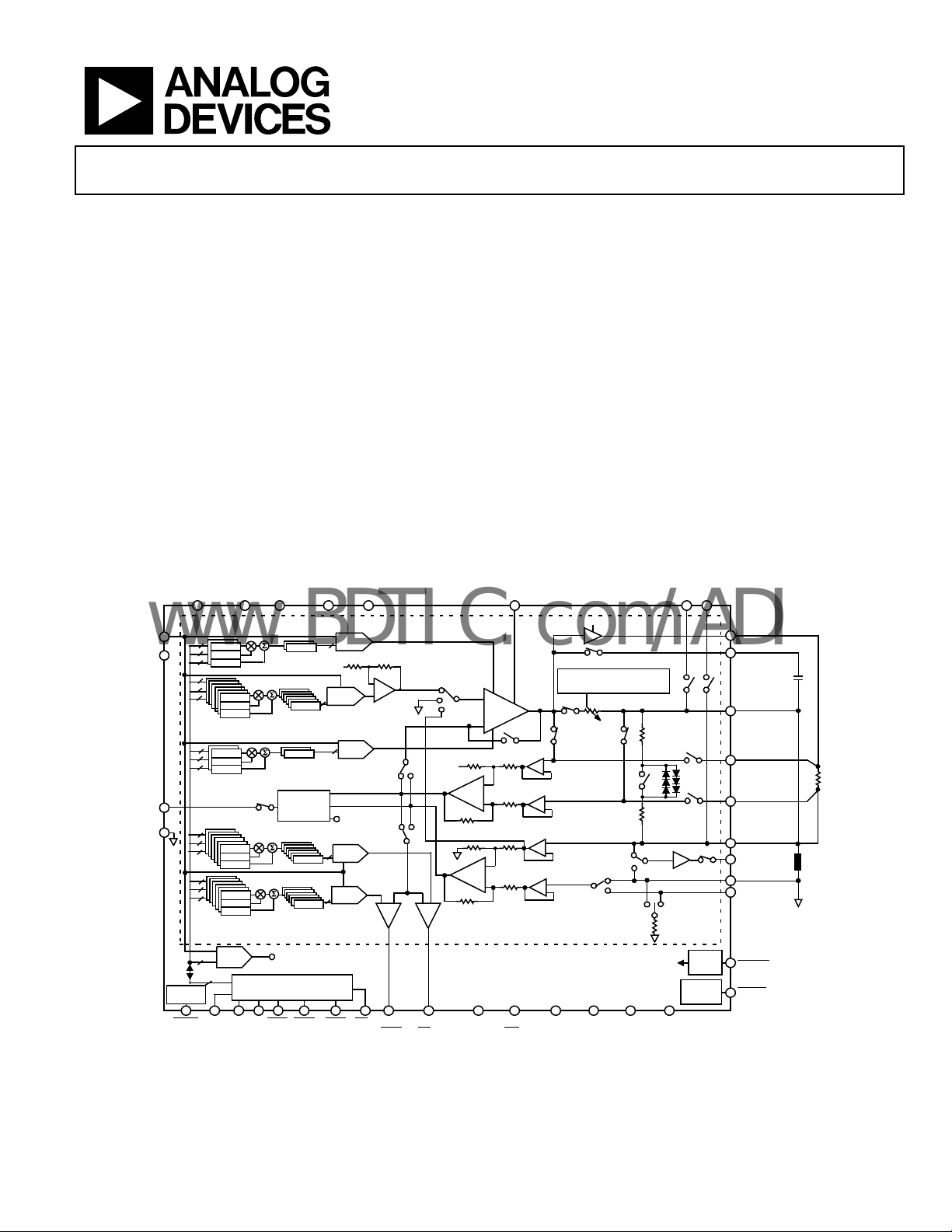

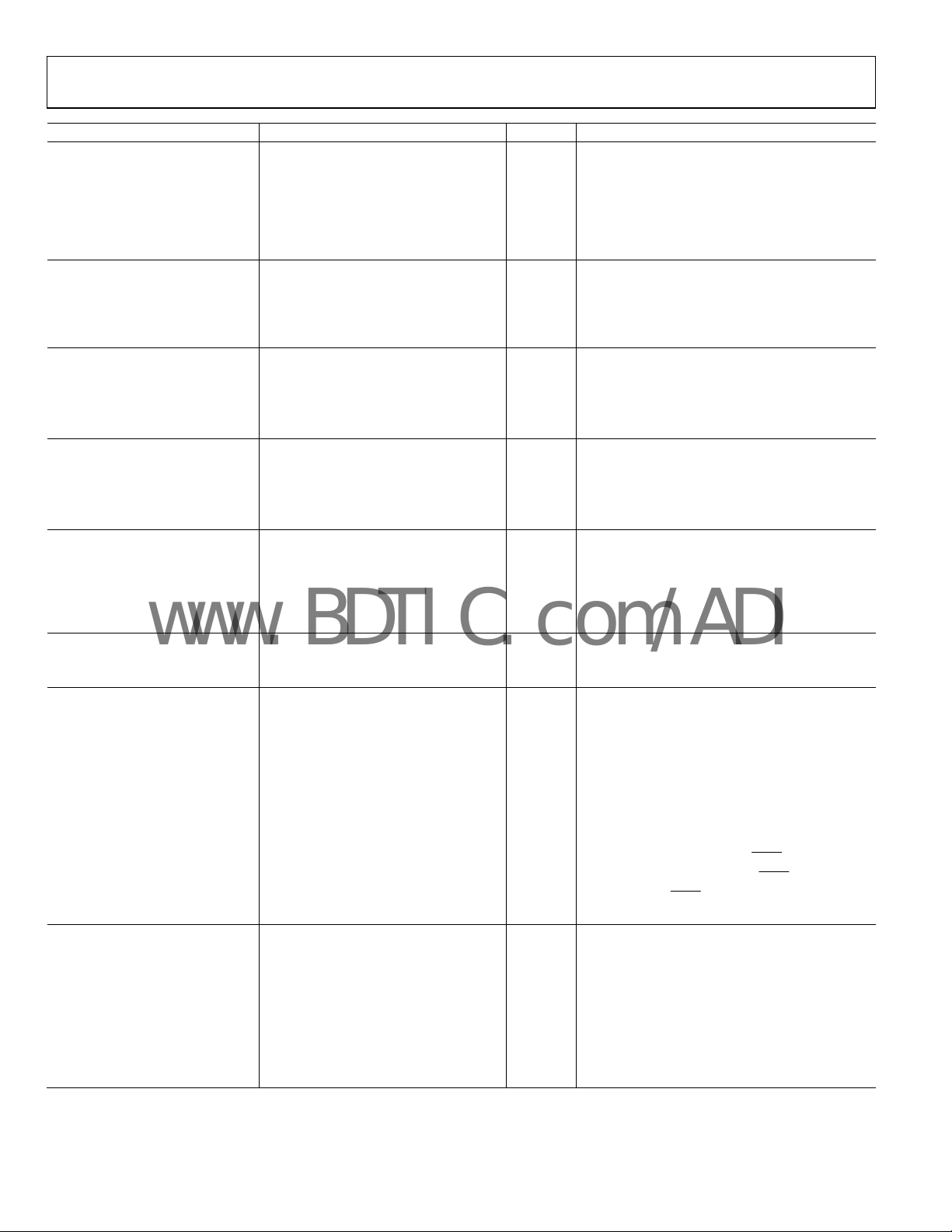

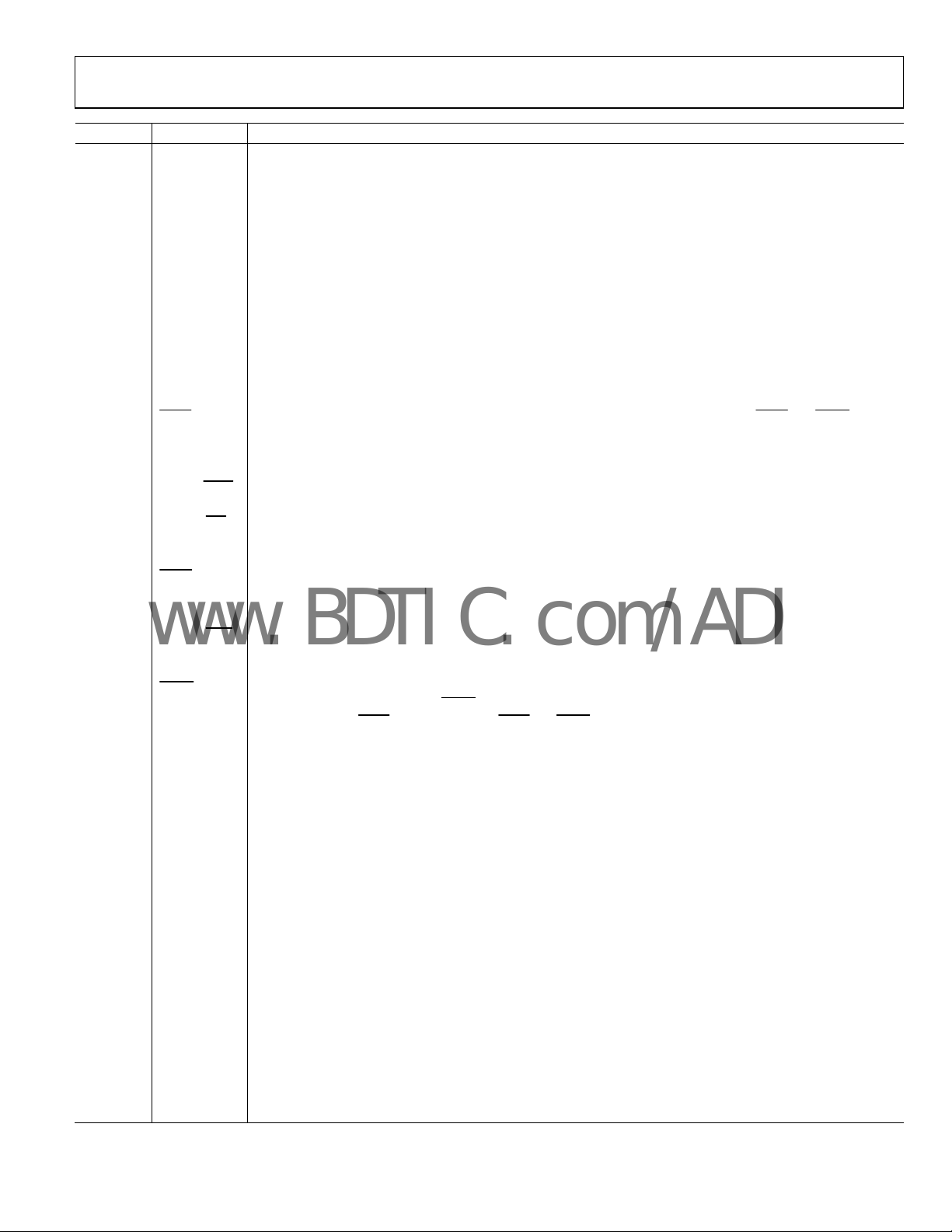

FUNCTIONAL BLOCK DIAGRAM

DGND

CPL

–

+

SW10

SW11

–

SCLK

+

AGND

×4

FIN

CPH

CPOH0/

SDI

–

16-BIT

CLH DAC

16-BIT

FIN DAC

16-BIT

16

CLL DAC

TEMP

SENSOR

16-BIT

CPH DAC

16-BIT

CPL DAC

COMPARATOR

SPI/

LVDS

Integrated 16-Bit Level Setting DACs

AD5522

APPLICATIONS

Automated test equipment (ATE)

Per-pin parametric measurement unit

Continuity and leakage testing

Device power supply

SENSE

VMIDTO

CENTER

I RANGE

+

)

SW1

MEASVH

(Hi-Z)

×5 or ×10

AGND

CPOL1/

SYNC

Figure 1.

Instrumentation

CCOMP[0:3]

CLH

+

FORCE

AMPLIFIER

–

SW2

CLL

+

–

MEASURE

CURRENT

IN-AMP

+

×1

–

MEASURE

VOLTAGE

IN-AMP

CPOH1/

SDO

Source measure unit (SMU)

Precision measurement

SYS_FORCE

EN

SW3

INTERNA L RANG E SELECT

(±5µA, ±20µA, ±200µ A, ±2m A)

SW5

R

SENSE

SW6

SW4

+

–

+

–

+

–

DUTGND

+

–

CPOL2/

CPO0

CPOH2/

CPO1

SW13

SW14

CPOL3/

CPO2

2kΩ

AGND

4kΩ

SW7

4kΩ

GUARDAMP

10kΩ

TO

MEASOU T

MUX

CPOH3/

CPO3

60Ω

SW15

SW8

SW9

CLAMPAND

GUARD

ALARM

SYS_SENSE

1kΩ

SW16

TEMP

SENSOR

EXTFOH[0:3]

CFF[0:3]

FOH[0:3]

EXTMEASIH[0:3]

EXTMEASIL[0:3]

MEASVH[0:3]

GUARD[0:3]

GUARDIN[0:3]/

DUTGND[0:3]

DUTGND

TMPALM

CGALM

EXTERNAL

R

(CURRENTS

UP TO ±80mA)

DUT

SENSE

06197-001

Rev.

A

Info

rmation furnished by Analog Devices is believed to be accurate and reliable. However, no

res

ponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

righ

ts of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2008 Analog Devices, Inc. All rights reserved.

.A.

AD5522

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 3

General Description ......................................................................... 4

Specifications ..................................................................................... 6

Timing Characteristics .............................................................. 11

Absolute Maximum Ratings .......................................................... 15

Thermal Resistance .................................................................... 15

ESD Caution ................................................................................ 15

Pin Configurations and Function Descriptions ......................... 16

Typical Performance Characteristics ........................................... 22

Terminology .................................................................................... 28

Theory of Operation ...................................................................... 29

Force Amplifier ........................................................................... 29

Comparators ................................................................................ 29

Clamps ......................................................................................... 29

Current Range Selection ............................................................ 30

High Current Ranges ................................................................. 30

Measure Current Gains .............................................................. 31

VMID Voltage ............................................................................. 31

Choosing Power Supply Rails ................................................... 32

Measure Output (MEASOUTx Pins) ...................................... 32

Device Under Test Ground (DUTGND) ................................. 32

Guard Amplifier ......................................................................... 33

Compensation Capacitors ......................................................... 33

System Force and Sense Switches ............................................. 33

Temperature Sensor ................................................................... 33

DAC Levels ...................................................................................... 34

Offset DAC .................................................................................. 34

Gain and Offset Registers .......................................................... 34

Cached X2 Registers ................................................................... 35

Reference Voltage (VREF) ......................................................... 35

Reference Selection .................................................................... 35

Calibration ................................................................................... 36

System Level Calibration ........................................................... 37

Circuit Operation ........................................................................... 38

Force Voltage (FV) Mode .......................................................... 38

Force Current (FI) Mode ........................................................... 39

Serial Interface ................................................................................ 40

SPI Interface ................................................................................ 40

LVDS Interface ............................................................................ 40

Serial Interface Write Mode ...................................................... 40

RESET

Function ......................................................................... 40

and

LOAD

Functions ..................................................... 40

BUSY

Register Update Rates ................................................................ 41

Register Selection ....................................................................... 41

Write System Control Register ................................................. 43

Write PMU Register ................................................................... 45

Write DAC Register ................................................................... 47

Read Registers ............................................................................. 50

Readback of System Control Register ...................................... 51

Readback of PMU Register ....................................................... 52

Readback of Comparator Status Register ................................ 53

Readback of Alarm Status Register .......................................... 53

Readback of DAC Register ........................................................ 54

Applications Information .............................................................. 55

Power-On Default ...................................................................... 55

Setting Up the Device on Power-On ....................................... 55

Changing Modes ........................................................................ 56

Required External Components ............................................... 56

Power Supply Decoupling ......................................................... 57

Power Supply Sequencing ......................................................... 57

Typical Application for the AD5522 ........................................ 57

Outline Dimensions ....................................................................... 59

Ordering Guide .......................................................................... 60

Rev. A | Page 2 of 60

AD5522

www.BDTIC.com/ADI

REVISION HISTORY

10/08—Rev. 0 to Rev. A

Changes to Table 1 ............................................................................ 6

Change to 4 DAC X1 Parameter, Table 2 ..................................... 11

Changes to Table 3 .......................................................................... 12

Change to Reflow Soldering Parameter, Table 4 ......................... 15

Changes to Figure 18, Figure 19, Figure 20, and Figure 21 ....... 23

Changes to Figure 25 ...................................................................... 24

Changes to Force Amplifier Section ............................................. 29

Changes to Clamps Section ........................................................... 29

Changes to High Current Ranges Section ................................... 30

Changes to Choosing Power Supply Rails Section ..................... 32

Changes to Compensation Capacitors Section ........................... 33

Added Table 14, Renumbered Tables Sequentially ..................... 36

Changes to Reference Selection Example .................................... 36

Changes to Table 15 and

Section .............................................................................................. 40

Changes to Table 17 and Register Update Rates Section ........... 41

Added Table 38 ................................................................................ 57

Changes to Ordering Guide ........................................................... 60

7/08—Revision 0: Initial Version

BUSY

and

LOAD

Functions

Rev. A | Page 3 of 60

AD5522

www.BDTIC.com/ADI

GENERAL DESCRIPTION

The AD5522 is a high performance, highly integrated parametric

measurement unit consisting of four independent channels. Each

per-pin parametric measurement unit (PPMU) channel includes

five 16-bit, voltage output DACs that set the programmable input

levels for the force voltage inputs, clamp inputs, and comparator

inputs (high and low). Five programmable force and measure

current ranges are available, ranging from ±5 µA to ±80 mA.

Four of these ranges use on-chip sense resistors; one high current

range up to ±80 mA is available per channel using off-chip sense

resistors. Currents in excess of ±80 mA require an external amplifier. Low capacitance DUT connections (FOH and EXTFOH)

ensure that the device is suited to relayless test systems.

The PMU functions are controlled via a simple 3-wire serial

interface compatible with SPI, QSPI™, MICROWIRE™, and DSP

interface standards. Interface clocks of 50 MHz allow fast updating

of modes. The low voltage differential signaling (LVDS) interface

protocol at 83 MHz is also supported. Comparator outputs are

provided per channel for device go-no-go testing and characterization. Control registers allow the user to easily change force or

measure conditions, DAC levels, and selected current ranges.

The SDO (serial data output) pin allows the user to read back

information for diagnostic purposes.

Rev. A | Page 4 of 60

AD5522

K

www.BDTIC.com/ADI

VREF

REFGND

MEASOUT0

AGND

CPOL0/SCL

CPOH0/SDI

CCOMP1

MEASOUT1

CPOL1/SYNC

CPOH1/SDO

AGND

CCOMP2

MEASOUT2

CPOL2/CPO0

CPOH2/CPO1

AGND

CCOMP3

MEASOUT3

AGND

AGND

POWER-ON

RESET

AVSS AVDD

16

X1 REG

16

M REG

16

C REG

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

×2

X1 REG

M REG

C REG

×6

X1 REG

M REG

C REG

×2

SW12

×6

X1 REG

M REG

C REG

×6

X1 REG

M REG

C REG

X1 REG

M REG

C REG

×2

X1 REG

M REG

C REG

×6

X1 REG

M REG

C REG

×2

SW12

×6

X1 REG

M REG

C REG

×6

X1 REG

M REG

C REG

16-BIT

16

OFFSET

DAC

16

SDI

SCLK SYNC

SDORESET BUSY LOAD

X2 REG

X2 REG

X2 REG

MEASOU T

MUX AND GAI N

×1/×0.2

X2 REG

X2 REG

X2 REG

X2 REG

X2 REG

MEASOU T

MUX AND GAI N

x1/x0.2

X2 REG

X2 REG

TO ALL DAC

OUTPUT

AMPLIFIERS

SERIAL

INTERFACE

DVCC

16

×2

OFFSET DAC

×6

16

FIN DAC

16

×2

×6

16

×6

16

COMPARATOR

16

×2

OFFSET DAC

×6

16

FIN DAC

16

×2

×6

16

×6

16

DGND

16-BIT

CLH DAC

16-BIT

16-BIT

CLL DAC

TEMP

SENSOR

16-BIT

CPH DAC

16-BIT

CPL DAC

16-BIT

CLH DAC

16-BIT

16-BIT

CLL DAC

TEMP

SENSOR

16-BIT

CPH DAC

16-BIT

CPL DAC

COMPARATOR

SPI/

LVDS

CH0

–

CPL

FIN

+

AGND

SW10

SW11

–

+

CPH

–

VMID TO

CENTER

I RANGE

+

SW1

MEASVH

(Hi-Z)

×5 OR ×10

AGND

CLL

×1

CH1

CH2

CH3

–

CPL

+

SW10

SW11

–

CPOL3/

CPO2

FIN

AGND

+

SW1

MEASVH

(Hi-Z)

CLL

VMID TO

CENTER

I RANGE

x5 or x10

AGND

CPH

–

CPOH3/

CPO3

x1

+

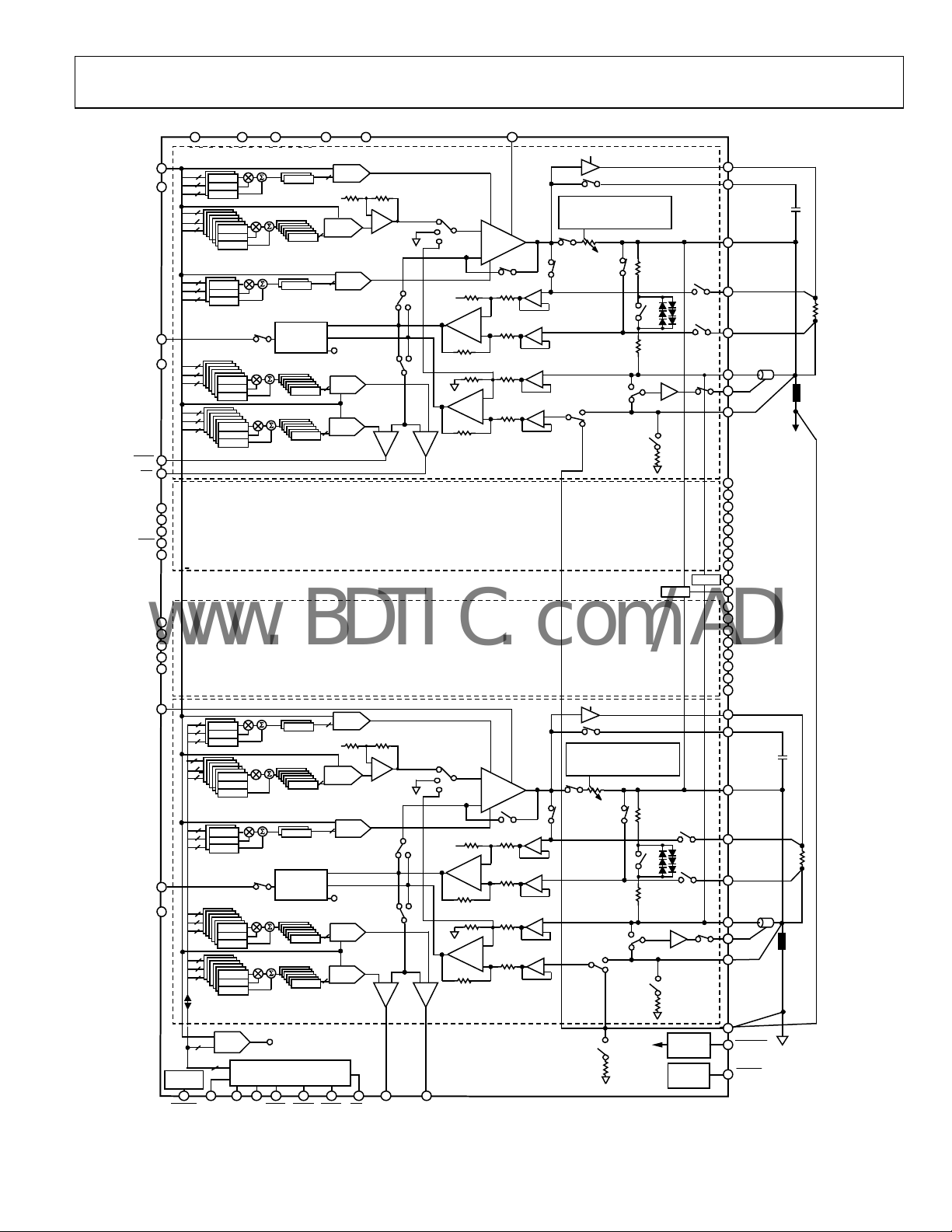

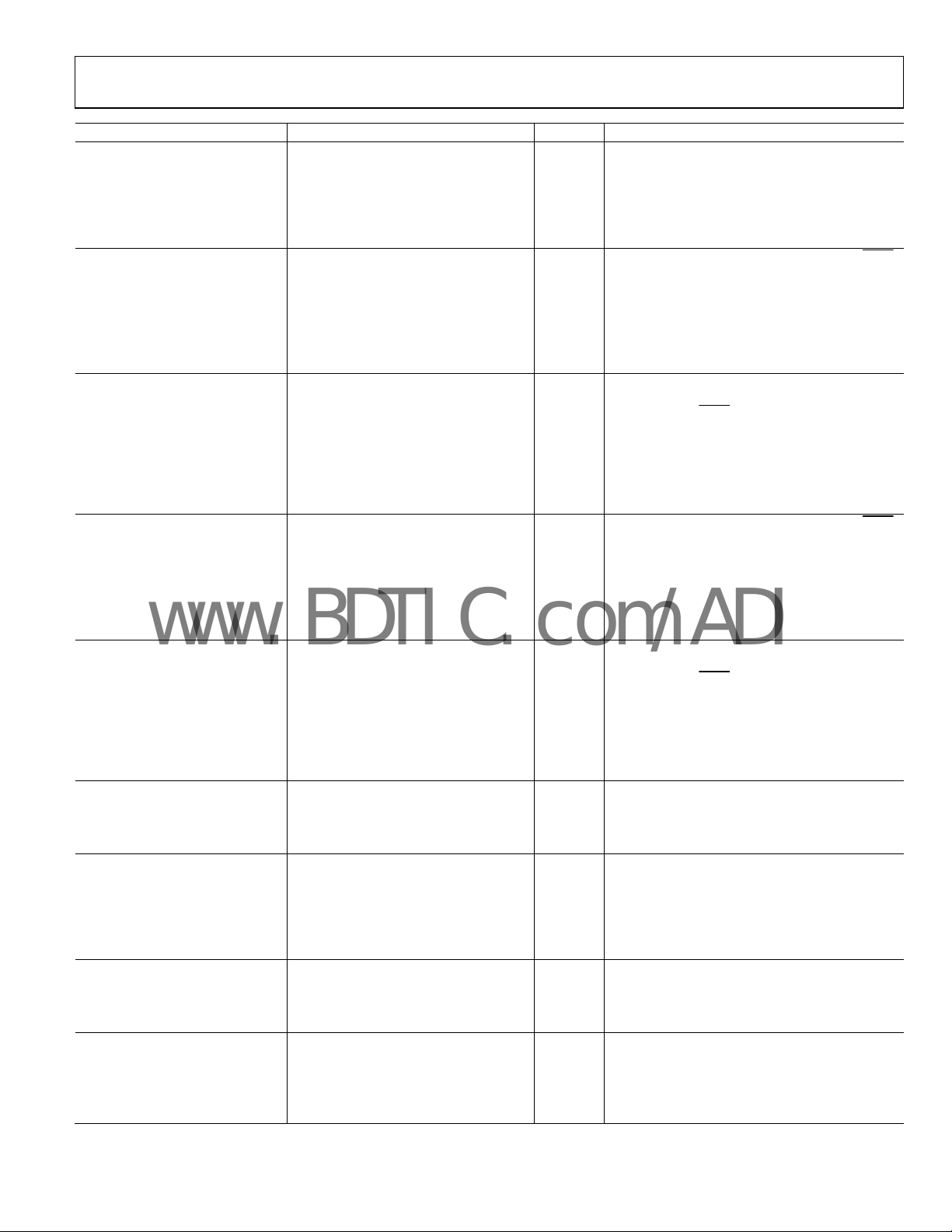

Figure 2. Detailed Block Diagram

CLH

+

FORCE

AMPLIFIER

–

+

–

+

–

CLH

+

FORCE

AMPLIFIER

–

+

–

+

–

CCOMP0

MEASURE

CURRENT

IN-AMP

MEASURE

VOLTAGE

IN-AMP

MEASURE

CURRENT

IN-AMP

MEASURE

VOLTAGE

IN-AMP

(±5µA, ±20µA, ±200µ A, ±2m A)

SW5

SW2

SW4

+

–

+

–

+

–

DUTGND

+

–

SW2

SW4

+

–

+

–

+

–

DUTGND

+

–

EN

SW3

INTERNAL RANGE

SELECT

R

SENSE

SW6

4kΩ

2kΩ

SW7

4kΩ

SW13

SW3

SELECT

SW6

SW13

SW14

2kΩ

MEASOUT

MUX

10kΩ

AGND

4kΩ

SW7

4kΩ

AGND

TO

GUARD AMP

SW15

10kΩ

GUARD AMP

SW15

10kΩ

SW14

EN

INTERNAL RANGE

(±5µA, ±20µA, ±200µ A, ±2m A)

SW5

R

SENSE

SW15a

AGND

SW16

MUX

SW8

SW9

TEMP

SENSOR

CLAMP AND

GUARD

ALARM

SW8

SW9

MUX

SW16

EXTFOH0

CFF0

FOH0

EXTMEASIH0

EXTMEASIL0

MEASVH0

GUARD0

GUARDIN0/

DUTGND0

EXTFOH1

CFF1

FOH1

EXTMEASIH1

EXTMEASIL1

MEASVH1

GUARD1

GUARDIN1/DUTGND1

SYS_SENSE

SYS_FORCE

EXTFOH2

CFF2

FOH2

EXTMEASIH2

EXTMEASIL2

MEASVH2

GUARD2

GUARDIN2/DUTGND2

EXTFOH3

CFF3

FOH3

EXTMEASIH3

EXTMEASIL3

MEASVH3

GUARD3

GUARDIN3/

DUTGND3

DUT

DUTGND

TMPALM

CGALM

EXTERNAL

R

SENSE

(CURRENTS

UP TO ±80mA)

DUT

DUTGND

EXTERNAL

R

SENSE

(CURRENTS

UP TO ±80mA)

06197-002

Rev. A | Page 5 of 60

AD5522

www.BDTIC.com/ADI

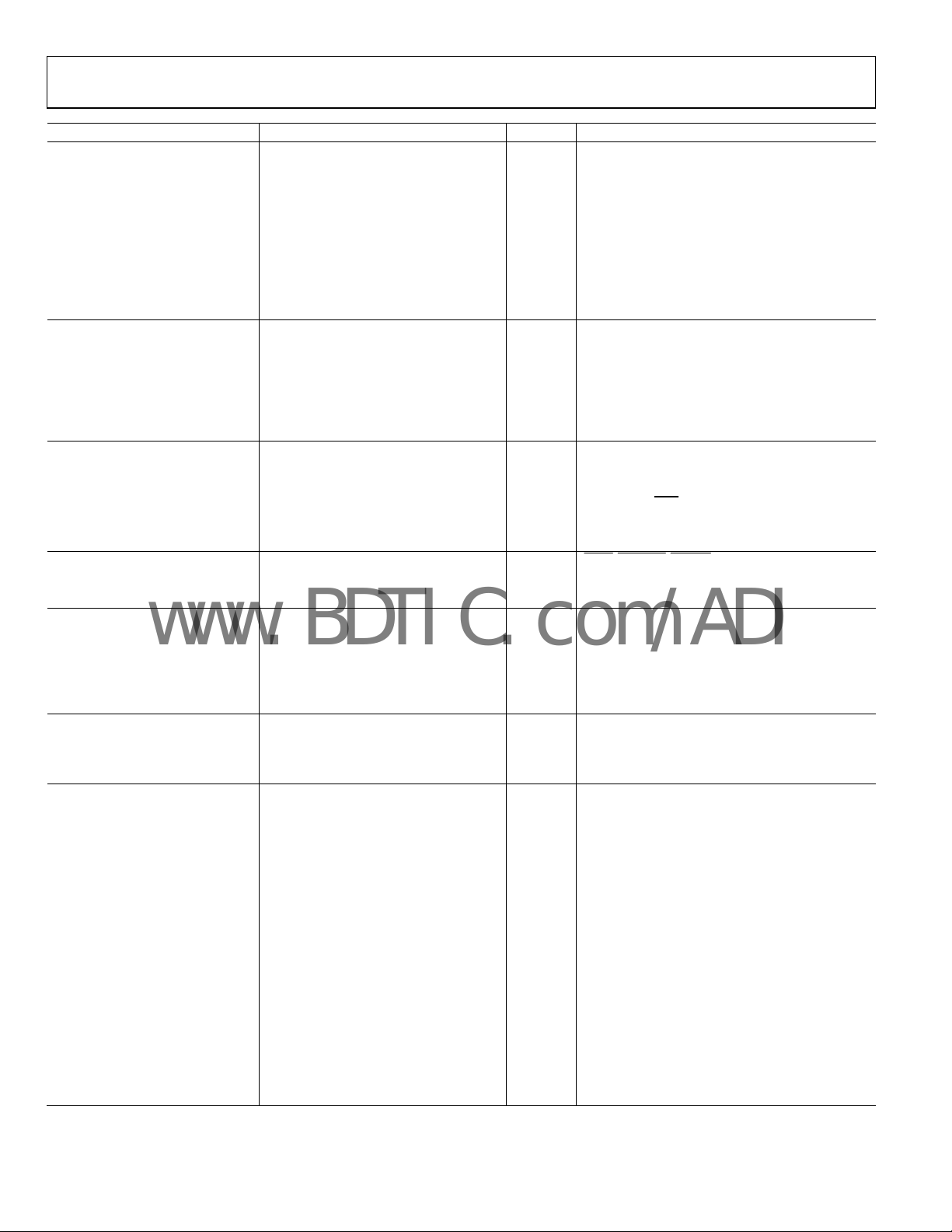

SPECIFICATIONS

AVDD ≥ 10 V; AVSS ≤ −5 V; |AVDD − AVSS| ≥ 20 V and ≤ 33 V; DVCC = 2.3 V to 5.25 V; VREF = 5 V; REFGND = DUTGND = AGND

= 0 V; gain (M), offset (C), and DAC offset registers at default values; T

FI = force current, MV = measure voltage, MI = measure current, FS = full scale, FSR = full-scale range, FSVR = full-scale voltage range,

FSCR = full-scale current range.)

Table 1.

Parameter Min Typ1 Max Unit Test Conditions/Comments

FORCE VOLTAGE

FOHx Output Voltage Range2 AVSS + 4 AVDD − 4 V All current ranges from FOHx at full-scale current;

EXTFOHx Output Voltage

Output Voltage Span 22.5 V

Offset Error −50 +50 mV Measured at midscale code; prior to calibration

Offset Error Tempco2 −10 µV/°C Standard deviation = 20 V/°C

Gain Error −0.5 +0.5 % FSR Prior to calibration

Gain Error Tempco2 0.5 ppm/°C Standard deviation = 0.5 ppm/°C

Linearity Error −0.01 +0.01 % FSR FSR = full-scale range (±10 V), gain and offset errors

Short-Circuit Current Limit2 −150 +150 mA ±80 mA range

−10 +10 mA All other ranges

Noise Spectral Density (NSD)2 320 nV/√Hz 1 kHz, at FOHx in FV mode

MEASURE CURRENT Measure current = (I

Differential Input Voltage

Range

Output Voltage Span 22.5 V Measure current block with VREF = 5 V, MEASOUT

Offset Error −0.5 +0.5 % FSCR V(R

Offset Error Tempco2 1 µV/°C Referred to MI input; standard deviation = 4 µV/°C

Gain Error −1 +1 % FSCR Using internal current ranges

−0.5 +0.5 % FSCR Measure current amplifier alone

Gain Error Tempco2 −2 ppm/°C Standard deviation = 2 ppm/°C

Linearity Error −0.015 +0.015 % FSCR Gain and offset errors calibrated out; MEASOUTx

−0.01 +0.01 % FSCR Gain and offset errors calibrated out; MEASOUTx

Common-Mode Voltage Range2 AVSS + 4 AVDD − 4 V

Common-Mode Error −0.005 +0.005 % FSVR/V % of full-scale change at measure output per V

Sense Resistors Sense resistors are trimmed to within 1%

200 kΩ ±5 µA range

50 kΩ ±20 µA range

5 kΩ ±200 µA range

0.5 kΩ ±2 mA range

Measure Current Ranges2 Specified current ranges are achieved with VREF = 5 V

±5 µA Set using internal sense resistor

±20 µA Set using internal sense resistor

±200 µA Set using internal sense resistor

±2 mA Set using internal sense resistor

±80 mA Set using external sense resistor; internal amplifier

Noise Spectral Density (NSD)2 400 nV/√Hz 1 kHz, MI amplifier only, inputs grounded

Range

2

2

AVSS + 3 AVDD − 3 V External high current range at full-scale current;

−1.125 +1.125 V Voltage across R

= 25°C to 90°C, unless otherwise noted. (FV = force voltage,

J

includes ±1 V dropped across sense resistor

does not include ±1 V dropped across sense resistor

calibrated out

× R

gain = 5 or 10, unless otherwise noted

scaling happens after

) = ±1 V, measured with zero current flowing

SENSE

gain = 1; MI gain = 10

gain = 1; MI gain = 5

change in DUT voltage

and MI gain = 10, or with VREF = 2.5 V and MI gain = 5

can drive up to ±80 mA

DUT

; gain = 5 or 10

SENSE

× gain); amplifier

SENSE

Rev. A | Page 6 of 60

AD5522

www.BDTIC.com/ADI

Parameter Min Typ1Max Unit Test Conditions/Comments

FORCE CURRENT

Voltage Compliance, FOHx

Voltage Compliance, EXTFOHx

Offset Error −0.5 +0.5 % FSCR Measured at midscale code, 0 V, prior to calibration

Offset Error Tempco

Gain Error −1.5 +1.5 % FSCR Prior to calibration

Gain Error Tempco

Linearity Error −0.02 +0.02 % FSCR

Force Current Ranges Specified current ranges achieved with VREF = 5 V and

±5 µA Set using internal sense resistor, 200 kΩ

±20 µA Set using internal sense resistor, 50 kΩ

±200 µA Set using internal sense resistor, 5 kΩ

±2 mA Set using internal sense resistor, 500 Ω

±80 mA Set using external sense resistor; internal amplifier

MEASURE VOLTAGE

Measure Voltage Range

Offset Error −10 +10 mV Gain = 1, measured at 0 V

−25 +25 mV Gain = 0.2, measured at 0 V

Offset Error Tempco

Gain Error −0.25 +0.25 % FSR MEASOUTx gain = 1

−0.5 +0.5 % FSR MEASOUTx gain = 0.2

Gain Error Tempco

Linearity Error −0.01 +0.01 % FSR Gain = 1

Noise Spectral Density (NSD)

OFFSET DAC

Span Error ±30 mV

COMPARATOR

Comparator Span 22.5 V

Offset Error −2 +1 +2 mV Measured directly at comparator; does not include

Offset Error Tempco

Propagation Delay

VOLTAGE CLAMPS

Clamp Span 22.5 V

Positive Clamp Accuracy 155 mV

Negative Clamp Accuracy −155 mV

CLL to CLH

Recovery Time

Activation Time

2

2

2

CURRENT CLAMPS

Clamp Accuracy Programmed

Programmed

2

CLL to CLH

10 % of

Recovery Time

Activation Time

2

0.5 1.5 s

2

2

AVSS + 4 AVDD − 4 V

2

AVSS + 3 AVDD − 3 V

2

5 ppm

Standard deviation = 5 ppm/°C

FS/°C

2

−6 ppm/°C Standard deviation = 5 ppm/°C

MI gain = 10, or with VREF = 2.5 V and MI gain = 5 V

can drive up to ±80 mA

2

AVSS + 4 AVDD − 4 V

2

−1 µV/°C Standard deviation = 6 µV /°C

2

1 ppm/°C Standard deviation = 4 ppm/°C

2

100 nV/√Hz 1 kHz; measure voltage amplifier only, inputs

grounded

measure block errors

2

1 µV/°C Standard deviation = 2 µV/°C

2

0.25 s

500 mV CLL < CLH and minimum voltage apart

0.5 1.5 s

1.5 3 s

clamp value

clamp value + 10

Programmed

Programmed

clamp value

clamp value + 20

5 % of

% FSCR MI gain = 10, clamp current scales with selected

range

% FSCR MI gain = 5, clamp current scales with selected range

CLL < CLH and minimum setting apart, MI gain = 10

I

RANGE

CLL < CLH and minimum setting apart, MI gain = 5

I

RANGE

1.5 3 s

Rev. A | Page 7 of 60

AD5522

www.BDTIC.com/ADI

Parameter Min Typ1Max Unit Test Conditions/Comments

FOHx, EXTFOHx, EXTMEASILx,

EXTMEASIHx, CFFx PINS

Pin Capacitance

2

10 pF

Leakage Current −3 +3 nA Individual pin on or off switch leakage, measured with

2

Leakage Current Tempco

MEASVHx PIN

Pin Capacitance

2

3 pF

Leakage Current −3 +3 nA Measured with ±11V stress applied to pin, channel

Leakage Current Tempco

2

±0.01 nA/°C

SYS_SENSE PIN SYS_SENSE connected, force amplifier inhibited

Pin Capacitance

2

3 pF

Switch Impedance 1 1.3 kΩ

Leakage Current −3 +3 nA Measured with ±11 V stress applied to pin, switch off

Leakage Current Tempco

2

±0.01 nA/°C

SYS_FORCE PIN SYS_FORCE connected, force amplifier inhibited

Pin Capacitance

2

6 pF

Switch Impedance 60 80 Ω

Leakage Current −3 +3 nA Measured with ±11 V stress applied to pin, switch off

Leakage Current Tempco

2

±0.01 nA/°C

COMBINED LEAKAGE AT DUT Includes FOHx, MEASVHx, SYS_SENSE, SYS_FORCE,

Leakage Current −15 +15 nA TJ = 25°C to 70°C

−25 +25 nA TJ = 25°C to 90°C

Leakage Current Tempco

2

±0.1 nA/°C

DUTGND PIN

Voltage Range −500 +500 mV

Leakage Current −30 +30 nA

MEASOUTx PIN With respect to AGND

Output Voltage Span 22.5 V Software programmable output range

Output Impedance 60 80 Ω

Output Leakage Current −3 +3 nA With SW12 off

2

Output Capacitance

Maximum Load Capacitance

2

Output Current Drive

Short-Circuit Current −10 +10 mA

Slew Rate

Enable Time

Disable Time

MI to MV Switching Time

2

2 V/s

2

150 320 ns

2

2

GUARDx PIN

Output Voltage Span 22.5 V

Output Offset −10 +10 mV

Short-Circuit Current −15 +15 mA

Maximum Load Capacitance

Output Impedance 85 Ω

Tristate Leakage Current

2

Slew Rate

Alarm Activation Time

2

2

±11 V stress applied to pin, channel enabled, but

tristate

±0.01 nA/°C

enabled, but tristate

EXTMEASILx, EXTMEASIHx, EXTFOHx, and CFFx;

calculation of all the individual leakage contributors

15 pF

2

0.5 F

2 mA

Closing SW12, measured from

400 1100 ns

200 ns

Opening SW12, measured from

Measured from

BUSY

rising edge; does not include

slewing or settling

2

100 nF

−30 +30 nA When guard amplifier is disabled

5 V/s C

LOAD

= 10 pF

200 s Alarm delayed to eliminate false alarms

BUSY

BUSY

rising edge

rising edge

Rev. A | Page 8 of 60

AD5522

www.BDTIC.com/ADI

Parameter Min Typ1 Max Unit Test Conditions/Comments

FORCE AMPLIFIER2

Slew Rate 0.4 V/s CCOMPx = 100 pF, CFFx = 220 pF, C

Gain Bandwidth 1.3 MHz CCOMPx = 100 pF, CFFx = 220 pF, C

Max Stable Load Capacitance 10,000 pF CCOMPx = 100 pF, larger C

requires larger

LOAD

CCOMP

100 nF CCOMPx = 1 nF, larger C

FV SETTLING TIME TO 0.05% OF FS2

Midscale to full-scale change; measured from

requires larger CCOMP

LOAD

rising edge, clamps on

±80 mA Range 22 40 µs CCOMPx = 100 pF, CFFx = 220 pF, C

±2 mA Range 24 40 µs CCOMPx = 100 pF, CFFx = 220 pF, C

±200 µA Range 40 80 µs CCOMPx = 100 pF, CFFx = 220 pF, C

±20 µA Range 300 µs CCOMPx = 100 pF, CFFx = 220 pF, C

±5 µA Range 1400 µs CCOMPx = 100 pF, CFFx = 220 pF, C

MI SETTLING TIME TO 0.05% OF FS2 Midscale to full-scale change; driven from force

amplifier in FV mode, so includes FV settling time;

SYNC

measured from

rising edge, clamps on

±80 mA Range 22 40 µs CCOMPx = 100 pF, CFFx = 220 pF, C

±2 mA Range 24 40 µs CCOMPx = 100 pF, CFFx = 220 pF, C

±200 µA Range 60 100 µs CCOMPx = 100 pF, CFFx = 220 pF, C

±20 µA Range 462 µs CCOMPx = 100 pF, CFFx = 220 pF, C

±5 µA Range 1902 µs CCOMPx = 100 pF, CFFx = 220 pF, C

FI SETTLING TIME TO 0.05% OF FS2

Midscale to full-scale change; measured from

rising edge, clamps on

±80 mA Range 24 55 µs CCOMPx = 100 pF, C

±2 mA Range 24 60 µs CCOMPx = 100 pF, C

±200 µA Range 50 120 µs CCOMPx = 100 pF, C

±20 µA Range 450 µs CCOMPx = 100 pF, C

±5 µA Range 2700 µs CCOMPx = 100 pF, C

= 200 pF

LOAD

= 200 pF

LOAD

= 200 pF

LOAD

= 200 pF

LOAD

= 200 pF

LOAD

MV SETTLING TIME TO 0.05% OF FS2 Midscale to full-scale change; driven from force

amplifier in FV mode, so includes FV settling time;

SYNC

measured from

±80 mA Range 24 55 µs CCOMPx = 100 pF, C

±2 mA Range 24 60 µs CCOMPx = 100 pF, C

±200 µA Range 50 120 µs CCOMPx = 100 pF, C

±20 µA Range 450 µs CCOMPx = 100 pF, C

±5 µA Range 2700 µs CCOMPx = 100 pF, C

rising edge, clamps on

= 200 pF

LOAD

= 200 pF

LOAD

= 200 pF

LOAD

= 200 pF

LOAD

= 200 pF

LOAD

DAC SPECIFICATIONS

Resolution 16 Bits

Output Voltage Span2 22.5 V VREF = 5 V, within a range of −16.25 V to +22.5 V

Differential Nonlinearity2 −1 +1 LSB Guaranteed monotonic by design over temperature

COMPARATOR DAC DYNAMIC

SPECIFICATIONS

2

Output Voltage Settling Time 1 µs 500 mV change to ±½ LSB

Slew Rate 5.5 V/µs

Digital-to-Analog Glitch Energy 20 nV-s

Glitch Impulse Peak Amplitude 10 mV

REFERENCE INPUT

VREF DC Input Impedance 1 100 MΩ

VREF Input Current −10 +0.03 +10 µA

VREF Range2 2 5 V

DIE TEMPERATURE SENSOR

Accuracy2 ±7 °C

Output Voltage at 25°C 1.5 V

Output Scale Factor2 4.6 mV/°C

Output Voltage Range2 0 3 V

= 200 pF

LOAD

= 200 pF

LOAD

= 200 pF

LOAD

= 200 pF

LOAD

= 200 pF

LOAD

= 200 pF

LOAD

= 200 pF

LOAD

= 200 pF

LOAD

= 200 pF

LOAD

= 200 pF

LOAD

= 200 pF

LOAD

= 200 pF

LOAD

SYNC

SYNC

Rev. A | Page 9 of 60

AD5522

www.BDTIC.com/ADI

Parameter Min Typ1Max Unit Test Conditions/Comments

INTERACTION AND CROSSTALK

DC Crosstalk (FOHx) 0.05 0.65 mV DC change resulting from a dc change in any DAC

DC Crosstalk (MEASOUTx) 0.05 0.65 mV DC change resulting from a dc change in any DAC

DC Crosstalk Within a Channel 0.05 mV All channels in FVMI mode, one channel at

SPI INTERFACE LOGIC INPUTS

Input High Voltage, VIH 1.7/2.0 V (2.3 V to 2.7 V)/(2.7 V to 5.25 V), JEDEC-compliant

Input Low Voltage, VIL 0.7/0.8 V (2.3 V to 2.7 V)/(2.7 V to 5.25 V), JEDEC-compliant

Input Current, I

, I

INH

INL

Input Capacitance, C

CMOS LOGIC OUTPUTS SDO, CPOx

Output High Voltage, VOH DVCC − 0.4 V

Output Low Voltage, VOL 0.4 V IOL = 500 µA.

Tristate Leakage Current −2 +2 µA

−1 +1 µA All other output pins

Output Capacitance

2

OPEN-DRAIN LOGIC OUTPUTS

Output Low Voltage, VOL 0.4 V IOL = 500 µA, C

Output Capacitance

2

LVDS INTERFACE LOGIC INPUTS

REDUCED RANGE LINK

Input Voltage Range 875 1575 mV

Input Differential Threshold −100 +100 mV

External Termination Resistance 80 100 120 Ω

Differential Input Voltage 100 mV

LVDS INTERFACE LOGIC OUTPUTS

REDUCED RANGE LINK

Output Offset Voltage 1200 mV

Output Differential Voltage 400 mV

POWER SUPPLIES

AVDD 10 28 V |AVDD − AVSS| ≤ 33 V

AVSS −23 −5 V

DVCC 2.3 5.25 V

AIDD 26 mA Internal ranges (±5 A to ±2 mA), excluding load

AISS −26 mA Internal ranges (±5 A to ±2 mA), excluding load

AIDD 28 mA Internal ranges (±5 A to ±2 mA), excluding load

AISS −28 mA Internal ranges (±5 A to ±2 mA), excluding load

AIDD 36 mA External range, excluding load conditions

AISS −36 mA External range, excluding load conditions

DICC 1.5 mA

Maximum Power Dissipation

2

in the device, FV and FI modes, ±2 mA range, C

= 200 pF, R

LOAD

in the device, MV and MI modes, ±2 mA range,

= 200 pF, R

C

LOAD

midscale; measure the current for one channel in

the lowest current range for a change in

comparator or clamp DAC levels for that PMU

input levels

input levels

−1 +1 µA

2

10 pF

IN

SDO, CPOH1/

10 pF

BUSY

10 pF

2

SDO

TMPALM, CGALM

,

LOAD

conditions; comparators and guard disabled

conditions; comparators and guard disabled

conditions; comparators and guard enabled

conditions; comparators and guard enabled

2

7 W Maximum power that should be dissipated in this

package under worst-case load conditions; careful

consideration should be given to supply selection

and thermal design

= 5.6 kΩ

= 5.6 kΩ

LOAD

= 50 pF, R

LOAD

= 1 kΩ

PULLUP

Rev. A | Page 10 of 60

AD5522

www.BDTIC.com/ADI

Parameter Min Typ1Max Unit Test Conditions/Comments

Power Supply Sensitivity

∆Forced Voltage/∆AVDD −80 dB

∆Forced Voltage/∆AVSS −80 dB

∆Measured Current/∆AVDD −85 dB

∆Measured Current/∆AVSS −75 dB

∆Forced Current/∆AVDD −75 dB

∆Forced Current/∆AVSS −75 dB

∆Measured Voltage/∆AVDD −85 dB

∆Measured Voltage/∆AVSS −80 dB

∆Forced Voltage/∆DVCC −90 dB

∆Measured Current/∆DVCC −90 dB

∆Forced Current/∆DVCC −90 dB

∆Measured Voltage/∆DVCC −90 dB

1

Typical specifications are at 25°C and nominal supply, ±15.25 V, unless otherwise noted.

2

Guaranteed by design and characterization; not production tested. Tempco values are mean and standard deviation, unless otherwise noted.

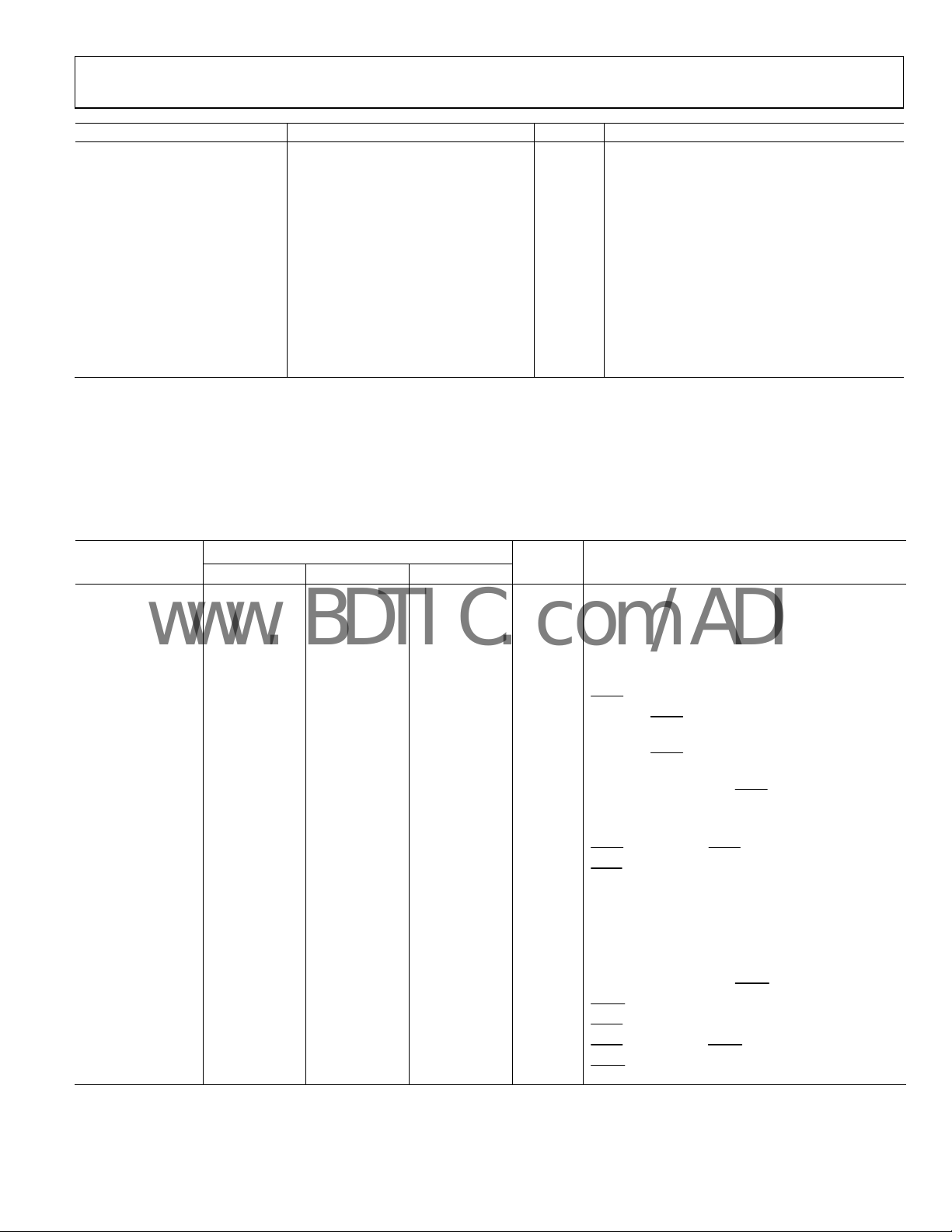

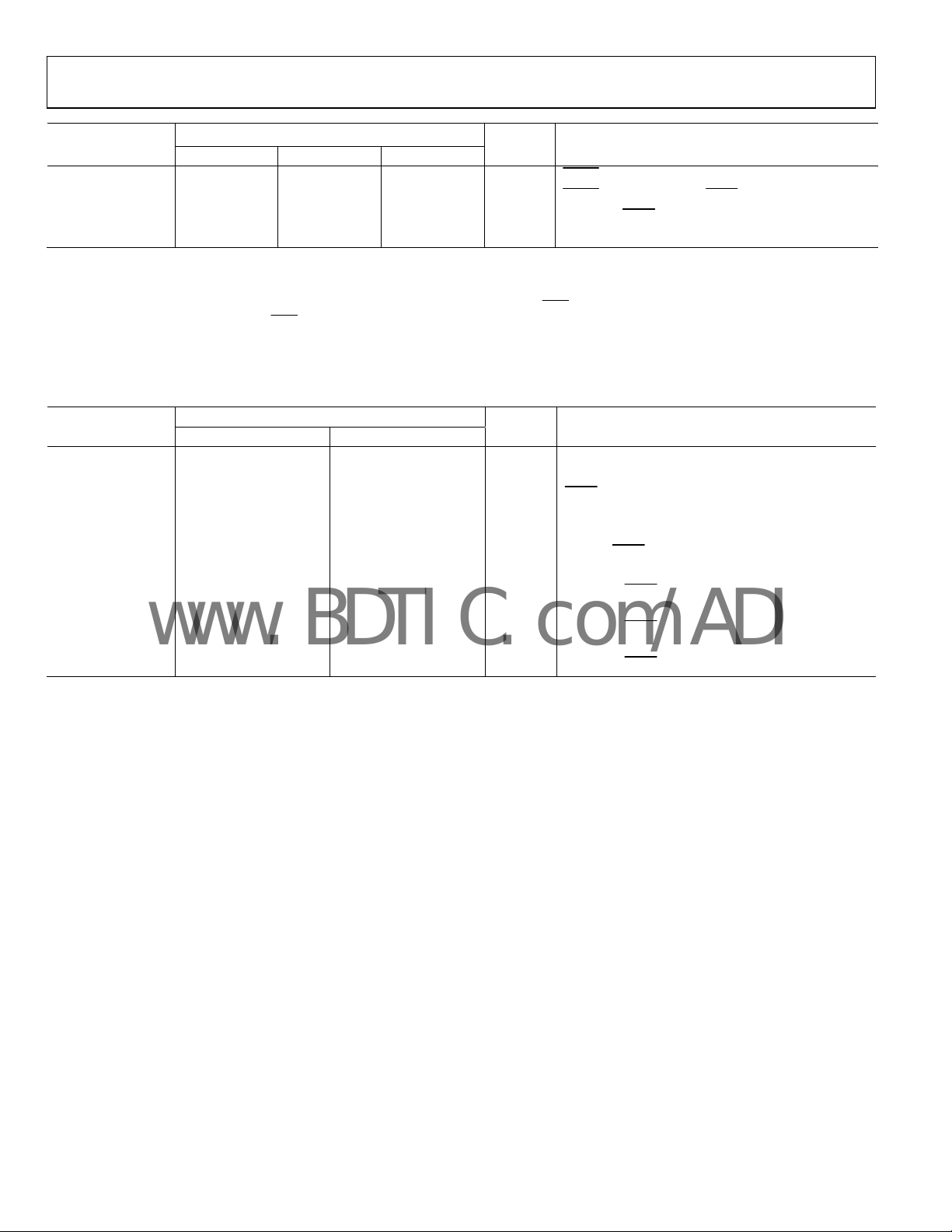

TIMING CHARACTERISTICS

AVDD ≥ 10 V, AVSS ≤ −5 V, |AVDD − AVSS| ≥ 20 V and ≤ 33 V, DVCC = 2.3 V to 5.25 V, VREF = 5 V, TJ = 25°C to 90°C, unless

otherwise noted.

Table 2. SPI Interface

1 , 2 , 3

Parameter

4

t

WRIT E

t

1

t2 8 8 8 ns min SCLK high time

t3 8 8 8 ns min SCLK low time

t4 10 10 10 ns min

4

t

150 150 150 ns min

5

t6 10 5 5 ns min

t

7

t8 9 7 4.5 ns min Data hold time

t9 120 75 55 ns max

t10

1 DAC X1 1.5 1.5 1.5 µs max

2 DAC X1 2.1 2.1 2.1 µs max

3 DAC X1 2.7 2.7 2.7 µs max

4 DAC X1 3.3 3.3 3.3 µs max

Other Registers 270 270 270 ns max System control register/PMU registers

t11 20 20 20 ns min

t12 20 20 20 ns min

t13 150 150 150 ns min

t14 0 0 0 ns min

t15 100 100 100 ns max

2

From dc to 1 kHz

DVCC, Limit at T

2.3 V to 2.7 V 2.7 V to 3.6 V 4.5 V to 5.25 V

MIN

, T

MAX

Unit Description

1030 735 735 ns min Single channel update cycle time (X1 register write)

950 655 655 ns min

Single channel update cycle time (any other register

write)

30 20 20 ns min SCLK cycle time

falling edge to SCLK falling edge setup time

SYNC

Minimum SYNC

high time in write mode after X1

register write (one channel)

70 70 70 ns min

Minimum SYNC

high time in write mode after any

other register write

th

SCLK falling edge to SYNC rising edge

29

5 5 5 ns min Data setup time

rising edge to BUSY falling edge

SYNC

pulse width low; see Table 17

BUSY

th

SCLK falling edge to LOAD falling edge

29

pulse width low

LOAD

rising edge to FOHx output response time

BUSY

rising edge to LOAD falling edge

BUSY

rising edge to FOHx output response time

LOAD

Rev. A | Page 11 of 60

AD5522

www.BDTIC.com/ADI

Parameter

1 , 2 , 3

2.3 V to 2.7 V 2.7 V to 3.6 V 4.5 V to 5.25 V

t16 1.8 1.2 0.9 ns min

t17 670 700 750 µs max

t18 400 400 400 ns min

DVCC, Limit at T

5, 6

t

60 45 25 ns max SCLK rising edge to SDO valid; DVCC = 5 V to 5.25 V

19

1

Guaranteed by design and characterization; not production tested.

2

All input signals are specified with tR = tF = 2 ns (10% to 90% of DVCC) and timed from a voltage level of 1.2 V.

3

See Figure 5 and Figure 6.

4

Writes to more than one X1 register, engages the calibration engine for longer times, shown by the

should either be timed or should wait until

5

t19 is measured with the load circuit shown in Figure 4.

6

SDO output slows with lower DVCC supply and may require use of a slower SCLK.

BUSY

returns high (see Figure 53). This is required to ensure data is not lost or overwritten.

Table 3. LVDS Interface

DVCC, Limit at T

Parameter

1, 2, 3

2.7 V to 3.6 V 4.5 V to 5.25 V Unit Description

t1 20 12 ns min SCLK cycle time

t2 8 5 ns min SCLK pulse width high and low time

t3 3 3 ns min

t4 3 3 ns min Data setup time

t5 5 3 ns min Data hold time

t6 3 3 ns min

4

t

7

45 25 ns min SCLK rising edge to SDO valid

t8 150 150 ns min

70 70 ns min

400 400 ns min

1

Guaranteed by design and characterization; not production tested.

2

All input signals are specified with tR = tF = 2 ns (10% to 90% of DVCC) and timed from a voltage level of 1.2 V.

3

See Figure 7.

4

SDO output slows with lower DVCC supply and may require use of slower SCLK.

MIN

MIN

, T

MAX

Unit Description

RESET

RESET

Minimum SYNC

BUSY

low time, t10. Subsequent writes to one or more X1 registers

, T

MAX

SYNC

SCLK to SYNC

Minimum SYNC

register write

Minimum SYNC

other register write

Minimum SYNC

pulse width low

time indicated by BUSY low

high time in readback mode

to SCLK setup time

hold time

high time in write mode after X1

high time in write mode after any

high time in readback mode

Rev. A | Page 12 of 60

AD5522

www.BDTIC.com/ADI

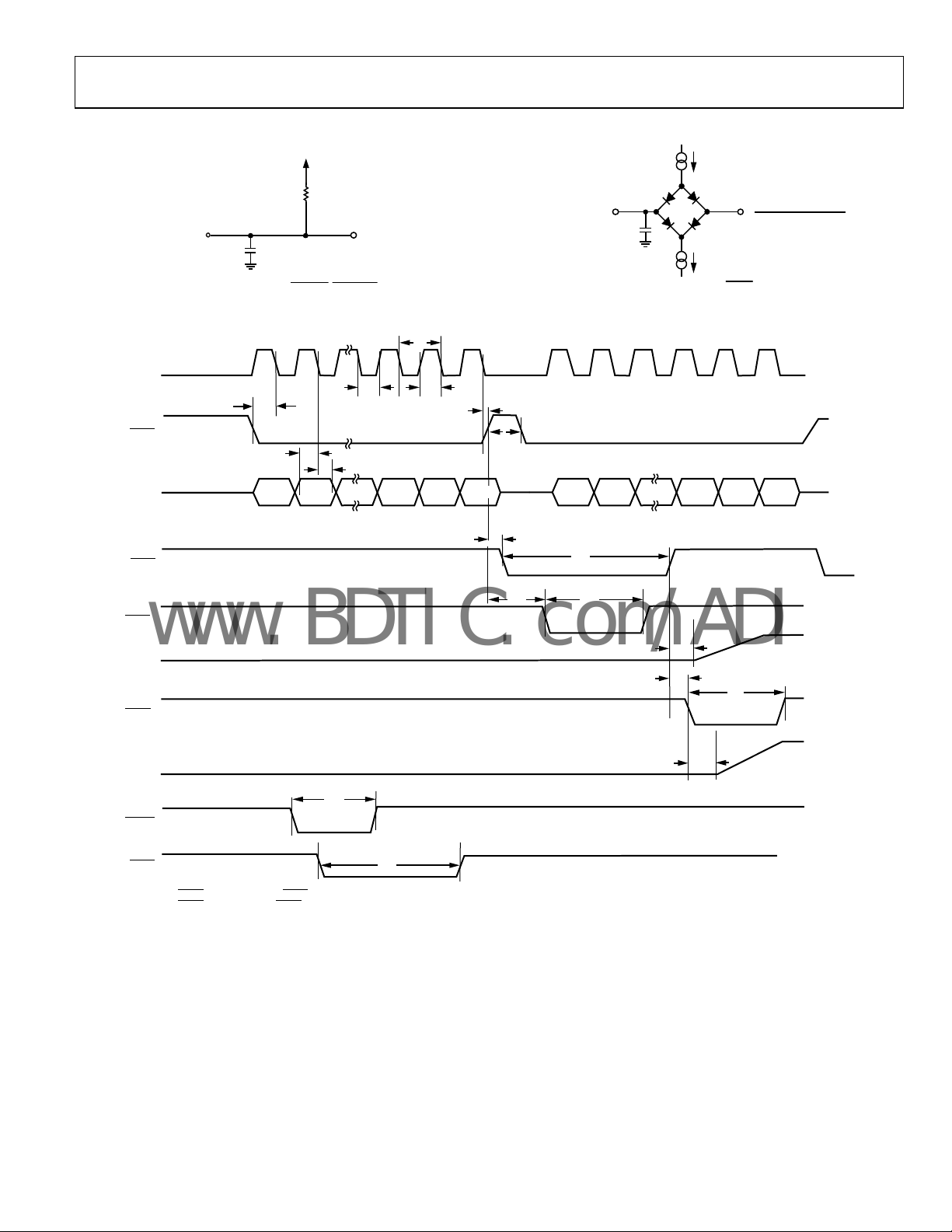

Circuit and Timing Diagrams

TO

OUTPUT

PIN

Figure 3. Load Circuit for

SCLK

SYNC

SDI

BUSY

C

DVCC

2.2kΩ

R

LOAD

V

50pF

LOAD

CGALM, TMPALM

11

2

t

4

t

7

DB28

OL

06197-003

t

1

29

t

3

t

8

t

2

t

6

t

5

DB0

t

9

TO OUTPUT

PIN

Figure 4. Load Circuit for SDO,

DB28

t

10

C

LOAD

50pF

200µA I

200µA I

OL

VOH(MIN) – VOL(MAX)

OH

BUSY

Timing Diagram

2

00406197-

29

DB0

LOAD

FOHx

LOAD

FOHx

RESET

BUSY

1

1

2

2

1

LOAD ACTIVE DURING BUSY.

2

LOAD ACTIVE AFTER BUSY.

t

11

t

16

t

17

t

12

t

13

t

14

t

12

t

15

06197-005

Figure 5. SPI Write Timing (Write Word Contains 29 Bits)

Rev. A | Page 13 of 60

AD5522

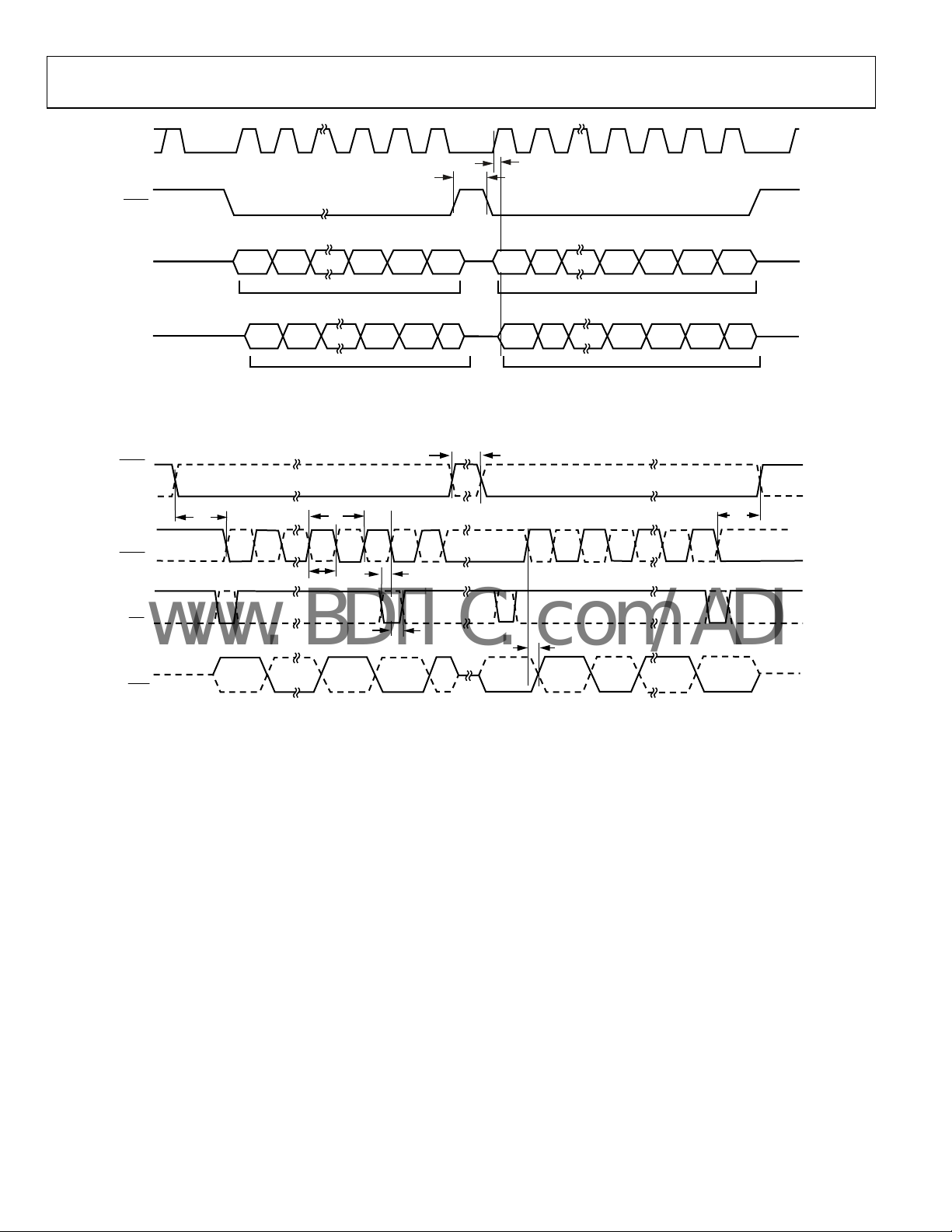

www.BDTIC.com/ADI

SCLK

SYNC

29

t

t

18

19

58

SDI

SDO

INPUT WORD SPECIFIES

REGISTE R TO BE READ

UNDEFINED

DB23/

0BD82BD DB0

DB28

DB23/

DB28

NOP CONDITION

SELECTED REGISTER DATA

CLOCKED OUT

DB0

7-0060619

Figure 6. SPI Read Timing (Readback Word Contains 24 Bits and Can Be Clocked Out with a Minimum of 24 Clock Edges)

t

SYNC

SYNC

SCLK

SCLK

SDI

SDI

SDO

SDO

t

3

MSB

D28

t

1

t

2

UNDEFINED

LSB

D0

t

4

t

5

8

MSB

D23/D28

LSB

D0

t

7

MSB

DB23/

DB28

SELECTED REGISTER DAT A CLOCKED OUT

LSB

DB0

t

6

6197-007

Figure 7. LVDS Read and Write Timing (Readback Word Contains 24 Bits and Can Be Clocked Out with a Minimum of 24 Clock Edges)

Rev. A | Page 14 of 60

AD5522

www.BDTIC.com/ADI

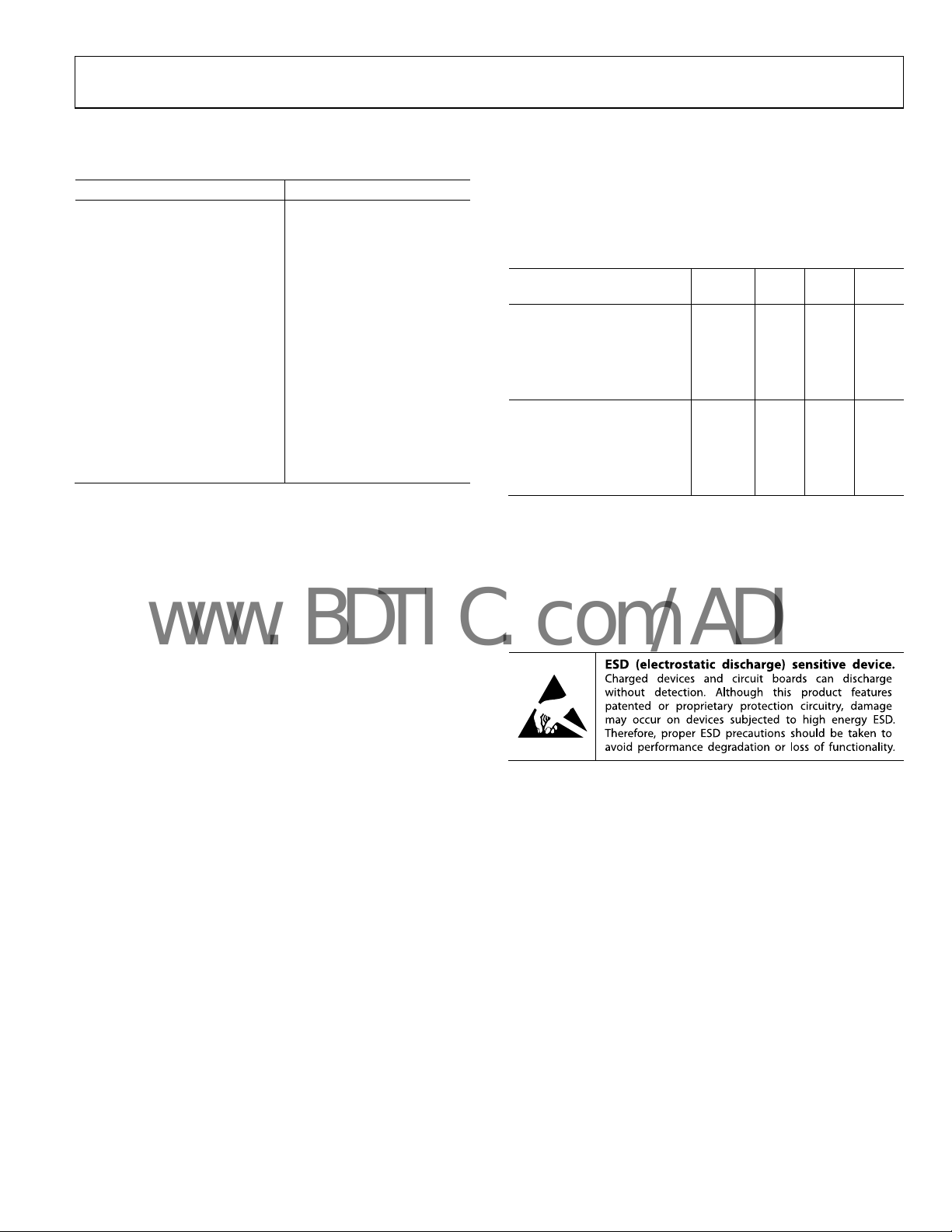

ABSOLUTE MAXIMUM RATINGS

Table 4.

Parameter

Supply Voltage, AVDD to AVSS 34 V

AVDD to AGND −0.3 V to +34 V

AVSS to AGND +0.3 V to −34 V

VREF to AGND −0.3 V to +7 V

DUTGND to AGND AVDD + 0.3 V to AVSS − 0.3 V

REFGND to AGND AVDD + 0.3 V to AVSS − 0.3 V

DVCC to DGND −0.3 V to +7 V

AGND to DGND −0.3 V to +0.3 V

Digital Inputs to DGND −0.3 V to DVCC + 0.3 V

Analog Inputs to AGND AVSS − 0.3 V to AVDD + 0.3 V

Storage Temperature Range −65°C to +125°C

Operating Junction Temperature

Range (J Version)

Reflow Soldering JEDEC Standard (J-STD-020)

Junction Temperature 150°C max

Rating

25°C to 90°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

Thermal resistance values are specified for the worst-case

conditions, that is, a device soldered in a circuit board for

surface-mount packages.

1

Table 5. Thermal Resistance

Package Type

TQFP Exposed Pad Down 4.8 °C/W

No Heat Sink

200 17.2

500 15.1

With Cooling Plate at 45°C

TQFP Exposed Pad Up 2 °C/W

No Heat Sink

200 37.2

500 35.7

With Cooling Plate at 45°C3 N/A4 3.0 2 °C/W

1

The information in this section is based on simulated thermal information.

2

These values apply to the package with no heat sink attached. The actual

thermal performance of the package depends on the attached heat sink and

environmental conditions.

3

Natural convection at 55°C ambient. Assumes perfect thermal contact

between the cooling plate and the exposed paddle.

3

N/A means not applicable.

2

0 22.3 °C/W

2

0 42.4 °C/W

(JEDEC 4-Layer (1S2P) Board)

Airflow

(LFPM) θJA θJC

3

N/A 5.4 4.8 °C/W

Unit

°C/W

°C/W

°C/W

°C/W

ESD CAUTION

Rev. A | Page 15 of

60

AD5522

www.BDTIC.com/ADI

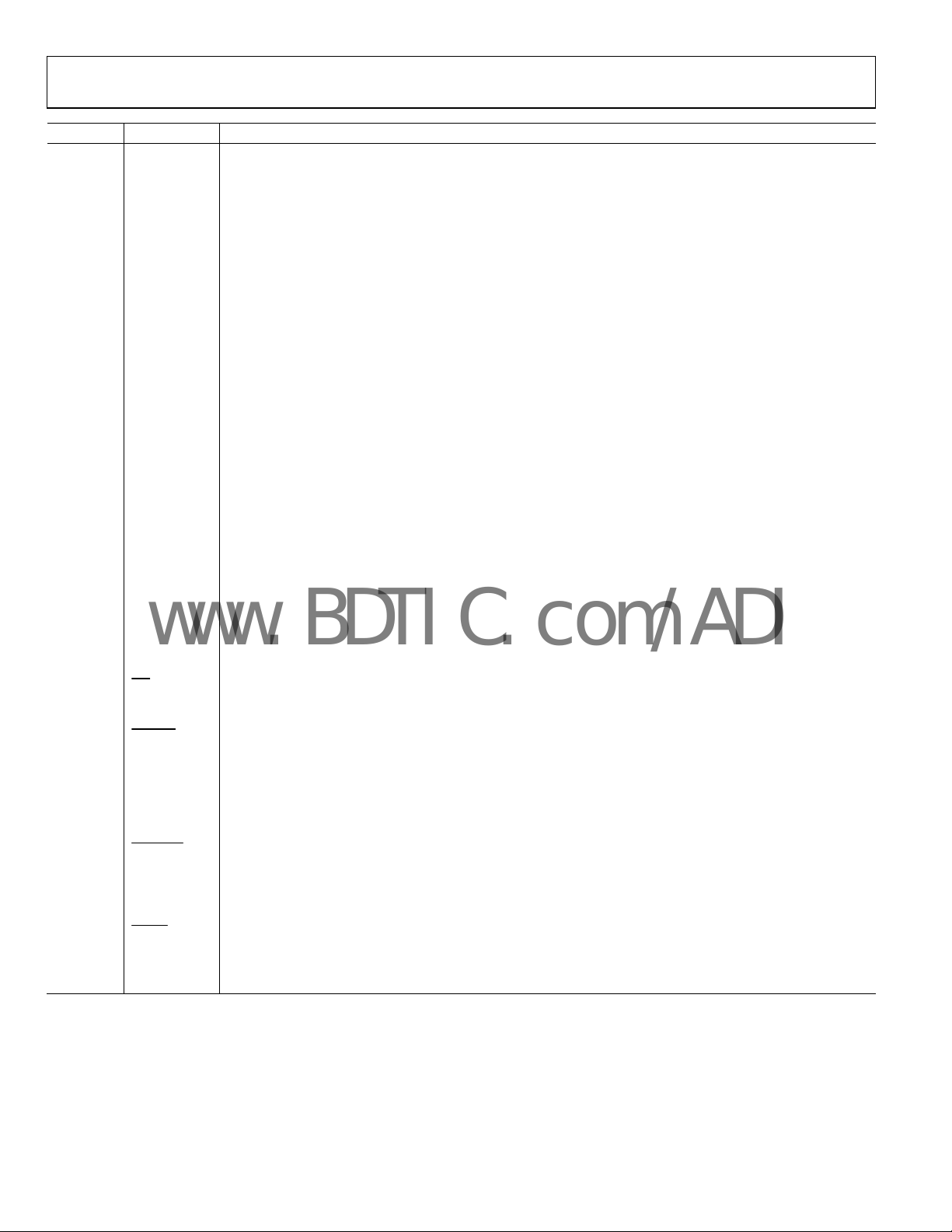

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

EXTFOH162AVSS

EXTFOH0

80

1

AVDD

CFF0

CCOMP0

EXTMEASIH0

EXTMEASIL0

FOH0

GUARD0

GUARDIN0/DUTGND0

GUARDIN2/DUTGND2

NOTES:

1.

FOR PROPER CONNECTION OFTHE EXPOSED PAD, REFER T O THE PIN CONFIGURAT I ON AND FUNCTIO N DESCRIPT IONS SECTI ON OF THIS DATA SHEE T.

MEASVH0

AGND

AGND

MEASVH2

GUARD2

FOH2

EXTMEASIL2

EXTMEASIH2

CCOMP2

CFF2

AVDD

PIN 1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

AVSS

SCLK

BUSY

EXTFOH2

CPOL0/SCLK

AD5522

TOP VIEW

EXPOSED PAD ON BOTTOM

(Not to S cale)

27

28

29

30

SDI

SYNC

DGND

CPOH0/SDI

CPOL1/SYNC

SYS_FORCE69AGND70SYS_SENSE71REFGND72VREF73DUTGND74AVDD75SPI/LVDS76CGALM77TMPALM78RESET79AVSS

68

31

32 33

CPOH1/SDO

35

SDO

LOAD34DVCC

CPOL2/CPO0

Figure 8. Pin Configuration, Exposed Pad on Bottom

MEASOUT364MEASOUT265MEASOUT166MEASOUT067AVSS

61

63

60

AVDD

59

CFF1

58

CCOMP1

57

EXTMEASIH1

56

EXTMEASIL1

55

FOH1

54

GUARD1

53

GUARDIN1/DUTGND1

52

MEASVH1

51

AGND

50

AGND

49

MEASVH3

48

GUARDIN3/DUTGND3

47

GUARD3

46

FOH3

45

EXTMEASIL3

44

EXTMEASIH3

43

CCOMP3

42

CFF3

41

AVDD

36

37

38

39

40

AVSS

EXTFOH3

CPOL3/CPO2

CPOH2/CPO1

CPOH3/CPO3

06197-008

Table 6. Pin Function Descriptions

Pin No. Mnemonic Description

Exposed pad

The exposed pad is internally electrically connected to AVSS. For enhanced thermal, electrical, and board level

performance, the exposed paddle on the bottom of the package should be soldered to a corresponding

thermal land paddle on the PCB.

1, 20, 41,

AVDD

Positive Analog Supply Voltage.

60, 74

2 CFF0

External Capacitor for Channel 0. This pin optimizes the stability and settling time performance of the force

amplifier when in force voltage mode. See the Compensation Capacitors section.

3 CCOMP0

4 EXTMEASIH0

5 EXTMEASIL0

6 FOH0

7 GUARD0

8

GUARDIN0/

DUTGND0

Compensation Capacitor Input for Channel 0. See the Compensation Capacitors section.

Sense Input (High Sense) for High Current Range (Channel 0).

Sense Input (Low Sense) for High Current Range (Channel 0).

Force Output for Internal Current Ranges (Channel 0).

Guard Output Drive for Channel 0.

Guard Amplifier Input for Channel 0/DUTGND Input for Channel 0. This dual function pin is configured via the

serial interface. The default function at power-on is GUARDIN0. If this pin is configured as a DUTGND input for

the channel, the input to the guard amplifier is internally connected to MEASVH0. For more information, see

the Device Under Test Ground (DUTGND) section and the Guard Amplifier section.

9 MEASVH0

10, 11, 50,

AGND

DUT Voltage Sense Input (High Sense) for Channel 0.

Analog Ground. These pins are the reference points for the analog supplies and the measure circuitry.

51, 69

12 MEASVH2 DUT Voltage Sense Input (High Sense) for Channel 2.

Rev. A | Page 16 of 60

AD5522

www.BDTIC.com/ADI

Pin No. Mnemonic Description

13

14 GUARD2 Guard Output Drive for Channel 2.

15 FOH2 Force Output for Internal Current Ranges (Channel 2).

16 EXTMEASIL2 Sense Input (Low Sense) for High Current Range (Channel 2).

17 EXTMEASIH2 Sense Input (High Sense) for High Current Range (Channel 2).

18 CCOMP2 Compensation Capacitor Input for Channel 2. See the Compensation Capacitors section.

19 CFF2

21 EXTFOH2

22, 39, 62,

67, 79

23

24 SCLK

25

26

27 SDI Serial Data Input for SPI or LVDS Interface.

28

29 CPOL1/SYNC Comparator Output Low (Channel 1) for SPI Interface/Differential SYNC Input for LVDS Interface.

30 DGND Digital Ground Reference Point.

31

32 SDO Serial Data Output for SPI or LVDS Interface. This pin can be used for data readback and diagnostic purposes.

33

34 DVCC Digital Supply Voltage.

35 CPOL2/CPO0

36 CPOH2/CPO1

37 CPOL3/CPO2

38 CPOH3/CPO3

40 EXTFOH3

42 CFF3

43 CCOMP3 Compensation Capacitor Input for Channel 3. See the Compensation Capacitors section.

44 EXTMEASIH3 Sense Input (High Sense) for High Current Range (Channel 3).

45 EXTMEASIL3 Sense Input (Low Sense) for High Current Range (Channel 3).

46 FOH3 Force Output for Internal Current Ranges (Channel 3).

47 GUARD3 Guard Output Drive for Channel 3.

48

GUARDIN2/

DUTGND2

Guard Amplifier Input for Channel 2/DUTGND Input for Channel 2. This dual function pin is configured via the

serial interface. The default function at power-on is GUARDIN2. If this pin is configured as a DUTGND input for

the channel, the input to the guard amplifier is internally connected to MEASVH2. For more information, see

the Device Under Test Ground (DUTGND) section and the Guard Amplifier section.

External Capacitor for Channel 2. This pin optimizes the stability and settling time performance of the force

amplifier when in force voltage mode. See the Compensation Capacitors section.

Force Output for High Current Range (Channel 2). Use an external resistor at this pin for current ranges up to

±80 mA. For more information, see the Current Range Selection section.

AVSS Negative Analog Supply Voltage.

Digital Input/Open-Drain Output. This pin indicates the status of the interface. See the BUSY and LOAD

BUSY

Functions section for more information.

Serial Clock Input, Active Falling Edge. Data is clocked into the shift register on the falling edge of SCLK. This

pin operates at clock speeds up to 50 MHz.

CPOL0/SCLK

Comparator Output Low (Channel 0) for SPI Interface/Differential Serial Clock Input (Complement) for LVDS

Interface.

CPOH0/SDI

Comparator Output High (Channel 0) for SPI Interface/Differential Serial Data Input (Complement) for LVDS

Interface.

SYNC

CPOH1/SDO

Active Low Frame Synchronization Input for SPI or LVDS Interface.

Comparator Output High (Channel 1) for SPI Interface/Differential Serial Data Output (Complement) for LVDS

Interface.

Logic Input (Active Low). This pin synchronizes updates within one device or across a group of devices. If

LOAD

synchronization is not required, LOAD

can be tied low; in this case, DAC channels and PMU modes are updated

immediately after BUSY goes high. See the BUSY and LOA D Functions section for more information.

Comparator Output Low (Channel 2) for SPI Interface/Comparator Output Window (Channel 0) for LVDS

Interface.

Comparator Output High (Channel 2) for SPI Interface/Comparator Output Window (Channel 1) for LVDS

Interface.

Comparator Output Low (Channel 3) for SPI Interface/Comparator Output Window (Channel 2) for LVDS

Interface.

Comparator Output High (Channel 3) for SPI Interface/Comparator Output Window (Channel 3) for LVDS

Interface.

Force Output for High Current Range (Channel 3). Use an external resistor at this pin for current ranges up to

±80 mA. For more information, see the Current Range Selection section.

External Capacitor for Channel 3. This pin optimizes the stability and settling time performance of the force

amplifier when in force voltage mode. See the Compensation Capacitors section.

GUARDIN3/

DUTGND3

Guard Amplifier Input for Channel 3/DUTGND Input for Channel 3. This dual function pin is configured via the

serial interface. The default function at power-on is GUARDIN3. If this pin is configured as a DUTGND input for

the channel, the input to the guard amplifier is internally connected to MEASVH3. For more information, see

the Device Under Test Ground (DUTGND) section and the Guard Amplifier section.

Rev. A | Page 17 of 60

AD5522

www.BDTIC.com/ADI

Pin No. Mnemonic Description

49 MEASVH3 DUT Voltage Sense Input (High Sense) for Channel 3.

52 MEASVH1 DUT Voltage Sense Input (High Sense) for Channel 1.

53

54 GUARD1 Guard Output Drive for Channel 1.

55 FOH1 Force Output for Internal Current Ranges (Channel 1).

56 EXTMEASIL1 Sense Input (Low Sense) for High Current Range (Channel 1).

57 EXTMEASIH1 Sense Input (High Sense) for High Current Range (Channel 1).

58 CCOMP1 Compensation Capacitor Input for Channel 1. See the Compensation Capacitors section.

59 CFF1

61 EXTFOH1

63 MEASOUT3

64 MEASOUT2

65 MEASOUT1

66 MEASOUT0

68 SYS_FORCE External Force Signal Input. This pin enables the connection of the system PMU.

70 SYS_SENSE External Sense Signal Output. This pin enables the connection of the system PMU.

71 REFGND Accurate Analog Reference Input Ground.

72 VREF Reference Input for DAC Channels (5 V for specified performance).

73 DUTGND

75

76

77

78

80 EXTFOH0

GUARDIN1/

DUTGND1

/LVDS Interface Select Pin. Logic low selects SPI-compatible interface mode; logic high selects LVDS interface mode.

SPI

Open-Drain Output for Guard and Clamp Alarms. This open-drain pin provides shared alarm information

CGALM

TMPALM

Digital Reset Input. This active low, level sensitive input resets all internal nodes on the device to their power-

RESET

Guard Amplifier Input for Channel 1/DUTGND Input for Channel 1. This dual function pin is configured via the

serial interface. The default function at power-on is GUARDIN1. If this pin is configured as a DUTGND input for

the channel, the input to the guard amplifier is internally connected to MEASVH1. For more information, see

the Device Under Test Ground (DUTGND) section and the Guard Amplifier section.

External Capacitor for Channel 1. This pin optimizes the stability and settling time performance of the force

amplifier when in force voltage mode. See the Compensation Capacitors section.

Force Output for High Current Range (Channel 1). Use an external resistor at this pin for current ranges up to

±80 mA. For more information, see the Current Range Selection section.

Multiplexed DUT Voltage, Current Sense Output, Temperature Sensor Voltage for Channel 3. This pin is

referenced to AGND.

Multiplexed DUT Voltage, Current Sense Output, Temperature Sensor Voltage for Channel 2. This pin is

referenced to AGND.

Multiplexed DUT Voltage, Current Sense Output, Temperature Sensor Voltage for Channel 1. This pin is

referenced to AGND.

Multiplexed DUT Voltage, Current Sense Output, Temperature Sensor Voltage for Channel 0. This pin is

referenced to AGND.

DUT Voltage Sense Input (Low Sense). By default, this input is shared among all four PMU channels. If a DUTGND

input is required for each channel, the user can configure the GUARDINx/DUTGNDx pins as DUTGND inputs for

each PMU channel.

This pin has a pull-down current source (~350 A). In LVDS interface mode, the CPOHx and CPOLx pins default

to differential interface pins.

about the guard amplifier and clamp circuitry. By default, this output pin is disabled. The system control

register allows the user to enable this function and to set the open-drain output as a latched output. The user

can also choose to enable alarms for the guard amplifier, the clamp circuitry, or both. When this pin flags an

alarm, the origins of the alarm can be determined by reading back the alarm status register. Two flags per

channel in this word (one latched, one unlatched) indicate which function caused the alarm and whether the

alarm is still present.

Open-Drain Output for Temperature Alarm. This latched, active low, open-drain output flags a temperature

alarm to indicate that the junction temperature has exceeded the default temperature setting (130°C) or the

user programmed temperature setting. Two flags in the alarm status register (one latched, one unlatched)

indicate whether the temperature has dropped below 130°C or remains above 130°C. User action is required

to clear this latched alarm flag by writing to the clear bit (Bit 6) in any of the PMU registers.

on reset values.

Force Output for High Current Range (Channel 0). Use an external resistor at this pin for current ranges up to

±80 mA. For more information, see the Current Range Selection section.

Rev. A | Page 18 of 60

Loading...

Loading...