查询AD5520供应商查询AD5520供应商

Per Pin Parametric

Measurement Unit/Source Measure Unit

AD5520

FEATURES

Force/Measure Functions

Force Voltage/Current, Measure Current/Voltage

Force Current/Voltage, Measure Current/Voltage

Force/Measure Voltage Range 11 V

4 Programmable Force/Measure Current Ranges

4 A, 40 A, 400 A, 4 mA

Extended Current Ranges

40 mA and 160 mA with External Driver

Clamp Circuitry and Window Comparators On Board

Guard Amplifier

64-Lead LQFP Package

APPLICATIONS

Automatic Test Equipment

Per Pin PMU, Shared Pin PMU, Device Power Supply

Instrumentation

Source Measure, Parametric Measurement, Precision

Measurement

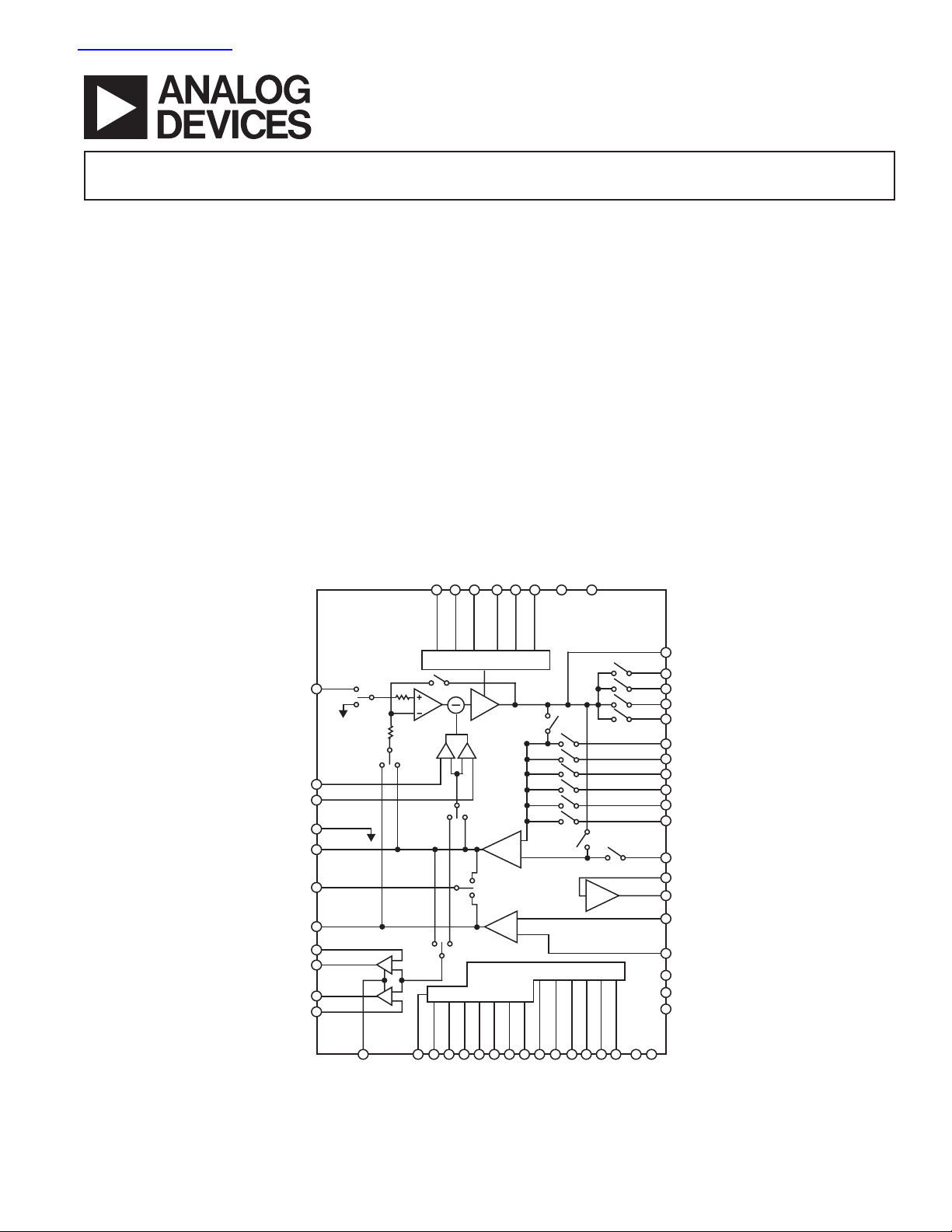

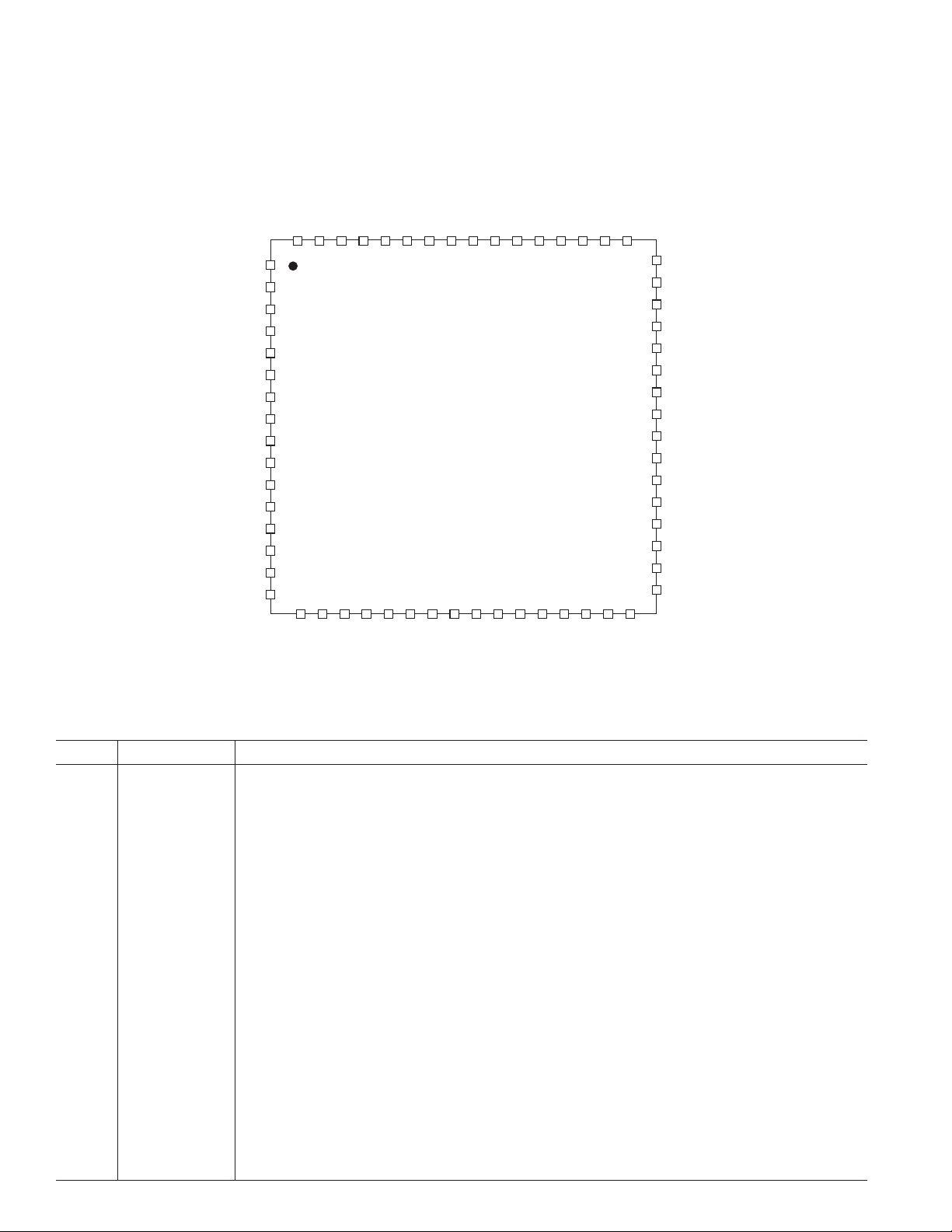

FUNCTIONAL BLOCK DIAGRAM

AD5520

FIN

CLH

CLL

REFGND

MEASIOUT

MEASOUT

MEASVOUT

COMPARATOR

CPH

CPOH

CPOH

CPL

CPCK

REV. A

COMPIN1

COMPIN0

STB

STANDBY

GENERAL DESCRIPTION

The AD5520 is a single channel per pin parametric measurement unit (PPMU) for use in semiconductor automatic test

equipment. The part is also suited for use as a source

measurement unit for instrumentation applications. It

contains programmable modes to force a pin voltage and

measure the corresponding current or force a current and

measure the voltage. The AD5520 can force/measure over a

± 11 V range or currents up to ± 4 mA with its on-board

force amplifier. An external amplifier is required for wider

current ranges. The device provides a force sense capability to

ensure accuracy at the tester pin. A guard output is also

available to drive the shield of a force/sense pair. The AD5520

is available in a 64-lead LQFP package.

AVEEAV

CC

COMPIN2

BW SELECT

CLAMP

DETECT

LOGICS

FSEL

CPSEL

COMPOUT1

COMPOUT0

G = 16

I

SENSE

INST AMP

V

SENSE

INST AMP

G = 1

AM1

AM2

MSEL

COMPOUT2

MOE

CLHDETECT

AM0

MEASI5H

MEASI4H

MEASI3H

MEASI2H

MEASI1H

MEASI0H

GUARDIN

G = 1

MEASVH

MEASVL

CLLDETECT

AC0

AC1

FOH

FOH3

FOH2

FOH1

FOH0

MEASIL

GUARD

AGND

QM5

QM4

DVDDCS

DGND

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

(AVCC = +15 V 5%, AVEE = –15 V 5%, DVDD = 5 V 10%, AGND = 0 V, REFGND = 0 V,

AD5520–SPECIFICATIONS

DGND = 0 V. All specifications 0C to 70C, unless otherwise noted.)

Parameter Min Typ1Max Unit Test Conditions/Comments

VOLTAGE FORCE MODE

Force Control Output Voltage Range ⫾11 V R

= 10 kΩ, C

LOAD

LOAD

= 50 pF

FOH Output Impedance 70 Ω

FOH0 2.5 kΩ

FOH1 3 kΩ

FOH2 500 Ω

FOH3 60 Ω

Input Offset Error ⫾1 ⫾5mV

Gain Error 1 %

Clamp Voltage Error

2

⫾1% FSof FIN

CURRENT MEASURE/FORCE Set with external sense resistors

FOH0 ± 4 µA MODE0, RS = 125 kΩ

FOH1 ± 40 µA MODE1, R

FOH2 ± 400 µA MODE2, R

= 12.5 kΩ

S

= 12.5 kΩ

S

FOH3 ± 4mAMODE3, RS = 125 Ω

CURRENT MEASURE MODE

High Sense Input Range, V

Linearity

3

Input Bias Current ⫾1 ⫾3nA

Input Bias Current Drift

1

MEASIxH

50 pA/°C

⫾11 V

⫾0.01 % FSR +11 V > V

> –11 V

FOL

Output Offset Error ⫾100 mV MODE0

⫾100 mV MODE1

⫾100 mV MODE2

⫾100 mV MODE3

Gain Error ⫾0.1 ⫾0.35 % Gain of 16

Gain Error Temperature Coefficient

4

30 µV/°C

MEASIOUT Output Load Current ⫾4mA

CMRR 95 dB @ DC

CURRENT FORCE MODE

Input Offset Error ⫾10 mV With MODE0, MODE1, MODE2, MODE3

Gain Error 1 %

Clamp Current Error

2

⫾1% FSof FIN

VOLTAGE MEASURE MODE

Differential Input Range ⫾11 V

Low Sense Input Voltage Range ⫾100 mV MEASVL

Linearity

3

+0.005 % FSR +11 V > V

MEASVH

to V

MEASVL

> –11 V

Input Offset Error ⫾5 ⫾10 mV FIN = 0 V, Measured @ MEASVOUT

Input Offset Error Temperature

Coefficient

Gain Error ⫾0.03 ⫾0.15 % Gain of 1

Gain Error Temperature Coefficient

Input Bias Current ⫾1 ⫾3nA

Input Bias Current Drift

MEASVOUT Output Load Current ⫾4mA

CMRR

AMPLIFIER SETTLING TIME

V

SENSE

I

SENSE

LOOP SETTLING

1

4

4

4

4, 5

⫾15 mV/°C

2 mV/°C

50 pA/°C

73 dB @ DC

Amp 20 µsTo 0.2%

Amp 12 µsTo 0.2%

4, 5

Settling to within 0.024% of 8 V step

COMPIN2 = 100 pF 450 600 µs MODE0

285 390 µs MODE1

170 240 µs MODE2, MODE3

COMPIN1 = 1000 pF 2 2.5 ms MODE0

1.8 2.4 ms MODE1, MODE2, MODE3

COMPIN0 = 3000 pF 5.75 8.7 ms MODE0, MODE1, MODE2, MODE3

REV. A–2–

Parameter Min Typ1Max Unit Test Conditions/Comments

SLEW RATE

4, 5

50 mV/µs COMPIN2 = 100 pF

4.3 mV/µs COMPIN1 = 1000 pF

1.28 mV/µs COMPIN0 = 3000 pF

COMPARATOR

CPH, CPL Input Range ⫾11 V V

CPH

> V

CPL

Input Offset ⫾7mV

GUARD DRIVER

Output Voltage ⫾11 V

Output Impedance 130 Ω Capacitive Load Only

Output Offset Voltage 400 mV

Load Current

Output Settling Time

4

4

⫾4mA

0.5 2 µs 100 pF Capacitive Load

ANALOG REFERENCE INPUTS

Force Control Input Range ⫾11 V

Force Control Input Impedance 1 MΩ

Clamp Control Input Range ⫾11 V V

CLH

> V

CLL

Clamp Control Input Impedance 1 MΩ

Comparator Threshold Input Range ⫾11 V

Comparator Threshold Input Impedance 1 MΩ

Input Capacitance

4

3pF

ANALOG MEASUREMENT OUTPUTS

Voltage Measure Output Impedance 2 Ω

Current Measure Output Impedance 3 Ω

Multiplexed Sense Output Impedance 1 kΩ

Input Capacitance

MEASIxH, MEASVH, FOHx 8 pF

LOGIC INPUTS

Input Current ⫾1 µAAll digital inputs together

Input Low Voltage, V

Input High Voltage, V

Input Capacitance

LOGIC OUTPUTS

Output Low Voltage, V

Output High Voltage, V

INL

IHL

4

4

OL

4

OH

POWER REQUIREMENTS

AV

CC

AV

EE

Power Supply Rejection Ratio, PSRR

2.0 V

2.4 V I

+14.25 +15 +15.75 V For specific performance

–14.25 –15 +15.75 V

1

0.8 V

3pF

0.4 V I

= 2 mA

SINK

SOURCE

= 2 mA

6

FOH –25 dB 100 kHz

–16 dB 500 kHz

–15 dB 1 MHz

MEASOUT –55 dB 100 kHz

–10 dB 500 kHz

DC PSR 90 dB

DV

DD

I

AVCC

I

AVEE

I

DVDD

NOTES

1

Typical values are at 25°C and nominal supply, unless otherwise noted.

2

Full-scale = 11 V.

3

Full-scale range = 22 V.

4

Guaranteed by design and characterization but not subject to production test.

5

Force control amplifier dominates slew rate and settling time.

6

Operational with ± 12 V supplies, force/measure range is reduced to ± 8.5 V.

Specifications subject to change without notice.

5V

12 mA

12 mA

0.5 mA Digital inputs at supply rails

AD5520

REV. A

–3–

AD5520

(AVCC = +15 V 5%, AVEE = –15 V 5%, AGND = 0 V, REFGND = 0 V, DGND = 0 V. All

1, 2

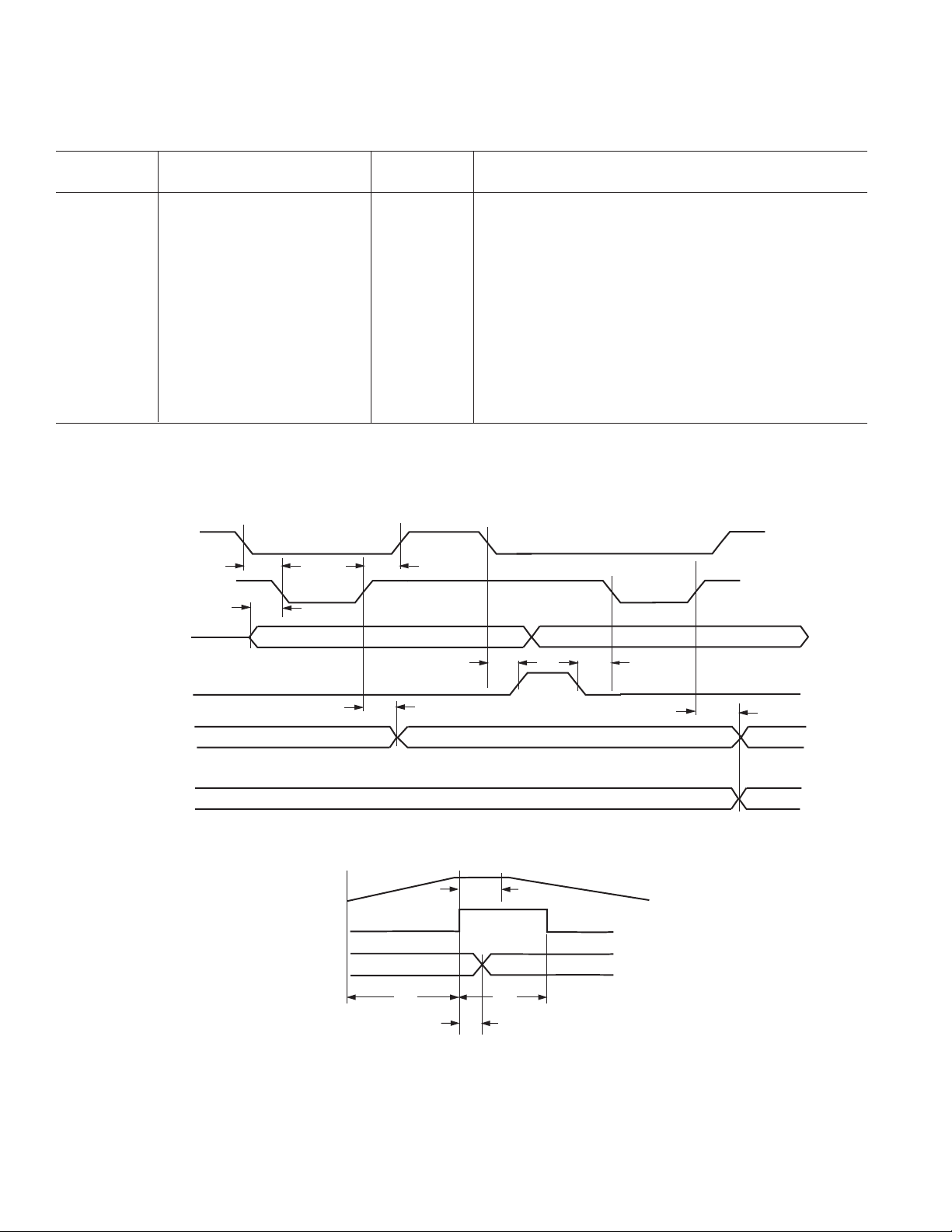

TIMING CHARACTERISTICS

DV

Parameter 5 V 10% 3.3 V Unit Conditions/Comments

t

1

t

2

t

3

t

4

t

5

t

6

t

7

t

8

t

9

t

10

t

11

t

12

t

13

NOTES

1

See Figure 1.

2

All input signals are specified with tr = tf = 1 ns (10% to 90% of VDD) and timed from a voltage level of (VIL + VIH)/2.

Specifications subject to change without notice.

00ns min CS Falling Edge to STB Falling Edge Setup Time

30 200 ns min STB Pulse Width

40 70 ns min STB Rising Edge to CS Rising Edge Setup Time

040ns min Data Setup Time

550 560 ns min CS Falling Edge to CPCK Rising Edge Setup Time

320 320 ns min CPCK Pulse Width

450 500 ns min CPCK to STB Falling Edge Setup Time

150 800 ns min STB Rising Edge to QMx, CLxDETECT Valid

100 440 ns min STB Rising Edge to CPOH, CPOL Valid

240 240 µs min Comparator Setup Time, MODE2, MODE3 settling

150 500 ns min Comparator Hold Time

100 440 ns min Comparator Output Delay Time

320 320 ns min Comparator Strobe Pulse Width

DD

specifications 0C to 70C, unless otherwise noted.)

STB

AMx, ACx, FSEL,

MSEL, CPSEL

CPCK

QM4, QM5,

CLHDETECT,

CLLDETECT

CPOL, CPOH

CS

t

1

t

4

MEASVOUT

OR MEASIOUT

CPOH, CPOL

t

2

CPCK

t

3

t

5

t

8

Figure 1. Timing Diagram

t

11

t

10

t

12

t

13

t

t

6

7

t

9

Figure 2. Comparator Timing

REV. A–4–

AD5520

ABSOLUTE MAXIMUM RATINGS*

(TA = 25°C, unless otherwise noted.)

AVCC to AVEE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 V

to AGND . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V, +17 V

AV

CC

AV

to AGND . . . . . . . . . . . . . . . . . . . . . . . . . +0.3 V, –17 V

EE

DV

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +6 V

DD

Digital Inputs to DGND . . . . . . . . . . –0.3 V to DV

Analog Inputs to AGND . . . . . AV

C

to CLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +34 V

LH

to CPL . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +34 V

C

PH

REFGND, DGND . . . . . . . . . AV

+ 0.3 V to AVEE – 0.3 V

CC

+ 0.3 V to AVEE – 0.3 V

CC

+ 0.3 V

DD

Operating Temperature Range

Commercial (J Version) . . . . . . . . . . . . . . . . . . 0°C to 70°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Maximum Junction Temperature, (T

Package Power Dissipation . . . . . . . . . . . . . (T

Thermal Impedance JA . . . . . . . . . . . . . . . . . . . . . . 47.8°C/W

Lead Temperature (Soldering 10 sec) . . . . . . . . . . . . . . 300°C

IR Reflow, Peak Temperature . . . . . . . . . . . . . . . . . . . . 220°C

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those listed in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD5520JST 0°C to 70°C 64-Lead LQFP ST-64-2

AD5520JST-REEL 0°C to 70°C 64-Lead LQFP ST-64-2

EVAL-AD5520EB Evaluation Board and Software

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

AD5520 features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended

to avoid performance degradation or loss of functionality.

max) . . . . . . . . . 150°C

J

max – TA)/

J

JA

REV. A

–5–

AD5520

CPH

CPL

DV

CPOH

CPOL

CPCK

DGND

CLHDETECT

CLLDETECT

QM4

QM5

MOE

CS

STB

AC0

AC1

PIN CONFIGURATION

64-Lead LQFP

COMPIN0

COMPIN1

COMPIN2

REFGND

MEASOUT

REFGND

MEASIOUT

MEASVOUT

FIN

CLH

CLL

1

2

3

DD

4

5

6

7

8

9

10

11

12

13

14

15

16

17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

AD5520

(Not to Scale)

COMPOUT1

COMPOUT2

CC_B

COMPOUT0

AV

49505152535455565758596061626364

FOH

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

AV

EE_B

MEASI5H

MEASI4H

FOH3

MEASI3H

FOH2

MEASI2H

FOH1

MEASI1H

FOH0

MEASI0H

MEASIL

MEASVH

GUARD(NC)

MEASVL

AV

CC_G

DGND

DV

DD

AM2

AM1

AM0

FSEL

STANDBY

NC = NO CONNECT

MSEL

CPSEL

AV

EE

AV

CC

AGND

EE_G

AV

NC

GUARD

GUARDIN

PIN FUNCTION DESCRIPTIONS

Pin No. Mnemonic Description

1 CPH Upper Comparator Threshold Voltage Input, CPH > CPL.

2 CPL Lower Comparator Threshold Voltage Input, CPL < CPH.

3, 18 DV

DD

Digital Supply Voltage.

4 CPOH Logic Output. When high, indicates MEASVOUT or MEASIOUT > CPH.

5 CPOL Logic Output. When high, indicates MEASVOUT or MEASIOUT < CPL.

6CPCK Logic Input. Used to initiate comparator sampling and update CPOH and CPOL.

7, 17 DGND Digital Ground.

8 CLHDETECT Logic Output. When high, indicates upper clamp active. For details, see the Clamp Function section.

9 CLLDETECT Logic Output. When high, indicates lower clamp active. For details, see the Clamp Function section.

10 QM4 Logic Output. When high, indicates current range Mode 4 is enabled. May be used to drive external

relay or switch. For details, see the High Current Ranges section.

11 QM5 Logic Output. When high, indicates current range Mode 5 is enabled. May be used to drive external

relay or switch. For details, see the High Current Ranges section.

12 MOE Active Low MEASOUT Enable.

13 CS Active Low Logic Input. The device is selected when this pin is low. For details, see the Interface

section.

14 STB Active Low Logic Input. Used in conjunction with CPCK and CS to configure the device for differ-

ent configurations. Rising edge of STB triggers sequence inputs. For details, see the Interface section.

15 AC0 Logic Input. Used in conjunction with AC1 to select one of three external compensation capacitors.

For details, see the Force Control Amplifier section.

16 AC1 Logic Input. Used in conjunction with AC0 to select one of three external compensation capacitors.

For details, see the Force Control Amplifier section.

REV. A–6–

Loading...

Loading...