Analog Devices AD5207BRU50-REEL7, AD5207BRU100-REEL7, AD5207BRU10-REEL7 Datasheet

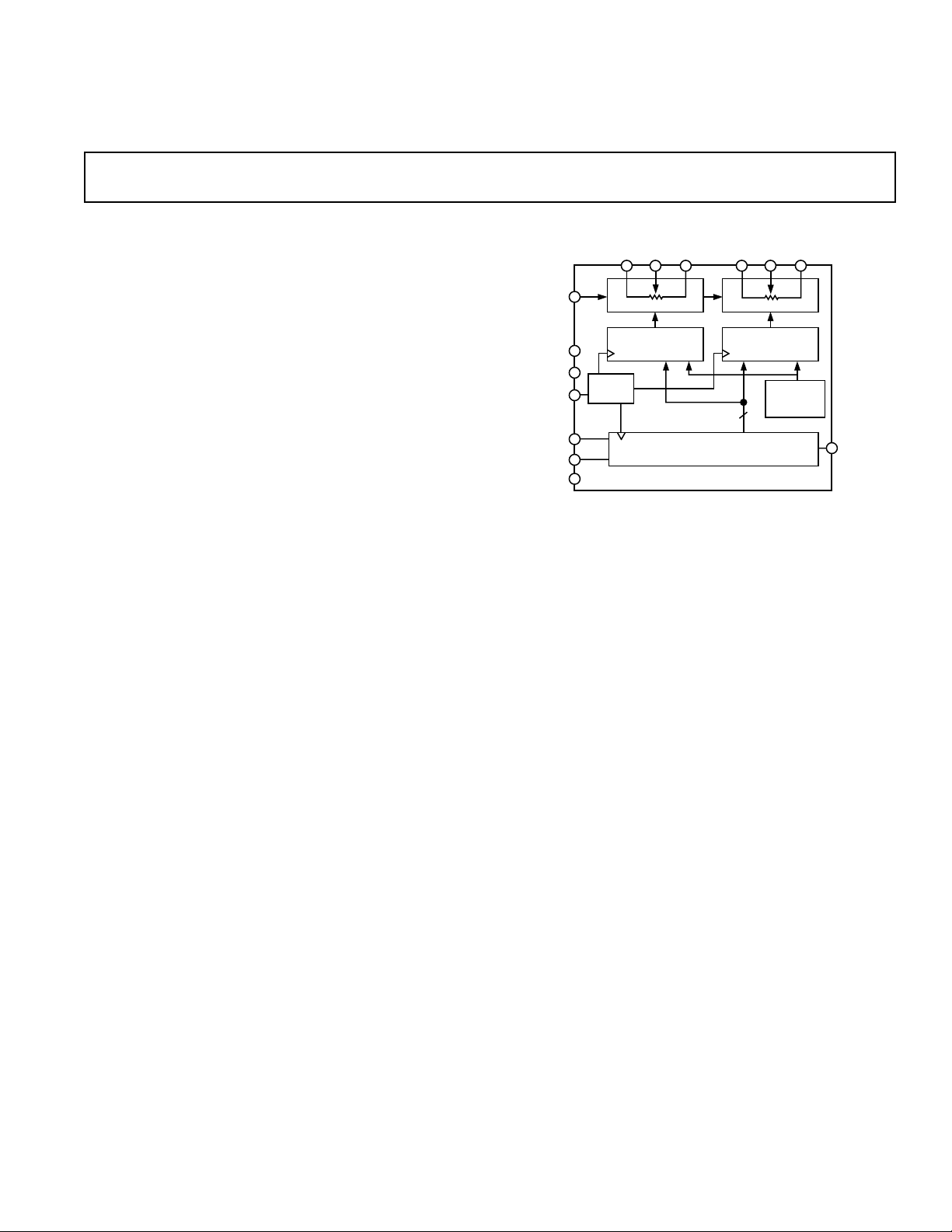

2-Channel, 256-Position

RDAC1 REGISTER

R

RDAC2 REGISTER

R

POWER-

ON

RESET

LOGIC

SERIAL INPUT REGISTER

AD5207

8

SDO

DGND

SDI

CS

V

SS

SHDN

V

DD

A1 W1 B1 A2 W2 B2

CLK

a

FEATURES

256-Position, 2-Channel

Potentiometer Replacement

10 k, 50 k, 100 k

Power Shut-Down, Less than 5 A

2.7 V to 5.5 V Single Supply

2.7 V Dual Supply

3-Wire SPI-Compatible Serial Data Input

Midscale Preset During Power-On

APPLICATIONS

Mechanical Potentiometer Replacement

Stereo Channel Audio Level Control

Instrumentation: Gain, Offset Adjustment

Programmable Voltage-to-Current Conversion

Programmable Filters, Delays, Time Constants

Line Impedance Matching

Automotive Electronics Adjustment

GENERAL DESCRIPTION

The AD5207 provides dual channel, 256-position, digitally

controlled variable resistor (VR) devices that perform the same

electronic adjustment function as a potentiometer or variable

resistor. Each channel of the AD5207 contains a fixed resistor with

a wiper contact that taps the fixed resistor value at a point

determined by a digital code loaded into the SPI-compatible

serial-input register. The resistance between the wiper and either

end point of the fixed resistor varies linearly with respect to the

digital code transferred into the VR latch. The variable resistor

offers a completely programmable value of resistance, between

the A Terminal and the wiper or the B Terminal and the wiper.

The fixed A-to-B terminal resistance of 10 kΩ, 50 kΩ or 100 kΩ

has a ±1% channel-to-channel matching tolerance with a nominal temperature coefficient of 500 ppm/°C. A unique switching

circuit minimizes the high glitch inherent in traditional switched

resistor designs and avoids any make-before-break or breakbefore-make operation.

Each VR has its own VR latch, which holds its programmed

resistance value. These VR latches are updated from an internal

serial-to-parallel shift register, which is loaded from a standard

3-wire serial-input digital interface. Ten bits, to make up the

data word, are required and clocked into the serial input register.

Digital Potentiometer

AD5207

FUNCTIONAL BLOCK DIAGRAM

The first two bits are address bits. The following eight bits are

the data bits that represent the 256 steps of the resistance value.

The reason for two address bits instead of one is to be compatible

with similar products such as AD8402 so that drop-in replacement

is possible. The address bit determines the corresponding VR

latch to be loaded with the data bits during the returned positive

edge of CS strobe. A serial data output pin at the opposite end

of the serial register allows simple daisy chaining in multiple

VR applications without additional external decoding logic.

An internal reset block will force the wiper to the midscale position during every power-up condition. The SHDN pin forces an

open circuit on the A Terminal and at the same time shorts the

wiper to the B Terminal, achieving a microwatt power shutdown

state. When SHDN is returned to logic high, the previous latch

settings put the wiper in the same resistance setting prior to

shutdown. The digital interface remains active during shutdown;

code changes can be made to produce new wiper positions when

the device is resumed from shutdown.

The AD5207 is available in 1.1 mm thin TSSOP-14 package,

which is suitable for PCMCIA applications. All parts are guaranteed to operate over the extended industrial temperature range

of –40°C to +125°C.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2001

AD5207–SPECIFICATIONS

(V

ELECTRICAL CHARACTERISTICS 10 k, 50 k, 100 k VERSION

= 5 V, V

DD

VB = 0, –40C < TA < +125C unless otherwise noted.)

Parameter Symbol Conditions Min Typ1Max Unit

DC CHARACTERISTICS

RHEOSTAT MODE

Specifications Apply to All VRs

Resistor Differential Nonlinearity

Resistor Nonlinearity

2

Nominal Resistor Tolerance

Resistance Temperature Coefficient R

Wiper Resistance R

Nominal Resistance Match ∆R/R

DC CHARACTERISTICS

POTENTIOMETER DIVIDER MODE

Specifications Apply to All VRs

Resolution N 8 Bits

Integral Nonlinearity

Differential Nonlinearity

4

4

Voltage Divider Temperature ∆V

Coefficient

Full-Scale Error V

Zero-Scale Error V

RESISTOR TERMINALS

Voltage Range

Capacitance

Capacitance

Shutdown Current

5

6

AX, B

6

W

X

X

7

Shutdown Wiper Resistance R

Common-Mode Leakage I

DIGITAL INPUTS AND OUTPUTS

Input Logic High V

Input Logic Low V

Input Logic High V

Input Logic Low V

Output Logic High V

Output Logic Low V

Input Current I

Input Capacitance

6

POWER SUPPLIES

Power Single-Supply Range V

Power Dual-Supply Range V

Positive Supply Current I

Negative Supply Current I

Power Dissipation

8

Power Supply Sensitivity, V

Power Supply Sensitivity, V

DYNAMIC CHARACTERISTICS

Bandwidth –3 dB BW_10 kΩ RAB = 10 kΩ 600 kHz

Bandwidth –3 dB BW_50 kΩ R

Bandwidth –3 dB BW_100 kΩ R

Total Harmonic Distortion THD

V

Settling Time t

W

Resistor Noise Voltage e

Crosstalk

10

3

DD

SS

2

R-DNL RWB, VA = NC –1 +1 LSB

R-INL RWB, VA = NC –1.5 +1.5 LSB

∆R –30 +30 %

/∆TV

AB

W

O

= VDD, Wiper = No Connect 500 ppm/°C

AB

IW = 1 V/R, VDD = 5 V 50 100 Ω

Ch 1 to 2, VAB = VDD, TA = 25°C 0.2 1 %

INL –1.5 +1.5 LSB

DNL VDD = 5 V, VSS = 0 V –1 +1 LSB

/∆T Code = 80

W

WFSE

WZSE

VA,

B, W

C

A,B

C

W

I

A_SD

W_SD

CM

IH

IL

IH

IL

OH

OL

IL

C

IL

DD RANGE

DD/SS RANGE

DD

SS

P

DISS

Code = FF

Code = 00

|VDD| + |VSS| ≤5.5 V V

f = 1 MHz, Measured to GND, Code = 80

f = 1 MHz, Measured to GND, Code = 80

VA = VDD, VB = 0 V, SHDN = 0 5 µA

VA = VDD, VB = 0 V, SHDN = 0, VDD = 5 V 200 Ω

VA = VB = VDD/2 1 nA

VDD = 5 V, VSS = 0 V 2.4 V

VDD = 5 V, VSS = 0 V 0.8 V

VDD = 3 V, VSS = 0 V 2.1 V

VDD = 3 V, VSS = 0 V 0.6 V

RL = 1 kΩ to V

IOL = 1.6 mA, VDD = 5 V 0.4 V

VIN = 0 V or 5 V ±10 µA

VSS = 0 V 2.7 5.5 V

VIH = VDD or VIL = GND, VSS = 0 V 40 µA

VIH = VDD or VIL = GND VSS = –2.5 V 40 µA

VIH = 5 V or VIL = 0 V, VDD = 5 V 0.2 mW

PSS ∆VDD = 5 V ± 10%, VSS = 0 V, Code = 80

PSS ∆VSS = –2.5 V ± 10%, VDD = 2.5 V, Code = 80

6, 9

AB

AB

VA = 1 V rms, VB = 0 V, f = 1 kHz, RAB = 10 kΩ 0.003 %

RAB = 10 kΩ/50 kΩ/100 kΩ, ± 1 LSB Error Band 2/9/18 µs

RWB = 5 kΩ, f = 1 kHz, RS = 0 9 nV√Hz

VA = 5 V, VB = 0 V –65 dB

S

N_WB

C

T

W

H

H

H

H

H

DD

–1.5 LSB

SS

VDD – 0.1 V

±2.2 ±2.7 V

H

H

= 50 kΩ 125 kHz

= 100 kΩ 71 kHz

= 0, VA = 5 V,

SS

15 ppm/°C

+1.5 LSB

V

DD

V

45 pF

70 pF

10 pF

0.01 %/%

0.03 %/%

–2–

REV. 0

AD5207

Parameter Symbol Conditions Min Typ

1

Max Unit

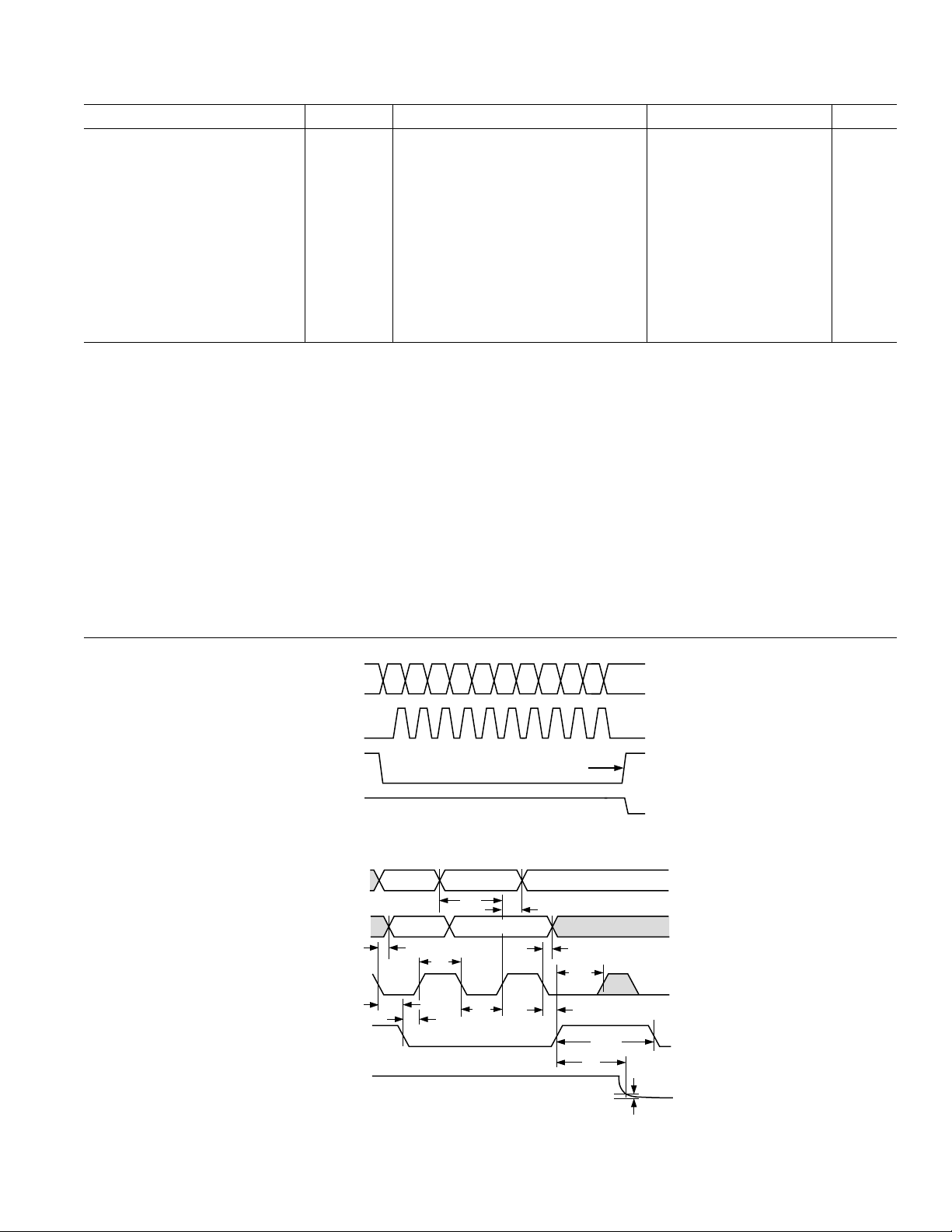

INTERFACE TIMING

CHARACTERISTICS

Applies to All Parts

Input Clock Pulsewidth tCH, t

Data Setup Time t

Data Hold Time t

CLK to SDO Propagation Delay

CS Setup Time t

CS High Pulsewidth t

CLK Fall to CS Fall Hold Time t

CLK Fall to CS Rise Hold Time t

CS Rise to Clock Rise Setup t

NOTES

1

Typicals represent average readings at 25°C and VDD = 5 V, VSS = 0 V.

2

Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper

positions. R-DNL measures the relative step change from ideal between successive tap positions. Parts are guaranteed monotonic. IW = VDD/R for both VDD = 5 V,

VSS = 0 V.

3

VAB = VDD, Wiper (VW) = No connect.

4

INL and DNL are measured at VW with the RDAC configured as a potentiometer divider similar to a voltage output D/A converter. V

specification limits of ± 1 LSB maximum are Guaranteed Monotonic operating conditions.

5

Resistor Terminals A, B, W have no limitations on polarity with respect to each other.

6

Guaranteed by design and not subject to production test.

7

Measured at the AX terminals. All AX terminals are open-circuited in shut-down mode.

8

P

is calculated from (IDD × VDD). CMOS logic level inputs result in minimum power dissipation.

DISS

9

All dynamic characteristics use VDD = 5 V, VSS = 0 V.

10

Measured at a VW pin where an adjacent VW pin is making a full-scale voltage change.

11

See timing diagram for location of measured values. All input control voltages are specified with tR = tF = 2 ns (10% to 90% of 3 V) and timed from a voltage level of

1.5 V. Switching characteristics are measured using VDD = 5 V.

12

Propagation delay depends on value of VDD, RL, and CL; see applications text.

The AD5207 contains 474 transistors. Die Size: 67 mil × 69 mil, 4623 sq. mil.

Specifications subject to change without notice.

6, 11

CL

DS

12

DH

t

PD

CSS

CSW

CSH0

CSH1

CS1

Clock Level High or Low 10 ns

5ns

5ns

RL = 1 kΩ to 5 V, CL < 20 pF 1 25 ns

10 ns

10 ns

0ns

0ns

10 ns

= VDD and VB = 0 V. DNL

A

SDI

CLK

CS

V

OUT

SDI

(DATA IN)

SDO

(DATA OUT)

CLK

CS

V

OUT

1

A1 A0 D7 D6 D5 D4 D3 D2 D1 D0

0

1

0

1

0

RDAC REGISTER LOAD

Figure 1a. Timing Diagram

1

Ax OR Dx Ax OR Dx

0

1

A'x OR D'x

0

1

0

1

t

CSS

0

V

DD

0V

t

CSH0

t

DS

t

DH

A'x OR D'x

t

CH

t

CL

t

PD_MAX

t

CS1

t

CSH1

t

CSW

t

S

ⴞ1LSB ERROR BAND

ⴞ1LSB

REV. 0

Figure 1b. Detail Timing Diagram

–3–

AD5207

ABSOLUTE MAXIMUM RATINGS

(TA = 25°C, unless otherwise noted)

1

VDD to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3, +7 V

V

to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0, –3 V

SS

to VSS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 V

V

DD

, VB, VW to GND . . . . . . . . . . . . . . . . . . . . . . . . . . VSS, V

V

A

2

I

(A, B, W) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±20 mA

MAX

Digital Inputs and Output Voltage to GND . . 0 V, V

DD

DD

+ 0.3 V

Operating Temperature Range . . . . . . . . . . –40°C to +125°C

Maximum Junction Temperature (T

Max) . . . . . . . . . . 150°C

J

Storage Temperature . . . . . . . . . . . . . . . . . . –65°C to +150°C

Lead Temperature (Soldering, 10 sec) . . . . . . . . . . . . . 300°C

Thermal Resistance

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2

Max current is bounded by the maximum current handling of the switches,

maximum power dissipation of the package, and maximum applied voltage

across any two of the A, B, and W Terminals at a given resistance. Please refer to

TPC 22 for detail.

3

Package Power Dissipation = (TJ Max–TA)/θJA.

3

θ

TSSOP-14 . . . . . . . . . . . . . 206°C/W

JA,

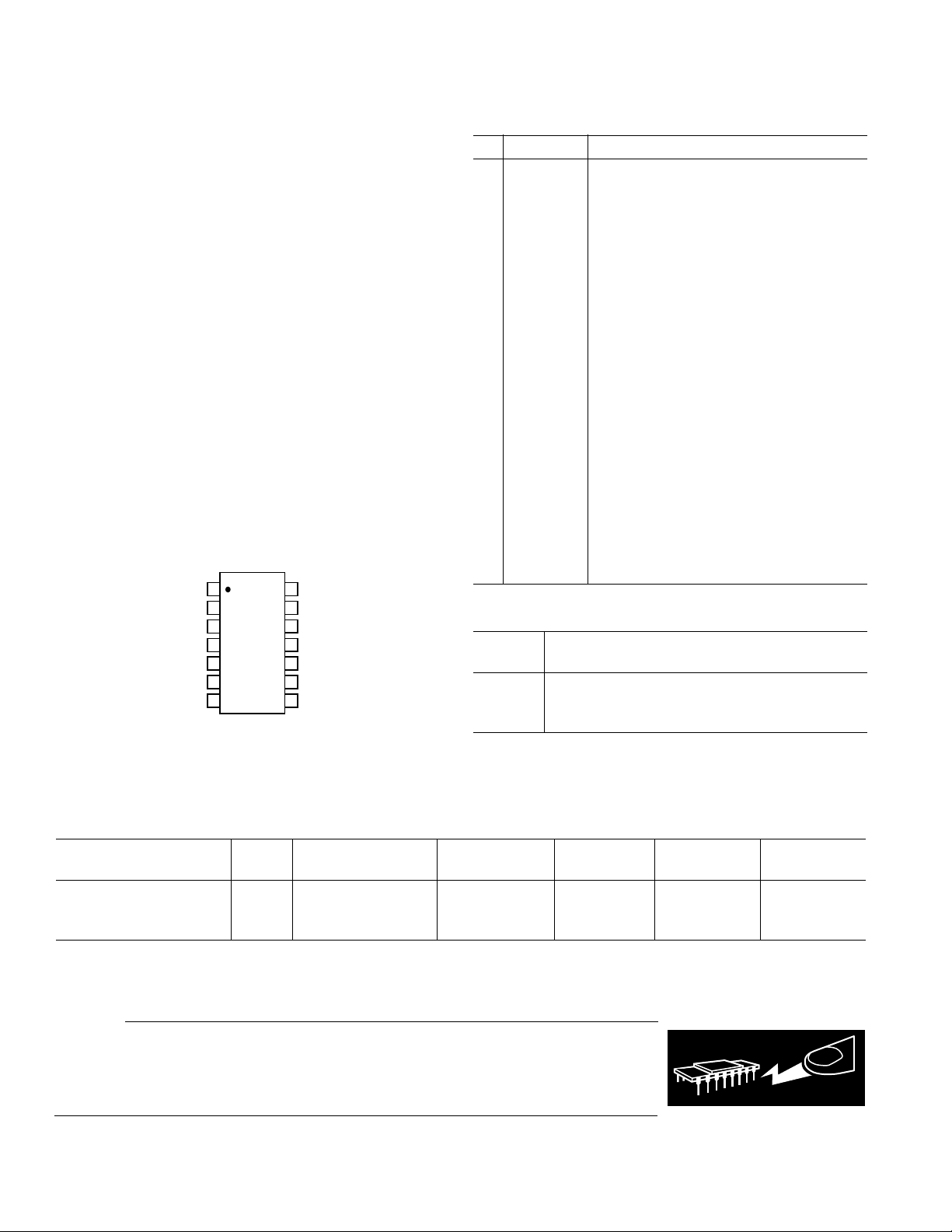

PIN CONFIGURATION

V

W2

DGND

SHDN

SS

B2

A2

CS

1

2

3

AD5207

4

TOP VIEW

(Not to Scale)

5

6

7

14

B1

13

A1

12

W1

11

V

DD

10

CLK

9

SDO

8

SDI

PIN FUNCTION DESCRIPTIONS

Pin Mnemonic Description

1V

SS

Negative Power Supply, specified for opera-

tion from 0 V to –2.7 V.

2 B2 Terminal B of RDAC#2.

3 A2 Terminal A of RDAC#2.

4 W2 Wiper, RDAC#2, addr = 1

2

5 DGND Digital Ground.

6 SHDN Active Low Input. Terminal A open-circuit

and Terminal B shorted to Wiper. Shut-

down controls both RDACs #1 and #2.

7 CS Chip Select Input, Active Low. When CS

returns high, data in the serial input register

is decoded, based on the address bit, and

loaded into the corresponding RDAC register.

8 SDI Serial Data Input. MSB is loaded first.

9 SDO Serial Data Output. Open Drain transistor

requires pull-up resistor.

10 CLK Serial Clock Input. Positive Edge Triggered.

11 V

DD

Positive Power Supply. Specified for opera-

tion at 2.7 V to 5.5 V.

12 W1 Wiper, RDAC #1, addr = 0

.

2

13 A1 Terminal A of RDAC #1.

14 B1 Terminal B of RDAC #1.

Table I. Serial-Data Word Format

ADDR DATA

B9 B8 B7 B6 B5 B4 B3 B2 B1 B0

A1 A0 D7 D6 D5 D4 D3 D2 D1 D0

9

2

NOTES

ADDR(RDAC1) = 00; ADDR(RDAC2 = 01).

Data loads B9 first into SDI pin.

MSB LSB

8

2

7

2

0

2

ORDERING GUIDE

Temperature Package Package Qty Per Branding

Model k Range Description Option Container Information*

AD5207BRU10-REEL7 10 –40°C to +125°C TSSOP-14 RU-14 1,000 B10

AD5207BRU50-REEL7 50 –40°C to +125°C TSSOP-14 RU-14 1,000 B50

AD5207BRU100-REEL7 100 –40°C to +125°C TSSOP-14 RU-14 1,000 B100

*Three lines of information appear on the device. Line 1 lists the part number; Line 2 includes branding information and the ADI logo, and Line 3 contains the

date code YYWW.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

WARNING!

the AD5207 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

–4–

ESD SENSITIVE DEVICE

REV. 0

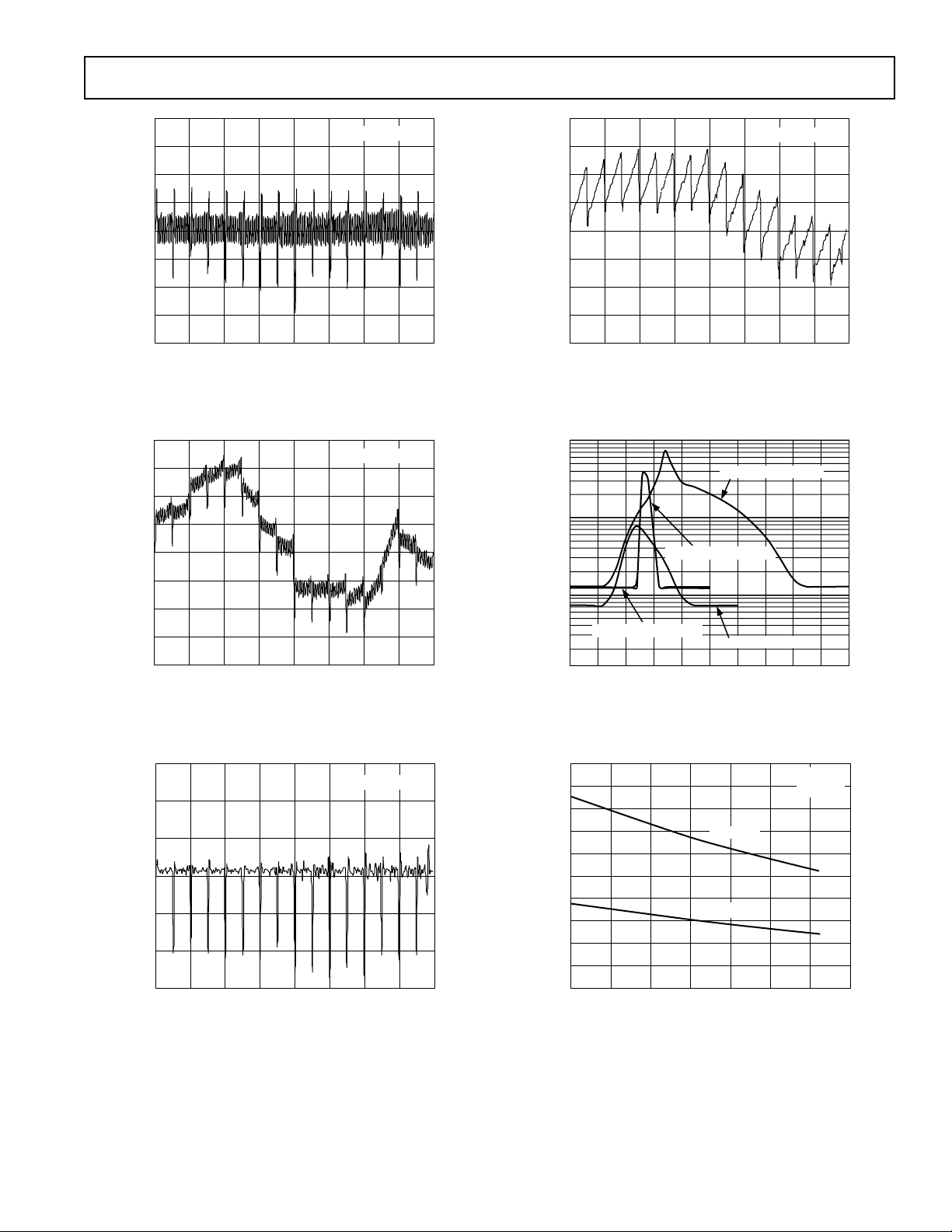

Typical Performance Characteristics–AD5207

CODE – Decimal

INL – LSB

224

–0.2

–0.1

0.0

0.1

0.3

1921601289664320 256

–0.3

0.2

–0.4

0.4

VDD = 5.5V, VSS = 0V

TEMPERATURE – C

I

DD

SUPPLY CURRENT – A

20

–40

V

IL

= V

SS

V

IH

= V

DD

18

16

14

12

10

8

6

4

2

0

–20 0 20 40 60 80 100

VDD = 5.5V

VDD = 2.7V

0.20

0.15

0.10

0.05

0.00

RDNL – LSB

0.05

0.10

0.15

0.20

0.20

0.15

0.10

0.05

0.00

RINL – LSB

–0.05

–0.10

–0.15

–0.20

VDD = 5.5V, VSS = 0V

CODE – Decimal

1921601289664320 256

TPC 1. 10 kΩ RDNL vs. Code

VDD = 5.5V, VSS = 0V

CODE – Decimal

1921601289664320 256

TPC 2. 10 kΩ RINL vs. Code

224

224

TPC 4. 10 kΩ INL vs. Code

1.0

IDD @ VDD/VSS = 5V/0V

0.1

– mA

SS

/I

DD

I

0.001

0.01

ISS @ VDD/VSS = 2.5V

IDD @ VDD/VSS = 2.5V

IDD @ VDD/VSS = 3V/0V

VIH – V

TPC 5. Supply Current vs. Logic Input Voltage

5.04.03.02.01.00.0

0.3

0.2

0.1

0.0

DNL – LSB

–0.1

–0.2

REV. 0

–0.3

TPC 3. 10 kΩ DNL vs. Code

CODE – Decimal

VDD = 5.5V, VSS = 0V

224

1921601289664320 256

TPC 6. Supply Current vs. Temperature

–5–

Loading...

Loading...