Analog Devices AD1887 Datasheet

a

ID0 ID1

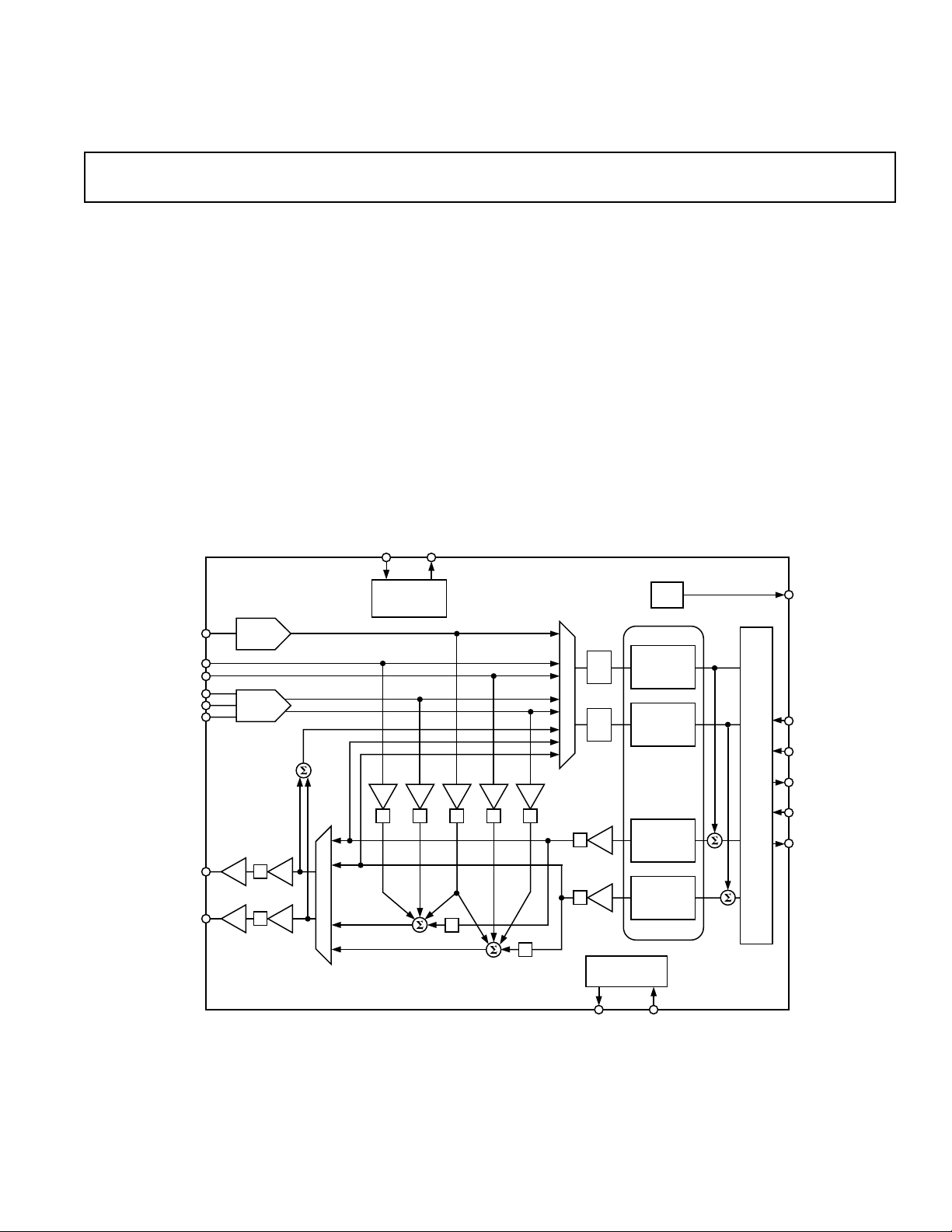

AC’97 SoundMAX® Codec

AD1887

AC’97 2.1 FEATURES

Variable Sample Rate Audio

AC’97 FEATURES

AC’97 2.2 Compliant

Greater than 90 dB Dynamic Range

Integrated Stereo Headphone Amplifier

Multibit ⌺-⌬ Converter Architecture for Improved S/N

Ratio Greater than 90 dB

16-Bit Stereo Full-Duplex Codec

Two Analog Line-Level Stereo Inputs for:

LINE-IN and CD

Mono MIC Input with Built-In Programmable Preamp

High-Quality CD Input with Ground Sense

Power Management Support

48-Terminal TQFP Package

FUNCTIONAL BLOCK DIAGRAM

MIC

LINE_IN

AD1887

MIC

PREAMP

CHIP SELECT

ENHANCED FEATURES

Full Duplex Variable Sample Rates from 7040 Hz to

48 kHz with 1 Hz Resolution

Software-Enabled V

Output for Microphones and

REFOUT

External Power Amp

Split Power Supplies (3.3 V Digital/5 V Analog)

Mobile Low-Power Mixer Mode

Extended 6-Bit Headphone Volume Control

Digital Audio Mixer Mode

PGA

V

REF

16-BIT

⌺-⌬ A/D

CONVERTER

V

REFOUT

CD

GA

GA

GA

M

M

M

GA

M

HP_OUT_L

HP_OUT_R

SoundMAX is a registered trademark of Analog Devices, Inc.

HP

HP

GA

M

SELECTOR

G = GAIN

A = ATTENUATE

M = MUTE

M

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

SELECTOR

PGA

GA

GA

M

M

GA

M

GA

M

M

OSCILLATOR

XTL_OUT XTL_IN

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2001

16-BIT

⌺-⌬ A/D

CONVERTER

SAMPLE

RATE

GENERATORS

16-BIT

⌺-⌬ A/D

CONVERTER

16-BIT

⌺-⌬ A/D

CONVERTER

AC

LINK

RESET

SYNC

BIT_CLK

SDATA_OUT

SDATA_IN

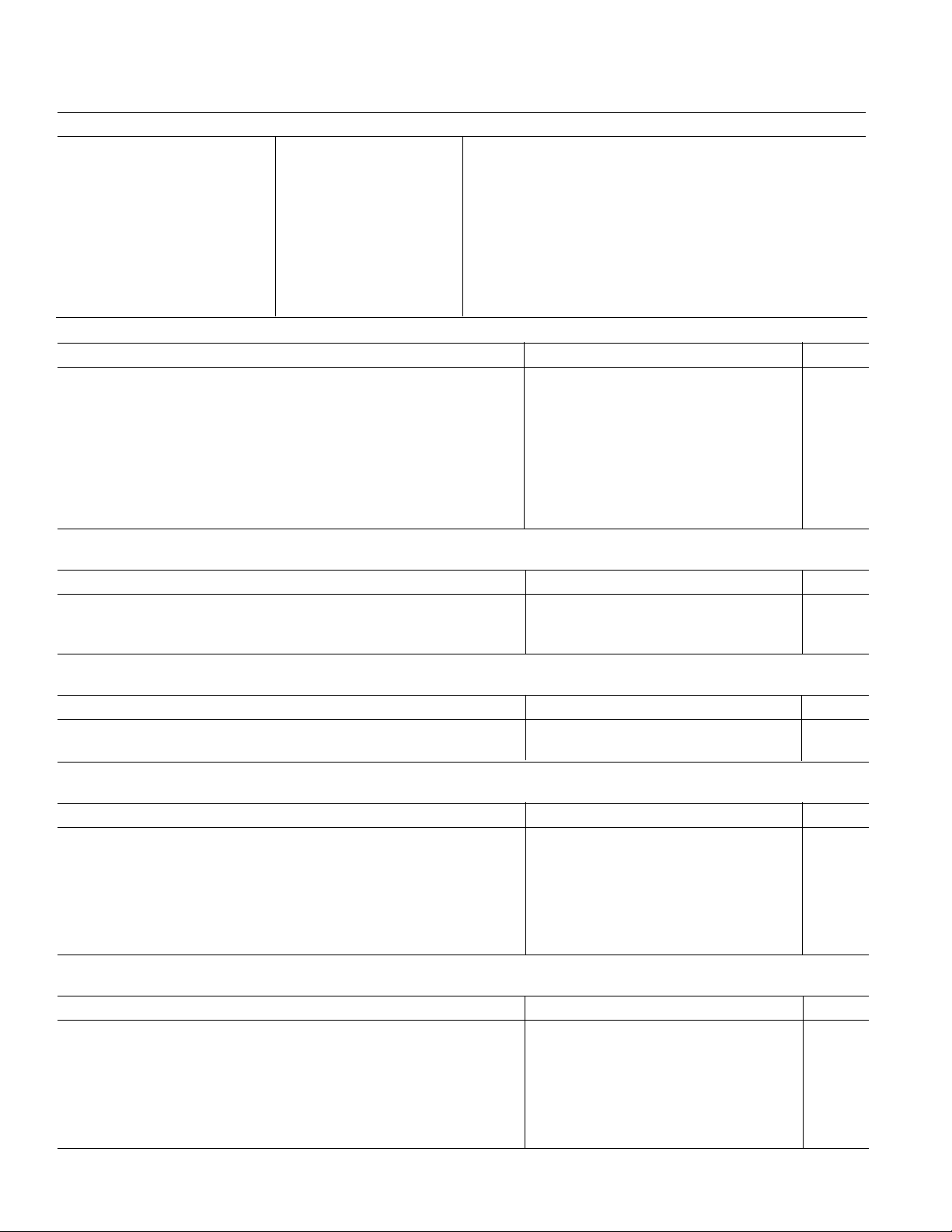

AD1887–SPECIFICATIONS

STANDARD TEST CONDITIONS UNLESS OTHERWISE NOTED

Temperature 25°C

Digital Supply (V

Analog Supply (V

Sample Rate (

) 3.3 V

DD

) 5.0 V

CC

fS) 48 kHz

Input Signal 1008 Hz

Analog Output Pass Band 20 Hz to 20 kHz

V

IH

V

IL

V

(CS0, CS1) 4.0 V

IH

V

IL

ANALOG INPUT

2.0 V

0.8 V

1.0 V

Parameter Min Typ Max Unit

Input Voltage (RMS Values Assume Sine Wave Input)

LINE_IN, CD 1V rms

MIC with 20 dB Gain 0.1 V rms

MIC with 0 dB Gain 1V rms

Input Impedance

Input Capacitance

*

*

DAC Test Conditions

Calibrated

–3 dB Attenuation Relative to Full Scale

Input 0 dB

32 Ω Output Load (HP_OUT)

ADC Test Conditions

Calibrated

0 dB Gain

Input –3.0 dB Relative to Full Scale

2.83 V p-p

0.283 V p-p

2.83 V p-p

20 kΩ

5 7.5 pF

HEADPHONE OUT VOLUME

Parameter Min Typ Max Unit

Step Size (+6 dB to –88.5 dB); HP_OUT_R, HP_OUT_L 1.5 dB

Output Attenuation Range Span

Mute Attenuation of 0 dB Fundamental

PROGRAMMABLE GAIN AMPLIFIER—ADC

*

*

–94.5 dB

80 dB

Parameter Min Typ Max Unit

Step Size (0 dB to 22.5 dB) 1.5 dB

PGA Gain Range Span 22.5 dB

ANALOG MIXER—INPUT GAIN/AMPLIFIERS/ATTENUATORS

Parameter Min Typ Max Unit

Signal-to-Noise Ratio (SNR)

CD to HP_OUT 90 dB

Other to HP_OUT 90 dB

Step Size (+12 dB to –34.5 dB): (All Steps Tested)

MIC, LINE_IN, CD, DAC 1.5 dB

Input Gain/Attenuation Range:

MIC, LINE_IN, CD, DAC –46.5 dB

DIGITAL DECIMATION AND INTERPOLATION FILTERS*

Parameter Min Typ Max Unit

Pass Band 0 0.4 ×

f

Hz

S

Pass-Band Ripple ± 0.09 dB

Transition Band 0.4 ×

Stop Band 0.6 ×

f

S

f

S

0.6 ×

f

Hz

S

∞ Hz

Stop-Band Rejection –74 dB

Group Delay 12/

f

S

sec

Group Delay Variation over Pass Band 0.0 µs

*Guaranteed but not tested.

–2–

REV. 0

AD1887

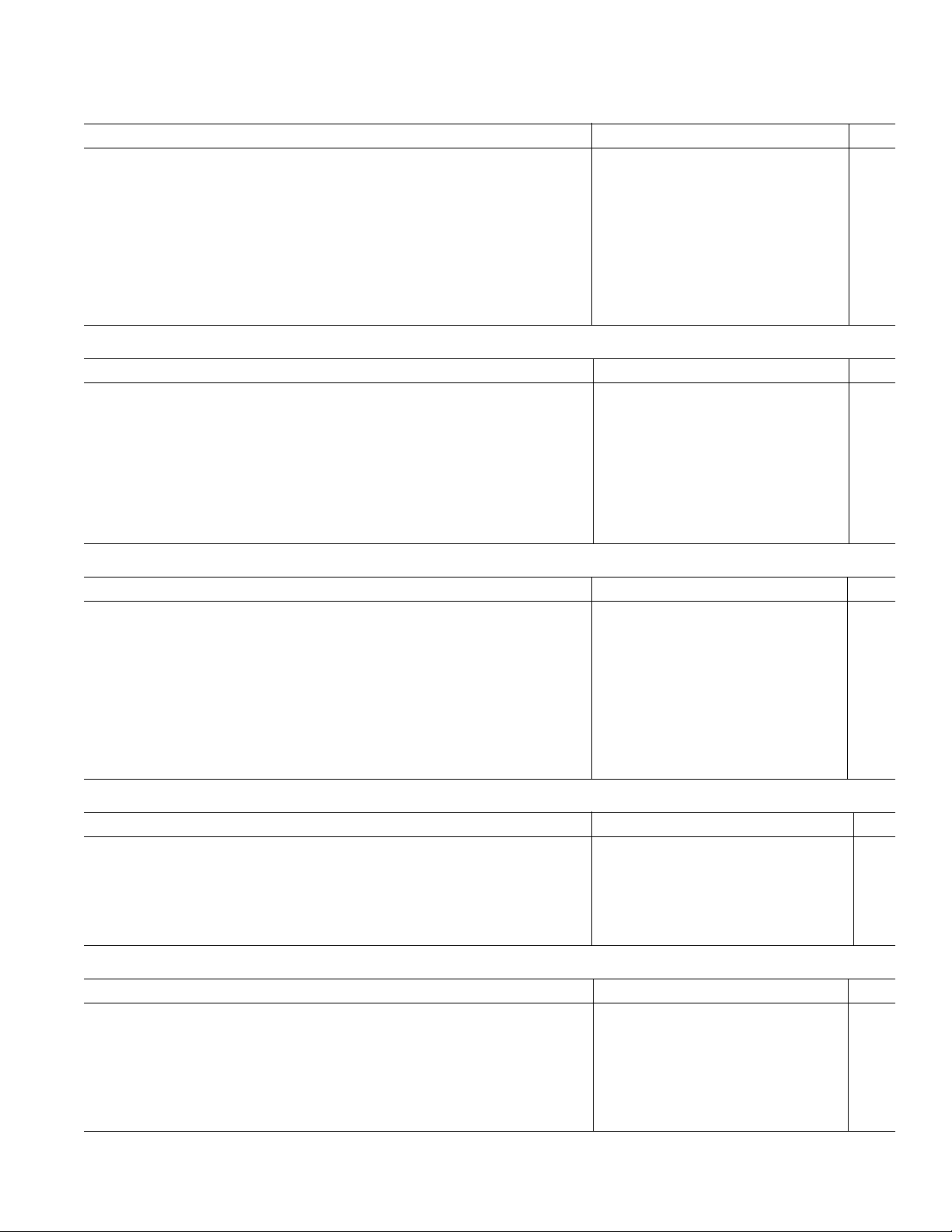

ANALOG-TO-DIGITAL CONVERTERS

Parameter Min Typ Max Unit

Resolution 16 Bits

Total Harmonic Distortion (THD) –84 dB

Dynamic Range (–60 dB Input THD + N Referenced to Full Scale, A-Weighted) 84 87 dB

*

Signal-to-Intermodulation Distortion

ADC Crosstalk

*

Line Inputs (Input L, Ground R, Read R; Input R, Ground L, Read L) –100 –90 dB

LINE_IN to Other –90 –85 dB

Gain Error (Full-Scale Span Relative to Nominal Input Voltage) ± 10 %

Interchannel Gain Mismatch (Difference of Gain Errors) ± 0.5 dB

ADC Offset Error ± 5mV

DIGITAL-TO-ANALOG CONVERTERS

Parameter Min Typ Max Unit

Resolution 16 Bits

Total Harmonic Distortion (THD) HP_OUT –75 dB

Dynamic Range (–60 dB Input THD + N Referenced to Full Scale, A-Weighted) 85 90 dB

Signal-to-Intermodulation Distortion

Gain Error (Full-Scale Span Relative to Nominal Input Voltage) ± 10 %

Interchannel Gain Mismatch (Difference of Gain Errors) ± 0.7 dB

*

DAC Crosstalk

(Input L, Zero R, Measure R_OUT; Input R, Zero L, –80 dB

Measure L_OUT)

Total Audible Out-of-Band Energy (Measured from 0.6 ×

(CCIF Method) 85 dB

*

(CCIF Method) –100 dB

fS to 20 kHz)

*

–40 dB

ANALOG OUTPUT

Parameter Min Typ Max Unit

Full-Scale Output Voltage; HP_OUT 1 V rms

2.83 V p-p

Output Impedance

*

External Load Impedance

Output Capacitance

*

*

32 Ω

800 Ω

15 pF

External Load Capacitance 100 pF

V

REF

V

REF_OUT

V

REF_OUT

Current Drive 5mA

2.05 2.25 2.45 V

2.25 V

Mute Click (Muted Output Minus Unmuted Midscale DAC Output) ± 5mV

STATIC DIGITAL SPECIFICATIONS

Parameter Min Typ Max Unit

High-Level Input Voltage (V

Low-Level Input Voltage (V

High-Level Output Voltage (V

Low-Level Output Voltage (V

IH

) 0.35 × DVDDV

IL

OH

OL

): Digital Inputs 0.65 × DV

), IOH = 2 mA 0.9 × DV

DD

DD

), IOL = 2 mA 0.1 × DV

DD

V

V

V

Input Leakage Current –10 +10 µA

Output Leakage Current –10 +10 µA

POWER SUPPLY

Parameter Min Typ Max Unit

Power Supply Range—Analog (AV

Power Supply Range—Digital (DV

) 4.75 5.25 V

DD

) 3.15 3.45 V

DD

Power Dissipation—5 V/3.3 V 253 mW

Analog Supply Current—5 V (AV

Digital Supply Current—3.3 V (DV

Power Supply Rejection (100 mV p-p Signal @ 1 kHz)

)36mA

DD

)22mA

DD

*

40 dB

(At Both Analog and Digital Supply Pins, Both ADCs and DACs)

*Guaranteed but not tested.

REV. 0

–3–

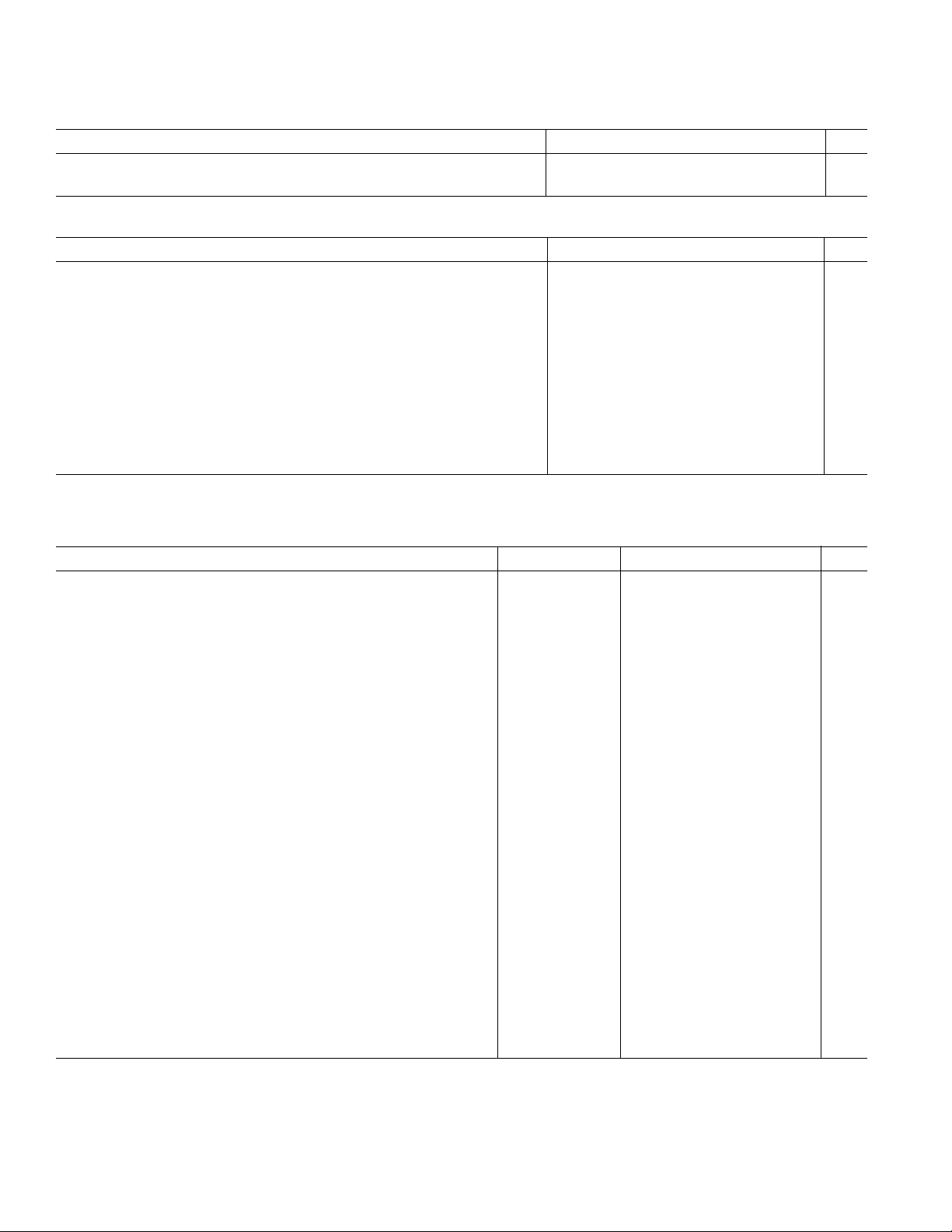

AD1887–SPECIFICATIONS

CLOCK SPECIFICATIONS*

Parameter Min Typ Max Unit

Input Clock Frequency 24.576 MHz

Recommended Clock Duty Cycle 40 50 60 %

POWER-DOWN STATES

Parameter Set Bits DVDD Typ AVDD Typ Unit

ADC PR0 15.82 30.0 mA

DAC PR1 15.08 26.3 mA

ADC + DAC PR1, PR0 3.79 19.9 mA

ADC + DAC + Mixer (Analog CD On) LPMIX, PR1, PR0 3.85 18.1 mA

Mixer PR2 17.65 17.4 mA

ADC + Mixer PR2, PR0 15.70 11.1 mA

DAC + Mixer PR2, PR1 15.07 8.3 mA

ADC + DAC + Mixer PR2, PR1, PR0 3.80 2.1 mA

Analog CD Only (AC-Link On) LPMIX, PR5, PR1, PR0 3.85 18.1 mA

Analog CD Only (AC-Link Off) LPMIX, PR1, PR0, PR4, PR5 0.06 18.1 mA

Standby PR5, PR4, PR3, PR2, PR1, PR0 0.06 0 mA

Headphone Standby PR6 17.66 26.1 mA

*Guaranteed but not tested.

Specifications subject to change without notice.

TIMING PARAMETERS (GUARANTEED OVER OPERATING TEMPERATURE RANGE)

Parameter Symbol Min Typ Max Unit

RESET Active Low Pulsewidth t

RESET Inactive to BIT_CLK Startup Delay t

SYNC Active High Pulsewidth t

SYNC Low Pulsewidth t

SYNC Inactive to BIT_CLK Startup Delay t

RST_LOW

RST2CLK

SYNC_HIGH

SYNC_LOW

SYNC2CLK

162.8 ns

162.8 ns

1.0 µs

1.3 µs

19.5 µs

BIT_CLK Frequency 12.288 MHz

BIT_CLK Period t

CLK_PERIOD

81.4 ns

BIT_CLK Output Jitter* 750 ps

BIT_CLK High Pulsewidth t

BIT_CLK Low Pulsewidth t

CLK_HIGH

CLK_LOW

32.56 42 48.84 ns

32.56 38 48.84 ns

SYNC Frequency 48.0 kHz

SYNC Period t

Setup to Falling Edge of BIT_CLK t

Hold from Falling Edge of BIT_CLK t

BIT_CLK Rise Time t

BIT_CLK Fall Time t

SYNC Rise Time t

SYNC Fall Time t

SDATA_IN Rise Time t

SDATA_IN Fall Time t

SDATA_OUT Rise Time t

SDATA_OUT Fall Time t

End of Slot 2 to BIT_CLK, SDATA_IN Low t

Setup to Trailing Edge of RESET (Applies to SYNC, SDATA_OUT) t

Rising Edge of RESET to HI-Z Delay t

SYNC_PERIOD

SETUP

HOLD

RISECLK

FALLCLK

RISESYNC

FALLSYNC

RISEDIN

FALLDIN

RISEDOUT

FALLDOUT

S2_PDOWN

SETUP2RST

OFF

5 2.5 ns

5ns

246 ns

246 ns

246 ns

246 ns

246 ns

246 ns

246 ns

246 ns

0 1.0 µs

15 ns

20.8 µs

25 ns

Propagation Delay 15 ns

RESET Rise Time 50 ns

Output Valid Delay from Rising Edge of BIT_CLK to SDI Valid 15 ns

*Output jitter is directly dependent on crystal input jitter.

Specifications subject to change without notice.

–4–

REV. 0

AD1887

RESET

BIT_CLK

SYNC

BIT_CLK

BIT_CLK

SYNC

t

RST_LOW

t

RST2CLK

Figure 1. Cold Reset

t

SYNC_HIGH

t

RST2CLK

Figure 2. Warm Reset

t

CLK_LOW

t

CLK_HIGH

t

CLK_PERIOD

t

SYNC_LOW

t

SYNC_HIGH

t

SYNC_PERIOD

BIT_CLK

t

RISECLK

SYNC

t

RISESYNC

SDATA_IN

t

RISEDIN

SDATA_OUT

t

RISEDOUT

Figure 5. Signal Rise and Fall Time

SLOT 2

SYNC

BIT_CLK

SDATA_OUT

SDATA_IN

SLOT 1

WRITE

TO 0x26

NOTE: BIT_CLK NOT TO SCALE

DATA

PR4

DON’T

CARE

t

FALLCLK

t

FALLSYNC

t

FALLDIN

t

FALLDOUT

t

S2_PDOWN

BIT_CLK

SYNC

SDATA_OUT

Figure 3. Clock Timing

t

SETUP

t

HOLD

Figure 4. Data Setup and Hold

Figure 6. AC Link Low Power Mode Timing

RESET

SDATA_OUT

SDATA_IN, BIT_CLK

t

OFF

t

SETUP2RST

HI-Z

Figure 7. ATE Test Mode

REV. 0

–5–

Loading...

Loading...