Analog Devices AD1881A Datasheet

a

AC’97 SoundMAX® Codec

AD1881A

AC’97 2.1 FEATURES

Variable Sample Rate

True Line-Level Output

Supports Secondary Codec Modes

AC’97 FEATURES

Designed for AC’97 Analog I/O Component

48-Lead LQFP Package

Multibit ⌺⌬ Converter Architecture for Improved

S/N Ratio Greater than 90 dB

ENHANCED FEATURES

Mobile Low Power Mixer Mode

Digital Audio Mixer Mode

Full Duplex Variable 8 kHz to 48 kHz Sampling Rate

PHAT™ Stereo 3D Stereo Enhancement

Split Power Supplies (3.3 V Digital/5 V Analog)

Extended 6-Bit Master Volume Control

Audio Amp Power-Down Signal

16-Bit Stereo Full-Duplex Codec

Four Analog Line-Level Stereo Inputs for Connection

from LINE, CD, VIDEO, and AUX

Two Analog Line-Level Mono Inputs for Speakerphone

and PC BEEP

Mono MIC Input Switchable from Two External

Sources

High Quality CD Input with Ground Sense

Stereo Line-Level Output

Mono Output for Speakerphone or Internal Speaker

Power Management Support

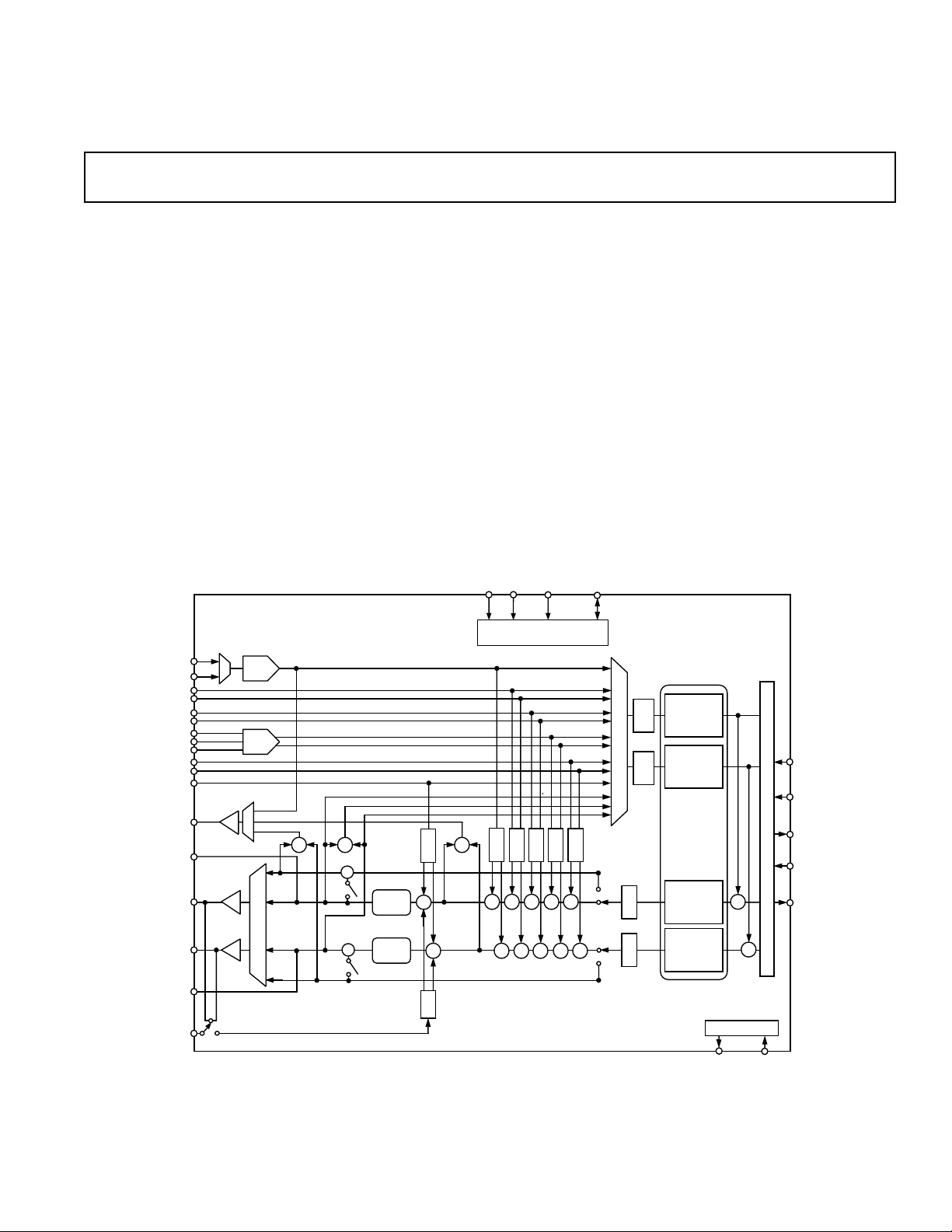

FUNCTIONAL BLOCK DIAGRAM

CS1

CS0

MIC1

MIC2

LINE_IN

AUX

CD

VIDEO

PHONE_IN

MONO_OUT

LNLVL_OUT_L

LINE_OUT_L

LINE_OUT_R

LNLVL_OUT_R

PC_BEEP

AD1881A

0dB/

20dB

MV

⌺

⌺

⌺

MV

D

A

M

MV

POP

POP

STEREO

⌺

STEREO

PHAT

PHAT

G

A

M

⌺

⌺

A

M

MODE/SYNCHRONIZER

G

A

⌺

M

⌺ ⌺ ⌺

⌺ ⌺ ⌺ ⌺

G = GAIN

A = ATTENUATE

M = MUTE

MV = MASTER VOLUME

NC = NO CONNECT

G

A

M

SoundMAX is a registered trademark and PHAT is a trademark of Analog Device, Inc.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2000

with 1 Hz Resolution

⌺

⌺

EAPD

G

A

M

MODE

PGA

SELECTOR

PGA

G

G

A

A

M

M

G

⌺

⌺

A

M

NC

G

NC

A

M

16-BIT

⌺⌬ A/D

CONVERTER

16-BIT

⌺⌬ A/D

CONVERTER

SAMPLE

RATE

GENERATORS

16-BIT

⌺⌬ D/A

CONVERTER

16-BIT

⌺⌬ D/A

CONVERTER

XTL_OUT

⌺

⌺

OSCILLATORS

XTL_IN

RESET

SYNC

BIT_CLK

AC LINK

SDATA_OUT

SDATA_IN

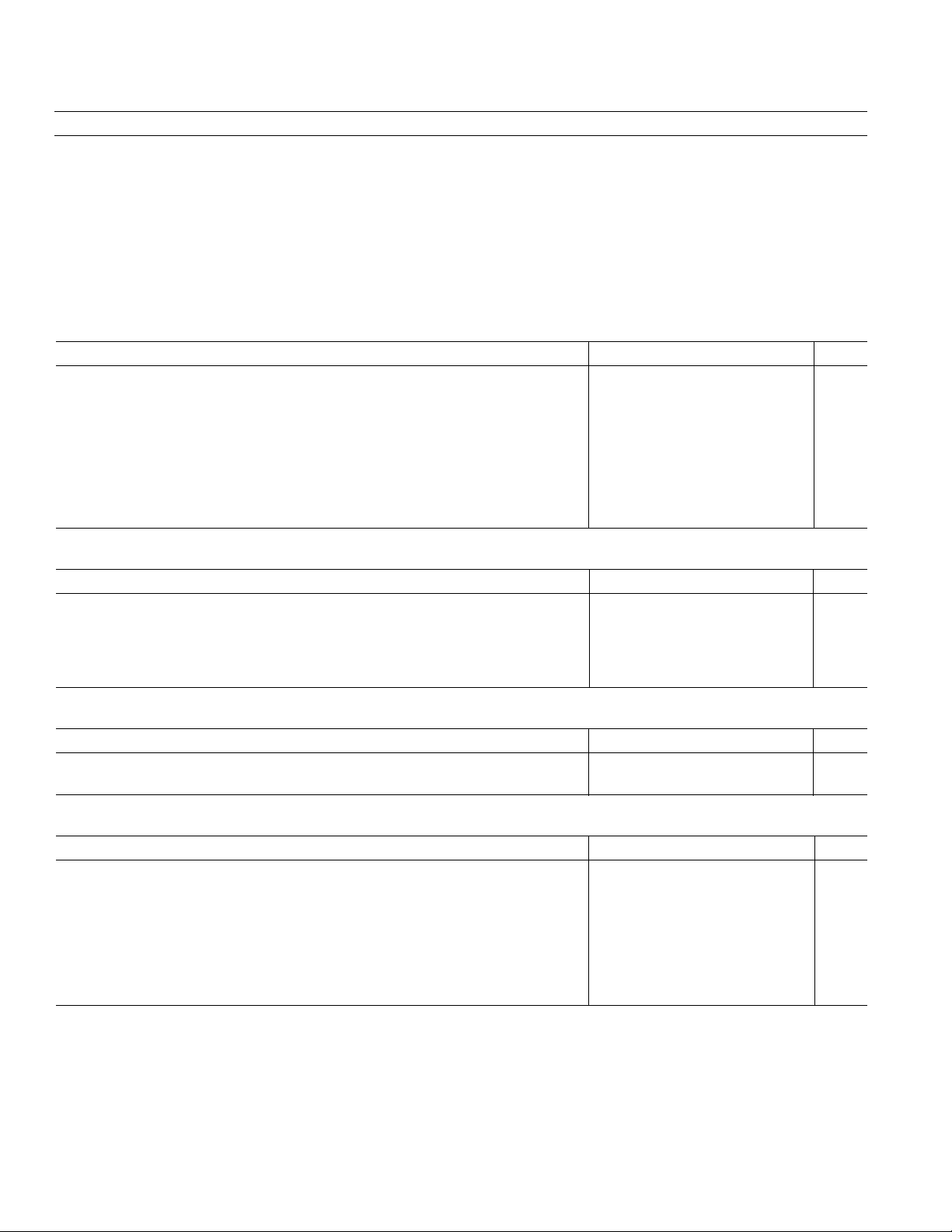

AD1881A–SPECIFICATIONS

STANDARD TEST CONDITIONS UNLESS OTHERWISE NOTED

Temperature 25 °C

Digital Supply (V

Analog Supply (V

Sample Rate (F

) 3.3 V

DD

) 5.0 V

CC

) 48 kHz

S

Input Signal 1008 Hz

ANALOG INPUT

Parameter Min Typ Max Unit

Input Voltage (RMS Values Assume Sine Wave Input)

LINE_IN, AUX, CD, VIDEO, PHONE_IN, PC_BEEP 1 V rms

MIC with +20 dB Gain (M20 = 1) 0.1 V rms

MIC with 0 dB Gain (M20 = 0) 1 V rms

Input Impedance* 20 kΩ

Input Capacitance* 5 7.5 pF

DAC Test Conditions

Calibrated

–3 dB Attenuation Relative to Full-Scale

Input 0 dB

10 kΩ Output Load

ADC Test Conditions

Calibrated

0 dB Gain

Input –3.0 dB Relative to Full-Scale

2.83 V p-p

0.283 V p-p

2.83 V p-p

MASTER VOLUME

Parameter Min Typ Max Unit

Step Size (0 dB to –94.5 dB); LINE_OUT_L, LINE_OUT_R 1.5 dB

Output Attenuation Range Span* –94.5 dB

Step Size (0 dB to –46.5 dB); MONO_OUT 1.5 dB

Output Attenuation Range Span* –46.5 dB

Mute Attenuation of 0 dB Fundamental* 80 dB

PROGRAMMABLE GAIN AMPLIFIER—ADC

Parameter Min Typ Max Unit

Step Size (0 dB to 22.5 dB) 1.5 dB

PGA Gain Range Span 22.5 dB

ANALOG MIXER—INPUT GAIN/AMPLIFIERS/ATTENUATORS

Parameter Min Typ Max Unit

Signal-to-Noise Ratio (SNR)

CD to LINE_OUT 90 dB

Other to LINE_OUT 90 dB

Step Size (+12 dB to –34.5 dB): (All Steps Tested)

MIC, LINE_IN, AUX, CD, VIDEO, PHONE_IN, DAC 1.5 dB

Input Gain/Attenuation Range: MIC, LINE, AUX, CD, VIDEO, PHONE_IN, DAC –46.5 dB

Step Size (0 dB to –45 dB): (All Steps Tested) PC_BEEP 3.0 dB

Input Gain/Attenuation Range: PC_BEEP –45 dB

*Guaranteed, not tested.

Specifications subject to change without notice.

–2–

REV. 0

AD1881A

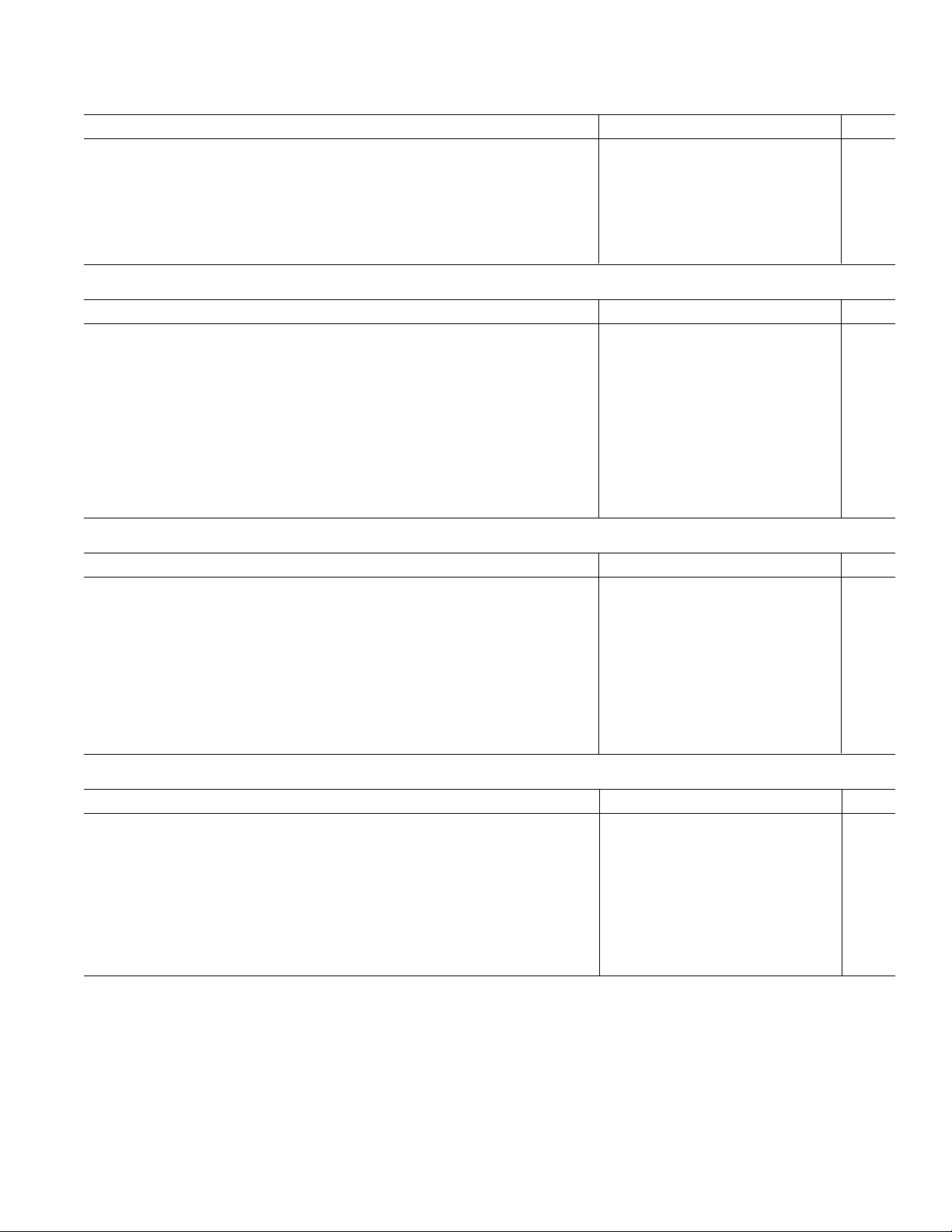

DIGITAL DECIMATION AND INTERPOLATION FILTERS*

Parameter Min Typ Max Unit

Passband 0 0.4 × F

Passband Ripple ± 0.09 dB

Transition Band 0.4 × F

Stopband 0.6 × F

S

S

0.6 × FSHz

∞

Stopband Rejection –74 dB

Group Delay 12/F

Group Delay Variation Over Passband 0.0 µs

ANALOG-TO-DIGITAL CONVERTERS

Parameter Min Typ Max Unit

Resolution 16 Bits

Total Harmonic Distortion (THD) 0.02 %

–74 dB

Dynamic Range (–60 dB Input THD+N Referenced to Full Scale, A-Weighted) 87 dB

Signal-to-Intermodulation Distortion* (CCIF Method) 85 dB

ADC Crosstalk*

Line Inputs (Input L, Ground R, Read R; Input R, Ground L, Read L) –100 –90 dB

LINE_IN to Other –90 –85 dB

Gain Error (Full-Scale Span Relative to Nominal Input Voltage) ± 10 %

Interchannel Gain Mismatch (Difference of Gain Errors) ± 0.5 dB

ADC Offset Error ± 10.5 mV

Hz

S

Hz

sec

S

DIGITAL-TO-ANALOG CONVERTERS

Parameter Min Typ Max Unit

Resolution 16 Bits

Total Harmonic Distortion (THD) LINE_OUT, LNLVL_OUT 0.02 %

–74 dB

Dynamic Range (–60 dB Input THD+N Referenced to Full Scale, A-Weighted) 90 dB

Signal-to-Intermodulation Distortion* (CCIF Method) 85 dB

Gain Error (Full-Scale Span Relative to Nominal Input Voltage) ± 10 %

Interchannel Gain Mismatch (Difference of Gain Errors) ± 0.7 dB

DAC Crosstalk* (Input L, Zero R, Measure R_OUT; Input R, Zero L, –80 dB

Measure L_OUT)

Total Audible Out-of-Band Energy (Measured from 0.6 × FS to 20 kHz)* –40 dB

ANALOG OUTPUT

Parameter Min Typ Max Unit

Full-Scale Output Voltage 1V rms

(LINE_OUT, LNLVL_OUT) 2.83 V p-p

Output Impedance* 500 Ω

External Load Impedance* 10 kΩ

Output Capacitance* 15 pF

External Load Capacitance 100 pF

V

REF

V

REF_OUT

2.0 2.2 2.5 V

2.2 V

Mute Click (Muted Output Minus Unmuted Midscale DAC Output) ± 5mV

*Guaranteed, not tested.

Specifications subject to change without notice.

REV. 0

–3–

AD1881A–SPECIFICATIONS

STATIC DIGITAL SPECIFICATIONS

Parameter Min Typ Max Unit

High Level Input Voltage (V

Low Level Input Voltage (V

High Level Output Voltage (V

Low Level Output Voltage (V

): Digital Inputs 0.65 × DV

IH

) 0.35 × DV

IL

), IOH = –0.5 mA 0.9 × DV

OH

), IOL = +0.5 mA 0.1 × DV

OL

DD

DD

DD

DD

Input Leakage Current –10 +10 µA

Output Leakage Current –10 +10 µA

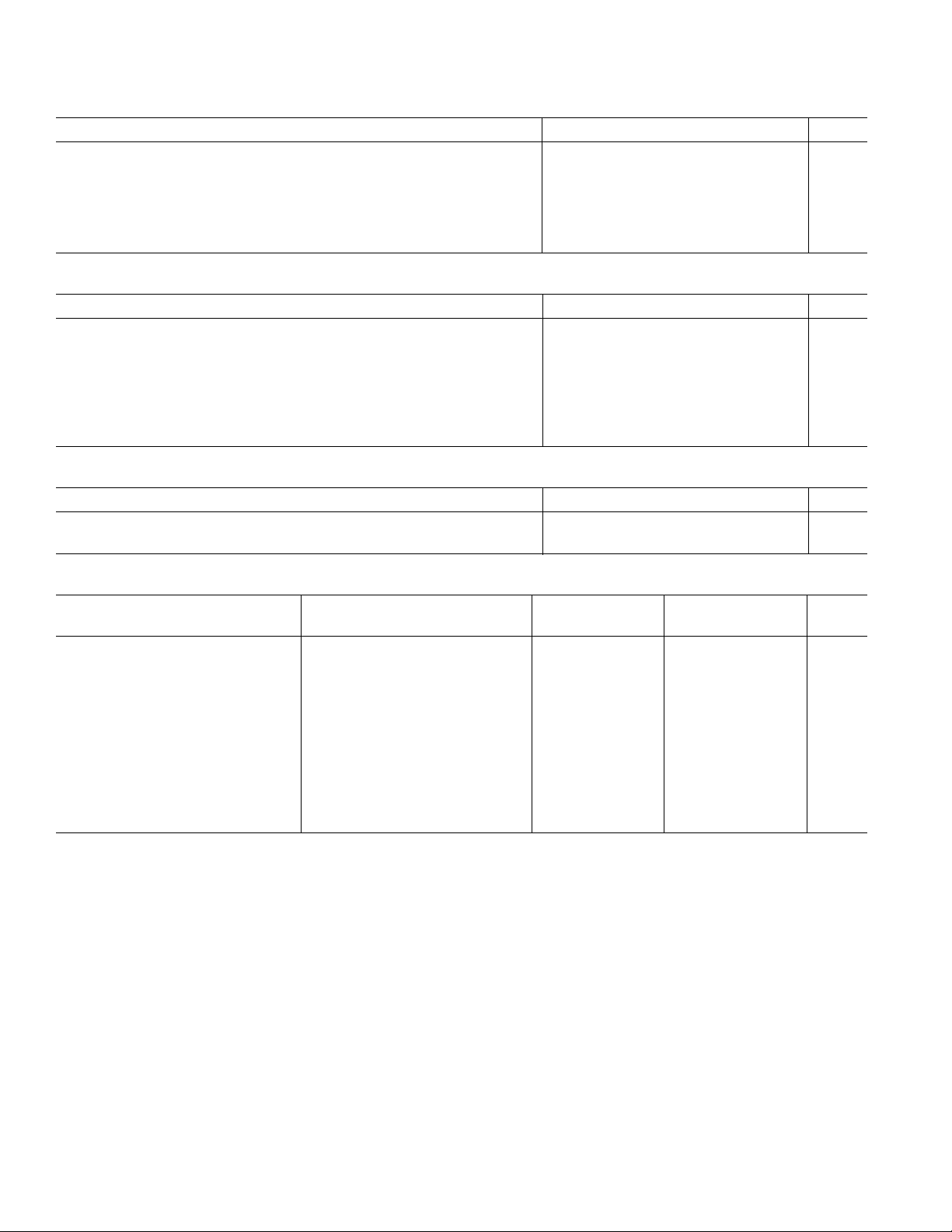

POWER SUPPLY

Parameter Min Typ Max Unit

Power Supply Range – Analog 4.75 5.25 V

Power Supply Range – Digital (3.3 V) 3.0 3.6 V

Power Dissipation – 5 V/3.3 V 280 mW

Analog Supply Current – 5 V 40 mA

Digital Supply Current – 3.3 V 23 mA

Power Supply Rejection (100 mV p-p Signal @ 1 kHz)* 40 dB

(At Both Analog and Digital Supply Pins, Both ADCs and DACs)

CLOCK SPECIFICATIONS*

Parameter Min Typ Max Unit

Input Clock Frequency 24.576 MHz

Recommended Clock Duty Cycle 45 50 55 %

V

V

V

V

POWER-DOWN MODE

DVDD (3.3 V) AVDD (5 V)

Parameter Set Bits Typ Typ Unit

ADC PR0 17 30 mA

DAC PR1 17 26 mA

ADC and DAC PR1, PR0 4 20 mA

ADC + DAC + Mixer (Analog CD On) LPMIX, PR1, PR0 4 12 mA

Mixer PR2 20 18 mA

ADC + Mixer PR2, PR0 17 12 mA

DAC + Mixer PR2, PR1 17 8 mA

ADC + DAC + Mixer PR2, PR1, PR0 4 2 mA

Analog CD Only (AC-Link On) LPMIX, PR5, PR1, PR0 4 12 mA

Analog CD Only (AC-Link Off) LPMIX, PR1, PR0, PR4, PR5 0 12 mA

Standby PR5, PR4, PR3, PR2, PR1, PR0 0 0.1 mA

*Guaranteed, not tested.

Specifications subject to change without notice.

–4–

REV. 0

AD1881A

TIMING PARAMETERS1 (GUARANTEED OVER OPERATING TEMPERATURE RANGE)

Parameter Symbol Min Typ Max Unit

RESET Active Low Pulsewidth t

RESET Inactive to BIT_CLK Startup Delay t

SYNC Active High Pulsewidth t

SYNC Low Pulsewidth t

SYNC Inactive to BIT_CLK Startup Delay t

RST_LOW

RST2CLK

SYNC_HIGH

SYNC_LOW

SYNC2CLK

BIT_CLK Frequency 12.288 MHz

BIT_CLK Period t

BIT_CLK Output Jitter

2

BIT_CLK High Pulsewidth t

BIT_CLK Low Pulsewidth t

CLK_PERIOD

CLK_HIGH

CLK_LOW

SYNC Frequency 48.0 kHz

SYNC Period t

Setup to Falling Edge of BIT_CLK t

Hold from Falling Edge of BIT_CLK t

BIT_CLK Rise Time t

BIT_CLK Fall Time t

SYNC Rise Time t

SYNC Fall Time t

SDATA_IN Rise Time t

SDATA_IN Fall Time t

SDATA_OUT Rise Time t

SDATA_OUT Fall Time t

End of Slot 2 to BIT_CLK, SDATA_IN Low t

Setup to Trailing Edge of RESET (Applies to SYNC, SDATA_OUT) t

Rising Edge of RESET to HI-Z Delay (ATE Test Mode) t

SYNC_PERIOD

SETUP

HOLD

RISECLK

FALLCLK

RISESYNC

FALLSYNC

RISEDIN

FALLDIN

RISEDOUT

FALLDOUT

S2_PDOWN

SETUP2RST

OFF

Propagation Delay 15 ns

RESET Rise Time 50 ns

NOTES

1

Guaranteed, not tested.

2

Output jitter is directly dependent on crystal input jitter.

Specifications subject to change without notice.

50 ns

833 µs

80 ns

19.5 µs

162.8 ns

81.4 ns

750 ps

36.62 40.69 44.76 ns

36.62 40.69 44.76 ns

20.8 µs

5 2.5 ns

5ns

24 10ns

24 10ns

24 10ns

24 10ns

24 10ns

24 10ns

24 10ns

24 10ns

010ms

15 ns

25 ns

REV. 0

–5–

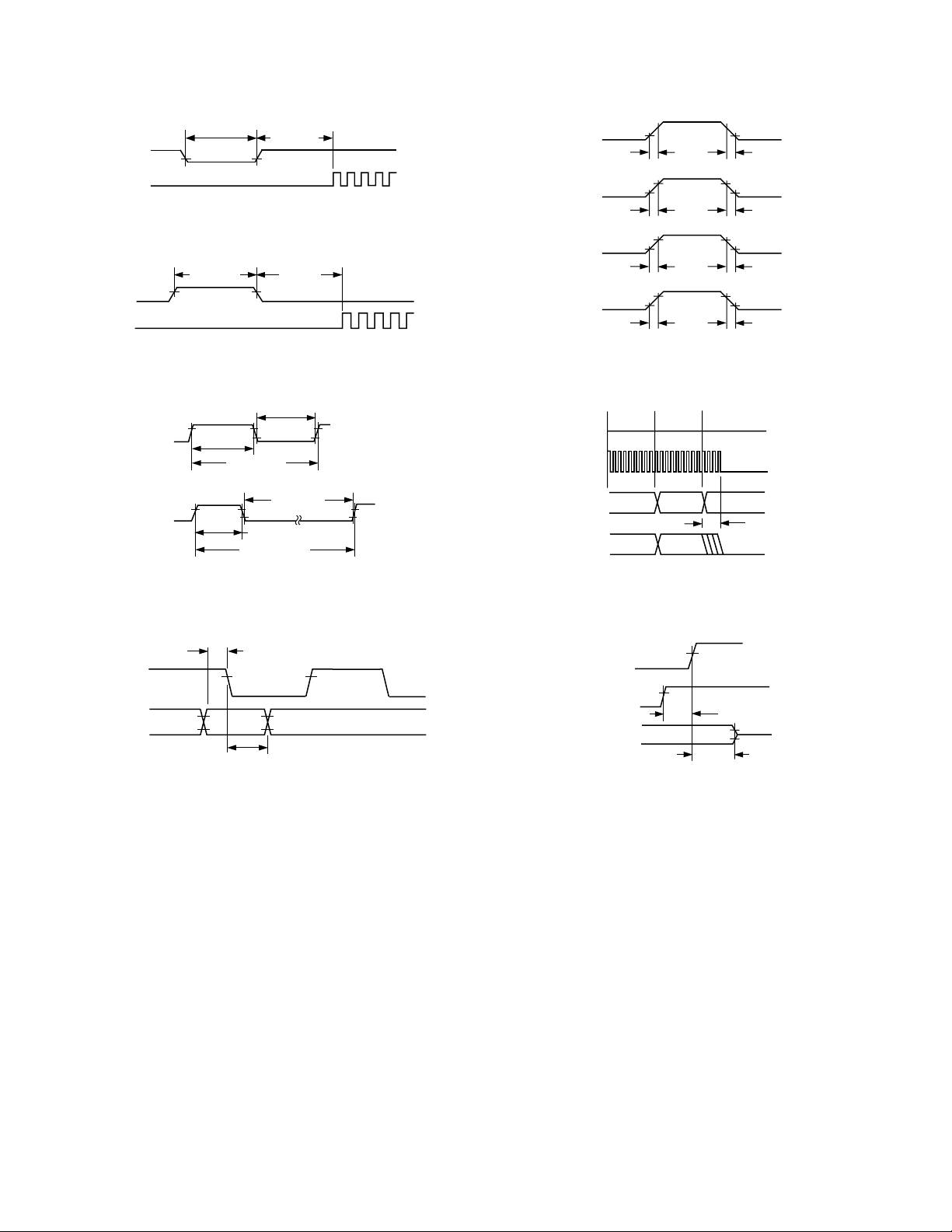

AD1881A

RESET

t

RST_LOW

t

RST2CLK

BIT_CLK

t

RISECLK

t

FALLCLK

BIT_CLK

SYNC

BIT_CLK

Figure 1. Cold Reset

t

SYNC_HIGH

Figure 2. Warm Reset

BIT_CLK

SYNC

t

CLK_HIGH

Figure 3. Clock Timing

t

CLK_PERIOD

t

SYNC_HIGH

t

SYNC_PERIOD

t

RST2CLK

t

CLK_LOW

t

SYNC_LOW

SYNC

SDATA_IN

SDATA_OUT

t

RISESYNC

t

RISEDIN

t

RISEDOUT

t

FALLSYNC

t

FALLDIN

t

FALLDOUT

Figure 5. Signal Rise and Fall Time

SLOT 2

SYNC

BIT_CLK

SDATA_OUT

SDATA_IN

SLOT 1

WRITE

TO 0x26

NOTE: BIT_CLK NOT TO SCALE

DATA

PR4

DON’T

CARE

t

S2_PDOWN

Figure 6. AC Link Low Power Mode Timing

BIT_CLK

SYNC

SDATA_OUT

t

SETUP

t

HOLD

Figure 4. Data Setup and Hold

RESET

SDATA_OUT

SDATA_IN, BIT_CLK

Figure 7. ATE Test Mode

t

OFF

t

SETUP2RST

HI-Z

–6–

REV. 0

AD1881A

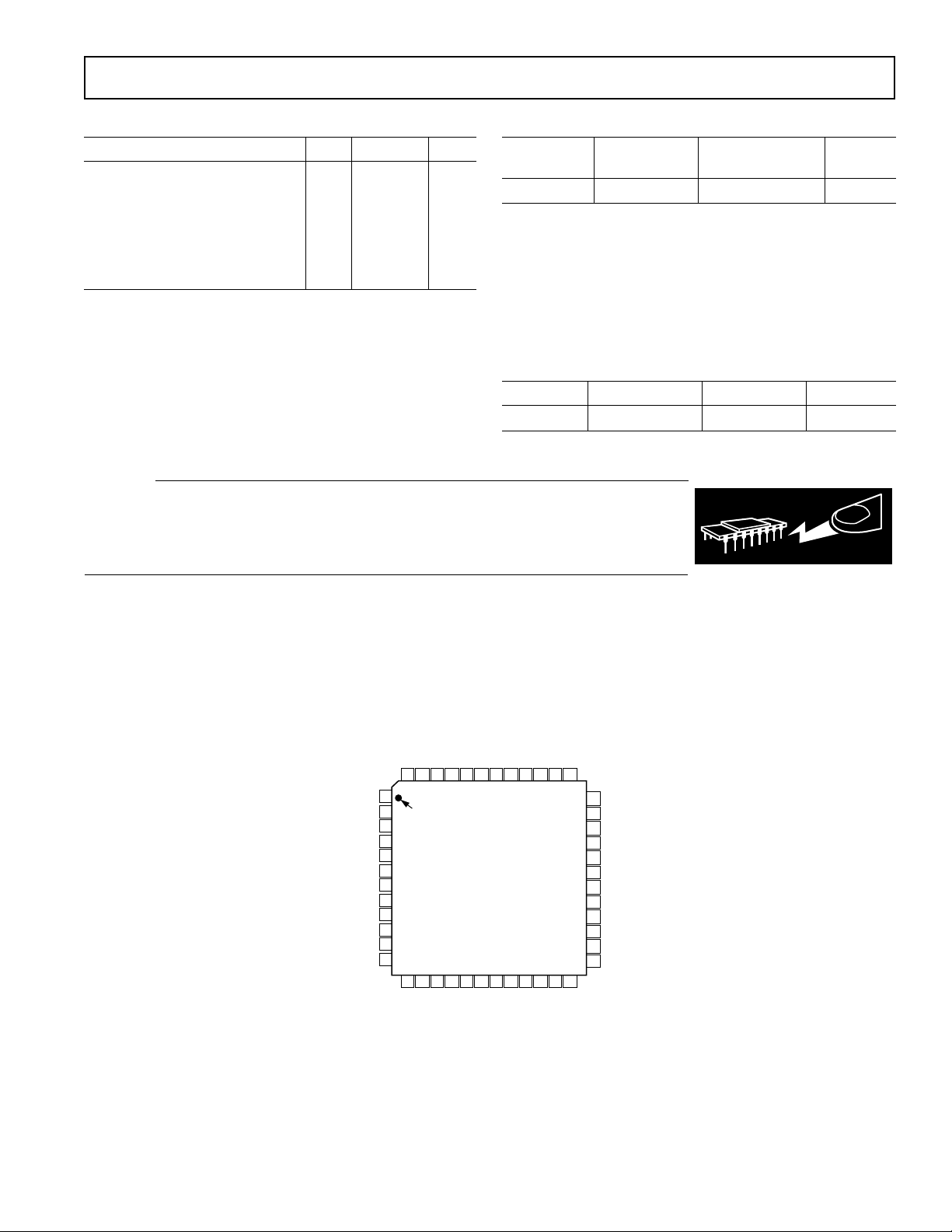

ABSOLUTE MAXIMUM RATINGS*

Parameter Min Max Unit

Power Supplies

Digital (VDD) –0.3 +3.6 V

Analog (V

Analog Input Voltage (Signal Pins) –0.3 V

Digital Input Voltage (Signal Pins) –0.3 V

) –0.3 +6.0 V

CC

+ 0.3 V

CC

+ 0.3 V

DD

Ambient Temperature (Operating) 0 +70 °C

Storage Temperature –65 +150 °C

*Stresses greater than those listed under Absolute Maximum Ratings may cause

permanent damage to the device. This is a stress rating only; functional operation

of the device at these or any other conditions above those indicated in the

operational section of this specification is not implied. Exposure to absolu te maximum

rating conditions for extended periods may affect device reliability.

Model Range Description Option

AD1881AJST 0°C to 70°C 48-Lead LQFP ST-48

ENVIRONMENTAL CONDITIONS

Ambient Temperature Rating

= T

T

T

P

θ

θ

θ

AMB

CASE

D

CA

JA

JC

CASE

= Case Temperature in °C

= Power Dissipation in W

= Thermal Resistance (Case-to-Ambient)

= Thermal Resistance (Junction-to-Ambient)

= Thermal Resistance (Junction-to-Case)

Package

ORDERING GUIDE

Temperature Package Package

– (PD × θCA)

JA

LQFP 76.2°C/W 17°C/W 59.2°C/W

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD1881A features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

JC

WARNING!

CA

ESD SENSITIVE DEVICE

DV

DD1

XTL_IN

XTL_OUT

DV

SS1

SDATA_OUT

BIT_CLK

DV

SS2

SDATA_IN

DV

DD2

SYNC

RESET

PC_BEEP

PIN CONFIGURATION

48-Lead LQFP

SS2

CS0NCNC

AD1881A

TOP VIEW

(Not to Scale)

CD_L

VIDEO_R

VIDEO_L

AV

LNLVL_OUT_R

CD_R

CD_GND_REF

EAPD/CHAIN_IN

CS1

MODE

48 47 46 45 44 39 38 3743 42 41 40

1

PIN 1

2

IDENTIFIER

3

4

5

6

7

8

9

10

11

12

13 14 15 16 17 18 19 20 21 22 23 24

AUX_L

AUX_R

PHONE_IN

NC = NO CONNECT

DD2

NC

LNLVL_OUT_L

AV

MIC1

MIC2

LINE_IN_L

MONO_OUT

LINE_OUT_R

36

35

LINE_OUT_L

CX3D

34

33

RX3D

FILT_L

32

31

FILT_R

AFILT2

30

29

AFILT1

28

VREFOUT

27

VREF

26

AV

25

AV

LINE_IN_R

SS1

DD1

REV. 0

–7–

AD1881A

PIN FUNCTION DESCRIPTIONS

Digital I/O

Pin Name LQFP I/O Description

XTL_IN 2 I Crystal (or Clock) Input, 24.576 MHz.

XTL_OUT 3 O Crystal Output.

SDATA_OUT 5 I AC-Link Serial Data Output, AD1881A Input Stream.

BIT_CLK 6 O AC-Link Bit Clock. 12.288 MHz Serial Data Clock. Daisy Chain Output Clock.

SDATA_IN 8 O AC-Link Serial Data Input. AD1881A Output Stream.

SYNC 10 I AC-Link Frame Sample Sync 48 kHz Fixed Rate.

RESET 11 I AC-Link Reset. AD1881A Master H/W Reset.

Miscellaneous Connections

Pin Name LQFP I/O Description

CS0 45 I Chip Select 0.

CS1 46 I Chip Select 1.

EAPD 47 O External Amp Power-Down Control Signal, Default LO, Active HI

MODE 48 I MODE Select.

Analog I/O

These signals connect the AD1881A component to analog sources and sinks, including microphones and speakers.

Pin Name LQFP I/O Description

PC_BEEP 12 I PC Beep. PC Speaker Beep Passthrough.

PHONE_IN 13 I Phone. From Telephony Subsystem Speakerphone or Handset.

AUX_L 14 I Auxiliary Input Left Channel.

AUX_R 15 I Auxiliary Input Right Channel.

VIDEO_L 16 I Video Audio Left Channel.

VIDEO_R 17 I Video Audio Right Channel.

CD_L 18 I CD Audio Left Channel.

CD_GND_REF 19 I CD Audio Analog Ground Reference for Pseudo-Differential CD Input.

CD_ R 20 I CD Audio Right Channel.

MIC1 21 I Microphone 1. Desktop Microphone Input.

MIC2 22 I Microphone 2. Second Microphone Input.

LINE_IN_L 23 I Line In Left Channel.

LINE_IN_R 24 I Line In Right Channel.

LINE_OUT_L 35 O Line Out Left Channel.

LINE_OUT_R 36 O Line Out Right Channel.

MONO_OUT 37 O Monaural Output to Telephony Subsystem Speakerphone.

LNLVL_OUT_L 39 O Line-Level Output Left Channel.

LNLVL_OUT_R 41 O Line-Level Output Right Channel.

Filter/Reference

These signals are connected to resistors, capacitors, or specific voltages.

Pin Name LQFP I/O Description

VREF 27 O Voltage Reference Filter.

VREFOUT 28 O Voltage Reference Output 5 mA Drive (Intended for MIC Bias).

AFILT1 29 O Antialiasing Filter Capacitor—ADC Right Channel.

AFILT2 30 O Antialiasing Filter Capacitor—ADC Left Channel.

FILT_R 31 O AC-Coupling Filter Capacitor—ADC Right Channel.

FILT_L 32 O AC-Coupling Filter Capacitor—ADC Left Channel.

RX3D 33 O 3D PHAT Stereo Enhancement—Capacitor.

CX3D 34 I 3D PHAT Stereo Enhancement—Capacitor.

–8–

REV. 0

Loading...

Loading...