Stereo Audio, 24-Bit,

a

FEATURES

5.0 V Stereo Audio ADC

with 3.3 V Tolerant Digital Interface

Supports 96 kHz Sample Rates

Supports 16-/20-/24-Bit Word Lengths

Multibit Sigma-Delta Modulators with

“Perfect Differential Linearity Restoration” for

Reduced Idle Tones and Noise Floor

105 dB (Typ) Dynamic Range

Supports 256/512 and 768 ⴛ f

Flexible Serial Data Port

Allows Right-Justified, Left-Justified, I

and DSP Serial Port Modes

Cascadable (up to Four Devices) from a Single DSP

SPORT

Device Control via SPI Compatible Serial Port or

Optional Control Pins

On-Chip Reference

28-Lead SSOP Package

APPLICATIONS

Professional Audio

Mixing Consoles

Musical Instruments

Digital Audio Recorders, Including

CD-R, MD, DVD-R, DAT, HDD

Home Theater Systems

Automotive Audio Systems

Multimedia

Master Clocks

S

2

S Compatible

96 kHz, Multibit ⌺-⌬ ADC

AD1871

PRODUCT OVERVIEW

The AD1871 is a stereo audio ADC intended for digital audio

applications requiring high performance analog-to-digital

conversion. It features two 24-bit conversion channels each

with programmable gain amplifier (PGA), multibit sigma-delta

modulator, and decimation filters. Each channel provides 105 db

of dynamic range, making the AD1871 suitable for applications

such as digital audio recorders and mixing consoles.

Each of the AD1871’s input channels (left and right) can be

configured as either differential or single-ended (two inputs

muxed with internal single-ended-to-differential conversion).

The input PGA features a gain range of 0 dB to 12 dB in steps

of 3 dB. The Σ-∆ modulator features a proprietary multibit

architecture that realizes optimum performance over an audio

bandwidth with standard audio sampling rates of 32 kHz up to

96 kHz. The decimation filter response features very low passband ripple and excellent stop-band attenuation.

The AD1871’s audio data interface supports all common interface

formats such as I

modes that allow for convenient connection to general-purpose

digital signal processors (DSPs). The AD1871 also features an

SPI compatible serial control port that allows for convenient

control of device parameters and functionality such as sample

word-width, PGA settings, interface modes, and so on.

The AD1871 operates from a single 5 V power supply—with

an optional digital interfacing capability of 3.3 V. It is housed in

a 28-lead SSOP package and is characterized for operation

over the temperature range –40°C to +105°C.

2

S, left-justified, right-justified as well as other

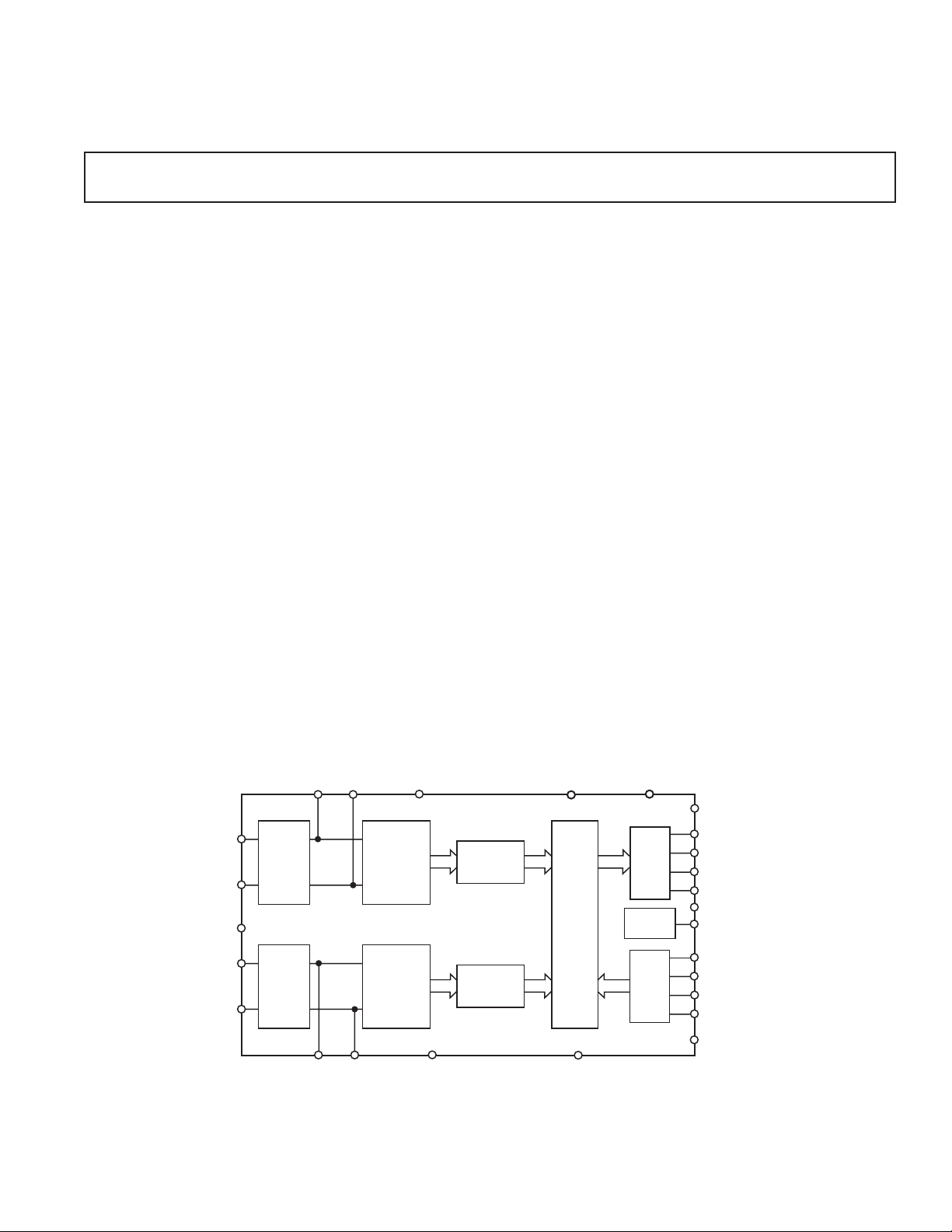

FUNCTIONAL BLOCK DIAGRAM

CAPLN CAPLP AVDD DVDD ODVDD

VINLP

VINLN

VREF

VINRP

VINRN

ANALOG

INPU T

BUFFER

ANALOG

INPU T

BUFFER

CAPRN CAPRP AGND DGND

MULTIBIT

⌺-⌬

MODULATOR

MULTIBIT

⌺-⌬

MODULATOR

AD1871

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

CASC

LRCLK

DECIMATOR

FILTER

ENGINE

DECIMATOR

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

DATA

PORT

CLOCK

DIVIDER

SPI

PORT

BCLK

DOUT

DIN

RESET

MCLK

CLATCH/(M/S)

CCLK/(256/512)

CIN/(DF1)

COUT/(DF0)

XCTRL

AD1871

TABLE OF CONTENTS

FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

FUNCTIONAL BLOCK DIAGRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

PRODUCT OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

TEST CONDITIONS UNLESS OTHERWISE SPECIFIED . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

ANALOG PERFORMANCE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

LOW-PASS DIGITAL FILTER CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

HIGH-PASS DIGITAL FILTER CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

MASTER CLOCK (MCLK) AND RESET TIMING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

DATA INTERFACE TIMING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

CONTROL INTERFACE TIMING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

DIGITAL I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

POWER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

TEMPERATURE RANGE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

ORDERING GUIDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

PIN CONFIGURATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

PIN FUNCTION DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

TERMINOLOGY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

TYPICAL PERFORMANCE CURVES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Filter Responses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Device Performance Curves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

FUNCTIONAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Clocking Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Modulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Digital Decimating Filters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

High-Pass Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

ADC Coding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Analog Input Section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Serial Data Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

CONTROL/STATUS REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Control Register I . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Control Register II . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Control Register III . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Peak Reading Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

EXTERNAL CONTROL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Master/Slave Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

MCLK Mode Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Serial Data Format Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

MODULATOR MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

INTERFACING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Analog Interfacing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

LAYOUT CONSIDERATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

OUTLINE DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

–2–

REV. 0

AD1871–SPECIFICA TIONS

TEST CONDITIONS UNLESS OTHERWISE NOTED

Supply Voltages . . . . . . . . . . . . . . . . . . . . . . 5.0 V

Ambient Temperature . . . . . . . . . . . . . . . . . 25∞C

Input Clock (f

Input Signal . . . . . . . . . . . . . . . . . . . . . . . . . 991.768 Hz

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.5 dB Full Scale (dBFS) (Differential, PGA/MUX Enabled)

Measurement Bandwidth . . . . . . . . . . . . . . . 23.2 Hz to 19.998 kHz

Word Width . . . . . . . . . . . . . . . . . . . . . . . . . 24 Bits

Load Capacitance on Digital Outputs . . . . . 100 pF

Input Voltage High (V

Input Voltage Low (V

Master Mode, Data I

ANALOG PERFORMANCE

Parameter Min Typ Max Unit Conditions

RESOLUTION 24 Bits

DIFFERENTIAL INPUT PGA/MUX Enabled

Dynamic Range (20 Hz to 20 kHz, –60 dB Input)

Unweighted 98 103 dB

A-Weighted 100 105 dB

Signal-to-Noise Ratio 106 dB

Total Harmonic Distortion + Noise –85 dB Input = –0.5 dBFS

(THD+N) –103 dB Input = –20 dBFS

Multibit Modulator Only Modulator Output @ 5.6448 MHz

Dynamic Range (A-Weighted) 102 dB

SINGLE-ENDED INPUT PGA/MUX Enabled

Dynamic Range (20 Hz to 20 kHz, –60 dB Input)

Unweighted 103 dB

A-Weighted 105 dB

Signal-to-Noise Ratio 106 dB

Total Harmonic Distortion + Noise –85 dB Input = –0.5 dBFS

(THD+N) –103 dB Input = –20 dBFS

DIFFERENTIAL INPUT (BYPASS) PGA/MUX Disabled

Dynamic Range (20 Hz to 20 kHz, –60 dB Input)

Unweighted 103 dB

A-Weighted 106 dB

Signal-to-Noise Ratio 106 dB

Total Harmonic Distortion + Noise –86 dB Input = –0.5 dBFS

(THD+N) –104 dB Input = –20 dBFS

DIFFERENTIAL INPUT (f

Dynamic Range (20 Hz to 20 kHz, –60 dB Input)

Unweighted 103 dB

A-Weighted 106 dB

Signal-to-Noise Ratio 106 dB

Total Harmonic Distortion + Noise –87 dB Input = –0.5 dBFS

(THD+N) –104 dB Input = –20 dBFS

Analog Inputs

Differential Input Range (± Full Scale) –2.828 +2.828 V

Input Impedance (PGA/MUX) 8 kW Differential

Input Impedance (ByPass) 40 kW Differential

Input Impedance (PGA/MUX) 4 kW Single Ended

V

REF

DC Accuracy

Gain Error –10 %

Interchannel Gain Mismatch –0.2 –0.01 +0.2 dB

Gain Drift 100 ppm/∞C

Crosstalk (EIAJ Method) –100 dB

) [256 ¥ fS] . . . . . . . . . . 12.288 MHz

CLKIN

) . . . . . . . . . . . . . . . 2.4 V

IH

) . . . . . . . . . . . . . . . 0.8 V

IL

2

S Justified

= 96 kHz) PGA/MUX Enabled; AMC = 1

S

2.138 2.25 2.363 V

REV. 0

–3–

AD1871–SPECIFICA TIONS

LOW-PASS DIGITAL FILTER CHARACTERISTICS (fS = 48 kHz)

Parameter Min Typ Max Unit

Decimation Factor 128

Pass-Band Frequency 21.77 kHz

Stop-Band Frequency 26.23 kHz

Pass-Band Ripple ± 0.01 dB

Stop-Band Attenuation 120 dB

Group Delay 910 ms

LOW-PASS DIGITAL FILTER CHARACTERISTICS (fS = 96 kHz)

Parameter Min Typ Max Unit

Decimation Factor 64

Pass-Band Frequency 43.54 kHz

Stop-Band Frequency 52.46 kHz

Pass-Band Ripple ± 0.01 dB

Stop-Band Attenuation 120 dB

Group Delay 460 ms

HIGH-PASS DIGITAL FILTER CHARACTERISTICS (fS = 48 kHz)

Parameter Min Typ Max Unit

Cutoff Frequency 2 Hz

HIGH-PASS DIGITAL FILTER CHARACTERISTICS (fS = 96 kHz)

Parameter Min Typ Max Unit

Cutoff Frequency 4 Hz

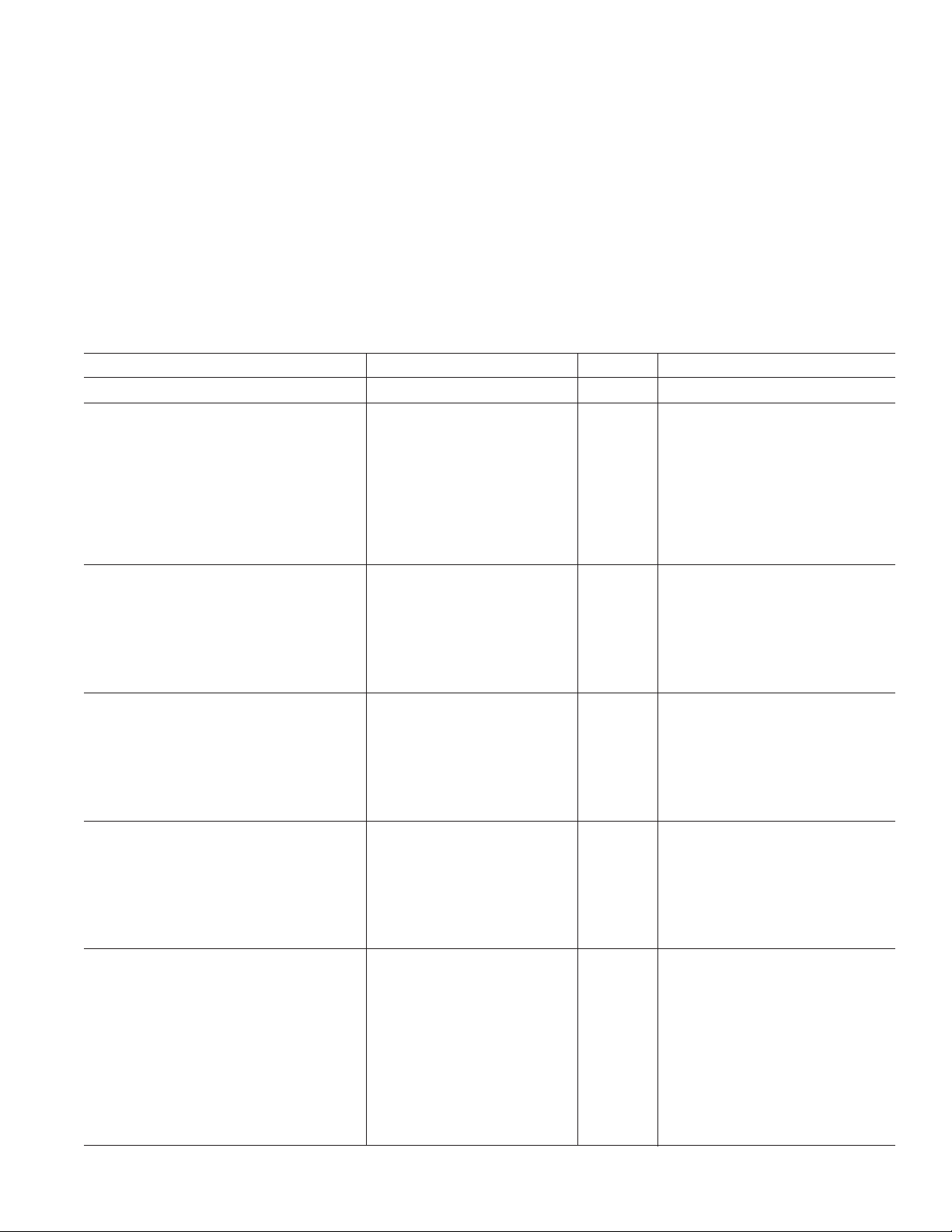

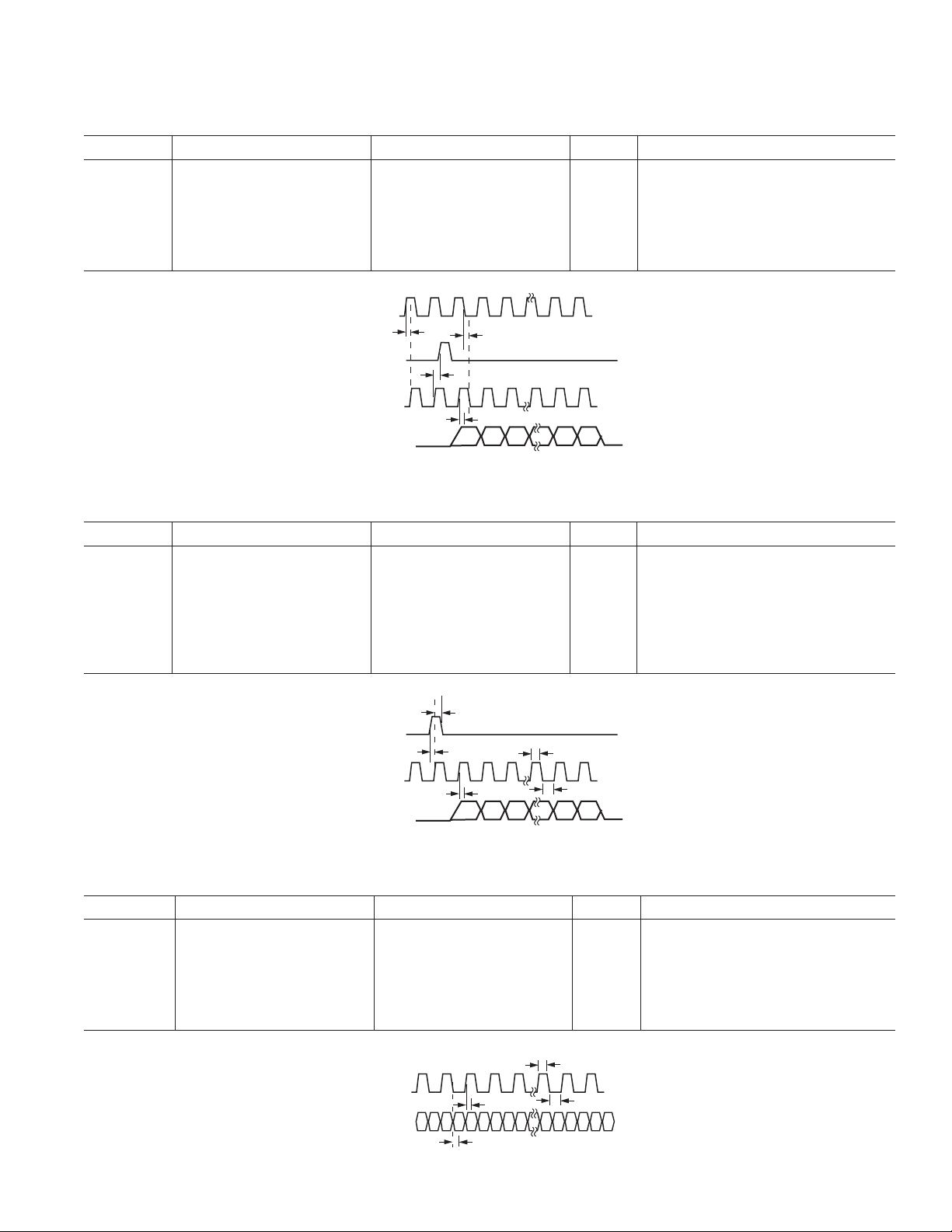

MASTER CLOCK (MCLK) AND RESET TIMING

Mnemonic Description Min Typ Max Unit Comment

t

MCH

t

MCL

t

PDR

MCLK High Width 20 ns

MCLK Low Width 20 ns

RESET Low Pulsewidth 20 ns

t

MCH

MCLK

t

MCL

RESET

t

Figure 1. MCLK/

RESET

PDR

Timing

–4–

REV. 0

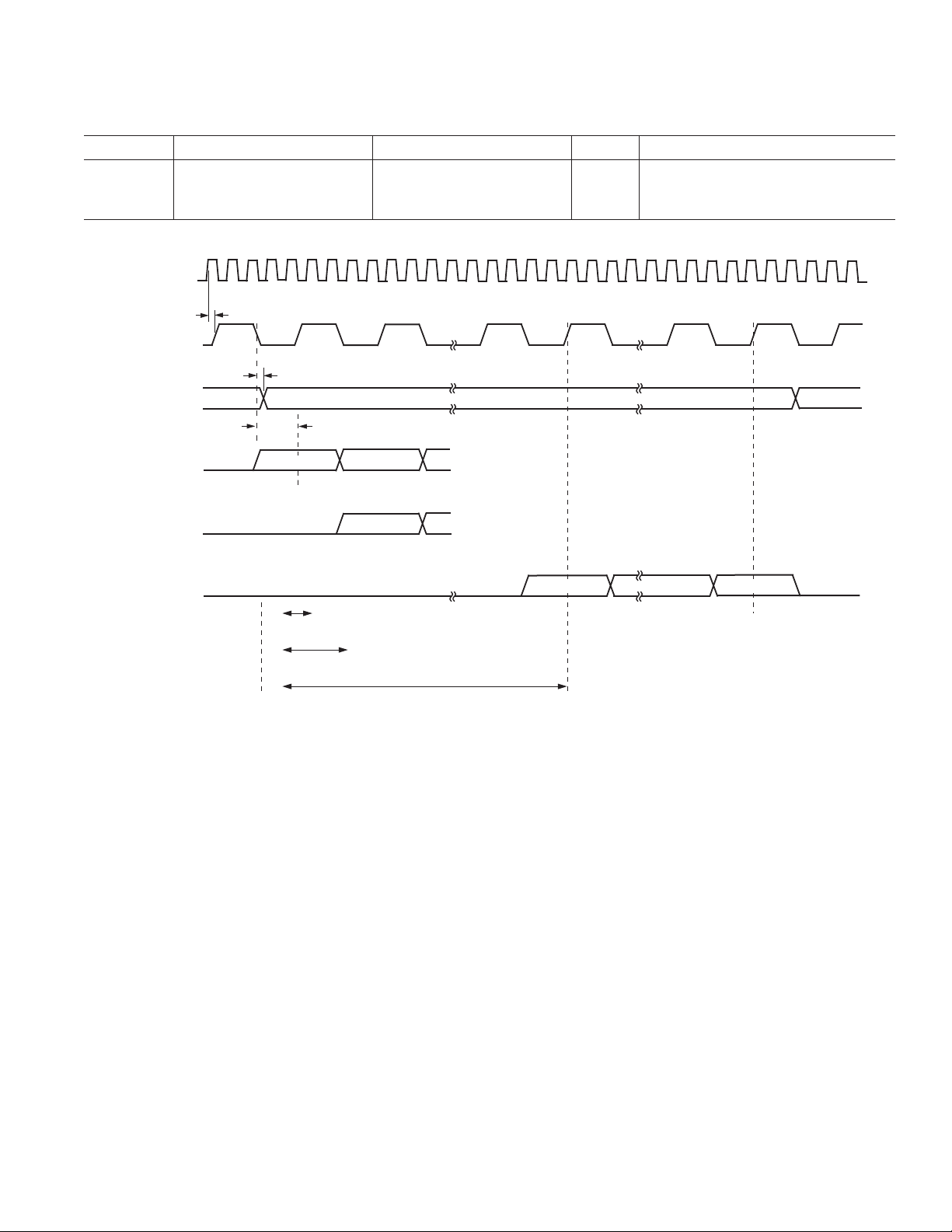

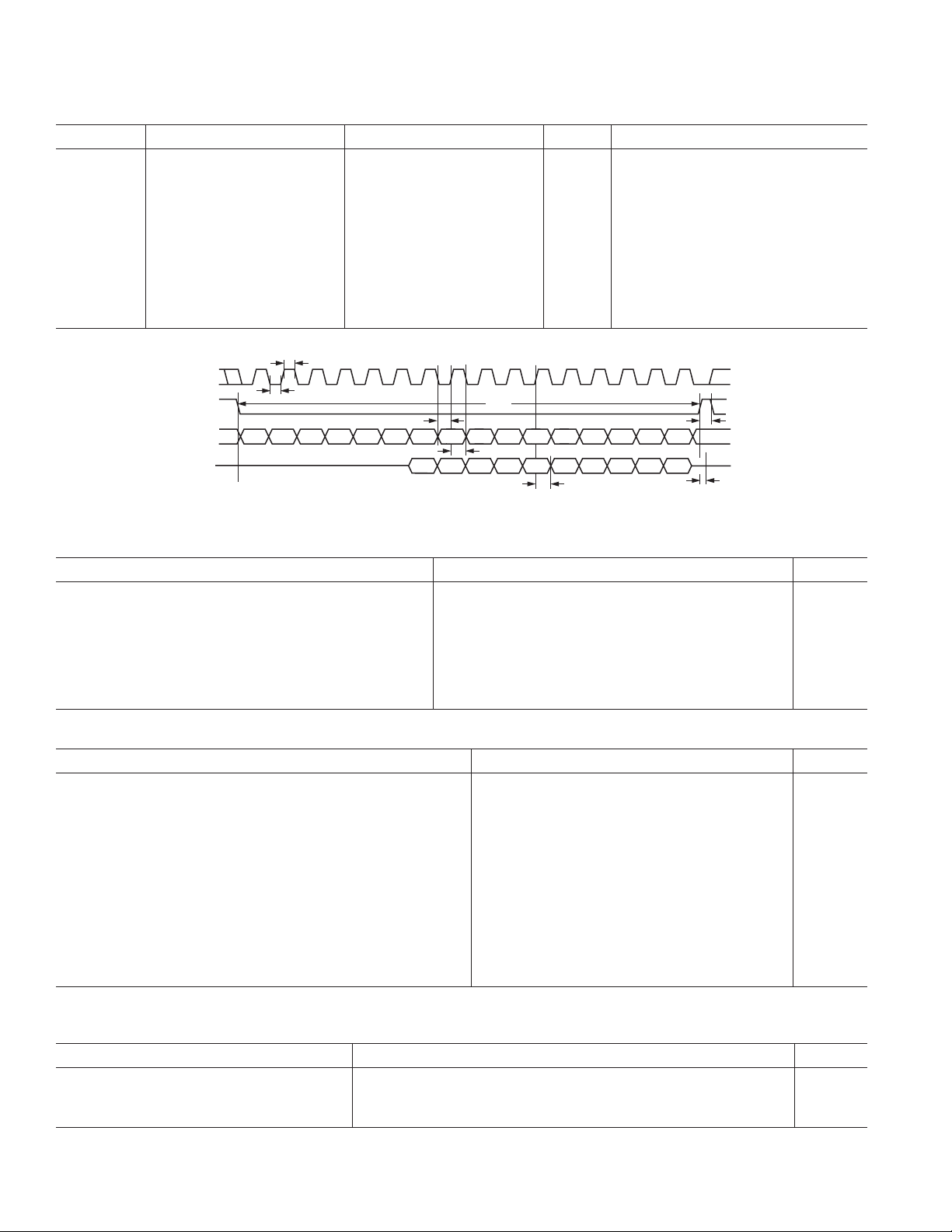

DATA INTERFACE TIMING (STANDALONE MODE–MASTER)

Mnemonic Description Min Typ Max Unit Comment

t

BDLY

t

BLDLY

t

BDDLY

LEFT-JUSTIFIED

2

I

S-JUSTIFIED

BCLK Delay 20 ns From MCLK Rising

LRCLK Delay to Low 10 ns From BCLK Falling

DOUT Delay 10 ns From BCLK Falling

MCLK

t

BDLY

BCLK

t

BLDLY

LRCLK

t

BDDLY

DOUT

MODE

DOUT

MODE

MSB

MSB–

MSB

1

AD1871

RIGHT-JUSTIFIED

DOUT

MODE

8-BIT CLOCKS

(24-BIT DATA)

12-BIT CLOCKS

(20-BIT DATA)

16-BIT CLOCKS

(16-BIT DATA)

MSB

Figure 2. Master Data Interface Timing

LSB

REV. 0

–5–

AD1871

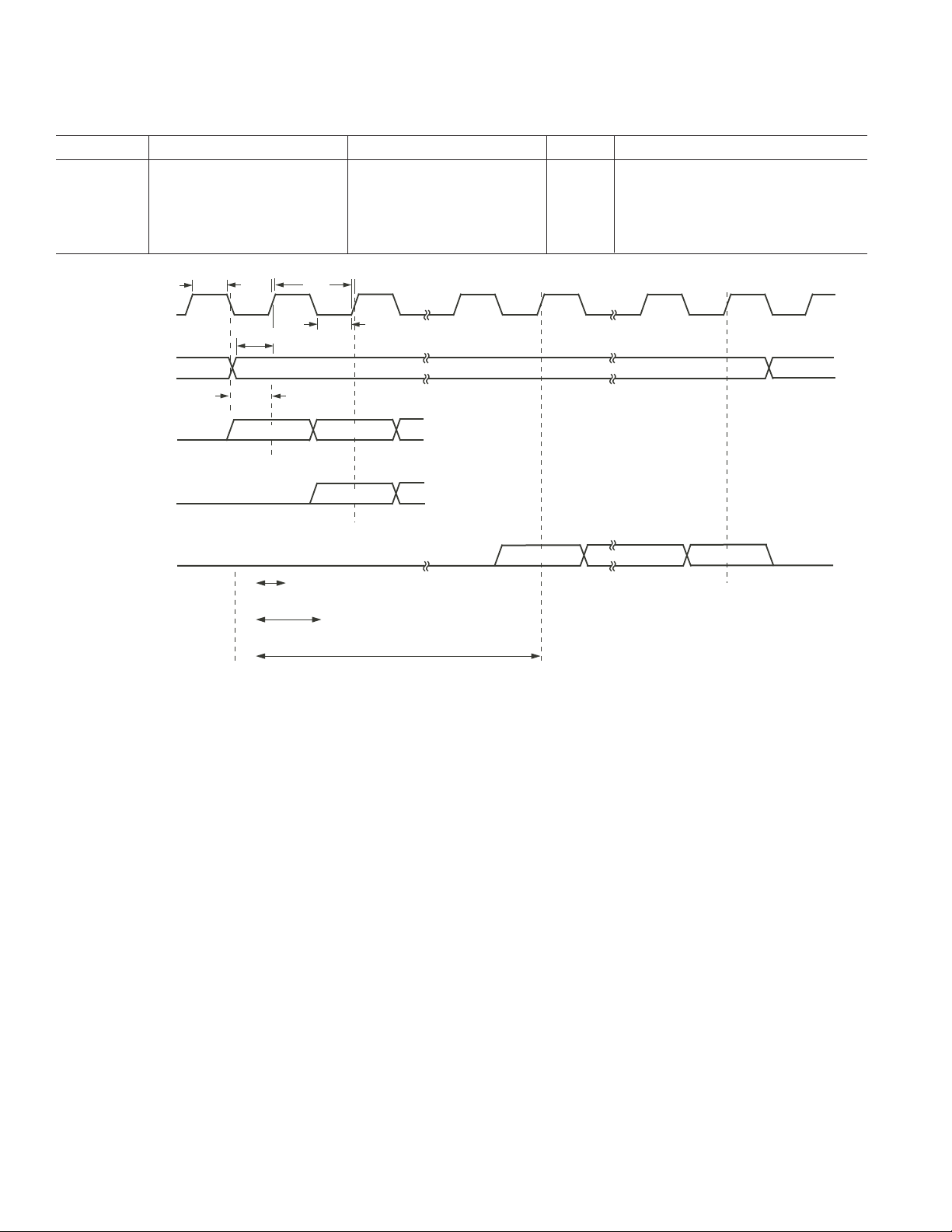

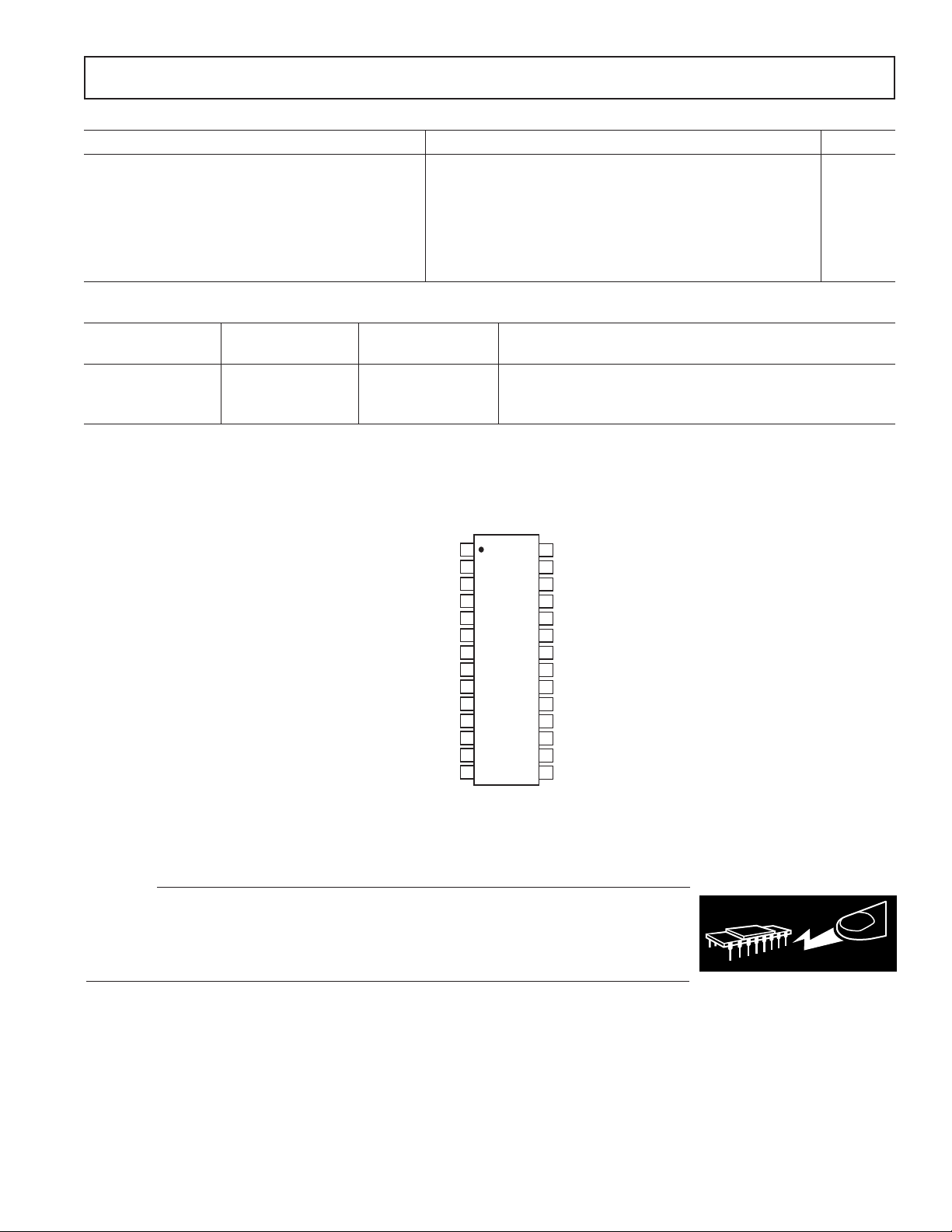

DATA INTERFACE TIMING (STANDALONE MODE–SLAVE)

Mnemonic Description Min Typ Max Unit Comment

t

BCH

t

BCL

t

BDSD

t

LRS

t

LRH

BCLK High Width 30 ns

BCLK Low Width 30 ns

DOUT Delay 20 ns From BCLK Falling

LRCLK Setup 10 ns To BCLK Rising

LRCLK Hold 5 ns From BCLK Rising

BCLK

LRCLK

DOUT

LEFT-JUSTIFIED

MO

DOUT

2

I

S-JUSTIFIED

DE

MO

RIGHT-JUSTIFIED

DOUT

DE

MO

DE

t

BCH

t

LRS

t

BDSD

MSB

8-BIT CLOCKS

(24-BIT DATA)

12-BIT CLOCKS

(20-BIT DATA)

16-BIT CLOCKS

(16-BIT DATA)

t

DBP

t

BCL

MSB–1

MSB

Figure 3. Slave Data Interface Timing

MSB

LSB

–6–

REV. 0

DATA INTERFACE TIMING (CASCADE MODE–MASTER)

Mnemonic Description Min Typ Max Unit Comment

t

BCHDC

t

BCLDC

t

BLRDC

t

BDDC

t

BDIS

t

BDIH

BCLK High Delay 20 ns From MCLK Rising

BCLK Low Delay 20 ns From MCLK Falling

LRCLK Delay 10 ns From BCLK Rising

DOUT Delay 10 ns From BCLK Rising

DIN Setup 10 ns To BCLK Rising

DIN Hold 10 ns From BCLK Rising

MCLK

t

BCHDC

LRCLK

BCLK

DOUT

t

BLRDC

t

t

BDDC

BCLDC

Figure 4. Master Cascade Interface Timing

DATA INTERFACE TIMING (CASCADE MODE–SLAVE)

Mnemonic Description Min Typ Max Unit Comment

t

BCHC

t

BCLC

t

BDSDC

t

LRSC

t

LRHC

t

BDIS

t

BDIH

BCLK High Width 30 ns

BCLK Low Width 30 ns

DOUT Delay 20 ns From BCLK Rising

LRCLK Setup 10 ns To BCLK Rising

LRCLK Hold 5 ns From BCLK Rising

DIN Setup 10 ns To BCLK Rising

DIN Hold 10 ns From BCLK Rising

AD1871

t

t

LRHC

LRSC

t

BDSDC

t

BCHC

t

BCLC

LRCLK

BCLK

DOUT

Figure 5. Slave Cascade Interface Timing

DATA INTERFACE TIMING (MODULATOR MODE)

Mnemonic Description Min Typ Max Unit Comment

t

MOCH

t

MOCL

t

MHDD

t

MLDD

t

MMDR

t

MMDF

MODCLK High Width MCLK ns

MODCLK Low Width MCLK ns

MOD DATA High Delay 30 ns From MCLK Rising

MOD DATA Low Delay 20 ns From MCLK Falling

MODCLK Delay Rising 30 ns MCLK Falling to MODCLK Rising

MODCLK Delay Falling 20 ns MCLK Falling to MODCLK Falling

t

MOCH

MODCLK

t

MOCL

D[0– 3 ]

t

MLDD

t

MHDD

Figure 6. Modulator Mode Timing

REV. 0

–7–

AD1871

CONTROL INTERFACE (SPI) TIMING

Mnemonic Description Min Typ Max Unit Comment

t

CCH

t

CCL

t

CCP

t

CDS

t

CDH

t

CLS

t

CLH

t

COE

t

COD

t

COTS

CCLK High Width 40 ns

CCLK Low Width 40 ns

CCLK Period 80 ns

CDATA Setup Time 10 ns To CCLK Rising

CDATA Hold Time 10 ns From CCLK Rising

CLATCH Setup Time 10 ns To CCLK Rising

CLATCH Hold Time 10 ns From CCLK Rising

COUT Enable 15 ns From CLATCH Falling

COUT Delay 20 ns From CCLK Falling

COUT Three-State 25 ns From CLATCH Rising

t

CCH

CCLK

CLATCH

CIN

COUT

D15 D14 D12 D11 D10 D07 D06 D04 D03 D02 D01 D00D13 D09

t

CCL

t

CSU

D08

D08 D07 D06 D05 D04 D03 D02 D01 D00D09

t

t

CHD

CCL

D05

Figure 7. Control Interface Timing

t

CLH

DIGITAL I/O

Parameter Min Typ Max Unit

Input Voltage High (V

Input Voltage Low (V

Input Leakage (I

Input Leakage (I

IH

IL

Output Voltage High (V

Output Voltage Low (V

) 2.4 V

IH

) 0.8 V

IL

@ VIH = 5 V) 10 mA

@ VIL = 0 V) 10 mA

@ IOH = –2 mA) ODVDD – 0.4 V V

OH

@ IOL = +2 mA) 0.4 V

OL

Input Capacitance 15 pF

POWER

Parameter Min Typ Max Unit

Supplies

Voltage, AVDD, and DVDD 4.5 5 5.5 V

Voltage, ODVDD 2.7 5.5 V

Analog Current 40 45 mA

Analog Current—Power-Down (MCLK Running) 4.0 6.0 mA

Digital Current, DVDD 18 22 mA

Digital Current, ODVDD 0.5 1.0 mA

Digital Current—Power-Down (MCLK Running) DVDD* 0.8 2.0 mA

Digital Current—Power-Down (MCLK Running) ODVDD* 1.0 15.0 mA

Power Supply Rejection

1 kHz 300 mV p-p Signal at Analog Supply Pins –86 dB

20 kHz 300 mV p-p Signal at Analog Supply Pins –77 dB

*RESET held low.

TEMPERATURE RANGE

Parameter Min Typ Max Unit

Specifications Guaranteed 25 ∞C

Functionality Guaranteed –40 +105 ∞C

Storage –65 +150 ∞C

Specifications subject to change without notice.

–8–

REV. 0

AD1871

ABSOLUTE MAXIMUM RATINGS

Min Typ Max Unit

DVDD to DGND and ODVDD to DGND 0 6 V

AVDD to AGND 0 6 V

Digital Inputs DGND – 0.3 DVDD + 0.3 V

Analog Inputs AGND – 0.3 AVDD + 0.3 V

AGND to DGND –0.3 +0.3 V

Reference Voltage Indefinite Short Circuit to Ground

Soldering (10 sec) 300 ∞C

ORDERING GUIDE

Package Package

Model Temperature Description Option

AD1871YRS –40∞C to +105∞C SSOP RS-28

AD1871YRS-REEL –40∞C to +105∞C SSOP RS-28 in 13” Reel (1500 pieces)

EVAL-AD1871EB Evaluation Board

PIN CONFIGURATION

MCLK

CCLK/(256/512)

COUT/(DF0)

CIN/(DF1)

CLATCH/(M/S)

DVDD

DGND

XCTRL

AVDD

VINLN

VINLP

CAPLN

CAPLP

VREF

1

2

3

4

5

6

AD1871

7

TOP VIEW

(Not to Scale)

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

LRCLK

BCLK

DOUT

DIN

RESET

ODVDD

DGND

CASC

AGND

VINRN

VINRP

CAPRN

CAPRP

AGND

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD1871 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

REV. 0

–9–

Loading...

Loading...