Page 1

External Memory PHY Interface (ALTMEMPHY)

(nonAFI) Megafunction User Guide

101 Innovation Drive

San Jose, CA 95134

www.altera.com

UG-01014-7.3

Software Version: 9.1 SP1

Document Version: 7.3

Document Date: January 2010

Page 2

Copyright © 2010 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the sty lized Altera logo, specific device designations, and all other words

and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending

applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use

of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of

device specifications before relying on any published information and before placing orders for products or services

.

Page 3

Contents

Chapter 1. About this Megafunction

Chapter 2. Parameter Settings

Memory Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–2

Use the Preset Editor to Create a Custom Memory Preset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–4

Creating an Emulated x36 QDR II+/QDR II SRAM ALTMEMPHY Variation . . . . . . . . . . . . . . . . . 2–7

Chapter 3. Functional Description—ALTMEMPHY (nonAFI)

QDR II+/QDR II SRAM Calibration Process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–1

PHY-to-Controller Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–4

Initialization Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–5

DDR SDRAM Initialization Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–5

DDR2 SDRAM Initialization Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–7

ALTMEMPHY Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–9

DDR2 and DDR SDRAM Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–9

QDR II+/QDR II SRAM Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–20

Understanding the Testbench . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–25

PLL Initialization and Lock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–25

Memory Device Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–25

Interface Training and Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–25

Write Training Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–26

Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–26

Functional Memory Use . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–26

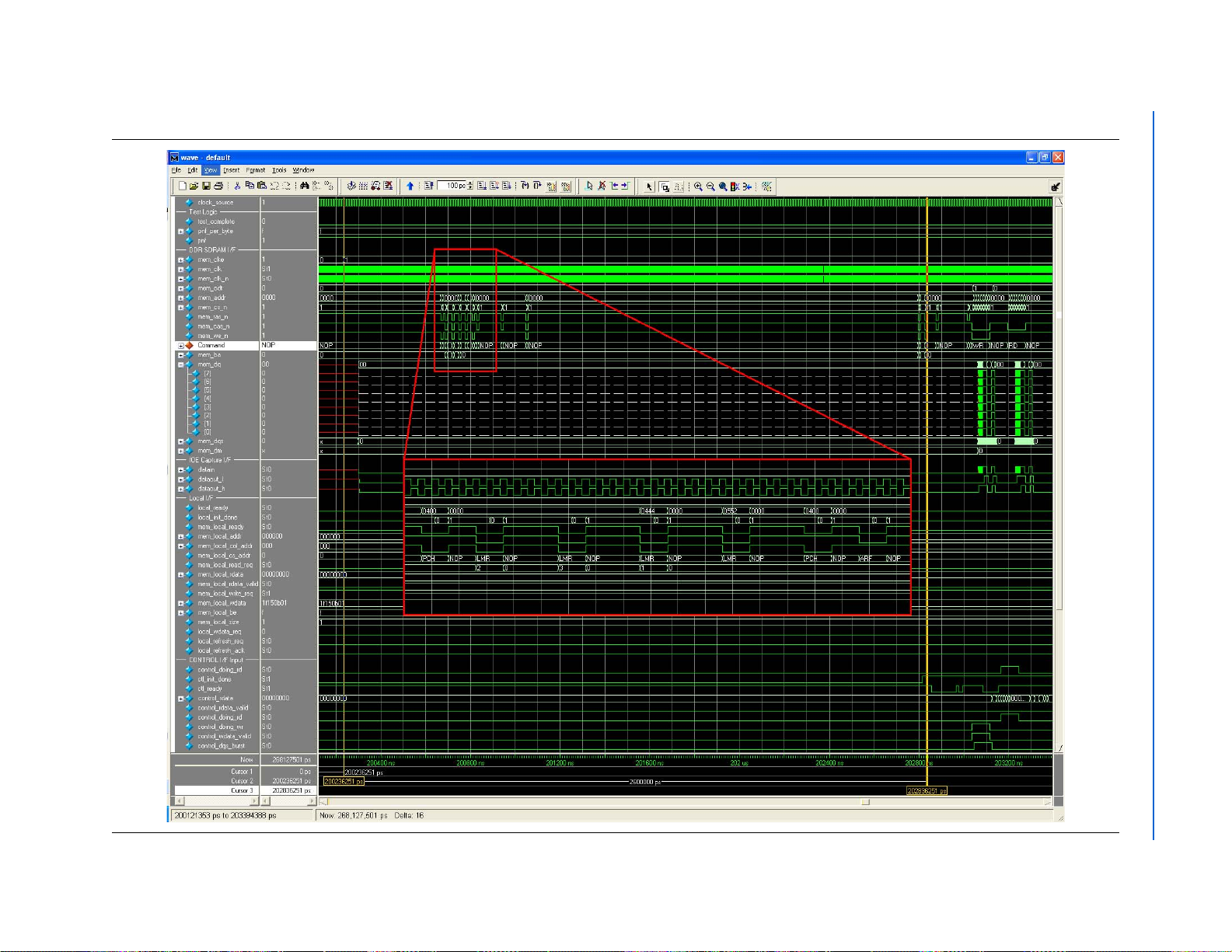

Functional Simulation—the ModelSim Wave and Transcript Window . . . . . . . . . . . . . . . . . . . . . . . . . 3–27

Full Window Stage Identification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–27

Initialization Stage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–29

Write Training Data Stage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–31

Read Calibration Phase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–33

Functional Memory Use Stage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–37

Additional Debug Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–39

PLL and PLL Reconfiguration Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–39

Calibration Status Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–40

Additional Calibration Status Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–40

Design Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–41

Clocks and Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–41

Calibration Process Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–41

Local Interface Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–42

DDR2/DDR SDRAM Half-Rate Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–42

Handshake Mechanism Between Read Commands and Read Data . . . . . . . . . . . . . . . . . . . . . . . 3–43

Handshake Mechanism Between Write Commands and Write Data . . . . . . . . . . . . . . . . . . . . . . 3–44

DDR2/DDR SDRAM Full-Rate Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–47

Handshake Mechanism Between Read Commands and Read Data . . . . . . . . . . . . . . . . . . . . . . . 3–47

Handshake Mechanism Between Write Commands and Write Data . . . . . . . . . . . . . . . . . . . . . . 3–49

Chapter 4. Support for Arria GX, HardCopy II, Stratix II, and Stratix II GX Devices

DDR2/DDR SDRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–1

© January 2010 Altera Corporation External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

Page 4

iv

Half-Rate Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–1

Read Datapath . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–1

Clock and Reset Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–3

Write Datapath . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–8

Address and Command Datapath . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–9

Full-Rate Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–11

Read Datapath . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–11

Clock and Reset Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–11

Write Datapath . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–11

Address and Command Datapath . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–11

Chapter Info. Additional Information

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

How to Contact Altera . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–2

Typographic Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–2

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide © January 2010 Altera Corporation

Page 5

1. About this Megafunction

This user guide is only for legacy designs as it describes the specifications and

functional descriptions of the ALTMEMPHY megafunctions that are common to

non-Altera PHY interface (nonAFI) variations. This user guide also describes the

implementation of the QDR II+ and QDR II SRAM interfaces for legacy designs

targeted for Arria

The ALTMEMPHY megafunction is an interface between a memory controller and

memory devices and performs read and write operations to the memory. The

megafunction is available as a stand-alone product or as an integrated product with

®

Altera

high-performance memory controllers. As a stand-alone product, use the

ALTMEMPHY megafunction with either custom or third-party controllers.

The ALTMEMPHY megafunction for DDR3, DDR2, and DDR SDRAM offers two

different PHY-to-controller interfaces: Altera PHY interface (AFI) and nonAFI. The

AFI is supported for all variations of ALTMEMPHY for DDR3, DDR2, and DDR

SDRAM. ALTMEMPHY for DDR3 SDRAM only support the AFI. The AFI results in a

simpler connection between the PHY and controller, so Altera recommends that you

use the AFI for new designs; only use the nonAFI for legacy designs.

®

GX, Stratix®II, and Stratix II GX devices.

f For information about using the external memory interfaces (DDR3, DDR2, and DDR

SDRAM) with AFI and the ALTMEMPHY megafunction, refer to Volume 3:

Implementing Altera Memory Interface IP of the External Memory Interface Handbook.

f For more information about the ALTMEMPHY megafunction features, refer to Volume

3: Implementing Altera Memory Interface IP of the External Memory Interface Handbook.

f For information about issues on the ALTMEMPHY megafunction in a particular

Quartus

®

II software version, refer to the Quartus II Software Release Notes

© Juanuary 2010 Altera Corporation External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

Page 6

1–2 Chapter 1: About this Megafunction

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide © Juanuary 2010 Altera Corporation

Page 7

2. Parameter Settings

This section describes the memory preset settings for the ALTMEMPHY (nonAFI)

megafunction with the QDR II+/QDR II SRAM interfaces only.

f For information about using the MegaWizard

™

Plug-In Manager or the SOPC Builder

flow to implement the ALTMEMPHY megafunction, refer to the Getting Started

chapter in Volume 3: Implementing Altera Memory Interface IP of the External Memory

Interface Handbook.

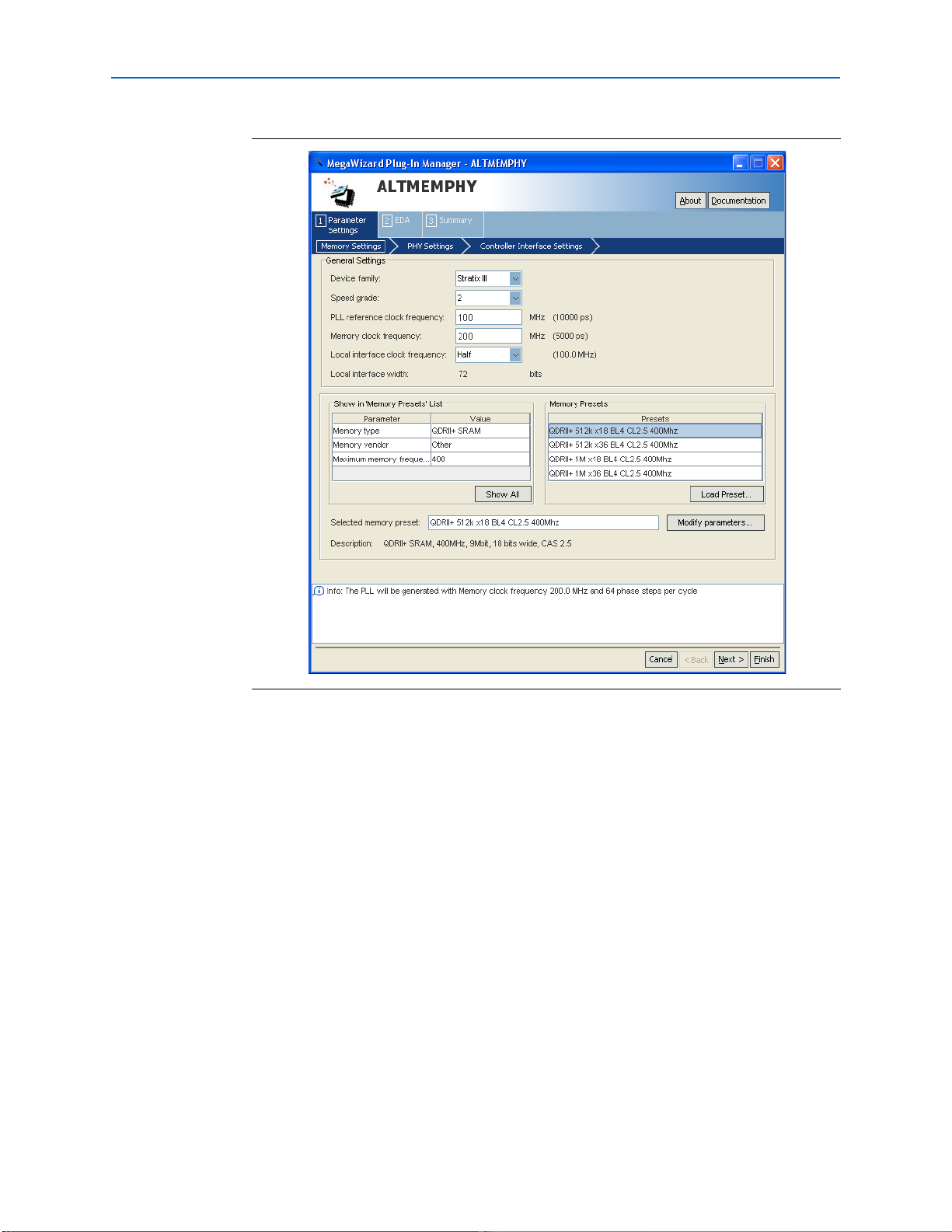

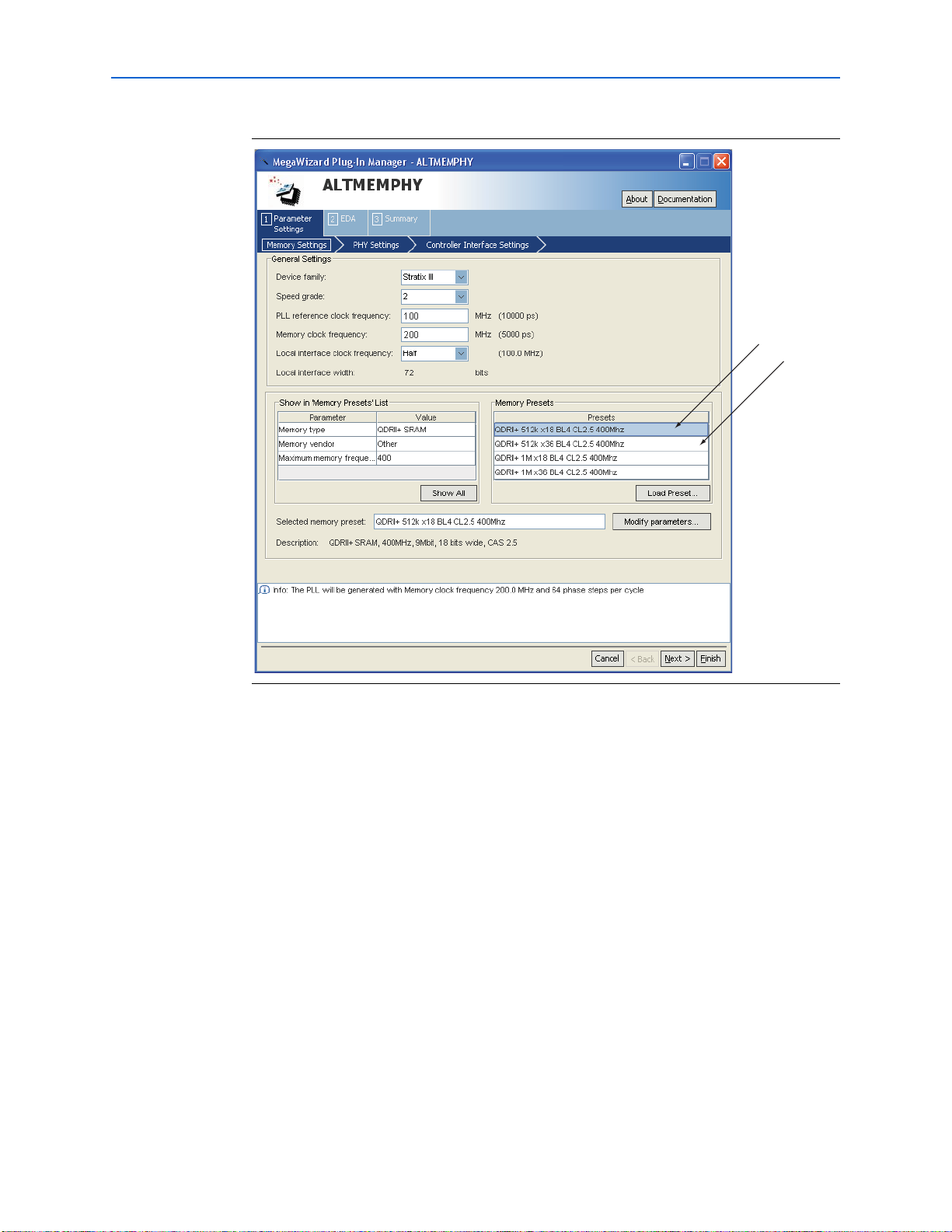

The ALTMEMPHY Parameter Settings page in the ALTMEMPHY MegaWizard

interface (Figure 2–1) allows you to parameterize the following settings:

■ Memory Settings

■ PHY Settings

■ Controller Interface Settings

1 The options for PHY Settings tab are editable if they apply to the Altera device that

you have chosen for your interface. Otherwise, the options are disabled. The options

for Controller Interface Settings tab are disabled when you are creating an

ALTMEMPHY (nonAFI) megafunction for QDR II+/QDR II SRAM interface.

f For more information about the PHY Settings and the Controller Interface Settings,

refer to the Parameter Settings chapter in Volume 3: Implementing Altera Memory Interface

IP of the External Memory Interface Handbook

© January 2010 Altera Corporation External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

Page 8

2–2 Chapter 2: Parameter Settings

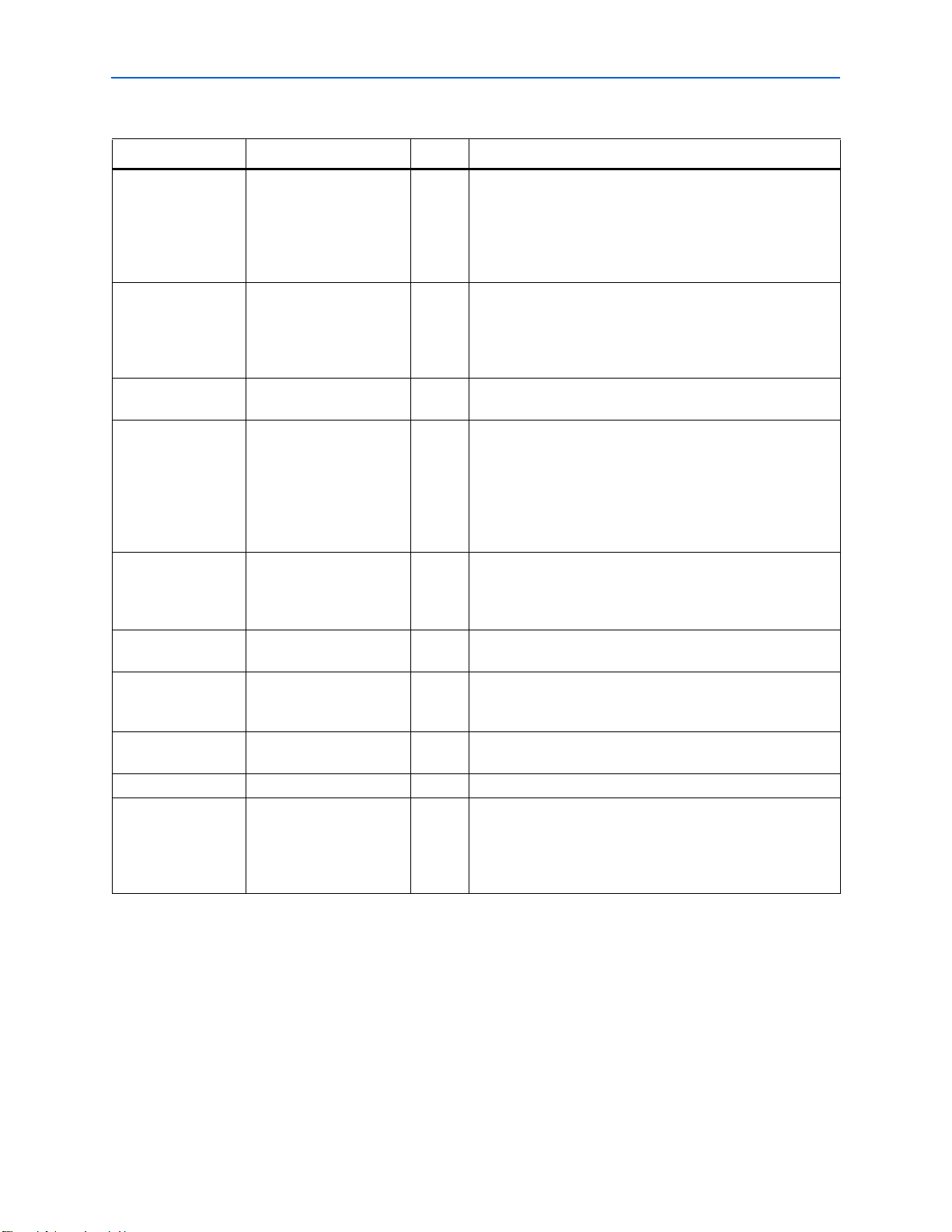

Figure 2–1. ALTMEMPHY Parameter Settings Page

The text window at the bottom of the MegaWizard Plug-In Manager displays

information about the memory interface, warnings (for example, if you are creating

an interface above the maximum frequency supported), and errors if you are trying to

create something that is not supported. The Finish button is disabled until you fix all

the errors indicated in this window.

The following section describes the Memory Settings tab for QDR II+/QDR II SRAM

interface in more detail.

Memory Settings

In the Memory Settings tab, you can choose the frequency of operation for the device

and a particular memory device for your system. Under General Settings, you can

choose the device family, speed grade, and clock information. In the middle of the

page (left-side), you can filter the available memory device listed on the right side of

the Memory Presets dialog box, refer to Figure 2–1. If you cannot find the exact device

that you are using, choose a device that has the closest specifications, then manually

modify the parameters to match your actual device by clicking Modify parameters,

next to the Selected memory preset field.

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide © January 2010 Altera Corporation

Page 9

Chapter 2: Parameter Settings 2–3

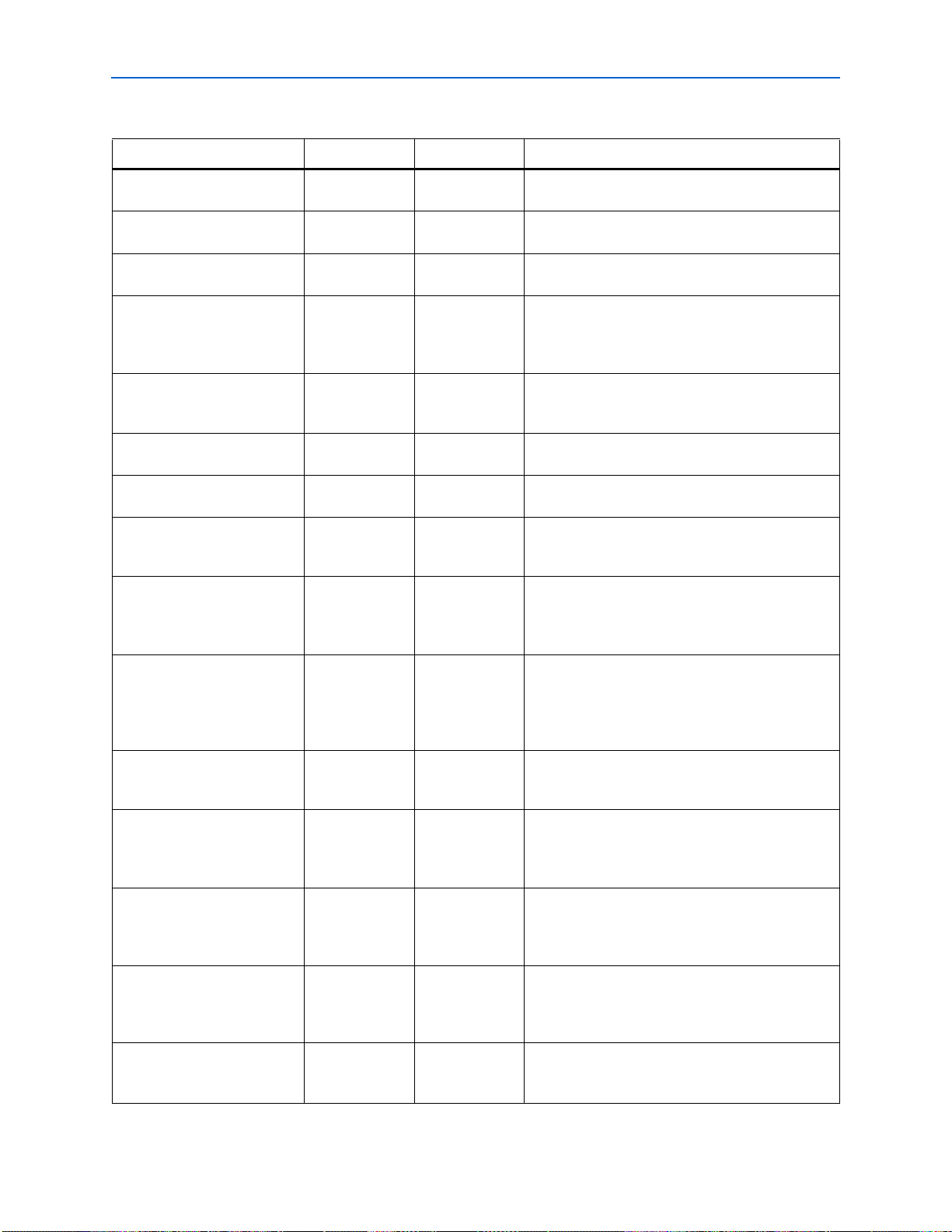

Tab le 2– 1 describes the General Settings available on the Memory Settings page of

the ALTMEMPHY MegaWizard interface.

Table 2–1. General Settings

Parameter Name Description

Device family Targets device family. The device family selected here must match the device family selected on

MegaWizard page 2a.

Speed grade Selects a particular speed grade of the device (for example, 2, 3, or 4 for the Stratix III device

family).

PLL reference clock

frequency

Determines the clock frequency of the external input clock to the PLL. Ensure that you use three

decimal points if the frequency is not a round number (for example, 166.667 MHz or 100 MHz) to

avoid a functional simulation or a PLL locking issue.

Memory clock

frequency

Determines the memory interface clock frequency. If you are operating a memory device below its

maximum achievable frequency, ensure that you enter the actual frequency of operation rather than

the maximum frequency achievable by the memory device. Also, ensure that you use three decimal

points if the frequency is not a round number (for example, 333.333 MHz or 400 MHz) to avoid a

functional simulation or a PLL locking issue.

Controller data rate Selects the data rate for the memory controller. Sets the frequency of the controller to equal to

either the memory interface frequency (full-rate) or half of the memory interface frequency

(half-rate).

Local interface clock

frequency

This field’s value depends on the memory clock frequency and controller data rate, and whether or

not you turn on the Enable Half Rate Bridge option.

Local interface width This field’s value depends on the memory clock frequency and controller data rate, and whether or

not you turn on the Enable Half Rate Bridge option.

Tab le 2– 2 describes the options available to filter the Memory Presets that are

displayed. This section is where you indicate that you are creating a datapath for

QDR II+/QDR II SRAM.

Table 2–2. Memory Presets List

Parameter Name Description

Memory type You can filter the type of memory to display. For the ALTMEMPHY megafunction with nonAFI, select

QDR II+ SRAM and QDR II SRAM.

Memory vendor You can filter the memory types by vendor. JEDEC is also one of the options, allowing you to

choose the JEDEC specifications. If your chosen vendor is not listed, you can choose Other for QDR

II+/QDR II SRAM interfaces. Then, pick a device that has similar specifications to your chosen

device and check the values of each parameter. Make sure you change the each parameter value to

match your device specifications.

Memory format You can filter the type of memory by format (for example, components or DIMM packages). This

option is only available for DDR3, DDR2, and DDR SDRAM interfaces.

Maximum frequency You can filter the type of memory by the maximum operating frequency.

© January 2010 Altera Corporation External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

Page 10

2–4 Chapter 2: Parameter Settings

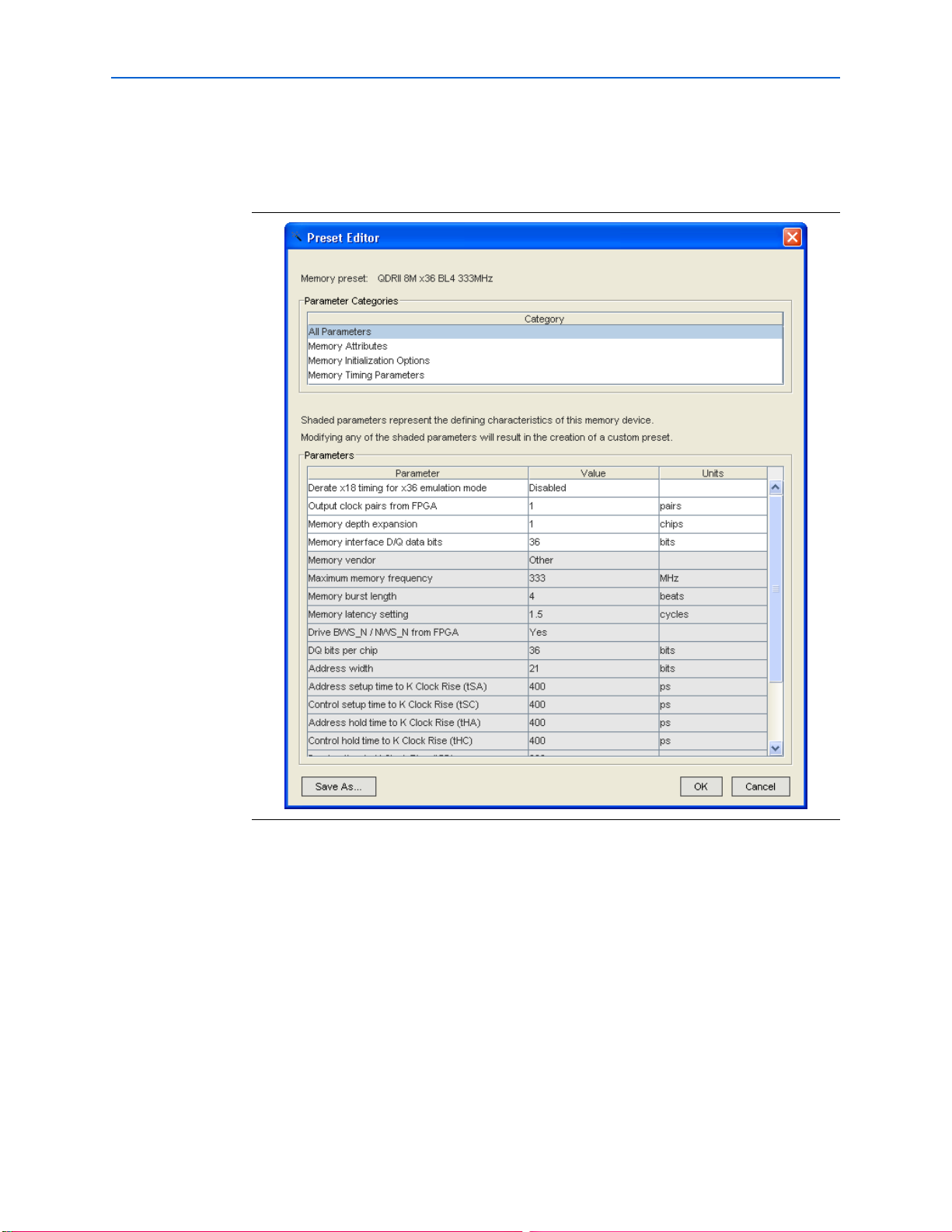

Use the Preset Editor to Create a Custom Memory Preset

Pick a device in the Memory Presets list that is closest or the same as the actual

memory device that you are using. Then, click the Modify Parameters button to

parameterize the following settings in the Preset Editor dialog box:

■ Memory attributes—These are the settings that determine your system's number of

DQ, DQS, address, and memory clock pins.

■ Memory initialization options—These settings are stored in the memory mode

registers as part of the initialization process.

■ Memory timing parameters—These are the parameters that create and

time-constraint the PHY.

1 Even though the device you are using is listed in Memory Presets, ensure that the

settings in the Preset Editor dialog box are accurate as some parameters may have

been updated in the memory device datasheets.

You can change the parameters with a white background to reflect your system. You

can also change the parameters with a gray background so the device parameters

match the device you are using. These parameters in gray background are

characteristics of the chosen memory device and changing them creates a new custom

memory preset. If you click Save As (at the bottom left of the page) and save the new

settings in the <quartus_install_dir>\quartus\common\ip\altera\altmemphy\lib\

directory, you can use this new memory preset in other Quartus II projects created in

the same version of the software.

When you click Save, the new memory preset appears at the bottom of the Memory

Presets list in the Memory Settings tab.

1 If you save the new settings in a directory other than the default directory, click Load

Preset in the Memory Settings tab to load the settings into the Memory Presets list.

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide © January 2010 Altera Corporation

Page 11

Chapter 2: Parameter Settings 2–5

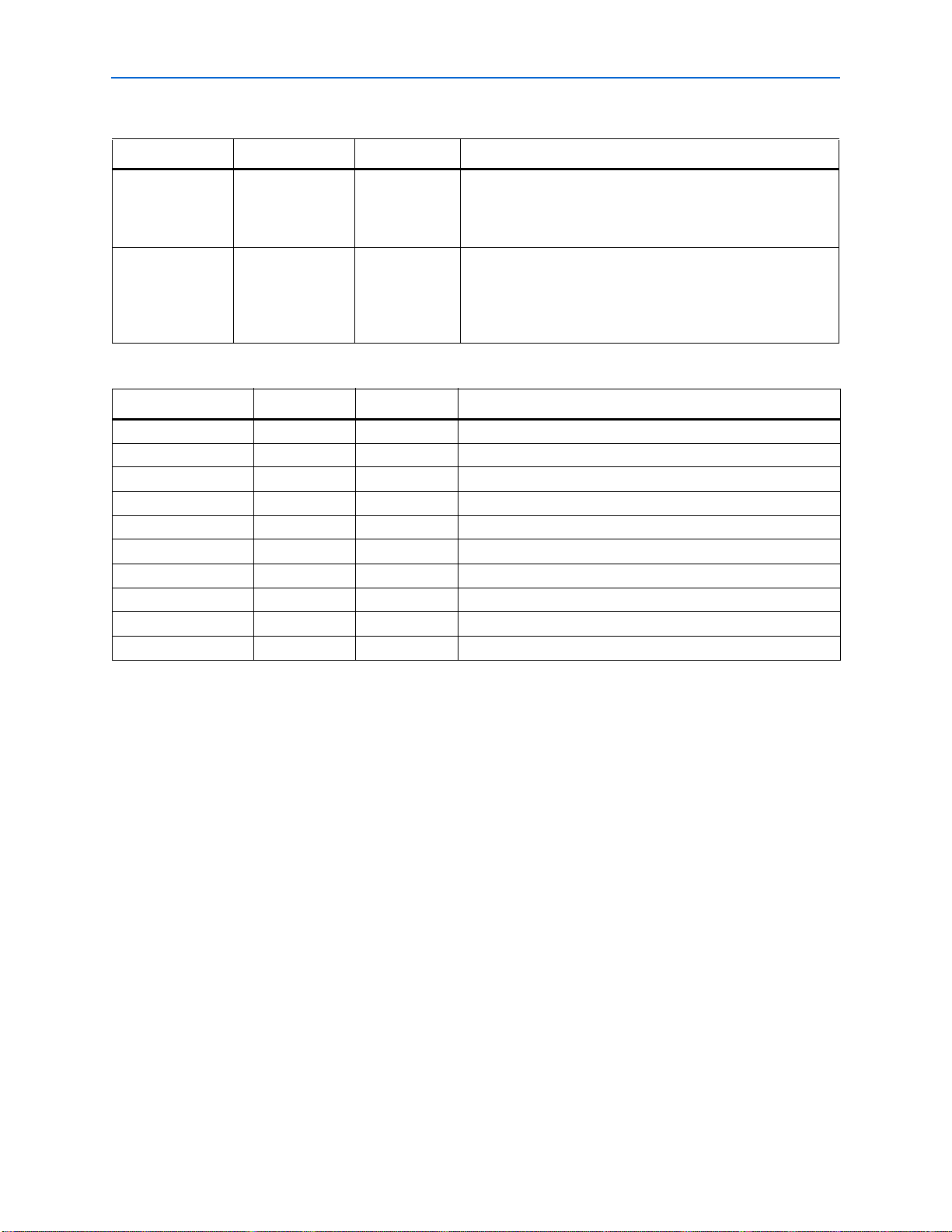

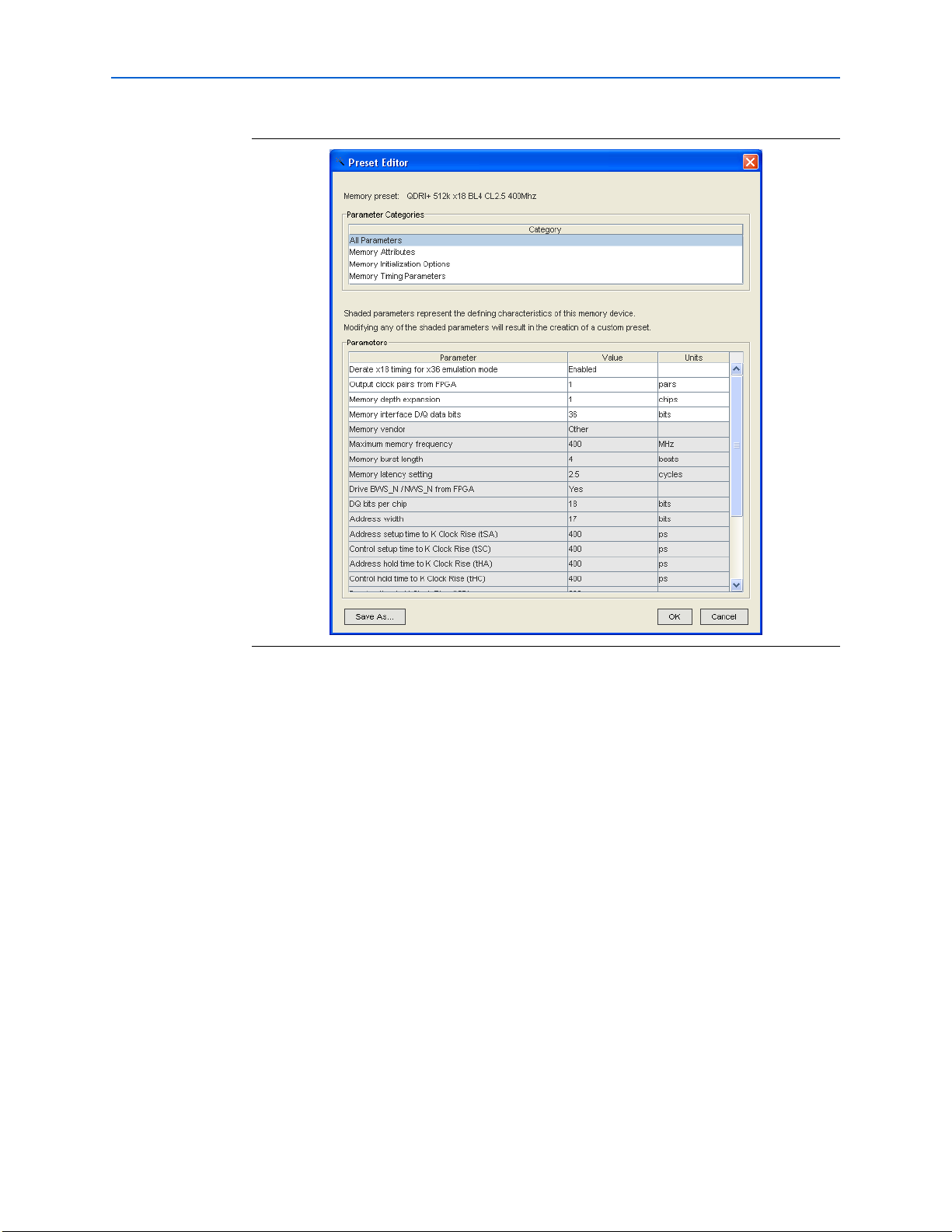

QDR II+/QDR II SRAM Preset Editor Page

Figure 2–2 shows the Preset Editor page for the ALTMEMPHY variation for

QDR II+/QDR II SRAM interfaces.

Figure 2–2. Preset Editor for QDR II+/QDR II SRAM Interfaces

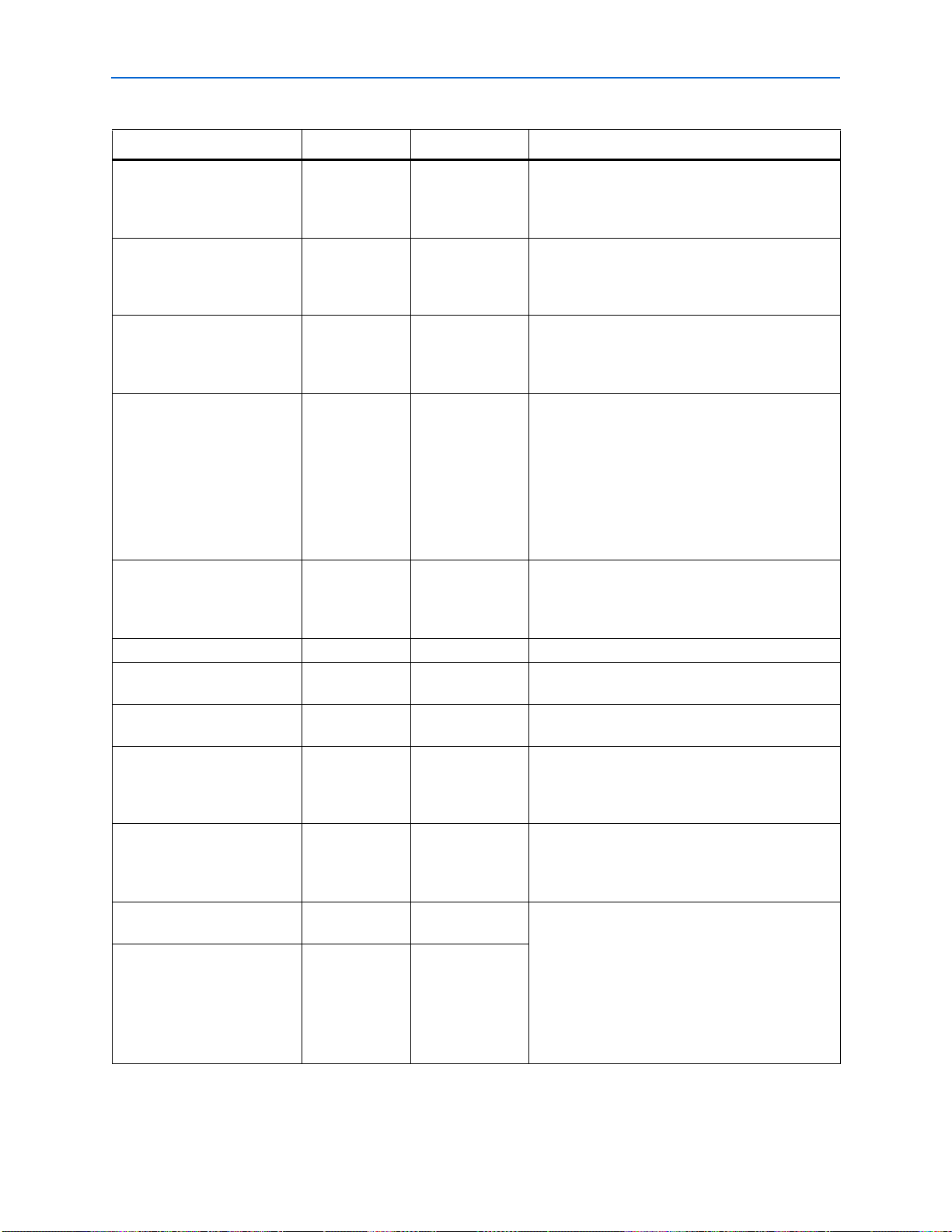

Tab le 2– 3 through Ta bl e 2 –5 describe the QDR II+/QDR II SRAM parameters

available for memory attributes, initialization options, and timing parameters.

The QDR II+ SRAM devices have the same parameters as QDR II SRAM devices, but

their value ranges can differ. Confirm that the value you have chosen is valid in the

ALTMEMPHY MegaWizard interface.

© January 2010 Altera Corporation External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

Page 12

2–6 Chapter 2: Parameter Settings

Table 2–3. QDR II+/QDR II SRAM Attribute Settings

Parameter Name Range (1) Units Description

De-rate ×18 timing

for emulation ×36

mode

Enabled or Disabled — Allows the ALTMEMPHY megafunction to derate the timing

calculation when creating ×36 QDR II+/QDR II SRAM

interfaces by using two ×18 DQS/DQ groups. For more

information on ×36 emulation, refer to “Creating an Emulated

x36 QDR II+/QDR II SRAM ALTMEMPHY Variation” on

page 2–7.

Output clock pairs

from FPGA

1–16 pairs Selects the number of differential clock pairs driven from the

FPGA to the memory. More clock pairs reduce the loading of

each output when interfacing with multiple memory devices.

Memory clock pins use the signal splitter feature in Stratix III

and Stratix IV devices for differential signaling.

Memory depth

expansion

Memory interface

D/Q data bits

1–2 chips Picks the number of chip selects of memory supported. This

option is for memory depth expansion.

8–288 bits Defines the width of external memory read and write data bus.

Multiply the number of devices with the number of DQ pins

per device when you create width-expanded memory

interfaces. Even though the GUI allows you to choose 288-bit

DQ width, the interface data width is limited by the number of

pins on the device. For best performance, have the whole

interface on one side of the device.

Memory vendor Others — Displays the name of the memory vendor for all supported

memory standards.The ALTMEMPHY megafunction only has

generic QDR II+/QDR II SRAM data sheet information listed

under vendor as Other.

Maximum memory

frequency

Drive

BWS_N/NWS_N

See the memory device

MHz Defines the maximum frequency supported by the memory.

data sheet

Yes or No — Enables the use of the write select pins for write operations

when set to Yes.

from FPGA

DQ bits per chip 8, 9, 18, 36 bits Defines the width of D and Q data bus on each QDRII SRAM

chip.

Address width 15–25 bits Sets the number of address bits.

I/O standard QDR II+ SRAM: 1.5 V

HSTL Class I;

— Selects the I/O standard to be applied to the memory interface

pins.

QDR II SRAM: 1.8 V HSTL

Class I or 1.5 V HSTL

Class I

Note to Table 2–3:

(1) The range values depend on the actual memory device used.

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide © January 2010 Altera Corporation

Page 13

Chapter 2: Parameter Settings 2–7

Table 2–4. QDR II+/QDR II SRAM Initialization Options

Parameter Name Range Units Description

Memory burst

length

4 beats Sets the memory burst length for the interface. As the

QDR II+/QDR II SRAM ALTMEMPHY megafunction only

supports half-rate designs, only a memory burst length of four

is supported, which equates to a local burst length of one.

Memory latency

setting

1.5 (QDR II

SRAM) or 2.5

(QDR II+ SRAM)

Cycles Sets the memory latency. Altera devices only support latency of

2.5 for QDR II+ SRAM and 1.5 for QDR II SRAM. QDR II+

SRAM with latency of 2.0 is not supported with Altera devices,

even though the ALTMEMPHY MegaWizard interface shows

this as an option.

Table 2–5. QDR II+/QDR II SRAM Timing Parameter Settings

Parameter Name Range Units Description

t

SA

t

SC

t

HA

t

HC

t

SD

t

HD

t

CQHQV

t

CQHQX

t

(1) 0–2,000 ps Echo clock high to inverted echo clock high.

CQHCQnH

t

(1) 0–2,000 ps Echo clock high.

CQH

Note to Table 2–5:

(1) This parameter is available for QDR II+ SRAM interfaces only.

200–500 ps Address setup time to K clock rise.

200–500 ps Control setup time to K clock rise.

200–500 ps Address hold time to K clock rise.

200–500 ps Control hold time after K clock rise.

200–500 ps D setup time to K clock rise.

200–500 ps D hold time to K clock rise.

200–500 ps Echo clock high to data valid.

200–500 ps Echo clock high to data invalid.

Creating an Emulated x36 QDR II+/QDR II SRAM ALTMEMPHY Variation

From software implementation point of view, creating a ×36 emulated QDR II+/QDR

II SRAM interface is exactly the same as implementing an interface with two ×18

QDR II+/QDR II SRAM devices. In the Memory Settings page of the ALTMEMPHY

MegaWizard interface, select a ×18 QDR II+/QDR II SRAM with the same timing

specifications as ×36 QDR II+/QDR II SRAM device (see Figure 2–3).

For more information about ×36 emulation for QDR II+/QDR II SRAM interfaces,

refer to the Exceptions for ×36 Emulated QDR II and QDR II+ SRAM Interfaces in Arria II

GX, Stratix III and Stratix IV Devices section in Volume 2: Device, Pin, and Board Layout

Guidelines of the External Memory Interface Handbook.

© January 2010 Altera Corporation External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

Page 14

2–8 Chapter 2: Parameter Settings

Emulated Device

Actual Device

Figure 2–3. Select a ×18 Device

To indicate that you are interfacing with 36-bit read and 36-bit write data follow these

steps:

1. On the Memory Settings page click Modify Parameters, to open the Preset Editor,

see Figure 2–4.

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide © January 2010 Altera Corporation

Page 15

Chapter 2: Parameter Settings 2–9

Figure 2–4. Preset Editor

2. For Derate ×18 timing for ×36 emulation mode, select Enabled. This setting tells

the report_timing.tcl script to use the derating factor for ×36 emulation. If you

have modified the board such that the slew rate of the ×36 emulated (doubleloaded) CQ/CQn signal is comparable to a non-emulated (single-loaded)

CQ/CQn signal, you can leave this option as Disabled, as there is no slew rate

degradation in your design.

3. For Output clock pairs from FPGA select 1. Only one mem_clk and mem_clk_n

pair connect to the QDR II+/QDR II SRAM device's K and Kn ports..

4. Memory interface D/Q data bits select 36, which is the data bus width for ×36

QDR II+/QDR II SRAM interfaces.

After generation, for devices with F780 and F1152 packages that do not have ×18 DQ

groups necessary to fit the write data bus, follow these steps to modify the

<variation_name>_pin_assignments.tcl file to change the assignments to use ×9 DQ

groups:

1. Remove the memory interface data pin group assignment of 18 for write data bus

and DM pins in the Assignment Editor.

2. Find the following assignments in the <variation_name>_pin_assignments.tcl.

set_instance_assignment -name MEMORY_INTERFACE_DATA_PIN_GROUP 18 -to

${d_pin_name}\[0..17\] -from ${d_pin_name}\[0\]

© January 2010 Altera Corporation External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

Page 16

2–10 Chapter 2: Parameter Settings

set_instance_assignment -name MEMORY_INTERFACE_DATA_PIN_GROUP 18 -to

${dm_pin_name}\[0..1\] -from ${d_pin_name}\[0\]

set_instance_assignment -name MEMORY_INTERFACE_DATA_PIN_GROUP 18 -to

${d_pin_name}\[18..35\] -from ${d_pin_name}\[18\]

set_instance_assignment -name MEMORY_INTERFACE_DATA_PIN_GROUP 18 -to

${dm_pin_name}\[2..3\] -from ${d_pin_name}\[18\]

3. Replace with the following assignment:

set_instance_assignment -name MEMORY_INTERFACE_DATA_PIN_GROUP 9 -from

${d_pin_name}[0] -to ${d_pin_name}[0..8]

set_instance_assignment -name MEMORY_INTERFACE_DATA_PIN_GROUP 9 -from

${d_pin_name}[0] -to ${dm_pin_name}[0]

set_instance_assignment -name MEMORY_INTERFACE_DATA_PIN_GROUP 9 -from

${d_pin_name}[18] -to ${d_pin_name}[18..26]

set_instance_assignment -name MEMORY_INTERFACE_DATA_PIN_GROUP 9 -from

${d_pin_name}[18] -to ${dm_pin_name}[2]

set_instance_assignment -name MEMORY_INTERFACE_DATA_PIN_GROUP 9 -from

${d_pin_name}[9] -to ${d_pin_name}[9..17]

set_instance_assignment -name MEMORY_INTERFACE_DATA_PIN_GROUP 9 -from

${d_pin_name}[9] -to ${dm_pin_name}[1]

set_instance_assignment -name MEMORY_INTERFACE_DATA_PIN_GROUP 9 -from

${d_pin_name}[27] -to ${d_pin_name}[27..35]

set_instance_assignment -name MEMORY_INTERFACE_DATA_PIN_GROUP 9 -from

${d_pin_name}[27] -to ${dm_pin_name}[3]

4. Save the <variation_name>_pin_assignments.tcl file.

The rest of the RTL implementation is similar to a regular QDR II+/QDR II SRAM

interface.

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide © January 2010 Altera Corporation

Page 17

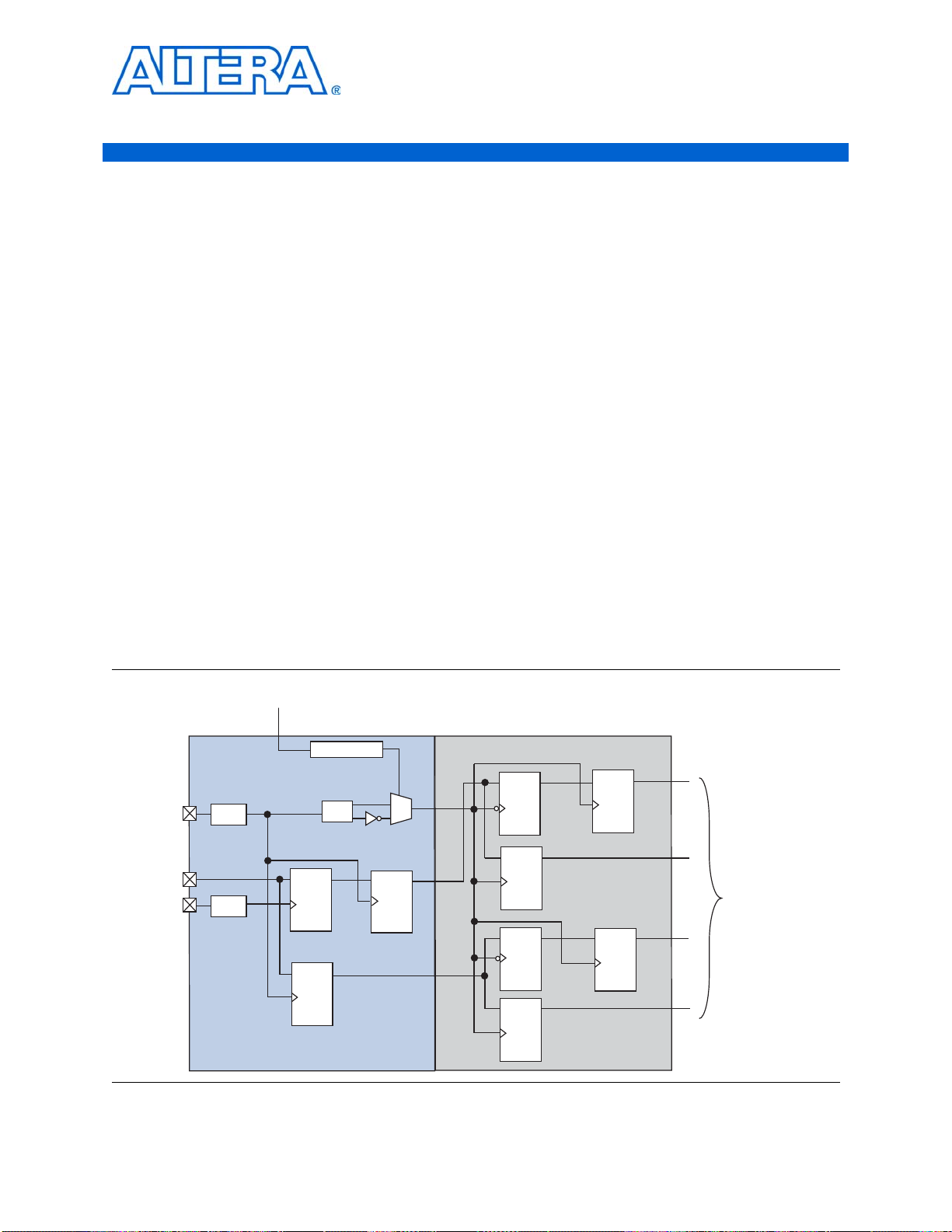

3. Functional Description—ALTMEMPHY

CQn

Input from

Sequencer

D

Q

D

Q

Shift Register

1/2

shifted

D

Q

DQ

D

Q

D

Q

D

Q

D

Q

D

Q

D

Q

Half-Rate Data

CQn

shifted

This chapter describes the QDR II+/QDR II SRAM calibration process, the typical

PHY-to-Controller interfaces that are connected to the ALTMEMPHY variation and

the signal name prefixes each module uses for nonAFI variations.

1 Altera recommends that you use the AFI for new designs; only use the nonAFI for

existing designs.

QDR II+/QDR II SRAM Calibration Process

1 This section describes the calibration process for QDR II+/QDR II SRAM interfaces

only. For information about the calibration process for DDR2 and DDR SDRAM, refer

to the Calibration section in the DDR and DDR2 SDRAM High-Performance Controllers

and ALTMEMPHY IP User Guide.

The calibration process of a QDR II+/QDR II SRAM device is considerably simpler

than that of a calibration process for a DDR2/DDR SDRAM device. The calibration

process involves selecting the right phase of the resynchronization clock to capture

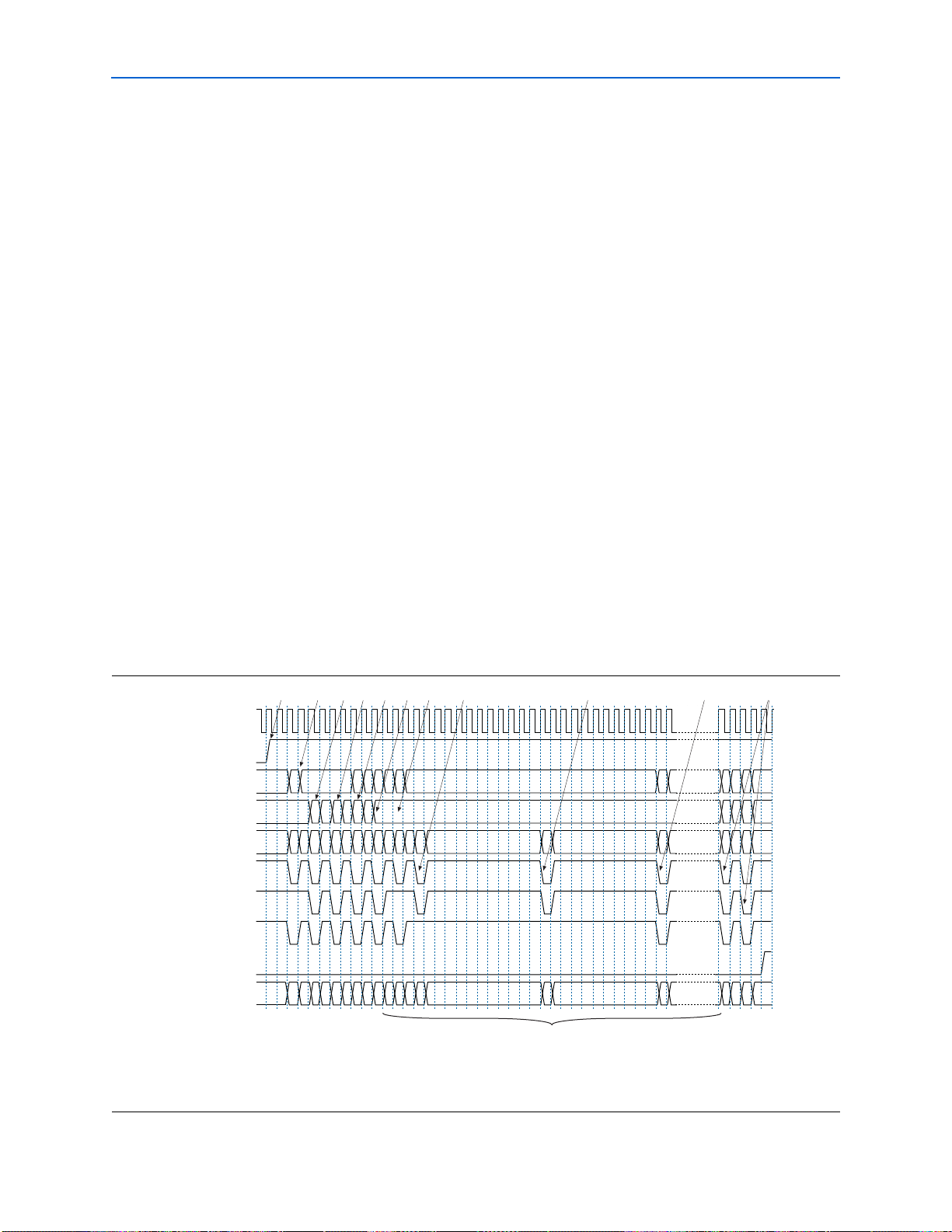

the read data at half rate. Figure 3–1 shows the generation of the resynchronization

clock which then clocks the HDR registers in the IOE. During calibration, the

sequencer determines whether to use the half-rate clock or the inverted half-rate clock

to capture the half-rate data.

(nonAFI)

Figure 3–1. Resynchronization Clock in QDR II+/QDR II SRAM ALTMEMPHY Megafunction

© January 2010 Altera Corporation External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

Page 18

3–2 Chapter 3: Functional Description—ALTMEMPHY (nonAFI)

Calibration start

Write 0's pattern to address 3

Write 1's pattern to address 5

Setup resync_clk_1x phase associated with

DQS group being calibrated

Read 0's pattern

Read 1's pattern

Start latency counter and search for

0's followed by 1's pattern

All DQS groups

calibrated?

Align all DQS groups to worst case latency

Calibration

successful

Ye s

No

Timed out for both

phases of

resync_clk_1x

Invert resync_clk_1x phase

No

Latency counter

timeout

Calibration

unsuccessful

Ye s

If pattern found

QDR II+/QDR II SRAM Calibration Process

The clock CQ coming from the QDR II+/QDR II SRAM is delayed and is divided by

two to generate a half-rate clock (resync_clk_1x). Data is captured on the rising

edges of the shifted CQ and shifted CQn signals. There is one resync_clk_1x per

DQS group. QDR II+/QDR II SRAM devices can only have one DQS group per

device, which means that there is one resync_clk_1x signal associated with each

memory device. This signal clocks the registers doing the full-rate to half-rate

conversion. It also clocks the front side of the read datapath clock-crossing FIFO.

There is one FIFO per DQS group (or memory device).

The resync_clk_1x signal can be inverted or not inverted. You can transfer data in

the correct byte order with one of these options. The main objective of calibration is to

find out whether the resync_clk_1x signal requires inversion, which is done by

loading the shift register, see Figure 3–1 (at most twice per QDR II+/QDR II SRAM

device). Each memory device is calibrated one after the other.

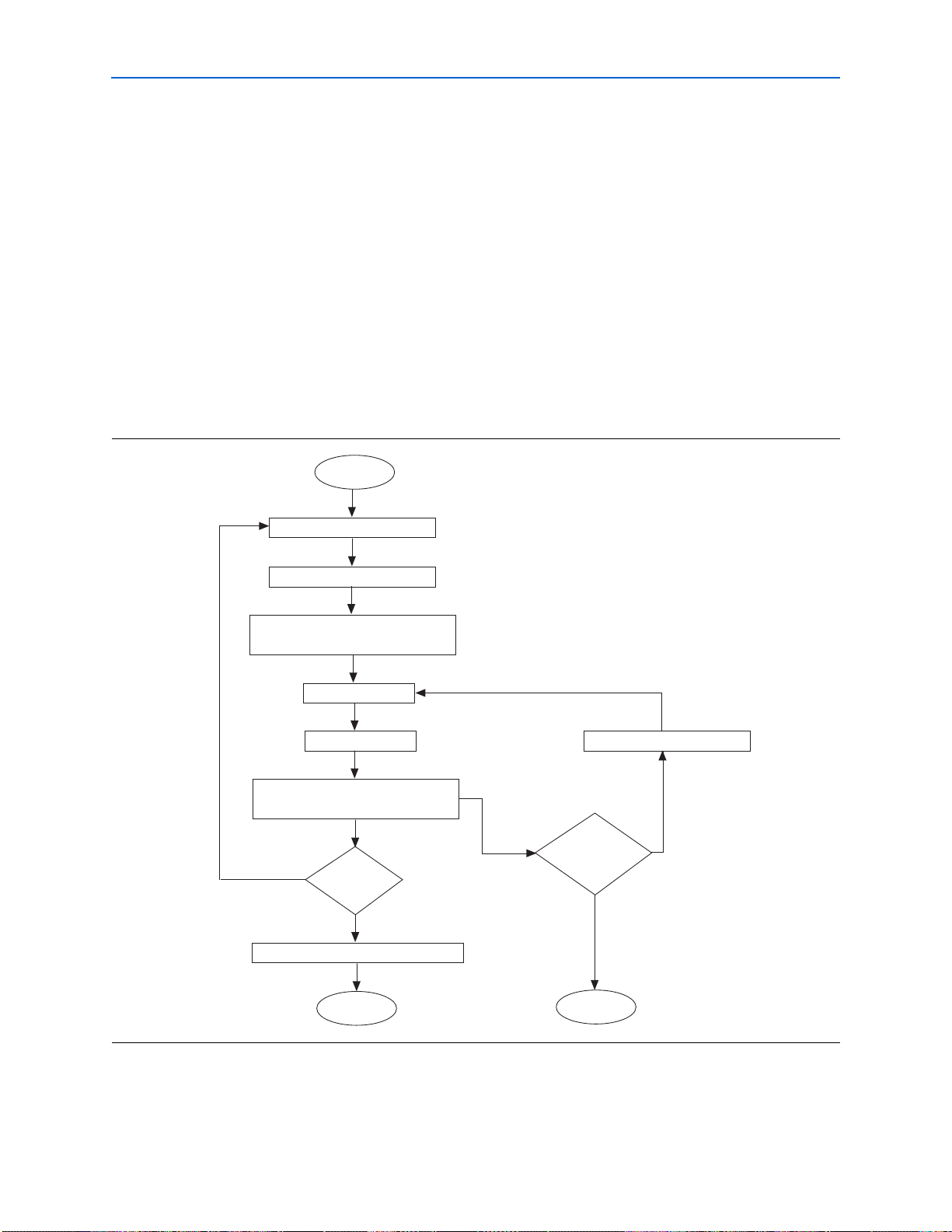

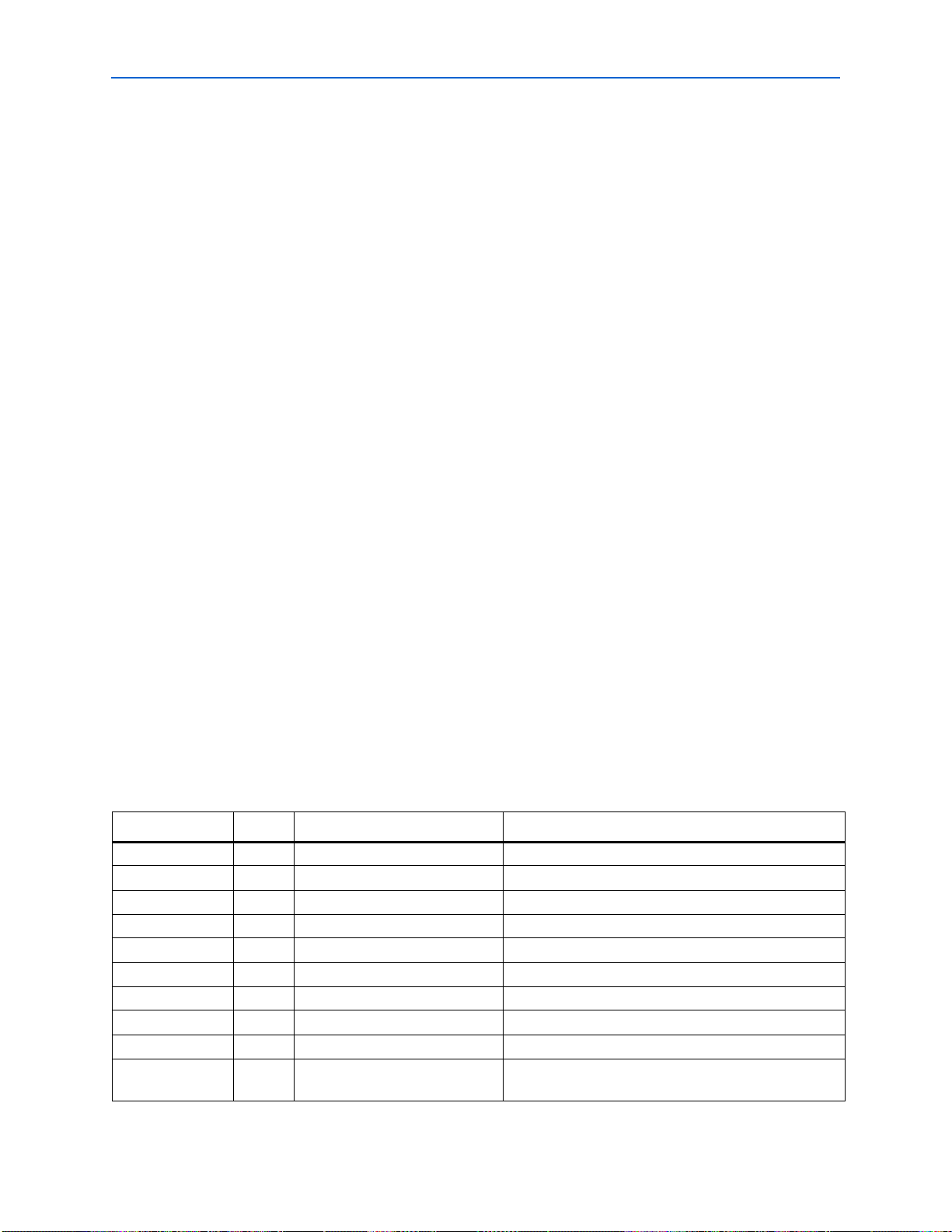

Figure 3–2 shows the QDR II+/QDR II SRAM calibration flowchart.

Figure 3–2. QDR II+/QDR II SRAM Calibration Flowchart

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide © January 2010 Altera Corporation

Page 19

Chapter 3: Functional Description—ALTMEMPHY (nonAFI) 3–3

QDR II+/QDR II SRAM Calibration Process

During the QDR II+/QDR II SRAM calibration, the sequencer first writes all 0s to

address space 3 in the external memory, followed by all 1s to address space 5. It then

loads the scan chain for the first time, to program the first setting for

resync_clk_1x.

The sequencer then starts reading 0s from address space 3 several times, followed by a

single read from address space 5 and starts the latency counter. If a pattern of all 0s

followed by all 1s is read before the latency counter reaches its time-out value (31

clock cycles), the latency value for that memory device is stored.

If all 0s followed by all 1s is not found when reading back from memory and the

latency count has reached the time-out value, the sequencer loads the scan chains a

second time to invert the resync_clk_1x signal. The sequencer then starts reading

from address space 3 several times, followed by a single read from address space 5 as

before and starts the latency counter again. If all 0s followed by all 1s are read back

from memory, the latency value for that memory device is stored.

1 The training pattern must be read back correctly on this second iteration (if it was not

already read correctly on the first iteration). If it is not read back correctly, it indicates

an underlying problem in the system.

The previous process is repeated until all memory devices are tested and a latency

value obtained for each device.

The latency values found for the different devices are compared with each other. If

necessary, they are aligned to the worst case latency (or to the user-requested

deterministic latency value if this option is used), which done by adjusting address

pointers in order to add latency to some of the read datapath RAMs inside the

ALTMEMPHY megafunction until the latency associated with all of the memory

devices is aligned to the worst case latency measured.

1 You cannot have a latency difference of more than two PHY clock cycles between all

the QDR II+/QDR II SRAM devices in non-deterministic latency mode.

When calibration has finished, the sequencer hands over control to the driver/user

logic, and generates the p_rdata_out_valid flag to indicate when read data is

valid. The sequencer also outputs the following signals upon completion of

calibration:

■ p_ready—Indicates completion of the calibration process (but does not mean

calibration was successful). This signal is renamed as the ctl_usr_mode_rdy

signal at the ALTMEMPHY top-level file.

■ p_calibration_successful—Indicates calibration was successfully

completed. This port is renamed resynchronisation_successful port at the

ALTMEMPHY top-level file.

■ p_user_defined_latency_ok—Indicates that the read latency requested by

the user was achievable, when using deterministic latency. This port is not

instantiated at the top-level of the file. Currently this signal exists at the

sequencer_wrapper file level only.

■ p_detectedlatency—Specifies the read latency achieved in phy_clk clock

cycles. This port is renamed ctl_rlat port at the ALTMEMPHY top-level file.

© January 2010 Altera Corporation External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

Page 20

3–4 Chapter 3: Functional Description—ALTMEMPHY (nonAFI)

User logic

(or example

driver)

Auto-calibration

Memory

Controller

Clock & reset

management

ALTMEMPHY

Addr &

Cmd Path

Write path

Read path

Ports named local_*

Ports named ctl_*

Ports named ctl_mem_*

Ports named mem_*

External

Memory

PHY-to-Controller Interfaces

VT tracking is not required because the read strobe from the QDR II+/QDR II SRAM

memory is continuous. So all registers in the I/O to the read RAM path are clocked

using a clock that is derived from the QDR II+/QDR II SRAM read clock.

1 For more information about the QDR II+/QDR II SRAM signals, refer to “QDR

II+/QDR II SRAM Signals” on page 3–20.

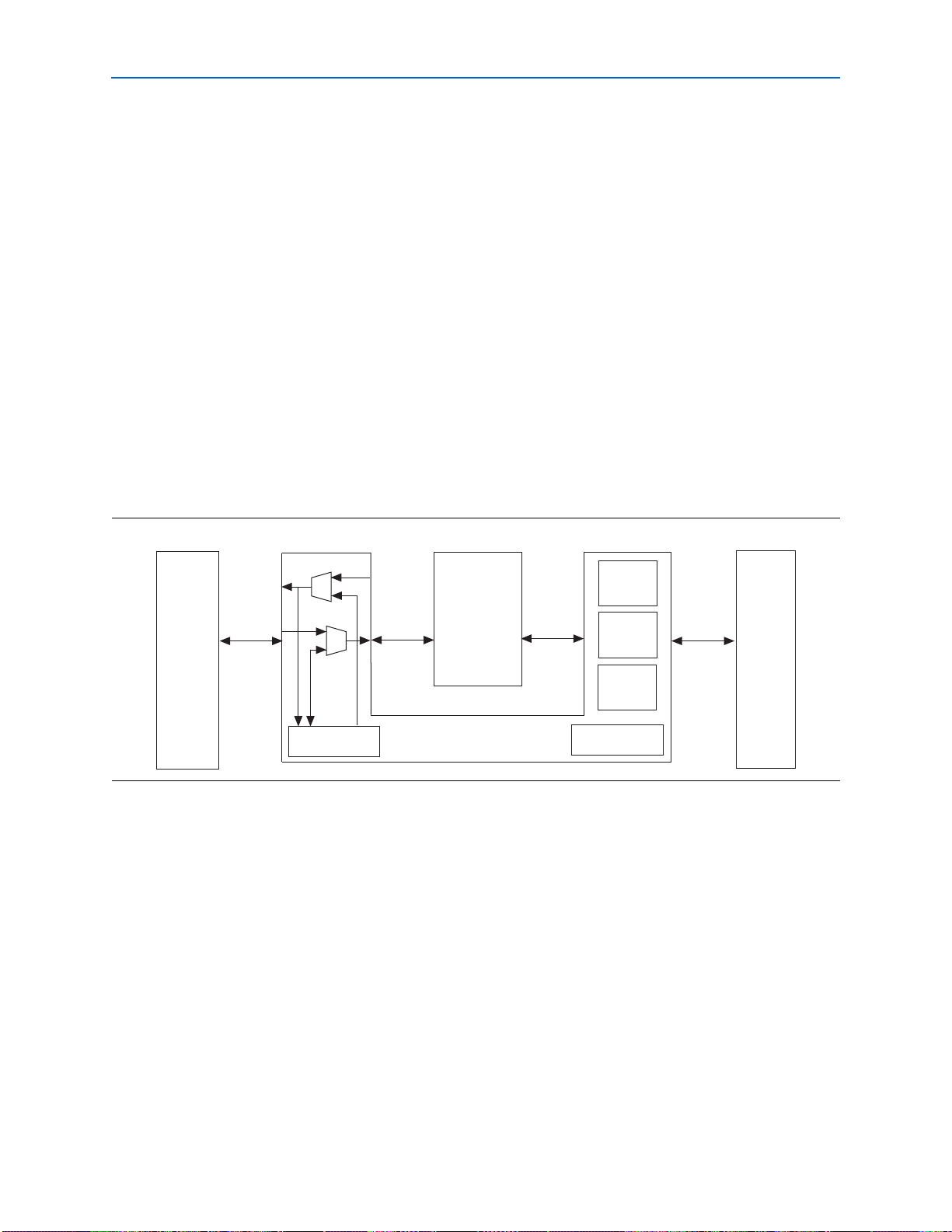

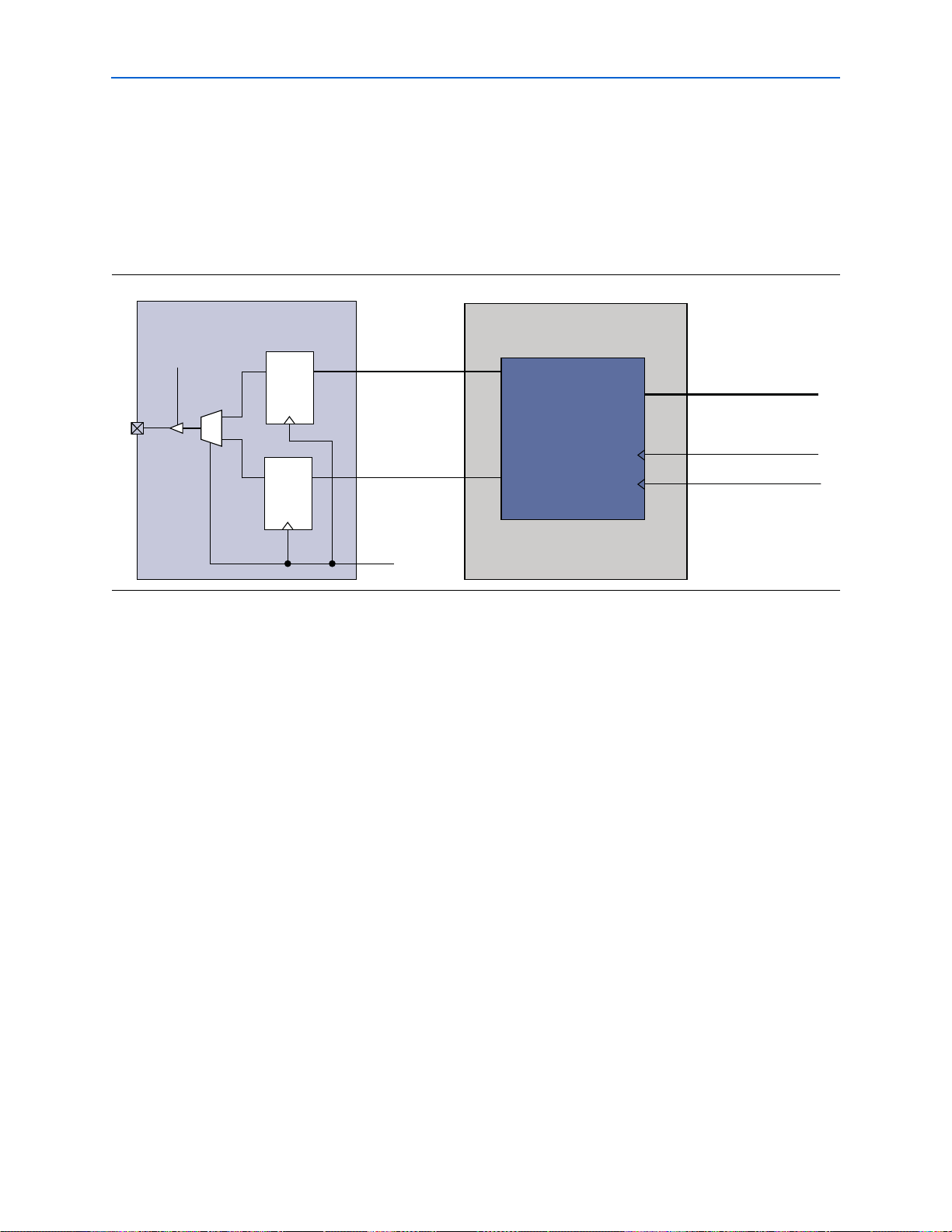

PHY-to-Controller Interfaces

The nonAFI’s autocalibration logic relies on the services of the memory controller to

perform its calibration writes, reads, and memory initialization, so it must have

control of the controller's local interface during the initial calibration stage. The

ALTMEMPHY megafunction has four interfaces that all must be connected

appropriately. Figure 3–3 shows the four interfaces.

1 As an SRAM, the PHY for QDR II+/QDR II SRAM lacks most of the ctl_ and

local_ ports as you can use a driver that acts as a controller to generate read and

write commands and data in the QDR II+/QDR II SRAM PHY.

Figure 3–3. The Four ALTMEMPHY Megafunction Interfaces

The four ALTMEMPHY interfaces, from left to right, are:

1. The local interface is the interface between the user logic and the memory

controller. The signals between user logic and the controller traverse through the

ALTMEMPHY megafunction. This can either be an Avalon

slave interface or a Native interface. All the ports on this interface have their

names prefixed with local_; for example, local_init_done. During the initial

calibration period, the auto-calibration logic takes control of this interface and

issues the write and read requests that the memory controller requires. When the

calibration process is complete, control is handed back to the user logic and

normal operation occurs. The ALTMEMPHY megafunction auto-calibration logic

does not require any further access to the memory controller when the initial

autocalibration is complete.

®

Memory-Mapped

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide © January 2010 Altera Corporation

Page 21

Chapter 3: Functional Description—ALTMEMPHY (nonAFI) 3–5

Initialization Timing

2. The ALTMEMPHY-controller local interface is the interface between the

ALTMEMPHY megafunction and the controller local interface. All the port names

on this interface are prefixed with ctl_; for example, ctl_init_done. This

interface connects the ALTMEMPHY megafunction to the controller’s local

interface and is of the same type as the local interface, either an Avalon-MM

interface or a native interface. When the calibration process is complete, this

connection becomes a straight-through connection and you have complete control

of the memory controller.

3. The ALTMEMPHY-controller command interface is the interface between the

controller and ALTMEMPHY. All the ports on this interface are prefixed with

ctl_mem_; for example, ctl_mem_rdata. They are clocked by the phy_clk.

This interface contains the memory control and address signals from the controller

to the memory. The controller also sends write data to, and receives read data

from, the external memory through this interface. All the signals on this interface

are clocked at the phy_clk rate. The ALTMEMPHY megafunction converts

between this clock and the memory interface clock.

4. The fourth interface is between the ALTMEMPHY megafunction and the external

memory devices and consists of the memory address, command, and data pins.

These must be connected directly to the external pins of your Altera FPGA.

Initialization Timing

DDR SDRAM initialization timing is different to DDR2 SDRAM initialization timing.

DDR SDRAM Initialization Timing

f For DDR2 SDRAM initialization timing, see “DDR2 SDRAM Initialization Timing” on

page 3–7.

The DDR SDRAM high-performance controller initializes the SDRAM devices by

issuing the following memory command sequence:

■ NOP (for 200 µs, programmable)

■ PCH

■ Extended LMR (ELMR)

■ LMR

■ NOP (for 200 clock cycles, fixed)

■ PCH

■ ARF

■ ARF

■ LMR

Figure 3–4 on page 3–6 shows a typical initialization timing sequence. The length of

time between the reset and the first PCH command should be 200 µs. The value that

you specify for the Memory initialization time at power up (tINIt) setting in the

MegaWizard interface is only used for hardware that you generate. The controller

simulation model is created with a much shorter t

© January 2010 Altera Corporation External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

time to make simulation easier.

INIT

Page 22

3–6 Chapter 3: Functional Description—ALTMEMPHY (nonAFI)

clk

ddr_cke

ddr_a

ddr_ba

ddr_cs_n

ddr_ras_n

ddr_cas_n

ddr_we_n

local_init_done

0 0

0 1 01

0 0 0 0 0 0 00

[1] [2] [3] [4] [6][5][5]

200 clock cycles

Key:

P = PCH

L = LMR

A = ARF

DDR Command P L L P A A LL

Initialization Timing

1 Do not set tINIT to zero.

Figure 3–4. DDR SDRAM Device Initialization Timing

The following sequence corresponds with the numbered items in Figure 3–4.

1. A PCH command is sent to all banks by setting the precharge pin, the address bit

a[10], or a[8] high.

2. An ELMR command is issued to enable the internal delay-locked loop (DLL) in the

memory devices. An ELMR command is an LMR command with the bank address

bits set to address the extended mode register.

3. An LMR command sets the operating parameters of the memory such as CAS

latency and burst length. This LMR command also resets the internal memory

device DLL. The DDR SDRAM high-performance controller allows 200 clock

cycles to elapse after a DLL reset and before it issues the next command to the

memory.

4. A further PCH command places all the banks in their idle state.

5. Two ARF commands must follow the PCH command.

6. The final LMR command programs the operating parameters without resetting the

DLL.

After issuing the final LMR command, the memory controller hands over control of

the memory to the ALTMEMPHY megafunction to allow it to carry out its calibration

process.

When the ALTMEMPHY megafunction has finished calibrating, the memory

controller asserts the local_init_done signal, which shows that it has initialized

the memory devices.

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide © January 2010 Altera Corporation

Page 23

Chapter 3: Functional Description—ALTMEMPHY (nonAFI) 3–7

Key:

P = PCH

L = LMR

A = ARF

clk

ddr_cke

ddr_a

ddr_ba

ddr_cs_n

ddr_ras_n

ddr_cas_n

ddr_we_n

local_init_done

DDR Command

2 0 3 0 1 0 0 1 0 1 11

0 0 0 0 0 0 0

P L L L L P A A L N L LL

200 clock cycles

[1] [2] [3] [3] [4] [7][6][5] [7] [8] [9]

Initialization Timing

DDR2 SDRAM Initialization Timing

The DDR2 SDRAM high-performance controller initializes the memory devices by

issuing the following command sequence:

■ NOP (for 200 µs, programmable)

■ PCH

■ ELMR, register 2

■ ELMR, register 3

■ ELMR, register 1

■ LMR

■ PCH

■ ARF

■ ARF

■ LMR

■ ELMR, register 1

■ ELMR, register 1

Figure 3–5 shows a typical DDR2 SDRAM initialization timing sequence, which is

described below. The length of time between the reset and the clock enable signal

going high should be 200 µs. The value that you choose for the Memory initialization

time at power up (tINIt) setting in the MegaWizard interface is only used for

hardware that you generate. The controller simulation model is created with a much

shorter t

time to make simulation easier.

INIT

Figure 3–5. DDR2 SDRAM Device Initialization Timing

Note to Figure 3–5:

(1) local_init_done only goes high when calibration has completed.

© January 2010 Altera Corporation External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

Page 24

3–8 Chapter 3: Functional Description—ALTMEMPHY (nonAFI)

Initialization Timing

The following sequence corresponds with the numbered items in Figure 3–5 on

page 3–7.

1. The clock enable signal (CKE) is asserted 200 µs after coming out of reset.

2. The controller then waits 400 ns and then issues the first PCH command by setting

the precharge pin, the address bit a[10] or a[8] high. The 400 ns is calculated by

taking the number of clock cycles calculated by the wizard for the 200 µs delay and

dividing this by 500. If a small initialization time is selected for simulation

purposes, this delay is always at least 1 clock cycle.

3. Two ELMR commands are issued to load extend mode registers 2 and 3 with

zeros.

4. An ELMR command is issued to extend mode register 1 to enable the internal DLL

in the memory devices.

5. An LMR command is issued to set the operating parameters of the memory such

as CAS latency and burst length. This LMR command is also used to reset the

internal memory device DLL.

6. A further PCH command places all the banks in their idle state.

7. Two ARF commands must follow the PCH command.

8. A final LMR command is issued to program the operating parameters without

resetting the DLL.

9. 200 clock cycles after step 5, two ELMR commands are issued to set the memory

device off-chip driver (OCD) impedance to the default setting.

After issuing the final ELMR command, the memory controller hands over control of

the memory to the ALTMEMPHY megafunction to allow it to carry out its calibration

process.

When ALTMEMPHY megafunction has finished calibrating, the memory controller

asserts the local_init_done signal, which shows that it has initialized the memory

devices.

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide © January 2010 Altera Corporation

Page 25

Chapter 3: Functional Description—ALTMEMPHY (nonAFI) 3–9

ALTMEMPHY Signals

ALTMEMPHY Signals

This section describes the ALMEMPHY megafunction signals for the following

interfaces:

■ DDR2 and DDR SDRAM signals

■ QDR II+ and QDR II SRAM signals

DDR2 and DDR SDRAM Signals

Tab le 3– 1 through Table 3–10 show the signals for DDR2 and DDR SDRAM nonAFIs.

The signal lists include the following signal groups:

■ I/O interface to the external memory device

■ Clock and reset signals

■ PLL reconfiguration signals

■ External DLL signals

■ User-mode calibrated on-chip termination (OCT) control signals

■ Interface to the memory controller

■ Local interface signals

■ Datapath interface for the controller

■ ALTMEMPHY megafunction calibration status interface

■ Additional calibration signals from the sequencer

1 Ports with the prefix “mem_” connect the PHY with the memory device; ports with the

prefix “ctl_” connect the PHY with the controller. Ports with prefix “ctl_mem_”

indicate the datapath for the controller; ports with the prefix “local_” indicate the

signal to be connected with the example driver or user logic.

1 Signals with suffix _n are active low; signals without suffix _n are active high.

Table 3–1. I/O Interface for DDR2 and DDR SDRAM—nonAFI (Note 1) (Part 1 of 2)

Signal Name Type Width Description

mem_addr output MEM_IF_ROWADDR_WIDTH The memory row and column address bus.

mem_ba output MEM_IF_BANKADDR_WIDTH The memory bank address bus.

mem_cas_n output 1 The memory column address strobe.

mem_cke output MEM_IF_CS_WIDTH The memory clock enable.

mem_clk bidir MEM_IF_CLK_PAIR_COUNT The memory clock, positive edge clock. (2)

mem_clk_n bidir MEM_IF_CLK_PAIR_COUNT The memory clock, negative edge clock. (2)

mem_cs_n output MEM_IF_CS_WIDTH The memory chip select signal.

mem_dm output MEM_IF_DM_WIDTH The optional memory data mask bus.

mem_dq bidir MEM_IF_DWIDTH The memory bidirectional data bus.

mem_dqs bidir MEM_IF_DWIDTH /

The memory bidirectional data strobe bus.

MEM_IF_DQ_PER_DQS

© January 2010 Altera Corporation External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

Page 26

3–10 Chapter 3: Functional Description—ALTMEMPHY (nonAFI)

ALTMEMPHY Signals

Table 3–1. I/O Interface for DDR2 and DDR SDRAM—nonAFI (Note 1) (Part 2 of 2)

Signal Name Type Width Description

mem_dqsn bidir MEM_IF_DWIDTH /

MEM_IF_DQ_PER_DQS

The memory bidirectional data strobe bus. Not used in

Arria GX, HardCopy II, Stratix II, and Stratix II GX

designs.

mem_odt output MEM_IF_CS_WIDTH The memory on-die termination control signal.

mem_ras_n output 1 The memory row address strobe.

mem_reset_n output 1 The memory-reset signal.

mem_we_n output 1 The memory write-enable signal.

Notes to Table 3–1:

(1) Connected to I/O pads.

(2) Output is for memory device, and input path is fed back to ALTMEMPHY megafunction for VT tracking.

Table 3–2. Clock and Reset Signals for DDR2/DDR SDRAM—nonAFI (Note 1) (Part 1 of 2)

Signal Name Type Width Description

global_reset_n (1) input 1 The asynchronous reset input to the controller. All other

reset signals are derived from resynchronized versions of

this. This signal holds the complete ALTMEMPHY

megafunction, including the PLL, in reset while low.

soft_reset_n (1) input 1 The asynchronous reset input to reset controller, for

SOPC Builder use, or to be controlled by other system

reset logic. This signal causes a complete reset of the

PHY, but not the PLL in the PHY. In Arria GX, Stratix II,

and Stratix II GX devices, this signal also resets the PLL

reconfiguration block on a falling-edge detection.

phy_clk output 1 The ALTMEMPHY megafunction half-rate clock provided

to the user. All user inputs and outputs to the

ALTMEMPHY megafunction are synchronous to this clock

in half-rate designs. However, this clock is not used in

full-rate designs.

pll_ref_clk input 1 The reference clock input to PLL.

reset_phy_clk_n (1) output 1 Asynchronous reset, that is de-asserted synchronously

with respect to the associated phy_clock clock

domain. Use this to reset any additional user logic on that

clock domain.

reset_request_n (1) output 1 Directly connected to the locked output of the PLL and is

intended for optional use either by automated tools such

as SOPC Builder or could be manually ANDed with any

other system-level signals and combined with any edge

detect logic as required and then fed back to the

global_reset_n input.

Reset request output that indicates when the PLL outputs

are not locked. Use this as a reset request input to any

system-level reset controller you may have. This signal is

always low while the PLL is locking (but not locked), and

so any reset logic using it is advised to detect a reset

request on a falling-edge rather than by level detection.

aux_half_rate_clk output 1 A copy of the phy_clk_1x signal that you can use in

other parts of your design, same as phy_clk port.

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide © January 2010 Altera Corporation

Page 27

Chapter 3: Functional Description—ALTMEMPHY (nonAFI) 3–11

ALTMEMPHY Signals

Table 3–2. Clock and Reset Signals for DDR2/DDR SDRAM—nonAFI (Note 1) (Part 2 of 2)

Signal Name Type Width Description

aux_full_rate_clk output 1 A copy of the mem_clk_2x signal that you can use in

other parts of your design.

Note to Table 3–2:

(1) Refer to Figure 4–3 for the reset mechanism in Arria GX, Cyclone III, Stratix II and Stratix II GX devices.

The ports in Ta bl e 3 –3 exists for all DDR2/DDR SDRAM variations.

Table 3–3. PLL Reconfiguration Signals for DDR2 and DDR SDRAM—nonAFI

Signal Name Type Width Description

pll_reconfig_

enable

input 1 Allows access to the PLL reconfiguration block. Hold this

signal low in normal operation. While the ALTMEMPHY is held

in reset (via the soft_reset_n signal), and the

reset_request_n signal is 1, it is safe to reconfigure the

PLL. To reconfigure the PLL, set this signal to 1 and use the

other pll_reconfig signals to access the PLL. When

finished reconfiguring, set this signal to 0, and then set the

soft_reset_n signal to 1 to bring the ALTMEMPHY out of

reset. For this signal to work, the

PLL_RECONFIG_PORTS_EN parameter must be set to

TRUE.

pll_reconfig_

write_param

pll_reconfig_read

_param

input 1 For more information, refer to the Phase-Locked Loop

(ALTPLL_RECONFIG) User Guide.

input 1 For more information, refer to the Phase-Locked Loop

(ALTPLL_RECONFIG) User Guide.

pll_reconfig input 1 For more information, refer to the Phase-Locked Loop

(ALTPLL_RECONFIG) User Guide.

pll_reconfig_

counter_type

pll_reconfig_

counter_param

pll_reconfig_data

_in

pll_reconfig_soft

_reset_en_n

input 4 For more information, refer to the Phase-Locked Loop

(ALTPLL_RECONFIG) User Guide.

input 3 For more information, refer to the Phase-Locked Loop

(ALTPLL_RECONFIG) User Guide.

input 9 For more information, refer to the Phase-Locked Loop

(ALTPLL_RECONFIG) User Guide.

input 1 The asynchronous reset input to the PLL reconfiguration

block. This reset causes a PLL reconfiguration block reset and

holds the reset if the ALTMEMPHY megafunction in reset while

the signal is low. This port only exists in the DDR2/DDR

SDRAM variation for Arria GX, Stratix II, and Stratix II GX

devices.

pll_reconfig_busy output 1 For more information, refer to the Phase-Locked Loop

(ALTPLL_RECONFIG) User Guide.

pll_reconfig_data

_out

output 9 For more information, refer to the Phase-Locked Loop

(ALTPLL_RECONFIG) User Guide.

pll_reconfig_clk output 1 Synchronous clock to use for any logic accessing the PLL

reconfiguration interface.

pll_reconfig_

reset

output 1 Resynchronized reset to use for any logic accessing the PLL

reconfiguration interface.

© January 2010 Altera Corporation External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

Page 28

3–12 Chapter 3: Functional Description—ALTMEMPHY (nonAFI)

ALTMEMPHY Signals

Table 3–4. External DLL Signals for DDR2 and DDR SDRAM—nonAFI

Signal Name Type Width Description

dqs_delay_ctrl_

export

output 6 Allows sharing DLL in this ALTMEMPHY instance with another

ALTMEMPHY instance. Connect the

dqs_delay_ctrl_export port on the ALTMEMPHY

instance with a DLL to the dqs_delay_ctrl_import port

on the other ALTMEMPHY instance.

dqs_delay_ctrl_

import

input 6 Allows the use of DLL in another ALTMEMPHY instance in this

ALTMEMPHY instance. Connect the

dqs_delay_ctrl_export port on the ALTMEMPHY

instance with a DLL to the dqs_delay_ctrl_import port

on the other ALTMEMPHY instance.

dll_reference_

clk

output 1 Reference clock to feed to an externally instantiated DLL. This

clock is typically from one of the PHY PLL outputs.

The ports listed in Ta bl e 3 –5 only exist when you target Stratix III and Stratix IV

devices. You can leave them unconnected if you are not using user-mode calibrated

OCT. For more information about StratixIII and StratixIV ports, refer to

ALTMEMPHY Signals section in chapter 5 of the DDR and DDR2 SDRAM

High-Performance Controllers and ALTMEMPHY IP User Guide.

Table 3–5. User-Mode Calibrated OCT Control Signals for DDR2/DDR SDRAM—nonAFI (Note 1), (2)

Signal Name Type Width Description

oct_ctl_rs_value input 14 Specifies serial termination value. Connects to the

seriesterminationcontrol bus of the ALT_OCT

megafunction. This port exists when you target Stratix IV and

Stratix III devices only.

oct_ctl_rt_value input 14 Specifies parallel termination value. Connects to the

parallelterminationcontrol bus of the ALT_OCT

megafunction. This port exists when you target Stratix IV and

Stratix III devices only.

Notes to Table 3–5:

(1) These ports are available if you want to use user-mode OCT calibration. Otherwise, they can be left unconnected.

(2) For more information on OCT, see the ALT_OCT Megafunction User Guide.

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide © January 2010 Altera Corporation

Page 29

Chapter 3: Functional Description—ALTMEMPHY (nonAFI) 3–13

ALTMEMPHY Signals

Table 3–6. Interface to the Memory Controller for DDR2 and DDR SDRAM—nonAFI (Note 1) (Part 1 of 3)

Signal Name Type Width Description

ctl_add_1t_ac_lat input 1 When asserted, one extra address and command

clock cycle (1T) of latency is inserted in the address

and command path if the ADDR_CMD_ADD_1T

parameter is set to EXT_SELECT, see “Handshake

Mechanism Between Write Commands and Write

Data” on page 3–49.

For DDR SDRAM, the write latency is fixed at one

memory clock cycle, but for DDR2 SDRAM, this

value changes with the read CAS latency. As the

controller is running at half the rate of the memory

clock, a latency change of one controller clock cycle

is two memory clock cycles. The ALTMEMPHY

megafunction allows you to dynamically insert an

extra memory clock of delay in the address and

command path to compensate.

The insertion of delay is controlled by the

ADDR_CMD_ADD_1T parameter and the

ctl_add_1t_ac_lat signal. If

ADDR_CMD_ADD_1T is set to the string

EXT_SELECT, an extra cycle of latency can be

dynamically inserted on the address and command

outputs by asserting the ctl_add_1t_ac_lat

input, which allows run-time control of the address

and command latency. If ADDR_CMD_ADD_1T is

set to the string value TRUE, the extra clock cycle of

latency is always present. If it is set to the string

value FALSE, the extra latency is never added.

ctl_add_intermediate_

regs

Input 1 When asserted, an additional intermediate register or

registers is included in the address and command

path if the

ADDR_CMD_ADD_INTERMEDIATE_REGS

parameter is set to EXT_SELECT.

For Stratix II and Cyclone III devices only, to maintain

the clock cycle relationship between

address/command and the write data. You must

include the address/command phases where

required.

ctl_address output LOCAL_IF_

AWIDTH

The address corresponding to a write or read

request. The ALTMEMPHY sequencer logic drives

ctl_address during calibration. ctl_address

has the same timing as local_address.

ctl_be output LOCAL_IF_

DWIDTH/8

The output to the controller indicating the

byte-enable flags. The ALTMEMPHY sequencer logic

drives ctl_be during calibration. ctl_be is

mandatory and has the same timing as local_be.

© January 2010 Altera Corporation External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

Page 30

3–14 Chapter 3: Functional Description—ALTMEMPHY (nonAFI)

ALTMEMPHY Signals

Table 3–6. Interface to the Memory Controller for DDR2 and DDR SDRAM—nonAFI (Note 1) (Part 2 of 3)

Signal Name Type Width Description

ctl_doing_rd input 1 The active-high signal from the controller specifying

that a read command has been issued to the external

RAM.

For more information, see “Handshake Mechanism

Between Read Commands and Read Data” on

page 3–47.

ctl_init_done input 1 The memory controller drives this active-high signal

to specify that the controller has initialized the

memory and the calibration process should begin.

ctl_negedge_en input 1 This signal is used if ADDR_CMD_NEGEDGE_EN is

set to EXT_SELECT. If true, the address and

command signals are output on the falling edge of

the address and command clock, ac_clk_2x. If

false, the address and command signals are output

on the rising edge of the address and command

clock. When set to EXT_SELECT, the

ctl_negedge_en top level input determines

whether the edge is used.

ctl_read_req output 1 The active-high signal requesting a read command to

the address on the ctl_address bus.

ctl_ready input 1 The controller-ready signal which indicates that the

currently asserted read or write request has been

accepted. The address of the request is sampled

when both the ready and request signals are high.

ctl_size output LOCAL_

BURST_LEN_

BITS

The output to the controller indicating the size

(length) of the burst transfer, fixed at 1 for this

version.

ctl_usr_mode_rdy output 1 The ALTMEMPHY sequencer logic drives this

active-high signal to specify the ALTMEMPHY has

finished its calibration and is ready to accept user

read or write requests.

ctl_wdata output LOCAL_IF_

DWIDTH

The write data from the ALTMEMPHY to the

controller. The ALTMEMPHY sequencer logic drives

ctl_wdata during calibration. ctl_wdata has

the same timing as local_wdata.

ctl_wdata_req input 1 The controller-request for write data; not required

when the controller has an Avalon-MM interface.

The memory controller that the ALTMEMPHY

sequencer uses during calibration drives

ctl_wdata_req. Same timing as

local_wdata_req.

ctl_write_req output 1 The active-high signal specifying that a write

command should be issued to the address on the

ctl_address signal. The ALTMEMPHY

sequencer logic drives ctl_write_req during

calibration. Same timing as local_write_req.

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide © January 2010 Altera Corporation

Page 31

Chapter 3: Functional Description—ALTMEMPHY (nonAFI) 3–15

ALTMEMPHY Signals

Table 3–6. Interface to the Memory Controller for DDR2 and DDR SDRAM—nonAFI (Note 1) (Part 3 of 3)

Signal Name Type Width Description

ctl_refresh_ack input 1 The active-high valid signal from the controller

acknowledging the refresh request. The

ALTMEMPHY sequencer logic uses

ctl_refresh_ack during calibration.

ctl_refresh_req output 1 The output to the controller requesting a refresh.

Same timing as local_refresh_req.

ctl_burstbegin output 1 The output to the controller indicating the start of a

burst. Only available for the Avalon-MM interface.

ctl_rdata input LOCAL_IF_

DWIDTH

The read data from the controller. The ALTMEMPHY

sequencer logic uses ctl_rdata during

calibration. ctl_rdata has the same timing as

local_rdata.

ctl_rdata_valid input 1 The active-high valid signal for the controller read

data. Asserted coincident with the read data on

ctl_rdata. The controller drives

ctl_rdata_valid and has the same timing as

local_rdata_valid.

ctl_add_1t_odt_lat input 1 When asserted, one extra address and command

clock cycle (1T) of latency is inserted in the address

and command ODT path if ODT_ADD_1T is set to

EXT_SELECT, see “Handshake Mechanism

Between Write Commands and Write Data” on

page 3–49.

The timing of the mem_odt signal can be controlled

in the same way as mem_addr, but is independent

of the address and command latency. If the

ODT_ADD_1T parameter is set to EXT_SELECT,

an extra cycle of latency can be dynamically inserted

on the ODT command outputs by asserting the

ctl_add_1t_odt_lat input, which allows

separate run-time control of the latency of the ODT

signal. If ODT_ADD_1T is set to TRUE, the extra

clock cycle of latency is always present. If

ODT_ADD_1T is set to FALSE, the extra latency is

never added.

ctl_rlat output READ_LAT_

WIDTH

Unused port that exists when you target Stratix IV

and Stratix III devices. The default

READ_LAT_WIDTH is set to 4.

ctl_self_rfsh_ack input 1 Signal from the Altera high-performance controller

ctl_powerdn_ack input 1

that is passed through the PHY.

ctl_autopch_req output 1

ctl_powerdn_req output 1

ctl_self_rfsh_req output 1

Note to Table 3–6:

(1) Interface signals to the controller either through the sequencer or user interface.

© January 2010 Altera Corporation External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

Page 32

3–16 Chapter 3: Functional Description—ALTMEMPHY (nonAFI)

ALTMEMPHY Signals

Table 3–7. Local Interface Signals for DDR2 and DDR SDRAM—nonAFI (Part 1 of 2) (Note 1)

Signal Name Type Width Description

local_address input LOCAL_IF_

AWIDTH

local_be input LOCAL_IF_

DWIDTH / 8

The address corresponding to a write or read

request.

The input to ALTMEMPHY megafunction indicating

the byte-enable flags.

local_read_req input 1 The active-high signal requesting a read command

to the address on the ctl_address bus.

local_ready output 1 The controller-ready signal which indicates that the

currently asserted read or write request has been

accepted. The address of the request is sampled

when both the ready and request signals are high.

local_size input LOCAL_

BURST_LEN_

The controller signal to indicate the size (length) of

the burst transfer, fixed at 1 for this version.

BITS

local_wdata input LOCAL_IF_

DWIDTH

The write data from the user to the ALTMEMPHY

megafunction.

local_wdata_req output 1 The controller request for write data; not required

when the controller has an Avalon-MM interface.

local_write_req input 1 The active-high signal specifying that a write

command should be issued to the address on the

ctl_address signal.

local_refresh_req input 1 The ALTMEMPHY megafunction receives refresh

requests from the local interface and passes them to

the controller via ctl_refresh_req when in

user mode (ctl_usr_mode output is high).

local_burstbegin input 1 The ALTMEMPHY megafunction receives the

burstbegin signal from the local interface and

passes it to the controller via ctl_burstbegin

when in user mode (ctl_usr_mode output is

high).

local_rdata output LOCAL_IF_

DWIDTH

When ctl_usr_mode is high, this output passes

through the read data from the controller to the local

interface. Otherwise, it is tied low.

local_rdata_valid output 1 When ctl_usr_mode is high, this output passes

through the read data valid signal

(ctl_rdata_valid) from the controller to the

local interface. Otherwise, it is driven low.

local_init_done output 1 When ctl_usr_mode is high, this output passes

through the controller’s initialization done signal

(ctl_init_done) from the controller to the local

interface. Otherwise, it is driven low.

local_refresh_ack output 1 When ctl_usr_mode is high, this output passes

through the controller’s refresh acknowledge signal

(ctl_refresh_ack) from the controller to the

local interface. Otherwise, it is driven low.

local_autopch_req input 1 User control for auto precharge to request the

controller to issue an autoprecharge write or

autoprecharge read command.

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide © January 2010 Altera Corporation

Page 33

Chapter 3: Functional Description—ALTMEMPHY (nonAFI) 3–17

ALTMEMPHY Signals

Table 3–7. Local Interface Signals for DDR2 and DDR SDRAM—nonAFI (Part 2 of 2) (Note 1)

Signal Name Type Width Description

local_powerdn_req input 1 User control to power down the memory device to

request the controller to place the memory devices

into a power-down state as soon as it can without

violating the relevant timing parameters and

responds by asserting the local_powerdn_ack

signal.

local_self_rfsh_req input 1 User control of the self-refresh feature to request

that the controller place the memory devices into a

self-refresh state by asserting this signal.

local_self_rfsh_ack output 1 Self-refresh request acknowledge signal. This signal

is asserted and deasserted in response to the

local_self_rfsh_req signal from the user.

local_powerdn_ack output 1 Power-down request acknowledge signal. This

signal is asserted and deasserted in response to the

local_powerdn_req signal from the user.

Note to Table 3–7:

(1) Passed through PHY to the controller.

Table 3–8. Datapath Interface for DDR2 and DDR SDRAM—nonAFI (Part 1 of 3) (Note 1)

Signal Name Type Width Description

ctl_mem_addr_h (1) input MEM_IF_

ROWADDR_

WIDTH

The row or column address that is sent to the

external memory. Output during the high halfperiod of the address and command clock and

driven by the memory controller.

ctl_mem_addr_l (1) input MEM_IF_

ROWADDR_

WIDTH

The row or column address that is sent to the

external memory. Output during the low half-period

of the address and command clock and driven by

the memory controller.

ctl_mem_ba_h (1) input MEM_IF_

BANKADDR_

WIDTH

The bank address that is sent to the external

memory. Output during the high half-period of the

address and command clock and driven by the

memory controller.

ctl_mem_ba_l (1) input MEM_IF_

BANKADDR_

WIDTH

The bank address that is sent to the external

memory. Output during the low half-period of the

address and command clock and driven by the

memory controller.

ctl_mem_be input LOCAL_IF_

DWIDTH/8

The optional byte-enable signals for the write data

to the external memory. The ALTMEMPHY

megafunction converts the byte enables into

memory mem_dm signals. If mem_dm pins are not

required (mem_dm_pins set to FALSE), the

mem_dm logic is not generated and the mem_dm

pins are not instantiated.

ctl_mem_cas_n_h (1) input 1 The column-address strobe signal from the

controller to the memory. Output during the high

half-period of the address and command clock and

driven by the memory controller.

© January 2010 Altera Corporation External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

Page 34

3–18 Chapter 3: Functional Description—ALTMEMPHY (nonAFI)

ALTMEMPHY Signals

Table 3–8. Datapath Interface for DDR2 and DDR SDRAM—nonAFI (Part 2 of 3) (Note 1)

Signal Name Type Width Description

ctl_mem_cas_n_l (1) input 1 The column-address strobe signal from the

controller to the memory. Output during the low

half-period of the address and command clock and

driven by the memory controller.

ctl_mem_cke_h (1) input MEM_IF_CS_

WIDTH

The clock-enable signal from the controller to the

memory. Output during the high half-period of the

address and command clock and driven by the

memory controller.

ctl_mem_cke_l (1) input MEM_IF_CS_

WIDTH

The clock-enable signal from the controller to the

memory. Output during the low half-period of the

address and command clock and driven by the

memory controller.

ctl_mem_cs_n_h (1) input MEM_IF_CS_

WIDTH

The chip-select signal from the controller to the

memory. For half-rate designs, always tie

ctl_mem_cs_n_h high, as even with 2T

addressing, the chip select is only driven for the

second clock cycle, to allow an extra clock cycle of

setup time for the other address and command

signals. Output during the high half-period of the

address and command clock and driven by the

memory controller

ctl_mem_cs_n_l (1) input MEM_IF_CS_

WIDTH

The chip-select signal from the controller to the

memory. Output during the low half-period of the

address and command clock and driven by the

memory controller.

ctl_mem_dqs_burst input 1 Controls the DQS output enables of the DQS pins.

ctl_mem_odt_h (1) input MEM_IF_CS_

WIDTH

ctl_mem_odt_l (1) input MEM_IF_CS_

WIDTH

The on-die termination signal from the controller to

the memory.

The on-die termination signal from the controller to

the memory.

ctl_mem_ras_n_h (1) input 1 The row-address strobe signal from the controller

to the memory. Output during the high half-period

of the address and command clock and driven by

the memory controller.

ctl_mem_ras_n_l (1) input 1 The row-address strobe signal from the controller

to the memory. Output during the low half-period of

the address and command clock and driven by the

memory controller.

ctl_mem_rdata output LOCAL_IF_

DWIDTH

ctl_mem_rdata_valid output 1

The ctl_mem_rdata signal is the captured,

resynchronized, and demultiplexed read data from

the ALTMEMPHY megafunction to the controller.

The ctl_mem_rdata_valid signal Indicates

when the ctl_mem_rdata is valid.

For more information, see “Handshake Mechanism

Between Read Commands and Read Data” on

page 3–47.

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide © January 2010 Altera Corporation

Page 35

Chapter 3: Functional Description—ALTMEMPHY (nonAFI) 3–19

ALTMEMPHY Signals

Table 3–8. Datapath Interface for DDR2 and DDR SDRAM—nonAFI (Part 3 of 3) (Note 1)

Signal Name Type Width Description

ctl_mem_wdata input MEM_IF_

DWIDTH×

DWIDTH_

RATIO

The write data bus, which has valid data in the same

clock cycles that control_wdata_valid is

asserted, see “Handshake Mechanism Between

Read Commands and Read Data” on page 3–47.

ctl_mem_wdata_valid input 1 Generates the mem_dq output enable. When

asserted, the ctl_mem_rdata_valid signal

indicates that the coincident read data on

ctl_mem_rdata is valid.

ctl_mem_we_n_h (1) input 1 The write-enable signal from the controller to the

memory. Output during the high half-period of the

address and command clock and driven by the

memory controller.

ctl_mem_we_n_l (1) input 1 The write-enable signal from the controller to the

memory. Output during the low half-period of the

address and command clock and driven by the

memory controller.

Note to Table 3–8:

(1) The “_h” and “_l” stand for high and low. They signify in which half of the clock cycle the data is output. The _h data is output when the

corresponding clock, for example ac_clk_2x, is high. The _l data is output when the ac_clk_2x clock is low. The signals with _h and

_l allow you to select between 1T and 2T addressing. For half-rate designs, 1T is where the address and command signals are driven for one

clock; 2T is where they are driven for 2 clocks. For full-rate designs, ensure the same signal drives both _h and _l signals and 2T addressing

is used. Also when high-performance controllers use ALTMEMPHY, 2T addressing is used.

Table 3–9. Calibration Status Interface for DDR2 and DDR SDRAM—nonAFI

Signal Name Type Width Description

resynchronisation_

successful

output 1 Active-high signal that is set to indicate that

calibration of the read data resynchronization clock

phase was completed and successful.

postamble_successful output 1 Active-high signal that is set to indicate that read

postamble calibration was completed.

tracking_successful output 1 Active-high signal that is set to indicate the

completion of mimic path VT variation tracking

operation.