Page 1

Embedded Peripheral IP User Guide

Subscribe

Send Feedback

UG-01085

2014.24.07

101 Innovation Drive

San Jose, CA 95134

www.altera.com

Page 2

TOC-2

Contents

Introduction........................................................................................................ 1-1

SDRAM Controller Core.....................................................................................2-1

Tool Support.................................................................................................................................................1-1

Obsolescence.................................................................................................................................................1-1

Device Support.............................................................................................................................................1-2

Document Revision History.......................................................................................................................1-2

Core Overview..............................................................................................................................................2-1

Functional Description............................................................................................................................... 2-1

Avalon-MM Interface......................................................................................................................2-2

Off-Chip SDRAM Interface............................................................................................................2-2

Board Layout and Pinout Considerations....................................................................................2-3

Performance Considerations..........................................................................................................2-4

Configuration............................................................................................................................................... 2-4

Memory Profile Page.......................................................................................................................2-5

Timing Page......................................................................................................................................2-6

Hardware Simulation Considerations.......................................................................................................2-7

SDRAM Controller Simulation Model.........................................................................................2-7

SDRAM Memory Model.................................................................................................................2-7

Example Configurations............................................................................................................................. 2-8

Software Programming Model...................................................................................................................2-9

Clock, PLL and Timing Considerations................................................................................................... 2-9

Factors Affecting SDRAM Timing................................................................................................2-9

Symptoms of an Untuned PLL.....................................................................................................2-10

Estimating the Valid Signal Window..........................................................................................2-10

Example Calculation......................................................................................................................2-11

Document Revision History.....................................................................................................................2-13

Tri-State SDRAM................................................................................................ 3-1

Altera Corporation

Feature Description..................................................................................................................................... 3-1

Block Diagram..................................................................................................................................3-2

Configuration Parameter............................................................................................................................3-2

Memory Profile Page.......................................................................................................................3-2

Timing Page......................................................................................................................................3-2

Interface.........................................................................................................................................................3-3

Reset and Clock Requirements.................................................................................................................. 3-8

Architecture..................................................................................................................................................3-8

Avalon-MM Slave Interface and CSR........................................................................................... 3-9

Block Level Usage Model................................................................................................................3-9

Document Revision History.....................................................................................................................3-10

Page 3

TOC-3

Compact Flash Core............................................................................................ 4-1

Core Overview..............................................................................................................................................4-1

Functional Description............................................................................................................................... 4-1

Required Connections.................................................................................................................................4-2

Software Programming Model...................................................................................................................4-3

HAL System Library Support.........................................................................................................4-3

Software Files....................................................................................................................................4-3

Register Maps................................................................................................................................... 4-4

Document Revision History.......................................................................................................................4-5

Common Flash Interface Controller Core..........................................................5-1

........................................................................................................................................................................ 5-1

Core Overview..............................................................................................................................................5-1

Functional Description............................................................................................................................... 5-2

Configuration............................................................................................................................................... 5-2

Attributes Page.................................................................................................................................5-2

Timing page......................................................................................................................................5-3

Software Programming Model...................................................................................................................5-3

HAL System Library Support.........................................................................................................5-4

Software Files....................................................................................................................................5-4

Document Revision History.......................................................................................................................5-4

EPCS Serial Flash Controller Core..................................................................... 6-1

Core Overview..............................................................................................................................................6-1

Functional Description............................................................................................................................... 6-2

Avalon-MM Slave Interface and Registers...................................................................................6-3

Configuration..............................................................................................................................................6-4

Software Programming Model...................................................................................................................6-4

HAL System Library Support.........................................................................................................6-4

Software Files....................................................................................................................................6-5

Document Revision History.......................................................................................................................6-5

JTAG UART Core................................................................................................7-1

Core Overview..............................................................................................................................................7-1

Functional Description............................................................................................................................... 7-1

Avalon Slave Interface and Registers.............................................................................................7-2

Read and Write FIFOs.....................................................................................................................7-2

JTAG Interface................................................................................................................................. 7-2

Host-Target Connection.................................................................................................................7-2

Configuration............................................................................................................................................... 7-3

Configuration Page..........................................................................................................................7-3

Simulation Settings..........................................................................................................................7-4

Hardware Simulation Considerations.......................................................................................................7-5

Software Programming Model...................................................................................................................7-5

Altera Corporation

Page 4

TOC-4

HAL System Library Support.........................................................................................................7-5

Software Files....................................................................................................................................7-8

Accessing the JTAG UART Core via a Host PC..........................................................................7-9

Register Map.....................................................................................................................................7-9

Interrupt Behavior.........................................................................................................................7-10

Document Revision History.....................................................................................................................7-11

UART Core..........................................................................................................8-1

Core Overview..............................................................................................................................................8-1

Functional Description............................................................................................................................... 8-1

Avalon-MM Slave Interface and Registers...................................................................................8-2

RS-232 Interface...............................................................................................................................8-2

Transmitter Logic.............................................................................................................................8-2

Receiver Logic...................................................................................................................................8-2

Baud Rate Generation..................................................................................................................... 8-3

Instantiating the Core..................................................................................................................................8-3

Configuration Settings.................................................................................................................... 8-3

Simulation Settings..........................................................................................................................8-6

Simulation Considerations.........................................................................................................................8-7

Software Programming Model...................................................................................................................8-7

HAL System Library Support.........................................................................................................8-7

Software Files..................................................................................................................................8-11

Register Map...................................................................................................................................8-11

Interrupt Behavior.........................................................................................................................8-16

Document Revision History.....................................................................................................................8-16

16550 UART........................................................................................................ 9-1

Core Overview..............................................................................................................................................9-1

Feature Description..................................................................................................................................... 9-1

Unsupported Features.....................................................................................................................9-2

Interface.............................................................................................................................................9-2

General Architecture....................................................................................................................... 9-4

Configuration Parameters.............................................................................................................. 9-4

DMA Support...................................................................................................................................9-5

FPGA Resource Usage.....................................................................................................................9-5

Timing and Fmax.............................................................................................................................9-6

Avalon-MM Slave............................................................................................................................ 9-7

Overrun/Underrun Conditions.....................................................................................................9-8

Hardware Auto Flow-Control........................................................................................................9-9

Clock and Baud Rate Selection.................................................................................................... 9-10

Software Programming Model.................................................................................................................9-10

Overview......................................................................................................................................... 9-10

Supported Features........................................................................................................................9-10

Unsupported Features...................................................................................................................9-11

Configuration.................................................................................................................................9-11

16550 UART API...........................................................................................................................9-12

Driver Examples.............................................................................................................................9-16

Altera Corporation

Page 5

TOC-5

Document Revision History.....................................................................................................................9-20

SPI Core.............................................................................................................10-1

Core Overview............................................................................................................................................10-1

Functional Description............................................................................................................................. 10-1

Example Configurations............................................................................................................... 10-2

Transmitter Logic.......................................................................................................................... 10-2

Receiver Logic.................................................................................................................................10-3

Master and Slave Modes............................................................................................................... 10-3

Avalon-MM Interface....................................................................................................................10-5

Configuration.............................................................................................................................................10-5

Master/Slave Settings.....................................................................................................................10-5

Data Register Settings....................................................................................................................10-6

Timing Settings.............................................................................................................................. 10-6

Software Programming Model.................................................................................................................10-7

Hardware Access Routines...........................................................................................................10-7

Software Files..................................................................................................................................10-8

Register Map...................................................................................................................................10-9

Document Revision History...................................................................................................................10-11

Optrex 16207 LCD Controller Core..................................................................11-1

Core Overview............................................................................................................................................11-1

Functional Description............................................................................................................................. 11-1

Software Programming Model.................................................................................................................11-2

HAL System Library Support.......................................................................................................11-2

Displaying Characters on the LCD..............................................................................................11-2

Software Files..................................................................................................................................11-3

Register Map...................................................................................................................................11-3

Interrupt Behavior.........................................................................................................................11-3

Document Revision History.....................................................................................................................11-4

PIO Core............................................................................................................12-1

Core Overview............................................................................................................................................12-1

Functional Description............................................................................................................................. 12-1

Data Input and Output................................................................................................................. 12-2

Edge Capture.................................................................................................................................. 12-2

IRQ Generation..............................................................................................................................12-2

Example Configurations...........................................................................................................................12-3

Avalon-MM Interface....................................................................................................................12-3

Configuration.............................................................................................................................................12-3

Basic Settings.................................................................................................................................. 12-3

Input Options.................................................................................................................................12-4

Simulation.......................................................................................................................................12-5

Software Programming Model.................................................................................................................12-5

Software Files..................................................................................................................................12-5

Register Map...................................................................................................................................12-5

Altera Corporation

Page 6

TOC-6

Interrupt Behavior.........................................................................................................................12-7

Software Files..................................................................................................................................12-7

Document Revision History.....................................................................................................................12-8

Avalon-ST Serial Peripheral Interface Core.....................................................13-1

Core Overview............................................................................................................................................13-1

Functional Description............................................................................................................................. 13-1

Interfaces.........................................................................................................................................13-1

Operation........................................................................................................................................13-2

Timing.............................................................................................................................................13-2

Limitations......................................................................................................................................13-3

Configuration.............................................................................................................................................13-3

Document Revision History.....................................................................................................................13-3

PCI Lite Core..................................................................................................... 14-1

Core Overview............................................................................................................................................14-1

Performance and Resource Utilization...................................................................................................14-1

Functional Description............................................................................................................................. 14-2

PCI-Avalon Bridge Blocks............................................................................................................14-2

Avalon-MM Ports..........................................................................................................................14-3

Prefetchable Avalon-MM Master................................................................................................14-3

Non-Prefectchable Avalon-MM Master.....................................................................................14-3

I/O Avalon-MM Master................................................................................................................14-4

PCI Bus Access Slave.....................................................................................................................14-4

Control Register Access (CRA) Avalon-MM Slave...................................................................14-4

Master and Target Performance..................................................................................................14-5

PCI-to-Avalon Address Translation...........................................................................................14-6

Avalon-to-PCI Address Translation...........................................................................................14-6

Avalon-To-PCI Read and Write Operation...............................................................................14-8

Ordering of Requests.....................................................................................................................14-9

PCI Interrupt................................................................................................................................14-10

Configuration...........................................................................................................................................14-10

PCI Timing Constraint Files......................................................................................................14-12

Simulation Considerations.....................................................................................................................14-13

Master Transactor (mstr_tranx)................................................................................................14-14

Simulation Flow...........................................................................................................................14-15

Document Revision History...................................................................................................................14-16

MDIO Core........................................................................................................15-1

Altera Corporation

Functional Description............................................................................................................................. 15-1

MDIO Frame Format (Clause 45)...............................................................................................15-2

MDIO Clock Generation..............................................................................................................15-3

Interfaces.........................................................................................................................................15-3

Operation........................................................................................................................................15-3

Parameter....................................................................................................................................................15-4

Configuration Registers............................................................................................................................ 15-4

Page 7

TOC-7

Document Revision History.....................................................................................................................15-5

On-Chip FIFO Memory Core............................................................................16-1

Core Overview............................................................................................................................................16-1

Functional Description............................................................................................................................. 16-1

Avalon-MM Write Slave to Avalon-MM Read Slave............................................................... 16-1

Avalon-ST Sink to Avalon-ST Source.........................................................................................16-2

Avalon-MM Write Slave to Avalon-ST Source......................................................................... 16-2

Avalon-ST Sink to Avalon-MM Read Slave...............................................................................16-4

Status Interface...............................................................................................................................16-5

Clocking Modes............................................................................................................................. 16-5

Configuration.............................................................................................................................................16-5

FIFO Settings..................................................................................................................................16-6

Interface Parameters......................................................................................................................16-6

Software Programming Model.................................................................................................................16-7

HAL System Library Support.......................................................................................................16-7

Software Files..................................................................................................................................16-7

Programming with the On-Chip FIFO Memory...................................................................................16-7

Software Control............................................................................................................................16-8

Software Example........................................................................................................................ 16-11

On-Chip FIFO Memory API..................................................................................................................16-12

altera_avalon_fifo_init().............................................................................................................16-12

altera_avalon_fifo_read_status()...............................................................................................16-12

altera_avalon_fifo_read_ienable().............................................................................................16-13

altera_avalon_fifo_read_almostfull()........................................................................................16-13

altera_avalon_fifo_read_almostempty().................................................................................. 16-13

altera_avalon_fifo_read_event()................................................................................................16-14

altera_avalon_fifo_read_level()................................................................................................. 16-14

altera_avalon_fifo_clear_event()...............................................................................................16-14

altera_avalon_fifo_write_ienable()........................................................................................... 16-15

altera_avalon_fifo_write_almostfull()...................................................................................... 16-15

altera_avalon_fifo_write_almostempty().................................................................................16-15

altera_avalon_write_fifo()..........................................................................................................16-16

altera_avalon_write_other_info()............................................................................................. 16-16

altera_avalon_fifo_read_fifo()...................................................................................................16-17

Document Revision History...................................................................................................................16-18

Avalon-ST Multi-Channel Shared Memory FIFO Core...................................17-1

Core Overview............................................................................................................................................17-1

Performance and Resource Utilization...................................................................................................17-1

Functional Description............................................................................................................................. 17-3

Interfaces.........................................................................................................................................17-3

Operation........................................................................................................................................17-4

Parameters.................................................................................................................................................. 17-4

Software Programming Model.................................................................................................................17-6

HAL System Library Support.......................................................................................................17-6

Register Map...................................................................................................................................17-6

Altera Corporation

Page 8

TOC-8

Document Revision History.....................................................................................................................17-8

SPI Slave/JTAG to Avalon Master Bridge Cores.............................................. 18-1

Core Overview............................................................................................................................................18-1

Functional Description............................................................................................................................. 18-1

Parameters.................................................................................................................................................. 18-3

Document Revision History.....................................................................................................................18-3

Avalon-ST Bytes to Packets and Packets to Bytes Converter Cores................ 19-1

Functional Description............................................................................................................................. 19-1

Interfaces.........................................................................................................................................19-2

Operation—Avalon-ST Bytes to Packets Converter Core....................................................... 19-2

Operation—Avalon-ST Packets to Bytes Converter Core....................................................... 19-3

Document Revision History.....................................................................................................................19-3

Avalon Packets to Transactions Converter Core..............................................20-1

Core Overview............................................................................................................................................20-1

Functional Description............................................................................................................................. 20-1

Interfaces.........................................................................................................................................20-1

Operation........................................................................................................................................20-2

Document Revision History.....................................................................................................................20-4

Scatter-Gather DMA Controller Core.............................................................. 21-1

Core Overview............................................................................................................................................21-1

Example Systems............................................................................................................................21-1

Comparison of SG-DMA Controller Core and DMA Controller Core.................................21-2

Resource Usage and Performance...........................................................................................................21-2

Functional Description............................................................................................................................. 21-3

Functional Blocks and Configurations....................................................................................... 21-3

DMA Descriptors...........................................................................................................................21-6

Error Conditions............................................................................................................................21-7

Parameters.................................................................................................................................................. 21-9

Simulation Considerations.....................................................................................................................21-10

Software Programming Model...............................................................................................................21-10

HAL System Library Support.....................................................................................................21-10

Software Files................................................................................................................................21-10

Register Maps...............................................................................................................................21-10

DMA Descriptors.........................................................................................................................21-13

Timeouts....................................................................................................................................... 21-15

Programming with SG-DMA Controller.............................................................................................21-16

Data Structure.............................................................................................................................. 21-16

SG-DMA API............................................................................................................................... 21-17

alt_avalon_sgdma_do_async_transfer()...................................................................................21-18

alt_avalon_sgdma_do_sync_transfer().....................................................................................21-18

alt_avalon_sgdma_construct_mem_to_mem_desc()............................................................ 21-19

Altera Corporation

Page 9

TOC-9

alt_avalon_sgdma_construct_stream_to_mem_desc()..........................................................21-20

alt_avalon_sgdma_construct_mem_to_stream_desc()..........................................................21-21

alt_avalon_sgdma_check_descriptor_status().........................................................................21-22

alt_avalon_sgdma_register_callback()......................................................................................21-23

alt_avalon_sgdma_start()........................................................................................................... 21-23

alt_avalon_sgdma_stop()............................................................................................................21-24

alt_avalon_sgdma_open().......................................................................................................... 21-24

Document Revision History...................................................................................................................21-25

Altera Modular Scatter-Gather DMA...............................................................22-1

Overview..................................................................................................................................................... 22-1

Feature Description...................................................................................................................................22-1

mSGDMA Interfaces and Parameters.........................................................................................22-4

mSGDMA Descriptors..................................................................................................................22-7

Register Map of mSGDMA........................................................................................................ 22-12

Unsupported Feature.................................................................................................................. 22-15

Document Revision History.......................................................................................................22-15

DMA Controller Core....................................................................................... 23-1

Core Overview............................................................................................................................................23-1

Functional Description............................................................................................................................. 23-1

Setting Up DMA Transactions.....................................................................................................23-2

The Master Read and Write Ports...............................................................................................23-2

Addressing and Address Incrementing...................................................................................... 23-3

Parameters.................................................................................................................................................. 23-3

DMA Parameters (Basic)..............................................................................................................23-3

Advanced Options......................................................................................................................... 23-4

Software Programming Model.................................................................................................................23-5

HAL System Library Support.......................................................................................................23-5

Software Files..................................................................................................................................23-6

Register Map...................................................................................................................................23-6

Interrupt Behavior.........................................................................................................................23-9

Document Revision History...................................................................................................................23-10

Video Sync Generator and Pixel Converter Cores........................................... 24-1

Core Overview............................................................................................................................................24-1

Video Sync Generator............................................................................................................................... 24-1

Functional Description................................................................................................................. 24-1

Parameters...................................................................................................................................... 24-2

Signals..............................................................................................................................................24-3

Timing Diagrams...........................................................................................................................24-4

Pixel Converter...........................................................................................................................................24-5

Functional Description................................................................................................................. 24-5

Parameters...................................................................................................................................... 24-5

Signals..............................................................................................................................................24-5

Hardware Simulation Considerations.................................................................................................... 24-6

Altera Corporation

Page 10

TOC-10

Document Revision History.....................................................................................................................24-6

Interval Timer Core...........................................................................................25-1

Core Overview............................................................................................................................................25-1

Functional Description............................................................................................................................. 25-1

Avalon-MM Slave Interface..........................................................................................................25-2

Configuration.............................................................................................................................................25-2

Timeout Period.............................................................................................................................. 25-2

Counter Size....................................................................................................................................25-3

Hardware Options......................................................................................................................... 25-3

Configuring the Timer as a Watchdog Timer........................................................................... 25-4

Software Programming Model.................................................................................................................25-4

HAL System Library Support.......................................................................................................25-4

Software Files..................................................................................................................................25-5

Register Map...................................................................................................................................25-5

Interrupt Behavior.........................................................................................................................25-8

Document Revision History.....................................................................................................................25-8

Mutex Core........................................................................................................ 26-1

Core Overview............................................................................................................................................26-1

Functional Description............................................................................................................................. 26-1

Configuration.............................................................................................................................................26-2

Software Programming Model.................................................................................................................26-2

Software Files..................................................................................................................................26-2

Hardware Access Routines...........................................................................................................26-2

Mutex API...................................................................................................................................................26-3

altera_avalon_mutex_is_mine()..................................................................................................26-3

altera_avalon_mutex_first_lock()............................................................................................... 26-4

altera_avalon_mutex_lock().........................................................................................................26-4

altera_avalon_mutex_open()....................................................................................................... 26-4

altera_avalon_mutex_trylock()....................................................................................................26-5

altera_avalon_mutex_unlock()....................................................................................................26-5

Document Revision History.....................................................................................................................26-5

Mailbox Core..................................................................................................... 27-1

Altera Corporation

Core Overview............................................................................................................................................27-1

Functional Description............................................................................................................................. 27-1

Configuration.............................................................................................................................................27-2

Software Programming Model.................................................................................................................27-2

Software Files..................................................................................................................................27-3

Programming with the Mailbox Core.........................................................................................27-3

Mailbox API................................................................................................................................................27-4

altera_avalon_mailbox_close().................................................................................................... 27-4

altera_avalon_mailbox_get()........................................................................................................27-5

altera_avalon_mailbox_open()....................................................................................................27-5

altera_avalon_mailbox_pend()....................................................................................................27-5

Page 11

TOC-11

altera_avalon_mailbox_post()..................................................................................................... 27-6

Document Revision History.....................................................................................................................27-6

Vectored Interrupt Controller Core.................................................................28-1

Core Overview............................................................................................................................................28-1

Functional Description............................................................................................................................. 28-3

External Interfaces.........................................................................................................................28-3

Functional Blocks...........................................................................................................................28-4

Register Maps............................................................................................................................................. 28-6

Parameters................................................................................................................................................ 28-11

Altera HAL Software Programming Model.........................................................................................28-11

Software Files................................................................................................................................28-11

Macros...........................................................................................................................................28-12

Data Structure.............................................................................................................................. 28-13

VIC API.........................................................................................................................................28-13

Run-time Initialization................................................................................................................28-16

Board Support Package...............................................................................................................28-16

Document Revision History...................................................................................................................28-23

Avalon-ST JTAG Interface Core.......................................................................29-1

Functional Description............................................................................................................................. 29-1

Interfaces.........................................................................................................................................29-1

Core Behavior.................................................................................................................................29-2

Parameters...................................................................................................................................... 29-3

Document Revision History.....................................................................................................................29-3

System ID Core..................................................................................................30-1

Core Overview............................................................................................................................................30-1

Functional Description............................................................................................................................. 30-1

Configuration.............................................................................................................................................30-2

Software Programming Model.................................................................................................................30-2

alt_avalon_sysid_test()..................................................................................................................30-2

Document Revision History.....................................................................................................................30-3

Performance Counter Core...............................................................................31-1

Core Overview............................................................................................................................................31-1

Functional Description............................................................................................................................. 31-1

Section Counters............................................................................................................................31-1

Global Counter...............................................................................................................................31-2

Register Map...................................................................................................................................31-2

System Reset................................................................................................................................... 31-3

Configuration.............................................................................................................................................31-3

Define Counters.............................................................................................................................31-3

Multiple Clock Domain Considerations.....................................................................................31-3

Hardware Simulation Considerations.................................................................................................... 31-3

Altera Corporation

Page 12

TOC-12

Software Programming Model.................................................................................................................31-3

Software Files..................................................................................................................................31-4

Using the Performance Counter..................................................................................................31-4

Interrupt Behavior.........................................................................................................................31-6

Performance Counter API........................................................................................................................31-6

PERF_RESET()...............................................................................................................................31-6

PERF_START_MEASURING().................................................................................................. 31-7

PERF_STOP_MEASURING().....................................................................................................31-7

PERF_BEGIN()..............................................................................................................................31-7

PERF_END()..................................................................................................................................31-8

perf_print_formatted_report().................................................................................................... 31-8

perf_get_total_time().................................................................................................................... 31-9

perf_get_section_time()................................................................................................................31-9

perf_get_num_starts()................................................................................................................ 31-10

alt_get_cpu_freq()....................................................................................................................... 31-10

Document Revision History...................................................................................................................31-11

PLL Cores...........................................................................................................32-1

Core Overview............................................................................................................................................32-1

Functional Description............................................................................................................................. 32-2

ALTPLL Megafunction................................................................................................................. 32-2

Clock Outputs................................................................................................................................ 32-2

PLL Status and Control Signals....................................................................................................32-2

System Reset Considerations........................................................................................................32-3

Instantiating the Avalon ALTPLL Core..................................................................................................32-3

Instantiating the PLL Core....................................................................................................................... 32-3

Hardware Simulation Considerations.................................................................................................... 32-5

Register Definitions and Bit List..............................................................................................................32-5

Status Register................................................................................................................................ 32-5

Control Register.............................................................................................................................32-6

Phase Reconfig Control Register................................................................................................. 32-7

Document Revision History.....................................................................................................................32-8

Altera MSI to GIC Generator............................................................................33-1

Altera Interrupt Latency Counter.....................................................................34-1

Altera Corporation

Overview..................................................................................................................................................... 33-1

Background.................................................................................................................................................33-1

Feature Description...................................................................................................................................33-1

Interrupt Servicing Process.......................................................................................................... 33-2

Registers of Component................................................................................................................33-3

Unsupported Feature.................................................................................................................... 33-4

Altera SMBus Core Interface....................................................................................................................33-5

Component Interface.................................................................................................................... 33-7

Component Parameterization......................................................................................................33-7

Document Revision History.....................................................................................................................33-9

Page 13

TOC-13

Overview..................................................................................................................................................... 34-1

Feature Description...................................................................................................................................34-2

Avalon-MM Compliant CSR Registers.......................................................................................34-2

32-bit Counter................................................................................................................................34-4

Interrupt Detector..........................................................................................................................34-5

Component Interface................................................................................................................................ 34-5

Component Parameterization..................................................................................................................34-5

Software Access..........................................................................................................................................34-6

Routine for Level Sensitive Interrupts........................................................................................ 34-6

Routine for Edge/Pulse Sensitive Interrupts..............................................................................34-6

Implementation Details............................................................................................................................ 34-7

Interrupt Latency Counter Architecture.................................................................................... 34-7

IP Caveats....................................................................................................................................................34-8

Document Revision History.....................................................................................................................34-8

Altera Corporation

Page 14

2014.24.07

www.altera.com

101 Innovation Drive, San Jose, CA 95134

Introduction

1

UG-01085

This user guide describes the IP cores provided by Altera that are included in the Quartus® II design

software.

The IP cores are optimized for Altera® devices and can be easily implemented to reduce design and test

time. You can use the IP parameter editor from Qsys to add the IP cores to your system, configure the

cores, and specify their connectivity.

Altera's Qsys system integration tool is available in the Quartus II software subcription edition version

14.0.

Before using Qsys, review the (Quartus II software Version 14.0 Release Notes) for known issues and

limitations. To submit general feedback or technical support, click Feedback on the Quartus II software

Help menu and also on all Altera technical documentation.

Quartus II Handbook 14.0

Quartus II Software and Device Support Release Notes Version 14.0

Tool Support

Qsys is a system-level integration tool which is included as part of the Quartus II software. Qsys leverages

the easy-to-use interface of SOPC Builder and provides backward compatibility for easy migration of

existing embedded systems.You can implement a design using the IP cores from the Qsys component

library.

Subscribe

Send Feedback

All the IP cores described in this user guide are supported by Qsys except for the following cores which

are only supported by SOPC Builder.

• Common Flash Interface Controller Core

• SDRAM Controller Core (pin-sharing mode)

• System ID Core

Obsolescence

The following IP cores are scheduled for product obsolescence and discontinued support:

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 15

1-2

Device Support

• PCI Lite Core

• Mailbox Core

Altera recommends that you do not use these cores in new designs.

For more information about Altera’s current IP offering, refer to Altera’s Intellectual Property

website.

Device Support

The IP cores described in this user guide support all Altera® device families except the cores listed in the

table below.

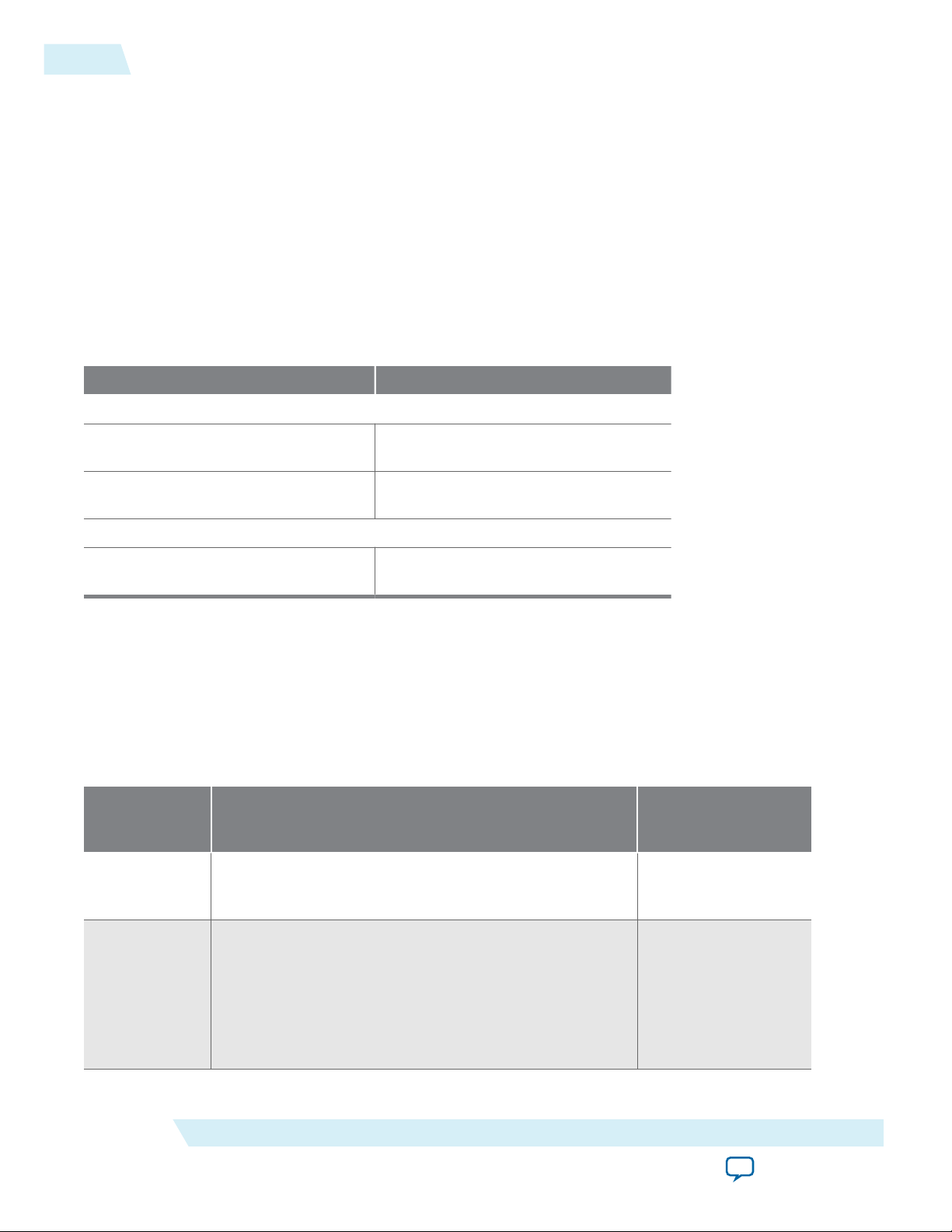

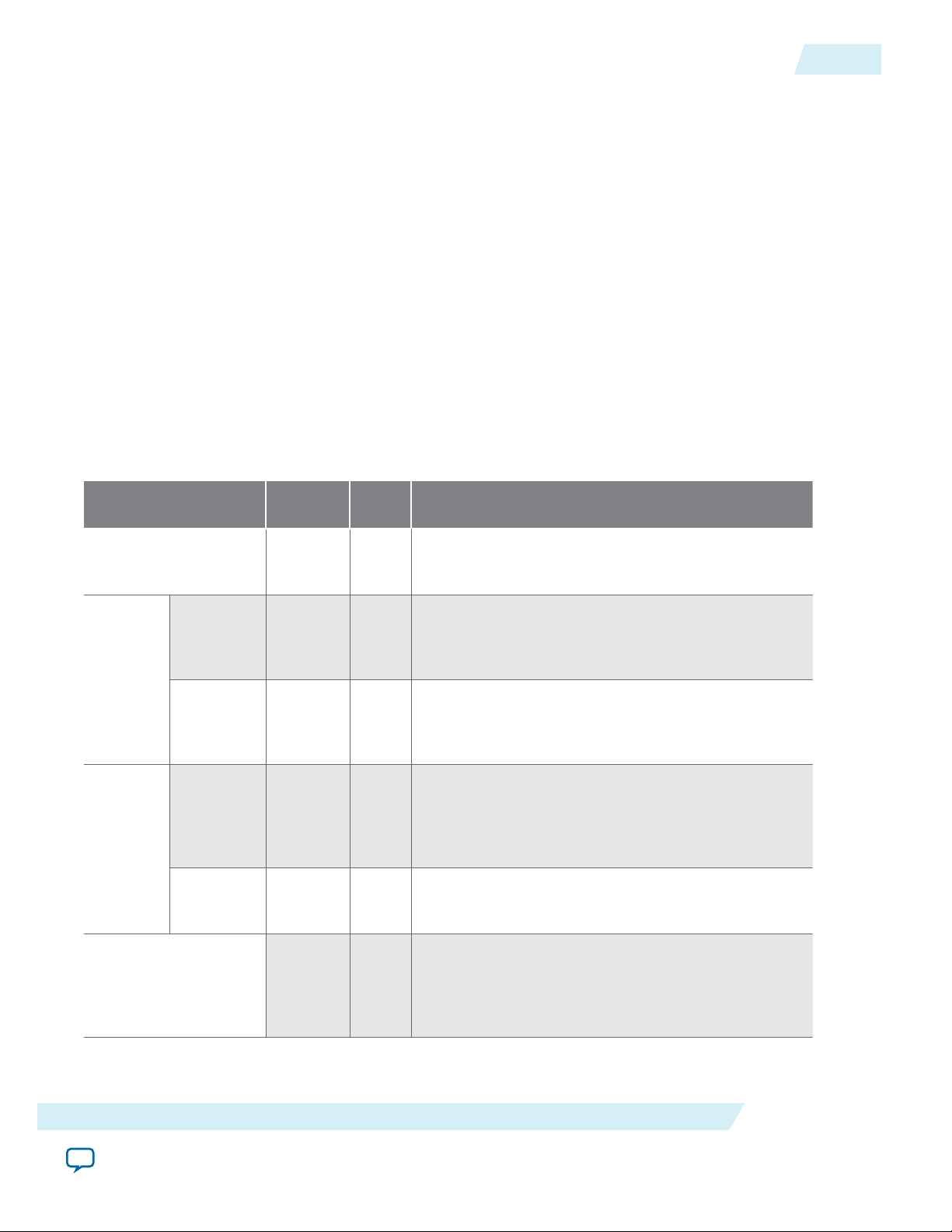

Table 1-1: Device Support

IP Cores Device Support

Off-Chip Interfaces

EPCS Serial Flash Controller Core All device families except HardCopy

series.

UG-01085

2014.24.07

®

Cyclone III Remote Update

Only Cyclone III device.

Controller Core

On-Chip Interfaces

On-Chip FIFO Memory Core All device families except HardCopy

series.

Different device families support different I/O standards, which may affect the ability of the core to

interface to certain components. For details about supported I/O types, refer to the device handbook for

the target device family.

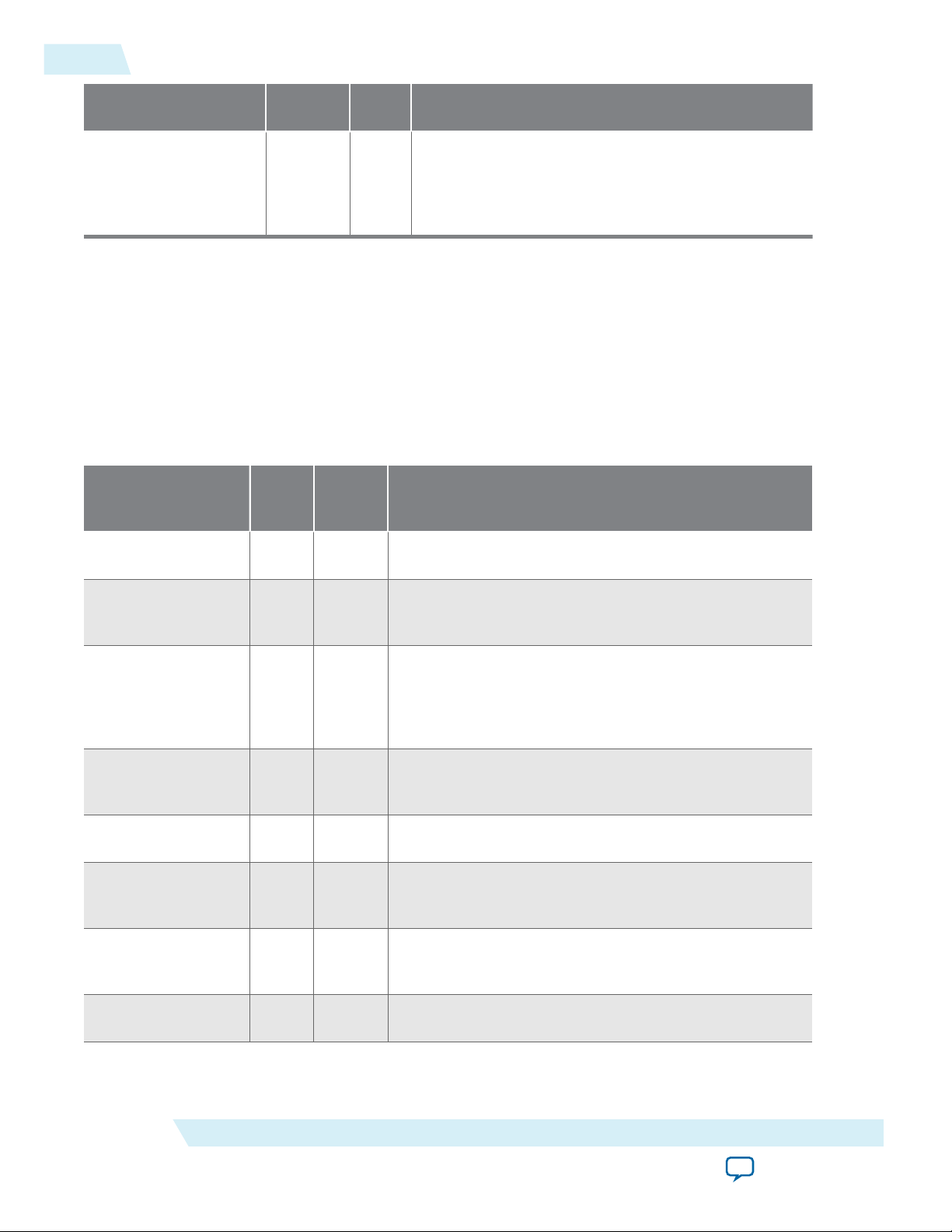

Document Revision History

Table 1-2: Document Revision History

Date and

Document

Version

July 2014

v14.0.0

December

2013 v13.1.0

-Removed mention of SOPC Builder, updated to Qsys Maintenance

Removed listing of the DMA Controller core in the Qsys

unsupported list. The DMA controller core is now

supported in Qsys.

Changes Made Summary of Changes

®

Release

—

Altera Corporation

Removed listing of the MDIO core in Device Support Table.

The MDIO core support all device families that the 10-Gbps

Ethernet MAC MegaCore Function supports.

Introduction

Send Feedback

Page 16

UG-01085

2014.24.07

Document Revision History

1-3

Date and

Document

Version

December

2010

v10.1.0

Changes Made Summary of Changes

Initial release. —

Introduction

Send Feedback

Altera Corporation

Page 17

2014.24.07

www.altera.com

101 Innovation Drive, San Jose, CA 95134

SDRAM Controller Core

2

UG-01085

Core Overview

The SDRAM controller core with Avalon® interface provides an Avalon Memory-Mapped (Avalon-MM)

interface to off-chip SDRAM. The SDRAM controller allows designers to create custom systems in an

Altera® device that connect easily to SDRAM chips. The SDRAM controller supports standard SDRAM as

described in the PC100 specification.

SDRAM is commonly used in cost-sensitive applications requiring large amounts of volatile memory.

While SDRAM is relatively inexpensive, control logic is required to perform refresh operations, open-row

management, and other delays and command sequences. The SDRAM controller connects to one or more

SDRAM chips, and handles all SDRAM protocol requirements. Internal to the device, the core presents an

Avalon-MM slave port that appears as linear memory (flat address space) to Avalon-MM master

peripherals.

The core can access SDRAM subsystems with various data widths (8, 16, 32, or 64 bits), various memory

sizes, and multiple chip selects. The Avalon-MM interface is latency-aware, allowing read transfers to be

pipelined. The core can optionally share its address and data buses with other off-chip Avalon-MM tristate devices. This feature is valuable in systems that have limited I/O pins, yet must connect to multiple

memory chips in addition to SDRAM.

Subscribe

Send Feedback

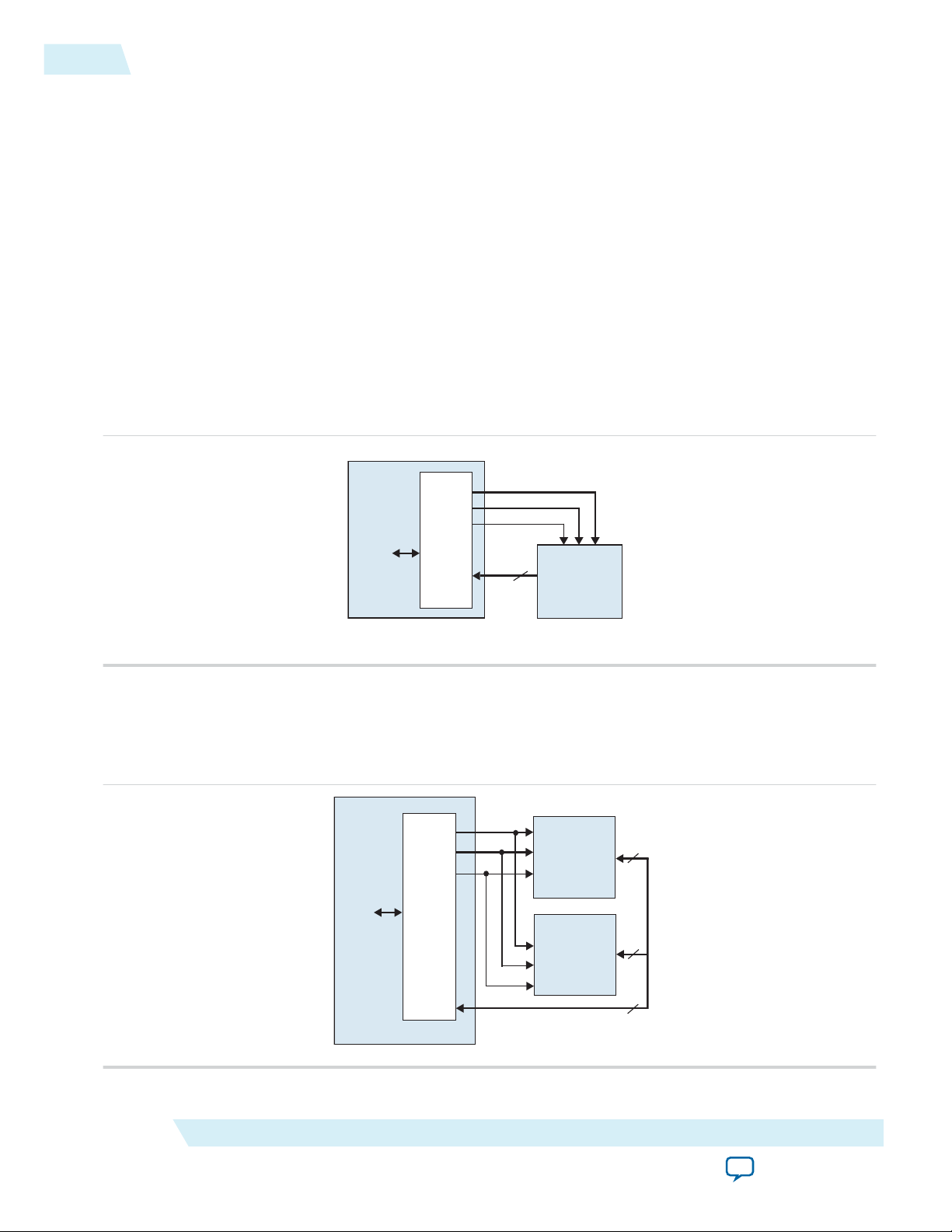

Functional Description

The diagram below shows a block diagram of the SDRAM controller core connected to an external

SDRAM chip.

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 18

Avalon-MM slave

interface

to on-chip

logic

SDRAM Controller Core

data, control

Avalon-MM Slave Port

clock

waitrequest

readdatavalid

dq

dqm

PLL

Phase Shift

Interface to SDRAM pins

Altera FPGA

clk

addr

ras

cas

cs

cke

ba

we

Control

Logic

address

SDRAM Clock

Controller Clock