Page 1

101 Innovation Drive

San Jose, CA 95134

http://www.altera.com

UG-DDRTMNG-3.0

DDR Timing Wizard

User Guide

Document Version: 3.0

Document Date: November 2007

Page 2

Copyright © 2007 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company,

the stylized Altera logo, specific device designations, and all other words and logos that are identified as

trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera

Corporation in the U.S. and other countries. All other product or service names are the property of their re-

101 Innovation Drive

San Jose, CA 95134

www.altera.com

Technical Support:

www.altera.com/support/

Literature Services:

spective holders. Altera products are protected under numerous U.S. and foreign patents and pending

applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products

to current specifications in a ccordance with Altera's standard warranty, but reserve s the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability

arising out of the application or use of any information, product, or service described

herein except as expressly agreed to in writing by Altera Corporation. Altera customers

are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

literature@altera.com

ii Altera Corporation

Page 3

Table of Contents

About this User Guide .............................................................................. v

Revision History .................................................................................................................................... 1–v

How to Contact Altera .......................................................................................................................... 1–v

Typographic Conventions .................................................................................................................. 1–vi

Chapter 1. About the DDR Timing Wizard

Release Information ............................................................................................................................... 1–1

Device Family Support ......................................................................................................................... 1–2

Introduction ............................................................................................................................................ 1–2

Background ....................................................................................................................................... 1–2

DDR Timing Wizard ........................................................................................................................ 1–3

Features ................................................................................................................................................... 1–6

Chapter 2. Getting Started

System and Software Requirements ................................................................................................... 2–1

Design Flow ............................................................................................................................................ 2–1

Launching the DDR Timing Wizard ................................................................................................... 2–5

Entering and Editing Inputs to the DTW ........................................................................................... 2–6

Import Flow for the Altera Legacy Memory Controller IP Core or Recommended Data Path

.............................................................................................................................................................. 2–7

Manual Flow for Other External Memory Interfaces or Source Synchronous Systems ...... 2–14

The DTW Pages for DDR/DDR2 SDRAM ............................................................................ 2–14

The DTW Pages for QDRII+/QDRII SRAM & RLDRAM II ............................................... 2–45

DTW Limitations ................................................................................................................................. 2–46

Chapter 3. Using the dtw_timing_analysis.tcl Script

Introduction ............................................................................................................................................ 3–1

Running dtw_timing_analysis.tcl Script ....................................................................................... 3–3

The dtw_timing_analysis.tcl Script Results .................................................................................. 3–6

Timing Closure Process ...................................................................................................................... 3–12

Timing Closure Differences in DDR2/DDR SDRAM, QDRII+/QDRII SRAM, and RLDRAM II

Interfaces .......................................................................................................................................... 3–14

DDR2/DDR SDRAM Interfaces ............................................................................................. 3–14

QDRII+/QDRII SRAM Interfaces ........................................................................................... 3–14

RLDRAM II Interfaces .............................................................................................................. 3–15

Selecting Initial Phase Shifts ......................................................................................................... 3–16

Re-run DTW After First Compile When Using Classic Timing Analyzer ............................. 3–18

Ensure the Changes Made Outside Legacy Controller MegaWizard Are Not Erased When the

Core is Regenerated ....................................................................................................................... 3–19

Decide When to Change Clock Phase Shift ................................................................................ 3–21

Altera Corporation iii

November 2007

Page 4

Table of Contents DDR Timing Wizard User Guide

Changing Clock Phase Shift .......................................................................................................... 3–23

Adjusting Clock Cycle Selections ................................................................................................. 3–25

Changing Clock Cycles .................................................................................................................. 3–27

Changing the Address/Command Clock Connection and Phase Shift ................................. 3–28

Moving the Data Path Registers Closer to the Pins ................................................................... 3–30

Conclusion ............................................................................................................................................ 3–32

iv Altera Corporation

November 2007

Page 5

About this User Guide

Revision History

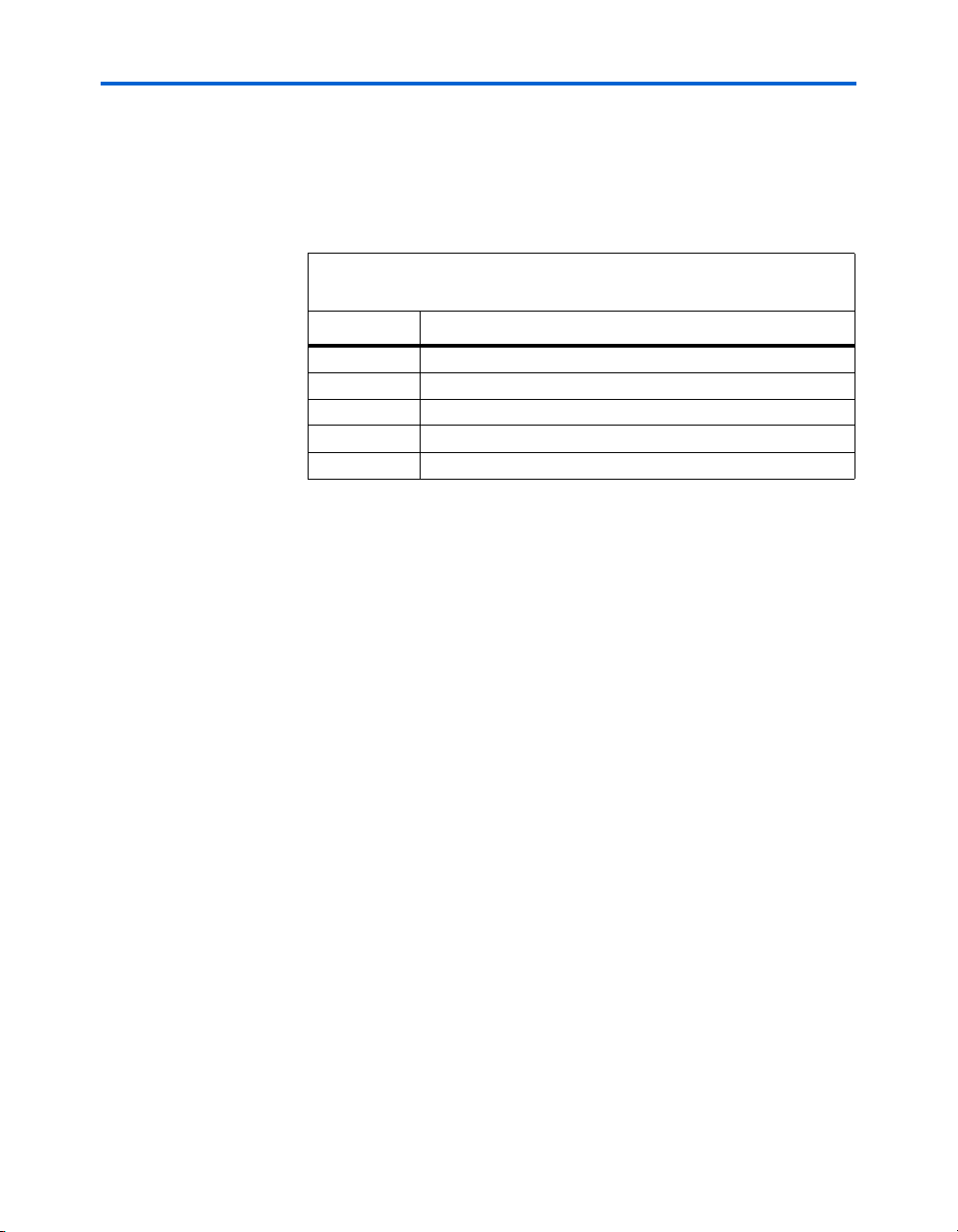

Chapter Date

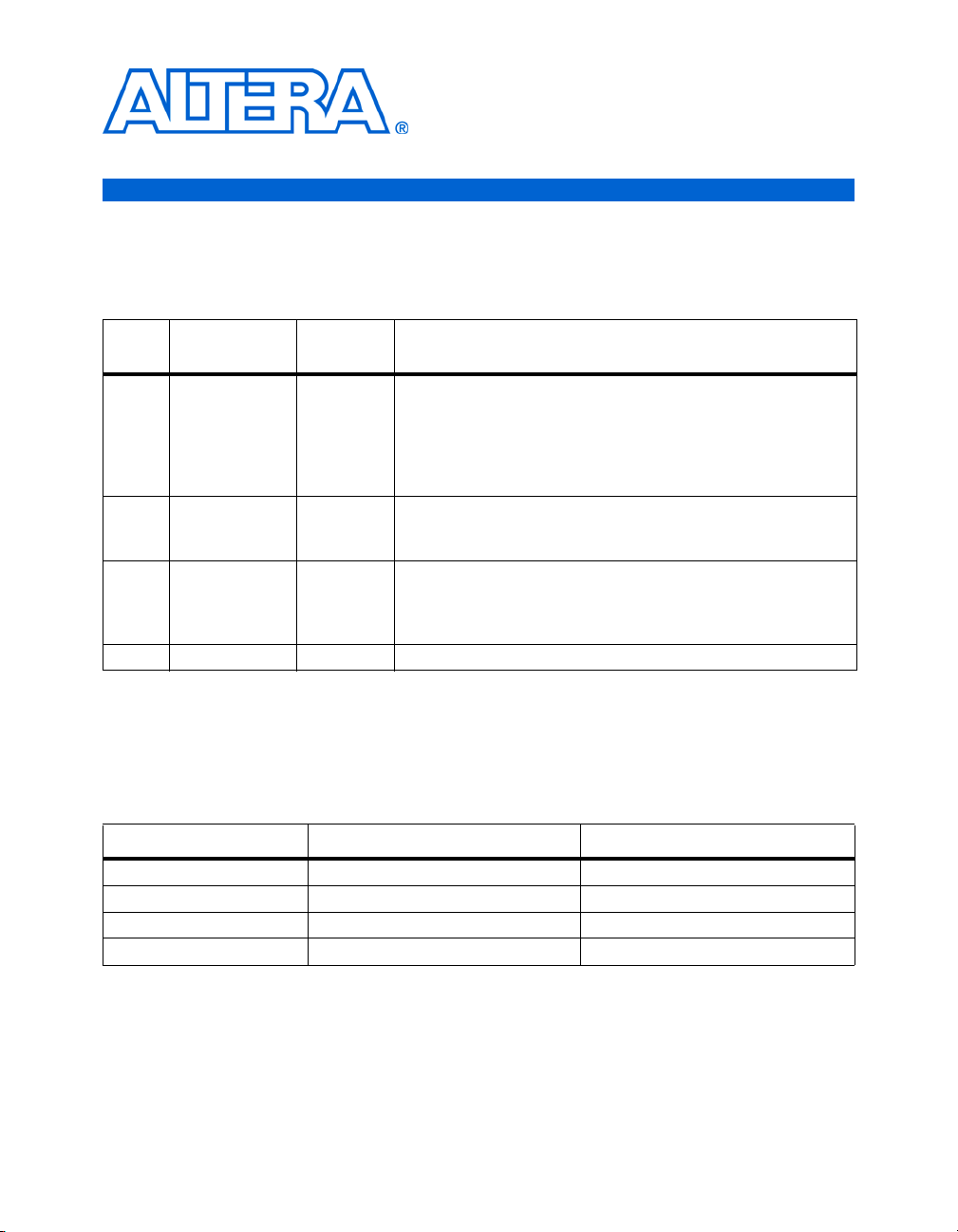

All November 2007 3.0 ● Replaced all references to “IP Tool Bench” to “legacy controller

All July 2007 2.1

All December 2006 2.0

All May 2006 1.0

How to Contact Altera

The table below displays the revision history for the chapters in this user

guide.

Document

Version

MegaWizard” and “altmemphy” to “ALTMEMPHY”.

● Updated the Entering and Editing Inputs to the DTW section in

Chapter 2. Getting Started for Quartus II 7.2 support.

● Added Chapter 3. Using the dtw_timing_analysis.tcl Script to

replace the Performing Timing Analysis section.

● Changed title of referenced document to: AN 413, Using Legacy

Integrated Static Data Path and Controller Megafunction with

Hardcopy II Structured ASICs.

● Updated document for Quartus II version 6.1 software.

● Added design flow.

● Introduced dtw_timing_analysis.tcl and usage.

● Introduced the clock uncertainties option.

● Initial version of the document.

Changes Made

For the most up-to-date information about Altera products, go to the

Altera world-wide web site at www.altera.com. For technical support on

this product, go to www.altera.com/mysupport. For additional

information about Altera products, consult the sources shown below.

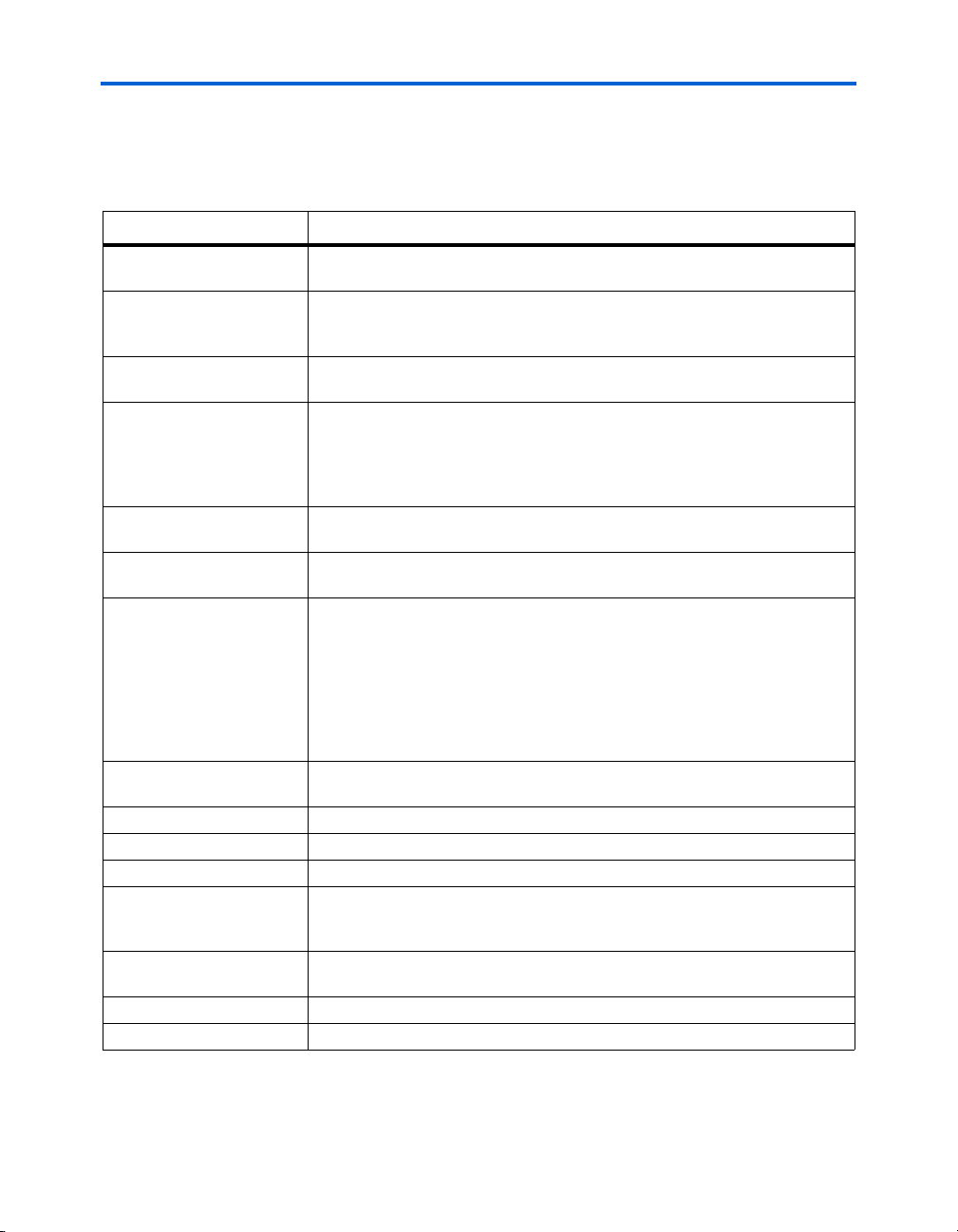

Information Type USA & Canada All Other Locations

Technical support www.altera.com/mysupport/ www.altera.com/mysupport/

Product literature www.altera.com (1) www.altera.com (1)

Altera literature services literature@altera.com literature@altera.com

FTP site ftp.altera.com ftp.altera.com

Note to table:

(1) You can also contact your local Altera sales office or sales representative.

Altera Corporation v

November 2007 Preliminary

Page 6

Typographic Conventions DDR Timing Wizard User Guide

Typographic

This document uses the typographic conventions shown below.

Conventions

Visual Cue Meaning

Bold Type with Initial

Capital Letters

bold type External timing parameters, directory names, project names, disk drive names,

Italic Type with Initial Capital

Letters

Italic type Internal timing parameters and variables are shown in italic type.

Initial Capital Letters Keyboard keys and menu names are shown with initial capital letters. Examples:

“Subheading Title” References to sections within a document and titles of on-line help topics are

Courier type Signal and port names are shown in lowercase Courier type. Examples: data1,

1., 2., 3., and

a., b., c., etc.

● • Bullets are used in a list of items when the sequence of the items is not important.

■

v The checkmark indicates a procedure that consists of one step only.

1 The hand points to information that requires special attention.

c

w

r The angled arrow indicates you should press the Enter key.

f The feet direct you to more information on a particular topic.

Command names, dialog box titles, checkbox options, and dialog box options are

shown in bold, initial capital letters. Example: Save As dialog box.

filenames, filename extensions, and software utility names are shown in bold

type. Examples: f

Document titles are shown in italic type with initial capital letters. Example: AN

75: High-Speed Board Design.

Examples: t

Variable names are enclosed in angle brackets (< >) and shown in italic type.

Example: <file name>, <project name>.pof file.

Delete key, the Options menu.

shown in quotation marks. Example: “Typographic Conventions.”

PIA

, \qdesigns directory, d: drive, chiptrip.gdf file.

MAX

, n + 1.

tdi, input. Active-low signals are denoted by suffix n, e.g., resetn.

Anything that must be typed exactly as it appears is shown in Courier type. For

example:

actual file, such as a Report File, references to parts of files (e.g., the AHDL

keyword

Courier.

Numbered steps are used in a list of items when the sequence of the items is

important, such as the steps listed in a procedure.

The caution indicates required information that needs special consideration and

understanding and should be read prior to starting or continuing with the

procedure or process.

The warning indicates information that should be read prior to starting or

continuing the procedure or processes

c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an

SUBDESIGN), as well as logic function names (e.g., TRI) are shown in

vi Altera Corporation

Preliminary November 2007

Page 7

1. About the DDR Timing Wizard

Release Information

Table 1–1 shows the first Quartus® II software version that supports the

DDR Timing Wizard (DTW) Tcl script for each device family. The

dtw_timing_analysis.tcl script supports Quartus II version 6.0 SP1 and

higher.

Table 1–1. DTW Release Information

Device Family Quartus II Version

Stratix®III (1)

Stratix II 5.1

Stratix II GX 6.0

®

HardCopy

Cyclone

Note to Ta b l e 1– 1 :

(1) Stratix III support is only for migration of legacy PHY designs from Stratix II

II

®

II

devices. Any new Stratix III designs containing a memory interface must use the

ALTMEMPHY-based controllers. DTW and the dtw_timing_analysis.tcl script

do not support ALTMEMPHY.

6.1

5.1

6.0

Use DTW and the dtw_timing_analysis.tcl script to constrain and report

your memory interface timing when using the legacy integrated static

data path and controller.

1 The legacy integrated static data path and controller is referred

to as the legacy controller from this point onwards in this

document.

f Altera

®

also offers memory interfaces with dynamically calibrated

resynchronization using the ALTMEMPHY megafunction. For more

information about ALTMEMPHY-based memory controllers, refer to the

ALTMEMPHY Megafunction User Guide.

Altera Corporation 1–1

November 2007

Page 8

Device Family Support

Device Family

Support

Introduction

The DTW Tcl script provides full support for the target Altera device

families and memory interfaces listed in Table 1–2. In Quartus II software

version 6.0 SP1, the dtw_timing_analysis.tcl script was created to

supplement DTW. The dtw_timing_analysis.tcl script supports the same

device family and external memory interface combinations as the DTW.

Table 1–2. Device Family and External Memory Support for Quartus II

version 7.2

Device Family External Memory Supported (2)

Stratix III (1) DDR2/DDR SDRAM, QDRII+/QDRII SRAM, RLDRAM II

Stratix II DDR2/DDR SDRAM, QDRII+/QDRII SRAM, RLDRAM II

Stratix II GX DDR2/DDR SDRAM, QDRII+/QDRII SRAM, RLDRAM II

HardCopy II DDR2/DDR SDRAM, QDRII+/QDRII SRAM, RLDRAM II

Cyclone II DDR2/DDR SDRAM

Notes to Ta b l e 1– 2

(1) DTW support for Stratix III devices is only for design migration from Stratix II

devices. Any new Stratix III designs containing a memory interface must use the

ALTMEMPHY solution. DTW and the dtw_timing_analysis.tcl script do not

support ALTMEMPHY.

(2) DTW constrains the data path timing for these memory interfaces. The example

driver and the controller are not constrained by the DTW.

:

External memory interfaces have timing requirements that must be met

for both the FPGA and the memory devices. Some timing requirements,

such as controller f

, can be analyzed by the Quartus II software and

MAX

easily met, but some timing requirements need further analysis or

manual handling. To meet these timing requirements, you should

constrain the placements of the registers or specify timing constraints for

the Quartus II software to optimize during compilation.

Background

Previously, the legacy controller MegaWizard generated a script to

constrain critical registers for the system called

auto_add_ddr_constraints.tcl. This script was used with the

verify_timing.tcl script, which was run to verify the system timing based

on these constraints. The verify_timing.tcl script, however, made some

assumptions that may not have been true for your design. For example,

the verify_timing.tcl script assumed that all clocks used for the memory

interface were using the global clock networks, so if you used a regional

clock network, some of the timing reported by the verify_timing.tcl

script may not have been accurate.

1–2 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 9

About the DDR Timing Wizard

1 The new ALTMEMPHY megafunction, introduced in Quartus II

version 6.1 uses timing constraints generated by the

ALTMEMPHY MegaWizard, so that you do not need to use

DTW to constrain the design. DTW does not support

ALTMEMPHY-based memory controllers.

In addition to possible inaccurate assumptions of the design, placement

constraints did not work well for designs migrating to HardCopy II or

other FPGA devices. When migrating designs, especially to a HardCopy

II device, you would need two different sets of placement constraints: one

for the FPGA prototype device and one for the HardCopy production

device. This also applies when migrating designs to a different FPGA

device.

DDR Timing Wizard

The DDR Timing Wizard (DTW) is a Tcl-based GUI that calculates timing

constraints based on the FPGA and memory device chosen. It simplifies

the process of constraining your design by using timing assignments,

which the Quartus II software uses to place and route the design in the

target device. These timing constraints are applicable for FPGAs and their

HardCopy-equivalent devices, eliminating the need to convert

assignments for the different device families (as you would have

previously done with the placement constraints from legacy controller

MegaWizard). Some critical register placements can be constrained by

using LogicLock region assignments, but other than the pin location,

output pin load, and I/O standards assignments, you do not need any

hard placement constraints. Instead, the timing-driven compilation of the

Quartus II software ensures that all DTW timing constraints are met in

both FPGA-prototype and HardCopy-production devices.

DTW also gives you the ability to change the pin names of the memory

interface to use regional clock networks, and to use TimeQuest Timing

Analyzer to analyze the design, which are not supported by the

verify_timing.tcl script. DTW constraints also lead to a more accurate

timing analysis, as all the information used are based on your particular

design, instead of general assumptions made by the MegaWizard.

Furthermore, the timing verification script does not report write timing

margin. DTW, on the other hand, constrains timing for the write path,

allowing Quartus II to analyze the write timing margin. You can then use

the dtw_timing_analysis.tcl script to report read, write,

address/command, resynchronization, and postamble timing margins

that are applicable to your memory interface design. DTW constraints

provide more accurate timing results compared to the verify_timing.tcl

script.

Altera Corporation 1–3

November 2007 DDR Timing Wizard User Guide

Page 10

Introduction

1 Critical resynchronization register placement constraints

provided by the legacy controller MegaWizard can still be used

even when DTW is used. You can use LogicLock regions in lieu

of hard placement constraints.

1 The results reported by the dtw_timing_analysis.tcl script have

no correlation with the verify_timing.tcl script. You should rely

on the dtw_timing_analysis.tcl report, as it is more accurate

due to the design-specific constraints created by the DTW. The

verify_timing.tcl script may have some assumption that does

not apply to your particular design.

To use the DTW, you must enter the memory device parameters and your

board information correctly in the legacy controller MegaWizard. The

Quartus II Fitter uses timing-driven compilation to route the design to

meet the timing constraints set by the DTW.

Because the DTW is primarily a constraining tool, the

dtw_timing_analysis.tcl script is provided to help you analyze and close

timing with a minimum number of compilations. The

dtw_timing_analysis.tcl script extracts the system timing margin by

re-running timing analysis if needed, adjusting the clock cycles in the

DTW (with the -auto_adjust_cycles switch) if required, and

suggesting the ideal phase shifts for the system. The

dtw_timing_analysis.tcl is backwards-compatible with designs

constrained with an older version of DTW. Both DTW and the

dtw_timing_analysis.tcl scripts are available in the Quartus II

installation directory.

1 If you use the default installation directory, the DTW and

dtw_timing_analysis.tcl scripts are available in the

c:\altera\<version>\quartus\common\tcl\apps\

gui\dtw directory.

1–4 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 11

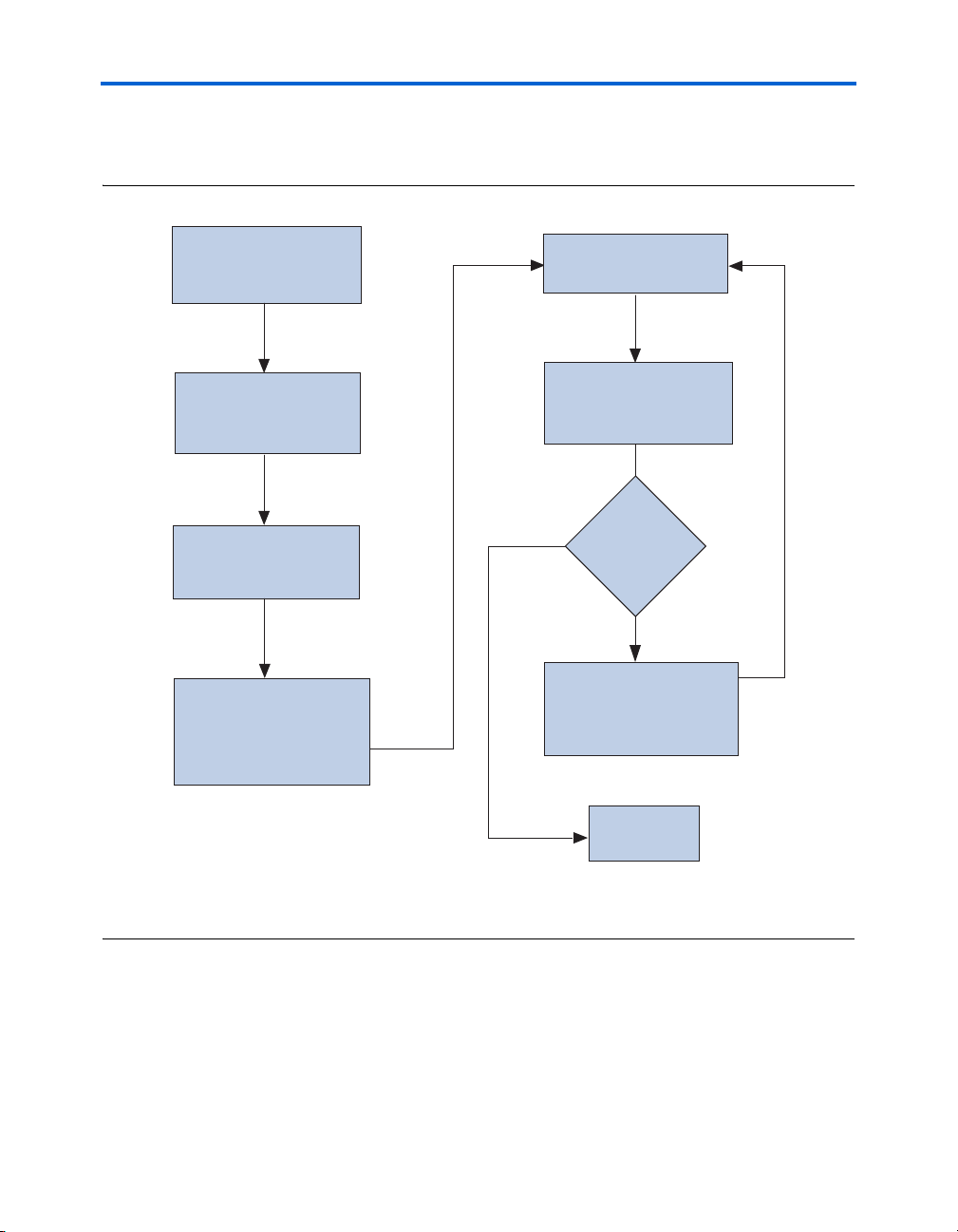

Figure 1–1 shows the typical Quartus II external memory design flow

using DTW and the dtw_timing_analysis.tcl script.

Figure 1–1. Quartus II External Memory Design Flow

Instantiate PHY

and Controller in a

Quartus II Project

About the DDR Timing Wizard

Compile Design

Run add_constraints.tcl

(Pin Locations,

I/O Standards, and Loading)

Run DTW

(Timing Constraints)

Add Assignments for Clock,

Command, and Address Pin

Locations, and Other Pertinent

Assignments for the Interface

Run dtw_timing_analysis.tcl

to Get Margin and

Recommended Settings

Memory

Interface Timing

Adjust Constraints

Using the MegaWizard,

the Assignment Editor,

or the DTW

Ye s

(1)

Is

Met?

No

Done

Note to Figure 1–1:

(1) It may be necessary to modify the controller and PHY settings (such as the clock cycles and clock phase shifts) using

the legacy controller or the altpll MegaWizard, based on dtw_timing_analysis.tcl results.

This user guide explains how to constrain designs using DTW, how to

analyze the memory interface timing using the dtw_timing_analysis.tcl

script, and how to adjust design constraints using the MegaWizard, the

Assignment Editor, or DTW to achieve timing closure.

Altera Corporation 1–5

November 2007 DDR Timing Wizard User Guide

Page 12

Features

Features

The DDR Timing Wizard has the capability to:

■ Constrain a design with one or multiple memory controllers that

may reside in subdirectories of the main project.

■ Calculate all of the timing constraints based on your chosen FPGA or

HardCopy device, and memory device.

■ Import timing information from the legacy controller MegaWizard.

■ Enable timing driven compilation.

■ Allow the Quartus II software to analyze and report the

post-compile timing analysis for both fast and slow timing models in

one panel.

■ Create both classic timing analyzer and TimeQuest Timing Analyzer

assignments for memory interface timing paths.

The dtw_timing_analysis.tcl script complements the DTW with the

ability to:

■ Extract and report system timing margin for both fast and slow

model timing.

■ Re-run timing analysis using either the Classic Timing Analyzer or

TimeQuest Timing Analyzer.

■ Adjust resynchronization and postamble clock cycles in DTW.

■ Calculate ideal PLL phase shifts.

■ Import legacy controller MegaWizard settings into DTW (with the

option to compile the design after the import).

■ Update design t

information in DTW.

CO

1–6 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 13

2. Getting Started

System and Software Requirements

Design Flow

The instructions in this section require Quartus II software version 7.2 or

higher. DTW and the dtw_timing_analysis.tcl script can be found in the

Quartus II installation directory. You can either run the script from that

directory or copy the script to your project directory.

1 If you use the default installation directory, the DTW and

dtw_timing_analysis.tcl script are available in the

c:\altera\<version>\quartus\common\tcl\apps\

gui\dtw directory.

The design flow when creating a system with external memory interfaces

is as follows:

1. Create a memory interface PHY with Altera’s legacy memory

controller MegaWizard.

f For more information about how to create a memory

controller, refer to the DDR & DDR2 SDRAM Controller

Compiler User Guide, QDRII SRAM Controller MegaCore

Function User Guide, and RLDRAM II Controller MegaCore

Function User Guide. Follow the instructions up to

generating the core, but do not compile the design yet.

®

f To create an example design, follow the Instantiate PHY

and Controller in a Quartus II Project step of the

"Example Walkthrough for 267-MHz DDR2 SDRAM

Interface using the Legacy PHY" section in AN328:

Interfacing DDR2 SDRAM with Stratix II, Stratix II GX, and

Arria GX Devices.

If you are not using the Altera memory controller, remove the

encrypted controller produced by the legacy controller MegaWizard

and connect the Altera-recommended data path from the legacy

controller MegaWizard with your memory controller.

2. Run the auto_add_ddr_constraints.tcl script produced by the

legacy controller MegaWizard for pin location, I/O standard,

output pin load, and register placement assignments for the

resynchronization and postamble registers in DDR2/DDR SDRAM

interfaces.

Altera Corporation 2–1

November 2007

Page 14

Design Flow

1 You do not need to remove these location assignments

when using DTW even though DTW makes the correct

timing constraints for the paths to these registers.

To locate the auto_add_ddr_constraints.tcl script, on the Tools

menu, click Tcl Scripts. The script is under the Project folder.

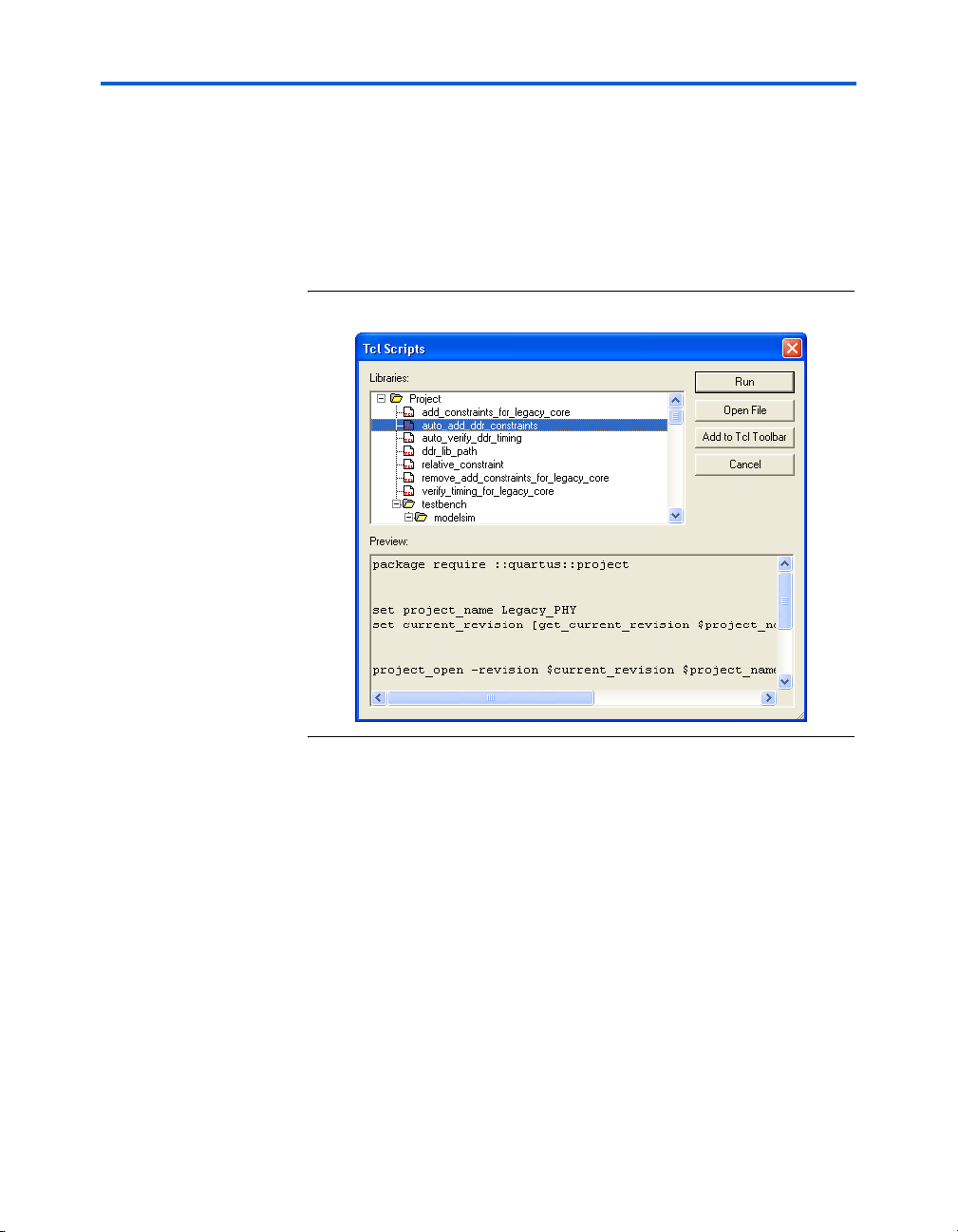

(Figure 2–1).

Figure 2–1. Add Constraints TCL Script

After running the auto_add_ddr_constraints.tcl script, assign the

other pin locations, I/O standards, and loading for the design. The

legacy controller MegaWizard does not make pin location

constraints for the command, address, input, and output clock pins.

You can add those constraints using the Quartus II Pin Planner or the

Quartus II Assignment Editor.

1 Place address, command, and clock pins in the same bank

as the DQS/DQ pins to minimize output skew.

3. Specify timing requirements using DTW.

Because the controller is generated by the legacy controller

MegaWizard, you can import the memory and board specifications

and pin names entered into the legacy controller MegaWizard

instead of manually entering them into the DTW. Also, DTW extracts

2–2 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 15

Getting Started

the names of the PLL clocks and registers (as needed) for the timing

requirements. It also extracts the phase shifts of synthesized PLLs.

The step-by-step instructions are listed in “Import Flow for the

Altera Legacy Memory Controller IP Core or Recommended Data

Path” on page 2–7.

1 You may need to re-run DTW and compile the design

multiple times before achieving timing closure. You can

close timing within two compiles if you do not need to

change the intermediate registers option in the legacy

controller MegaWizard.

4. Add other assignments for the design.

Add the following assignments in the Assignment Editor (unless

indicated otherwise) to the project before you compile the design:

● If you are using classic Timing Analyzer:

• In the Settings tab of the Assignment menu, uncheck the

Optimize hold timing option.

• In the Settings tab of the Assignment menu, uncheck the

Optimize fast corner timing option.

This disallows the Quartus II Fitter from optimize placement

each time the project is recompiled. Having these options

enabled may render your phase shift changes invalid because

the Quartus II Fitter has the priority to optimize for hold timing

and fast cornering.

You can re-enable the Optimize hold timing and Optimize fast

corner timing options for the remainder of the design after you

close timing on your memory interface. To ensure the memory

interface part of the design has similar timing, back-annotate

placements and routing for that portion of the design before reenabling the options.

● If you are using TimeQuest Timing Analyzer, add the

DTW-generated .sdc file to the project.

● Set the delay from Output Register to Output Pin to 0 for the

CK/CK# (clk_to_sdram*) clock outputs and fedback clock

output.

● Assign pin constraints for all the CK/CK# and feedback output

pins and ensure that the feedback output pins use the same I/O

Altera Corporation 2–3

November 2007 DDR Timing Wizard User Guide

Page 16

Design Flow

standard as the CK/CK# pins, and are placed on the same side

as the DQS/DQ pins.

● Assign pin location, I/O standard, and output pin load

constraints for clock_source, feedback input pins, and

address and command pins.

● For RLDRAM II memory interfaces created in Quartus II

version 7.2 and higher, add the

<variation_name>_controller.sdc file to the project

● For QDRII+/QDRII SRAM memory interfaces using TimeQuest

Timing Analyzer, convert the setup_relationship and

hold_relationship MegaWizard-generated constraints to

SDC constraints. The setup_relationship and

hold_relationship assignment can be directly converted to

set_max_delay and set_min_delay assignments, as shown

in the below example:

set_max_delay -0.2 -from * -to <resync_registers*>

set_min_delay -1.6 -from * -to <resync_registers*>

5. Compile the design.

6. Check the timing analysis results.

After completing a DTW design compilation, refer to Chapter 3,

Using the dtw_timing_analysis.tcl Script for information about

analyzing the memory interfaces.

If problem paths are reported, locate and fix them to maximize setup

and hold slack. For example, you can:

● Adjust PLL clock phases with the legacy controller or the

altpll MegaWizard.

1 Note that some clock phases can only be changed in the

legacy controller MegaWizard, especially for shared PLL

outputs. For example, if your postamble clock was set to 90°

initially, but you want to change it to use either a dedicated

clock or a 180° phase shift.

● Insert or remove intermediate resynchronization and/or

postamble registers in the legacy controller MegaWizard.

2–4 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 17

Getting Started

1 You need to insert intermediate resynchronization registers

when you have negative margin in the transfer between

resynchronization registers and the registers clocked by the

system clock. The dtw_timing_analysis.tcl script will tell

you when to add or remove the intermediate postamble

registers.

● Change the data path resynchronization and/or postamble

clock cycles in the legacy controller MegaWizard.

● Change location assignments to the problem PLL clocks, I/O

pins, or registers.

f Refer to Chapter 3, Using the dtw_timing_analysis.tcl

Script for information on how to fix your timing violations

using the dtw_timing_analysis.tcl script.

1 If you need to change any PLL phase shifts, re-run the

Quartus II Analysis and Synthesis to refresh the PLL

settings before importing the new phase shift in the DTW.

You can click on the Start Analyze & Synthesis button

manually or use the –after_iptb import option in the

dtw_timing_analysis.tcl script. You can also enter the PLL

phase shifts manually in the DTW to bypass Quartus II

Analysis and Synthesis. However, DTW will not be able to

confirm if the phase shift entered is the correct phase shift

that is implemented in the design.

If there are no failing paths, your design is complete. Otherwise, go

back to step 5 after making the necessary timing requirements

changes until the design achieves timing closure.

Launching the

To launch the DDR Timing Wizard from the Quartus II software, follow

these steps:

DDR Timing

Wizard

Altera Corporation 2–5

November 2007 DDR Timing Wizard User Guide

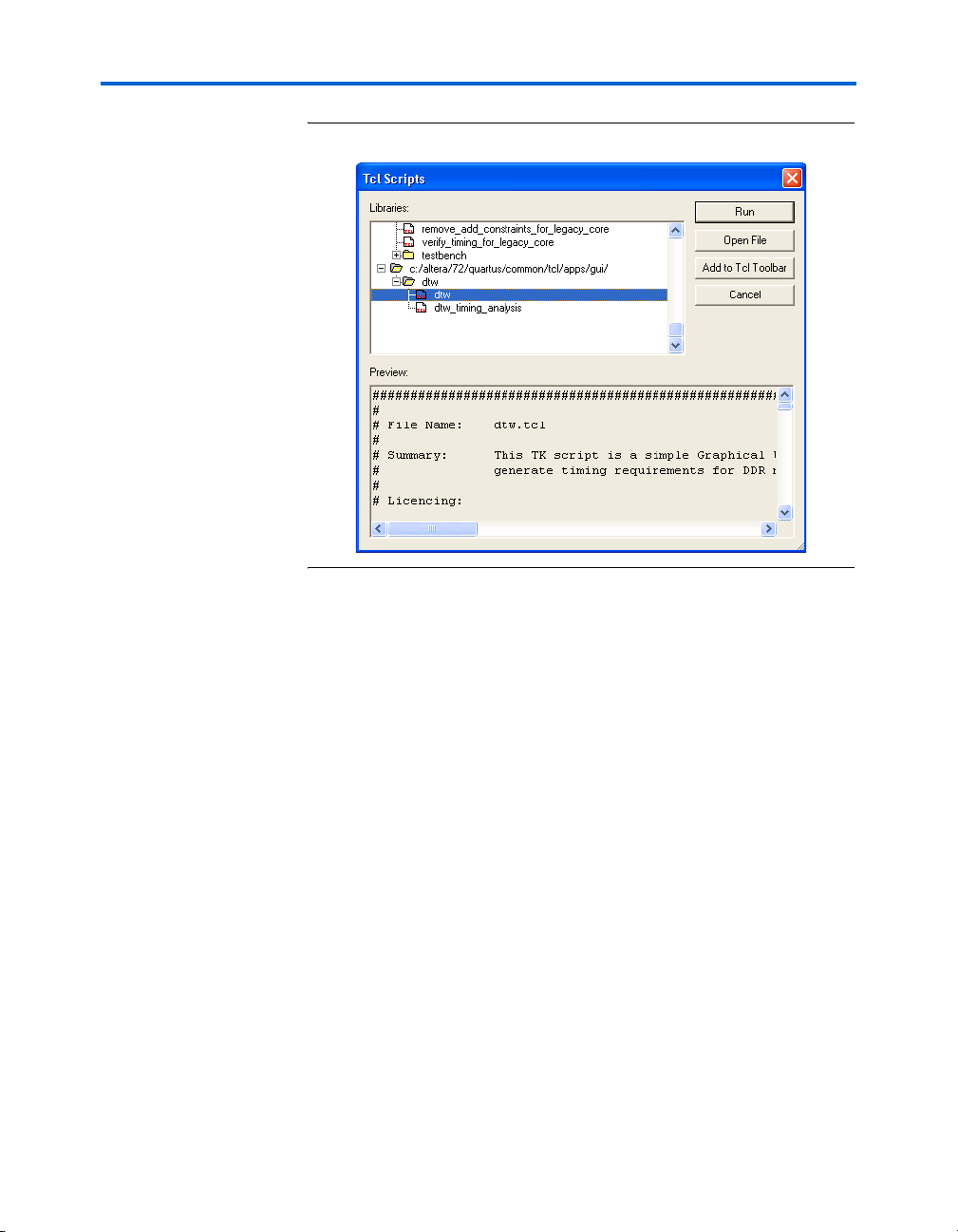

1. On the Tools menu, click Tcl S c r i pt s.

2. In the Tcl Scripts dialog box, under Libraries, expand the

<installation_directory>/quartus/common/tcl/apps/gui/dtw

folder, select dtw (Figure 2–2).

Page 18

Entering and Editing Inputs to the DTW

Figure 2–2. Launching the DDR Timing Wizard

3. Click Run.

1 You can also launch the DTW from the command line with

the following command:

<quartus_ii_installation_directory>/bin/quartus_sh --dtw

Entering and

Editing Inputs to

the DTW

2–6 Altera Corporation

DDR Timing Wizard User Guide November 2007

If you use the Altera legacy controller MegaWizard as a starting point for

your memory interfaces, follow the import flow described below to enter

and edit inputs to the DTW. The legacy controller MegaWizard is the

recommended tool, and simplifies entry of the essential design

requirements. If you have an interface that is not supported by the legacy

controller MegaWizard , refer to “Manual Flow for Other External

Memory Interfaces or Source Synchronous Systems” on page 2–14.

1 The screen captures of the DTW pages shown in this section are

from the Legacy_PHY.qar design that is downloadable with

AN328: Interfacing DDR2 SDRAM in Stratix II, Stratix II GX, and

Arria GX Devices.

Page 19

Getting Started

1 You do not need to perform Quartus II Analysis and Synthesis

the first time you run DTW as this has been done when running

the auto_add_ddr_constraints.tcl script. However, any

subsequent calls to the DTW must be preceded with a Quartus II

Analysis and Synthesis process, otherwise DTW will not be able

to read any changes to the design.

Import Flow for the Altera Legacy Memory Controller IP Core or Recommended Data Path

When you use the Altera-provided data path, you can benefit by

importing the memory data path settings, which saves time because

parameters required by the DTW do not need to be filled in manually. If

you choose to create your own data path, you can find more information

about the DTW pages in “Manual Flow for Other External Memory

Interfaces or Source Synchronous Systems” on page 2–14.

The following procedure illustrates a DDR/DDR2 SDRAM interface

example, but the steps are identical for the QDRII+/QDRII SRAM or the

RLDRAM II interface. Before performing the following steps, be sure to

run the legacy controller MegaWizard auto_add_ddr_constraints.tcl

script and run Quartus II Analysis and Synthesis.

After launching the DTW, follow these steps to import the timing

parameters and pin names from the legacy controller MegaWizard:

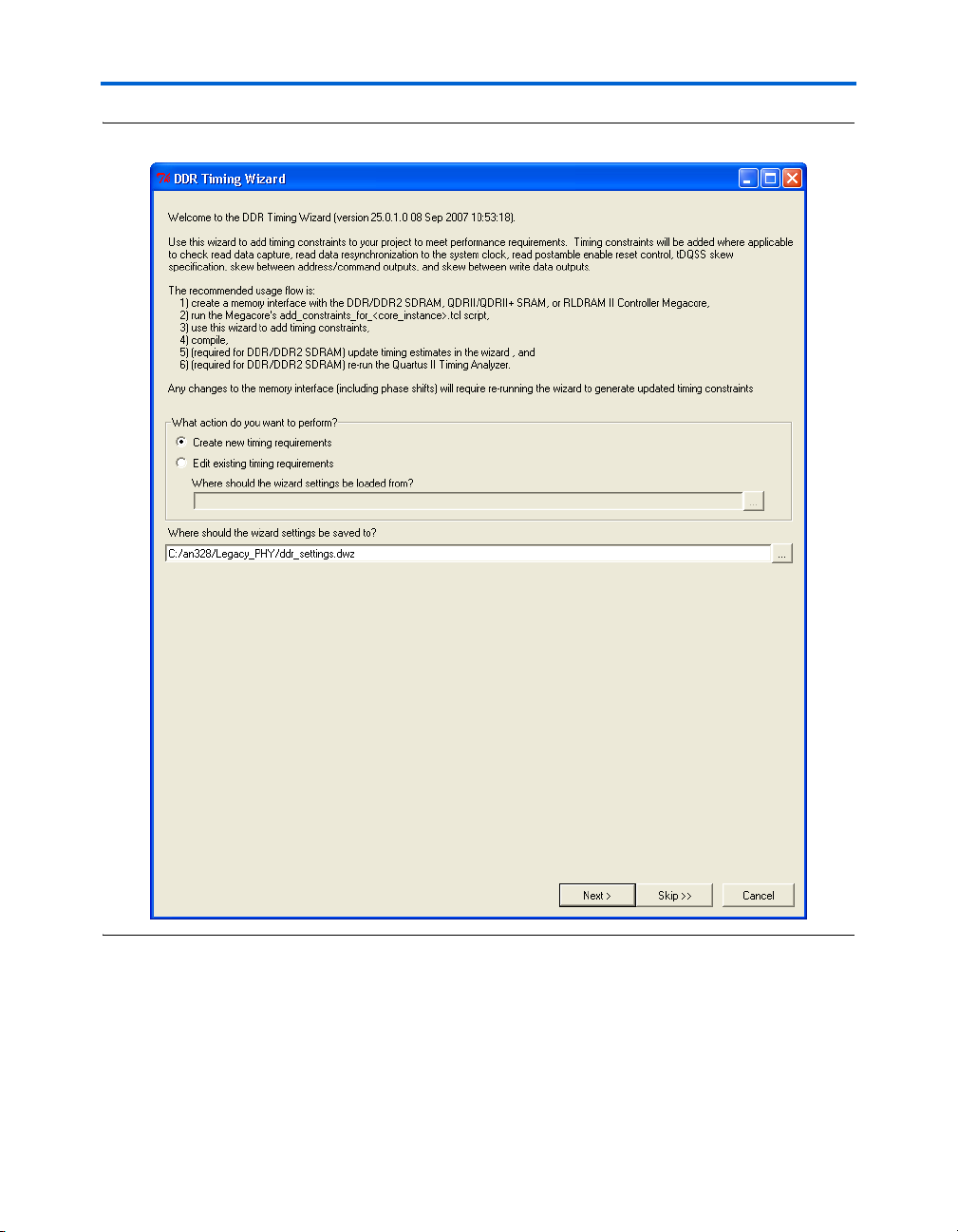

1. On the first page of the DTW, you are prompted to create or edit a

.dwz file. Opening the DTW allows you to make changes to the

saved .dwz file or to create a new .dwz file. This file contains all of

the parameters you enter in the DTW script.

Figure 2–3 shows the first page of the DTW software in which you

can specify the location for the .dwz file. The default name and

location for the file is:

<quartus_ii_project_directory>/ddr_settings.dwz

Ensure that the .dwz file points to the project directory that you are

working on. If you have un-archived the project, the .dwz file may

still be pointing to the old project directory. You can change the file

name and click Next.

1 The saved file name always defaults to ddr_setting.dwz.

Ensure that it is the file name you want to use. If you have

multiple memory controllers in a design, you must have a

unique .dwz file name for each controller.

Altera Corporation 2–7

November 2007 DDR Timing Wizard User Guide

Page 20

Entering and Editing Inputs to the DTW

Figure 2–3. First Page of the DDR Timing Wizard—Create or Edit File

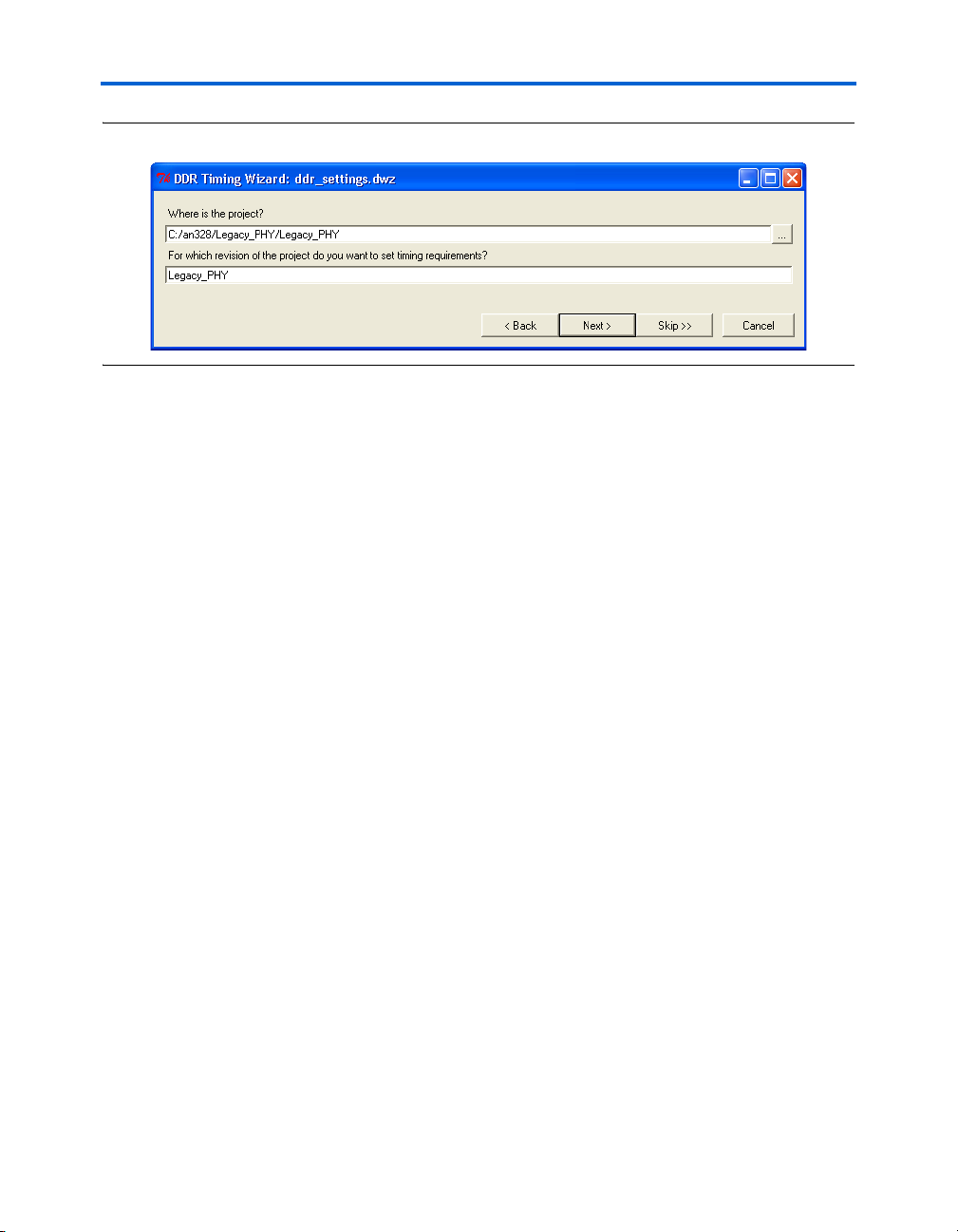

2. Page 2 of the DTW (Figure 2–4) asks you to confirm the project

directory and the revision you want to use. (Note that the project

name is case-sensitive.) The DTW automatically fills in the fields,

but you can change those fields if the project has been moved or if

you have a newer revision. Click Next.

2–8 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 21

Figure 2–4. Page 2 of the DTW—Confirm the Project Directory and Revision Name

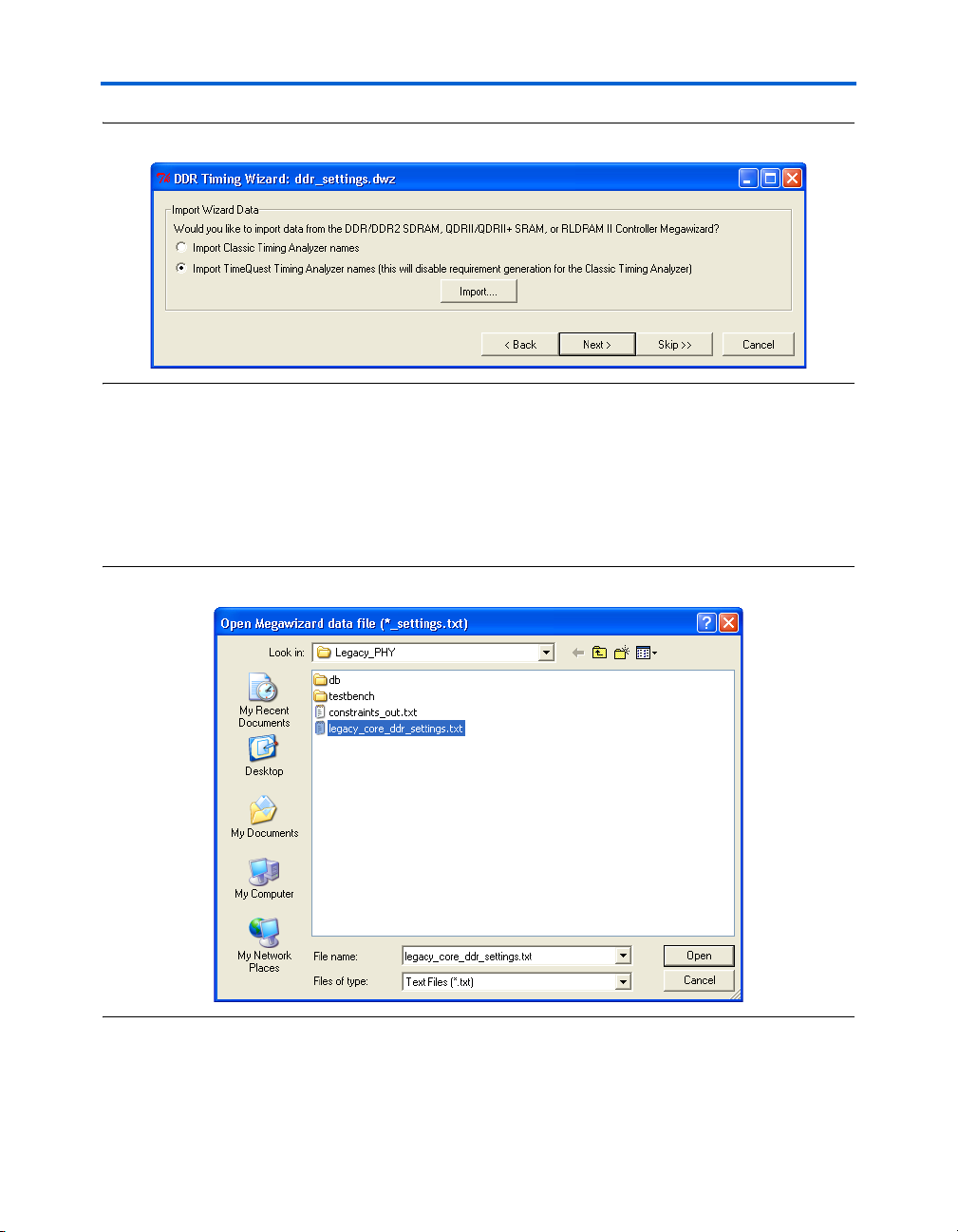

3. Figure 2–5 shows page 3 of the DTW. This page asks whether you

would like to import data from the legacy controller MegaWizard

instance using Classic Timing Analyzer or TimeQuest Timing

Analyzer names.

If you choose TimeQuest Timing Analyzer names, DTW creates

assignments that are stored in an .sdc file. Choosing Classic Timing

Analyzer names generates both .qsf assignments and an .sdc file.

This means that you can still use TimeQuest Timing Analyzer for

compilation and timing analysis even when you choose Classic

Timing Analyzer names.

Getting Started

You need to add the .sdc file to the project when using TimeQuest

Timing Analyzer for compilation and timing analysis.

1 The difference between the .sdc file created using Classic

Timing Analyzer and TimeQuest Timing Analyzer names

is the clock name convention. There should not be any

difference in timing analysis results between these two .sdc

files.

1 You should use TimeQuest Timing Analyzer for a more

accurate timing analysis as the constraints of the .sdc file

apply to both fast and slow timing models.

Click Import.

Altera Corporation 2–9

November 2007 DDR Timing Wizard User Guide

Page 22

Entering and Editing Inputs to the DTW

Figure 2–5. Page 3 of the DTW—Importing Data from the Legacy Controller MegaWizard

4. Choose the location from which to import the data. Select

<core_variation_name>_<ddr|qdr|rldramii>_settings.txt from the

project directory. The example in Figure 2–6 uses a the DDR2

SDRAM controller named legacy_core, so the DTW must import

data from the legacy_core_ddr_settings.txt file generated by the

legacy controller MegaWizard.

Figure 2–6. Choose the <core_variation_name>_<ddr|qdr|rldramii>_settings.txt File to be Imported

5. The DTW then imports data from the

<core_variation_name>_<ddr|qdr|rldramii>_settings.txt file.

This process may take some time if your design is large.

2–10 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 23

Getting Started

1 The DTW can extract the names of PLL clocks, PLL phase

shifts, and names of registers, if you have already run the

Quartus II Analysis and Synthesis. The

auto_add_ddr_constraints.tcl script automatically

analyzes and synthesizes the design, so you do not have to

perform Quartus II Analysis and Synthesis the first time

you invoke DTW after running the

auto_add_ddr_constraints.tcl script. However, any time

you make a change in the PLL or the legacy controller

MegaWizard, you need to analyze and synthesize the

design before invoking DTW, so that DTW can extract the

correct clock names and phase shifts when performing an

Import function.

When the import is complete, click Skip to get to the last page of

DTW.

1 Instead of skipping to the end, you can verify the values in

the DTW by clicking Next and checking each page of the

DTW to ensure that everything is imported correctly. These

pages are described in detail in “Manual Flow for Other

External Memory Interfaces or Source Synchronous

Systems” on page 2–14.

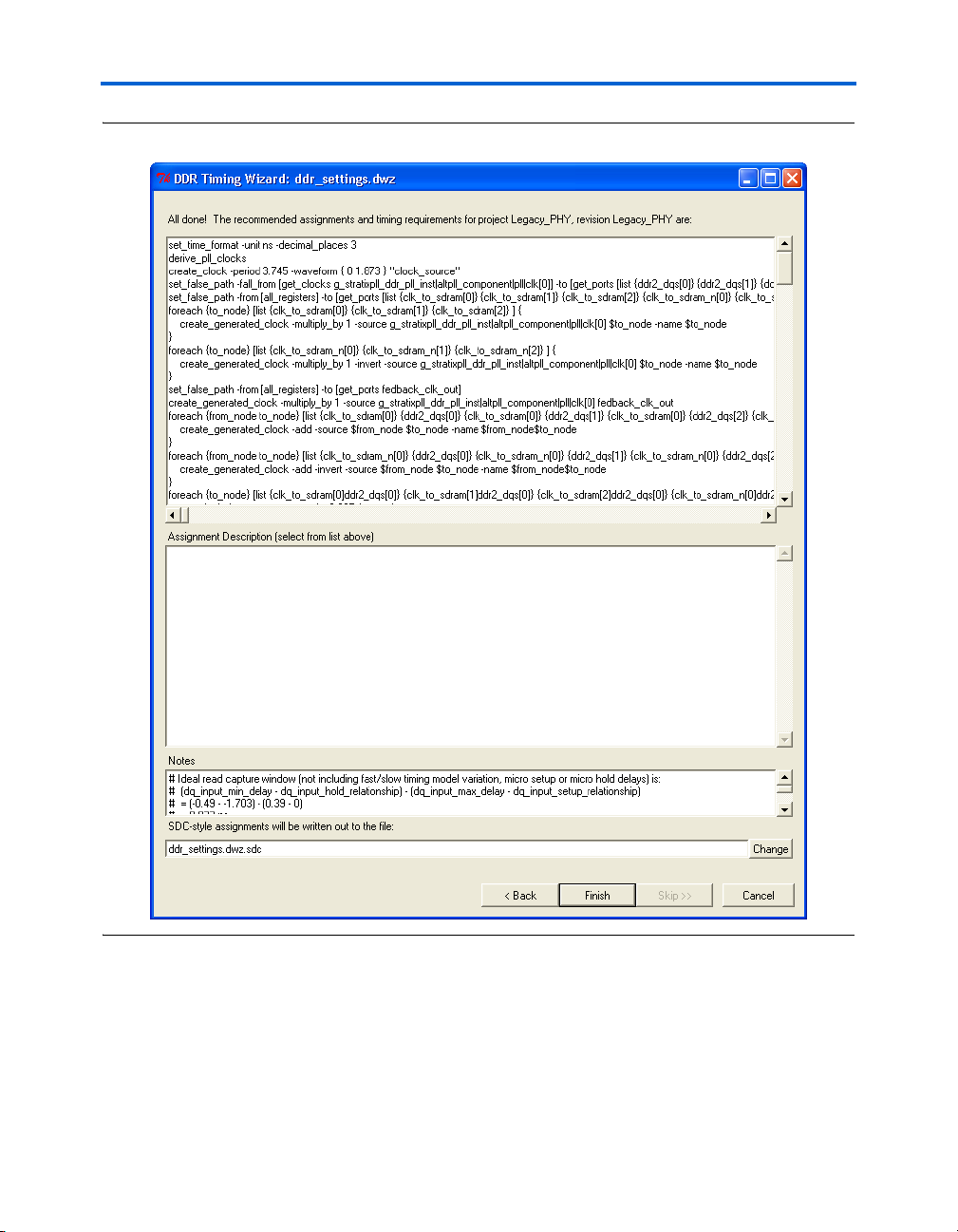

At this point, if the DTW has all of the needed information, a page

similar to the one shown in Figure 2–7 appears. Click Finish.

Altera Corporation 2–11

November 2007 DDR Timing Wizard User Guide

Page 24

Entering and Editing Inputs to the DTW

Figure 2–7. Timing Assignments to be Added to the Project

When using Classic Timing Analyzer, the last page of the DTW

names looks a little different than Figure 2–7. This is described in

more detail in “Manual Flow for Other External Memory Interfaces

or Source Synchronous Systems” on page 2–14.

2–12 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 25

If DTW failed to extract PLL clock information during the import

step, it asks you to input this information manually. The PLL Phase

Shift Selection page (Figure 2–8) then displays a warning indicating

“Missing required PLL clock info.” Figure 2–8 shows an example in

which the DTW cannot find the resynchronization clock from the

system PLL.

Figure 2–8. PLL Phase Shift Selection Page

Getting Started

Altera Corporation 2–13

November 2007 DDR Timing Wizard User Guide

Page 26

Entering and Editing Inputs to the DTW

After entering the resynchronization clock name (omitted in

Figure 2–8) click Skip to get to the last page of DTW.

Click Finish.

6. Add the additional assignments as listed on Step 4 of the “Design

Flow” section.

7. Compile the design and perform timing analysis.

f For more details, refer to Chapter 3, Using the dtw_timing_analysis.tcl

Script.

Manual Flow for Other External Memory Interfaces or Source Synchronous Systems

Use this flow when you have a custom implementation for an

Altera-supported memory interface, including the following:

■ DDR/DDR2 SDRAM

■ QDRII+/QDRII SRAM

■ RLDRAM II

1 Always implement the Altera data path and use the legacy

controller MegaWizard flow unless the feature set of the Altera

memory controller makes it impossible to do so.

The DTW Pages for DDR/DDR2 SDRAM

This section details each page in the DDR/DDR2 SDRAM interface. The

pages for QDRII+/QDRII SRAM and RLDRAM II interfaces are slightly

different than the pages for DDR/DDR2 SDRAM interfaces. The DTW

pages for QDRII+/QDRII SRAM and RLDRAM II are listed in “The DTW

Pages for QDRII+/QDRII SRAM & RLDRAM II” on page 2–45.

1 The following page-by-page information is based from a

controller created by the legacy controller MegaWizard but the

DTW import option is not used.

1. On the Tools menu, select Tc l S c r i pt s. Select dtw and click Run.

2. Specify a .dwz file name to save the timing constraints for the

design and click Next.

3. Confirm the project directory and revision you want to use.

Click Next.

2–14 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 27

Getting Started

4. Page 3 asks if you want to import data from the legacy controller

MegaWizard, and whether you want to use TimeQuest or Classic

Timing Analyzer names. Click on one of the radio buttons (even if

you are not using the Import function) and click Next.

5. Select your memory type: DDR/DDR2 SDRAM, QDRII+/QDRII

SRAM or RLDRAM II. For this example, choose DDR/DDR2

SDRAM. Refer to Figure 2–9.

Altera Corporation 2–15

November 2007 DDR Timing Wizard User Guide

Page 28

Entering and Editing Inputs to the DTW

Figure 2–9. Select Memory Type

6. Select the appropriate memory device from the drop-down menu

(Figure 2–10).

The rest of the fields are filled in automatically when you pick a

device. Click Next.

2–16 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 29

Figure 2–10. Select Memory Device

Getting Started

1 If you do not find your memory device in the pull-down

menu, select Custom, and fill in the other fields from the

memory device datasheet.

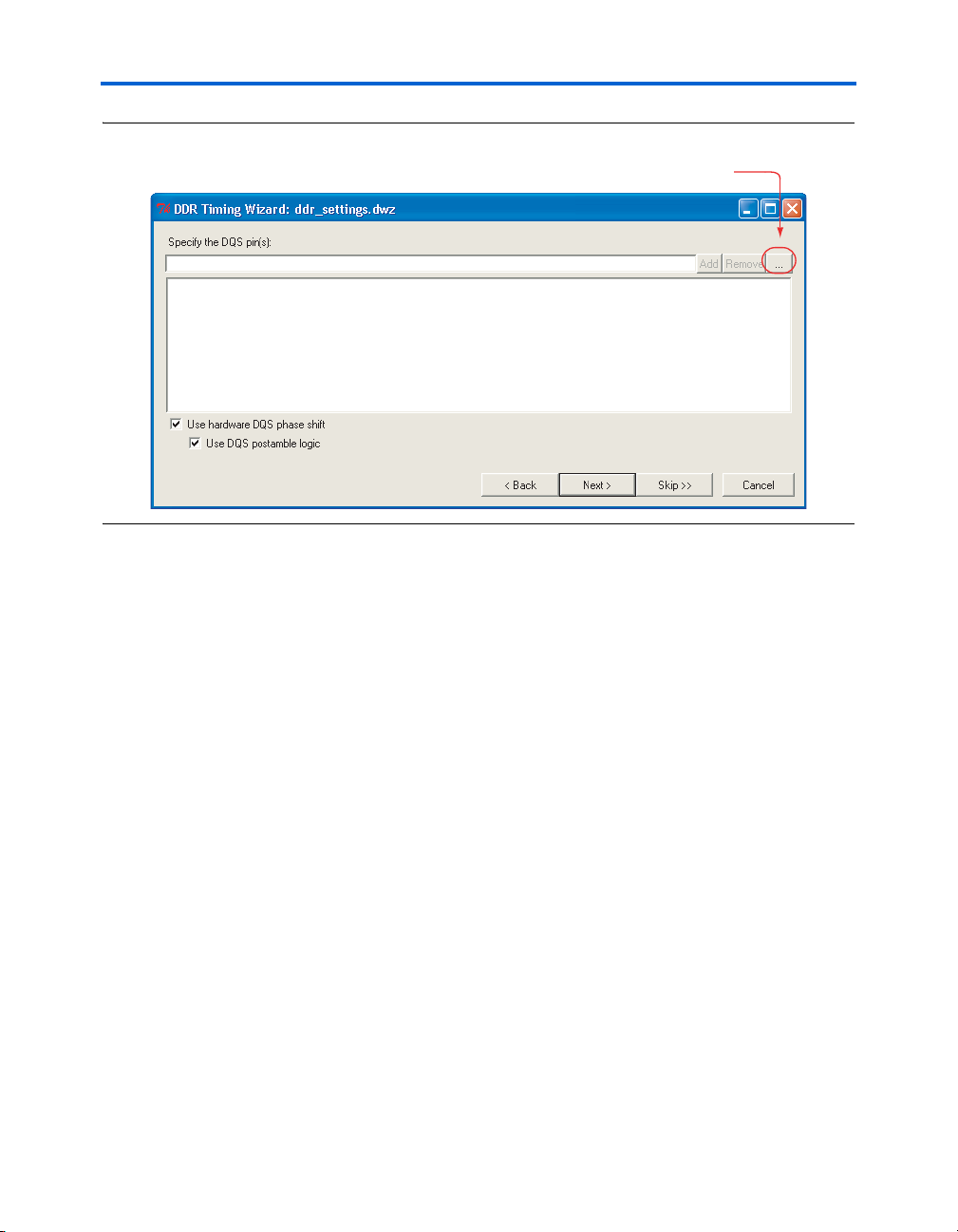

7. You must fill in the interface signal names in the subsequent pages.

First, specify whether you are using the DQS mode (using DLL for

read capture) or the non-DQS mode (using PLL for read capture).

Indicate whether you are using the DQS postamble circuitry. (DQS

mode and postamble circuitry are recommended whenever

possible.) Figure 2–11 shows the DTW page with the DQS mode and

DQS postamble check boxes checked at the bottom of the page.

Altera Corporation 2–17

November 2007 DDR Timing Wizard User Guide

Page 30

Entering and Editing Inputs to the DTW

Figure 2–11. Specify DQS Pins

You can either manually enter each of the DQS pin names, or click on

the Browse (...) button to open the Node Name Browser

(Figure 2–12).

Browse

1 If you are using the Altera DDR/DDR2 SDRAM controller,

the default names for the pins have ddr or ddr2 prefixes.

You can change the prefix in the DDR/DDR2 SDRAM

legacy controller MegaWizard. The default prefixes for

QDRII+/QDRII SRAM and RLDRAM II interfaces are

qdrii and rldramii, respectively.

1 If your design is large, browsing for a node name may be

very labor-intensive. Manually enter the pin names

whenever possible.

If you followed the recommended flow, you should have already

performed Analysis and Synthesis on the design, when

auto_add_ddr_constraints.tcl script was run. If so, the Quartus II

software will list all of the pin names, as shown in Figure 2–12.

2–18 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 31

If you have not performed Analysis and Synthesis on the design, the

Node Name Browser page will not have any nodes listed under

Nodes Found. If this is the case, click on the Analysis and Synthesis

button (Figure 2–12).

Figure 2–12. Node Name Browser of a Sample DDR2 SDRAM Interface

Analysis & Synthesis

Getting Started

To use the node name browser to add the DQS pin names, perform

the following steps:

a. Highlight the DQS pin names under Nodes Found and click the

arrow button to move the pins to the Selected Nodes field

(Figure 2–13 and Figure 2–14).

Altera Corporation 2–19

November 2007 DDR Timing Wizard User Guide

Page 32

Entering and Editing Inputs to the DTW

Figure 2–13. Selecting the DQS Pins

Figure 2–14. DQS Pins Selected

2–20 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 33

b. The DQS pins are now displayed in the DTW GUI

(Figure 2–15).

Figure 2–15. Selected DQS Pin Names Transferred to the DTW

Getting Started

Click OK.

8. On the next page, list the DQ pins, DM pin, and postamble register

related to each DQS pin. Use the same method to enter these pins as

entering the DQS pin names on step 7. Figure 2–16 shows an

example of the DQ pins, DM pin, and postamble register for one

DQS pin.

Altera Corporation 2–21

November 2007 DDR Timing Wizard User Guide

Page 34

Entering and Editing Inputs to the DTW

1 The postamble register name from the Altera DDR2/DDR

SDRAM controller is listed in Figure 2–16. You can find this

register using the Node Finder in the Assignment Editor.

You can then copy the register name and add it into the

postamble register field. In designs targeting Stratix II,

Stratix II GX, Arria GX, or Hardcopy II devices, search for

these text in the Node Finder to find the postamble

registers: *dqs_io~regout*

After you enter the pins’ and registers’ names for each DQS pin, click

Next.

Figure 2–16. Sample Page of DQ Pins, DM Pin and Postamble Register for One DQS Pin

2–22 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 35

9. Identify the CK and CK# pins. The Altera DDR/DDR2 SDRAM

Controller uses clk_to_sdram and clk_to_sdram_n signal

names for CK and CK# pins, respectively, as shown in Figure 2–17.

Figure 2–17. Default CK & CK# Pin Names for the DDR/DDR2 SDRAM Controller

Getting Started

Click Next.

Altera Corporation 2–23

November 2007 DDR Timing Wizard User Guide

Page 36

Entering and Editing Inputs to the DTW

10. Identify the address and control pins. The sample list of the address

and control pins for a DDR2 SDRAM interface is shown in

Figure 2–18.

Figure 2–18. Sample Page of Filled Address and Control Pins Page

Click Next.

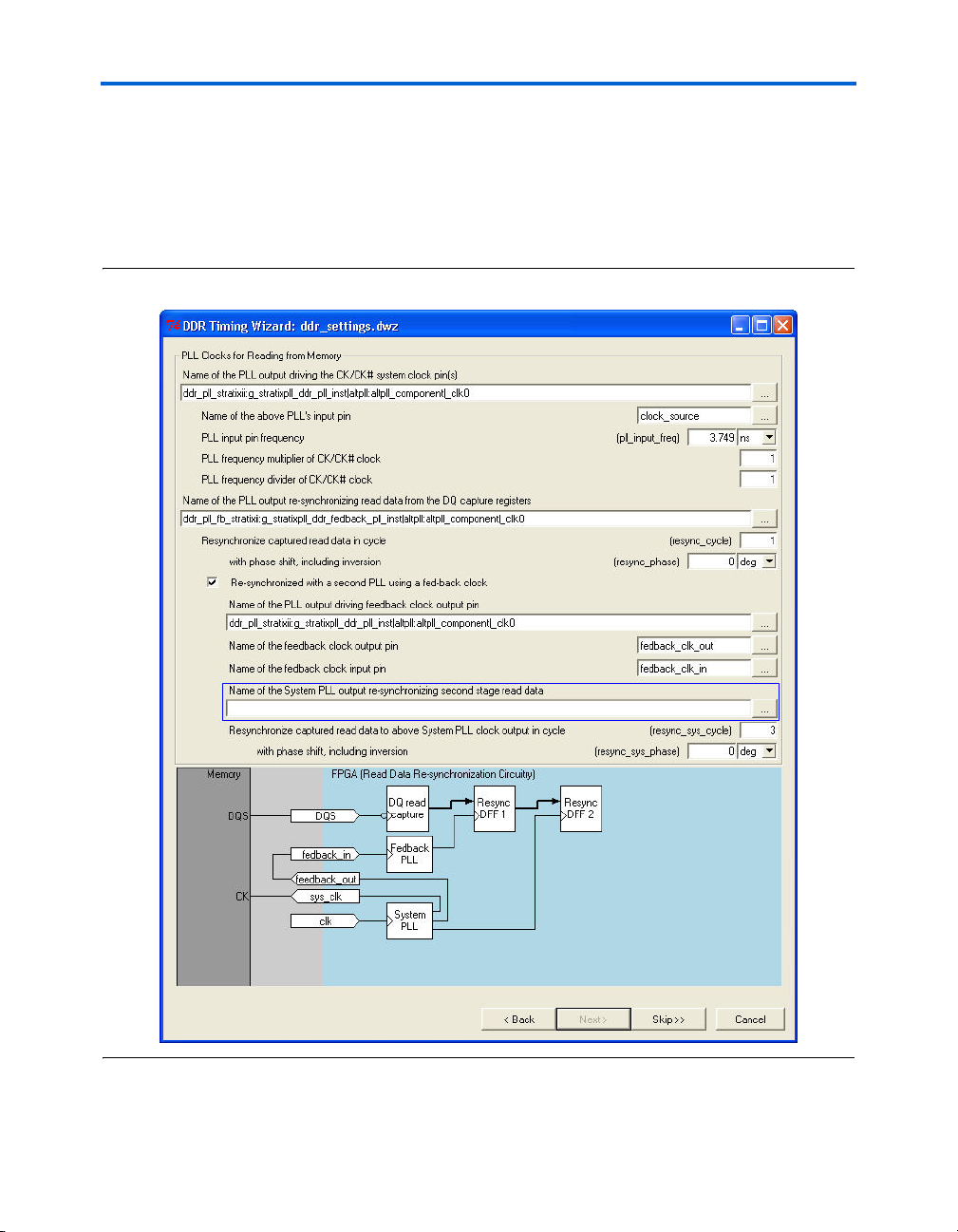

11. When the DTW has all of the pin connectivity information, set up

the design resynchronization clocking scheme as shown in

Figure 2–19, which uses the legacy controller MegaWizard default

name clock selection.

1 The clock input frequency, multiplication, division, phase

shifts, and clock cycle selection differ from design to design.

1 The resynchronization page selection for QDRII+/QDRII

SRAM and RLDRAM II interfaces do not have any clock

cycle or phase shift selections. You can also indicate that

you are using a FIFO for resynchronization in these

interfaces.

2–24 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 37

f Refer to Appendix A of the DDR and DDR2 SDRAM

Controller Compiler User Guide for more information on the

resynchronization and postamble clock cycles and phase

shifts.

Figure 2–19. Resynchronization Clock Connectivity

Getting Started

Altera Corporation 2–25

November 2007 DDR Timing Wizard User Guide

Page 38

Entering and Editing Inputs to the DTW

1 The default TimeQuest Timing Analyzer clocking names

Clicking on a field in this page highlights the location of that field in

the design schematic in the bottom of the page. For example, if you

click on the resync_cycle field as shown in Figure 2–20, the path

from the system PLL to the Resync DFF1 is highlighted to show

where the resync_cycle information is used. The DTW shows a

different schematic if the interface is using 1-PLL mode.

1 You can use the highlights as a guide when you must enter

are shown in Figure 2–19. If you are using Classic Timing

Analyzer, the default clocking names for the system PLL

are:

ddr_pll_stratixii:g_stratixpll_ddr_pll_inst

|altpll:altpll_component|_clkn

where n denotes the PLL output counter number.

each field manually. The design schematic varies

depending on the interface mode, whether you are using

DQS, or whether you are using 2-PLL (with the fedback

PLL) or 1-PLL mode. This example design uses DQS with

2-PLL implementation.

2–26 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 39

Figure 2–20. Fedback Resynchronization Path (Highlighted)

Getting Started

The first field of this page asks for the name of the PLL output

generating the CK/CK# system clock pins. Typically, this clock is the

system clock, which also drives the controller. However, if you are

using the dedicated clock output pins without the DDIO circuitry as

required in HardCopy II devices, you may need a separate PLL

output to ensure that t

is met at both fast and slow timing

DQSS

models.

Altera Corporation 2–27

November 2007 DDR Timing Wizard User Guide

Page 40

Entering and Editing Inputs to the DTW

f Refer to AN 413: Using Legacy Integrated Static Data Path and

You then must enter the PLL input clock name and the multiplication

and division factors to achieve the memory interface frequency of

operation. In Figure 2–19, the design uses a 100-MHz input clock, so

the multiplication and division factors are set to 8 and 3, respectively,

to interface with a 267-MHz DDR2 SDRAM DIMM.

The name of the PLL output resynchronizing read data from the read

capture registers depends on whether you are using the 2-PLL mode

or the 1-PLL mode. The example design uses the 2-PLL mode, so the

PLL output resynchronizing read data from the read capture

registers that comes from the fedback PLL.

In 2-PLL mode, the DTW must know the clock cycle of the fedback

resynchronization clock and the system (second) resynchronization

clock. The legacy controller MegaWizard only provides the clock

cycle for the system resynchronization clock, so the DTW has to

calculate the fedback resynchronization clock cycle

(resync_cycle) in 2-PLL mode.

Controller Megafunction with HardCopy Structured ASICs on

how to generate CK/CK# signals using dedicated clock

outputs.

1 In 1-PLL mode, there is only one clock cycle information

required since there is only one resynchronization clock.

This clock cycle is also called resync_cycle and is

provided by the legacy controller MegaWizard.

Because the DTW must know the clock cycle and the clock phase

shift for each data transfer, there is a register transfer between the

fedback PLL resynchronization clock and the system PLL

resynchronization clock in 2-PLL mode interfaces. The legacy

controller MegaWizard only needs to know the clock cycle on the

system PLL side, so the DTW manually calculates this in 2-PLL

mode. The legacy controller MegaWizard provides this number in

1-PLL mode since there is only one resynchronization clock from the

system PLL in this implementation.

The resync_phase field should match the phase shift entered in

the legacy controller MegaWizard in the Fed-back clock phase field.

An example of the proper name for a PLL clock output for

resynchronization clock is shown in Figure 2–20. See Figure 2–21 for

matching each resynchronization field in the legacy controller

MegaWizard in the DTW.

2–28 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 41

Getting Started

Figure 2–21. Resynchronization Clock and Phase Shift Relationship in DTW and the DDR2/DDR SDRAM

Controller MegaWizard

The Resynchronized with a second PLL using a fed-back clock field

must be checked when using the fedback-clock mode, as the

controlller uses this clock before resynchronizing data back to the

system clock domain. You then must specify the fedback clock input

and output pins, as well as the name of the system PLL output clock

to resynchronize the data from the fedback PLL to the system PLL.

The clock cycle (resync_sys_cycle) and clock phase shift

(resync_sys_phase) in this section should match with the legacy

controller MegaWizard information. If not, you need to fix this

information in DTW. After running the dtw_timing_analysis.tcl

Altera Corporation 2–29

November 2007 DDR Timing Wizard User Guide

Page 42

Entering and Editing Inputs to the DTW

with the –auto_adjust_cycles option, the DTW will have the best

clock cycle settings, so you need to update the legacy controller

MegaWizard at that point if the numbers do not match.

Table 2–1 shows the relationship between the legacy controller

MegaWizard and the DTW, in terms of resynchronization clock

cycles and phase shifts.

Table 2–1. Legacy Controller MegaWizard and DTW Resynchronization Clock Cycles

DTW Resynchronization

Fields

resync_cycle

resync_phase

resync_sys_cycle

resync_sys_phase

Note to Ta b le 2 – 1:

(1) For new designs targeting memory interfaces higher than 200 MHz, Altera recommends using the

high-performance controller featuring the ALTMEMPHY megafunction in the Quartus II software.

From the Resynchronize captured read

data in cycle field in the legacy controller

MegaWizard Manual Timings tab

From the Dedicated clock phase field in

the legacy controller MegaWizard Manual

Timings tab

Not used From the Resynchronize captured

Not used From the Dedicated clock phase field

Interfaces with One PLL

(≤ 200 MHz)

Interfaces with Fedback-Clock Mode

(> 200 MHz) (1)

Calculated by DTW

From the Fed-back clock phase field

in the legacy controller MegaWizard

Manual Timings tab

read data in cycle field in the legacy

controller MegaWizard Manual

Timings tab

in the legacy controller MegaWizard

Manual Timings tab

Click Next.

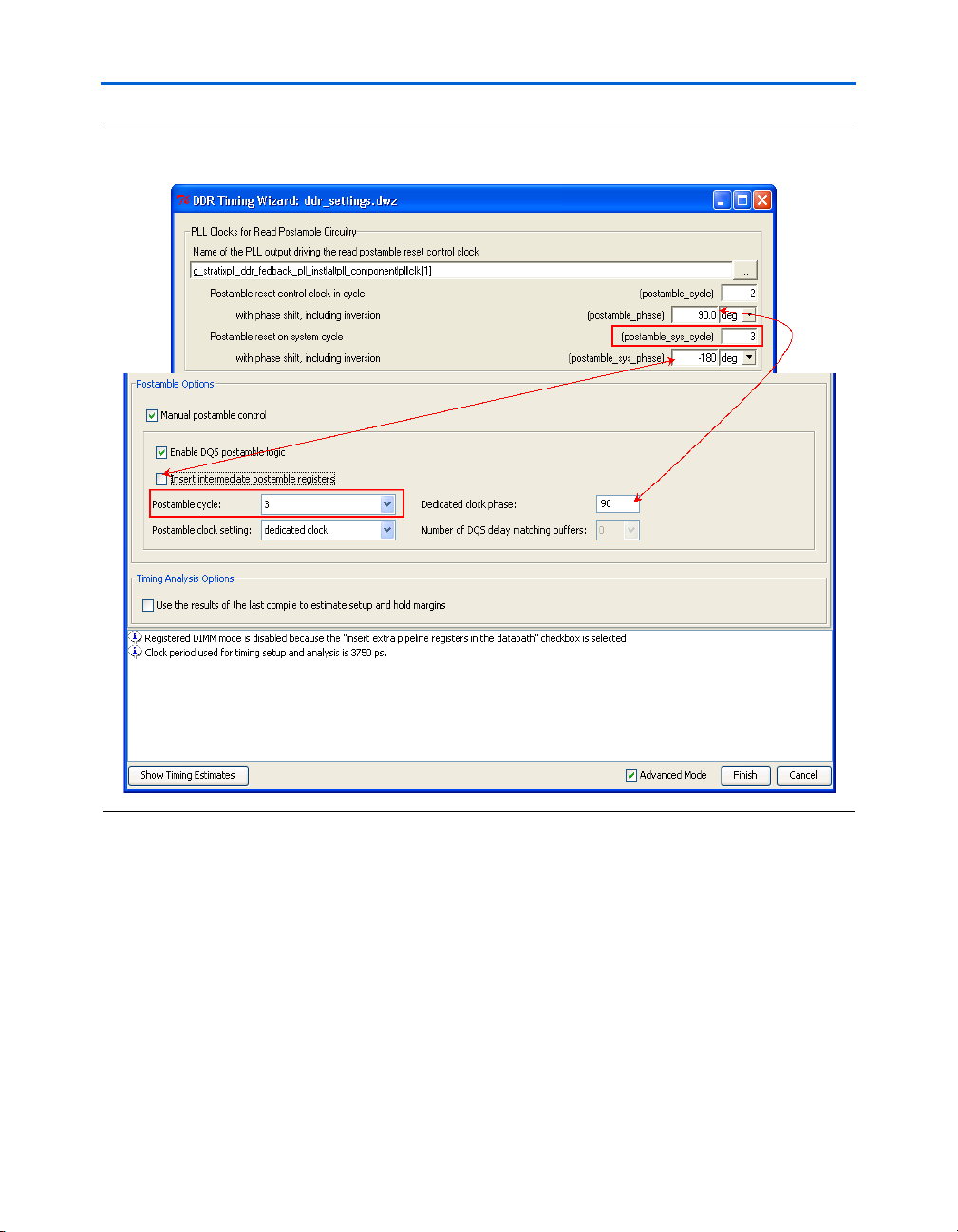

12. Figure 2–22 shows the DTW page for postamble clock connectivity.

The name of the PLL output driving the read postamble reset

control clock can come from the system PLL (when using 1-PLL

mode) or the fedback PLL (when using the fedback-clock mode).

Similar to the the resync_cycle field, the postamble_cycle

field is calculated by DTW when using the fedback-clock mode, but

is from the legacy controller MegaWizard when using one PLL only.

The postamble_phase is the postamble phase shift you entered in

legacy controller MegaWizard when you created the data path or

controller.

2–30 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 43

Figure 2–22. Postamble Clock Connectivity

Getting Started

The postamble_sys_cycle and postamble_sys_phase are

specific to the fedback-clock mode implementation. The

postamble_sys_cycle information should match with the

number in the legacy controller MegaWizard. The

postamble_sys_phase, however, depends on whether the option

to use intermediate postamble registers is checked in the legacy

controller MegaWizard or not. When the option is checked,

postamble_sys_phase is set to 0

in the design, postamble_sys_phase is set to –180

Altera Corporation 2–31

November 2007 DDR Timing Wizard User Guide

°. When the option is not checked

°.

Page 44

Entering and Editing Inputs to the DTW

Table 2–2 shows the relationship between the legacy controller

MegaWizard and the DTW in terms of postamble clock cycles and

phase shifts. This relationship for a 2-PLL mode example is also

shown in Figure 2–23.

Table 2–2. Relationship Between the Legacy Controller MegaWizard and the DTW

DTW Postamble Fields

postamble_cycle

postamble_phase

postamble_sys_cycle

postamble_sys_phase

Note to Ta b le 2 – 2:

(1) For new designs targeting memory interfaces higher than 200 MHz, Altera recommends using the

high-performance controller featuring the ALTMEMPHY megafunction in the Quartus II software.

Interfaces with One PLL

(≤ 200 MHz)

From the Postamble cycle field in the

legacy controller MegaWizard Manual

Timings tab

From the Dedicated clock phase

field in the legacy controller

MegaWizard Manual Timings tab

Not used From the “Postamble cycle” field in

Not used 0° or -180° whether intermediate

Interfaces with Fedback-Clock Mode

(> 200 MHz) (1)

Calculated by DTW

From the Dedicated clock phase field

in the legacy controller MegaWizard

Manual Timings tab

the legacy controller MegaWizard

Manual Timings tab

postamble registers are used or not.

2–32 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 45

Getting Started

Figure 2–23. Postamble Clock and Phase Shift Relationship in DTW and the DDR2/DDR SDRAM Controller

MegaWizard

Similar to the resynchronization clock connectivity page, clicking on

any field in this page highlights the appropriate paths in the

schematic at the bottom of the page. The schematic also changes

when you are using only one PLL to create the interface.

Click Next.

13. You must specify which PLL output clocks drive the DQS and DQ

write signals so the DTW can properly constrain the skew between

these pins.

Altera Corporation 2–33

November 2007 DDR Timing Wizard User Guide

Page 46

Entering and Editing Inputs to the DTW

You also must specify which PLL output clock drives the address

and control signals so the DTW can constrain the skew between

those pins and the CK/CK# pins properly. The Altera DDR/DDR2

SDRAM controller uses clk0 and clk1 of the system PLL to

generate DQS and DQ signals, respectively, as shown in Figure 2–25.

Figure 2–24. Default Clock Selection for the Altera DDR/DDR2 SDRAM Controller

Click Next.

14. Figure 2–25 shows the DTW page in which you specify board trace

lengths. This information is required to calculate the

resynchronization and postamble clock phase shifts. The

DDR/DDR2 SDRAM legacy controller MegaWizard has some

default values (as shown in Figure 2–25); however, you should enter

the accurate trace lengths, skew, and board tolerance so that the

DTW can calculate the correct timing constraints for your data

resynchronization and postamble clocks.

1 It is preferred that the trace delay information is extracted

from the board design with a signal integrity tool. If you can

only provide trace lengths and a constant scaling factor (for

example, 166 ps/in), the timing margin analysis will not be

as accurate. The flight time information should be the

nominal delay for each signal, but you also need to

determine a global tolerance for these numbers as well. If an

accurate number cannot be provided for that tolerance, the

DTW defaults to ±5%. Note that if you use a signal integrity

tool to generate the signal delays, you should set the

Output Pin Load setting to 0 pF since that load capacitance

is factored into the signal delay.

2–34 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 47

Getting Started

DTW requires the following numbers to be entered:

● Nominal memory to FPGA trace (DQ and DQS traces)

The midpoint between the maximum DQ/DQS trace delay and

the minimum DQ/DQS trace delay, using typical delays. For

example:

nominal_tpd (memory_to_FPGA) = (max(DQ, DQS) + min (DQ,

DQS)) / 2.

● Nominal FPGA output to memory trace

The midpoint between the maximum CK/CK# trace delay and

the minimum CK/CK# trace delay, using typical delays. For

example:

nominal_tpd (FPGA_to_memory) = (max(CK, CK#) + min (CK,

CK#)) / 2.

● Nominal feedback clock trace

The average delay of the two differential feedback clock traces.

For example:

nominal_tpd (feedback_trace) = (feedback_clock_p +

feedback_clock_n) / 2

For a single-ended feedback clock, just use the delay of that

clock trace.

● Board tolerance (measurement error in the above delays)

Maximum ± percent variation of the trace delays due to board

manufacturing tolerances and environmental conditions. Note

the other board delays specified use typical delays that do not

include these variations.

● Skew between wires in a data group (maximum delay difference

between DQS and DQ/DM board traces)

Maximum difference of DQ and DM board traces relative to

DQS/DQS# board traces.

Altera Corporation 2–35

November 2007 DDR Timing Wizard User Guide

Page 48

Entering and Editing Inputs to the DTW

● Skew between wires in an address/control group (maximum

delay difference between CK/CK# and address/control wires)

Maximum difference of BA, A, RAS#, CAS#, WE#, CS#, CKE,

and ODT board traces relative to CK/CK# board trace.

● Skew between CK/CK# and DQS outputs

Maximum difference of CK/CK# board traces relative to

DQS/DQS# board traces.

Figure 2–25. Board Information Page with Default Legacy Controller MegaWizard Values

Click Next.

15. The next two pages, which are also the last two pages of the DTW,

are dependent on whether you are using TimeQuest or Classic

Timing Analyzer names. The second-to-last page shows the FPGA

parameters used for the interface, while the last page shows a

summary of the assignment as well as the location of the files that

contain the assignment.

Figure 2–26 and Figure 2–27 show the FPGA parameter page of the

DTW when you are using TimeQuest or Classic Timing Analyzer

names, respectively. Both figures show a clock uncertainty section

with an option to use explicit clock uncertainties for HardCopy II

devices.

2–36 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 49

Figure 2–26. FPGA Timing Parameters When Using TimeQuest Timing Analyzer Names

Getting Started

Altera Corporation 2–37

November 2007 DDR Timing Wizard User Guide

Page 50

Entering and Editing Inputs to the DTW

Figure 2–27. FPGA Timing Parameters Page When Using Classic Timing Analyzer Names

Use the Use explicit uncertainties option in lieu of the separate clock

skew adder, PLL jitter, compensation error, and phase shift error

when targeting a HardCopy II device. These numbers were

characterized for the FPGA and are included in the timing model,

2–38 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 51

Getting Started

while in HardCopy II, these numbers need to be calculated

separately based on the design. HardCopy II designs must use this

explicit clock uncertainties option. When the option is not checked,

as in Figure 2–26 and Figure 2–27, you specify the clock skew adder,

PLL jitter, compensation error, and phase shift error individually.

DTW automatically populates these fields based on the synthesized

design. When the option is checked, the individual numbers are

added up to create clock uncertainty requirements for data capture,

fedback-clock resynchronization, write data, address, and t

DQSS

specifications.

When the Use explicit clock uncertainties option is checked, you

must import clock uncertainties from the HardCopy II Clock

Uncertainty Calculator. The calculator is available by request when

you have a design with memory interfaces targeting HardCopy II

devices. You should have used this calculator before the design

review process. Contact your Field Applications Engineers (FAEs)

for access to the calculator.

f The duty cycle distortion, PLL uncertainties, DQS

uncertainties, and skew parameters are specified in the

Stratix II Device Handbook.

Figure 2–27 also display estimated t

numbers for the clocks. These

CO

are only used when using Classic Timing Analyzer as DTW uses tCO

skew to determine the write timing constraints. The numbers shown

in Figure 2–27 are pre-compiled t

estimates that the DTW uses to

CO

generate the timing constraints before the design in compiled. After

you compile the design, rerun the DTW and click the Extract tcos

button to use actual timing data for more accurate timing constraints.

(Note that this process may take some time if your design is large.)

You can also use the -extract_tcos yes option when running

dtw_timing_analysis.tcl. Click on the Defaults for <device> button

to reset any of the numbers with the pre-compiled numbers.

1 Extract tcos assumes that you are using DDIOs for your

memory clocks. If you are targeting HardCopy II, you need

to use dedicated PLL clock outputs for your memory clocks.

In this case, you have to manually enter the CK/CK# t

for both timing models.

The bottom of Figure 2–27 shows the option to either use Both fast

and slow timing model tcos or to use Slow timing model tcos and

Fast timing model tcos separately. You can use either mode, but

Altera recommends using the separate timing model for memory

interface designs running at or above 200 MHz.

CO

s

Altera Corporation 2–39

November 2007 DDR Timing Wizard User Guide

Page 52

Entering and Editing Inputs to the DTW

When you check the option to use Both fast and slow timing model

tcos, DTW uses the fastest t

from the slow model to generate constraints for resynchronization

and postamble paths. This means that you may be over-constraining

your design since both the fastest and slowest t

simultaneously. The advantage of the option is that the Quartus II

software analyzes timing for both fast and slow timing model

concurrently, and shows timing analysis results for both models in

the same compilation panel.

Using Slow timing model tco and Fast timing model tco separately

gives you more accurate timing constraints. If you want to use slow

and fast timing model separately, always check the Slow timing

model tcos option as you must use the slow model timing

constraints for compilation. The dtw_timing_analysis.tcl will then

use the fast timing model t

the design, and then returns the DTW mode back to the slow timing

model tCOs.

Click Next.

16. The last page of the DTW lists the timing assignments that the DTW

applies to the project. The top dialog box in the page shows the

timing assignments made based on your inputs. For descriptions of

any of these assignments, highlight any of the assignments in the

top dialog box. The description of the highlighted assignment is

displayed in the Assignment Description dialog box.

from the fast model and slowest tCO

CO

s never occur

CO

s to extract fast model timing margin for

CO

The third dialog box reports the ideal data window for capture and

resynchronization. It also shows you how to check t

DQSS

, address,

command, and write timing manually. This dialog box also suggests

methods to close timing.

The last section of the page shows the name of the .sdc (and .tcl) files

that contain the assignments made by DTW, which should match the

.dwz name that was chosen in the first page of DTW. When using

TimeQuest Timing Analyzer names, DTW generates an .sdc file that

contains timing constraints for both fast and slow timing models.

When using Classic Timing Analyzer names, DTW generates both a

.tcl file (containing assignments that can be saved in the project’s .qsf

file) and an .sdc file (if you decide to compile the design using

TimeQuest Timing Analyzer later) if you choose to run the fast and

slow timing analysis concurrently, as shown in Figure 2–28. If you

choose to run the fast and slow timing analysis separately, DTW

2–40 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 53

generates two .tcl files with a .fast and .slow extensions to indicate

fast and slow timing model constraints, respectively, in addition to

the .sdc file, as shown in Figure 2–29.

Figure 2–28. Last Page of DTW with Both Fast and Slow Timing Model tcos Option

Getting Started

Altera Corporation 2–41

November 2007 DDR Timing Wizard User Guide

Page 54

Entering and Editing Inputs to the DTW

Figure 2–29. Last Page of DTW with Separate Timing Model Option

When using the Classic Timing Analyzer, a warning may appear

(Figure 2–30) to alert conflicting assignments. Click Yes to All to

overwrite the MegaWizard-generated script settings. The warning

could be due to the DTW needing to disable the cut on the timing

assignment legacy controller MegaWizard set to get the necessary

2–42 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 55

timing results from the Quartus II Classic Timing Analyzer. This

message can also occur if you are updating some timing constrains

from a previously-run DTW assignments. Figure 2–30 shows an

example of conflicting assignment on the cut timing path.

Figure 2–30. The DTW Warning Window on Conflicting Assignments

The last page of DTW when using TimeQuest Timing Analyzer

names is shown in Figure 2–31 on page 2–44.

Getting Started

Altera Corporation 2–43

November 2007 DDR Timing Wizard User Guide

Page 56

Entering and Editing Inputs to the DTW

Figure 2–31. Last Page of the DTW When Using TimeQuest Timing Analyzer

To change the output file name and location, type in the new file

name and location, and click the Change button.

Click Finish.

2–44 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 57

Getting Started

After you click Finish, your project should have the following

assignments:

● DQS/DQ pin location, loading, and I/O standard assignments

from the legacy controller MegaWizard-generated script

● Timing constraints from the DTW

17. Add the additional assignments as listed on Step 4 of the “Design

Flow” section.

You are now ready to compile the design and perform timing

analysis.

The DTW Pages for QDRII+/QDRII SRAM & RLDRAM II

The steps for the QDRII+/QDRII SRAM or RLDRAM II interface are

similar to the steps for the DDR/DDR2 SDRAM interface. The following

is a summary:

1. From the Tools menu, select Tc l S c ri pt s. Select DTW and click Run.

2. Specify a .dwz file name to save the timing constraints for the

design and click Next.

3. Confirm the project directory and revision you want to use and click

Next.

4. On the Import page, click Next, then click Next again.

5. Select the memory type and device and click Next.

6. Specify your CQ pins (for QDRII+/QDRII SRAM) or QK pins for

(RLDRAM II) and click Next.

7. Specify the read data associated with each CQ and QK pins. For

QDRII+/QDRII SRAM, you must specify the QK# pins if you are

using it to capture data and click Next.

8. Specify the clocks to the memory and click Next.

9. Specify the write data and data mask pins associated with each

write clock and click Next.

10. Specify control and address pins and click Next.

11. Specify PLL outputs driving the memory clocks and the

resynchronization scheme and click Next.

Altera Corporation 2–45

November 2007 DDR Timing Wizard User Guide

Page 58

DTW Limitations

1 You can use a similar resynchronization scheme like

DDR/DDR2 interfaces or use a FIFO to resynchronize the

data back to the system clocks. Altera RLDRAM II and

QDRII+/QDRII SRAM Controller MegaCore functions use

a FIFO for data resynchronization.

12. Specify the PLL output generating the write clocks and click Next.

13. Enter board skew information and click Next.

14. Verify the FPGA parameters page and click Next.

DTW Limitations

1 You can either use the default numbers or t

s if you have

CO

compiled the design.

1 All of the assignments made based on your inputs are

available on the final page.

15. Confirm the final page and click Finish.

16. Add the additional assignments as listed on Step 4 of “Design Flow”

on page 2–1.

17. Compile the design.

Limitations when using the DTW include:

■ Proper timing analysis of outputs (such as write data, data masks,

addresses, and commands) can only be performed with the

TimeQuest Timing Analyzer using the Synopsys design constraints

(SDC) file generated by the DTW. The SDC file is specified by the last

line on the last panel of the DTW (see Figure 2–31 on page 2–44).

However, even if you are using the classic timing analyzer, the

dtw_timing_analysis.tcl script will use TimeQuest Timing Analyzer

to analyze the timing of these outputs.

■ The SDC file currently only supports full-rate address/command

timing.

■ If you are using a custom QDRII+ SRAM interface, add the QVLD

pin as an additional read data pin. The current version of the Altera

QDRII+ SRAM controller MegaCore function does not support

QVLD pin.

2–46 Altera Corporation

DDR Timing Wizard User Guide November 2007

Page 59

Getting Started

■ When using the DDR/DDR2 SDRAM core version 3.4.0 and

Quartus II version 6.0 or older with DQS hardware capture and a

fedback clock, the read resynchronization to the System PLL cycle is

imported from the IP, assuming it is normalized for a CAS 2

memory. It is actually normalized for a CAS 3 memory, so adjust the

read resynchronization cycle by +1 on the PLL Parameters page (see

Figure 2–19 on page 2–25).

■ When using the DDR/DDR2 SDRAM core version 3.4.0 with DQS

hardware capture and a fedback clock, the DTW may make poor

estimates for the first stage read resynchronization and postamble

cycles in the PLL parameters page (Figure 2–19 on page 2–25). These