Page 1

13.1CPRI MegaCore Function User Guide

CPRI MegaCore Function

User Guide

101 Innovation Drive

San Jose, CA 95134

www.altera.com

UG-01062-6.3

Document last updated for Altera Complete Design Suite version:

Document publication date:

13.1

December 2013

Feedback Subscribe

Page 2

© 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos

are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its

semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and

services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service

described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying

on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

December 2013 Altera Corporation CPRI MegaCore Function

User Guide

Page 3

Contents

Chapter 1. About This MegaCore Function

General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–2

CPRI IP Core Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–3

Device Family Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–5

MegaCore Verification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–6

Performance and Resource Utilization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–6

Release Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–8

Installation and Licensing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–9

OpenCore Plus Evaluation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–10

OpenCore Plus Time-Out Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–10

Chapter 2. Getting Started

MegaWizard Plug-In Manager Design Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1

Specifying Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–2

Simulation Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–3

Simulating the Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–4

Integrating the CPRI IP Core in a Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–5

Supporting the Transceivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–5

Specifying Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–5

Compiling and Programming the Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–6

Instantiating Multiple CPRI IP Cores . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–6

Chapter 3. Parameter Settings

Physical Layer Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–1

Operation Mode Parameter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–2

Line Rate Parameter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–2

Enable Autorate Negotiation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

Transceiver Starting Channel Number . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

Rx Elastic Buffer Depth . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

Transceiver Reference Clock Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–4

Automatic Round-Trip Delay Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–4

Data Link Layer Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–4

Include MAC Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–4

Include HDLC Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–5

Application Layer Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–5

Mapping Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–5

Number of Antenna-Carrier Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–6

Enable Internally-Clocked Synchronization Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–7

Vendor-Specific Space (VSS) Access through CPU Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–7

Chapter 4. Functional Description

Architecture Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–2

Clocking Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–3

CPRI IP Core Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–3

Clock Diagrams for the CPRI IP Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–5

Clock Diagrams for Most CPRI IP Core Variations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–6

Clock Diagrams for CPRI IP Core Arria V GT Variations at 9830.4 Mbps . . . . . . . . . . . . . . . . . . . 4–7

Dynamically Switching Clock Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–9

December 2013 Altera Corporation CPRI MegaCore Function

User Guide

Page 4

iv ContentsContents

CPRI Communication Link Line Rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–10

Reset Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–11

MAP Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–12

MAP Interface Mapping Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–13

Basic AxC Mapping Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–14

Advanced AxC Mapping Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–18

MAP Receiver Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–18

MAP Receiver Interface Signals in Different Synchronization Modes . . . . . . . . . . . . . . . . . . . . . 4–19

MAP Receiver in FIFO Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–20

MAP Receiver in Synchronous Buffer Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–21

MAP Receiver in the Internally-Clocked Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–23

MAP Transmitter Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–24

MAP Transmitter Interface Signals in Different Synchronization Modes . . . . . . . . . . . . . . . . . . 4–25

MAP Transmitter in FIFO Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–26

MAP Transmitter in Synchronous Buffer Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–27

MAP Transmitter in the Internally-clocked Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–29

Auxiliary Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–30

AUX Receiver Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–31

AUX Transmitter Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–34

Media Independent Interface to an External Ethernet Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–37

MII Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–38

MII Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–39

CPU Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–41

Accessing the Hyperframe Control Words . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–42

Recording and Retrieving the Incoming Control Words . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–43

Writing the Outgoing Control Words . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–44

Control Word Order . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–46

Control Word Transmission Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–46

Control Word Retrieval Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–47

Accessing the Ethernet Channel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–47

Transmitting Ethernet Traffic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–48

Receiving Ethernet Traffic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–49

Accessing the HDLC Channel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–50

CPRI Protocol Interface Layer (Physical Layer) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–51

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–52

Physical Layer Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–52

Ensuring the Physical Layer Routes Your Data as Expected . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–53

Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–53

High-Speed Transceiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–54

Rx Elastic Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–54

Descrambling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–55

Frame Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–55

Alarm Indications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–56

Reset Control Word . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–57

Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–58

Scrambling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–59

Tx Elastic Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–59

High-Speed Transceiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–59

Chapter 5. Testing Features

Loopback Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–1

External Loopback . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–1

Internal Reverse Loopback . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–2

Physical Layer Loopback Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–2

CPRI MegaCore Function December 2013 Altera Corporation

User Guide

Page 5

ContentsContents v

Reverse Loopback Through CPRI Rx and Tx Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–2

PRBS Generation and Validation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–2

Achieving Link Synchronization Without an REC Master . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–4

Chapter 6. Signals

MAP Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–1

MAP Receiver Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–1

MAP Transmitter Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–3

Auxiliary Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–5

AUX Receiver Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–6

AUX Transmitter Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–7

Extended Rx Status Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–9

CPRI MII Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–10

CPRI MII Receiver Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–10

CPRI MII Transmitter Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–10

CPU Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–11

Physical Layer Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–12

CPRI Data Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–12

Layer 1 Clock and Reset Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–13

Layer 1 Error Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–13

Autorate Negotiation Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–13

Transceiver Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–15

Clock and Reset Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–17

Chapter 7. Software Interface

CPRI Protocol Interface Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–2

MAP Interface and AUX Interface Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–15

Ethernet Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–22

HDLC Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–27

Chapter 8. CPRI IP Core Demonstration Testbench

Test Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8–3

Reset, Frame Synchronization, and Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8–4

Running the Testbench . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8–5

Appendix A. Initialization Sequence

Appendix B. Implementing CPRI Link Autorate Negotiation

Design Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B–1

Configuring the CPRI IP Core for Autorate Negotiation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B–3

Running Autorate Negotiation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B–3

Autorate Negotiation From 9.8304 Gbps in Arria V GT Variations . . . . . . . . . . . . . . . . . . . . . . . . . . . . B–4

Appendix C. CPRI Autorate Negotiation Testbench

Test Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C–4

Running the Autorate Negotiation Testbench . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C–5

Appendix D. Advanced AxC Mapping Modes

Backward Compability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D–1

Advanced Mapping Mode Similarities and Differences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D–2

Fifteen-Bit Width Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D–3

Sixteen-Bit Width Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D–4

December 2013 Altera Corporation CPRI MegaCore Function

User Guide

Page 6

vi ContentsContents

Appendix E. Delay Measurement and Calibration

Delay Measurement and Calibration Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–1

Delay Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–1

Single-Hop Delay Measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–3

Rx Path Delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–3

Most CPRI IP Core Variations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–3

Arria V GT 9.8 Gbps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–10

Tx Path Delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–12

Most CPRI IP Core Variations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–12

Arria V GT 9.8 Gbps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–17

Toffset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–18

Round-Trip Delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–18

Round-Trip Cable Delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–18

Tx Bitslip Delay in the Round-Trip Delay Calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–19

Dynamic Pipelining for Automatic Round-Trip Delay Calibration . . . . . . . . . . . . . . . . . . . . . . . . . E–19

Round-Trip and Cable Delay Calculation Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–21

Round-Trip and Cable Delay Calculation Example 1: Two Stratix IV GX Devices . . . . . . . . . . E–21

Round-Trip and Cable Delay Calculation Example 2: Two Arria II GX Devices . . . . . . . . . . . . E–23

Round-Trip and Cable Delay Calculation Example 3: Two Different Device Families . . . . . . E–24

Round-Trip and Cable Delay Calculation Example 4: Two Different Device Families . . . . . . E–25

Multi-Hop Delay Measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–27

Round-Trip Delay Calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–27

Round-Trip Cable Delay Calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–27

Two-Hop Round-Trip and Cable Delay Calculation Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–28

Appendix F. Integrating the CPRI IP Core Timing Constraints in the Full Design

Appendix G. Porting a CPRI IP Core from the Previous Version of the Software

Additional Information

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

How to Contact Altera . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–6

Typographic Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–6

CPRI MegaCore Function December 2013 Altera Corporation

User Guide

Page 7

The Altera® CPRI MegaCore® function implements the Common Public Radio

CPRI

MegaCore Function

(RE Slave)

FPGA FPGA

CPRI

MegaCore Function

(RE Slave)

CPRI

MegaCore Function

(RE Master)

FPGA

CPRI

MegaCore Function

(REC)

Clock

Module

RF

Base Band Module

Optical Link

Optical Link

CPRICPRICPRI

CPRI

RF

Routing Layer

MAP MAPAUX AUX

Interface (CPRI) specification. CPRI is a high-speed serial interface designed for

network radio equipment controllers (REC) to receive data from and provide data to

remote radio equipment (RE).

1 The information in this user guide, including the latency numbers in “Delay

Measurement and Calibration Features” on page E–1, is applicable to version 13.1 of

the CPRI IP core.

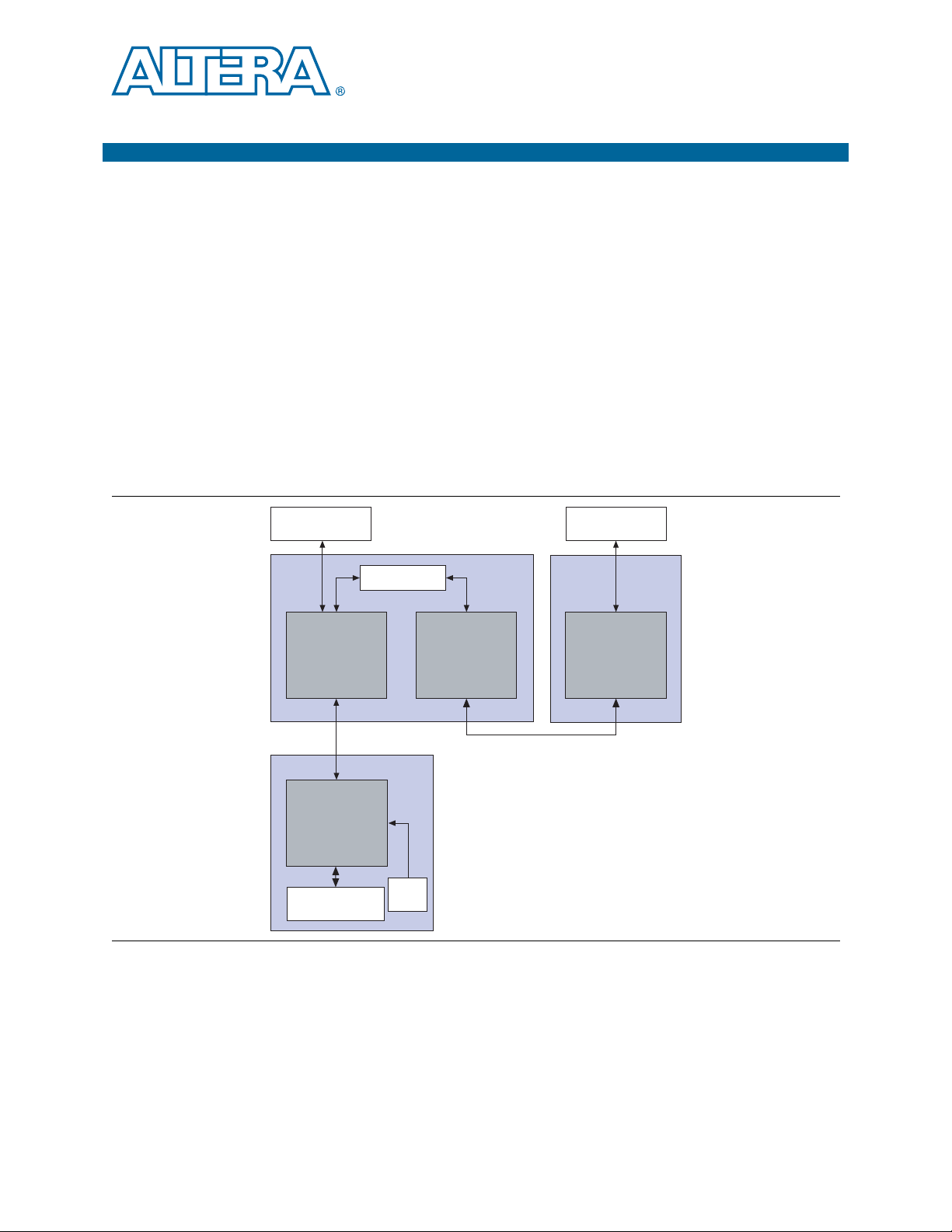

The CPRI IP core targets high-performance, remote, radio network applications. You

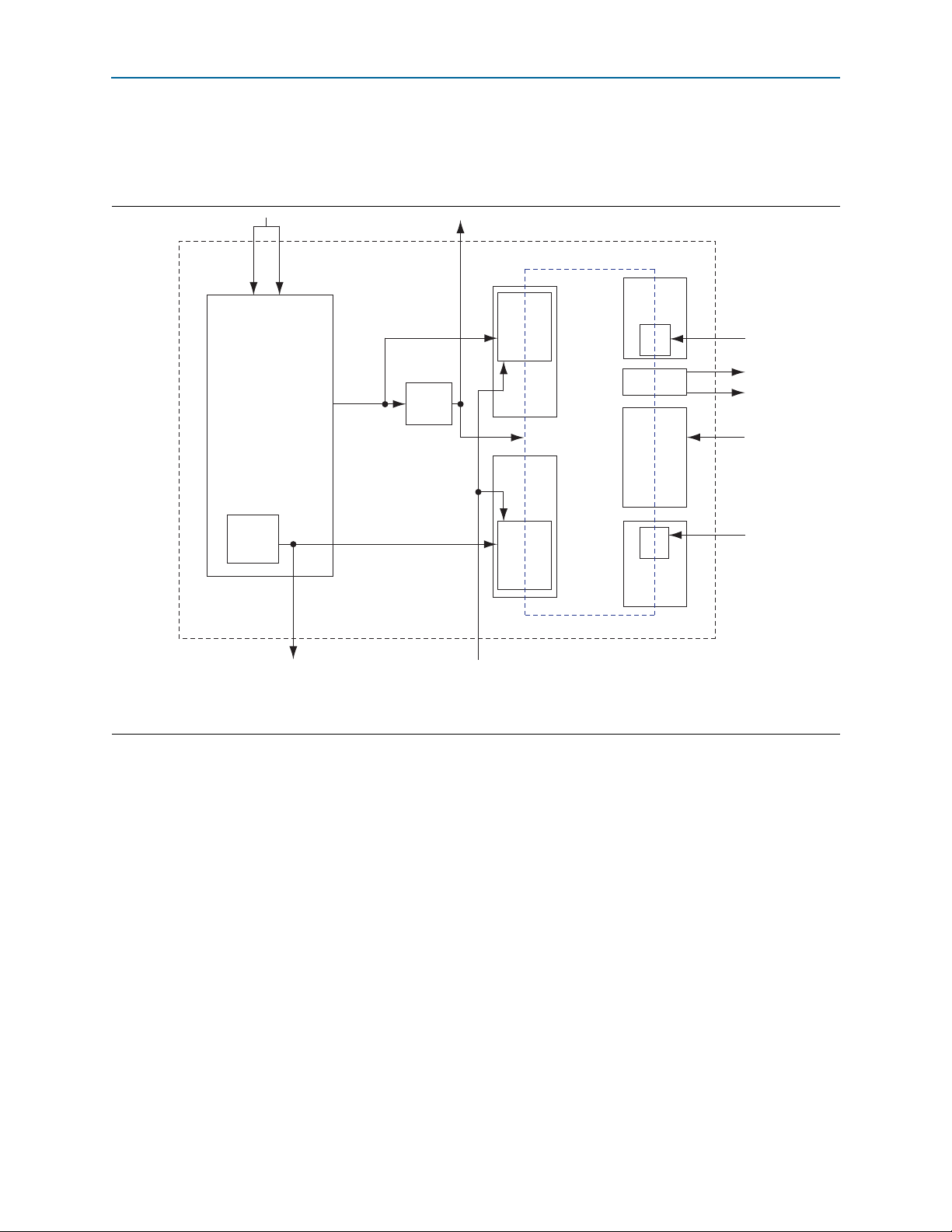

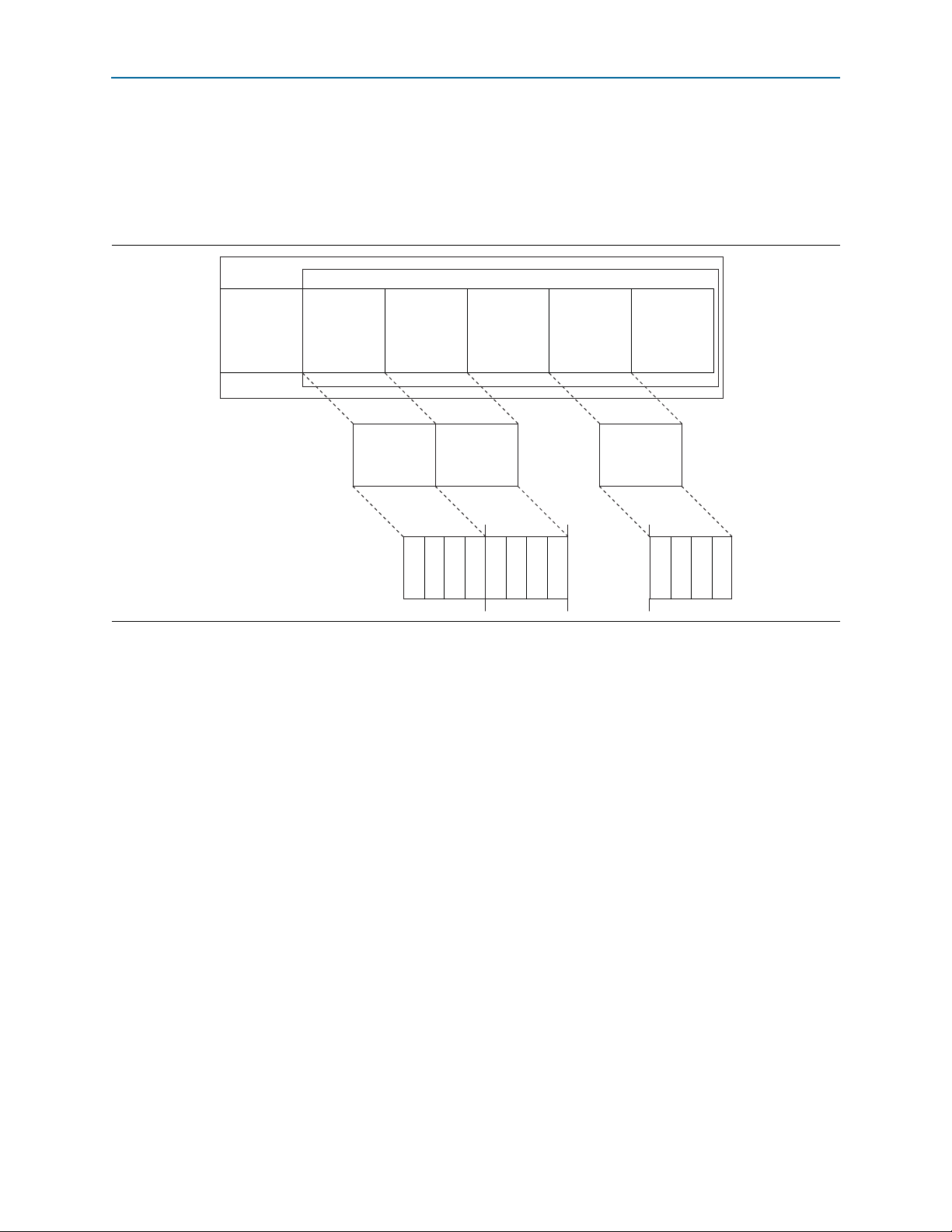

can configure the CPRI IP core as an RE or an REC. Figure 1–1 shows an example

system implementation with a two-hop daisy chain. Optical links between devices

support high performance.

Figure 1–1. Typical CPRI Application on Altera Devices

1. About This MegaCore Function

December 2013 Altera Corporation CPRI MegaCore Function

User Guide

Page 8

1–2 Chapter 1: About This MegaCore Function

General Description

General Description

The Altera CPRI IP core implements Layer 1 and Layer 2 of the CPRI V5.0

specification. It provides access to the V5.0 Layer 1 and Layer 2 access points through

various interfaces:

■ V5.0 Layer 1 access:

■ Auxiliary (AUX) interface for full access to V5.0 control data stream for

antenna-carrier (Ctrl_AxC) bytes in control word.

■ Register support for loading and unloading full control words, including

Ctrl_AxC bytes.

■ Auxiliary (AUX) interface support for user-defined GSM mapping.

■ IQ data access:

■ Mapping block (MAP) to antenna-carrier interfaces for easy IQ user data plane

access based on pre-configured antenna-carrier channels.

■ Auxiliary (AUX) interface for full access to the user data plane.

■ Ethernet channel access:

■ Auxiliary interface for full access to the Ethernet space in the CPRI frame.

■ Register support for loading and unloading the Ethernet frame.

■ Media independent (MI) interface port for Ethernet Frame access.

■ High level data link control (HDLC) channel access:

■ Auxiliary interface for full access to the HDLC space in the CPRI frame.

■ Register support for loading and unloading the HDLC frame.

■ Vendor-specific space (VSS) data:

■ Auxiliary interface for full access to control words.

■ Register support for loading and unloading full control words, including VSS

space.

■ Synchronization and timing access:

■ Auxiliary interface for full access to synchronization and timing.

You configure the CPRI IP core to include an Ethernet media access control (MAC)

block or to communicate with an external Ethernet module through an MI interface.

You can configure the CPRI link line rate.

For information about the CPRI IP core interfaces and functionality, refer to Chapter 4,

Functional Description. For information about configuration options, refer to

Chapter 3, Parameter Settings.

CPRI MegaCore Function December 2013 Altera Corporation

User Guide

Page 9

Chapter 1: About This MegaCore Function 1–3

tx_dataout

Transmitter

Transceiver

Transmitter

rx_datain

CPRI LinkCPRI Link

Receiver

Transceiver

Receiver

Multiplexing

Time Division Multiplexing

IQ

Data

Full access

to

CPRI frame

Vendor

Specific

L1

Inband

Protocol

HDLC (2) Ethernet (3)

MAP

Interface (1)

AUX

Interface

CPU

Interface

MI

Interface

CPRI IP Core Features

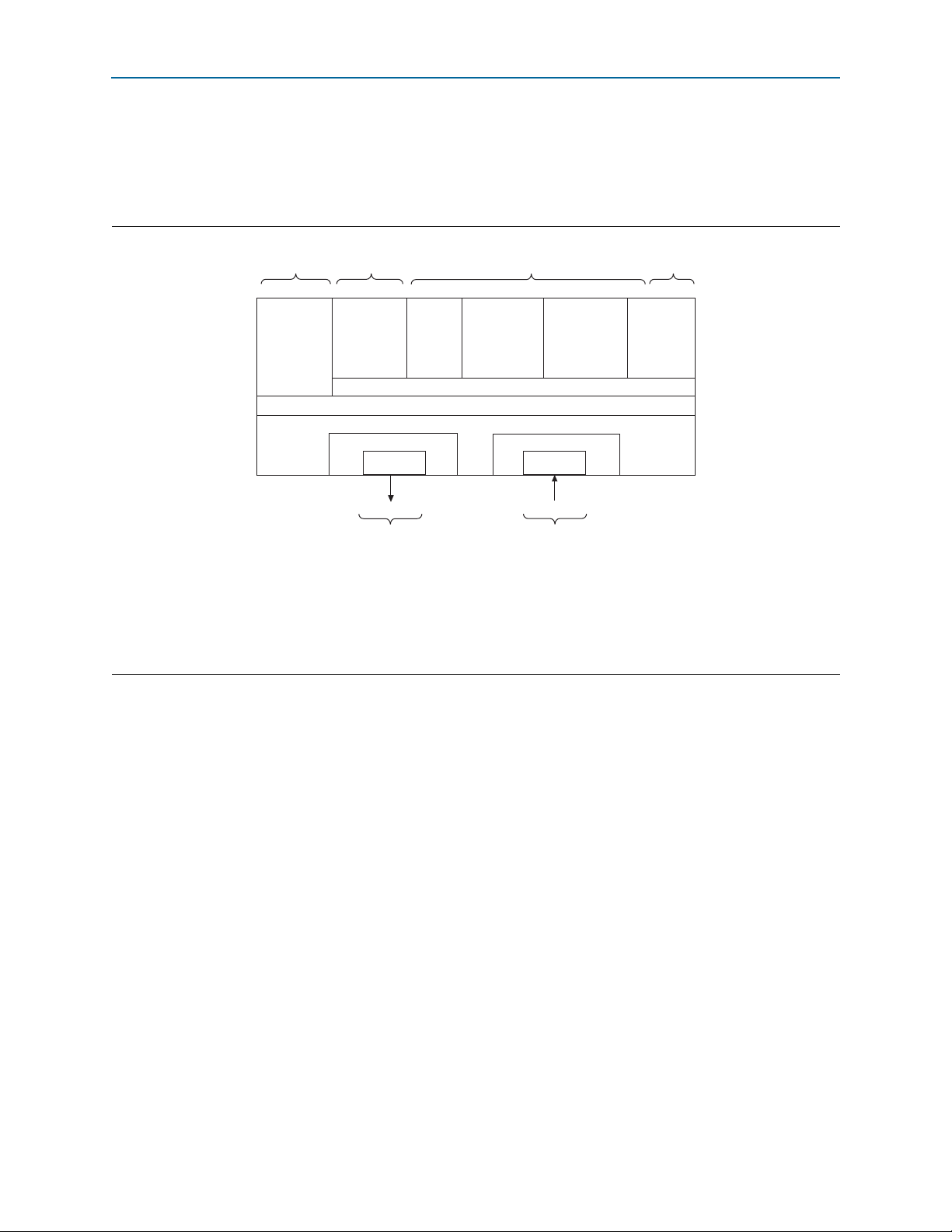

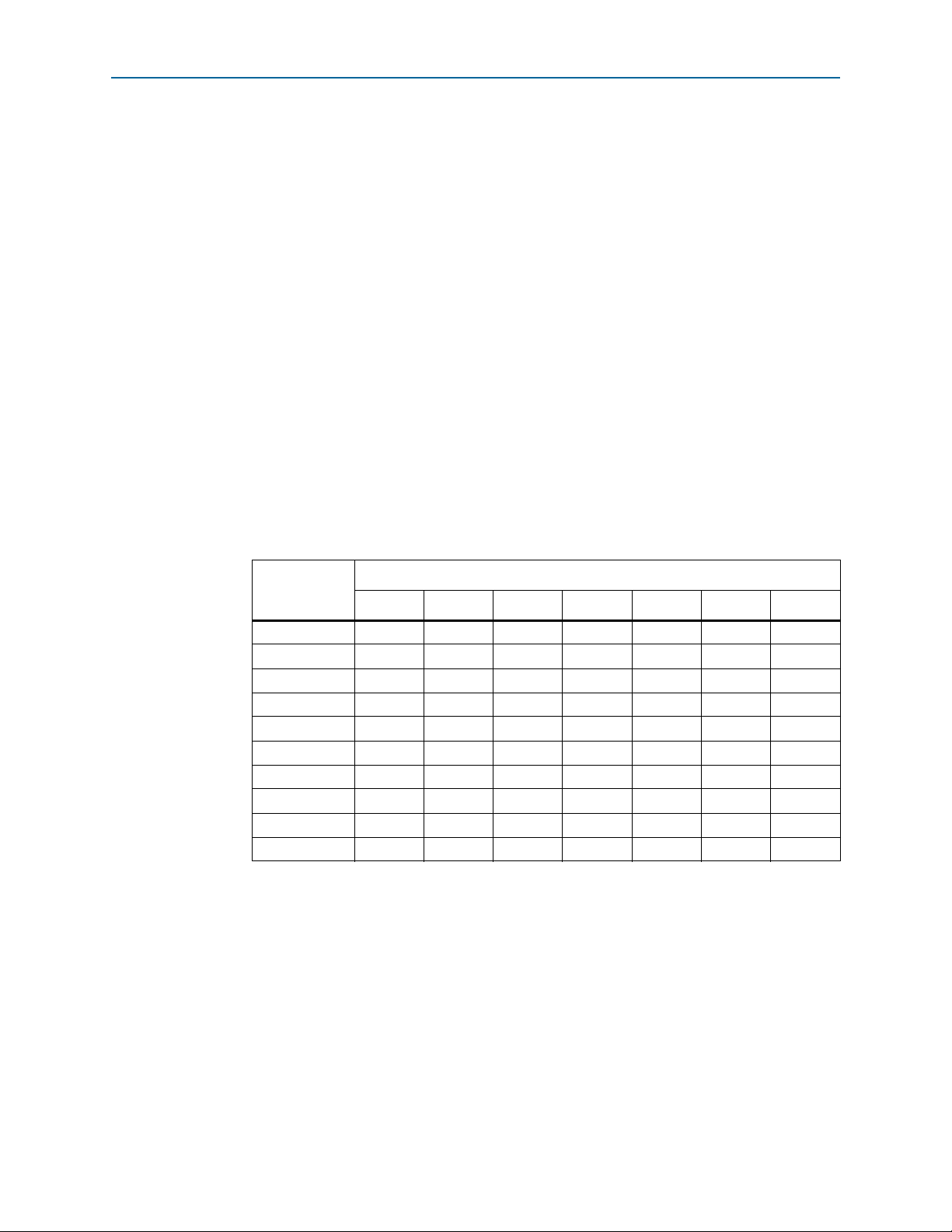

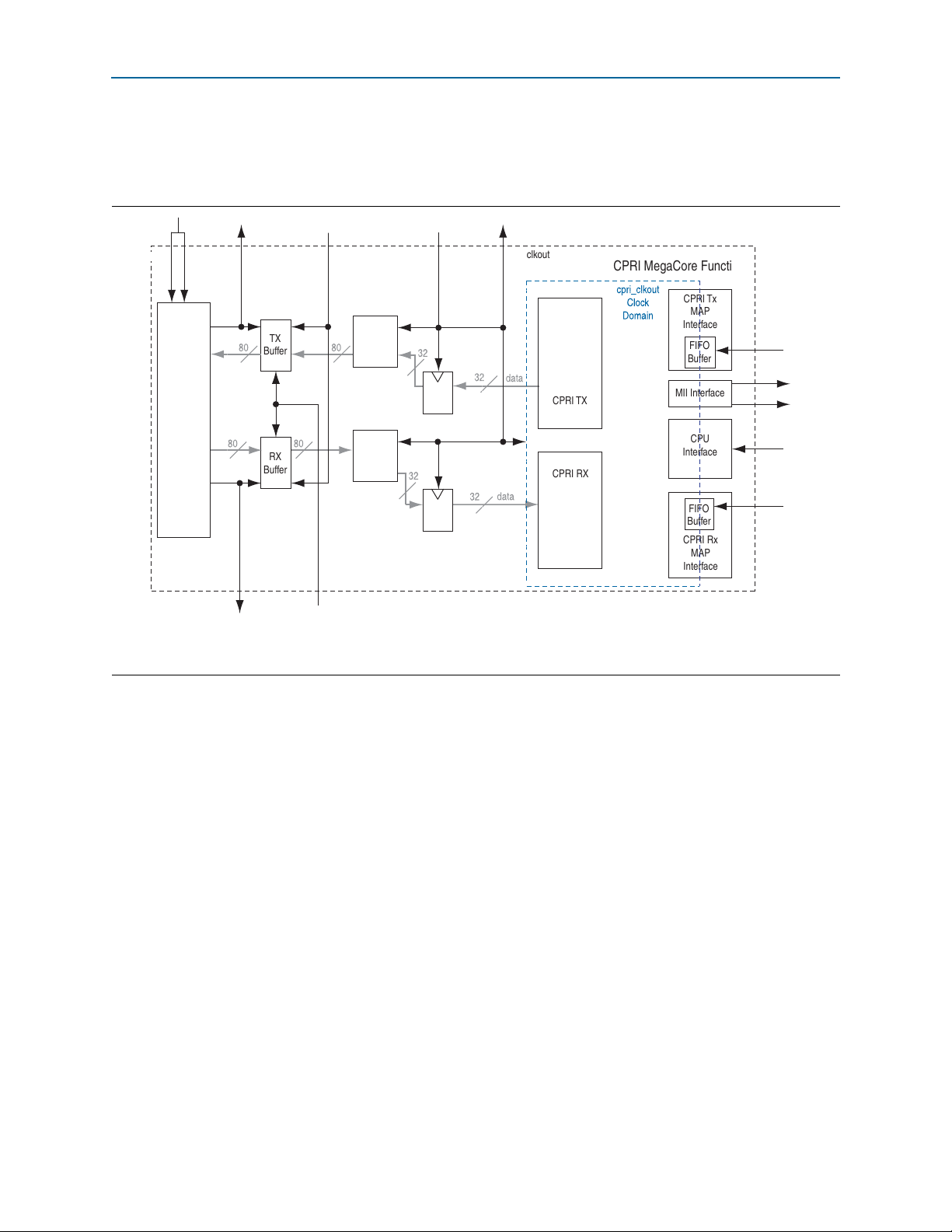

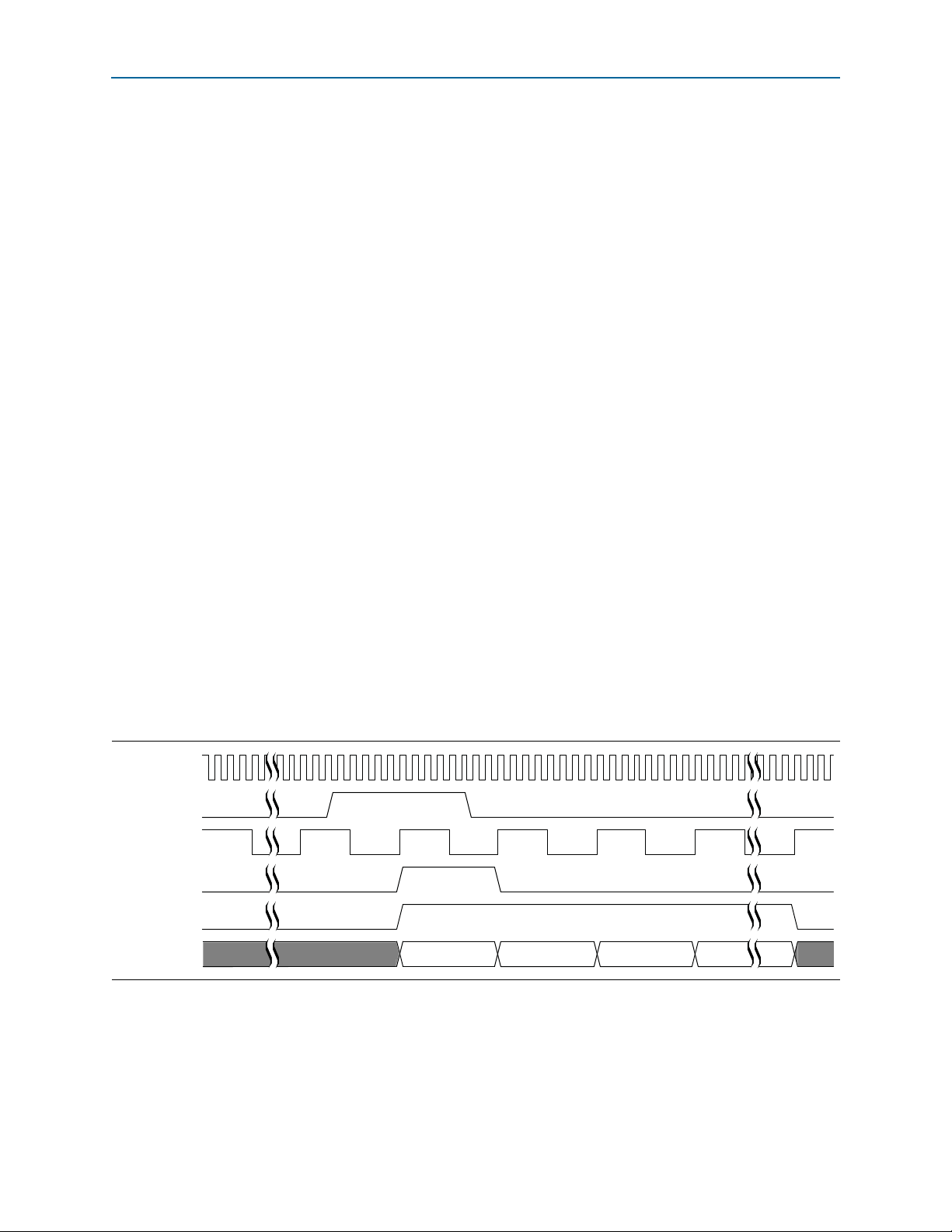

Figure 1–2 shows the CPRI IP core interfaces. The IP core assembles the outbound

CPRI frame control words and data from all of these interfaces, and unloads and

routes control words and data from the inbound CPRI frame to the appropriate

interfaces, based on configuration and register settings.

Figure 1–2. CPRI IP Core Interfaces

Notes to Figure 1–2:

(1) You can configure your CPRI IP core with zero, one, or multiple antenna-carrier interfaces. If you configure zero antenna-carrier interfaces, the

MAP interface is not configured in your CPRI IP core. In that case you can communicate IQ data through the AUX interface to your user-defined

routing layer.

(2) You can configure your CPRI IP core with or without an HDLC block.

(3) You can configure your CPRI IP core with an Ethernet MAC block or a media-independent (MI) interface (MII) block. The two options are mutually

exclusive.

CPRI IP Core Features

The CPRI IP core has the following features:

■ Complies with the Common Public Radio Interface (CPRI) Specification V5.0

(2011-09-21) Interface Specification for wireless base station submodule

interconnections, without the full range of IQ data sample widths, using auxiliary

interface for user-defined GSM mapping.

■ Supports radio equipment controller (REC) and radio equipment (RE) module

configurations, including RE master, RE slave, and REC master ports.

■ Supports Universal Mobile Telecommunication System (UMTS) Terrestrial Radio

Access (UTRA) – frequency division duplexing (UTRA-FDD) (UMTS/Wideband

Code Division Multiple Access (W-CDMA)), Evolved UTRA (E-UTRA) (3rd

Generation Partnership Project (3GPP) Long Term Evolution (LTE) specification),

3GPP Global System for Mobile Communications (GSM)/Enhanced Data Rates for

GSM Evolution (EDGE) Radio Access Network, and Worldwide interoperability

■ Provides full access to CPRI frame.

for Microwave Access (WiMAX) (IEEE 802.16 standard).

December 2013 Altera Corporation CPRI MegaCore Function

User Guide

Page 10

1–4 Chapter 1: About This MegaCore Function

CPRI IP Core Features

■ Supports the following additional CPRI link features:

■ Programmable CPRI communication line rate (to 614.4, 1228.8, 2457.6, 3072.0,

4915.2, 6144.0, or 9830.4 Mbps) using Altera on-chip high-speed transceivers.

■ Programmable operation mode: CPRI link master or CPRI link slave.

■ Auto-rate negotiation support.

■ Scrambling and descrambling at 4915.2 Mbps, 6144.0 Mbps, and 9830.4 Mbps.

■ Receiver (Rx) delay measurement.

■ Transmitter (Tx) delay calibration.

■ Programmable hardware processing of the reset request bit in the CPRI frame.

■ Vendor-specific subchannel (VSS) communication on the CPRI link.

■ Diagnostic parallel reverse loopback paths.

■ Diagnostic stand-alone RE slave testing mode.

■ Includes the following additional interfaces:

■ Interface to external or on-chip processor, using the Altera Avalon

®

Memory-Mapped (Avalon-MM) interconnect specification.

■ Ethernet communication interfaces that support simultaneous Ethernet and

HDLC communication to and from the CPRI link.

■ Optional configuration of Ethernet MAC.

■ Optional Media-Independent Interface for Ethernet frame access.

■ Optional configuration of HDLC block.

■ Auxiliary interface provides full access to CPRI frame.

■ Supports data transfer to and from custom mapping functions, including

user-defined GSM mapping.

■ Supports data transfer from slave to master ports to implement daisy-chain

topologies.

■ Supports custom IQ sample widths.

■ Optional built-in IQ data interface with the following features:

■ Implements mapping methods in Sections 4.2.7.2.5 and 4.2.7.2.7 of the CPRI

V4.2 Specification, and mapping Options 1 and 2 in Sections 4.2.7.2.3 and

4.2.7.2.4 of the CPRI V4.2 Specification.

■ Implements WiMAX mapping methods described in Sections 4.2.7.2.2,

4.2.7.2.5, and 4.2.7.2.7 of the CPRI V4.2 Specification.

■ Implements UMTS/LTE mapping methods described in Section 4.2.7.2 of

the CPRI V4.2 Specification.

■ Implements WiMAX timing control methodology described in Section

4.2.8.2 of the CPRI V4.2 Specification.

■ Supports as many as 24 antenna-carrier interfaces.

■ Supports clocking antenna-carrier interfaces with external data channel

clocks or internal IP core clock.

CPRI MegaCore Function December 2013 Altera Corporation

User Guide

Page 11

Chapter 1: About This MegaCore Function 1–5

Device Family Support

■ Supports synchronous buffer or simple FIFO synchronization modes for

externally clocked antenna-carrier interfaces.

■ Supports independent sample rates for each antenna-carrier interface.

■ Supports 15- and 16-bit data sample widths on uplink and downlink using

the Altera Avalon Streaming (Avalon-ST) interconnect specification.

Device Family Support

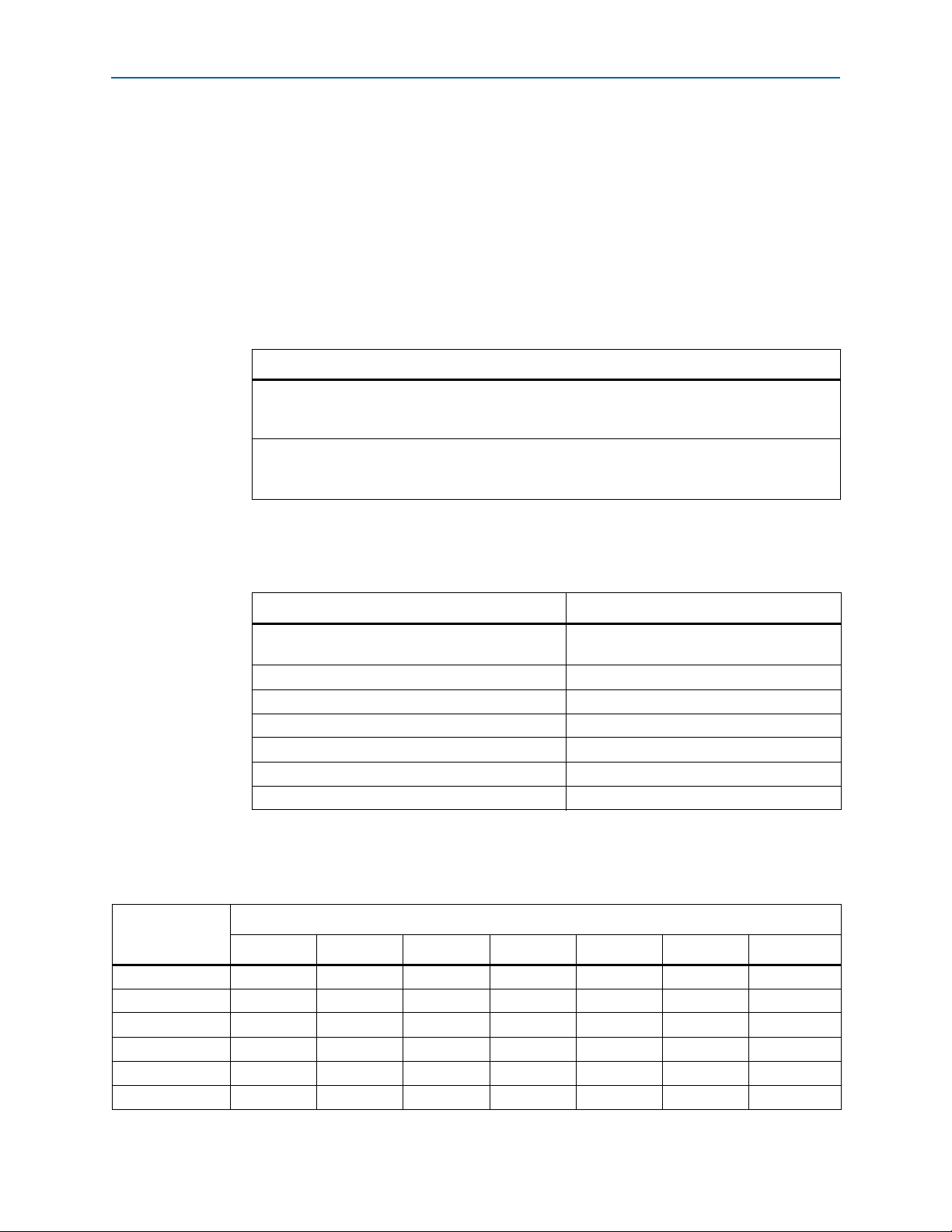

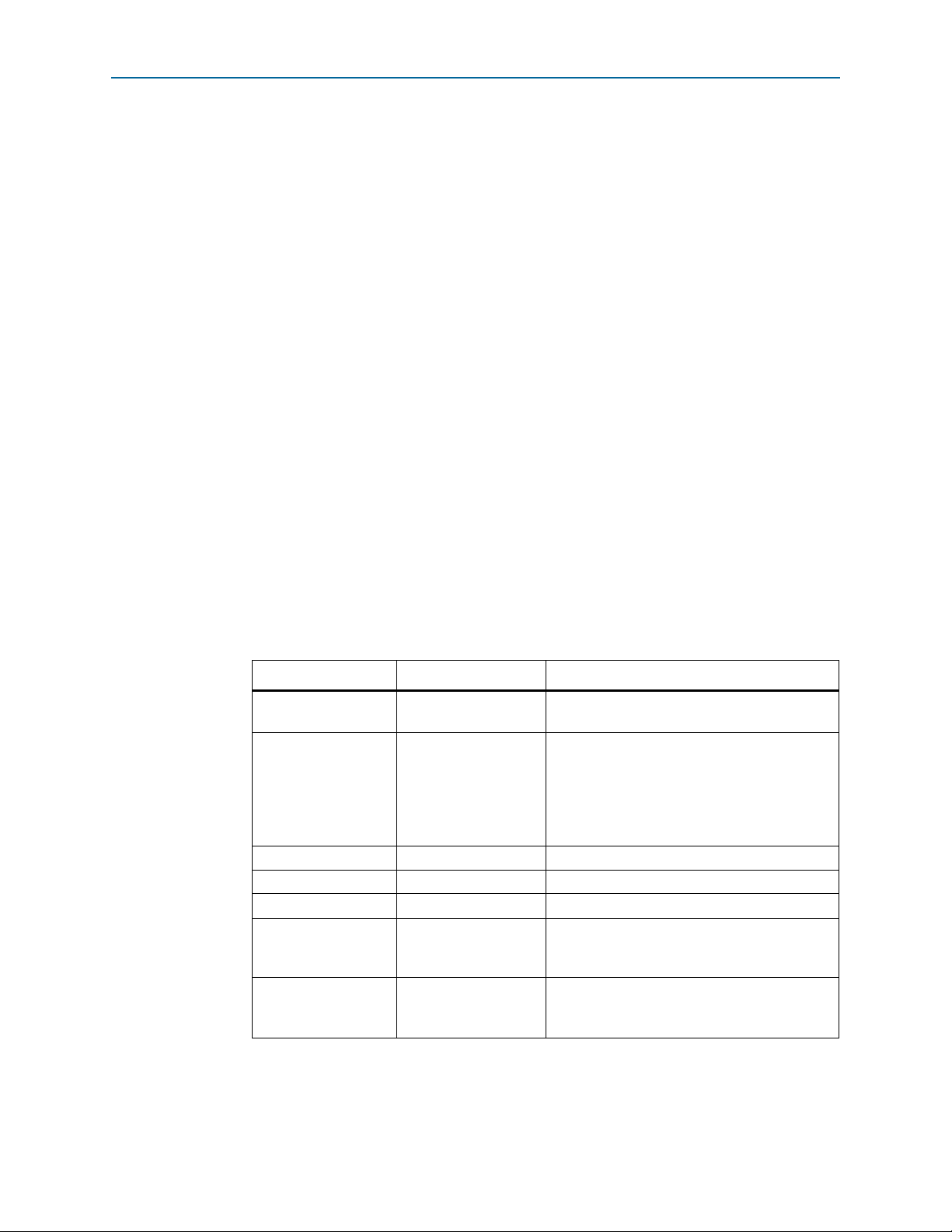

Tab le 1– 1 defines the device support levels for Altera IP cores.

Table 1–1. Altera IP Core Device Support Levels

FPGA Device Families

Preliminary support—The IP core is verified with preliminary timing models for this device family.

The IP core meets all functional requirements, but might still be undergoing timing analysis for the

device family. It can be used in production designs with caution.

Final support—The IP core is verified with final timing models for this device family. The IP core

meets all functional and timing requirements for the device family and can be used in production

designs.

Tab le 1– 2 lists the level of support offered by the CPRI IP core for each Altera device

family.

Table 1–2. Device Family Support

Device Family Support

Stratix

®

V

Refer to the What’s New in Altera IP page of

the Altera website.

Stratix IV GX Final

®

V (GX, GT, and GZ variants) Preliminary

Arria

Arria II (GX and GZ variants) Final

®

Cyclone

V GX Preliminary

Cyclone IV GX Final

Other device families No support

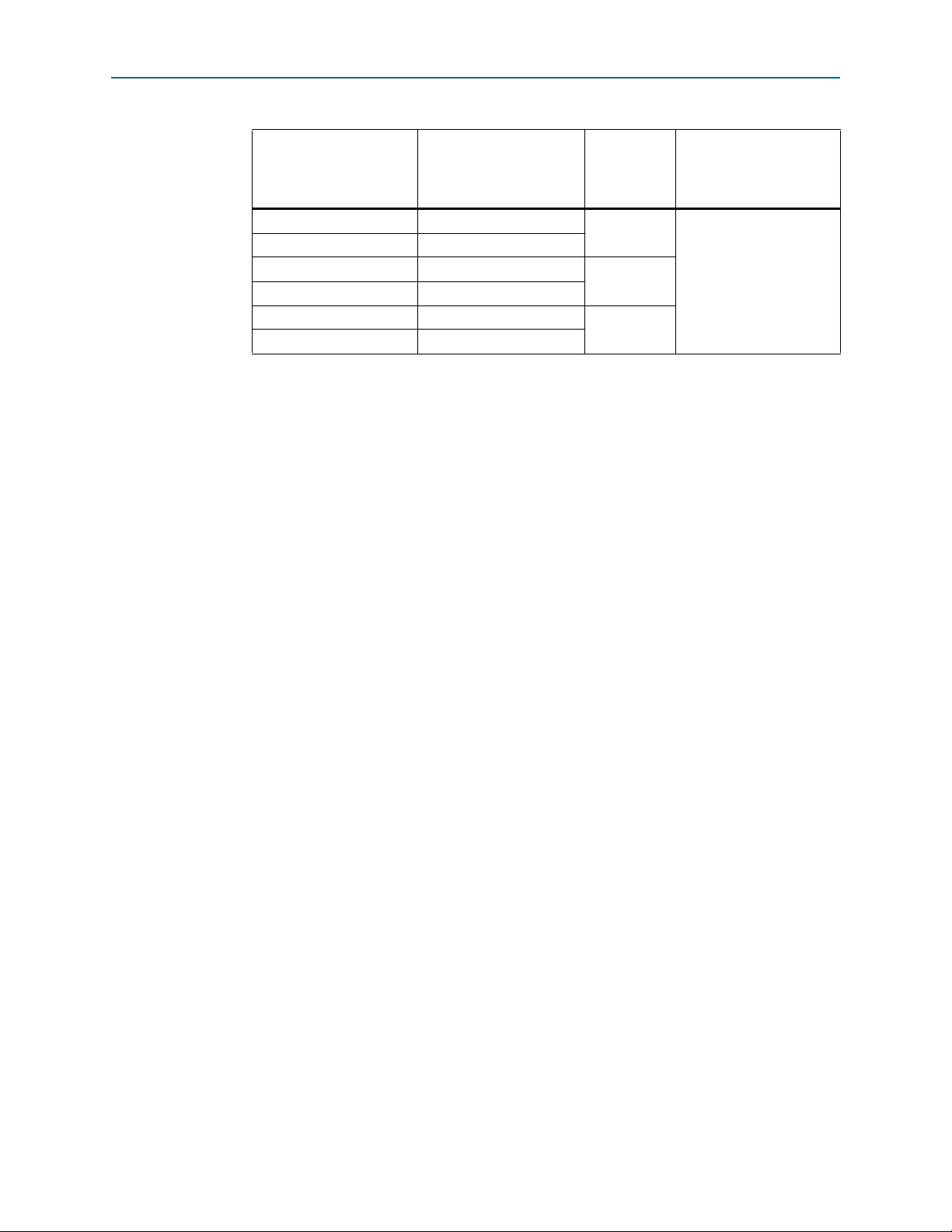

Tab le 1– 3 shows the slowest device family speed grade that supports each CPRI line

rate in each device family. Lower speed grade numbers correspond to faster devices.

Table 1–3. Slowest Recommended Device Family Speed Grades

Device Family

or Variant

614.4 1228.8 2457.6 3072.0 4915.2 6144 9830.4

(1)

(Part 1 of 2)

CPRI Line Rate (Mbps)

Stratix V GX –4 –4 –4 –4 –4 –4 -2

StratixIVGX–4–4–4–4–4–3

Arria V GT C6 C6 C6 I5 I5 I5 I5

Arria V GX C6 C6 C6 I5 I5 I5

Arria V GZ –4 –4 –4 –4 –4 –4 –3

ArriaIIGX –6–6–6–6I3

(2)

(2) (3)

I3

(3)

(4)

(3)

December 2013 Altera Corporation CPRI MegaCore Function

User Guide

Page 12

1–6 Chapter 1: About This MegaCore Function

MegaCore Verification

Table 1–3. Slowest Recommended Device Family Speed Grades

Device Family

or Variant

614.4 1228.8 2457.6 3072.0 4915.2 6144 9830.4

ArriaIIGZ –4–4–4–4–3–3

CycloneVGXC8–7–7–7

Cyclone IV GX C8, I7 C8, I7 C8, I7 –7

Notes to Table 1–3:

(1) The entry –x indicates that both the industrial speed grade Ix and the commercial speed grade Cx are supported for this device family and CPRI

line rate.

(2) Only the I3 speed grade is available for a CPRI IP core that runs at this line rate and targets the Arria II GX device family.

(3) This CPRI line rate is not supported for this device family.

(4) Altera recommends that for designs that include a 9.8304 Gbps CPRI IP core variation that targets an Arria V GT device, you use multiple seeds

in the Quartus II Design Space Explorer to find the optimal Fitter settings to meet the timing constraints. Following the Timing Advisor's

recommendations, including optimizing for speed and using LogicLock regions may be necessary to meet timing, especially for more complex

variations implemented in the largest devices.

(1)

(Part 2 of 2)

CPRI Line Rate (Mbps)

(3)

(3) (3) (3)

(3) (3) (3)

MegaCore Verification

Before releasing a version of the CPRI IP core, Altera runs comprehensive regression

tests in the current version of the Quartus

MegaWizard

™

Plug-In Manager to create the instance files. Altera tests these files in

simulation and hardware to confirm functionality.

®

II software. These tests use the

Altera tests and verifies the CPRI IP core in hardware, especially the deterministic

latency feature, for different platforms and environments.

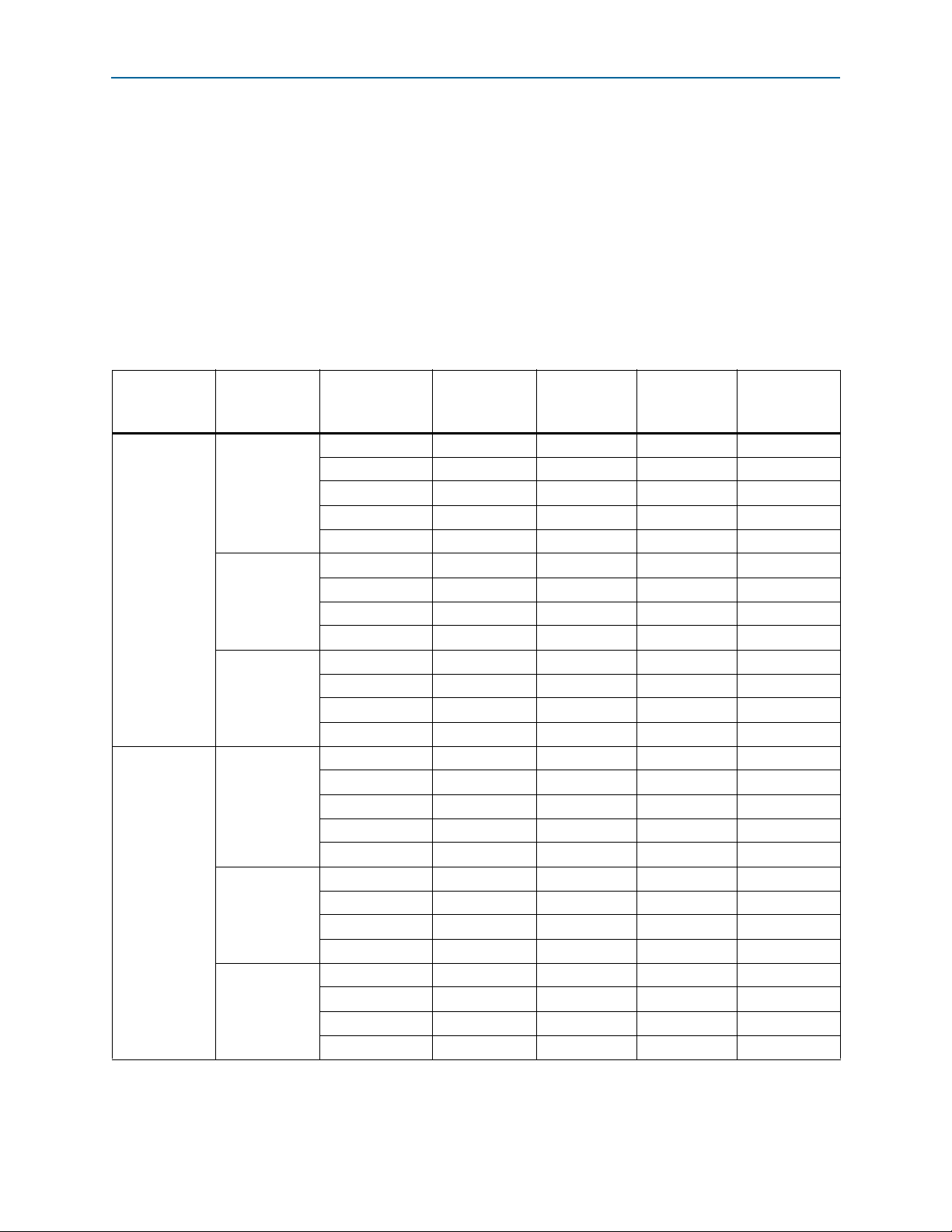

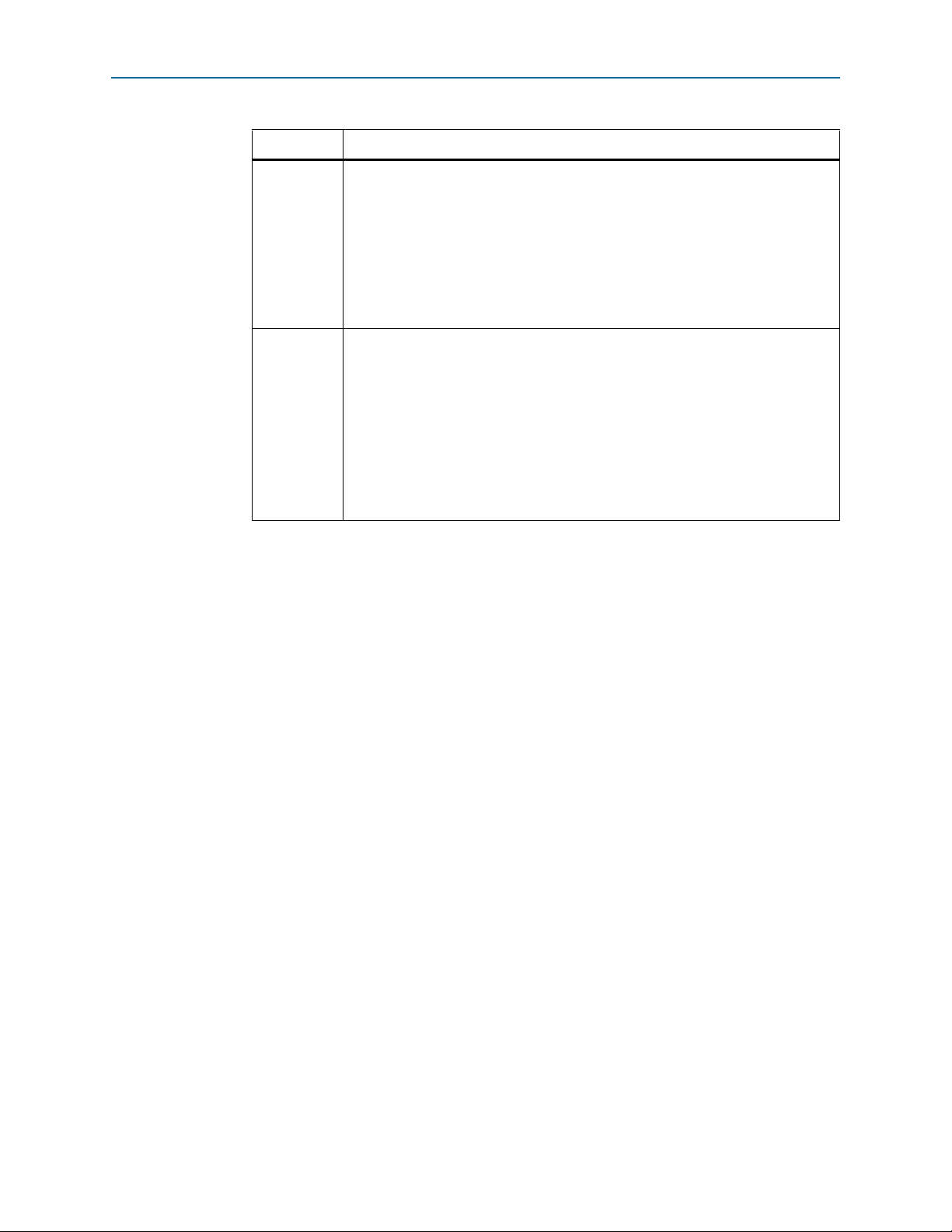

Performance and Resource Utilization

This section contains tables showing IP core variation size and performance examples.

For resource utilization information for additional CPRI IP core variations, refer to the

reports the Quartus II software generates during compilation.

Tab le 1– 4 lists the resources and expected performance for CPRI IP core variations

configured with the following features:

■ Operate in REC master mode

■ Include autorate negotiation support

■ Provide Ethernet access through the MI interface

■ Do not provide an HDLC block

■ Use Basic mapping mode

■ Clock the AxC channels with independent clocks (the Enable MAP interface

synchronization with core clock parameter is turned off)

■ Do not include automatic round-trip delay calibration logic

■ Do not include VSS access through the CPU interface

The numbers of ALMs and logic registers are rounded up to the nearest 100.

CPRI MegaCore Function December 2013 Altera Corporation

User Guide

Page 13

Chapter 1: About This MegaCore Function 1–7

Performance and Resource Utilization

Tab le 1– 4 lists results obtained with the Quartus II software v12.1 SP1 for the

following devices:

■ Stratix V GX (5SGXMA5N3F40I4

■ Arria V GT (5AGTMD3G3F31I3)

■ Arria V GX (5AGXFB3H6F35C6 for 614.4, 1228.8, 2457.6, and 3072 Mbps variations

and 5AGXFB3H4F35I5 for other variations)

■ Arria V GZ (5AGZME7K3F40I4)

■ Cyclone V GX (5CGXFC9E7F35C8 for 6144 Mbps variations and 5CGXFC9E6F35I7

for 122.8, 2457.6, and 3072 Mbps variations)

Table 1–4. CPRI IP Core FPGA Resource Utilization (Part 1 of 2)

Device

Stratix V GX

Arria GZ

Line Rate

(Mbps)

614.4

1228.8,

2457.6,

3072.0,

4915.2

6144.0,

9830.4

614.4

1228.8,

2457.6,

3072.0,

4915.2

6144.0,

9830.4

Number of

Antenna-Carrier

Interfaces

ALMs

Primary

Register

Secondary

Register

0 2089 2346 230 3

1 2695 3218 323 9

2 2867 3499 330 11

3 3032 3703 343 13

4 3185 3943 394 15

0 2062 2331 217 3

1 2662 3128 317 9

4 3126 3770 333 15

8 3810 4582 410 23

0 2450 3408 350 3

1 3241 4990 546 9

4 3734 5687 606 15

8 4443 6581 697 23

0 2068 2356 230 3

1 2786 3368 299 9

2 2984 3589 352 11

3 3189 3818 403 13

4 3378 4073 285 15

0 2029 2319 221 3

1 2796 3309 210 9

4 3321 3891 371 15

8 3998 4737 428 23

0 2438 3451 219 3

1 3488 5145 515 9

4 3988 5844 649 15

8 4651 6806 707 23

M10K or M20K

Blocks

(1)

December 2013 Altera Corporation CPRI MegaCore Function

User Guide

Page 14

1–8 Chapter 1: About This MegaCore Function

Release Information

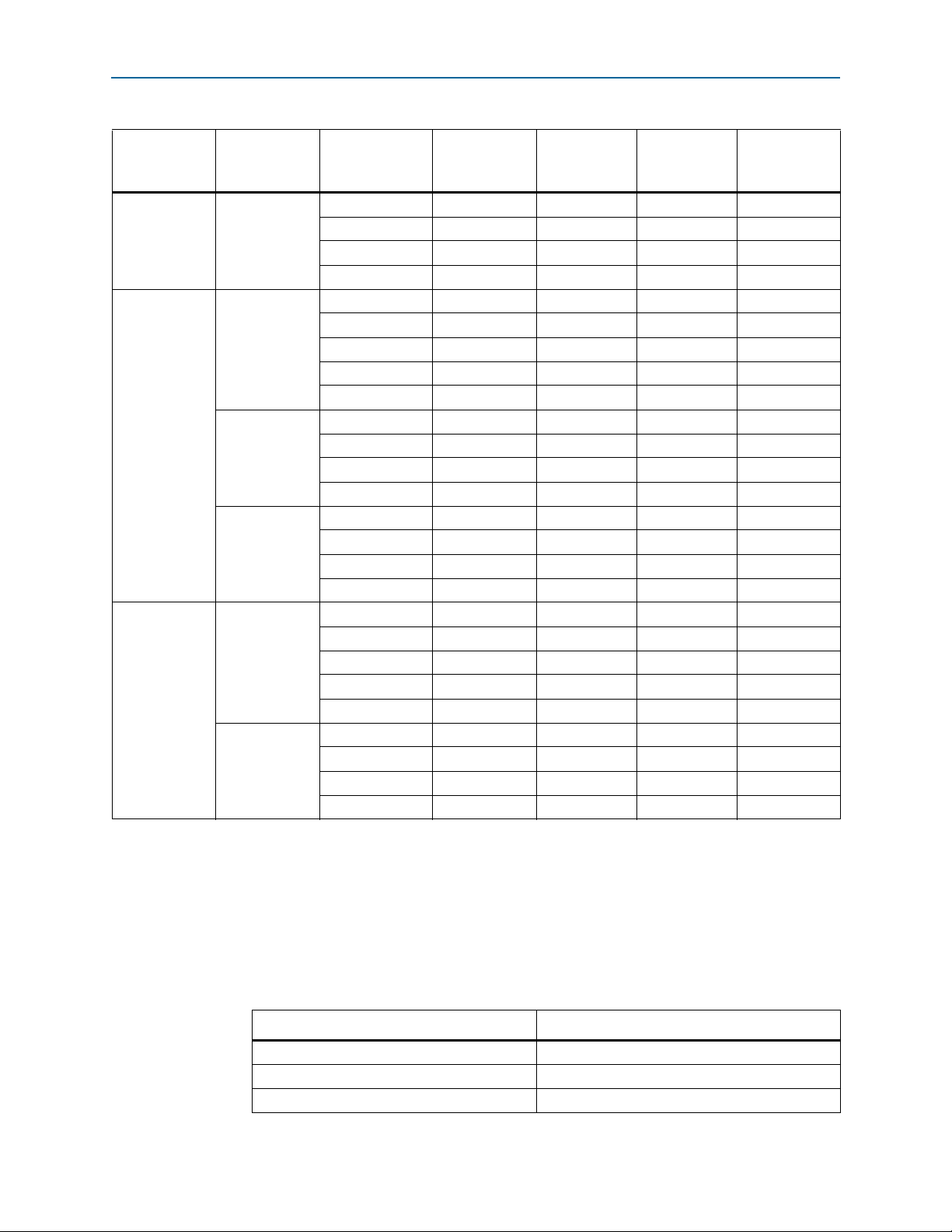

Table 1–4. CPRI IP Core FPGA Resource Utilization (Part 2 of 2)

Number of

Antenna-Carrier

Interfaces

ALMs

Primary

Register

Secondary

Register

Device

Line Rate

(Mbps)

0 6649 9239 738 5

Arria V GT

(Soft PCS

Variant)

9830.4

1 7523 10979 911 15

4 7990 11718 922 21

8 8696 12707 1057 29

0 2299 2321 202 3

1 2983 3131 428 15

614.4

2 3117 3332 291 17

3 3324 3553 287 19

4 3560 3795 414 21

0 2266 2345 175 3

Arria V GX

1228.8,

2457.6,

3072.0

1 2924 3157 186 15

4 3484 3811 237 21

8 4126 4635 285 29

0 3254 5156 169 3

4915.2,

6144.0

1 4065 6702 421 13

4 4568 7473 411 19

8 5689 8402 425 27

0 2398 2416 410 3

1 3200 3526 580 14

614.4

2 3401 3667 648 16

3 3580 3931 609 18

Cyclone V

4 3667 4016 594 20

0 2238 2417 133 3

1228.8,

2457.6,

3072.0

1 3139 3494 170 14

4 3704 4006 247 20

8 4501 4842 302 28

Note to Table 1–4:

(1) M10K blocks in Arria V GX, Arria V GT, and Cyclone V GX devices and M20K blocks in Arria V GZ and Stratix V devices.

M10K or M20K

Blocks

(1)

Release Information

Tab le 1– 5 provides information about this release of the CPRI IP core.

Table 1–5. CPRI Release Information (Part 1 of 2)

Item Description

Version 13.1

Release Date November 2013

Ordering Code IP-CPRI

CPRI MegaCore Function December 2013 Altera Corporation

User Guide

Page 15

Chapter 1: About This MegaCore Function 1–9

Installation and Licensing

Table 1–5. CPRI Release Information (Part 2 of 2)

Item Description

Product ID 00CB

Vendor ID 6AF7

Altera verifies that the current version of the Quartus II software compiles the

previous version of each Altera IP core. Any exceptions to this verification are

reported in the MegaCore IP Library Release Notes and Errata. Altera does not verify

compilation with IP core versions older than the previous release.

Installation and Licensing

The CPRI IP core is part of the MegaCore IP Library, which is distributed with the

Quartus II software. The combined software is downloadable from the Altera website,

www.altera.com.

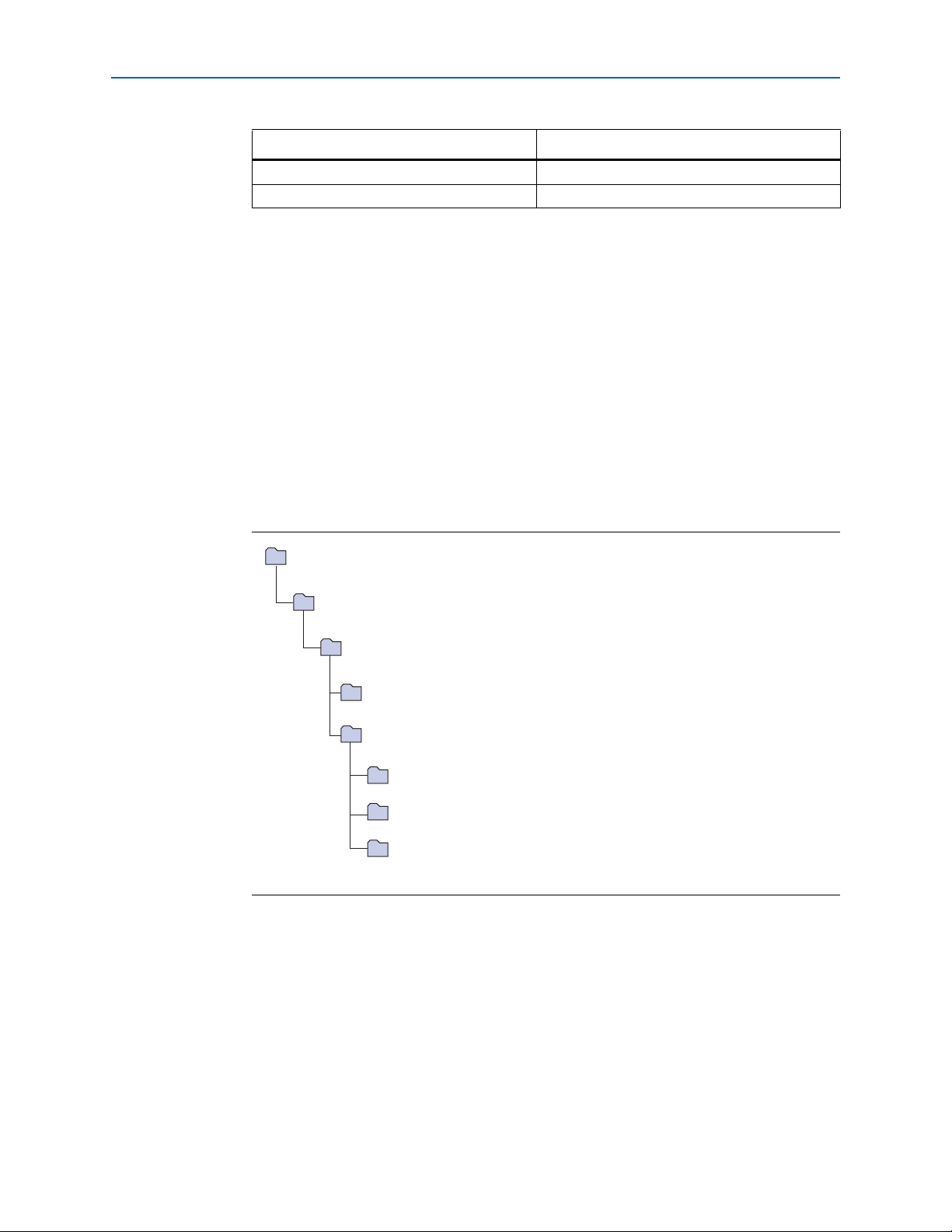

Figure 1–3 shows the directory structure after you install the CPRI IP core, where

<

path> is the installation directory. The default installation directory on Windows is

C:\altera\<version number>; on Linux it is /opt/altera<version number>.

Figure 1–3. Directory Structure

<path>

Installation directory

ip

Contains the Altera MegaCore IP Library and third-party IP cores

altera

Contains the Altera MegaCore IP Library

common

Contains shared components

cpri

Contains the CPRI IP core files

src

Contains the CPRI IP core encrypted lower-level design files

constraints

Contains the Synopsys Design Constraints and Tcl constraints scripts for the CPRI IP core

cus_demo_tb

Contains the demonstration testbenches for the CPRI IP core

You can use Altera’s free OpenCore Plus evaluation feature to evaluate the CPRI IP

core in simulation and in hardware before you purchase a license. You must purchase

a license for the CPRI IP core only when you are satisfied with its functionality and

performance, and you want to take your design to production.

After you purchase a license for the CPRI IP core, you can request a license file from

the Altera website at www.altera.com/licensing and install it on your computer.

When you request a license file, Altera emails you a license.dat file. If you do not have

internet access, contact your local Altera representative.

December 2013 Altera Corporation CPRI MegaCore Function

User Guide

Page 16

1–10 Chapter 1: About This MegaCore Function

Installation and Licensing

OpenCore Plus Evaluation

With the Altera free OpenCore Plus evaluation feature, you can perform the following

actions:

■ Simulate the behavior of a megafunction (Altera IP core or AMPP

SM

megafunction) in your system using the Quartus II software and Altera-supported

VHDL and Verilog HDL simulators

■ Verify the functionality of your design and evaluate its size and speed quickly and

easily

■ Generate time-limited device programming files for designs that include Altera IP

cores

■ Program a device and verify your design in hardware

OpenCore Plus Time-Out Behavior

OpenCore Plus hardware evaluation supports the following two operation modes:

■ Untethered—the design runs for a limited time.

■ Tethered—requires a connection between your board and the host computer. If

tethered mode is supported by all megafunctions in a design, the device can

operate for a longer time or indefinitely.

All megafunctions in a device time out simultaneously when the most restrictive

evaluation time is reached. If there is more than one megafunction in a design, a

specific megafunction's time-out behavior might be masked by the time-out behavior

of the other megafunctions.

1 For Altera IP cores, the untethered time-out is 1 hour; the tethered time-out value is

indefinite.

Your design stops working after the hardware evaluation time expires.

The CPRI IP core then behaves as if the

reset

and

cpu_reset

signals are asserted: the

CPRI link and the CPU interface reset. The transceivers do not reset, because the

transceiver quad might be shared with other designs, IP cores, and megafunctions.

The CPRI IP core cannot achieve frame synchronization, and cannot participate in

further CPRI communication.

f For information about installation and licensing, refer to Altera Software Installation and

Licensing. For information about the OpenCore Plus evaluation feature, refer to

AN 320: OpenCore Plus Evaluation of Megafunctions.

CPRI MegaCore Function December 2013 Altera Corporation

User Guide

Page 17

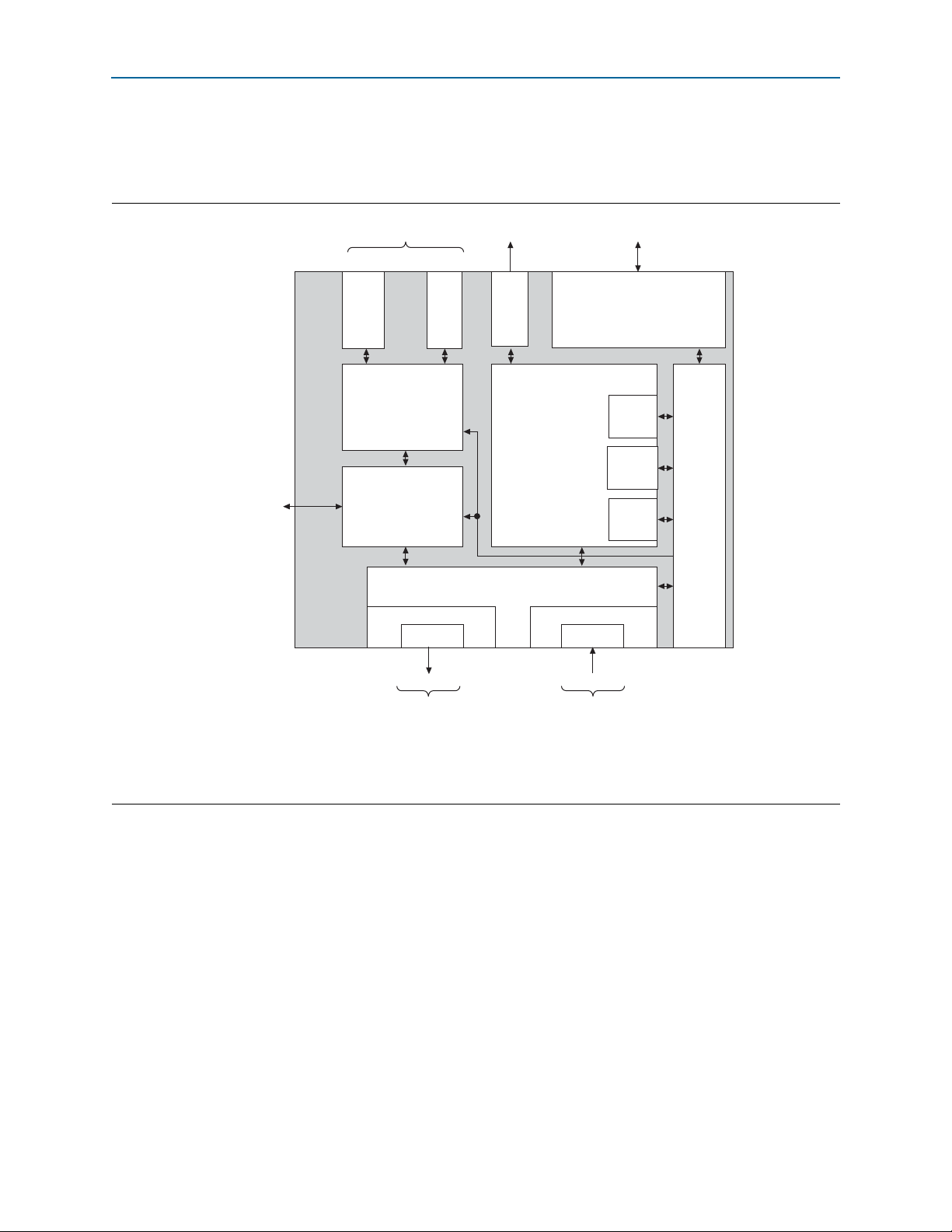

You can customize the CPRI IP core to support a wide variety of applications. You use

MegaWizard Plug-In

Manager Flow

Instantiate MegaCore

In Design

Specify Constraints

Specify Parameters

Generate

MegaCore Function

Compile Design

Program Device

Simulate with

T estbench

Generate

MegaCore Function

the MegaWizard Plug-In Manager in the Quartus II software to parameterize a

custom IP core variation in a CPRI parameter editor. The CPRI parameter editor lets

you interactively set parameter values and select optional ports.

The CPRI IP core supports the Altera MegaWizard Plug-In Manager design flow. The

CPRI IP core is not available in the Qsys design flow. To include a CPRI IP core in your

Qsys-based design, you must generate the IP core in the MegaWizard Plug-In

Manager design flow and connect it manually in the design.

MegaWizard Plug-In Manager Design Flow

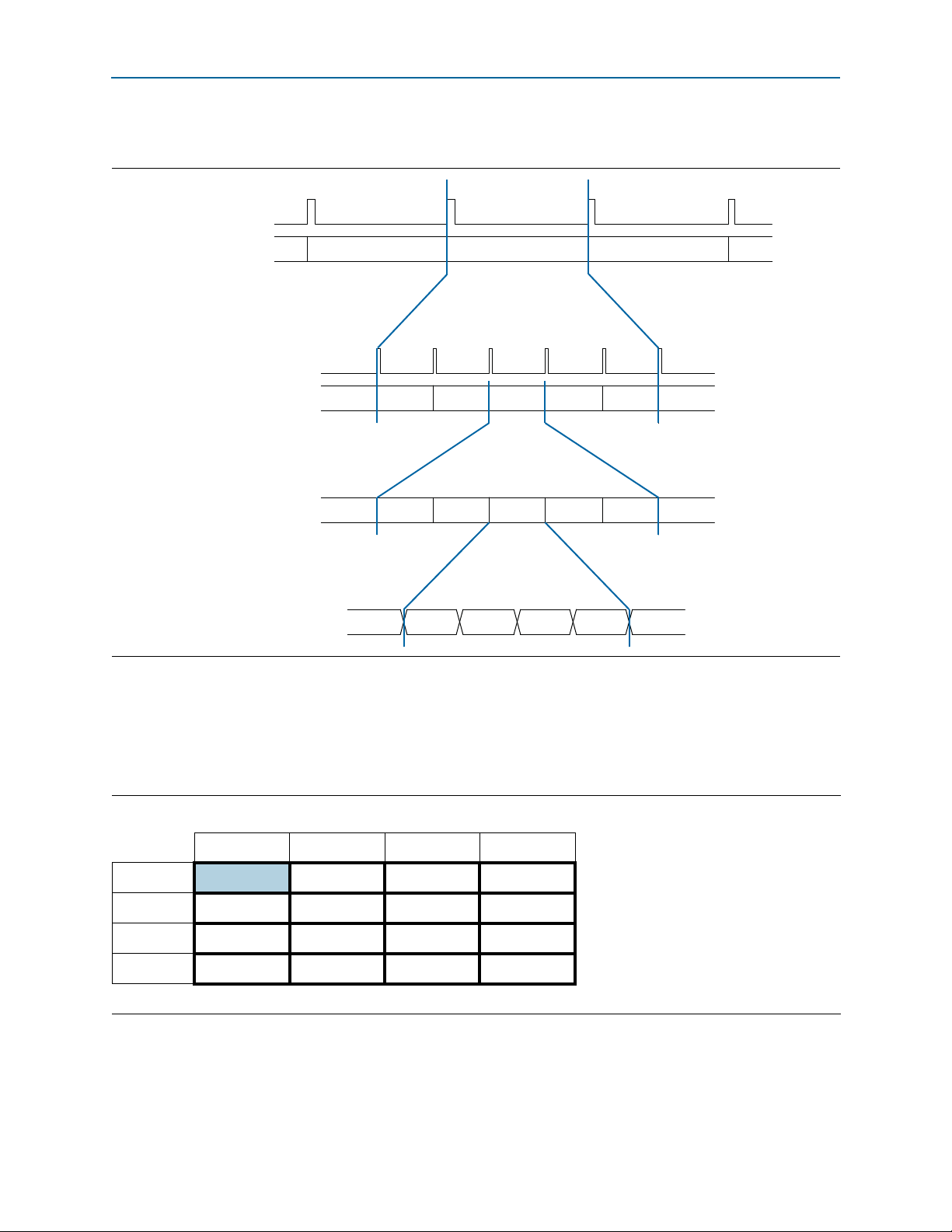

Figure 2–1 shows the stages for creating a system with the CPRI IP core and the

Quartus II software. Each stage is described in detail in subsequent sections.

Figure 2–1. CPRI Design Flow

2. Getting Started

The MegaWizard Plug-In Manager flow allows you to customize the CPRI IP core,

and manually integrate the function in your design.

December 2013 Altera Corporation CPRI MegaCore Function

User Guide

Page 18

2–2 Chapter 2: Getting Started

MegaWizard Plug-In Manager Design Flow

Specifying Parameters

To specify CPRI IP core parameters using the MegaWizard Plug-In Manager, perform

the following steps:

1. Create a Quartus II project using the New Project Wizard available from the File

menu.

2. Launch the MegaWizard Plug-In Manager from the Tools menu, and follow the

prompts in the MegaWizard Plug-In Manager interface to create a custom CPRI IP

core variation.

To select the CPRI IP core, click

Installed Plug-Ins > Interfaces > CPRI > CPRI v13.1.

3. Specify the parameters. For details about these parameters, refer to Chapter 3,

Parameter Settings.

As you specify parameters, the CPRI parameter editor displays messages about

the variation that your current settings define.

If your settings define a variation for which an autorate negotiation testbench can

be automatically generated when the CPRI IP core is generated, an information

message tells you the name of the relevant autorate negotiation testbench. For

more information about the autorate negotiation testbench and the variations that

provide it, refer to Appendix C, CPRI Autorate Negotiation Testbench.

For information about the other testbenches that can be automatically generated

with the CPRI IP core, but for which no information messages appear, refer to

Chapter 8, CPRI IP Core Demonstration Testbench.

4. Click Finish to generate the CPRI IP core and supporting files.

You might have to wait several minutes for file generation to complete.

5. When you are prompted to generate an example design, turn on Generate

Example Design. You must turn on this option to generate the testbenches

described in Chapter 8, CPRI IP Core Demonstration Testbench and in

Appendix C, CPRI Autorate Negotiation Testbench.

The prompt appears even for those few CPRI IP core variations for which no

testbench is generated. If you are generating a variation for which no testbench is

available, and you turn on Generate Example Design, a directory with

compile.tcl files is generated. You can use these compile.tcl files as initial

templates to build your own testbench.

6. Click Generate. Despite the moving progress bar, generation does not progress

until you click this button.

7. If you generate the CPRI IP core instance in a Quartus II project, you are prompted

to add the Quartus II IP File (.qip) to the current Quartus II project. You can also

turn on Automatically add Quartus II IP Files to all projects.

The .qip file is generated by the parameter editor, and contains information about

the generated IP core. In most cases, the .qip file contains all of the necessary

information required to process the IP core in the Quartus II compiler. The

parameter editor generates a single .qip file for each instance of the IP core.

CPRI MegaCore Function December 2013 Altera Corporation

User Guide

Page 19

Chapter 2: Getting Started 2–3

MegaWizard Plug-In Manager Design Flow

Generating your custom CPRI IP core variation creates a set of HDL files and

simulation models. You can now integrate your custom CPRI IP core variation in your

design, simulate, and compile.

Simulation Files

Generating a CPRI IP core creates an <instance_name>_sim directory with a

subdirectory for each of four different Altera-supported simulators for the current

software release. Each of the vendor-specific directories contains files and scripts to

simulate your CPRI IP core with that vendor’s simulation tools.

The <instance_name>_sim/altera_cpri directory contains the top-level simulation file

for your CPRI IP core.

Generating a CPRI IP core creates a more complex directory structure for Arria V,

Cyclone V, and Stratix V variations than for variations that target other device

families, because the Arria V, Cyclone V, and Stratix V variations instantiate an Altera

Deterministic Latency PHY IP core or an Altera Native PHY IP core. In an Arria V,

Cyclone V, or Stratix V variation, your <instance_name>_sim directory contains

multiple subdirectories, one for each of the various components in the CPRI IP core, in

addition to the individual directories for vendors for four different simulators.

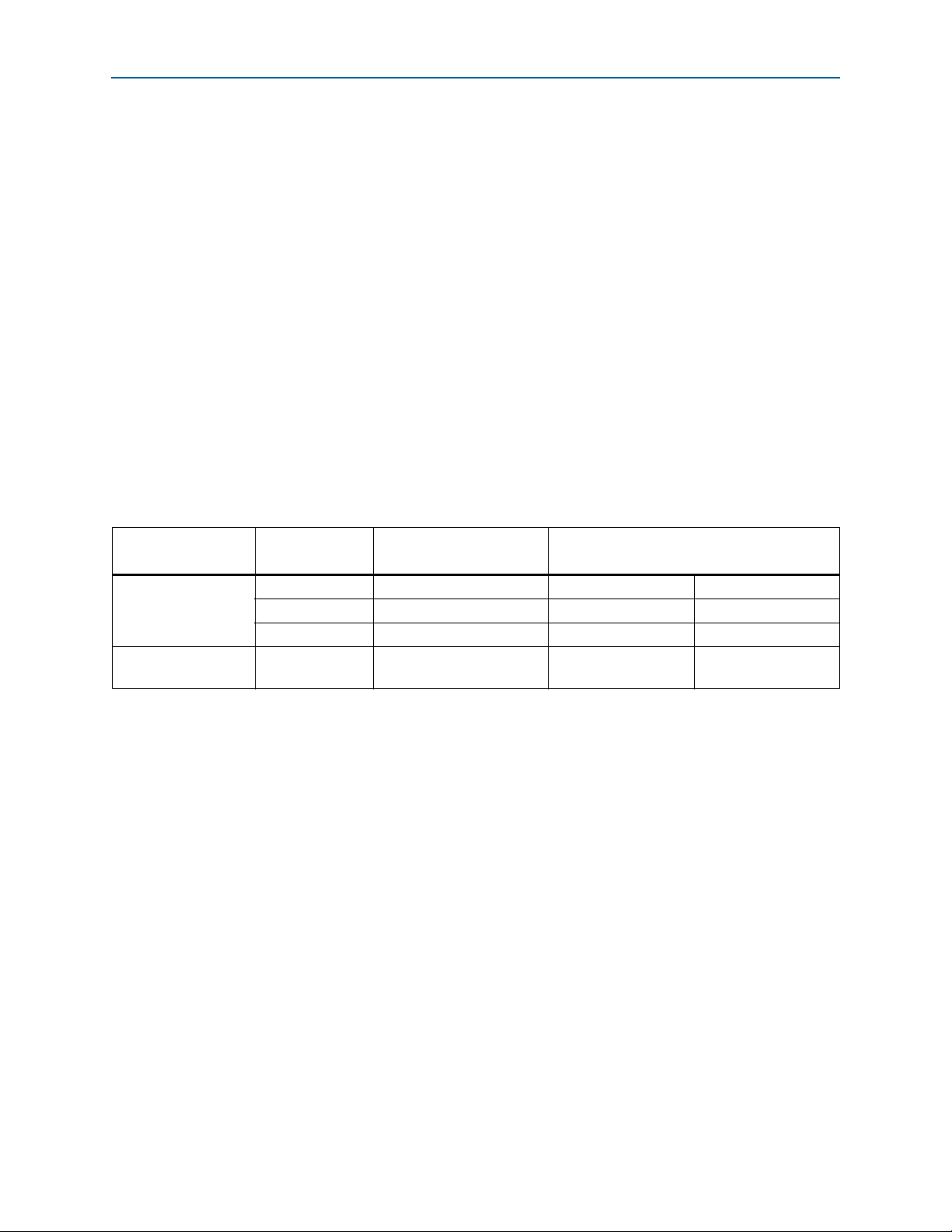

Figure 2–2 shows the directory structure of your CPRI IP core that contains a

Deterministic Latency PHY IP core and generates a testbench. Not all CPRI IP core

variations provide matching demonstration testbenches. For information about the

CPRI IP core variations that provide a testbench, refer to “Simulating the Design”.

Figure 2–2. Generated CPRI IP Core Directory Structure for Most 28-nm Variations

<working directory>

Quartus II project working directory

<instance name>

CPRI IP core instance HDL files

<instance name>_sim

CPRI IP core instance simulation files and scripts

altera_cpri

Contains the CPRI IP core instance top-level simulation file

altera_cpri_instance, altera_merlin_master_translator,

altera_merlin_slave_translator, altera_xcvr_det_latency

Contain the CPRI IP core instance lower-level simulation files

Vendor-specific directories contain simulation scripts

<instance name>_testbench

Contains the VHDL and System Verilog testbench simulation files

altera_cpri

Contains the lower-level testbench simulation files

The altera_xcvr_det_latency directory contains the files to simulate the Altera

Deterministic Latency PHY IP core that is generated as part of your CPRI IP core. It

also contains a mentor subdirectory with IEEE encrypted files to simulate the PHY IP

core efficiently.

December 2013 Altera Corporation CPRI MegaCore Function

User Guide

Page 20

2–4 Chapter 2: Getting Started

MegaWizard Plug-In Manager Design Flow

Simulating the Design

During the design process, to check your design quickly, you can simulate your CPRI

IP core with any of several Altera-supported EDA simulation tools.

f For more information about these tools and how to simulate designs created using the

Quartus II software, refer to the “Simulation” section in volume 3 of the Quartus II

Handbook.

Most CPRI IP core variations support a demonstration testbench. You can simulate

your CPRI IP core variation using its IP functional simulation model and

demonstration testbench. The IP functional simulation model, and testbench files for

the CPRI IP core variations that support demonstration testbenches, are generated in

your project directory when you generate your CPRI IP core. The testbench files

include scripts to compile and run the demonstration testbench. The testbench

demonstrates how to instantiate a model in a design and includes simple stimuli to

control the user interfaces of the CPRI IP core.

1 The autorate negotiation testbench is generated in VHDL, and the non-autorate

negotiation testbench is generated in System Verilog. If you specify Verilog HDL in

the MegaWizard Plug-In Manager, it generates a Verilog HDL IP functional

simulation model for the CPRI IP core. If you specify VHDL, the MegaWizard Plug-In

Manager generates a VHDL IP functional simulation model for the CPRI IP core.

Testbenches are generated as supported by the CPRI IP core variation you specify if

you turn on Generate Example Design. You can use the Verilog HDL functional

simulation model with the VHDL demonstration testbench for simulation, or vice

versa, using a mixed-language simulator.

For a complete list of models or libraries required to simulate the CPRI IP core, refer to

the compile.tcl scripts provided with the demonstration testbenches described in

Chapter 8, CPRI IP Core Demonstration Testbench and in Appendix C, CPRI Autorate

Negotiation Testbench. If you turn on Generate Example Design for a variation

without a demonstration testbench, you can view the example scripts in the generated

testbench directory, and use them as a basis to assist you in building your own

testbench.

Not all variations provide demonstration testbenches. To run a demonstration

testbench, you must generate a variation that provides a working testbench. To ensure

your CPRI variation has a non-autorate negotiation testbench you can simulate, set

the following values in the CPRI parameter editor:

■ Operation mode must have the value of Master.

■ If the CPRI variation has a MAP interface, Mapping mode must have the value of

All or Basic.

■ If the CPRI variation has a MAP interface, Enable MAP interface synchronization

with core clock must be turned off.

To ensure your CPRI variation has an autorate negotiation testbench, set the following

values in the CPRI parameter editor:

■ Operation mode must have the value of Master.

■ Enable auto-rate negotiation must be turned on.

CPRI MegaCore Function December 2013 Altera Corporation

User Guide

Page 21

Chapter 2: Getting Started 2–5

Integrating the CPRI IP Core in a Design

■ Include MAC block must be turned on.

■ Number of antenna-carrier interfaces must have the value of zero.

■ Include HDLC block must be turned off.

Refer to Chapter 3, Parameter Settings for information about these parameter values.

Refer to Chapter 8, CPRI IP Core Demonstration Testbench for more information

about the non-autorate negotiation testbench and to Appendix C, CPRI Autorate

Negotiation Testbench for more information about the autorate negotiation testbench.

f For information about IP functional simulation models, refer to the Simulating Altera

Designs chapter in volume 3 of the Quartus II Handbook.

Integrating the CPRI IP Core in a Design

To compile the CPRI IP core and configure it on a device, you must integrate it in a

Quartus II project that provides additional functionality and constraints.

Supporting the Transceivers

When you integrate your CPRI IP core variation in your design, observe the following

connection requirements:

■ In Arria II, Cyclone IV GX, and Stratix IV GX designs:

■ Ensure that you connect the calibration clock (

signal with the appropriate frequency range of 10–125 MHz. The

gxb_cal_blk_clk

) to a clock

cal_blk_clk

ports on other components that use transceivers must be connected to the same

clock signal.

■ Add a dynamic reconfiguration block (

altgx_reconfig

) and connect it as

specified in the Arria II Device Handbook, Cyclone IV Device Handbook, or

Stratix IV Device Handbook. This block supports offset cancellation to

compensate for analog voltages offset from required ranges due to process

variations. This block is not required for CPRI IP core autorate negotiation to

function correctly. The design compiles without the

altgx_reconfig

block, but

it cannot function correctly in hardware.

■ In Arria V, Cyclone V, and Stratix V designs, add an Altera Transceiver

Reconfiguration Controller and connect it as specified in the Altera Transceiver PHY

IP Core User Guide. This block supports offset cancellation to compensate for

analog voltages offset from required ranges due to process variations. The design

does compile without the Altera Transceiver Reconfiguration Controller, with a

critical warning, but it cannot function correctly in hardware.

Specifying Constraints

Altera provides a Synopsys Design Constraints (.sdc) file that you must apply to

ensure that the CPRI IP core meets design timing requirements. In most cases the

script requires modification for your design. For modification guidelines, refer to

Appendix F, Integrating the CPRI IP Core Timing Constraints in the Full Design.

December 2013 Altera Corporation CPRI MegaCore Function

User Guide

Page 22

2–6 Chapter 2: Getting Started

In addition, before you compile your system to generate an SRAM Object File (.sof)

with which to configure your device, Altera recommends that you create assignments

for the high-speed transceiver VCCH settings.

To create assignments for the high-speed transceiver VCCH settings, perform the

following steps:

1. In the Quartus II window, on the Assignments menu, click Assignment Editor.

2. In the <<new>> cell in the To column, type the top-level signal name for your

CPRI IP core instance

3. Double-click in the Assignment Name column and click I/O Standard.

4. Double-click in the Val u e column and click your standard (for example, 1.5-V

PCML).

5. In the new <<new>> row, repeat steps 2 to 4 for your CPRI IP core instance

gxb_rxdatain

f For information about timing analyzers, refer to the Quartus II Help and the “Timing

Analysis” section in volume 3 of the Quartus II Handbook.

signal.

gxb_txdataout

signal.

Compiling and Programming the Device

Compiling and Programming the Device

You can use the Start Compilation command on the Processing menu in the

Quartus II software to compile your design. After successfully compiling your design,

program the targeted Altera device with the Programmer and verify the design in

hardware.

1 Before compiling your CPRI IP core or other incomplete CPRI design in the Quartus II

software, you must assign unconnected CPRI IP core signals to virtual pins.

f For information about compiling your design in the Quartus II software, refer to the

Quartus II Incremental Compilation for Hierarchical and Team-Based Design chapter in

volume 1 of the Quartus II Handbook. For information about programming an Altera

device, refer to the “Device Programming” section in volume 3 of the Quartus II

Handbook.

Instantiating Multiple CPRI IP Cores

If you want to instantiate multiple CPRI IP cores in an Arria II, Cyclone IV GX, or

Stratix IV GX device, to ensure your design optimizes its use of device pins, you must

observe the following additional requirements:

CPRI MegaCore Function December 2013 Altera Corporation

User Guide

Page 23

Chapter 2: Getting Started 2–7

Instantiating Multiple CPRI IP Cores

■ You m u st en su re t ha t th e

gxb_cal_blk_clk

input and

gxb_powerdown

signals are

connected according to the requirements for your target device family.

■ You must ensure that a single calibration clock source drives the

gxb_cal_blk_clk

input to each CPRI IP core (or any other megafunction or

user logic that uses the ALTGX megafunction).

■ When you merge multiple CPRI IP cores in a single transceiver block, the same

signal must drive

gxb_powerdown

to each of the CPRI IP core variations and

other megafunctions, Altera IP cores, and user logic that use the ALTGX

megafunction.

■ You must ensure that the instances each have different starting channel numbers.

Multiple CPRI IP cores in a single device must use distinct transceiver channels.

You enforce this restriction by specifying different starting channel numbers for

the distinct CPRI IP cores. Refer to Chapter 3, Parameter Settings.

■ To configure multiple CPRI IP cores in a single transceiver block, you must specify

in your Quartus Settings File (.qsf) that these CPRI link data lines are configured

in the same

outgoing CPRI link

set_instance_assignment -name GXB_TX_PLL_RECONFIG_GROUP 1 -to cN_gxb_txdataout

GXB_TX_PLL_RECONFIG_GROUP

cN_gxb_txdataout

:

, using the following syntax for each

December 2013 Altera Corporation CPRI MegaCore Function

User Guide

Page 24

2–8 Chapter 2: Getting Started

Instantiating Multiple CPRI IP Cores

CPRI MegaCore Function December 2013 Altera Corporation

User Guide

Page 25

3. Parameter Settings

You customize the CPRI IP core by specifying parameters in the CPRI parameter

editor, which you access from the MegaWizard Plug-In Manager in the Quartus II

software.

This chapter describes the parameters and how they affect the behavior of the CPRI IP

core. You can modify parameter values to specify the following CPRI IP core

properties:

■ Default clocking mode—whether this CPRI IP core instance is configured initially

with slave clocking mode (RE slave) or with master clocking mode (REC or RE

master).

■ Line rate.

■ Autorate negotiation—whether this CPRI IP core instance supports the connection

of external logic to implement autorate negotiation.

■ Starting channel number. This option is available only in the following devices:

■ Arria II GX and Arria II GZ

■ Cyclone IV

■ Stratix IV

■ Depth of the low-level receiver elastic buffer.

■ Transceiver reference clock frequency. This option is available only in Arria V,

Cyclone V, and Stratix V devices.

■ Ethernet MAC—whether to include an internal Ethernet MAC block or provide an

MII to connect to an external Ethernet module. These two options are mutually

exclusive.

■ HDLC block—whether to include an internal HDLC block or not.

■ Number of antenna-carrier interfaces.

■ Whether the antenna-carrier interfaces are clocked by the CPRI IP core clock

cpri_clkout

■ Mapping modes—select the mode: All, Basic, Advanced1, Advanced2, and

or by external clocks.

Advanced3.

■ Whether to include an automatic round-trip delay calibration block or not.

■ Whether to allow vendor-specific space (VSS) access through the CPU interface or

not.

Physical Layer Parameters

This section lists the parameters that affect the configuration of the physical layer of

the CPRI IP core.

December 2013 Altera Corporation CPRI MegaCore Function

User Guide

Page 26

3–2 Chapter 3: Parameter Settings

Physical Layer Parameters

Operation Mode Parameter

The Operation mode parameter specifies whether the CPRI IP core is configured with

slave clocking mode or with master clocking mode. An REC is configured with master

clocking mode.

The value of this parameter determines the initial operation mode of the CPRI IP core.

In IP core variations that target an Arria V, Cyclone V, or Stratix V device, you can

modify the IP core operation mode dynamically by modifying the value of the

operation_mode

bit of the

CPRI_CONFIG

register (Table 7–6 on page 7–4).

In your design, you must connect the clocks appropriately for the operation mode.

Refer to “Clock Diagrams for the CPRI IP Core” on page 4–5.

For information about how to dynamically switch the clock mode of your CPRI IP

core in variations that target an Arria V, Cyclone V, or Stratix V device, refer to

“Dynamically Switching Clock Mode” on page 4–9.

Line Rate Parameter

The Line rate parameter specifies the line rate on the CPRI link in gigabits per second

(Gbps). Ta bl e 3 –1 lists the CPRI line rates that each device family supports. A

checkmark indicates a supported variation.

Table 3–1. Device Family Support for CPRI Line Rates

Device Family

or Variant

Arria II GX vvvvvv—

Arria II GZ vvvvvv—

Arria V GX vvvvvv—

Arria V GT vvvvvvv

Arria V GZ vvvvvvv

Cyclone IV GX vvvv———

Cyclone V GX vvvv———

Stratix IV GX vvvvvv—

Stratix V GX vvvvvvv

Stratix V GT vvvvvvv

Note to Tab le 3– 1:

(1) Refer to Table 1–3 on page 1–5 for information about the device speed grades that support each CPRI line rate.

The parameter editor does not enforce these restrictions. However, if you target a device whose speed grade does

not support the CPRI line rate you configure, compilation fails because the design cannot meet timing in hardware.

0.6144 1.2288 2.4576 3.072 4.9152 6.144 9.8304

CPRI Line Rate (Gbps)

(1)

CPRI MegaCore Function December 2013 Altera Corporation

User Guide

Page 27

Chapter 3: Parameter Settings 3–3

Physical Layer Parameters

Enable Autorate Negotiation

Autorate negotiation is the process of stepping down from a higher target CPRI line

rate to a lower target CPRI line rate if you are unable to establish a link at the higher

line rate. If your CPRI IP core has autorate negotiation enabled, and you program it to

step down from its highest target CPRI line rate to its lower target CPRI line rates

when it does not achieve frame synchronization, your CPRI IP core achieves frame

synchronization at the highest possible CPRI line rate in its range of potential line

rates, depending on the capability of its CPRI partner.

For information about the autorate negotiation feature, refer to Appendix B,

Implementing CPRI Link Autorate Negotiation.

Turn o n t he Enable auto-rate negotiation parameter to specify that your CPRI IP core

supports autorate negotiation. By default, this parameter is turned off.

Transceiver Starting Channel Number

You can specify the starting number for the CPRI IP core transceiver. For a CPRI IP

core master, the Master transceiver starting channel number specifies the starting

channel number for the transceiver.

For a CPRI IP core configured with slave clocking mode, the Slave transmitter

starting channel number and Slave receiver starting channel number are two

separate parameters. Both must have values that are starting channel numbers

available in your design. The two numbers must be different but the Quartus II

software creates an FPGA configuration with a single slave transceiver.

If you instantiate multiple CPRI IP cores on the same device, you must ensure each

uses distinct transceiver channels.

These parameters are not available in Arria V, Cyclone V, and Stratix V devices.

Rx Elastic Buffer Depth

You can specify the depth of the Rx elastic buffer in the CPRI Receiver block. The

Receiver buffer depth value is the log

are 4 to 8, inclusive.

The default depth of the Rx elastic buffer is 64, specified by the Receiver buffer depth

parameter default value of 6. For most systems, the default Rx elastic buffer depth is

adequate to handle dispersion, jitter, and drift that can occur on the link while the

system is running. However, the parameter is available for cases in which additional

depth is required.

1 Altera recommends that you set Receiver buffer depth to 4 in CPRI RE slave

variations.

of the Rx elastic buffer depth. Allowed values

2

CPRI IP core variations configured at a CPRI line rate of 9830.4 Mbps that target an

Arria V GT device do not include an Rx elastic buffer. However, this parameter affects

the depth of the RX buffer between the soft PCS and the Altera Transceiver Native

PHY IP core, instead. Refer to Figure 4–4 on page 4–8 and Figure 4–5 on page 4–9.

f For information about the Altera Transceiver Native PHY IP core, refer to the Altera

Transceiver PHY IP Core User Guide.

December 2013 Altera Corporation CPRI MegaCore Function

User Guide

Page 28

3–4 Chapter 3: Parameter Settings

The value you specify for Receiver buffer depth is referred to as WIDTH_RX_BUF in

this user guide.

For more information about the Rx elastic buffer, refer to “Rx Elastic Buffer” on

page 4–54.

Data Link Layer Parameters

Transceiver Reference Clock Frequency

If your CPRI variation targets an Arria V, Cyclone V, or Stratix V device, the

Transceiver reference clock frequency parameter is available. Use this parameter to

modify the expected frequency of the CPRI transceiver input reference clock to the

frequency of an available clock for your design.

The frequency you specify is an input parameter to the Altera Deterministic Latency

PHY IP core that is included in your Arria V, Cyclone V, or Stratix V CPRI variation.

Values available at each CPRI line rate are the reference clock frequencies for which

the Deterministic Latency PHY IP core supports the target CPRI line rate. The default

value is 122.88 MHz.

In the case of an Arria V GT variation configured with CPRI line rate 9830.4 Mbps, the

frequency is an input parameter to the Altera Native PHY IP core.

f For more information about the Altera Deterministic Latency PHY IP core and the

Altera Native PHY IP core, refer to the Altera Transceiver PHY IP Core User Guide.

Automatic Round-Trip Delay Calibration

Turn o n t he Automatic round-trip delay calibration parameter to specify that your

CPRI IP core includes the calibration logic. By default, the parameter is turned off.

f For more information on automatic round-trip calibration delay feature, refer to

“Dynamic Pipelining for Automatic Round-Trip Delay Calibration” on page E–19

Data Link Layer Parameters

This section lists the parameter that affects the configuration of the data link layer of

the CPRI IP core.

Include MAC Block

Turn o n t he Include MAC block parameter to specify that your CPRI IP core includes

an internal Ethernet MAC block. By default, this parameter is turned off. If this

parameter is turned off, the CPRI IP core implements the media-independent

interface (MII) to your own external Ethernet MAC, instead.

If this parameter is turned off in your CPRI IP core, your application cannot access the

Ethernet registers. Attempts to access these registers read zeroes and do not write

successfully, as for a reserved register address.

For information about the internal Ethernet MAC block, refer to “Accessing the

Ethernet Channel” on page 4–47.

For information about the MII, refer to “Media Independent Interface to an External

Ethernet Block” on page 4–37.

CPRI MegaCore Function December 2013 Altera Corporation

User Guide

Page 29

Chapter 3: Parameter Settings 3–5

Application Layer Parameters

Include HDLC Block

Turn o n t he Include HDLC block parameter to specify that your CPRI IP core

includes an internal HDLC block. By default, this parameter is turned off.

If this parameter is turned off in your CPRI IP core, your application cannot access the

HDLC registers. Attempts to access these registers read zeroes and do not write

successfully, as for a reserved register address.

For information about the HDLC block, refer to “Accessing the HDLC Channel” on

page 4–50.

Application Layer Parameters

This section lists the parameters that affect the configuration of the application layer

of the CPRI IP core.

Mapping Mode

The Mapping mode(s) parameter specifies whether your CPRI IP core MAP interface

supports a programmable AxC mapping mode or is configured with a specific

mapping mode. Tab le 3– 2 lists the supported values.

Table 3–2. MAP Interface AxC Mapping Mode Support (Part 1 of 2)

Value Description

If you select this value, you configure a CPRI IP core which you can program

dynamically to be in any mapping mode. In this case, you determine the current

mapping mode for your CPRI IP core by programming the

All

Basic

Advanced 1

CPRI_MAP_CONFIG

For backward compatibility with previous releases of the CPRI IP core, the value of

All is the default value for this parameter.

For information about the

page 7–15.

Your CPRI IP core MAP interface is configured to function in basic mapping mode

only. This mapping mode has the following features:

■ Conforms to the description in Sections 4.2.7.2.2 and 4.2.7.2.3 of the CPRI

Specification V4.2 Interface Specification.

■ Supports communication that complies with the LTE/E-UTRA or UMTS/WCDMA

standard.