Page 1

Arria V GT FPGA Development Board Reference Manual

Arria V GT FPGA Development Board

Reference Manual

101 Innovation Drive

San Jose, CA 95134

www.altera.com

MNL-01074-1.2

Feedback Subscribe

Page 2

© 2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos

are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its

semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and

services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service

described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying

on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

December 2014 Altera Corporation Arria V GT FPGA Development Board

Reference Manual

Page 3

Contents

Chapter 1. Overview

General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

Board Component Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–2

Dual FPGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–3

FPGA 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–3

FPGA 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–4

Development Board Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–5

Handling the Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–5

Chapter 2. Board Components

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1

Board Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–2

Featured Device: Arria V GT FPGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–6

I/O Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–6

MAX II CPLD EPM2210 System Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–8

Configuration, Status, and Setup Elements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–14

Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–14

FPGA Programming over On-Board USB-Blaster II . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–14

FPGA Programming from Flash Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–16

FPGA Programming over External USB-Blaster . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–18

Status Elements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–18

Setup Elements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–20

Board Settings DIP Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–20

JTAG Settings DIP Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–20

PCI Express Control DIP Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–21

CPU Reset Push Button . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–21

MAX II Reset Push Button . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–21

Configuration Push Button . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–21

Image Select Push Button . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–22

Clock Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–22

On-Board Oscillators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–22

Off-Board Clock Input/Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–25

General User Input/Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–27

User-Defined Push Buttons . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–27

User-Defined DIP Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–27

User-Defined LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–28

General User-Defined LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–28

HSMC User-Defined LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–30

LCD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–30

SDI Video Output/Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–31

Components and Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–33

PCI Express . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–33

10/100/1000 Ethernet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–36

HSMC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–37

SFP+ Modules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–45

FMC Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–46

Bull's Eye Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–52

Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–54

December 2014 Altera Corporation Arria V GT FPGA Development Board

Reference Manual

Page 4

iv ContentsContents

DDR3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–54

DDR3A for FPGA 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–54

DDR3B/C for FPGA 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–59

QDRII+ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–64

Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–67

Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–68

Power Distribution System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–69

Power Measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–70

Statement of China-RoHS Compliance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–72

Chapter 3. Board Components Reference

Additional Information

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

How to Contact Altera . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

Typographic Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

Arria V GT FPGA Development Board December 2014 Altera Corporation

Reference Manual

Page 5

This document describes the hardware features of the Arria® V GT FPGA

development board, including the detailed pin-out and component reference

information required to create custom FPGA designs that interface with all

components of the board.

General Description

The Arria V GT FPGA development board provides a hardware platform for

developing and prototyping low-power, high-performance, and logic-intensive

designs using Altera’s Arria V GT FPGA device. The board provides a wide range of

peripherals and memory interfaces to facilitate the development of Arria V GT FPGA

designs.

1. Overview

Two high-speed mezzanine card (HSMC) connectors are available to add additional

functionality via a variety of HSMCs available from Altera

®

and various partners.

f To see a list of the latest HSMCs available or to download a copy of the HSMC

specification, refer to the Development Board Daughtercards page of the Altera

website.

Design advancements and innovations, such as the PCI Express hard IP

implementation and programmable power technology ensure that designs

implemented in the Arria V GT FPGAs operate faster, with lower power, and have a

faster time to market than previous FPGA families.

f For more information on the following topics, refer to the respective documents:

■ Arria V device family, refer to the Arria V Device Handbook.

■ PCI Express MegaCore function, refer to the PCI Express Compiler User Guide.

■ HSMC Specification, refer to the High Speed Mezzanine Card (HSMC) Specification.

December 2014 Altera Corporation Arria V GT FPGA Development Board

Reference Manual

Page 6

1–2 Chapter 1: Overview

Board Component Blocks

Board Component Blocks

The development board features the following major component blocks:

■ Two Arria V GT FPGA 5AGTFD7K3F40I3N in the 1517-pin FineLine BGA (FBGA)

package

■ 504K LEs

■ 190,240 adaptive logic modules (ALMs)

■ 24,140 Kbit (Kb) M10K on-die memory

■ 2,906 Kb MLAB memory

■ 36 transceivers

■ 16 phase locked loops (PLLs)

■ 2,312 18x18 multipliers

■ 1.15-V core voltage

■ MAX

■ FPGA configuration circuitry

®

II CPLD EPM2210GF324 System Controller in the 324-pin FBGA package

■ MAX

II CPLD EPM570GM100 and flash fast passive parallel (FPP)

configuration

■ On-board USB-Blaster

TM

II for use with the Quartus® II Programmer

■ Clocking circuitry

■ Nine on-board oscillators

■ One 50-MHz oscillator

■ Two 125-MHz oscillators

■ Clock buffer with six outputs sourced by SMA or programmable oscillator

with a default frequency of 100-MHz

■ One programmable oscillator with a default frequency of 148.5-MHz

■ Four programmable oscillators with four outputs each of various default

frequencies

■ Clock buffer with two outputs sourced by one of the above four

programmable oscillators with one output to the FPGA reference clock and

Bull's Eye

■ SMA connectors for external LVPECL clock input

■ Power supply

■ 14-V – 20-V DC input

■ PCI Express edge connector power

■ 12-V PCI Express ATX supply

®

SMA

■ On-board power measurement circuitry

Arria V GT FPGA Development Board December 2014 Altera Corporation

Reference Manual

Page 7

Chapter 1: Overview 1–3

Board Component Blocks

■ Mechanical

■ PCI Express long form factor (4.376” x 10.45”)

■ PCI Express chassis or bench-top operation

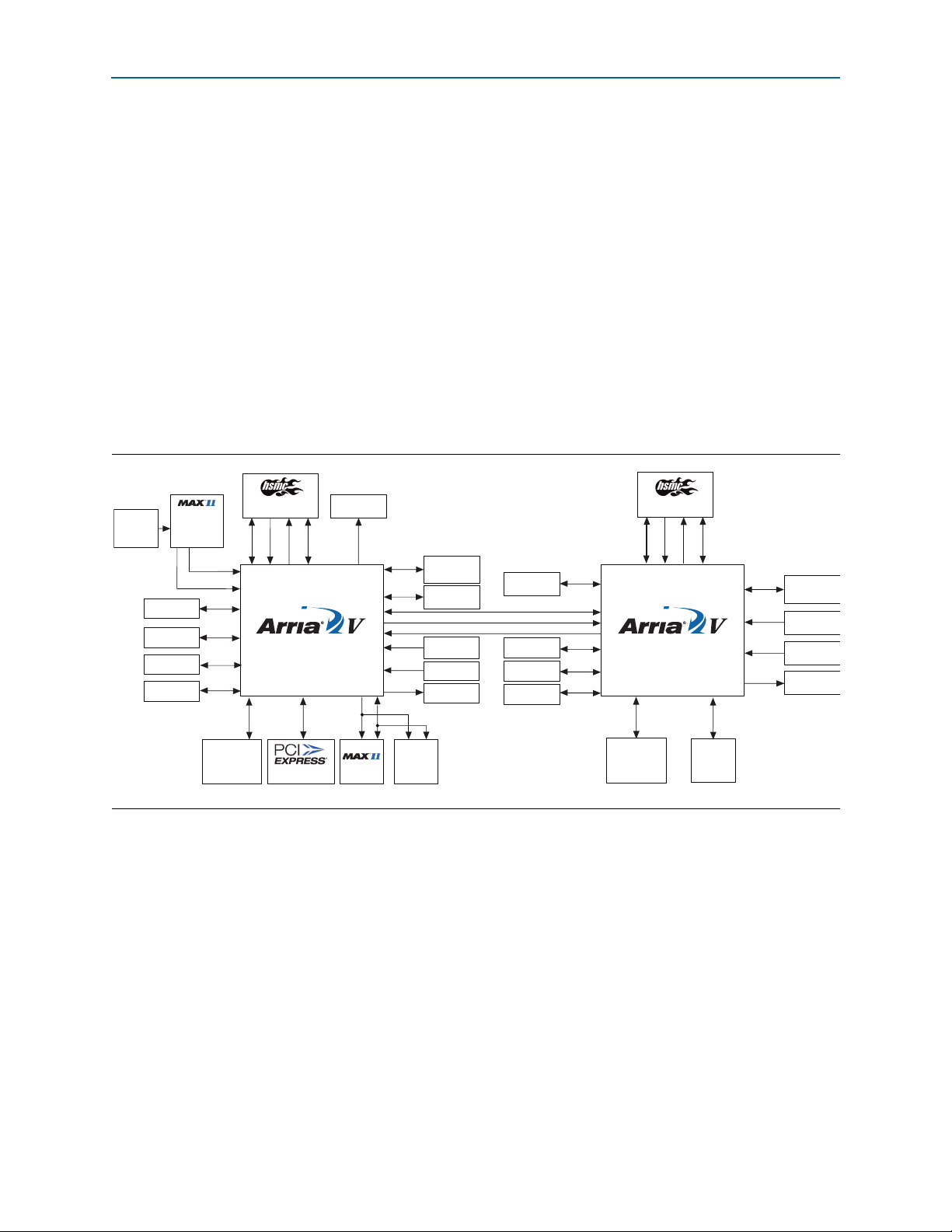

Dual FPGA

The development board includes two Arria V GT FPGAs that connect to other

components on the board to provide a better transceiver and bandwidth design

solution.

FPGA 1

The first FPGA device (FPGA 1) connects to the following components:

■ Communication ports

■ One PCI Express x8 edge connector

■ One universal HSMC expansion port (port A)

■ One USB 2.0 connector

■ One gigabit Ethernet port

■ Chip-to-Chip (C2C) bridge with 29 LVDS inputs and 29 LVDS outputs, and x8

transceivers

■ Two small form factor pluggable plus (SFP+) channels

■ One SMA 10 Gbps transceiver channel

■ Three Bull’s Eye 10 Gbps transceiver channels

■ Memory

■ 1152-Mbyte (MB) DDR3 SDRAM with a 72-bit data bus

■ 72-Mbit (Mb) QDRII+ SRAM

■ 1-Gbit (Gb) synchronous flash with a 16-bit data bus

December 2014 Altera Corporation Arria V GT FPGA Development Board

Reference Manual

Page 8

1–4 Chapter 1: Overview

Board Component Blocks

■ General user I/O

■ LEDs and displays

■ Eight dual color user LEDs

■ Two-line character LCD display

■ Three configuration select LEDs

■ One configuration done LED

■ Two HSMC interface transmit/receive (TX/RX) LEDs

■ Three PCI Express LEDs

■ Five Ethernet LEDs

■ Push buttons

■ One CPU reset push button

■ One Max II CPLD EPM2210 System Controller configuration reset

push button

■ One load image push button (to program the FPGA from flash memory)

■ One image select push button (select an image to load from flash memory)

■ Three general user push buttons

■ Eight user control DIP switches

FPGA 2

The second FPGA device (FPGA 2) connects to the following components:

■ Communication ports

■ One universal HSMC expansion port (port B)

■ One FMC port

■ C2C bridge with 29 LVDS inputs and 29 LVDS outputs, and x8 transceivers

■ One serial digital interface (SDI) channel

■ One SMA 10 Gbps transceiver channel

■ One Bull's Eye 6 Gbps transceiver channel

■ One Bull’s Eye 10 Gbps transceiver channel

■ Memory

■ 1024-MB DDR3 SDRAM with a 64-bit data bus (soft controller)

■ 512-MB DDR3 SDRAM with a 32-bit data bus (hard IP controller)

Arria V GT FPGA Development Board December 2014 Altera Corporation

Reference Manual

Page 9

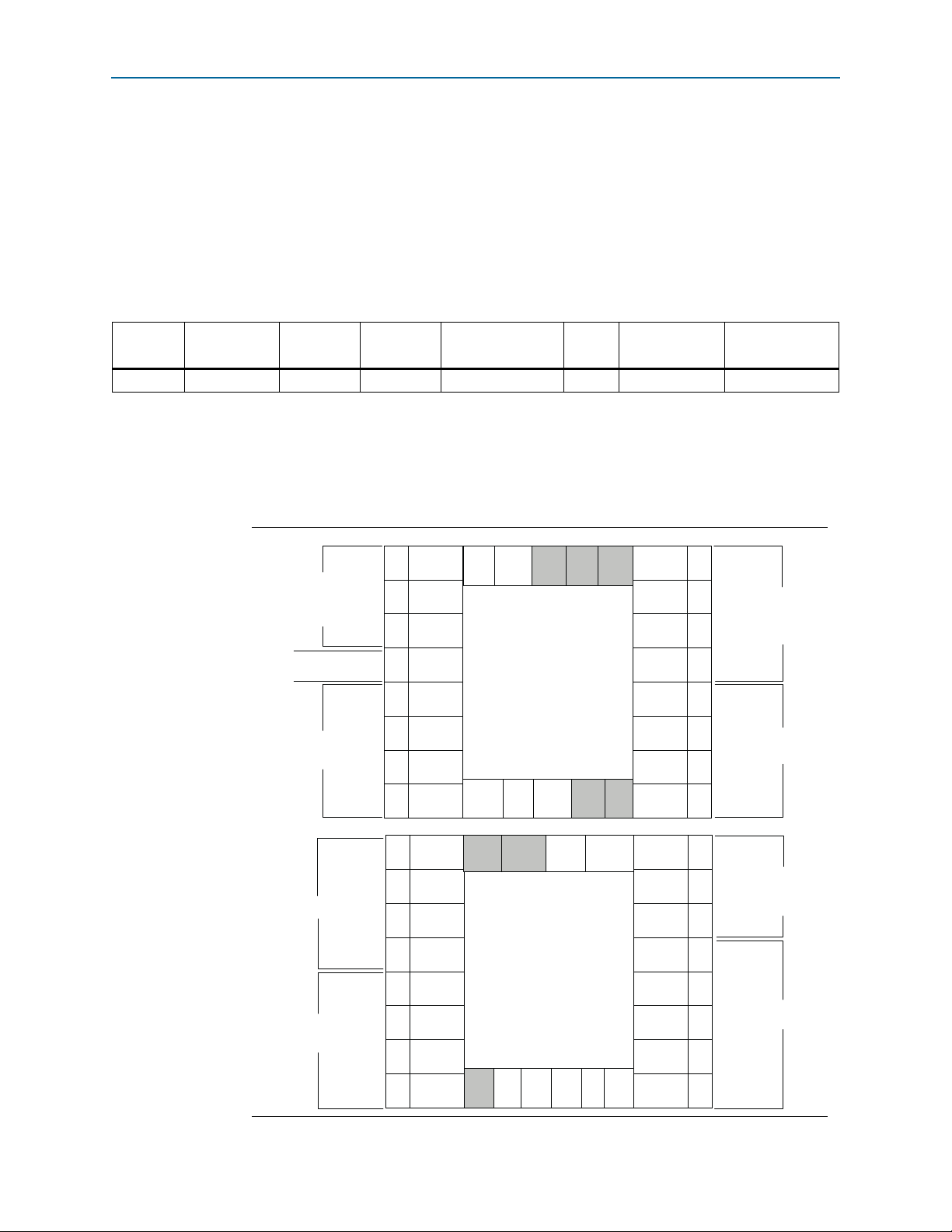

Chapter 1: Overview 1–5

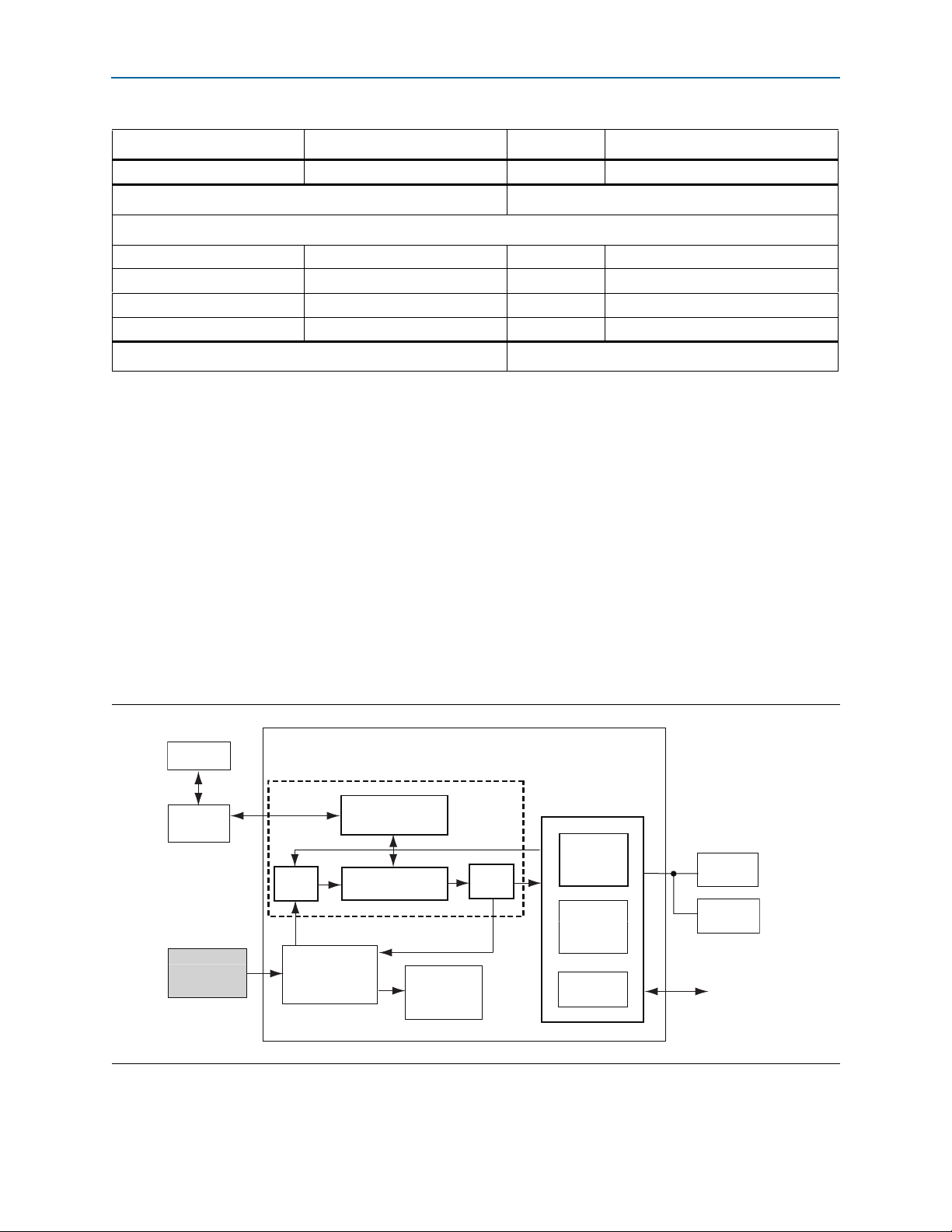

Port B

Port A

1152-MB

DDR3

2x16 LCD

Push buttons

8 bi-color LEDs

CPLD

1-Gb

Flash

FMC

x8 Edge

SMAs

10G

Gigabit Ethernet

PHY (RGMII)

On-Board

USB-Blaster II

and

USB Interface

Mini-USB

2.0

XCVR x1

Bull’s Eye

10G

XCVR x3

SDI

TX/RX

XCVR x1

Bull’s Eye

10G

Bull’s Eye

6G

XCVR x1

XCVR x1

SMAs

10G

XCVR x1

SFP+

XCVR x2

x16

x72

DDR3

(x64)

x32 Hard IP

(x64 Soft IP)

72-Mb

QDRII+

x36

x11

x8

x4

ADDR x16

XCVR x8 Chip-to Chip

LVDS x29 Chip-to Chip + 1 Clock Input

LVDS x29 Chip-to Chip + 1 Clock Input

XVCR x8

XVCR x10

x80

CLKIN x3

CLKOUT x3

XCVR x4

x80

CLKIN x3

CLKOUT x3

XCVR x8

JTAG Chain

USB Interface x19

Programmable

Oscillators +

50 M, 100 M

Programmable

Oscillators +

50 M, 100 M

5AGTFD7K3F40

FPGA 1

5AGTFD7K3F40

FPGA 2

x16

Push Buttons

DIP Switches

DIP Switches

8 bi-color LEDs

x8

x4

x16

Development Board Block Diagram

■ General user I/O

■ LEDs and displays

■ Eight dual color user LEDs

■ Two HSMC interface transmit/receive (TX/RX) LEDs

■ Push buttons

■ One CPU reset push button

■ Three general user push buttons

■ Eight user control DIP switches

Development Board Block Diagram

Figure 1–1 shows a block diagram of the Arria V GT FPGA development board.

Figure 1–1. Arria V GT FPGA Development Board Block Diagram

Handling the Board

When handling the board, it is important to observe the following static discharge

precaution:

December 2014 Altera Corporation Arria V GT FPGA Development Board

anti-static handling precautions when touching the board.

c Without proper anti-static handling, the board can be damaged. Therefore, use

Reference Manual

Page 10

1–6 Chapter 1: Overview

Handling the Board

Arria V GT FPGA Development Board December 2014 Altera Corporation

Reference Manual

Page 11

Introduction

1 A complete set of schematics, a physical layout database, and GERBER files for the

f For information about powering up the board and installing the demonstration

2. Board Components

This chapter introduces the major components on the Arria V GT FPGA development

board. Figure 2–1 illustrates the component locations and Tab le 2– 1 provides a brief

description of all component features of the board.

development board reside in the Arria V GT FPGA development kit documents

directory.

software, refer to the Arria V GT FPGA Development Kit User Guide.

This chapter consists of the following sections:

■ “Board Overview”

■ “Featured Device: Arria V GT FPGA” on page 2–6

■ “MAX II CPLD EPM2210 System Controller” on page 2–8

■ “Configuration, Status, and Setup Elements” on page 2–14

■ “Clock Circuitry” on page 2–22

■ “General User Input/Output” on page 2–27

■ “Components and Interfaces” on page 2–33

■ “Memory” on page 2–54

■ “Power Supply” on page 2–68

■ “Statement of China-RoHS Compliance” on page 2–72

December 2014 Altera Corporation Arria V GT FPGA Development Board

Reference Manual

Page 12

2–2 Chapter 2: Board Components

Arria V FPGA

(U16)

Arria V FPGA (U13)

FMC Bank B Voltage Select (J11)

FMC VCCPD

B4 Select (J5)

FMC Bank B Power Source Select (J28)

MAX II CPLD

EPM2210 System

Controller (U2)

PCI

Express Edge

Connector

(J14)

JTAG Connector

(J1)

Embedded

USB-Blaster

Circuitry (J7)

Gigabit Ethernet

Port (J8)

SFP+ Port (J10)

SFP+ Port (J15)

[Available in

Arria V GT

Development

Board Only]

DC Input

Jack (J6)

Character

LCD (J29)

Board

Power Switch

(SW1)

ATX Power

Connector

(J4)

FMC

Connector

(J9)

CPU Reset

Push

Button (S4)

DDR3A

(U7, U11, U18,

U21, U28)

DDR3C

(U19, U22)

DDR3B (U6, U12)

Tx/Rx

Transceivers

(J19-J22)

Tx/Rx

Transceivers

(J12, J13,

J24, J25)

Fan Power

(J23)

Fan Power

(J14)

SDI Video

Por t

(J26, J27)

Bullseye

SMA

Connector

(J16)

Clock Input

SMA

Connector

(J10, J11)

Configuration LEDs (D12-D17)

Configuration

Push Buttons

(S1-S3)

Flash

Memory (U4)

User LEDs (D18-D25)

User Push

Buttons

(S5-S7)

User LEDs (D26-D33)

User Push Buttons (S9-S11)

CPU Reset

Push Button (S8)

User DIP Switch (SW3)

User DIP

Switch (SW2)

HSMC

Port A (J2)

HSMC

Port B (J3)

Board Overview

Board Overview

This section provides an overview of the Arria V GT FPGA development board,

including an annotated board image and component descriptions. Figure 2–1 shows

an overview of the available components.

Figure 2–1. Overview of the Arria V GT FPGA Development Board Features

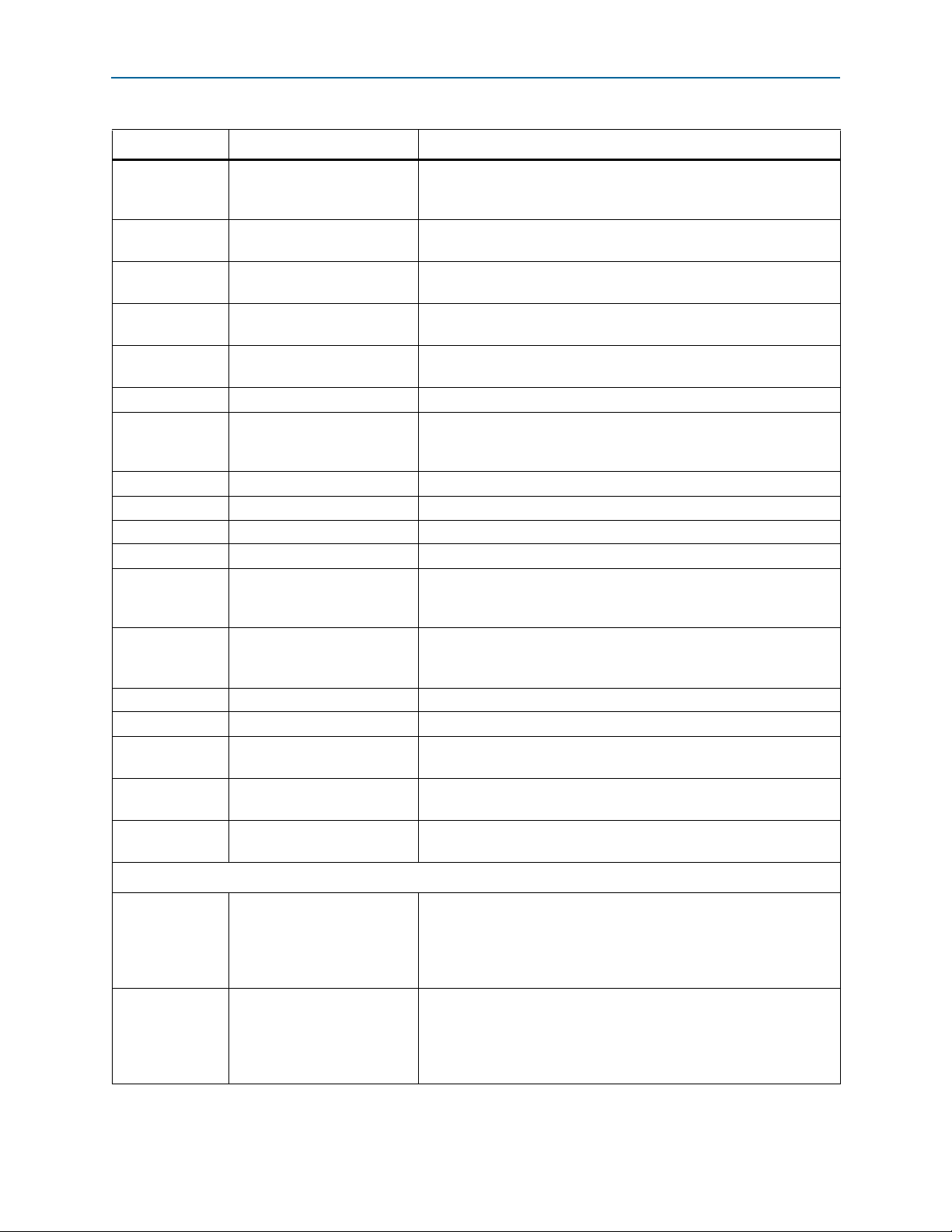

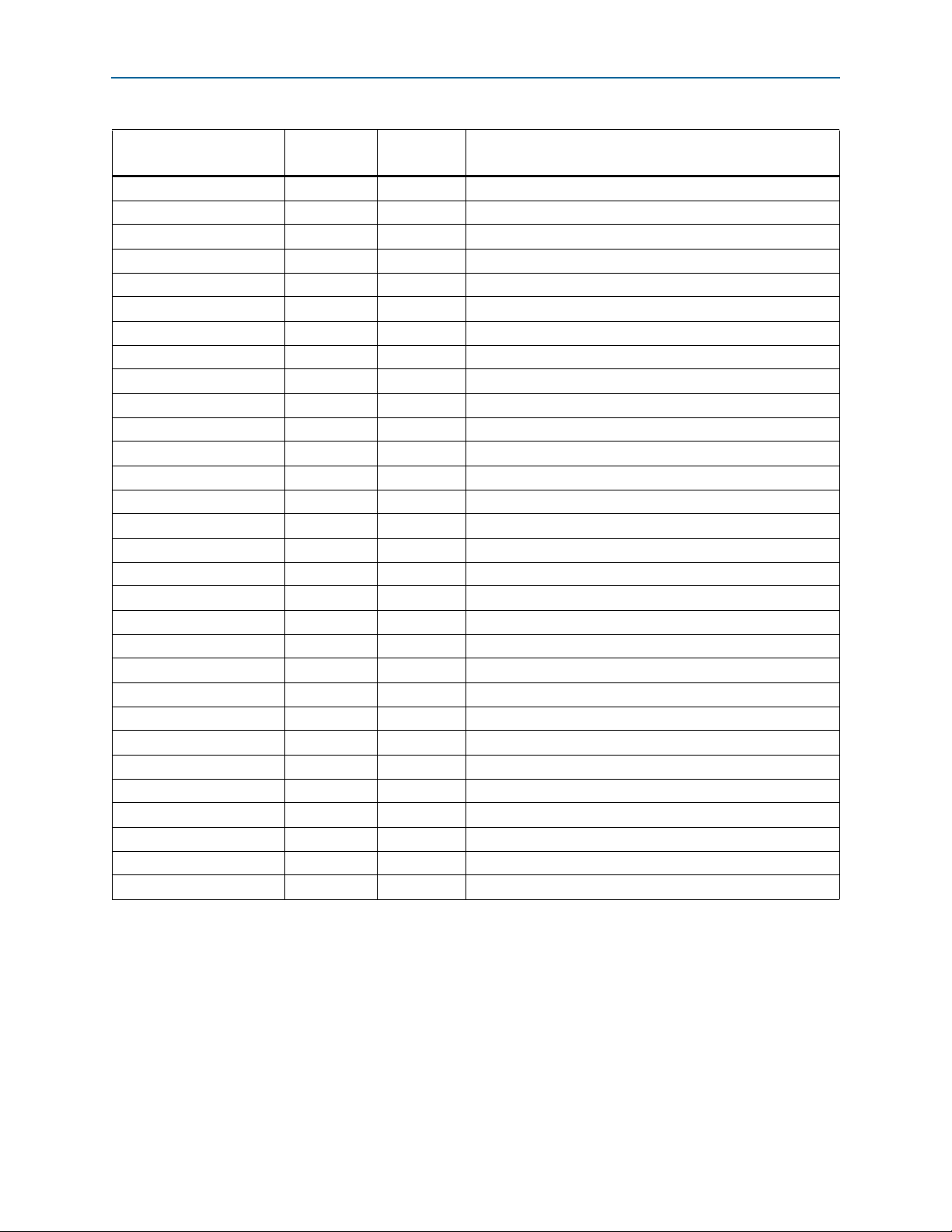

Tab le 2– 1 describes the components and lists their corresponding board references.

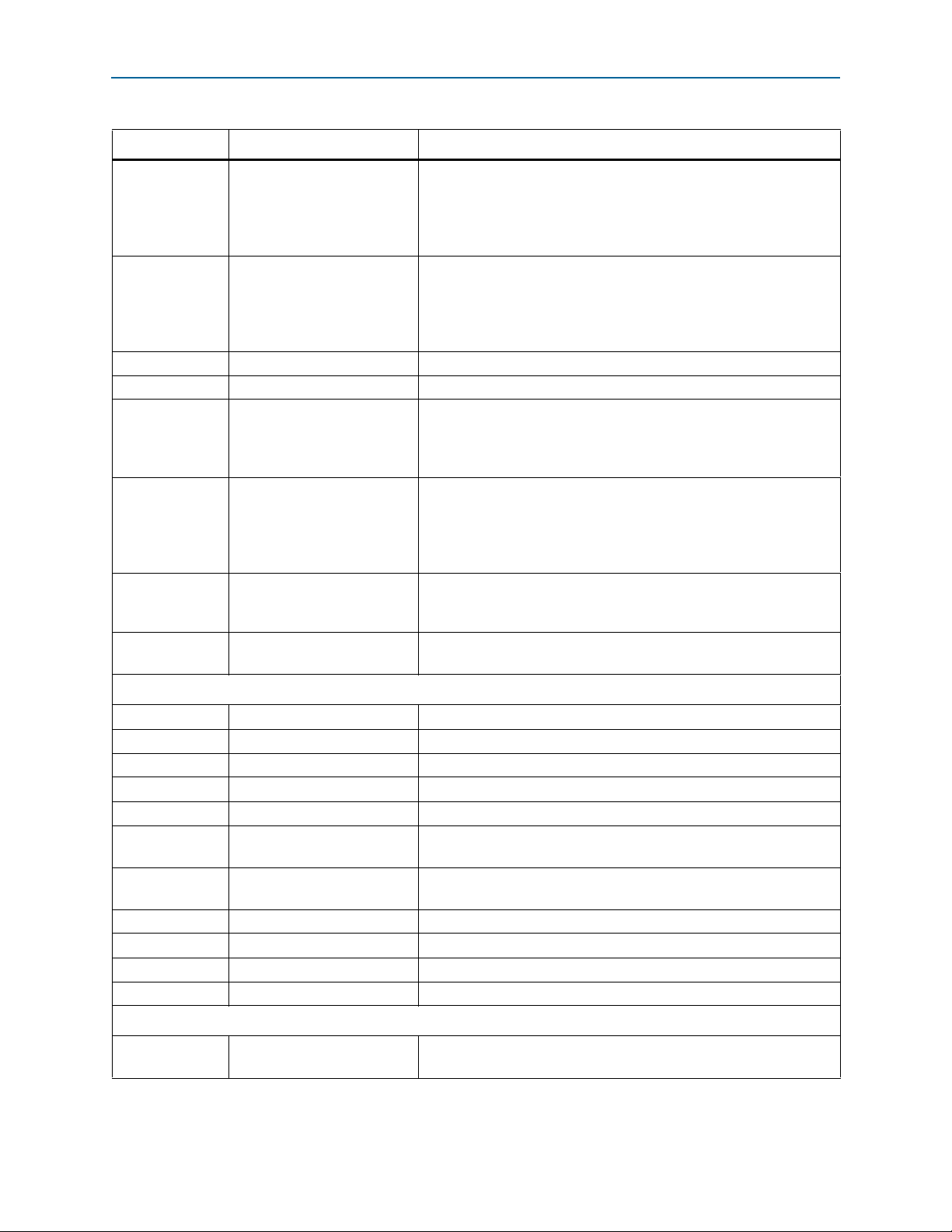

Table 2–1. Arria V GT FPGA Development Board Components (Part 1 of 4)

Board Reference Type Description

Featured Devices

U13, U16 FPGA Two Arria V GT FPGA, 5AGTFD7K3F40I3N, 1517-pin FBGA.

U2 CPLD MAX II CPLD, EPM2210GF324, 324-pin BGA.

Configuration, Status, and Setup Elements

J1 JTAG connector

J7 On-Board USB-Blaster II Mini-USB 2.0 connector for programming and debugging the FPGA.

SW5 Board settings DIP switch

SW6 JTAG chain DIP switch

Arria V GT FPGA Development Board December 2014 Altera Corporation

Reference Manual

Disables the on-board USB-Blaster II (for use with external

USB-Blasters).

Controls the MAX

as clock enable, SMA clock input control, and which image to load

from flash memory at power-up. This switch is located on the bottom

of the board.

II CPLD EPM2210 System Controller functions such

Enables and disables devices in the JTAG chain. This switch is located

on the bottom of the board.

Page 13

Chapter 2: Board Components 2–3

Board Overview

Table 2–1. Arria V GT FPGA Development Board Components (Part 2 of 4)

Board Reference Type Description

SW7 PCI Express DIP switch

Controls the PCI Express lane width by connecting

together on the PCI Express edge connector. This switch is located on

prsnt

pins

the bottom of the board.

SW8

SW4

FPGA 1 mode select DIP

switch

FPGA 2 mode select DIP

switch

S2 Image select push button

S3

Program configuration push

button

Sets the Arria V MSEL[4,2,1] pins. This switch is located on the

bottom of the board.

Sets the Arria V MSEL[4,2,1] pins. This switch is located on the

bottom of the board.

Toggles the configuration LEDs which selects the program image that

loads from flash memory to the FPGA.

Configures the FPGA from flash memory image based on the program

LEDs.

D1 Power LED Illuminates when 5.0-V power is present.

Indicate the transmit or receive activity of the JTAG chain. The Tx and

D2, D3 JTAG Tx/Rx LEDs

Rx LEDs blink when the link is in use and active. The LEDs are off when

not in use and on when in use or idle.

D4, D5 HSMC port A LEDs You can configure these LEDs to indicate transmit or receive activity.

D6 HSMC port A present LED Illuminates when a daughtercard is plugged into the HSMC port A.

D7, D8 HSMC port B LEDs You can configure these LEDs to indicate transmit or receive activity.

D9 HSMC port B present LED Illuminates when a daughtercard is plugged into the HSMC port B.

Indicate the transmit or receive activity of the System Console USB

D10, D11 System Console Tx/Rx LEDs

interface. The Tx and Rx LEDs blink when the link is in use and active.

The LEDs are off when not in use and on when in use or idle.

Illuminates to show the LED sequence that determines which flash

D12, D13, D14 Configuration LEDs

memory image loads to the FPGA when you press the

PGM1_SEL

push

button.

D15 Error LED Illuminates when the FPGA configuration from flash memory fails.

D16 Configuration done LED Illuminates when the FPGA is configured.

D17 Load LED

D36, D37, D38,

D39, D40

Ethernet LEDs Shows the connection speed as well as transmit or receive activity.

D42, D43, D44 PCI Express link LEDs

Illuminates when the MAX II CPLD EPM2210 System Controller is

actively configuring the FPGA.

You can configure these LEDs to display the PCI Express link width

(x1, x4, x8).

Clock Circuitry

Programmable oscillator with default frequencies of CLK0=125 MHz,

2

C address

U48

Si5338 programmable

oscillator

CLK1=100 MHz, CLK2=625 MHz, CLK3=125 MHz at I

71 HEX. The frequency is programmable using the clock GUI with the

default MAX II CPLD EPM2210 System Controller design programmed

into the MAX II EPM2210.

Programmable oscillator with default frequencies of CLK0=625 MHz,

2

C address

U53

Si5338 programmable

oscillator

CLK1=156.25 MHz, CLK2=125 MHz, CLK3=125 MHz at I

70 HEX. The frequency is programmable using the clock GUI with the

default MAX II CPLD EPM2210 System Controller design programmed

into the MAX II EPM2210.

December 2014 Altera Corporation Arria V GT FPGA Development Board

Reference Manual

Page 14

2–4 Chapter 2: Board Components

Board Overview

Table 2–1. Arria V GT FPGA Development Board Components (Part 3 of 4)

Board Reference Type Description

Programmable oscillator with default frequencies of CLK0=125 MHz,

2

C address

U52

Si5338 programmable

oscillator

CLK1=100 MHz, CLK2=156.25 MHz, CLK3=125 MHz at I

73 HEX. The frequency is programmable using the clock GUI with the

default MAX II CPLD EPM2210 System Controller design programmed

into the MAX II EPM2210.

Programmable oscillator with default frequencies of CLK0=625 MHz,

2

C address

U34

Si5338 programmable

oscillator

CLK1=100 MHz, CLK2=625 MHz, CLK3=125 MHz at I

72 HEX. The frequency is programmable using the clock GUI with the

default MAX II CPLD EPM2210 System Controller design programmed

into the MAX II EPM2210.

X1 125 MHz oscillator 125.000 MHz crystal oscillator for general purpose logic to FPGA 1.

X4 125 MHz oscillator 125.000 MHz crystal oscillator for general purpose logic to FPGA 2.

Programmable oscillator for SDI or REFCLK0RP/N with default

2

X2

Si571 programmable

Oscillator (148.5 MHz default)

frequencies at I

using the clock GUI with the default MAX II EPM2210 System

C address 55 HEX. The frequency is programmable

Controller design programmed into the MAX II EPM2210.

Programmable oscillator with a default frequency of 100.00 MHz. The

X7, or J17 and

J18 to U56 buffer

Programmable oscillator

(100 MHz default)

frequency is programmable using the clock GUI with the default MAX II

CPLD EPM2210 System Controller design programmed into the MAX

II EPM2210. Multiplex with

CLKIN_SMA_P/N

based on

CLK_SEL

switch value.

X6 to U51 1:3

zero delay clock

50 MHz oscillator

buffer

J17, J18 Clock input SMAs

50.000 MHz crystal oscillator for general purpose logic. Three outputs

connect to the FPGA 1, FPGA 2, and MAX II devices.

Drive LVPECL-compatible clock inputs into the clock multiplexer buffer

(U56).

General User Input/Output

SW2 FPGA 1 user DIP switch Octal user DIP switches. When the switch is ON, a logic 0 is selected.

SW3 FPGA 2 user DIP switch Octal user DIP switches. When the switch is ON, a logic 0 is selected.

S1 MAX II reset push button Resets the MAX II CPLD EPM2210 System Controller.

S4 FPGA 1 CPU reset push button Resets the FPGA 1 logic.

S8 FPGA 2 CPU reset push button Resets the FPGA 2 logic.

S5–S7

S9–S11

FPGA 1 general user push

buttons

FPGA 2 general user push

buttons

Three user push buttons. Driven low when pressed.

Three user push buttons. Driven low when pressed.

D18–D25 FPGA 1 user LEDs Eight bi-color user LEDs. Illuminates when driven low.

D26–D33 FPGA 2 user LEDs Eight bi-color user LEDs. Illuminates when driven low.

D35 FPGA 1 LED LED indicator for FPGA 1.

D32 FPGA 2 LED LED indicator for FPGA 2.

Memory Devices

U4 Flash x16 memory

Synchronous burst mode flash device that provides a 16-bit 125-MB

non-volatile memory port.

Arria V GT FPGA Development Board December 2014 Altera Corporation

Reference Manual

Page 15

Chapter 2: Board Components 2–5

Board Overview

Table 2–1. Arria V GT FPGA Development Board Components (Part 4 of 4)

Board Reference Type Description

U8 QDRII+ memory

U7, U11, U18,

U21, U28

DDR3A memory

9-MB QDRII+ SRAM with a 36-bit data bus. The device has a separate

36-bit read and 36-bit write port with DDR signalling at up to 400 MHz.

DDR3 SDRAM interface on FPGA 1. This 1152-MB DDR3 x72-bit data

bus consists of four x16 devices and one x8 device with a single

address or command bus.

DDR3 SDRAM interface on FPGA 2. There are two interface options:

■ Option 1: 512-MB interface with a 32-bit data bus. This DDR3

U6, U12, U19,

U22

DDR3B/C memory

x32-bit data bus consists of two x16 devices with a single shared

address.

■ Option 2: 1024-MB interface with a 64-bit data bus. This DDR3

x64-bit data bus consists of four x16 devices with a single shared

address.

Communication Ports

J30 PCI Express edge connector

J2 HSMC port A

J3 HSMC port B

J7 Mini-USB type-AB connector

Gold-plated edge fingers connector for up to ×8 signaling in Gen1 and

x4 Gen2 modes.

Provides four transceiver channels and 80 CMOS or 17 LVDS channels

per the HSMC specification.

Provides four transceiver channels and 80 CMOS or 17 LVDS channels

per the HSMC specification.

USB interface for programming the FPGA through on-board

USB-Blaster II JTAG via a type-AB Mini-USB cable.

RJ-45 connector which provides a 10/100/1000 Ethernet connection

J8 Gigabit Ethernet

via a Marvell 88E1111 PHY and the FPGA-based Altera Triple Speed

Ethernet MegaCore function in RGMII mode.

Display Ports

J29 Character LCD connector

Connector which interfaces to the provided 16 character × 2 line LCD

module along with two standoffs at MTH7 and MTH8.

Power Supply

J6 DC input jack

Accepts a 19-V DC power supply. Do not use this input jack while the

board is plugged into a PCI Express slot.

J4 ATX power connector PCI Express auxiliary power source option.

J30 PCI Express edge connector

SW1 Power switch

Interfaces to a PCI Express root port such as an appropriate PC

motherboard.

Switch to power on or off the board when power is supplied from the

DC input jack.

December 2014 Altera Corporation Arria V GT FPGA Development Board

Reference Manual

Page 16

2–6 Chapter 2: Board Components

Featured Device: Arria V GT FPGA

Featured Device: Arria V GT FPGA

The Arria V GT FPGA development board features two Arria V GT FPGA

5AGTFD7K3F40I3N device (U13 and U16) in a 1517-pin FBGA package.

f For more information about Arria V device family, refer to the Arria V Device

Handbook.

Tab le 2– 2 describes the features of the Arria V GT FPGA 5AGTFD7K3F40I3N device.

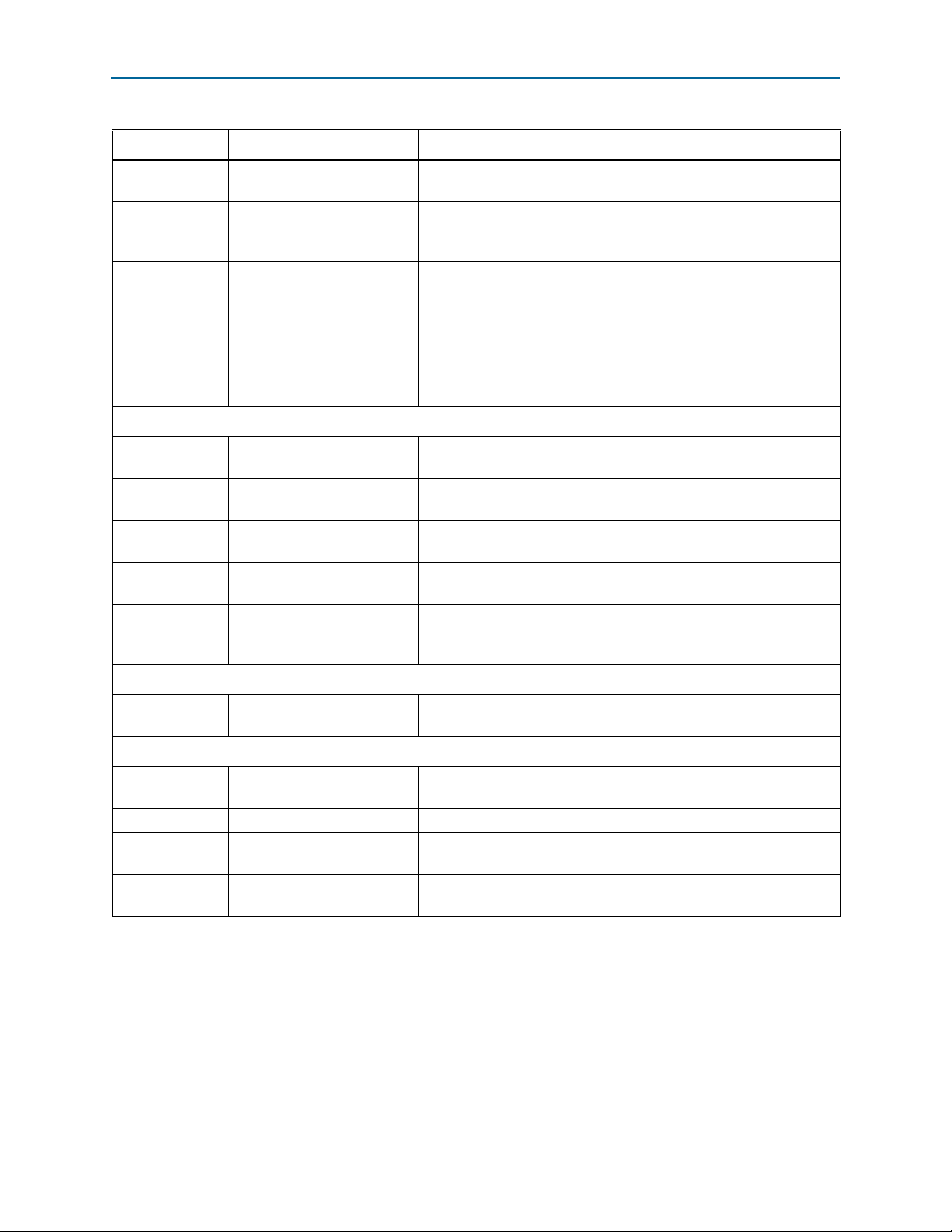

Table 2–2. Arria V GT FPGA Features

ALMs

Equivalent

LEs

M10K RAM

Blocks

Total RAM

Kbits

18-bit × 18-bit

Multipliers

PLLs Transceivers Package Type

190,240 504,000 24,140 27,046 2,312 16 36 1517-pin FBGA

I/O Resources

Figure 2–2 illustrates the bank organization and I/O count for the Arria V GT FPGA

5AGTFD7K3F40I3N device in the 1517-pin FBGA package.

Figure 2–2. Arria V GT FPGA Device I/O Bank Diagrams

A1

2.5 V

Chip-to-Chip

32

48

48

48

32

48

LCD

USER

1.5 V

DDR3 x72

USB

ENET

PCIe

SFP+

HSMA

SFP+

USER

QDRII+

Flash/MAX

2.5 V

2.5 V

1.8 V

AW1

HSMA

Bank 4A48

Bank 4B48

Bank 4C32

Bank 4D48

Bank 3D48

Bank 3C48

Bank 3B32

Bank 3A48

C2C

x8

PCIe

x8

SMA

HSMA

(6G)

x4

GXB_R

XCVRs

5AGTFD7K3F40I3N

Device 1

GXB_L

XCVRs

SFP+

SMA

x1

(6G)

x8

SMA

(10G)

SMA

(10G)

SFP+

x1

Bank 7A4848

Bank 7B

Bank 7C

Bank 7D

Bank 8D

Bank 8C

Bank 8B

Bank 8A

DDR3 x72

Chip-to-Chip

LCD

1.5 V

2.5 V

48

Bank 8A

32

Bank 8B

48

Bank 8C

48

Bank 8D

48

Bank 7D

32

Bank 7C

48

Bank 7B

Bank 7A

48

A1

SMA

(10G)

5AGTFD7K3F40I3N

FMC

FMC

x4

x6

BP

x4

Device 2

SMA

(6G)

GXB_L

XCVRs

GXB_R

XCVRs

BP

x4

SMA

(10G)

SDI

x1

C2C

x8

HSMB

x4

Bank 3A 48

Bank 3B 32

Bank 3C 48

Bank 3D 48

Bank 4D 48

Bank 4C 32

Bank 4B 48

Bank 4A 48

2.5 V

HSMB

SDI

USER

2.5 V

FMC

Arria V GT FPGA Development Board December 2014 Altera Corporation

Reference Manual

Page 17

Chapter 2: Board Components 2–7

Featured Device: Arria V GT FPGA

Tab le 2– 3 lists the Arria V GT FPGA 1 pin count and usage by function on the

development board. Clocks are listed under special pins as it uses dedicated I/O pins.

Table 2–3. Arria V GT FPGA 1 Pin Count and Usage

Function I/O Standard I/O Count Special Pins

DDR3 ×72 interface 1.5-V SSTL 125 1 differential ×9 differential DQS

QDRII+ ×36 interface 1.8-V HSTL 103 1 differential ×36 differential DQS

MAX II System Controller 1.8-V CMOS 8 —

Flash 1.8-V CMOS 49 —

PCI Express 2.5-V CMOS 10 1 reference clock

HSMC port A 2.5-V CMOS + LVDS 84 1 reference clock

Gigabit Ethernet 2.5-V CMOS + LVDS 16 —

On-Board USB-Blaster II 1.5-V/2.5-V CMOS 19 —

SFP+ 2.5-V CMOS 16 2 reference clocks

Chip-to-chip bridge 2.5-V 120 2 reference clocks

Buttons 2.5-V CMOS 3 —

Switches 2.5-V CMOS 4 —

LCD 2.5-V CMOS 11 —

LEDs 2.5-V CMOS 16 —

Clocks or Oscillators 1.8-V CMOS + LVDS 10 5 differential clocks, 1 single-ended

Total I/O Used:

625

Transceivers

SMA or Bull’s Eye — 16 —

HSMC port A — 32 —

PCI Express — 32 —

Chip-to-chip bridge — 32 —

SFP+ — 8 —

Total Transceiver Used:

120

Tab le 2– 4 lists the Arria V GT FPGA 2 pin count and usage by function on the

development board. Clocks are listed under special pins as it uses dedicated I/O pins.

Table 2–4. Arria V GT FPGA 2 Pin Count and Usage (Part 1 of 2)

Function I/O Standard I/O Count Special Pins

DDR3 ×64 device 1.5-V SSTL 156 1 differential ×9 differential DQS

HSMC port B 2.5-V CMOS + LVDS 84 1 reference clock

FMC 2.5-V 178 1 reference clock

SDI 2.5-V CMOS 8 1 reference clock

Chip-to-chip bridge 2.5-V 120 1 reference clock

Buttons 2.5-V CMOS 4 —

Switches 2.5-V CMOS 8 —

LEDs 2.5-V CMOS 16 —

December 2014 Altera Corporation Arria V GT FPGA Development Board

Reference Manual

Page 18

2–8 Chapter 2: Board Components

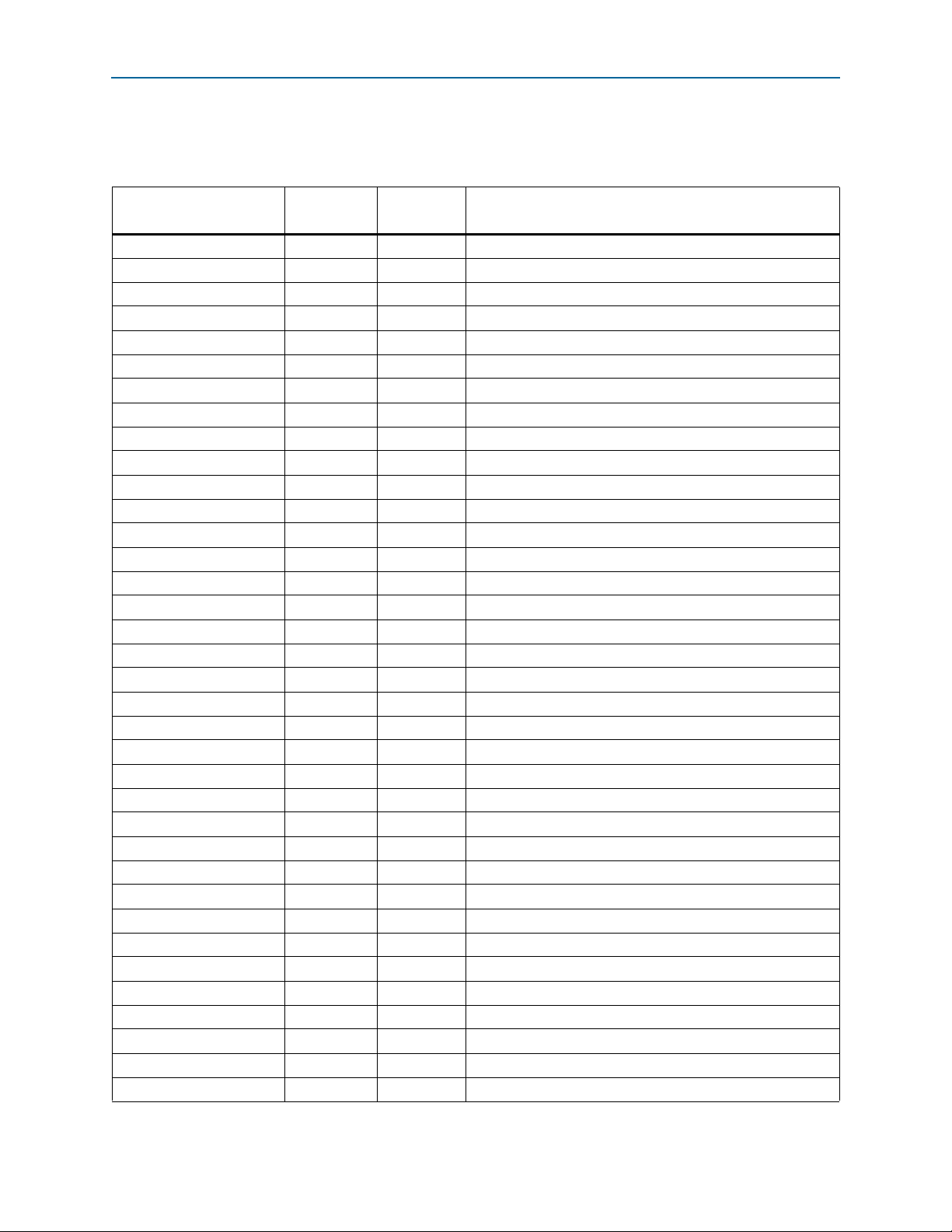

Information

Register

Embedded

Blaster

MAX II CPLD

Power

Calculations

SLD-HUB

PFL

Power

Measurement

Results

Virtual-JTAG

PC

Arria V

FPGA

LTC2418

Controller

Flash

Decoder

Encoder

GPIO

JTAG Control

Control

Register

MAX II CPLD EPM2210 System Controller

Table 2–4. Arria V GT FPGA 2 Pin Count and Usage (Part 2 of 2)

Function I/O Standard I/O Count Special Pins

Clocks or Oscillators 1.8-V CMOS + LVDS 10 5 differential clocks, 1 single-ended

Total I/O Used:

584

Transceivers

SMAs or Bull's Eye — 12 —

HSMC port B — 16 —

FMC — 40 —

Chip-to-chip bridge — 32 —

Total Transceivers:

116

MAX II CPLD EPM2210 System Controller

The board utilizes the EPM2210 System Controller, an Altera MAX II CPLD, for the

following purposes:

■ FPGA configuration from flash

■ Power consumption monitoring

■ Virtual JTAG interface for PC-based GUI

■ Control registers for clocks

■ Control registers for remote system update

Figure 2–3 illustrates the MAX II CPLD EPM2210 System Controller's functionality

and external circuit connections as a block diagram.

Figure 2–3. MAX II CPLD EPM2210 System Controller Block Diagram

Arria V GT FPGA Development Board December 2014 Altera Corporation

Reference Manual

Page 19

Chapter 2: Board Components 2–9

MAX II CPLD EPM2210 System Controller

Tab le 2– 5 lists the I/O signals present on the MAX II CPLD EPM2210 System

Controller. The signal names and functions are relative to the MAX

Table 2–5. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 1 of 5)

Schematic Signal Name

CLK125A_EN

CLK125B_EN

CLK50_EN

CLK_CONFIG

CLK_ENABLE

CLK_SEL

CLKIN_MAX_50

CLOCK_SCL

CLOCK_SDA

CPU1_RESETN

CPU2_RESETN

DEVICE1_LED

DEVICE2_LED

EXTRA_SIG0

EXTRA_SIG1

EXTRA_SIG2

FACTORY_USER1

FACTORY_USER2

FACTORY_REQUEST

FACTORY_STATUS

FLASH_ACCESSN

FLASH_ADVN

FLASH_CEN

FLASH_CLK

FLASH_OEN

FLASH_RDYBSYN

FLASH_RESETN

FLASH_WEN

FM_A0

FM_A1

FM_A2

FM_A3

FM_A4

FM_A5

FM_A6

FM_A7

MAX II CPLD

Pin Number

I/O Standard Description

B13 2.5-V 125 MHz oscillator enable

D7 2.5-V 125 MHz oscillator enable

D11 2.5-V 50 MHz oscillator enable

K6 2.5-V 100 MHz configuration clock input

B5 2.5-V DIP switch for clock oscillator enable

E7 2.5-V DIP switch for clock select—SMA or oscillator

K13 2.5-V 50 MHz clock input

C14 2.5-V Programmable oscillator I2C clock

L4 2.5-V Programmable oscillator I2C data

B8 2.5-V FPGA 1 reset push button

E6 2.5-V FPGA 2 reset push button

D13 2.5-V FPGA 1 configuration done LED

C15 2.5-V FPGA 2 configuration done LED

B10 2.5-V Reserved for future use.

F16 1.8-V Reserved for future use.

J16 1.8-V Reserved for future use.

A5 2.5-V Load factory or user design at power-up

C4 2.5-V Load factory or user design at power-up

B9 2.5-V On-Board USB-Blaster II request to send FACTORY command

F10 2.5-V On-Board USB-Blaster II FACTORY command status

B12 1.8-V FM bus flash memory access indication

G15 1.8-V FM bus flash memory address valid

E16 1.8-V FM bus flash memory chip enable

E17 1.8-V FM bus flash memory clock

F14 1.8-V FM bus flash memory output enable

D18 1.8-V FM bus flash memory ready

F13 1.8-V FM bus flash memory reset

D17 1.8-V FM bus flash memory write enable

T17 1.8-V FM bus address

R15 1.8-V FM bus address

T16 1.8-V FM bus address

F15 1.8-V FM bus address

R16 1.8-V FM bus address

P15 1.8-V FM bus address

R17 1.8-V FM bus address

P14 1.8-V FM bus address

II device (U2).

December 2014 Altera Corporation Arria V GT FPGA Development Board

Reference Manual

Page 20

2–10 Chapter 2: Board Components

MAX II CPLD EPM2210 System Controller

Table 2–5. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 2 of 5)

Schematic Signal Name

FM_A8

FM_A9

FM_A10

FM_A11

FM_A12

FM_A13

FM_A14

FM_A15

FM_A16

FM_A17

FM_A18

FM_A19

FM_A20

FM_A21

FM_A22

FM_A23

FM_A24

FM_A25

FM_A26

FM_D0

FM_D1

FM_D2

FM_D3

FM_D4

FM_D5

FM_D6

FM_D7

FM_D8

FM_D9

FM_D10

FM_D11

FM_D12

FM_D13

FM_D14

FM_D15

FMC_C2M_PG

FMC_M2C_PG

FMC_PRSNT

FMC_SCL

MAX II CPLD

Pin Number

I/O Standard Description

R18 1.8-V FM bus address

N15 1.8-V FM bus address

P16 1.8-V FM bus address

N14 1.8-V FM bus address

P18 1.8-V FM bus address

M15 1.8-V FM bus address

N16 1.8-V FM bus address

P17 1.8-V FM bus address

N13 1.8-V FM bus address

M14 1.8-V FM bus address

N17 1.8-V FM bus address

M13 1.8-V FM bus address

N18 1.8-V FM bus address

M12 1.8-V FM bus address

M16 1.8-V FM bus address

K14 1.8-V FM bus address

K18 1.8-V FM bus address

K15 1.8-V FM bus address

H17 1.8-V FM bus address

L16 1.8-V FM data bus

M18 1.8-V FM data bus

L14 1.8-V FM data bus

L17 1.8-V FM data bus

L13 1.8-V FM data bus

L18 1.8-V FM data bus

M17 1.8-V FM data bus

L15 1.8-V FM data bus

K16 1.8-V FM data bus

K17 1.8-V FM data bus

D15 1.8-V FM data bus

C17 1.8-V FM data bus

E15 1.8-V FM data bus

C16 1.8-V FM data bus

D16 1.8-V FM data bus

E14 1.8-V FM data bus

P6 2.5-V FMC card to module power good

T4 2.5-V FMC module to card power good

U3 2.5-V FMC module present

R5 2.5-V FMC module clock

Arria V GT FPGA Development Board December 2014 Altera Corporation

Reference Manual

Page 21

Chapter 2: Board Components 2–11

MAX II CPLD EPM2210 System Controller

Table 2–5. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 3 of 5)

Schematic Signal Name

FMC_SDA

FPGA1_CEN

FPGA1_CEON

FPGA1_CONF_DONE

FPGA1_CONFIG_D0

FPGA1_CONFIG_D1

FPGA1_CONFIG_D2

FPGA1_CONFIG_D3

FPGA1_CONFIG_D4

FPGA1_CONFIG_D5

FPGA1_CONFIG_D6

FPGA1_CONFIG_D7

FPGA1_CONFIG_D8

FPGA1_CONFIG_D9

FPGA1_CONFIG_D10

FPGA1_CONFIG_D11

FPGA1_CONFIG_D12

FPGA1_CONFIG_D13

FPGA1_CONFIG_D14

FPGA1_CONFIG_D15

FPGA1_CVP_CONFDONE

FPGA1_MSEL0

FPGA1_MSEL1

FPGA1_MSEL2

FPGA1_MSEL3

FPGA1_MSEL4

FPGA1_NCONFIG

FPGA1_NSTATUS

FPGA1_PR_DONE

FPGA1_PR_ERROR

FPGA1_PR_READY

FPGA1_PR_REQUEST

FPGA2_CEN

FPGA2_CEON

FPGA2_CONF_DONE

FPGA2_CVP_CONFDONE

FPGA2_MSEL0

FPGA2_MSEL1

FPGA2_MSEL2

MAX II CPLD

Pin Number

I/O Standard Description

V2 2.5-V FMC module data

L1 2.5-V FPGA 1 chip enable

F11 2.5-V FPGA 1 chip output enable

M4 2.5-V FPGA 1 configuration done

D1 2.5-V FPGA configuration data

D3 2.5-V FPGA configuration data

E2 2.5-V FPGA configuration data

D4 2.5-V FPGA configuration data

E1 2.5-V FPGA configuration data

E3 2.5-V FPGA configuration data

F3 2.5-V FPGA configuration data

E4 2.5-V FPGA configuration data

F2 2.5-V FPGA configuration data

E5 2.5-V FPGA configuration data

F1 2.5-V FPGA configuration data

F4 2.5-V FPGA configuration data

G3 2.5-V FPGA configuration data

F5 2.5-V FPGA configuration data

G2 2.5-V FPGA configuration data

F6 2.5-V FPGA configuration data

M1 2.5-V FPGA 1 configuration via protocol done

F8 2.5-V FPGA 1 mode select 0

A6 2.5-V FPGA 1 mode select 1

E8 2.5-V FPGA 1 mode select 2

B7 2.5-V FPGA 1 mode select 3

D8 2.5-V FPGA 1 mode select 4

M5 2.5-V FPGA 1 configuration active

N1 2.5-V FPGA 1 configuration ready

K4 2.5-V FPGA 1 partial reconfiguration done

L5 2.5-V FPGA 1 partial reconfiguration error

L6 2.5-V FPGA 1 partial reconfiguration ready

L2 2.5-V FPGA 1 partial reconfiguration request

K5 2.5-V FPGA 2 chip enable

C11 2.5-V FPGA 2 chip output enable

M3 2.5-V FPGA 2 configuration done

B18 2.5-V FPGA 2 configuration via protocol done

U5 2.5-V FPGA 2 mode select 0

R7 2.5-V FPGA 2 mode select 1

V5 2.5-V FPGA 2 mode select 2

December 2014 Altera Corporation Arria V GT FPGA Development Board

Reference Manual

Page 22

2–12 Chapter 2: Board Components

MAX II CPLD EPM2210 System Controller

Table 2–5. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 4 of 5)

Schematic Signal Name

FPGA2_MSEL3

FPGA2_MSEL4

FPGA2_NCONFIG

FPGA2_NSTATUS

FPGA2_PR_DONE

FPGA2_PR_ERROR

FPGA2_PR_READY

FPGA2_PR_REQUEST

FPGA_DCLK

HSMA_PRSNTN

HSMB_PRSNTN

INIT_DONE1

INIT_DONE2

JTAG_EPM2210_TDI

JTAG_BLASTER_TDI

JTAG_TCK

JTAG_TMS

M570_CLOCK

M570_PCIE_JTAG_EN

MAX_BEN0

MAX_BEN1

MAX_BEN2

MAX_BEN3

MAX_CLK

MAX_CSN

MAX_OEN

MAX_WEN

MAX_CONF_DONE1

MAX_CTL0

MAX_CTL1

MAX_CTL2

MAX_ERROR1

MAX_LOAD1

MAX_RESETN

OVERTEMP1

OVERTEMP2

PGM1_CONFIG

MAX II CPLD

Pin Number

I/O Standard Description

T7 2.5-V FPGA 2 mode select 3

U6 2.5-V FPGA 2 mode select 4

M2 2.5-V FPGA 2 configuration active

M6 2.5-V FPGA 2 configuration ready

B16 2.5-V FPGA 2 partial reconfiguration done

D14 2.5-V FPGA 2 partial reconfiguration error

A17 2.5-V FPGA 2 partial reconfiguration ready

E13 2.5-V FPGA 2 partial reconfiguration request

N2 2.5-V FPGA configuration clock

A14 2.5-V HSMC port A present

E11 2.5-V HSMC port B present

T6 2.5-V FPGA initialization done

V4 2.5-V FPGA initialization done

M7 2.5-V MAX II CPLD on-board JTAG chain data in

N6 2.5-V MAX II CPLD on-board JTAG chain data out

R4 2.5-V JTAG chain clock

P5 2.5-V JTAG mode select

A10 1.8-V

D9 1.8-V

25-MHz clock to the on-board USB-Blaster II for sending

FACTORY command

Low signal to disable the on-board USB-Blaster II when the

PCI Express acts as a master to the JTAG chain.

B11 2.5-V FM bus MAX II byte enable 0

C10 2.5-V FM bus MAX II byte enable 1

A11 2.5-V FM bus MAX II byte enable 2

C9 2.5-V FM bus MAX II byte enable 3

J18 1.8-V FM bus MAX II clock

J17 1.8-V FM bus MAX II chip select

J15 1.8-V FM bus MAX II output enable

J14 1.8-V FM bus MAX II write enable

B3 2.5-V FPGA configuration done LED

E10 2.5-V FPGA 1 to MAX II option

A12 2.5-V FPGA 1 to MAX II option

D10 2.5-V FPGA 1 to MAX II option

C7 2.5-V FPGA 1 configuration error LED

B6 2.5-V FPGA 1 configuration active LED

E18 1.8-V MAX II reset push button

B14 2.5-V FPGA 1 fan RPM control

C12 2.5-V FPGA 2 fan RPM control

B4 2.5-V Load the flash memory image identified by the PGM LEDs

Arria V GT FPGA Development Board December 2014 Altera Corporation

Reference Manual

Page 23

Chapter 2: Board Components 2–13

MAX II CPLD EPM2210 System Controller

Table 2–5. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 5 of 5)

Schematic Signal Name

PGM1_LED0

PGM1_LED1

PGM1_LED2

PGM1_SEL

PHASE0

SDI_A_RX_BYPASS

SDI_A_RX_EN

SDI_A_TX_EN

SENSE_CS0N

SENSE_CS1N

SENSE_SCK

SENSE_SDI

SENSE_SDO

SI570_EN

SI571_EN

USB_CFG0

USB_CFG1

USB_CFG2

USB_CFG3

USB_CFG4

USB_CFG5

USB_CFG6

USB_CFG7

USB_CFG8

USB_CFG9

USB_CFG10

USB_CFG11

USB_CLK

VCCINT_SCL

VCCINT_SDA

MAX II CPLD

Pin Number

I/O Standard Description

A4 2.5-V Flash memory PGM select indicator 0

F7 2.5-V Flash memory PGM select indicator 1

C5 2.5-V Flash memory PGM select indicator 2

D6 2.5-V Toggles the

PGM_LED[0:2]

P8 2.5-V LTM4601 phase control

A8 2.5-V SDI equalization bypass

E9 2.5-V SDI receive enable

F9 2.5-V SDI transmit enable

F12 2.5-V Power monitor chip select

B15 2.5-V Power monitor chip select

E12 2.5-V Power monitor SPI clock

A15 2.5-V Power monitor SPI data in

D12 2.5-V Power monitor SPI data out

A13 2.5-V Si570 programmable oscillator enable

C13 2.5-V Si571 programmable VCXO enable

H14 1.8-V On-board USB-Blaster II data

H13 1.8-V On-board USB-Blaster II data

G13 1.8-V On-board USB-Blaster II data

F17 1.8-V On-board USB-Blaster II data

G12 1.8-V On-board USB-Blaster II data

F18 1.8-V On-board USB-Blaster II data

H16 1.8-V On-board USB-Blaster II data

G16 1.8-V On-board USB-Blaster II data

H15 1.8-V On-board USB-Blaster II data

G17 1.8-V On-board USB-Blaster II data

G14 1.8-V On-board USB-Blaster II data

G18 1.8-V On-board USB-Blaster II data

J6 2.5-V On-board USB-Blaster II clock

R3 2.5-V LTC3880 serial clock

R2 2.5-V LTC3880 serial data

LED sequence

December 2014 Altera Corporation Arria V GT FPGA Development Board

Reference Manual

Page 24

2–14 Chapter 2: Board Components

Configuration, Status, and Setup Elements

Configuration, Status, and Setup Elements

This section describes the board's configuration, status, and setup elements.

Configuration

This section describes the FPGA, flash memory, and MAX II CPLD EPM2210 System

Controller device programming methods supported by the Arria V GT FPGA

development board.

The Arria V GT FPGA development board supports the following three configuration

methods:

■ On-board USB-Blaster II is the default method for configuring the FPGA at any

time using the Quartus II Programmer in JTAG mode with the supplied USB cable.

■ External USB-Blaster for configuring the FPGA using an external USB-Blaster that

connects to the JTAG programming header (J1).

■ Flash memory download for configuring the FPGA using stored images from the

flash memory on either power-up or pressing the program configuration

push button,

PGM1_CONFIG

(S3).

FPGA Programming over On-Board USB-Blaster II

This configuration method implements a USB Type-AB connector (J7), a FTDI USB 2.0

PHY device (U5), and an Altera MAX II CPLD (U2) to allow the FPGA configuration

using a USB cable that connects directly between the USB port on the board and a USB

port of a PC running the Quartus II software.

The on-board USB-Blaster II in the MAX II CPLD EPM570GM100 normally masters

the JTAG chain. To prevent contention between the JTAG masters, the on-board

USB-Blaster II is automatically disabled when you connect an external USB-Blaster to

the JTAG chain through the JTAG connector.

If the USB-Blaster II is detected but no hardware is found in the chain, try reducing

the clock frequency of the JTAG chain using these commands:

■ To check the current setting:

■ To set a new setting (example clock frequency = 16 M):

<cable-no> JtagClock 16M

The USB-Blaster II needs to be 16 M or slower in this case. Only 6 M, 16 M, and 24 M

clock frequency options are available. Insert a value of 1 for the

the only JTAG cable you attach to the board.

1 Installing daughtercards such as HSMC or FMC can affect performance and requires a

lower speed.

jtagconfig --getparam <cable-no> JtagClock

jtagconfig --setparam

<cable-no>

if this is

Arria V GT FPGA Development Board December 2014 Altera Corporation

Reference Manual

Page 25

Chapter 2: Board Components 2–15

Configuration, Status, and Setup Elements

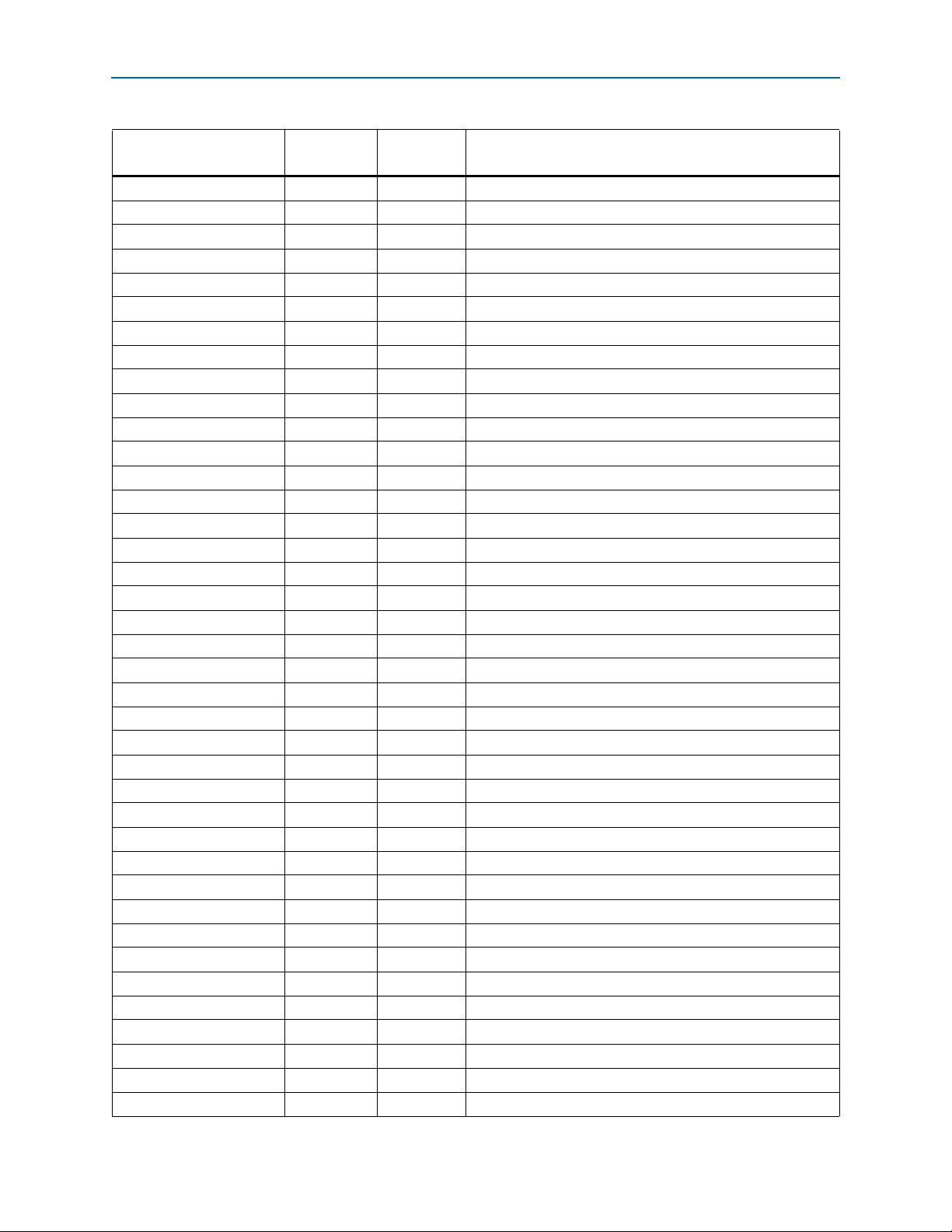

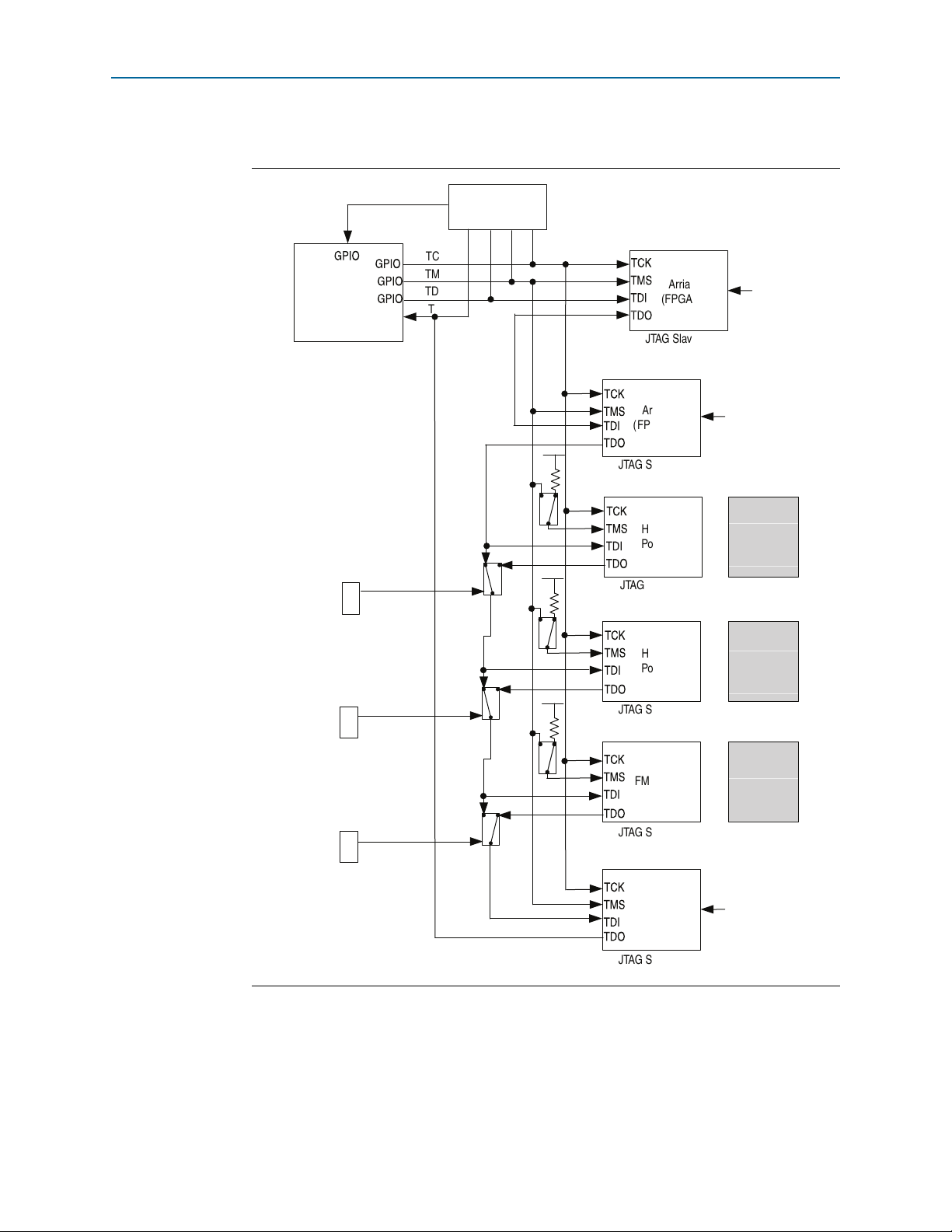

Figure 2–4 illustrates the JTAG chain.

Figure 2–4. JTAG Chain

10-pin

DISABLE

JTAG Header

GPIO

Cypress

On-Board

USB-Blaster

JTAG Master

GPIO

GPIO

GPIO

II

ENABLE

ENABLE

TCK

TMS

TDO

TDI

Analog

Switch

Analog

Switch

2.5V

2.5V

2.5V

TCK

TMS

TDI

TDO

JTAG Slave

TCK

TMS

TDI

TDO

JTAG Slave

TCK

TMS

TDI

TDO

JTAG Slave

TCK

TMS

TDI

TDO

JTAG Slave

Arria V

(FPGA 2)

HSMC

Por t A

HSMC

Por t B

Arria V

(FPGA 1)

ALWAYS

ENABLED

(in-chain)

ALWAYS

ENABLED

(in-chain)

Installed

HSMC

Card

Installed

HSMC

Card

DIP switch

DIP switch

ENABLE

Analog

Switch

TCK

TMS

TDI

TDO

JTAG Slave

TCK

TMS

TDI

TDO

JTAG Slave

FMC Port

MAX II CPLD

System

Controller

Installed

FMC

Card

ALWAYS

ENABLED

(in-chain)

Each jumper shown in Figure 2–4 is located in the JTAG chain DIP switch (SW6) on

the back of the board. To connect a device or interface in the chain, you must set the

corresponding switch from the JTAG chain DIP switch (SW6). The interface in the

JTAG chain depends on the switch settings but the FPGAs and MAX II devices are

always in the JTAG chain.

December 2014 Altera Corporation Arria V GT FPGA Development Board

Reference Manual

Page 26

2–16 Chapter 2: Board Components

Configuration, Status, and Setup Elements

Flash Memory Programming

Flash memory programming is possible through a variety of methods.

The default method is to use the factory design—Board Update Portal (BUP). This

design is an embedded webserver, which serves the BUP web page. The web page

allows you to select new FPGA designs including hardware, software, or both in an

industry-standard S-Record File (.flash) and write the design to the user hardware

page (page 1) of the flash memory over the network.

The secondary method is to use the pre-built parallel flash loader (PFL) design

included in the development kit. The development board implements the Altera PFL

megafunction for flash memory programming. The PFL megafunction is a block of

logic that is programmed into an Altera programmable logic device (FPGA or CPLD).

The PFL functions as a utility for writing to a compatible flash memory device. This

pre-built design contains the PFL megafunction that allows you to write either page 0,

page 1, or other areas of flash memory over the USB interface using the Quartus II

software. This method is used to restore the development board to its factory default

settings.

Other methods to program the flash memory can be used as well, including the

®

Nios

II processor.

f For more information on the Nios II processor, refer to the Nios II Processor page of

the Altera website.

FPGA Programming from Flash Memory

On either power-up or by pressing the program configuration push button,

PGM1_CONFIG

FPGA from the flash memory when the

megafunction reads 16-bit data from the flash memory and converts it to fast passive

parallel (FPP) format. This 8-bit data is then written to the FPGA's dedicated

configuration pins during configuration.

(S3), the MAX II CPLD EPM2210 System Controller's PFL configures the

PGM1_LED[2:0]

are ON. The PFL

Arria V GT FPGA Development Board December 2014 Altera Corporation

Reference Manual

Page 27

Chapter 2: Board Components 2–17

MAX II CPLD

EPM2210 System Controller

Arria V FPGA

FPGA_DATA [7:0]

FPGA_DCLK

FLASH_A [26:1]

FLASH_D [15:0]

DATA [7:0]

DCLK

INIT_DONE

nSTATUS

nCONFIG

CONF_DONE

CONF_DONE

MSEL0

MSEL1

MSEL2

MSEL3

MSEL4

MSEL[4:0] also

goes to MAX II CPLD

2.5 V

10 kΩ

nCE

CFI

Flash

FLASH_CEn

FLASH_OEn

FLASH_WEn

FLASH_A [26:0]

FLASH_D [15:0]

FLASH_CEn

FLASH_OEn

FLASH_WEn

FLASH_WPn

FLASH_ADVn

FPGA_nCONFIG

FPGA_CONF_DONE

FLASH_RYBSYn

FLASH_RYBSYn

FPGA_nSTATUS

FPGA_INIT_DONE

1.8 V

10 kΩ

10 kΩ

FLASH_ADVn

CONF_DONE_LED

2.5 V

FLASH_CLK

FLASH_CLK

FLASH_RSTn

FLASH_RESETn

PS Port

Flash Interface

56.2 Ω

100 Ω56.2 Ω

56.2 Ω

50 MHz

100 MHz

2.5 V

2.5 V

2.5 V

MAX_ERROR1

MAX_CONF_DONE1

MAX_LOAD1

FACTORY2

FACTORY1

CLK_ENABLE

CLK_SEL

MAX_RESETn

PGM1_CONFIG

PGM1_SEL

PGM1_LED0

PGM1_LED1

PGM1_LED2

DIP Switch

DIP Switch

1 kΩ

Configuration, Status, and Setup Elements

Figure 2–5 shows the PFL configuration.

Figure 2–5. PFL Configuration

December 2014 Altera Corporation Arria V GT FPGA Development Board

f For information on the flash memory map storage, refer to the Arria V GT FPGA

Development Kit User Guide.

There are two pages reserved for the FPGA configuration data. The factory hardware

page—page 0—loads upon power-up when the

'1'. Otherwise, the user hardware page 1 loads. Pressing the

(S3) loads the FPGA with a hardware page based on which

D13, D14) illuminates.

Factory1

DIP switch (SW5.3) is set to

PGM1_CONFIG

PGM1_LED[2:0]

push button

LED (D12,

Reference Manual

Page 28

2–18 Chapter 2: Board Components

Configuration, Status, and Setup Elements

Tab le 2– 6 defines the hardware page that loads when you press the

PGM1_CONFIG

button (S3).

Table 2–6. PGM1_LED Settings

PGM1_LED0 PGM1_LED1 PGM1_LED2 Design

ON OFF OFF Factory hardware

OFF ON OFF User design 1

OFF OFF ON User design 2

FPGA Programming over External USB-Blaster

The JTAG programming header provides another method for configuring the FPGA

using an external USB-Blaster device with the Quartus II Programmer running on a

PC. The external USB-Blaster connects to the board through the JTAG connector (J5).

Both FPGAs and the MAX II devices are always in the JTAG chain.

f For more information on the following topics, refer to the respective documents:

■ Board Update Portal and PFL design, refer to the Arria V GT FPGA Development Kit

User Guide.

■ PFL megafunction, refer to Parallel Flash Loader Megafunction User Guide.

push

Status Elements

The development board includes status LEDs. This section describes the status

elements.

Tab le 2– 7 lists the LED board references, names, and functional descriptions.

Table 2–7. Board-Specific LEDs (Part 1 of 2)

Board

Reference

D1 Power — 5.0-V Blue LED. Illuminates when 5.0 V power is active.

D16 MAX_CONF_DONE1 — 2.5-V

D17 MAX_LOAD1 — 2.5-V

D15 MAX_ERROR1 — 2.5-V

D12, D13,

D14

Schematic Signal

Name

PGM1_LED[2:0] — 2.5-V

Arria V GT FPGA

Pin Number

I/O

Standard

Description

Green LED. Illuminates when the MAX II CPLD

EPM2210 System Controller is successfully

configured. Driven by the MAX II CPLD EPM2210

System Controller.

Green LED. Illuminates when the MAX II CPLD

EPM2210 System Controller is actively configuring

the FPGA. Driven by the MAX II CPLD EPM2210

System Controller wire-OR'd with the on-board

USB-Blaster II CPLD.

Red LED. Illuminates when the MAX II CPLD

EPM2210 System Controller fails to configure the

FPGA. Driven by the MAX II CPLD EPM2210

System Controller.

Green LEDs. Illuminates to indicate which hardware

page loads from flash memory when you press the

PGM1_SEL

board.

push button or when you power-on the

Arria V GT FPGA Development Board December 2014 Altera Corporation

Reference Manual

Page 29

Chapter 2: Board Components 2–19

Configuration, Status, and Setup Elements

Table 2–7. Board-Specific LEDs (Part 2 of 2)

Board

Reference

Schematic Signal

Name

Arria V GT FPGA

Pin Number

D34 DEVICE1_LED — 2.5-V

D35 DEVICE2_LED — 2.5-V

D36 ENET_LED_TX — 2.5-V

D37 ENET_LED_RX — 2.5-V

D40 ENET_LED_LINK10 — 2.5-V

D38 ENET_LED_LINK100 — 2.5-V

D39 ENET_LED_LINK1000 AN17 2.5-V

D4 HSMA_RX_LED AT15 2.5-V

D5 HSMA_TX_LED AH14 2.5-V

D6 HSMA_PRSNTn AW15 3.3-V

D7 HSMB_RX_LED AG26 2.5-V

D8 HSMB_TX_LED AM28 2.5-V

D9 HSMB_PRSNTn AT24 3.3-V

D44 PCIE_LED_X1 AC18 2.5-V

D43 PCIE_LED_X4 AD17 2.5-V

D42 PCIE_LED_X8 AT16 2.5-V

I/O

Standard

Description

Green LED. Illuminates when FPGA 1 is

successfully configured. Driven by the MAX II

CPLD EPM2210 System Controller.

Green LED. Illuminates when FPGA 2 is

successfully configured. Driven by the MAX II

CPLD EPM2210 System Controller.

Green LED. Illuminates to indicate Ethernet PHY

transmit activity. Driven by the Marvell 88E1111

PHY.

Green LED. Illuminates to indicate Ethernet PHY

receive activity. Driven by the Marvell 88E1111

PHY.

Green LED. Illuminates to indicate Ethernet linked

at 10 Mbps connection speed. Driven by the

Marvell 88E1111 PHY.

Green LED. Illuminates to indicate Ethernet linked

at 100 Mbps connection speed. Driven by the

Marvell 88E1111 PHY.

Green LED. Illuminates to indicate Ethernet linked

at 1000 Mbps connection speed. Driven by the

Marvell 88E1111 PHY.

Green LED. Illuminates to indicate HSMA port A

receive data activity.

Green LED. Illuminates to indicate HSMA port A

transmit data activity.

Green LED. Illuminates when HSMC port A has a

board or cable plugged-in such that pin 160

becomes grounded. Driven by the add-in card.

Green LED. Illuminates to indicate HSMA port B

receive data activity.

Green LED. Illuminates to indicate HSMA port B

transmit data activity.

Green LED. Illuminates when HSMC port B has a

board or cable plugged-in such that pin 160

becomes grounded. Driven by the add-in card.

Yellow LED. Configure this LED to display the PCI

Express link width x1.

Yellow LED. Configure this LED to display the PCI

Express link width x4.

Yellow LED. Configure this LED to display the PCI

Express link width x8.

December 2014 Altera Corporation Arria V GT FPGA Development Board

Reference Manual

Page 30

2–20 Chapter 2: Board Components

Configuration, Status, and Setup Elements

Setup Elements

The development board includes several different kinds of setup elements. This

section describes the following setup elements:

■ Board settings DIP switch

■ JTAG chain header switch

■ PCI Express control DIP switch

■ CPU reset push button

■ MAX II reset push button

■ Configuration push button

■ Image select push button

f For more information about the default settings of the DIP switches, refer to the

Arria V GT FPGA Development Kit User Guide.

Board Settings DIP Switch

The board settings DIP switch (SW5) controls various features specific to the board

and the MAX

switch controls and descriptions.

II CPLD EPM2210 System Controller logic design. Tab le 2– 8 lists the

Table 2–8. Board Settings DIP Switch Controls

Switch

1

2

3

4

Schematic

Signal Name

CLK_SEL

CLK_ENABLE

FACTORY_USER1

FACTORY_USER2

Description

ON : 100 MHz clock select

OFF : SMA input clock select

ON : Enable on-board oscillators

OFF : Disable on-board oscillators

ON : Load the factory design from flash for Arria V FPGA 1 at power up

OFF : Load the user design from flash at power up

Unused

JTAG Settings DIP Switch

The JTAG settings DIP switch (SW6) either remove or include devices in the active

JTAG chain. However, the Arria V GT FPGAs and MAX

Controller are always in the JTAG chain. Tab le 2 –9 lists the switch controls and its

descriptions.

Table 2–9. JTAG Chain Header Switch Controls (Part 1 of 2)

Switch Schematic Signal Name Description

1

2

HSMA_JTAG_EN

HSMB_JTAG_EN

ON : Bypass HSMA

OFF : HSMA in-chain

ON : Bypass HSMB

OFF : HSMB in-chain

II CPLD EPM2210 System

Arria V GT FPGA Development Board December 2014 Altera Corporation

Reference Manual

Page 31

Chapter 2: Board Components 2–21

Configuration, Status, and Setup Elements

Table 2–9. JTAG Chain Header Switch Controls (Part 2 of 2)

Switch Schematic Signal Name Description

3

4

FMC_JTAG_EN

NC

ON : Bypass FMC connector

OFF : FMC connector in-chain

Unused

PCI Express Control DIP Switch

The PCI Express control DIP switch (SW7) is provided to enable or disable different

configurations. Table 2–10 lists the switch controls and descriptions.

Table 2–10. PCI Express Control DIP Switch Controls

Switch Schematic Signal Name Description

1

2

3

4

PCIE_PRSNT2n_x1

PCIE_PRSNT2n_x4

PCIE_PRSNT2n_x8

NC

ON : Enable x1 presence detect

OFF : Disable x1 presence detect

ON : Enable x4 presence detect

OFF : Disable x4 presence detect

ON : Enable x8 presence detect

OFF : Disable x8 presence detect

Unused

CPU Reset Push Button

Each Arria V GT FPGA has a CPU reset push button,

CPU2_RESETn

FPGA

(S8) for FPGA 2. Both these push buttons are inputs to the Arria V GT

DEV_CLRn

pin and are open-drain I/Os from the MAX II CPLD System

Controller. The push button is the default reset for both the FPGA and CPLD logic.

The MAX II System Controller also drives these push button during POR.

1 You must enable the

function to work. Otherwise, the

enable the signal in the Quartus II software, and then pull high on the board, every

register within the FPGA resets to a low signal.

MAX II Reset Push Button

The MAX II reset push button,

Controller. This push button is the default reset for the CPLD logic.

Configuration Push Button

The configuration push button,

EPM2210 System Controller. The push button forces a reconfiguration of the FPGA

from flash memory. The location in the flash memory is based on the settings of the

PGM1_LED[2:0]

Valid settings include

memory reserved for FPGA designs.

, which is controlled by the image select push button,

CPU_RESETn

signal within the Quartus II software for this reset

CPU_RESETn

MAX_RESETn

PGM1_CONFIG

PGM1_LED0, PGM1_LED1

CPU1_RESETn

(S4) for FPGA 1 and

acts as a regular I/O pin. When you

, is an input to the MAX II CPLD System

(S3), is an input to the MAX II CPLD

, or

PGM1_LED2

PGM1_SEL

on the three pages in flash

(S2).

December 2014 Altera Corporation Arria V GT FPGA Development Board

Reference Manual

Page 32

2–22 Chapter 2: Board Components

Clock Circuitry

Image Select Push Button

The program select push button,

System Controller. The push button toggles the

which location in the flash memory is used to configure the FPGA. Refer to Table 2–6

for the

PGM1_LED[2:0]

sequence definitions.

PGM1_SEL

(S2), is an input to the MAX II CPLD

PGM1_LED[2:0]

sequence that selects

Clock Circuitry

This section describes the board's clock inputs and outputs.

On-Board Oscillators

The development board includes fixed and programmable oscillators with a

frequency of 50-MHz, 100-MHz, 125-MHz, 148.5-MHz, 156.25-MHz, and 625-MHz.

Arria V GT FPGA Development Board December 2014 Altera Corporation

Reference Manual

Page 33

Chapter 2: Board Components 2–23

Clock Circuitry

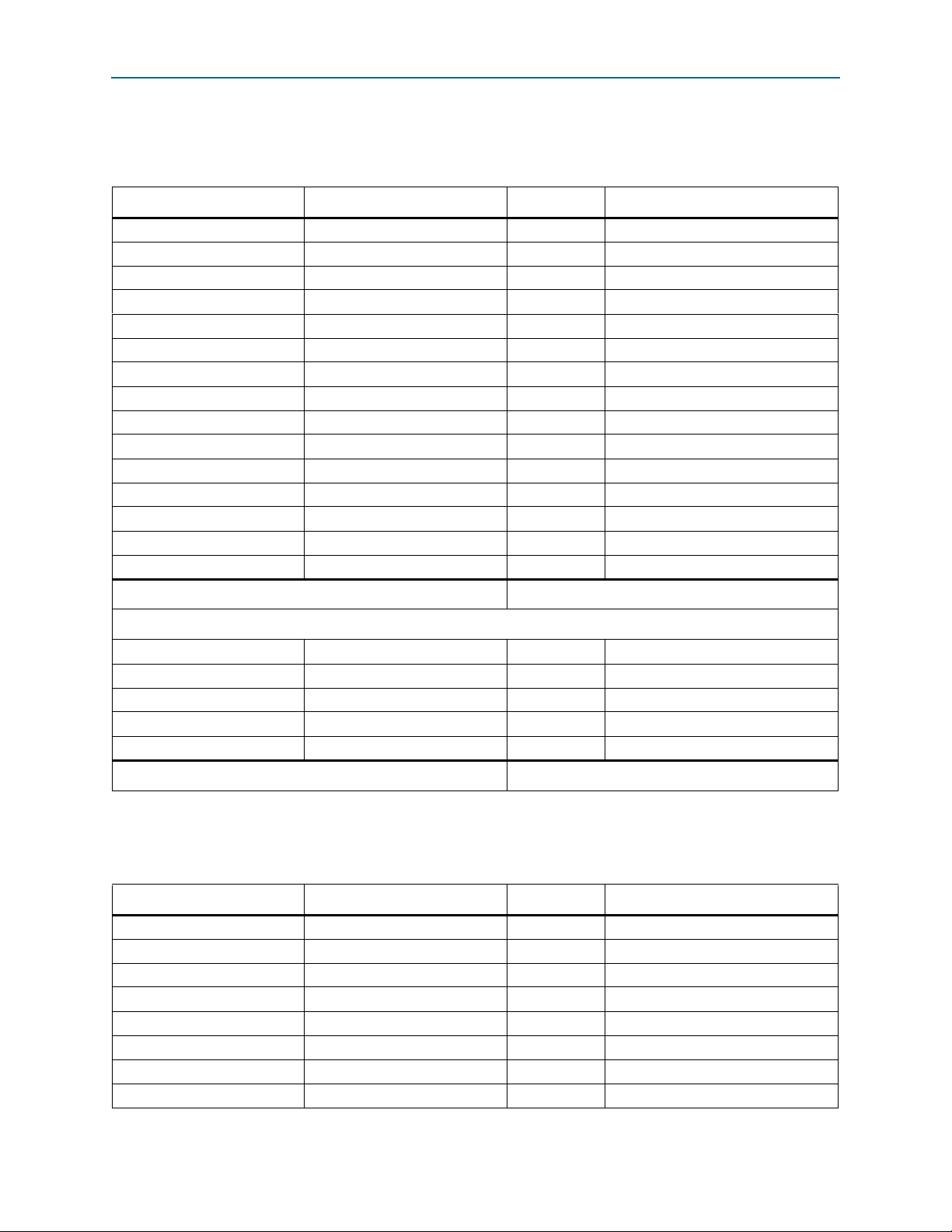

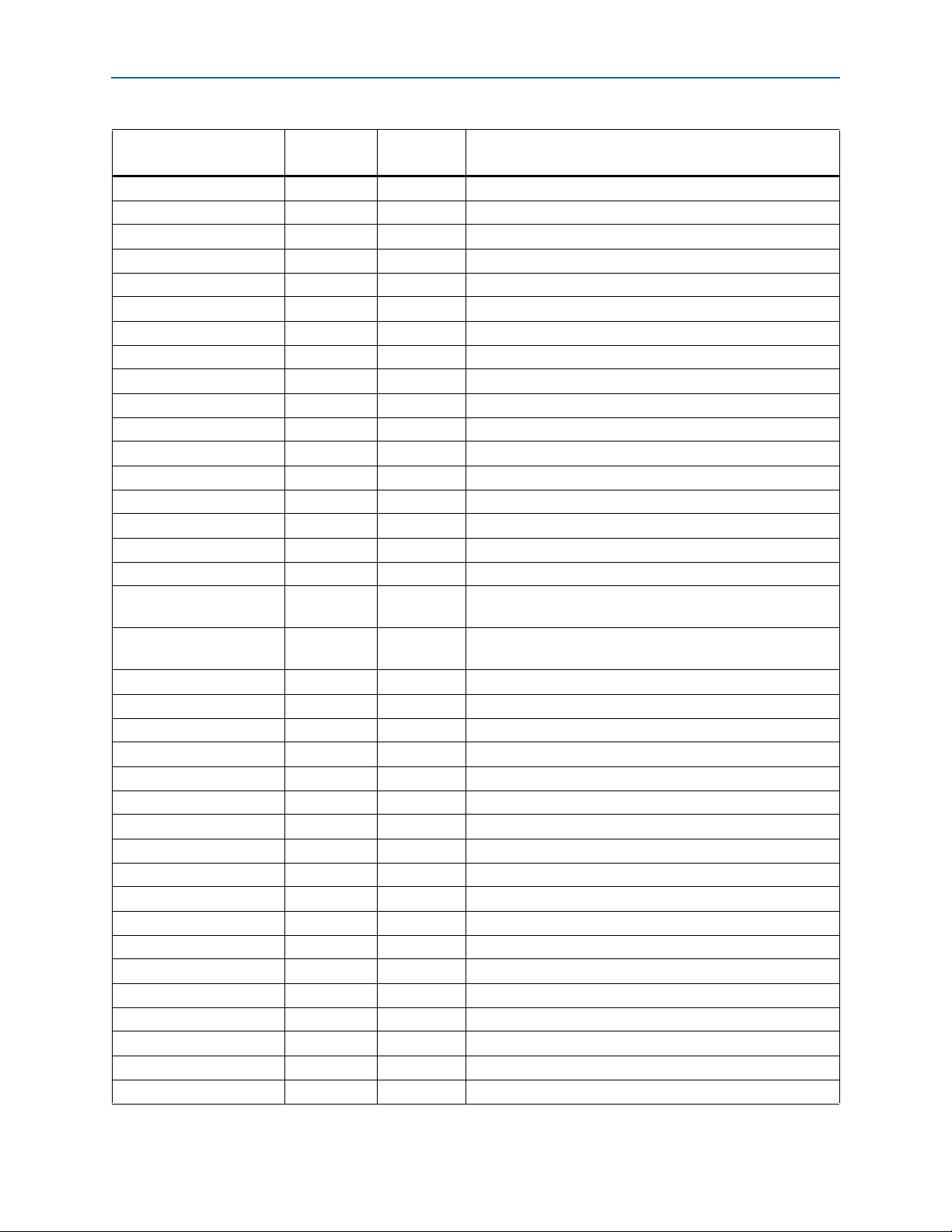

Figure 2–6 shows the default frequencies of all external clocks going to the Arria V GT

FPGA development board.

Figure 2–6. Arria V GT FPGA Development Board Clocks

U51

REFCLK INPUT

X6

50 MHz

SMA

Buffer

50 MHz

U56

SMA

Buffe

X7

Si570

100 MHz

Default

U53

Si5388

CLK3

CLK2

CLK1

CLK0

125 MHz

125 MHz

156.25 MHz

625 MHz

100 MHz

Default

REFCLK1A_Q L0_P/N

PCIE_REF_CLK_P /N

REFCLK3_A_Q L1_P/N

REFCLK2_A_Q L1_P/N

REFCLK4_A_Q L2_P/N

r

100 MHz

(PCIe )

(SFP +)

(SFP +)

(SFP +)

50 MHz

125 MHz

CLKIN_MAX_50

100 MHz

U16

QL0

QL1

QL2

BO TA_P/N [1]

N

KINBOTA_P/N[0]

L

CLKI

C

CLK6

CLK7

B3 B4

B8 B7

50 MHz

CLKINA_50

p

CLK5

125 MHz

CLKA_125_P/N

CLK0

QR0

QR1

QR2

REFCLK0_A_Q R0_P/N

C2C)

(

REFCLK2_A_Q R1_P/N

(C2C , HSMA )

REFCLK4_A_Q R2_P/N

HSMA)

(

125 MHz

625 MHz

100 MHz

125 MHz

CLK3

CLK2

CLK1

CLK0

U48

Si5388

Clock Buffer

1:2

156.25 MHz

J16U25

Bullseye

Connector

CLK17

CLK19CLKINTOPA_P/N[0]

125 MHz

CLKINTOPA_P/N[1]

100 MHz

100 MHz

125 MHz

125 MHz

N

_50

B

N

100 MHz

U13

QL0

QL1

QL2

I

B_125_P/

LK

C

CLK

0p

CLK6

CLK

B3 B4

B8 B7

50 MHz

100 MHz

U34

Si5388

CLK3

CLK2

CLK1

CLK0

125 MHz

625 MHz

100 MHz

625 MHz

REFCLK1_B_Q L0_P/N

REFCLK0_B_Q L0_P/N

(C2C )

REFCLK2_B_Q L1_P/N

(C2C )

REFCLK4_B_Q L2_P/N

(C2C )

0]

[

N

_P/

INB OTB

CLKINBOTB_P/N[1]

CLK

CLK7

CLK11

QR0

QR1

QR2

20

LK15

C

CLK

]

1

/N[0]

P

_

125 MHz

/N[

P

_

U53

SDI (148.5 M/148.35 M)

Si571

148.5 MHz

Default

R

EFCLK0_B_QR 0_P/N

(HSMB, SDI)

REFCLK1_B_Q R0_P/N

(HSMB, SDI)

REFCLK2_B_Q R1_P/N

(FMC )

REFCLK3_B_Q R2_P/N

(FMC )

125 MHz

156.25 MHz

100 MHz

125 MHz

U52

CLK3

CLK2

Si5388

CLK1

CLK0

KINTOPB

KINTOPB

L

L

C

C

December 2014 Altera Corporation Arria V GT FPGA Development Board

Reference Manual

Page 34

2–24 Chapter 2: Board Components

Clock Circuitry

Tab le 2 –11 lists the oscillators, its I/O standard, and voltages required for the

development board.

Table 2–11. On-Board Oscillators

Source

X6 to U51 1:3

clock buffer

X3

X7 to U56 1:6

clock buffer

X1

X4

X2

U53

U48

Schematic Signal

Name

CLKIN_MAX_50

CLKINA_50

CLKINB_50

CLK_CONFIG

REFCLK1_A_QL0_P

REFCLK1_A_QL0_N

CLKINBOTA_P0

CLKINBOTA_N0

CLKINTOPA_P0

CLKINTOPA_N0

CLKINBOTB_P0

CLKINBOTB_N0

CLKINTOPB_P0

CLKINTOPB_N0

CLKA_125_P

CLKA_125_N

CLKB_125_P

CLKB_125_N

REFCLK0_QR0_P

REFCLK0_QL2_N

REFCLK4_A_QL2_P

REFCLK4_A_QL2_N

REFCLK3_A_BUF_P

REFCLK3_A_BUF_N

REFCLK2_A_QL1_P

REFCLK2_A_QL1_N

CLKINBOTA_P1

CLKINBOTA_N1

REFCLK4_A_QR2_P

REFCLK4_A_QR2_N

REFCLK2_A_QR1_P

REFCLK2_A_QR1_N

REFCLK0_A_QR0_P

REFCLK0_A_QR0_N

CLKINTOPA_P1

CLKINTOPA_N1

Arria V GT

Frequency I/O Standard

FPGA Pin

Application

Number

1.8-V —

50.000 MHz

1.8-V AF21

Nios II and MAX II CPLD

1.8-V AP34

100.000 MHz 2.5-V CMOS — Fast FPGA configuration

100.000 MHz

125.000 MHz

125.000 MHz

148.500 MHz

625.000 MHz

156.250 MHz

125.000 MHz

125.000 MHz

125.000 MHz

100.000 MHz

625.000 MHz

125.000 MHz

LVDS

(fanout buffer)

LVDS AP34

LVDS AN34

LVDS AD20

LVDS AC21

LVDS —

LVDS —

LVDS W 31

LVDS W 32

LVDS —

LVDS —

LVDS U31

LVDS U32

LVDS AL20

LVDS AK20

LVDS T9

LVDS T8

LVDS AB9

LVDS AB8

LVDS AF 8

LVDS AF 7

LVDS A2 2

LVDS A2 1

AE31

AE32

AD20

AC21

C20

D20

AK7

AJ7

C34

D34

PCI Express host/dual-XTL

Bottom edge FPGA 1 – QDRII+

Top edge FPGA 1 – DDR3

Bottom edge FPGA 2

Top edge FPGA 2 – DDR3

Fixed clock at 125 MHz for

FPGA 1 bank 3A

Fixed clock at 125 MHz for

FPGA 1 bank 3D

HD-SDI video

SFP+

SFP+, Bull's Eye connector,

1:2 clock to REFCLK3 on FPGA 1,

Bottom edge FPGA 1 – memory

HSMC port A, C2C

C2C

Top edge FPGA 1 – memory

Arria V GT FPGA Development Board December 2014 Altera Corporation

Reference Manual

Page 35

Chapter 2: Board Components 2–25

Clock Circuitry

Table 2–11. On-Board Oscillators

U34

U52

Source

Schematic Signal

Name

REFCLK4_B_QL2_P

REFCLK4_B_QL2_N

REFCLK2_B_QL1_P

REFCLK2_B_QL1_N

REFCLK0_B_QL0_P

REFCLK0_B_QL0_N

CLKINBOTB_P1

CLKINBOTB_N1

REFCLK3_B_QR2_P

REFCLK3_B_QR2_N

REFCLK2_B_QR1_P

REFCLK2_B_QR1_N

REFCLK1_B_QR0_P

REFCLK1_B_QR0_N

CLKINTOPB_P1

CLKINTOPB_N1

Frequency I/O Standard

625.000 MHz

100.000 MHz

625.000 MHz

125.000 MHz

125.000 MHz

100.000 MHz

156.250 MHz

125.000 MHz

LVDS U31

LVDS U32

LVDS AC31

LVDS AC32

LVDS AG32

LVDS AG33

LVDS AL20

LVDS AK20

LVDS T9

LVDS T8

LVDS Y 9

LVDS Y 8

LVDS A D9

LVDS A D8

LVDS H6

LVDS J 6

Arria V GT

FPGA Pin

Number

Application

C2C

C2C

C2C

Bottom edge FPGA 2 – memory

FMC

FMC

HSMC port B, SDI

Top edge FPGA 2

Off-Board Clock Input/Output

The development board has input and output clocks which can be driven onto the

board. The output clocks can be programmed to different levels and I/O standards

according to the FPGA device’s specification.

Tab le 2 –1 2 lists the clock inputs for the development board.

Table 2–12. Off-Board Clock Inputs

Source

SMA

HSMC

HSMC

HSMC

HSMC