Page 1

INDEX:

LH216S92DT SERVICE MANUAL

PART 1:

PART 2:

PART 3

PART 4:

PART 5:

PART6:

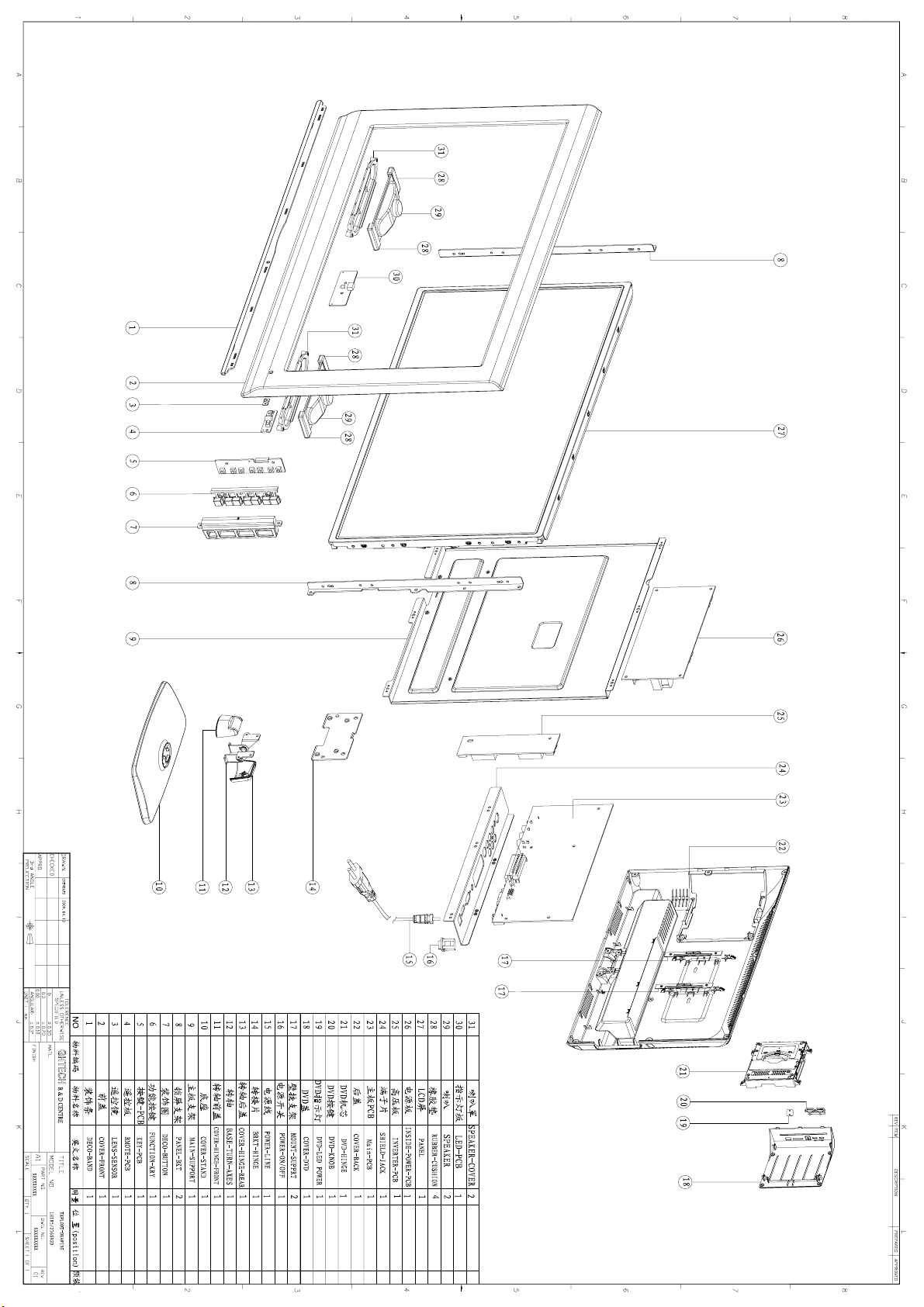

Brief Introduction Of The LH216S92DT

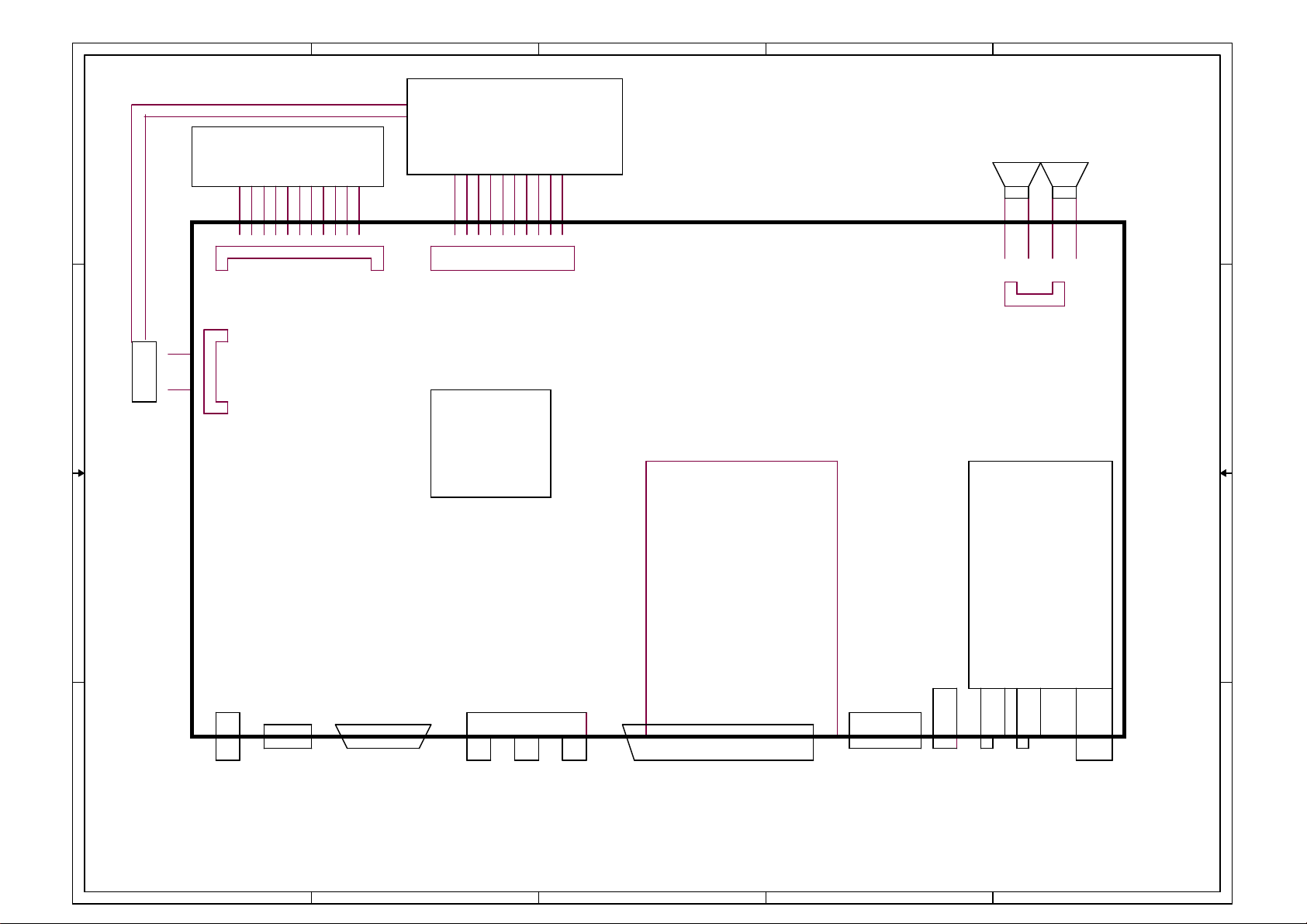

Exploded view

:

IC Introduction

Detailed Circuit

Components List

Debug Instruction

◆

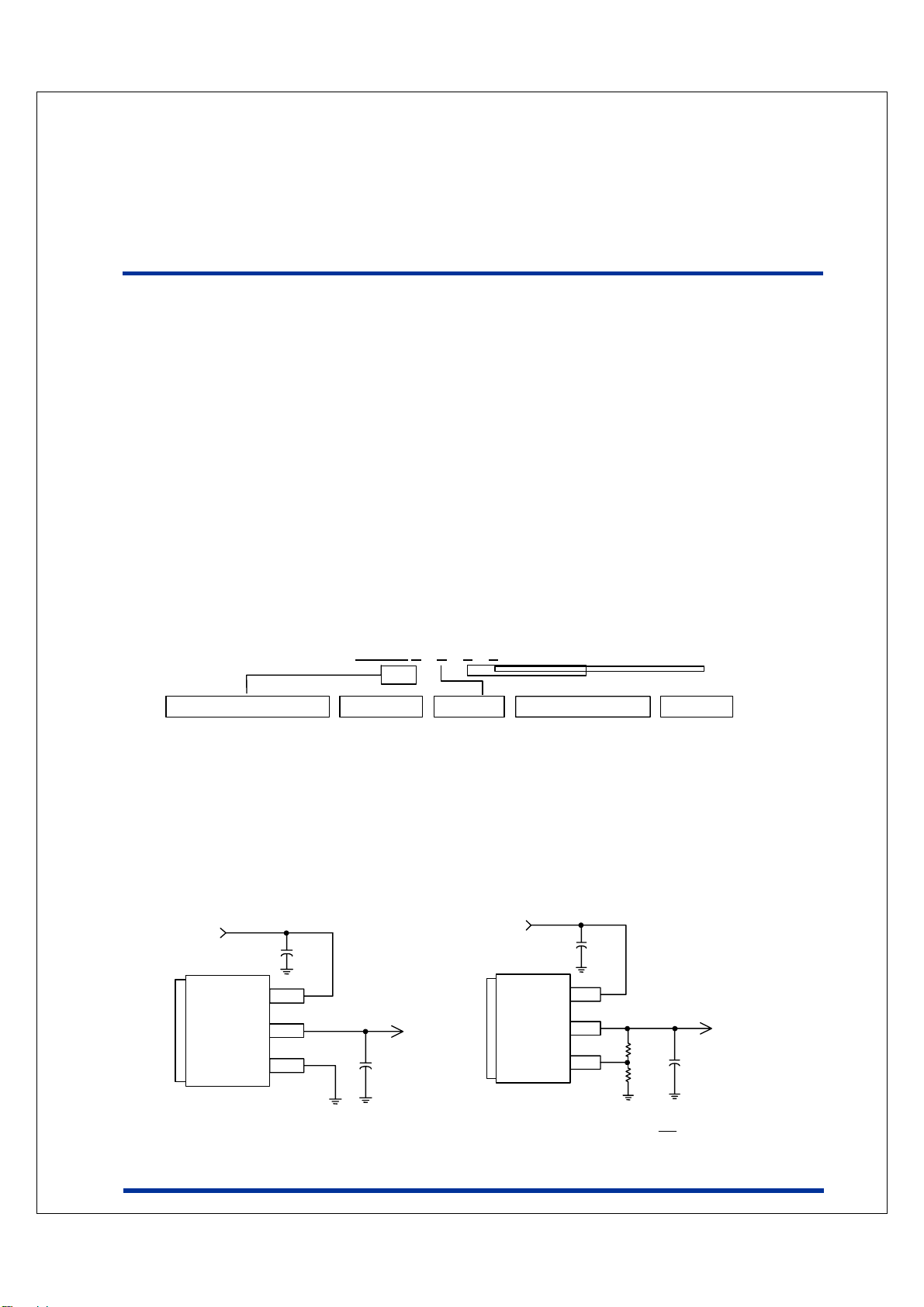

Schematic Diagram Block

◆

Printed Circuit

Page 2

Part1:

5

4

3

2

1

Schematic Diagram

PANEL

D D

KEY&IR BOARD

J3

KEY&IR CONNECTOR

CON8 J14

5V IR GND K0 R G GND K1 K2 K3 K4 K5 K6 K7

C C

INVERTER BOARD

J4

INVERTER CONNECTOR

12V 12V EN ADJ GND GND

B B

LVDS CONNECTOR

SPV7100

AMPLIFER CONNECTOR

GND R GND L

A A

HDMI PC AV

YUV

5

4

SCART SVHS

PCMCIA

3

USB

2

PC

AUDIO

IN

Earphone

TUNER

1

Page 3

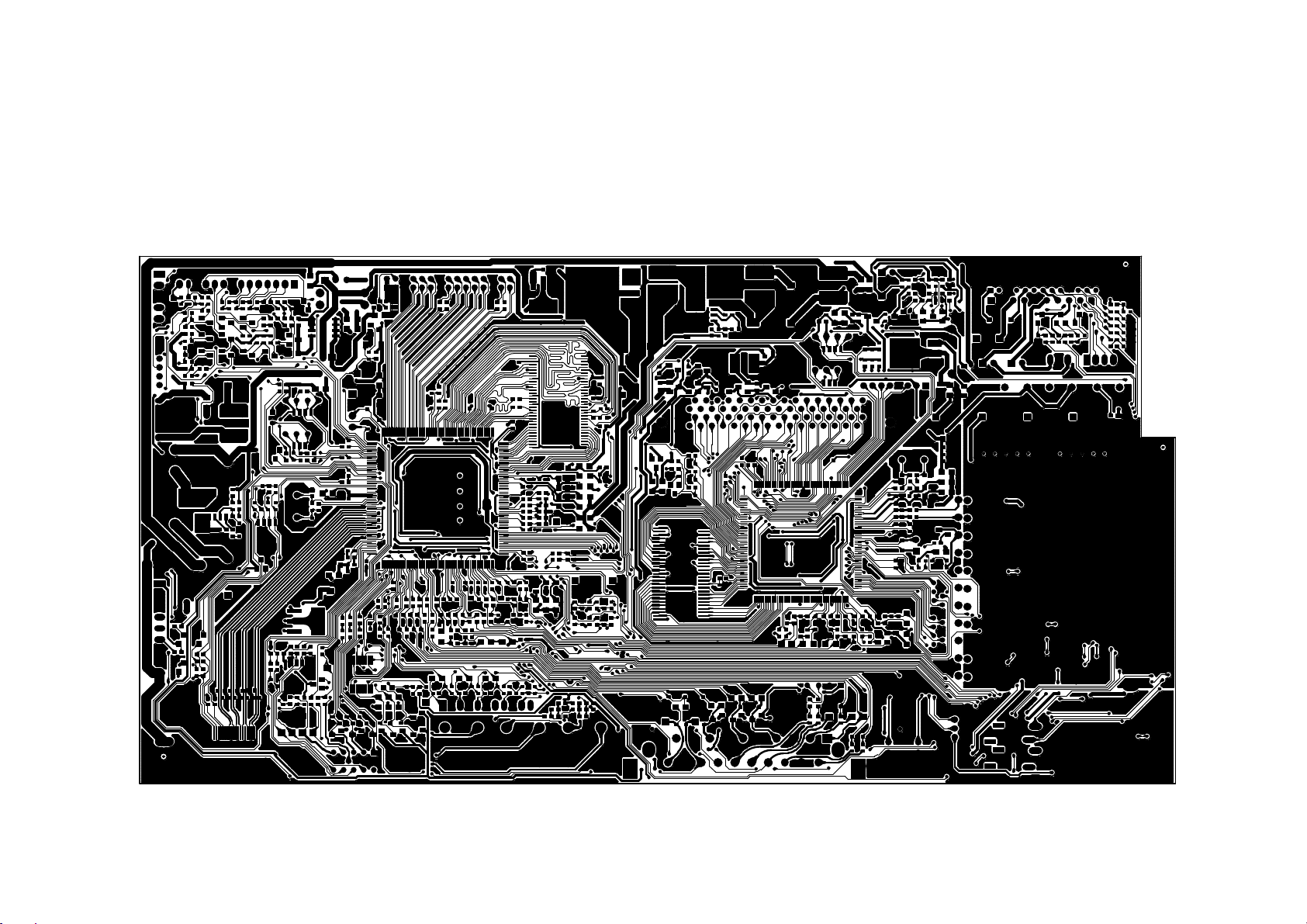

Printed Circuit

TV Main Board (Top View)

Page 4

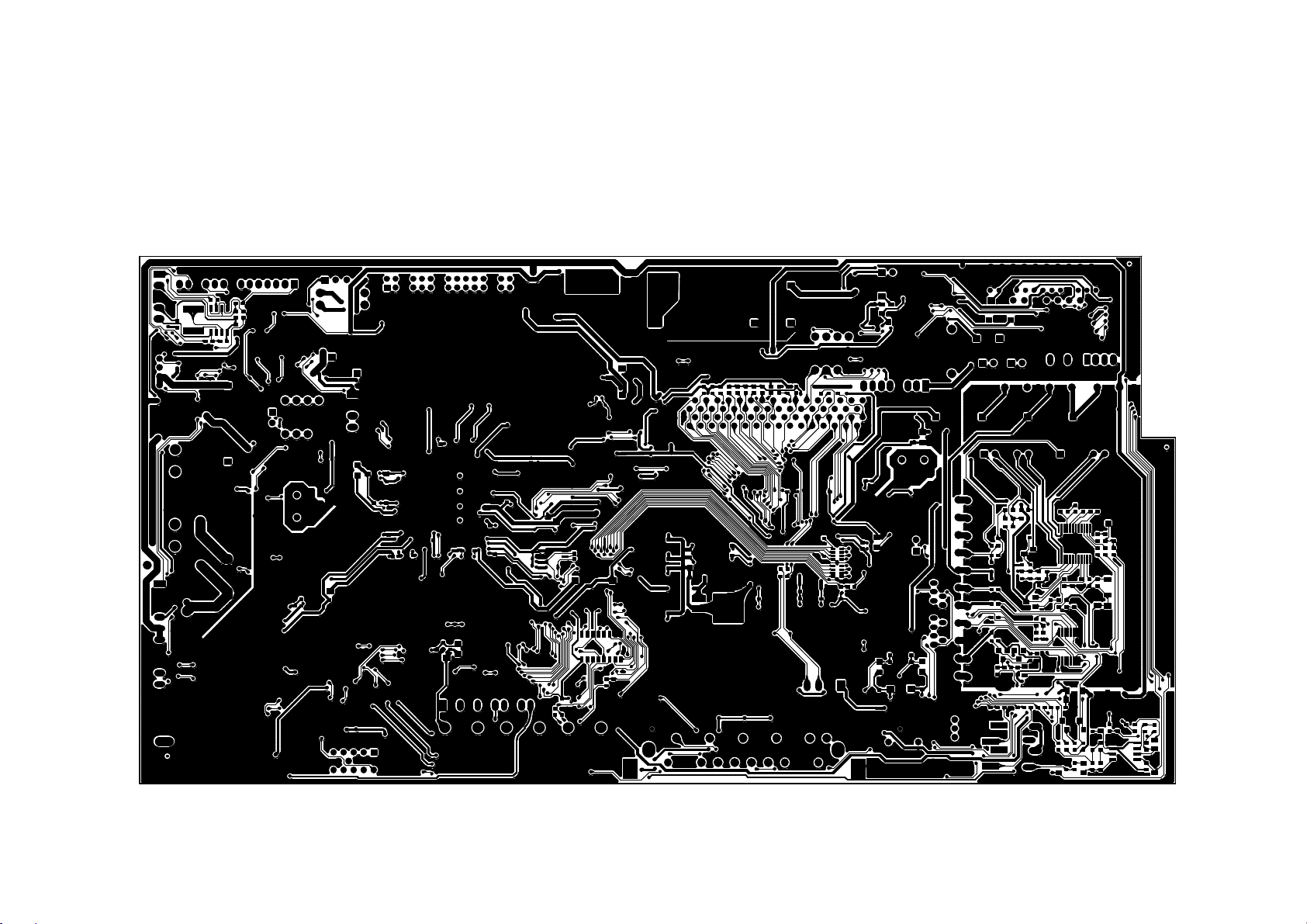

TV Main Board

(Bottom view)

Page 5

Page 6

Part3:

IC Introduction

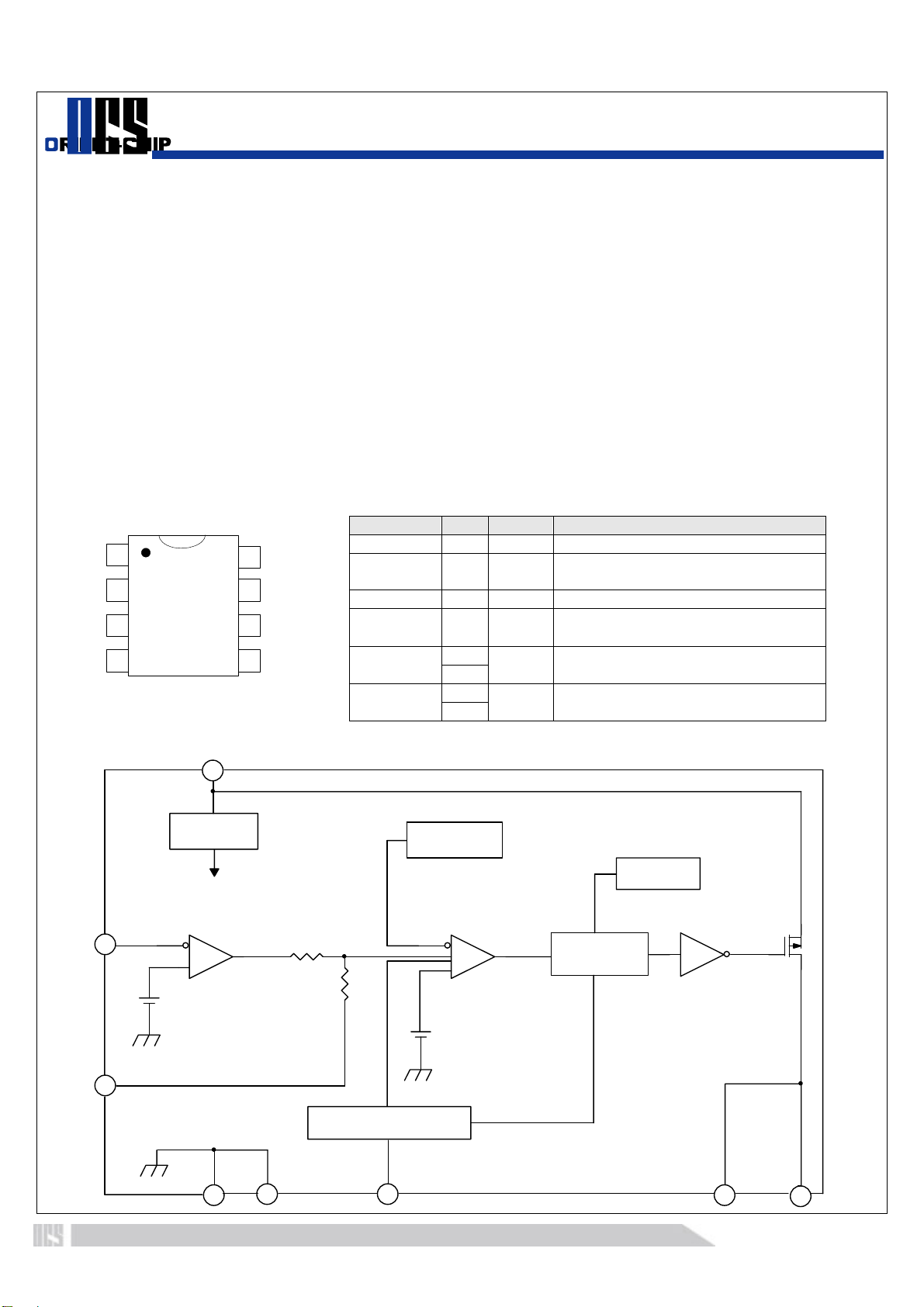

SWITCHING BUCK REGULATOR

OCP2030

General Description

The OCP2030 is a buck topology of switching regulator for wide operating voltage applications field. The OCP2030

includes a high current P-MOSFET, high precision reference (0.5V) for comparing output voltage with feedback

amplifier, an internal dead-time controller and oscillator for controlling the maximum duty cycle and PWM frequency,

and has power-on programmable soft start time and short circuit PMOS turn-off and auto re-start protection functions.

Features

z Precision feedback reference voltage: 0.5V (2%)

z Wide supply voltage operating range: 3.6 to 20V

z

Low current consumption: 3mA

z Internal fixed oscillator frequency: Typ. 360KHz

z Programmable Soft-Start function (SS)

z Short Circuit Shutdown and Auto Re-start function(ARSCP)

z Built-in P-MOSFET for 3A loading capability

z Package: SOP8

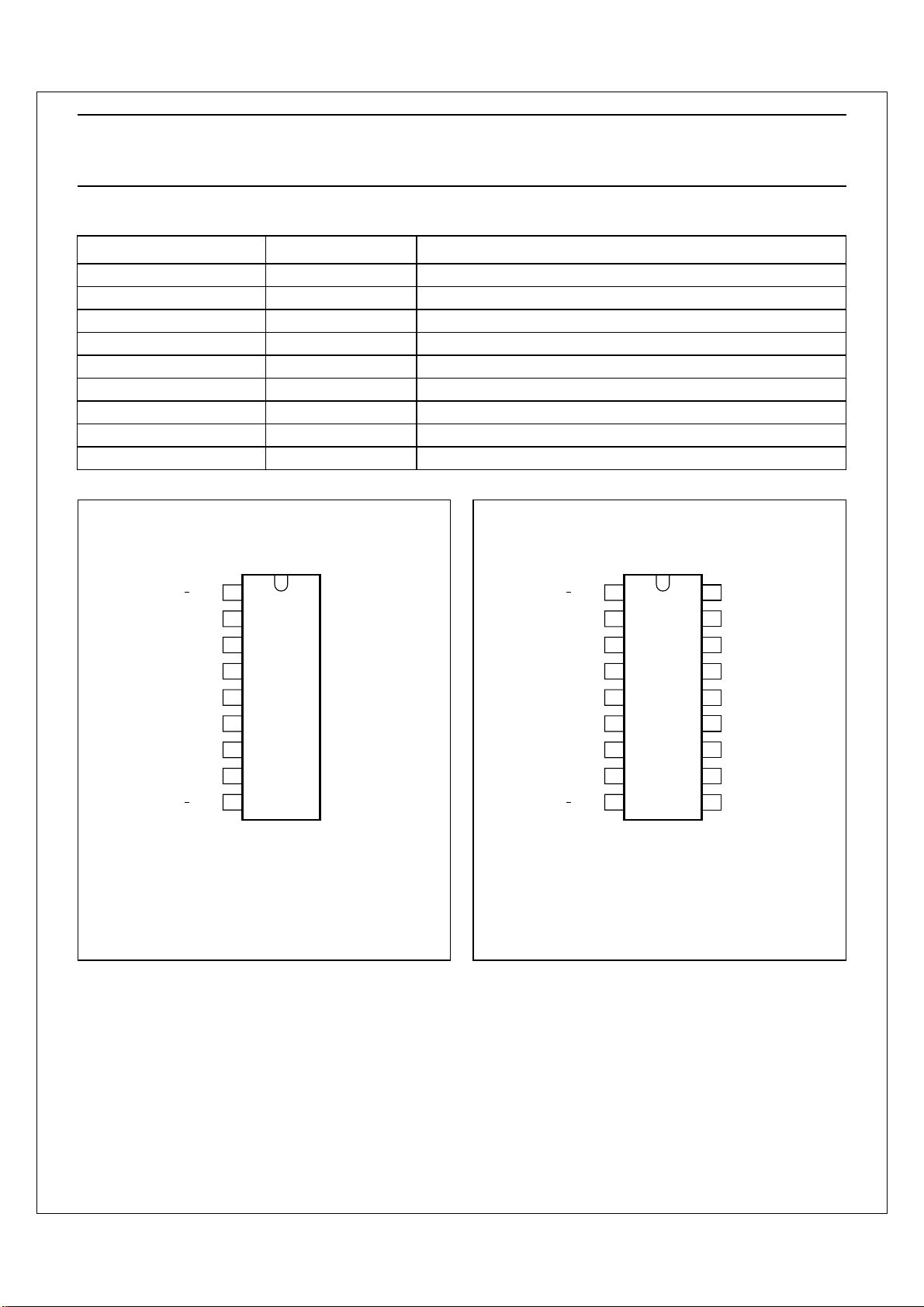

Pin Configuration

Top View

1

2

3

4

Block Diagram

8

7

OCP2030

6

5

1

Name No. Status Description

VCC 1 P IC Power Supply (PMOS Source)

SS/SCP 2 I

IN- 3 I Error Amplifier Inverting Input

FB 4 O

GND

LX

5

6

7

8

P

O PMOS High Current Output

Connecting with a Soft-start &

ARSCP timing capacitor

Error Amplifier Compensation

Output

IC Ground

Reference

Regulator

1.25V

Oscillator

Therm al

Shuntdown

3

0.5V

36KΩ

500Ω

Output drive

control circuits

0.8V

4

Soft start&Auto Re-start

S.C.P Circuits

5

6

2

Page 1 - 9

7

Rev. 1.1 May.22, 2007

8

Page 7

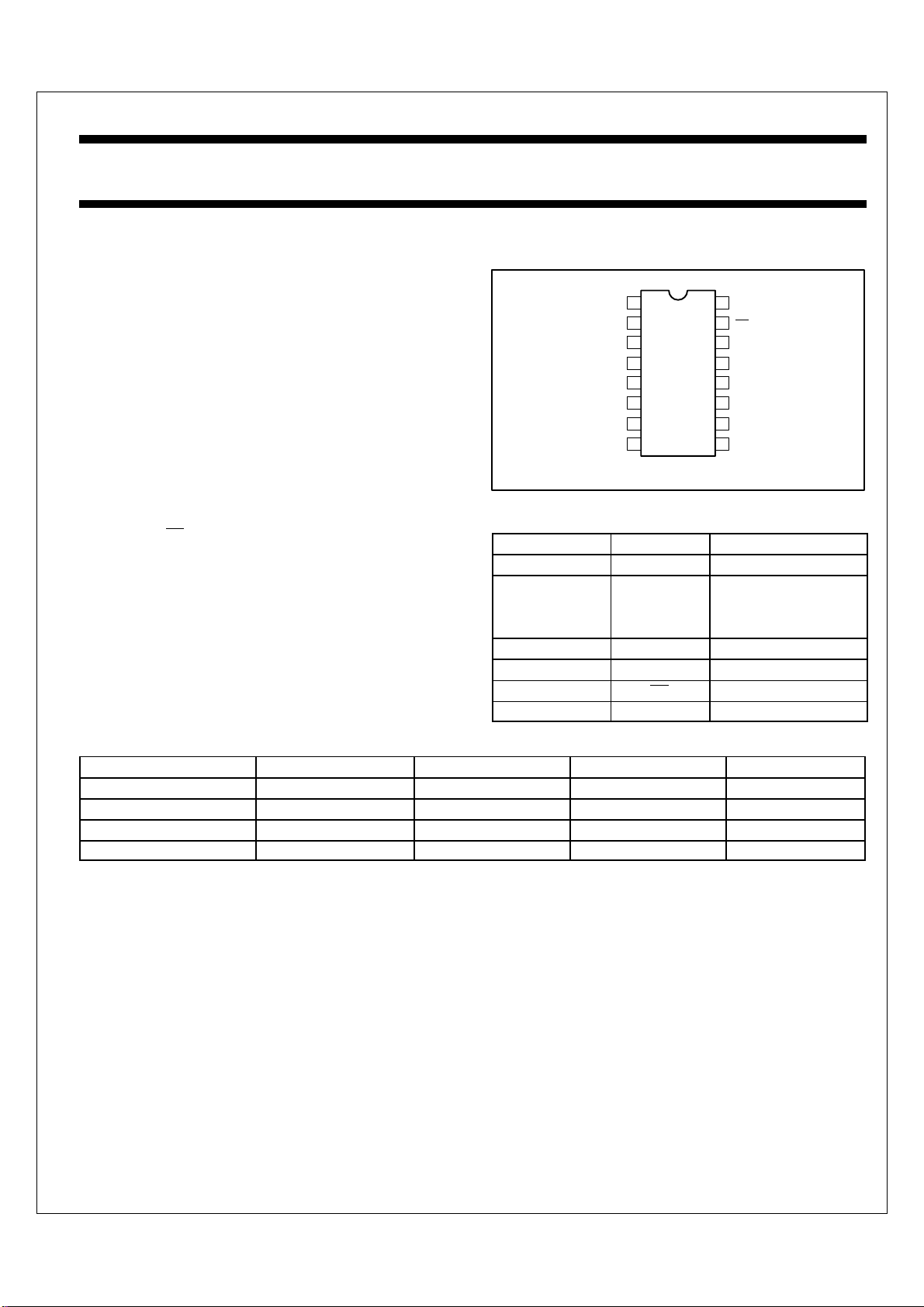

Philips Semiconductors Product data

CBT3257Quad 1-of-2 multiplexer/demultiplexer

FEATURES

• 5 Ω switch connection between two ports

TTL-compatible input levels

•

•

Minimal propagation delay through the switch

•

Latch-up protection exceeds 500 mA per JESD78

•

ESD protection exceeds 2000 V HBM per JESD22-A114,

200 V MM per JESD22-A115 and 1000 V CDM per JESD22-C101

DESCRIPTION

The CBT3257 is a quad 1-of-2 high-speed TTL-compatible

multiplexer/demultiplexer. The low on resistance of the switch allows

inputs to be connected to outputs without adding propagation delay

or generating additional ground bounce noise.

Output Enable (OE

appropriate B1 and B2 outputs for the A-input data.

The CBT3257 is characterized for operation from -40 to +85 °C.

) and select-control (S) inputs select the

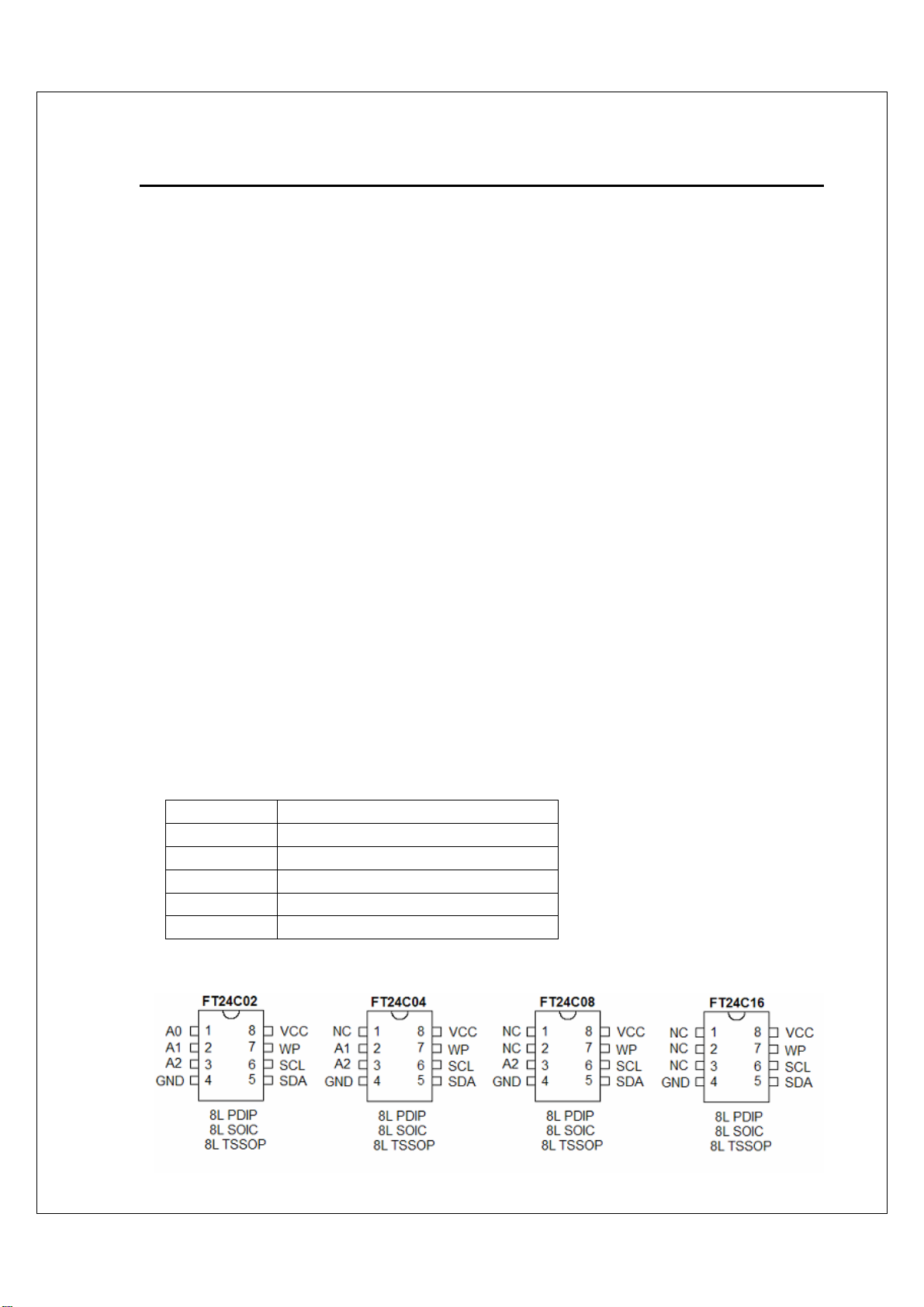

PIN CONFIGURATION

1

S

2

1B1

3

1B2

4

1A

5

2B1

6

2B2

7

2A

89

GND

16

15

14

13

12

11

10

SA00533

V

OE

4B1

4B2

4A

3B1

3B2

3A

CC

PIN DESCRIPTION

PIN NUMBER SYMBOL NAME AND FUNCTION

1 S Select-control input

2, 3,

5, 6,

10, 11,

13, 14

4, 7, 9, 12 1A, 2A, 3A, 4A A inputs

8 GND Ground (0 V)

15 OE Output enable

16 V

1B1, 1B2,

2B1, 2B2

3B1, 3B2

4B1, 4B2

CC

B outputs

Positive supply voltage

ORDERING INFORMATION

PACKAGES TEMPERATURE RANGE ORDER CODE TOPSIDE MARK DWG NUMBER

16-pin plastic SO -40 to 85 °C CBT3257D CBT3257D SOT109-1

16-pin plastic SSOP -40 to 85 °C CBT3257DB CT3257 SOT338-1

16-pin plastic SSOP (QSOP) -40 to 85 °C CBT3257DS CBT3257 SOT519-1

16-pin plastic TSSOP -40 to 85 °C CBT3257PW CBT3257 SOT403-1

Standard packing quantities and other packaging data is available at www.philipslogic.com/packaging.

Page 8

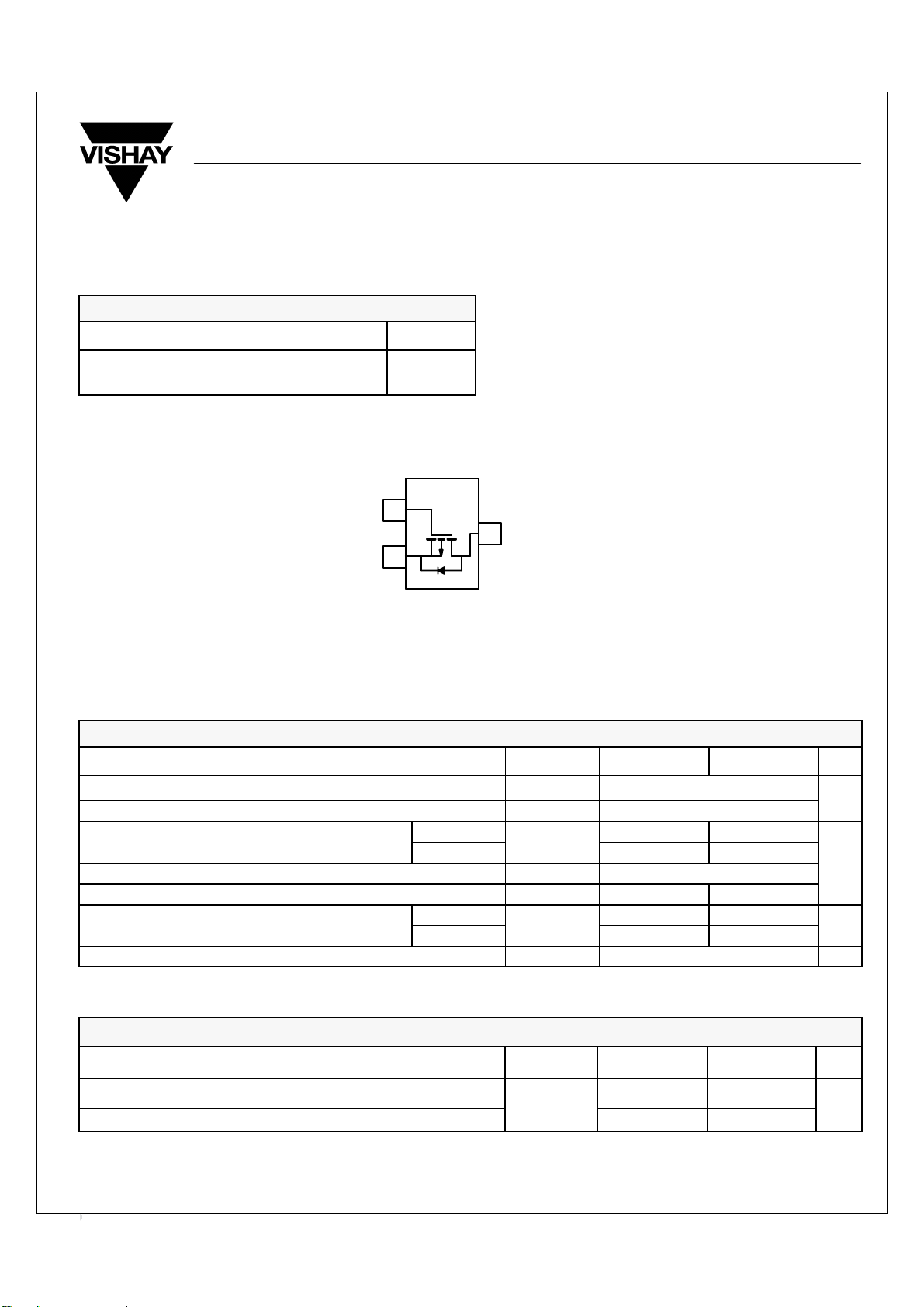

PRODUCT SUMMARY

V

b

b

VDS (V) r

-20

0.100 @ V

0.150 @ V

P-Channel 2.5-V (G-S) MOSFET

(W) ID (A)

DS(on)

= -4.5 V -2.4

GS

= -2.5 V -2.0

GS

G

1

S

2

b

TO-236

(SOT-23)

D

3

Ordering Information: Si2301BDS-T1

Si2301BDS

Vishay Siliconix

Top View

Si2301 BDS (L1)*

*Marking Code

ABSOLUTE MAXIMUM RATINGS (TA = 25_C UNLESS OTHERWISE NOTED)

Parameter Symbol 5 sec Steady State Unit

Drain-Source Voltage V

Gate-Source Voltage V

Continuous Drain Current (TJ = 150_C)

Pulsed Drain Current

Continuous Source Current (Diode Conduction)

Power Dissipation

Operating Junction and Storage Temperature Range TJ, T

a

_

b

TA= 25_C

TA= 70_C

TA= 25_C

TA= 70_C

DS

GS

I

D

I

DM

I

S

P

D

stg

-2.4 -2.2

-1.9 -1.8

-0.72 -0.6

0.9 0.7

0.57 0.45

-55 to 150 _C

THERMAL RESISTANCE RATINGS

-20

"8

-10

A

W

Parameter Symbol Typical Maximum Unit

Maximum Junction-to-Ambient

Maximum Junction-to-Ambient

Notes

a. Pulse width limited by maximum junction temperature.

b. Surface Mounted on FR4 Board, t v 5 sec.

c. Surface Mounted on FR4 Board.

b

R

c

thJA

120 145

140 175

_C/W

Page 9

5A Low Dropout Positive Adjustable or Fixed-Mode Regulator

Features

1.4V maximum dropout at full load current

•

•

Built-in thermal shutdown

•

Output current limiting

•

Adjustable output voltage or fixed 1.5V, 1.8V, 2.5V,

3.3V, 5.0V

•

Fast transient response

Good noise rejection

•

Package : TO252, TO263, TO220

•

General Description

AP1084 is a low dropout positive adjustable or fixedmode regulator with minimum of 5.0A output current

capability. The product is specifically designed to

provide well-regulated supply for low voltage IC

applications such as high-speed bus termination and

low current 3.3V logic supply. AP1084 is also well

suited for other applications such as VGA cards.

AP1084 is guaranteed to have lower than 1.4V

dropout at full load current making it ideal to provide

well-regulated outputs of 1.25 to 3.3V with 4.7 to

12V input supply.

Ordering Information

AP1084 X X X X

AP1084

Low Dropout Regulator Package Vout

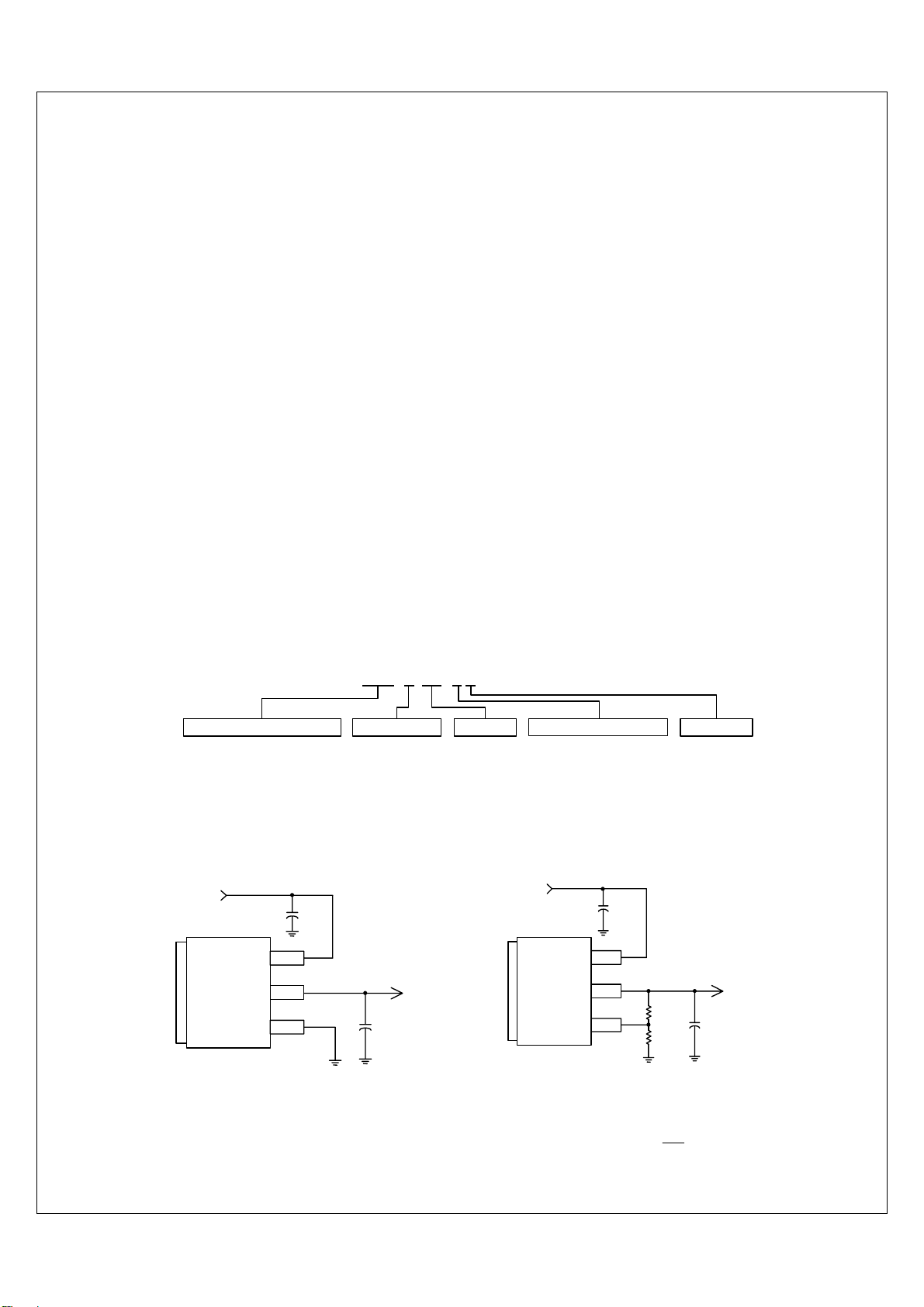

Typical Circuit

5.0V to 3.3V Fixed Mode Regulator

5V

Tab is Vout

Vin

Vout

GND

C1

100uF

D : TO252-3L

K : TO263-3L

T : TO220-3L

3.3V/5A

C2

100uF

Blank : Adj

15 = 1.5V

18 = 1.8V

25 = 2.5V

33 = 3.3V

50 = 5.0V

Lead Free

Blank : Normal

L : Lead Free Package

Adjustable Regulator

5V

Vin

Vout

Adj

Tab is Vout

C1

100uF

Note:

Packing

Blank : Tube

A : Taping

2.5V/5A

Ω

121

121

(1VV +∗=

C2

100uF

Ω

R

2

)

R

1

R1

R2

REFo

Page 10

1A Low Dropout Positive Adjustable or Fixed-Mode Regulator

Features

- 1.4V maximum dropout at full load current

- Fast transient response

- Output current limiting

- Built-in thermal shutdown

- Packages: SOT223, TO263, TO252, TO220,

SOT89

- Good noise rejection

- 3-Terminal Adjustable or Fixed 1.5V, 1.8V, 1.9V,

2.5V, 3.3V, 5.0V

Applications

- PC peripheral

- Communication

General Description

AP1117 is a low dropout positive adjustable or

fixed-mode regulator with minimum of 1A output

current capability. The product is specifically

designed to provide well-regulated supply for low

voltage IC applications such as high-speed bus

termination and low current 3.3V logic supply.

AP1117 is also well suited for other applications

such as VGA cards. AP1117 is guaranteed to have

lower than 1.4V dropout at full load current making

it ideal to provide well-regulated outputs of 1.25 to

5.0 with 6.4V to 12V input supply.

Ordering Information

AP 1117 X XX X X

AP1117

Low Dropout Regulator

Typical Circuit

5V

Tab is Vout

( 5V/3.3V fixed output )

Vin

Vout

GND

C1

100uF

Package Vout

E : SOT223-3L

K : TO263-3L

D : TO252-3L

T : TO220-3L

Y : SOT89-3L

C2

100uF

Blank : ADJ

15 : 1.5V

18 : 1.8V

19: 1.9V

25 : 2.5V

33 : 3.3V

50 : 5.0V

3.3V/1A

Lead Free

Blank : Normal

L : Lead Free Package

5V

Vout

Tab is Vout

C1

100uF

Vin

Adj

( 5V/2.5V ADJ output )

Note:

(1 VV +∗=

REFo

Blank : Tube

A : Taping

R1

121

Ω

R2

Ω

121

R

2

)

R

1

Packing

V

o

2.5V/1A

C2

100uF

Page 11

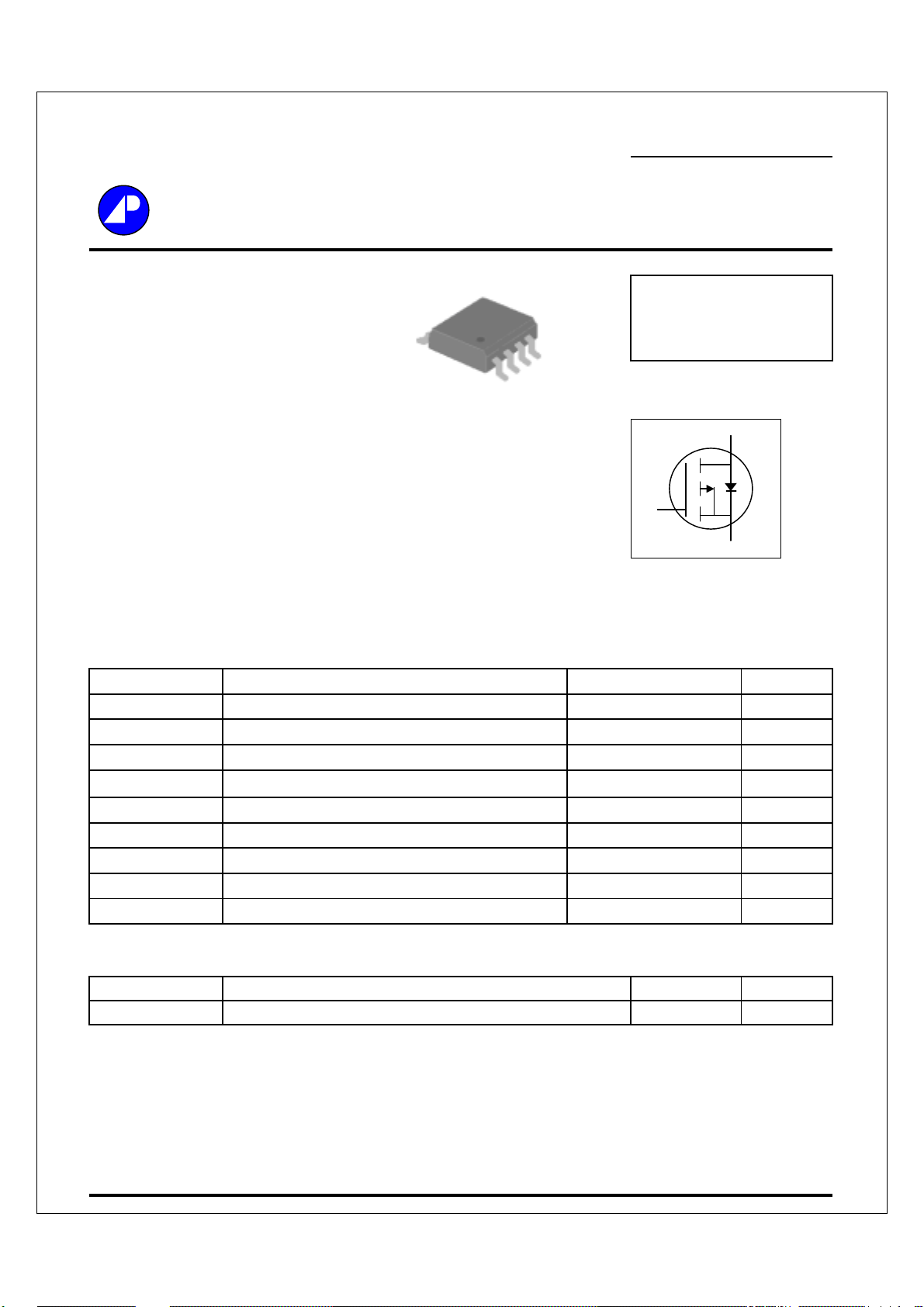

AP9435M

Advanced Power

Electronics Corp.

▼

▼ Simple Drive Requirement

▼ ▼

▼

▼ Low On-resistance

▼ ▼

▼

▼ Fast Switching

▼ ▼

D

D

D

SO-8

D

P-CHANNEL ENHANCEMENT MODE

POWER MOSFET

G

S

S

S

Description

The Advanced Power MOSFETs from APEC provide the

designer with the best combination of fast switching,

ruggedized device design, low on-resistance and cost-effectiveness.

The SO-8 package is universally preferred for all commercial-industrial

surface mount applications and suited for low voltage applications

such as DC/DC converters.

BV

R

DS(ON)

I

D

G

DSS

-30V

50mΩ

-5.3A

D

S

Absolute Maximum Ratings

Symbol Units

V

DS

V

GS

=25℃ A

I

D@TA

I

=70℃ A

D@TA

I

DM

PD@TA=25℃ W

Drain-Source Voltage

Gate-Source Voltage

Continuous Drain Current

Continuous Drain Current

Pulsed Drain Current

Total Power Dissipation 2.5

Linear Derating Factor 0.02

T

STG

T

J

Storage Temperature Range

Operating Junction Temperature Range -55 to 150

Parameter

3

3

1

Rating

-30

± 20

-5.3

-4.7

-20

-55 to 150

V

V

A

W/℃

℃

℃

Thermal Data

Symbol Value Unit

Rthj-amb Thermal Resistance Junction-ambient

Parameter

3

Max. 50 ℃/W

Page 12

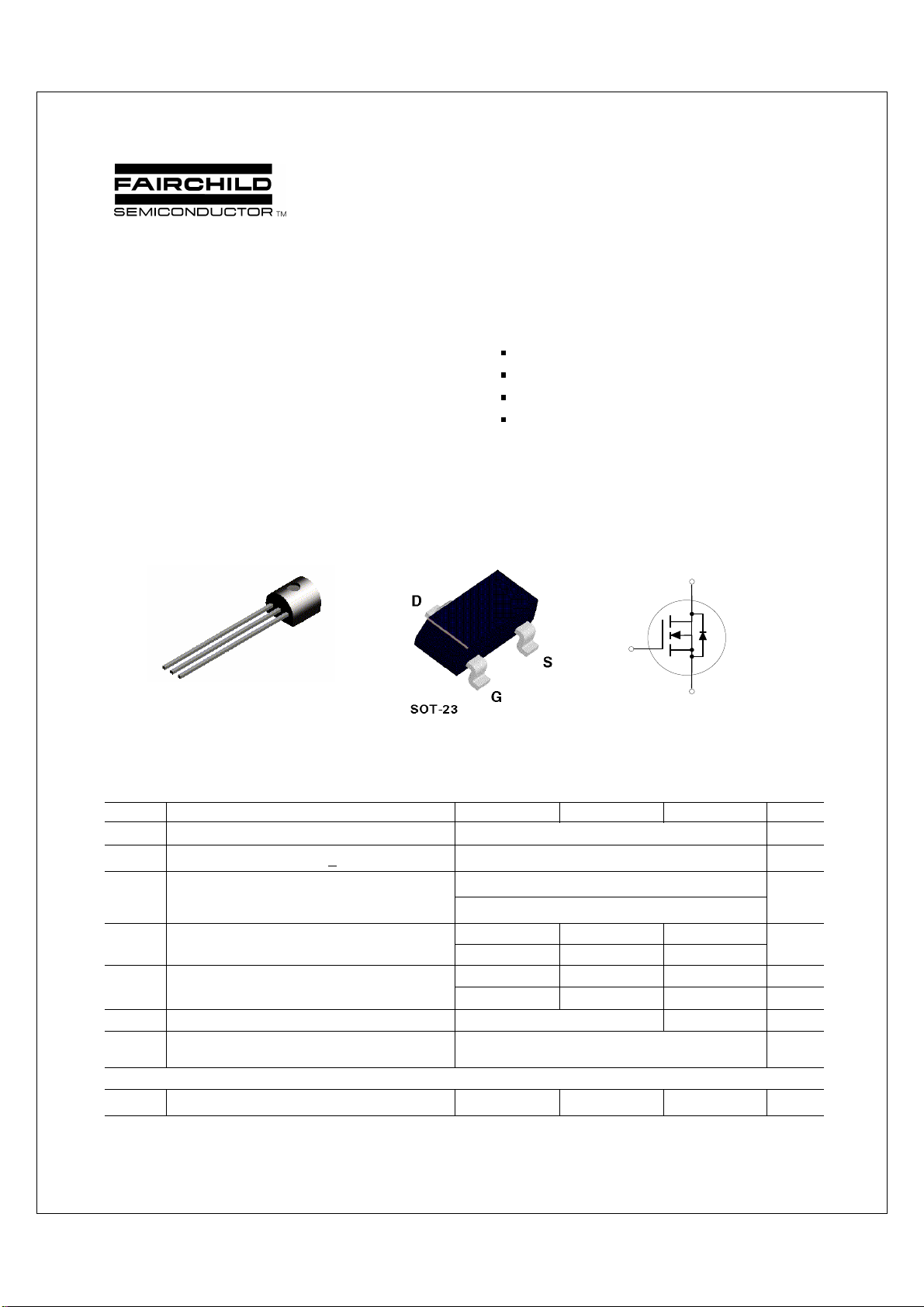

2N7000 / 2N7002 / NDS7002A

N-Channel Enhancement Mode Field Effect Transistor

General Description Features

November 1995

These N-Channel enhancement mode field effect transistors

are produced using Fairchild's proprietary, high cell density,

DMOS technology. These products have been designed to

minimize on-state resistance while provide rugged, reliable,

and fast switching performance. They can be used in most

applications requiring up to 400mA DC and can deliver

High density cell design for low R

Voltage controlled small signal switch.

Rugged and reliable.

High saturation current capability.

DS(ON)

.

pulsed currents up to 2A. These products are particularly

suited for low voltage, low current applications such as small

servo motor control, power MOSFET gate drivers, and other

switching applications.

___________________________________________________________________________________________

D

S

Units

V

G

S

TO-92

2N7000

D

Absolute Maximum Ratings

Symbol Parameter

V

DSS

V

DGR

V

GSS

I

D

P

D

T

J,TSTG

T

L

THERMAL CHARACTERISTICS

R

JA

θ

Drain-Source Voltage 60 V

Drain-Gate Voltage (RGS < 1 MΩ)

Gate-Source Voltage - Continuous

- Non Repetitive (tp < 50µs)

Maximum Drain Current - Continuous 200 115 280 mA

Maximum Power Dissipation 400 200 300 mW

Derated above 25oC 3.2 1.6 2.4 mW/°C

Operating and Storage Temperature Range -55 to 150 -65 to 150 °C

Maximum Lead Temperature for Soldering

Purposes, 1/16" from Case for 10 Seconds

Thermal Resistance, Junction-to-Ambient 312.5 625 417 °C/W

G

(TO-236AB)

2N7002/NDS7002A

TA = 25°C unless otherwise noted

2N7000 2N7002 NDS7002A

60 V

20

±

40

±

- Pulsed 500 800 1500

300 °C

Page 13

Philips Semiconductors Product specification

2 × 6 W stereo power amplifier TDA1517; TDA1517P

FEATURES

• Requires very few external components

• High output power

• Fixed gain

• Good ripple rejection

GENERAL DESCRIPTION

The TDA1517 is an integrated class-B dual output

amplifier in a plastic single in-line medium power package

with fin (SIL9MPF) and a plastic heat-dissipating dual

in-line package (HDIP18). The device is primarily

developed for multi-media applications.

• Mute/standby switch

• AC and DC short-circuit safe to ground and V

P

• Thermally protected

• Reverse polarity safe

• Capability to handle high energy on outputs (VP=0V)

• No switch-on/switch-off plop

• Electrostatic discharge protection.

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

P

I

ORM

I

q(tot)

I

sb

I

sw

|Z

| input impedance 50 −−kΩ

I

P

o

supply voltage 6.0 14.4 18.0 V

repetitive peak output current −−2.5 A

total quiescent current − 40 80 mA

standby current − 0.1 100 µA

switch-on current −−40 µA

output power RL=4Ω; THD = 0.5% − 5 − W

R

=4Ω; THD = 10% − 6 − W

L

SVRR supply voltage ripple rejection fi= 100 Hz to 10 kHz 48 −−dB

α

cs

G

v

V

no(rms)

T

c

channel separation 40 −−dB

closed loop voltage gain 19 20 21 dB

noise output voltage (RMS value) − 50 −µV

crystal temperature −−150 °C

ORDERING INFORMATION

TYPE

NUMBER

NAME DESCRIPTION VERSION

PACKAGE

TDA1517 SIL9MPF plastic single in-line medium power package with fin; 9 leads SOT110-1

TDA1517P HDIP18 plastic heat-dissipating dual in-line package; 18 leads SOT398-1

Page 14

Philips Semiconductors Product specification

2 × 6 W stereo power amplifier TDA1517; TDA1517P

PINNING

SYMBOL PIN DESCRIPTION

−INV1 1 non-inverting input 1

SGND 2 signal ground

SVRR 3 supply voltage ripple rejection output

OUT1 4 output 1

PGND 5 power ground

OUT2 6 output 2

V

P

M/SS 8 mute/standby switch input

−INV2 9 non-inverting input 2

7 supply voltage

dbook, halfpage

INV1

SGND

SVRR

OUT1

PGND

OUT2

V

M/SS

INV2

1

2

3

4

TDA1517

5

6

7

P

8

9

MLC352

Fig.2 Pin configuration for SOT110-1.

FUNCTIONAL DESCRIPTION

The TDA1517 contains two identical amplifiers with

differential input stages. The gain of each amplifier isfixed

at 20 dB. A special feature of the device is the

mute/standby switch which has the following features:

• Low standby current (<100 µA)

• Low mute/standby switching current

• Mute condition.

(low cost supply switch)

dbook, halfpage

Pins 10 to 18 should be connected to GND or floating.

INV1

SGND

SVRR

OUT1

PGND

OUT2

V

M/SS

INV2

1

2

3

4

TDA1517P

5

6

7

P

8

9

18

17

16

15

14

13

12

11

10

MLC353

Fig.3 Pin configuration for SOT398-1.

Page 15

Fremont Micro Devices, Inc.

FEATURES

Low voltage and low power operati ons:

• FT24C02/04/08/16: V

• FT24C02A/04A/08A/16A: VCC = 1.8V to 5.5V

Maximum Standby current < 1µA (typically 0.02µA and 0.06µA @ 1.8V and 5.5V respectively).

16 bytes page write mode.

Partial page write operation allowed.

Internally organized: 256 × 8 (2K), 512 × 8 (4K), 1024 × 8 (8K), 2048 × 8 (16K).

Standard 2-wire bi-directional serial interface.

Schmitt trigger, filtered inputs for noise protection.

Self-timed programming cycle (5ms maximum).

Automatic erase before write operation.

Write protect pin for hardware data protection.

High reliability: typically 800,000 cycles endurance.

100 years data retention.

Industrial temperature range (-40o C to 85o C).

Standard 8-pin PDIP/SOIC/TSSOP Pb-free packages.

CC

FT24C02 / 04 / 08 / 16

FT24C02A / 04A / 08A / 16A

= 2.5V to 5.5V

and

DESCRIPTION

The FT24C02/04/08/16 series are 2048/4096/8192/16384 bits of serial Electrical Erasable and

Programmable Read Only Memory, commonly known as EEPROM. They are organized as

256/512/1024/2048 words of 8 bits (1 byte) each. The devices are fabricated with proprietary

advanced CMOS process for low power and low voltage applications. These devices are available in

standard 8-lead PDIP, 8-lead JEDEC SOIC and 8-lead TSSOP packages. A standard 2-wire serial

interface is used to address all read and write functions. Our extended V

devices enables wide spectrum of applications.

range (1.8V to 5.5V)

CC

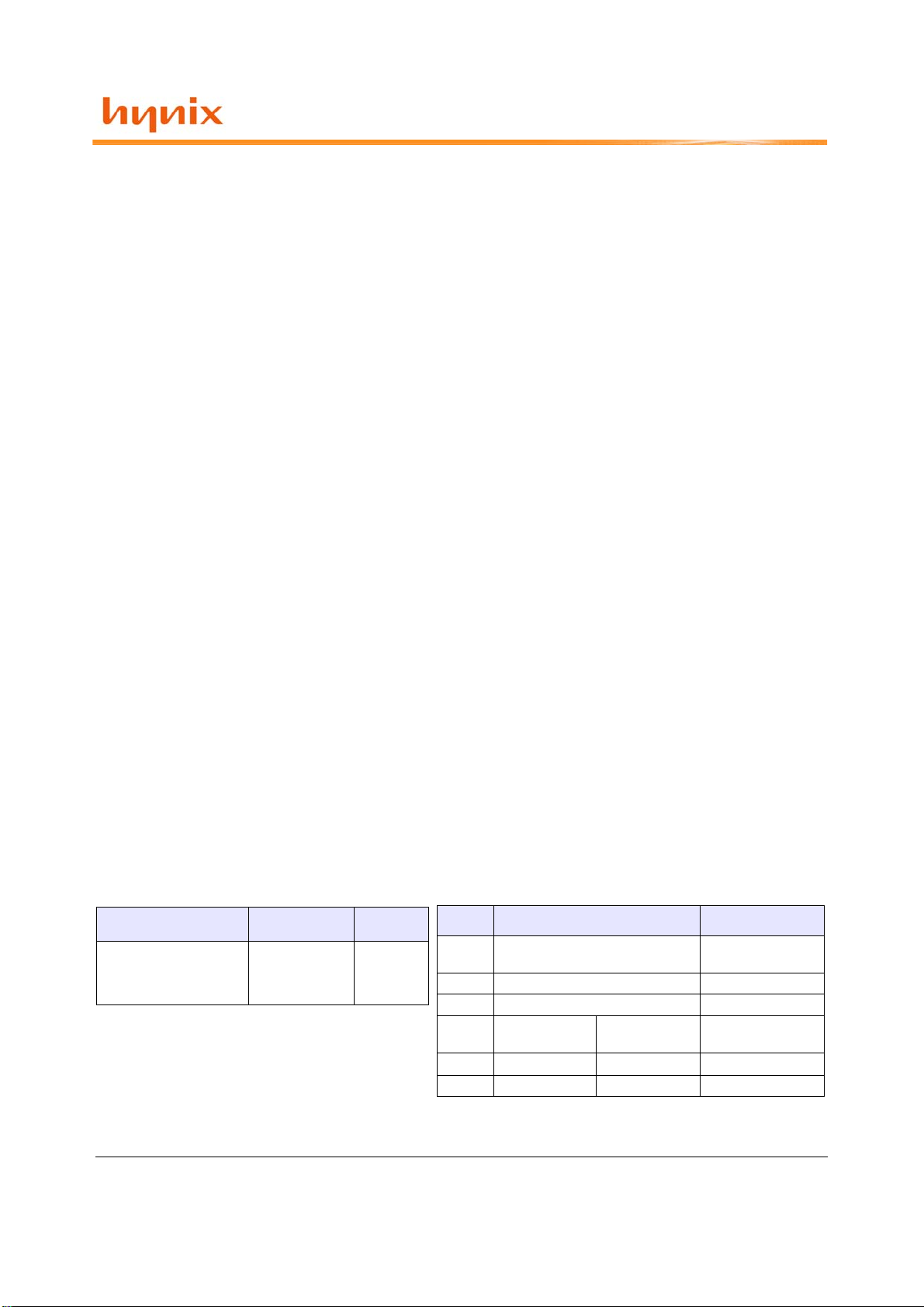

PIN CONFIGURATION

Pin Name Pin Function

A2, A1, A0 Device Address Inputs

SDA Serial Data Input / Open Drain Output

SCL Serial Clock Input

WP Write Protect

NC No-Connect

All three packaging types come in conventional or Pb-free certified.

Page 16

HY5DU281622FT(P) Series

DESCRIPTION

The HY5DU281622FT(P) is a 134,217,728-bit CMOS Double Data R ate (D DR) Synchronous DRAM, ideally suited for the

main memory applications which requires large memory density and high bandwidth.

This Hynix 128Mb DDR SDRAMs offer fully synchronous operations referenced to both rising and falling edges of the

clock. While all addresses and control inputs are latched on the rising edges of the CK (fal ling edges of the /CK), Data,

Data strobes and Write data masks inputs are sampled on both rising and falling edges of it. The data paths are internally pipelined and 2-bit prefetched to achieve very high ban dwid th. All inp ut a nd output voltage levels are compatible

with SSTL_2.

FEATURES

•VDD, V

DDQ

= 2.3V

min

~ 2.7V

max

(Typical 2.5V Operation +/- 0.2V for DDR266, 333)

•VDD, V

DDQ

= 2.4V

min

~ 2.7V

max

(Typical 2.6V Operation +0.1/- 0.2V for DDR400

and 400Mbps/pin product)

• All inputs and outputs are compatible with SSTL_2

interface

• Fully differential clock inputs (CK, /CK) operation

• Double data rate interface

• Source synchronous - data transaction aligned to

bidirectional data strobe (DQS)

• x16 device has two bytewide data strobes (UDQS,

LDQS) per each x8 I/O

• Data outputs on DQS edges when read (edged DQ)

Data inputs on DQS centers when write (centered

DQ)

• On chip DLL align DQ and DQS transition with CK

transition

• DM mask write data-in at the both rising and falling

edges of the data strobe

• All addresses and control inputs except data, data

strobes and data masks latched on the rising edges

of the clock

• Programmable CAS latency 2/2.5 (DDR266, 333)

and 3 (DDR400 and 400Mbps/pin product) supported

• Programmable burst length 2/4/8 with both sequential and interleave mode

• Internal four bank operations with single pulsed

/RAS

• Auto refresh and self refresh supported

lock out function supported

RAS

•t

• 4096 refresh cycles/64ms

• JEDEC standard 400mil 66pin TSOP-II with 0.65mm

pin pitch

• Lead free (*ROHS Compliant)

ORDERING INFORMATION

Part No. Configuration Package

400mil

HY5DU281622F(L)TP-X* 8Mx16

* X means speed grade

** Lead-free product

*ROHS (Restriction Of Hazardous Substances)

Rev. 0.03 /Jun. 2006 3

66pin

TSOP-II**

OPERATING FREQUENCY

Grade Clock Rate Remark

-5 200MHz@CL3

-D43 200MHz@CL3 DDR400B (3-3-3)

-D4 200MHz@CL3 DDR400 (3-4-4)

- J 133MHz@CL2

- K 133MHz@CL2 133MHz@CL2.5 DDR266A (2-3-3)

- H 100MHz@CL2 133MHz@CL2.5 DDR266B (2.5-3-3)

166MHz @CL2.5

& @CL3

400Mbps/pin (maxi-

mum Date rate)

DDR333 (2.5-3-3)

DDR333 (3-3-3)

Page 17

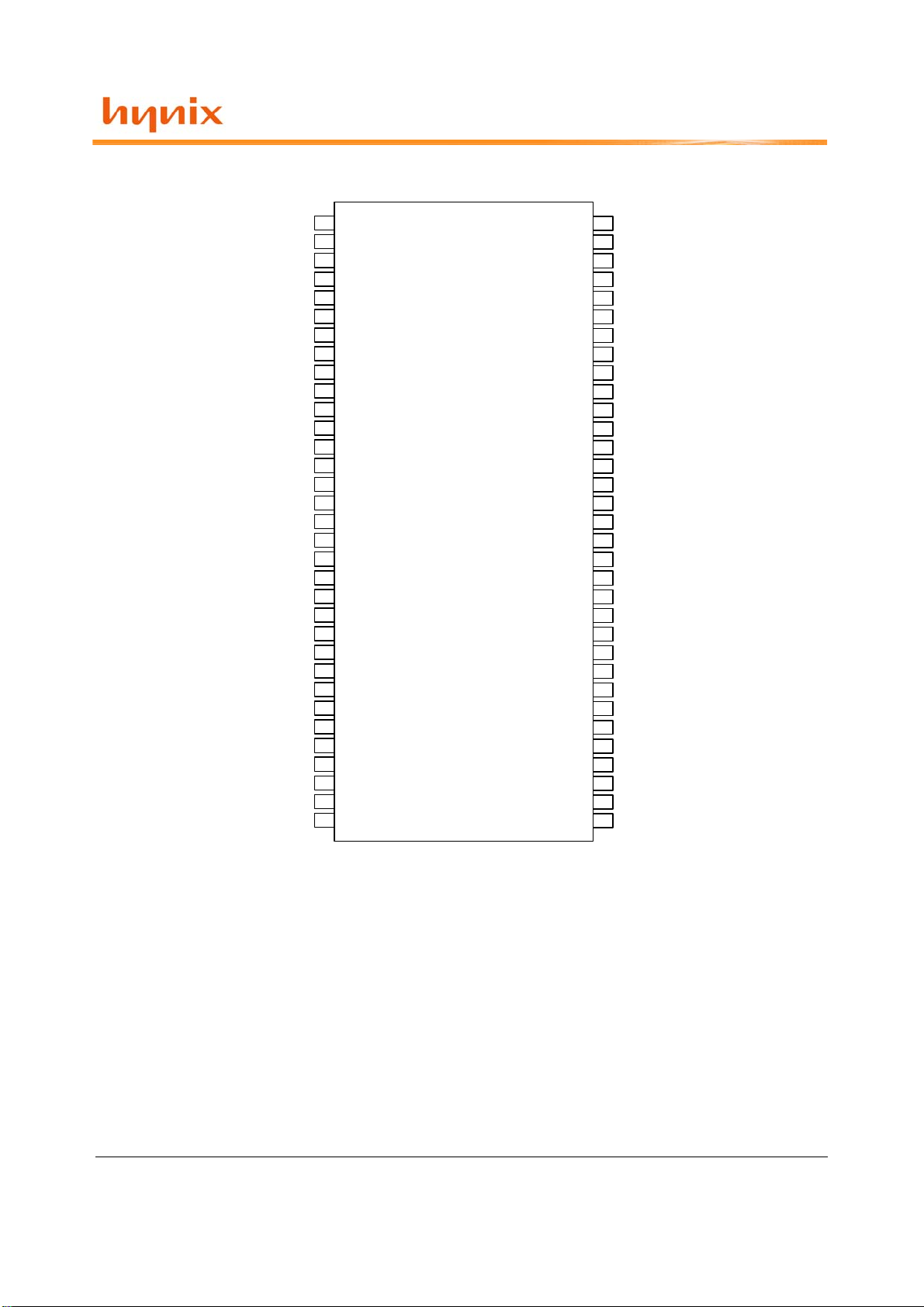

PIN CONFIGURATION

HY5DU281622FT(P) Series

V

DD

DQ0

V

DDQ

DQ1

DQ2

V

SSQ

DQ3

DQ4

V

DDQ

DQ5

DQ6

V

SSQ

DQ7

NC

V

DDQ

LDQ S

NC

V

DD

NC

LDM

/W E

/CAS

/RA S

/CS

NC

BA0

BA1

A10/AP

A0

A1

A2

A3

DD

V

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

1

2

3

4

5

6

7

8

9

400mil x 875m il

66pin TSOP-II

0.65mm pin pitch

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

V

SS

DQ15

V

SSQ

DQ14

DQ13

V

DDQ

DQ12

DQ11

V

SSQ

DQ10

DQ9

V

DDQ

DQ8

NC

V

SSQ

UDQS

NC

VREF

V

SS

UDM

/CK

CK

CKE

NC

NC

A11

A9

A8

A7

A6

A5

A4

SS

V

ROW AND COLUMN ADDRESS INFORMATION

• Organization : 2M x 16 x 4banks

• Row Address : A0 - A11

• Column Address : A0 - A8

• Bank Address : BA0, BA1

• Auto Precharge Flag : A10

• Refresh : 4K

Rev. 0.03 /Jun. 2006 4

Page 18

SHENZHEN TENA

ELECTRONICS CO., LTD.

PRODUCT

SPECIFICATION

MODEL

TNDT1A1200F

DESCRIPTION

DVB-T

PAGE

1

TNDT1A1200F

TNDT1A2200F

FOR DIGITAL TERRESTRIAL RECEPTION

A Original Release

REV DESCRIPTION DATE SIGN

CUSTOMER APPROVAL

DESCRIPTION

EUROPEAN DIGITAL

TERRESTRIAL STANDARD

DRAWING NO

REVISIONS

1.0

PAGES TOTAL

17

APPROVAL CHECK DESIGN

DATE DATE DATE

2008-10-16

Page 19

SHENZHEN TENA

ELECTRONICS CO., LTD.

PRODUCT

SPECIFICATION

MODEL

TNDT1A1200F

DESCRIPTION

DVB-T

PAGE

2

NO SPECIFICATION

1

FEATURES

1. +5V supply voltage only; no external tuning voltage required.

2. Tuners for horizontal and vertical mounting available.

3. Option with DC-power output through input connector (e. g. indoor antenna supply)

4. Tuners comply with relevant CENELEC standards with regard to requirements concerning signal

handling capability and immunity

5. Superior low noise and high sensitivity performance

6. RF-in to RF-out loopthrough amplifiers

7. low noise and excellent linearity

8. VHF high to UHF frequency range coverage

9. Standard connectors for in-and output e. g. IEC, F-connector. RCA

10. full UHF /VHF-H frequency coverage

11. Pattem generator included

2

12. I

C programmable

13. 400KHz Bus compliant

14. Stand-by mode addressable

15. High performance and cost effective single conversion tuner

2

16. I

C programmable

17. 400KHz Bus compliant

18. Fast PLL tuning speed (programmable step size e.g.62.5KHz and 166.67KHz)

19. Flat overall frequency response

20. High PLL loop bandwidth which ensures very low oscillator phase noise

21. SAW-filter and IF-amplifier included

a) Switchable 7/8 MHz SAW filter (full band tuners)

b) Fixed 8 MHz SAW filter (UHF only tuners)

c) IF-amplification controllable over a wide range

22. Differential, filtered (SAW)‘digital’ IF-output to directly drive the channel decoder

Page 20

Philips Semiconductors Product specification

Dual 4-channel analog multiplexer,

demultiplexer

FEATURES

• Wide analog input voltage range from −5 V to +5 V

• Low ON-resistance:

–80Ω (typical) at VCC− VEE= 4.5 V

–70Ω (typical) at VCC− VEE= 6.0 V

–60Ω (typical) at VCC− VEE= 9.0 V

• Logic level translation: to enable 5 V logic to

communicate with ±5 V analog signals

• Typical “break before make” built in

• Complies with JEDEC standard no. 7A

• ESD protection:

– HBM EIA/JESD22-A114-B exceeds 2000 V

– MM EIA/JESD22-A115-A exceeds 200 V.

• Specified from −40 °C to +85 °C and −40 °C to+125 °C.

APPLICATIONS

• Analog multiplexing and demultiplexing

• Digital multiplexing and demultiplexing

• Signal gating.

74HC4052; 74HCT4052

DESCRIPTION

The 74HC4052 and 74HCT4052 are high-speed Si-gate

CMOS devices and are pin compatible with the

HEF4052B. They are specified in compliance with JEDEC

standard no. 7A.

The 74HC4052 and 74HCT4052 are dual 4-channel

analog multiplexers or demultiplexerswith common select

logic. Each multiplexer has four independent

inputs/outputs (pins nY0 to nY3) and a common

input/output (pin nZ). The common channel select logics

include two digital select inputs (pins S0 and S1) and an

active LOW enable input (pin E). When pin E = LOW, one

of the four switches is selected (low-impedance ON-state)

with pins S0 and S1. When pin E = HIGH, all switches are

in the high-impedance OFF-state, independent of pins S0

and S1.

VCC and GND are the supply voltage pins for the digital

control inputs (pins S0, S1, and E). The VCC to GND

ranges are 2.0 V to 10.0 V for 74HC4052 and

4.5 V to 5.5 V for 74HCT4052. The analog inputs/outputs

(pins nY0 to nY3 and nZ) can swing between VCC as a

positive limit and VEE as a negative limit. VCC− VEE may

not exceed 10.0 V.

FUNCTION TABLE

ES1S0

L L L nY0 and nZ

L L H nY1 and nZ

L H L nY2 and nZ

L H H nY3 and nZ

H X X none

Note

1. H = HIGH voltage level

L = LOW voltage level

X = don’t care.

INPUT

For operation as a digital multiplexer/demultiplexer, VEEis

connected to GND (typically ground).

(1)

CHANNEL BETWEEN

Page 21

HIGHLY INTEGRATED LCD TV PROCESSOR

1. GENERAL DESCRIPTION

PPrreelliimmiinnaarry

SPV7100A

y

The SPV7100A is a highly integrated solution for the mainstream

LCD TV applications. The SPV7100A provides on-chip functions

including a high-speed triple-ADC and PLL, HDMI PanelLink

Cinema receiver, TV decoder with 3-D comb filter, 4-pair Audio

Line-In, 2-pair Audio Line-Out, one SIF demodulator and audio

decoder, 3D motion adaptive de-interlacing, 2:2/3:2 film mode

detection, video on graphic PIP/POP, SDRAM/DDR controller,

color management control, sRGB color management,

bitmap-based and font-based OSD engine, embedded CPU and a

dual channels LVDS transmitter. The chip could support LCD TV

up to 1080P input resolution and 1080p output resolution.

Note: PanelLink is the Trade Mark of Silicon Image Inc.

2. FEATURES

2.1. Graphics and Video Input Port

Integrate 150MHz 10-bit ADC/PLL

Dual CCIR656 digital video ports to support 2 input or 1 input/1

output

Support SDTV at 480i/576i and 480p/576p

Support HDTV at 720p and 1080i and1080p

Support PC graphics VGA, SVGA, XGA, WXGA, SXGA@75Hz

(135MHz)

Build-in sync. processor for separate, composite or sync on

Y/G

Support Video/Graphics PIP/DW

Channel swap for any source input

Image Format Detection/Auto Image Positioning/Auto Phase

Detection

Full SCART support including RGB fast blank

2.2. HDMI

HDMI 1.2 compliant and DVI 1.0 compliant receiver

HDCP 1.1 compliant receiver

Support DTV resolutions

(480i/576i/480p/576p/720p/1080i/1080p)

S/PDIF output supports PCM, Dolby Digital, DTS digital audio

with bypass mode

Four I2S audio outputs to SSD(Stereo Sound Decoder) with

bypass mode

Auto audio error detection with programmable soft mute

Build-in OTP for HDCP key

2.3. 3D Video Decoder

NTSC/PAL/SECAM video decoder

TM

3D comb filter for NTSC, PAL I (B,G,H,D,N), PAL-M, PAL-N

Enhanced NTSC/PAL/SECAM auto detection

4 analog inputs and one analog video output

Cross-color reduction for NTSC by 3-line comb filtering

Cross-color reduction for PAL by 5-line comb filtering

Motion adaptive 3D Y/C separation comb filter for NTSC/PAL

system

Multi-standard VBI data decoder, Teletext 2.5, WSS, VPS,

Closed-caption and V-chip

Macrovision detection

VBI data (C.C, TTX2.5, V-chip) overlay display

2.4. High Quality Video Processing

Enhanced Pixel-based 3D motion adaptive de-interlacing

(SDTV/HDTV)

Enhanced 2:2/3:2 film mode detection

Support Graphics mode frame rate conversion

Support Video mode frame rate conversion

2D Edge enhancement

Dynamic Peaking Filter

Enhanced Digital Luminance Transient Improvement (DLTI)

Digital Color Transient Improvement (DCTI)

Black/White Level Expansion and Dynamic Contrast

RGBYMC color adjustment

Dark and Gray area UV Suppression

Enhanced 3D motion adaptive noise reduction

De-blocking and de-mosquito filters

Color management/Color temperature adjustment

Brightness/Contrast/hue/Saturation adjustment

Support sRGB color correction

Build-in three 256-point gamma tables with 10 bits resolution

Color space conversion, both YCbCr to RGB and RGB to

YCbCr

Build-in temporal/spatial color dithering

10-bit video/image processing

2.5. High Quality Video Scaling Engine

Advanced third-generation scaling engine

Support 4:3 / 16:9 with non-linear scaling

Support Moiré Canceling

Page 22

2.6. Multi-standard TV Sound Decoder

Field proven TV sound decoder

Support BTSC, A2/Zweiton, NICAM, EIAJ, SECAM, FM stereo

Automatic TV-standard detection (ASD)

Non-standard carrier compatible

SAP decoding where applicable

Auto fallback from NICAM where applicable

2.7. Embedded OSD and VBI Controller

Build-in programmable OSD engine for two OSD windows (bit

map OSD)

1,2,4 and 8-bit per pixel (bit-map OSD)

Support hardware cursor

Support programmable 512 font-based OSD and

graphics-based OSD

Support VBI decoder (CC,V-Chip and Teletext)

Support VBI CC/TTX/Menu with more than 1000 char-fonts

2.8. Embedded DDR/SDRAM Controller

Integrated DDR/SDRAM controller with DLL (DDR)

Support 32-bit DRAM bus with memory size from 16Mb (limited

functions) to 256Mb

2.9. Programmable Digital Output for LCD

Support output sequence mapping for TI and Thine

Build-in dual channels 8-bit LVDS Tx or single channel 10-bit

LVD S Tx

Support display output up to 1920x1200 @60Hz (165Mhz

WUXGA reduced blanking)

Support Power Down Sequence

4-ch PWM backlight intensity control

2.10. CPU

Powerful 32-bit RISC CPU

Simple memory management stub (SMMU)

MIPS-I instruction with DSP instruction set extension

2K bytes 2-way instruction cache

4K bytes direct-mapped data cache

8K bytes data memory for DMA operation

EJTAG interface

One UART up to 115200 baud rate

Four 24-bit up/down timers

3K Bytes IMem for power saving mode

2.11. Audio Processor

Support SPDIF input

Support SPDIF output (signal could come from SPDIF input or

SSD)

Support up to 8 channels I2S I/O

4 channels audio DAC output

4 channels audio ADC input

Channel: L, R, C, S, Sub, Aux1, 2 and 3 @ 32 kHz

5- band Equalizer

3-D surround sound

Bass management

Volume control

Support sub-woofer output

Sample rate conversion

SSD could output up to 3 sources

Virtual Dolby Surround (VDSII 422 and 423) (support by

SPV7100AxD)

SRS TruSurround (XT, WOW, 3D Sound) (support by SPV7100

AxS)

2.12. Misc

Build-in TV remote control 1 infra-red receiver interface

2-channels 6-bits ADC for key scan function

Build-in pattern generator for auto testing

256-pin LQFP for LCD application

PPrreelliimmiinnaarry

SPV7100A

y

© Sunplus Technology Co., Ltd.

Proprietary & Confidential

5 MAR. 23, 2007

Preliminary Version: 0.1

Page 23

4.3. List of Packages and Pins

4.3. List of Packages and Pins

4.3.1. 256- LQFP Package

4.3.1. 256- LQFP Package

SPV7100A

SPV7100A

Figure 4-1 SPV7100A Pin Configuration

Figure 4-1 SPV7100A Pin Configuration

Page 24

V1.5

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1389L

5 Function

5-1 General Description

MediaTek MT1389L is a cost-effective DVD system-on-chip (SOC) which incorporates advanced features like

MPEG-4 video decoder, high quality TV encoder and state-of-art de-interlace processing. The MT1389L enables

consumer electronics manufacturers to build high quality, USB2.0, MS/SD/MMC reader, feature-rich DVD players,

portable DVD players or any other home entertainment audio/video devices.

World-Leading Technology: Based on MediaTek’s world-leading DVD player SOC architecture, the

MT1389L is the New generation of the DVD player SOC. It integrates the MediaTek 3

RF amplifier and the Servo/MPEG AV decoder.

Rich Feature for High Valued Product: To enrich the feature of DVD player, the MT1389 equips a

simplified MPEG-4 advanced simple profile (ASP) video decoder to fully support the DivX

makes the MT1389-based DVD player be capable of playback MPEG-4 content which become more and more

popular.

Incredible Audio/Video Quality: The progressive scan of the MT1389L utilized advanced motion-adaptive

de-interlace algorithm to achieve the best movie/video playback. It also supports a 3:2 pull down algorithm to give

the best film effect. The 108MHz/12-bit video DAC provides users a whole new viewing experience. Built-in 6ch

audio DACs and 2ch audio ADCs could give the variable function solutions.

High Performance Memory Storage Device: As the core of Portable DVD players need more capability to

support current multimedia contents. The MT1389L provides the interface for the 3-in-1 card reader, which

supports Memory-Stick, Secure Digital Memory Card, and MultiMediaCard, to connect with the mainstream digital

camera FLASH cards. For the USB application, we adopt USB2.0 High speed specification to reach rich-contents

transference. USB 2.0 High speed will support for high-speed devices. USB 2.0 High Speed is suitable for

high-performance devices such as high-density storage devices. In addition, USB 2.0 High Speed supports old

USB 1.0/1.1 software and peripherals, offering impressive and even better compatibility to customers

rd

generation front-end digital

1

Home Theater profile. It

Key Features

DVD

PUH

Module

FLASH

MT1389L

Desktop

CVBS, Y/C,

Component

SDPIF

Analog

Audio

Output

USB 2.0

High Speed

Front-panel

Remote

DRAM

DVD Player System Diagram Using MT1389L

1

DivX is a trademark of DivXNetworks

2

USB High Speed : 480Mbit/sec. USB Full Speed : 12Mbit/sec.

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

4

RF/Servo/MPEG Integration

DivX Home Theater Level MPEG4 ASP Video decoder

Support Nero-Digital

Support DivX Ultra

High Performance Audio Processor

Progressive Scan

108MHz/12-bit, 4 CH TV Encoder

Internal 6CH Audio DAC

Internal 2CH Audio ADC

USB2.0 High Speed (Host/Device)

3-in-1 MS/SD/MMC reader

Applications

Standard DVD Players

Page 25

V1.5

GPIO13

AudioAudioVid

DAC

ADC

DAC

_

DVDD18

INT RF

GPIO9

XTAL I

GPIO8

XTALO

GPIO7 / CKE

V20

V14

REXT

USB

DVSS18

_

_

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

6 Pin Assignment

AKIN1 / GPIO21 / Audio_mute

AKIN2 / GPIO19 / Audio_mute

ALF / CENTER / GPIO

RFH / OPINN /

RFIN / OPOUT /

RFG / OPINP /

128

127

126

1 96 VREF

RFA

2 95 DACVDDC

RFB

3 94

RFC

4

RFD

5

RFE

6 91 GPIO10

RFF

7 90

2

AVDD18

AVDD33_1

AGND33

AVDD33_2

TRAY

TRAY

FG / GPIO2 26 71 R A7

USB_DP 27 70 R A8

USB_DM 28 69 RA9

VDD33_USB 29 68 DVDD33

VSS33_USB 30 67 RA11

PAD_VRT 31 66 RCLK

VDD18_USB 32 65 DQM1

8

9 88

10 87

11 86 RA3

12 85 RA2

13 84 DVDD33

14 83 RA1

15 82 RA0

MDI1

16 81 RA10

MDI2

17 80 BA1

LDO1

18

LDO2

19 78 BA0

20 77 RAS#

DMO

21 76 CAS#

FMO

22 75 RW E#

OPEN

23 74 RA4

CLOSE

24 73 RA5

TRO

25 72 RA6

FOO

33343536373839404142434445464748495051525354555657585960616263

GPIO3 / INT#

GPIO4

GPIO6

RFIP

125

SF_CS_

AVDD18_1

AGND18

124

123

SF_DO

SF_DI

ADACVDD2

ADACVDD1

122

121

SF_CK

UP1_6 / SCL

120

UP1_7 / SDA

ALS / GPIO

119

ICE

AL / GPIO1

118

PRST#IRRD0

ARF / LFE / GPIO

ARS / GPIO

ADACVSS1

115

114

ADACVSS2

113

112

APLLCAP

111

AR / GPIO0

AVCM

117

116

MT1389L

Desktop

RD1

RD2

RD3

RD4

DVDD33

APLLVDD

110

RD5

AADVDD

109

RD6

108

RD7

ADVCM / GPIO20 /

107

DVDD18

106

DQM0

AADVSS

R

105

104

RD15

RD14

B

103

RD13

G

102

RD12

eo

DACVDDA

101

DVSS33

DACVDDB

100

RD11

DACVSSC

CVBS

FS

999897

93 SPDIF / GPIO12

92 GPIO11

89

79

64

RD10

RD9

RD8

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

20

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 26

EN25B16

EN25B16

16 Mbit Serial Flash Memory with Boot and Parameter Sectors

FEATURES

x Single power supply operation

- Full voltage range: 2.7-3.6 volt

x 16 M-bit Serial Flash

- 16 M-bit/2048 K-byte/8192 pages

- 256 bytes per programmable page

x High performance

- 75MHz clock rate

x Low power consumption

- 5 mA typical active current

- 1 PA typical power down current

x Flexible Sector Architecture:

- Two 4-Kbyte, one 8-Kbyte, one 16-Kbyte,one

32-Kbyte, and thirty one 64-Kbyte sectors

x Software and Hardware Write Protection:

- Write Protect all or portion of memory via

software

- Enable/Disable protection with WP# pin

x High performance program/erase speed

- Byte program time: 7μs typical

- Page program time: 1.5ms typical

- Sector erase time: 300 to 800ms typical

- Chip erase time: 18 Seconds typical

x Minimum 100K endurance cycle

x Package Options

- 8 pins SOP 200mil body width

- 8 contact VDFN

- 16 pin SOP 300mil body width

- All Pb-free packages are RoHS compliant

x Commercial and industrial temperature

Range

GENERAL DESCRIPTION

The EN25B16 is a 16M-bit (2048K-byte) Serial Flash memory, with advanced write protection

mechanisms, accessed by a high speed SPI-compatible bus. The memory can be programmed 1 to

256 bytes at a time, using the Page Program instruction.

The EN25B16 has thirty six sectors including thirty one sectors of 64KB, one sector of 32KB, one sector

of 16KB, one sector of 8KB and two sectors of 4KB. This device is designed to allow either single Sector

at a time or full chip erase operation. The EN25B16 can protect boot code stored in the small sectors for

either bottom or top boot configurations. The device can sustain a minimum of 100K program/erase cycles

on each sector.

This Data Sheet may be revised by subsequent versions ©2004 Eon Silicon Solution, Inc., www.essi.com.tw

or modifications due to changes in technical specifications.

Rev. C, Issue Date: 2006/12/22

1

Page 27

Figure.1 CONNECTION DIAGRAMS

ʳ

EN25B16

8 - LEAD SOP

8 - CONTACT VDFN

16 - LEAD SOP

This Data Sheet may be revised by subsequent versions ©2004 Eon Silicon Solution, Inc., www.essi.com.tw

or modifications due to changes in technical specifications.

Rev. C, Issue Date: 2006/12/22

2

Page 28

Figure 2. BLOCK DIAGRAM

EN25B16

This Data Sheet may be revised by subsequent versions ©2004 Eon Silicon Solution, Inc., www.essi.com.tw

or modifications due to changes in technical specifications.

Rev. C, Issue Date: 2006/12/22

3

Page 29

SDRAM 64Mb H-die (x4, x8, x16)

CMOS SDRAM

4M x 4Bit x 4 / 2M x 8Bit x 4 / 1M x 16Bit x 4 Banks SDRAM

FEATURES

• JEDEC standard 3.3V power supply

• LVTTL compatible with multiplexed address

• Four banks operation

• MRS cycle with address key programs

-. CAS latency (2 & 3)

-. Burst length (1, 2, 4, 8 & Full page)

-. Burst type (Sequential & Interleave)

• All inputs are sampled at the positive going edge of the system clock

• Burst read single-bit write operation

• DQM (x4,x8) & L(U)DQM (x16) for masking

• Auto & self refresh

• 64ms refresh period (4K cycle)

GENERAL DESCRIPTION

The K4S640432H / K4S640832H / K4S641632H is 67,108,864 bits synchronous high data rate Dynamic RAM organized as 4 x

4,194,304 words by 4 bits, / 4 x 2,097,152 words by 8 bits, / 4 x 1,048,576 words by 16 bits, fabricated with SAMSUNGcs high performance CMOS technology. Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible

on every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same device to

be useful for a variety of high bandwidth, high performance memory system applications.

Ordering Information

Part No. Orgainization Max Freq. Interface Package

K4S640432H-TC(L)75 16Mb x 4 133MHz(CL=3)

K4S640832H-TC(L)75 8Mb x 8 133MHz(CL=3)

K4S641632H-TC(L)60

K4S641632H-TC(L)70 143MHz(CL=3)

K4S641632H-TC(L)75 133MHz(CL=3)

Organization Row Address Column Address

4Mb x 16

16Mx4 A0~A11 A0-A9

8Mx8 A0~A11 A0-A8

4Mx16 A0~A11 A0-A7

Row & Column address configuration

166MHz(CL=3)

LVTTL 54pin TSOP(II)

Rev. 1.5 February 2004

Page 30

SDRAM 64Mb H-die (x4, x8, x16)

Package Physical Dimension

CMOS SDRAM

0.10

0.004

MAX

#54

#1

0.71

( )

0.028

#28

11. 76r0.20

0.463r0.008

#27

22.62

MAX

0.891

22.22

0.30

0.012

0.875

+0.10

-0.05

0.004

-0.002

r0.10

r0.004

0.80

0.0315

0.21

0.008

r0.05

r0.002

0.039

54Pin TSOP(II) Package Dimension

1.00

r0.10

r0.004

0.25

0.010

10.16

0.125

0.005

0.047

0.400

1.20

TYP

+0.075

-0.035

+0.003

-0.001

MAX

0.05

0.002

0~8qC

0.45~0.75

0.50

MIN

0.018~0.030

)

0.020

(

Rev. 1.5 February 2004

Page 31

SDRAM 64Mb H-die (x4, x8, x16)

FUNCTIONAL BLOCK DIAGRAM

Bank Select

CMOS SDRAM

LWE

Data Input Register

LDQM

CLK

ADD

Refresh Counter

Row Buffer

Address Register

LRAS

LCBR

LCKE

LRAS LCBR LWE LDQM

CLK CKE CS

Samsung Electronics reserves the right to change products or specification without notice.

*

Row Decoder Col. Buffer

LCAS LWCBR

Timing Register

RAS CAS WE L(U)DQM

4M x 4 / 2M x 8 / 1M x 16

4M x 4 / 2M x 8 / 1M x 16

4M x 4 / 2M x 8 / 1M x 16

4M x 4 / 2M x 8 / 1M x 16

Column Decoder

Latency & Burst Length

Programming Register

Sense AMP

Output BufferI/O Control

DQi

Rev. 1.5 February 2004

Page 32

5

+12V_IN

+12V_IN

R446

1k

C352

1uF

D60

BAV99

E1

+

47uF

R459

47K

GND_PHONE

R464

47K

GND_PHONE

GND_AMP

GND_AMP

R442

nc

R450

470K

R454

470K

EC80

+

2.2uF

R457

100K

R460 10K

C359

820pF

R462

100K

R466 10K

C362

820pF

+12V_IN

12

1 2

PVCC6

PVCC6

R379

NC

GND_AMP

1

GND_PHONE

2

3

PVCC12

GND_PHONE

6

5

PVCC12

R443

47k

1 2

1 2

Q60

2N3904

+

32

Q63

2N3906

C357

100pF

-

+

8 4

C360

100pF

-

+

8 4

R445

47k

EC88

47uF16V

GND_AMP

1

U6A

NJM4558

7

U6B

NJM4558

R455

22K

R451

470

Q59

2N3904

1 2

GND_AMP

C364

10uF

C365

10uF

HPD_PHONE

R384

6.8K

+12V_IN

+12V_IN1,5,10

GND1,2,3,4,5,6,7,8,9,10,12,13,14,15

AOUT1R

AOUT1R7

AOUT1L

AOUT1L7

MUTE_AMP

D D

C C

B B

MUTE_AMP7

MUTE_AMP

+12V_IN

GND_PHONE

1 2

3

2

R456

100K

C358

1uF

C361

1uF

1

GND_AMP

MUTE_AMP7

AOUT1L

AOUT1R

4

R447

100K

R467

8.2K

Q62

2N3904

PHONE OUT

GND_PHONE

R461

10R

PHONE_OUTR

PHONE_OUTL

R268

10R

R283

75R

R444

22K

MUTE_C

C371

EC87

+

10uF

47uF16V

Q61

2N3904

C350

GND_AMP

1uF

GND_AMP

MUTE_C

R498

220

R282

R458

1K

1K

PVCC12 PVCC6

R465

C366

10uF

GND_PHONE

HPD_PHONE

20K

CON9

PHONE

1

2

3

4

5

R284

20K

R463

100K

3

SPEAKER OUT

SPEAKER_ROUT

SPEAKER_LOUT

GND_AMP

R440

NC/8.2K

R441 0

AOUT1_LAOUT1L

RIN

LIN

EC83

MUTE_C

GND

GND

EC76

220uF/16V

GND

EC78

220uF/16V

A_POWER

AOUT1_RAOUT1R

R448 0

R449

NC/8.2K

GND_AMP

R4522.2

R4532.2

C353

0.1uF

C356

C355

0.1uF

0.1uF

R269

47K

SPEAKER OUT

+12V_IN

SPEAKER_LOUT

+12V_IN

U26

PWR GND

PRE GND

Ripple Filter

LA42102

+OUT1

-OUT1

-OUT2

+OUT2

MUTE

Stanby

C368

0.1uF

NC

VCC

IN2

IN1

L43

22uH/2A

470uF/16V

GND_AMP

13

12

11

10

9

8

7

6

5

4

3

2

1

47UF/16V

SPEAKER_ROUT

EC79

A_POWER

MUTE_C

EC82

GND_AMP

R2652.2

R2662.2

47UF/16V

+12V_IN

GND_PHONE

AOUT1R

AOUT1L

MUTE_AMP

C367

10uF

+12V_IN

+12V_IN1,4,9

GND1,2,3,4,5,6,7,8,9,10

AOUT1R6

AOUT1L6

MUTE_AMP6

C351

2.2uF

C354

0.1uF

+12V_IN

GND_AMP

C363

2.2uF

2

LIN

EC75

100uF/16V

RIN

GND_AMP

U27

1

-INV1

2

SGND

3

SVRR

4

OUT1

5

PGND

6

OUT2

7

VP

8

M/SS

9

-INV2

GND10GND

J15

1

2

3

4

DIP/PIN4/2.0

TDA1517P

1

J14

1

2

3

4

DIP/PIN4/2.0

21

20

sink

GND

19

GND

18

GND

17

GND

16

GND

15

GND

14

GND

13

GND

12

GND

11

sink

22

GND_AMP

GND_PHONE GND_AMP

A A

5

4

3

2

1

Page 33

5

4

3

2

1

CON6

NC_4PIN/2.0mm

1

2

3

4

F1

CN3

DC-JACK-2mm

D D

C C

+5VSB

C19

0.1uF

+5VSB

+3V3_SW7100

B B

+12V_power

1

2

3

10

9

8

7

6

5

4

3

2

1

CN2

CON10/2.54mm

+5V_DC +5VSB

L19

0R

STANDBY

UP2

4

ADJ/GND

AP1117-25/SOT-223

SOT-223

C7

0.1uF

4

4

C77

UP4

0.1uF

1117-ADJ

SOT-223

OUT

IN

IN

OUT

ADJ

+12V_IN

5A/12V

+5VSB GND

STB_CON

POWER_ON

3

2

1

UP3

3

IN

AP1084-3V3/256

TOP-263

2

OUT

+3.3V Regulator

1

ADJ

3

2

1

10/26 Add

+5VSB1

R143

220R

R138

100R

L5

22uH/3A/DIP

1 2

EC50

470uF/25V

100K

+2V5

+

+3V3

+

+1V8_ADCA

EC34

+

100uF/16V

10K

R58

R42

EC12

100uF/16V

EC33

100uF/16V

EC37

470uF/25V

+5V_DC

+5VSB

+12V_IN

2

Q12

2N3904

Q15

AP2301

SOT-23

3 1

R437

NC

R438

0ohm-0805

C220

0.1uF

470uF/25V

+5V_SW

L42

22uH/2A

1 2

EC62

C369

10uF

470uF/25V

C221

0.47uF

EC63

U21

OCP2030SA

1

VCC

2

SCP

C2

0.1uF

11/30 Modify

R320

1K

IR

L20

1 2

22uH/4A(33uH/4A)

D33

B340B

R123

100K

+5VSB1

R503 nc

AX3101

OUTPUT

OUTPUT

VSS

8

C218

C217

0.1uF

1uF

+3V3

2

R127

10K

Q24

2N3904

R499

nc

R501

nc

5

6

1

8

LX

7

LX

3

IN

FB4GND5GND

6

C222

2200pF

STANDBY

POWER_ON

R6

1K3

FOR SPV7100 ONLY 3.3V 1.8V 2.5V

U1

4

VCC

OCSET3EN2VSS7FB

R7

100K

C4

0.1uF

3 1

XT4

nc

CRISTAL-B

PICVPP

D3

SK34/SOP

SR34B

EC52

470uF/16V

Q23

AP2301

2

L2 22uH/2A

R318

9K1

R494

1K

R488

100

C385

0.1uF

R319

1K1%

+3V3_SW

C370

10uF

Q64

AP2301

3 1

U28

1

VDD

2

GP5/T1CKI/OSC1/CLKIN

3

GP4/AN3/T1G/OSC2/CLKOUT

4

GP3/MCLR/VPP

PIC12F675

R439

2K2

R41

390

R33

2K

5.6V

+5V_DC

R486

nc

R487

nc

GP0/AN0/CIN+/ICSPDAT

GP1/AN1/CIN-/VREF/ICSPCLK

GP2/AN2/T0CKI/INT/COUT

+1V8

C1

1000pF

EC21

C37

470uF/16V

0.1uF

D41

1 2

+3V3_SW7100

+

+12V_IN

+5V_SW

+5VSB

STB_AC_ON7

POWER_ON7

+3V3

+1V8

VSS

+12V_IN

+5V_SW

+5VSB

+3V3

+1V8

8

7

6

5

+5VSB

R227

10K

STB_CON

3

Q30

2

1

2N3904

SOT-23

STB_AC_ON

POWER_ON

+12V_IN5,10,11

+5V_SW 3,4,12,13,15

+5VSB 5,9,10,13

+3V3 2,3,7,8,9,10,13,14,15

+1V8 8

GND 2,3,4,5,6,7,8,9,10,11,12,13,14,15

R500

C393

nc

nc

GND

GND

R504 nc

R506 nc

R228 4.7K

OFF

KPD_POWER

MCU_IO

GND_PWRGND_TMDSGNDV

STB_AC_ON

PICVPP

PICPGD

PICPGC

R505 nc

ON

CN11

HEADER5-2.54

5

4

3

2

1

STB_CON

A A

Title

Size Document Number

C

5

4

3

2

Date: Sheet of

SUNPLUS

System Power

SPTV05-13-V1

1

Rev

1.0

1 15Sunday, June 15, 2008

Page 34

5

HDMI Input

Layout Note

differential impedance 100ohm

CN4

20

SHELL1

D D

GND_CASE

C C

SHELL221D2+

22

SHELL3

23

SHELL4

HDMI CON-SMT

D2 Shield

D1+

D1 Shield

D0+

D0 Shield

CK+

CK Shield

CE Remote

DDC CLK

DDC DATA

GND

+5V

HPD

D2-

D1-

D0-

CK-

1

2

3

4

5

6

7

8

9

10

11

12

13

14

NC

15

16

17

18

19

GND_TMDS

EDID Defult: NOT write protect

10K

R160

4.7K

NC/10K

5v_hdmi

R158

/WP

R323

GND_TMDS

RXP2

RXM2

RXP1

RXM1

RXP0

RXM0

RXCP

RXCM

ASCL

ASDA

+5V_HDMI_A

R298

nc

5v_hdmi

R159

4.7K

5v_hdmi

D6

3

4

INPUT1

BAT54C

2

+5V_DC

1

+5V_HDMI_A

U1424C02

8

VCC

7

WP

6

SCK

5

SDA

C105 1uF

VSS

A0

A1

A2

1

2

3

4

GND_TMDS

3

RXP2 RXM2 RXP1 RXM1

DM8

NC

GND_TMDS GND_TMDS GND_TMDS GND_TMDS

RXP0 RXM0 RXCP RXCM

DM6

NC

GND_TMDS GND_TMDS GND_TMDS GND_TMDS

ASCL

DM4

NC

DM2

NC

R324 33

DM7

NC

DM5

NC

ASCL

DM3

NC

DM1

NC

SCL_HDMI 7

GND_TMDS

ASDA

GND_TMDS

DM10

NC

DM9

NC

RXP0

RXM0

RXP1

RXM1

RXP2

RXM2

RXCP

RXCM

SOG_IN

B_IN

G_IN

R_IN

2

ISP_TRAP

RXP0 7

RXM0 7

RXP1 7

RXM1 7

RXP2 7

RXM2 7

RXCP 7

RXCM 7

+5V_DC

SOG_IN 3,7

B_IN 7

G_IN 7

R_IN 7

R105 10K

R313

100K

+3V3

2

SCL_VGA

SDA_VGA

VS_VGA

HS_VGA

HPD_PC

/WP

+5V_DC

+3V3

HOLD_FLASH

3

Q22

2N3904

1

SCL_VGA 7

SDA_VGA 7

VS_VGA 7

HS_VGA 7

HPD_PC 7

/WP 7

+3V3

WP# 9

10/25 Modify

R114

100K

1

+5V_DC1,3,9,10,13

+3V31,3,7,8,9,10,13,14,15

GND1,3,4,5,6,7,8,9,10,11,12,13,14,15

HOLD_FLASH7

R297

2

GND_TMDS

1K

3

Q35

Si2302

1

VGA Analog Input

SCL_VGA2

SDA_VGA2

D11

D27

nc

1 2

1 2

GND_ADC

GND_ADC

R327 NC/33

R328 33

+5V_VGA

nc

GND_ADC

GND_ADC

4

15

10

14

13

12

9

8

7

6

CN5

VGA/CON

5

4

3

2

111

VGA Con.

DSUB 15Pin-3/Female

16

17

D13

5.6V

1 2

GND_CASE GND_TMDS GND_TMDSGND_ADCGND_CASE

R326 nc

R296

1K

3

R136

HPD_HDMI7

B B

A A

HPD_HDMI

GND_ADC

VS_VGA

R208 100

HS_VGA

R199 100

C149

C150

NC

GND_ADC GND_ADC

NC

5

1K

Q34

Si2302

2

1

R206

R207

510

510

ASDA

GND_ADC

GND_ADC

+5V_DC +5V_DC +5V_DC

1

2

D31

D30

BAV99L

BAV99L

3

VGA_BIN

VGA_GIN

VGA_RIN

D12

5.6V

1 2

GND_ADC

GND_ADC

1

2

D32

BAV99L

3

R263

R264 22R

R325 33

R311 10K

R309 NC

1

2

3

22R

3

1 2

GND_ADC

PC-BIN

C212

NC/22pF

ISP_TRAP

HPD_PC

D28

nc

PC-GIN

PC-RIN

C213

NC/22pF

GND_ADC

TXD 7,9

RXD 7,9

SDA_HDMI 7

C214

NC/22pF

PC-BIN

PC-GIN

PC-GIN

R300

R301

75R

75R

GND_ADC

PC DDC

D29

3

BAT54C

C184

1uF

GND_ADC GND_ADC

R209 100R

R210 100R

PC-RIN R_IN

PC-RIN

2

1

2

R302

75R

+5V_DC

+5V_VGA

+5V_DDC

U19

A01VCC

A12WP

A23SCL

GND4SDA

24C02

DDC EDID Data

SOP 8Pin

R211 100R

+5V_DDC

8

7

6

5

GND_ADC

SCL_VGA2

SDA_VGA2

ISP FROM VGA

GND_ADCGND_ADC

B_INPC-BIN

C151

0.01uF

G_IN

C152

0.01uF

C153

0.01uF

+5V_DDC

R254

R251

2K2

2K2

R252 100

R253 100

Title

Size Document Number

Date: Sheet of

HDMI Switch

Custom

SCL_VGA

SDA_VGA

SUNPLUS

SPTV05-13-V1

1

Rev

1.0

2 15Thursday, June 12, 2008

Page 35

5

+5V_SW

+5V_SW1,4,12,13,15

CN7

SHILED

VOUT

GNDVI

GNDVO

RGBSW

RIN

GNDSW

GNDR

GIN

GNDG

FunSel

BIN

GNDB

AOL

AOR

SCART Connector

CN9

7

Y

7

8

8

Pb

9

9

Pr

10

10

11

11

12

12

13

13

Y

14

14

Pb

15

15

16

Pr

16

AV1-3X2

GND

TXD_1003

RXD_1003

VIN

N.C.

N.C.

AIL

GNDA

AIR

1

3

5

2

4

6

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

L29

120ohm/100MHz

L30

120ohm/100MHz

L31

120ohm/100MHz

,4,5,6,7,8,9,10,11,12,13,14,15

D D

Y Pr Pr CVBS

C C

B B

+5V_SW

TXD_1003 2,7,9

RXD_1003 2,7,9

5.6V

SC1_FB

SC1_RIN

SCART_ISP

SC1_GIN

SC1_FS

SC1_BIN

SC1_AU_LIN

SC1_AU_LOUT

SC1_AU_RIN

SC1_AU_ROUT

GNDV

AV_VIN

SC2_AU_LIN

SC2_AU_RIN

3

3

BAV99L

BAV99L

BAV99L

D22

D23

D21

1

2

1

2

2

+5V_DC

GND_ADCGND_ADC

+5V_DC

GND_ADC +5V_DC

D25

GNDV

R286NC/0R

R287NC/0R

3

GND_ADC

1

1 2

av_1_out

R-0603

R-0603

R304

75R

12

12

C199

220pF

RXD_1003

TXD_1003

R274

75R

L14

1.8uH

DTV_Y_IN1

DTV_Pb_IN1

DTV_Pr_IN1

R270

75R

DVD_Y_IN13

DVD_PB_IN13

DVD_PR_IN13

CVBS2_INav_1_in

C185

220pF

av_1_out 3

R289

10K

D17

nc/15V

1 2

SC1_AU_LOUT SC1_AU_ROUT

4

11/28 Modify

CVBS2_IN 7

R258

75R

GNDV

R216

2.4K

1 2

GNDVGNDV

D18

9.2V

1 2

SCART1 AV+RGB

FS -> SOY2 / SARIN1

0-2v: TV Mode -> 0-0.4v

5-8v: 16:9 AV -> 1.0-1.6v

9.5-12v: 4:3 AV -> 1.9-2.4v

SOG_IN

SOY2_IN

D24

R303

5.6V

75R

GNDVGNDV

D19

9.2V

1 2

SC1_BIN

BAV99L

D16

SC1_GIN

BAV99L

D15

SC1_RIN

SOG_IN 7

SOY2_IN 7

SC1_AU_LOUT

SC1_AU_ROUT AOUT0R

SC1_AU_RIN

AU_AIN1L

AU_AIN1R

AV_VIN

DTV_Y_IN1

DTV_Pb_IN1

DTV_Pr_IN1

GNDV

C3271uF

C3281uF

R190 10K

R312 10K

AU_AIN1L 4

AU_AIN1R 4

D20

1 2

GNDV

C238

R330 22K

BAV99L

R292

47K

C215

220pF

5.6V

+5V_SW_4052

R329

22K

10uF

GNDV

PI5V330

R230

D14

R412

10R

2

47K

R314

6.8K

2

5

11

14

3

6

10

13

2

2

3

L17

1.8uH

3

1

+5V_DCGND_ADC

3

1

+5V_DCGND_ADC

1

+5V_DCGND_ADC

AOUT0L

16

U18

1A

1B

1C

1D

2A

2B

2C

2D

8

3

C232

220pF

GNDV GNDV

C234

220pF

GNDV GNDV

C236

220pF

GNDV GNDV

AU_AIN1LSC1_AU_LIN

AU_AIN1R

R186

6.8K

C207

220pF

GNDV

C223

1uF

GNDV

4

A

7

B

VCC

9

C

12

D

15

EN

1

S

VSS

L21

1.8uH

L22

1.8uH

L23

1.8uH

GNDV

CVBS0_IN

R259

75R

C233

220pF

C235

220pF

C237

220pF

GNDV

AOUT0L

AOUT0L7

AOUT0R

AOUT0R7

11/28 Modify

CVBS0_IN 7

SW_HD

R244

R245

75R

75R

SW_HD 7

R242

75R

SCART_ISP

SC2_AU_LIN

C324

2.2uF

C-0603

C325

2.2uF

C-0603

C326

2.2uF

C-0603

R243

100R

R213

0R

R246

100R

R257

100R

GND_ADC

PR2_IN

PB2_IN

Y2_IN

C155

NC/10pF

R12810K

11/28 Modify

PR2_IN 7

PB2_IN 7

Y2_IN 7

2

R306 10K

R308 10K

C158

0.01uF

C131

1000pF

C165

0.01uF

C179

0.01uF

2

+3V3

R129

NC/100K

SCART_ISP_TRAP

3

Q21

2N3904

1

R104

100R

ISP FROM SCART

GND

R307

6.8K

Y1_IN

SOY1_IN

PB1_IN

PR1_IN

AU_AIN2L

AU_AIN2RSC2_AU_RIN

R305

6.8K

Y1_IN 7

SOY1_IN 7

PB1_IN 7

PR1_IN 7

SCART_ISP_TRAP13

AU_AIN2L

AU_AIN2R

AU_AIN2L 4

AU_AIN2R 4

11/28 Modify

1

11/30 Modify

GND_ADC

GNDV

A A

Title

Size Document Number

C

5

4

3

2

Date: Sheet of

SUNPLUS

Input-2 Video

SPTV05-13-V1

1

Rev

1.0

3 15Thursday, May 01, 2008

Page 36

5

PC Audio Input

CN6

D D

C C

PHONE

Stereo Audio In

2

5

1

3

R-Pho L-Pho

L-Out

Stereo Audio Connector

Top Diagram

DVB_AL_OUT13

DVB_AR_OUT13

AIN2L

AIN2R

AIN3L

AIN3R

AU_SW0

AU_SW1

AU_AIN1L

AU_AIN1R

5

4

3

2

1

4

R-Out

AIN2L 7

AIN2R 7

AIN3L 7

AIN3R 7

AU_SW0 7

AU_SW1 7

AU_AIN1L 3

AU_AIN1R 3

R278 10K

R276 10K

AIN3L

AIN3R

AIN0L

AIN0R

R275

6.8K

R277

6.8K

AU_AIN2L

AU_AIN2R

C331 1uF

C332 1uF

AIN0R

AU_AIN1L

AU_AIN1R

R177

47K

R173

47K

C333 1uF

C334 1uF

4

C329 1uF

C330 1uF

+5V_SW_4052

R191

47K

R273

47K

R196

47K

+5V_SW_4052

R198

47K

R192

47K

+5V_SW_4052

R181

47K

R187

47K

R180

47K

3

4052 ch0:SCART

4052 ch1:YPrPr,CVBS

4052 ch2:PC output

4052 ch3:TV MONO

U16

12

1Y0

14

1Y1

15

1Y2

11

1Y3

1

2Y0

5

2Y1

2

2Y2

4

AU_SW0

AU_SW1

2Y3

10

S0

9

S1

6

IE

74HC4052

AUDIO_EN 12

VCC

VEE

GND

1Z

2Z

(to SPV7100

& SCART-2)

16

AIN2L

13

AIN2R

3

7

8

PC-->SPV7100 :NC

DVD-->SPV7100 :CH1

4052-->SPV7100 :CH2

DVB-->SPV7100 :CH3

+5V_SW_4052

C239

0.1uF

+5V_SWAIN0L

+5V_SW1,3,12,13,15

+3V31,2,3,7,8,9,10,13,14,15

GND1,2,3,5,6,7,8,9,10,11,12,13,14,15

+3V3

+5V_SW

+3V3

2

1

R200

R188

47K

AU_AIN2L

AU_AIN2R

B B

A A

AIN1L

AIN1R

AU_AIN2L 3

AU_AIN2R 3

AIN1L 5

AIN1R 5

5

GNDV

AIN1L

AIN1R

C335 1uF

C336 1uF

R331

47K

R333

47K

4

47K

+5V_SW_4052

R332

47K

R334

47K

Title

Size Document Number

A3

3

2

Date: Sheet of

SUNPLUS

Input-3 Audio and DTV

SPTV05-13-V1

1

Rev

1.0

4 15Thursday, May 01, 2008

Page 37

5

4

3

2

1

CN8

2

D D

GNDV

C C

B B

CON7

Y

GND

PB

GND

PR

GND

LEFT

RIGHT

GND

EN

10

IR

A A

11

CON11/2.0mm

41

1

2

3

4

5

6

7

8

9

3

567

S_VIDEO

4

2

1

3

5

GNDV

s-c

s-y

GND_ADC

R294 10K

R234 10K

DVD_EN

IR_DVD

D63

5.6V

1 2

AIN1L

AIN1R

DVD_EN 7

IR_DVD 9

GNDV GNDV

C313

NC/220pF

D55

nc

L37

3.3uH

1 2

GNDV

L38

1.8uH

D56

nc

C315

220pF

1 2

GNDV GNDVGNDV GNDV

L39

1.8uH

L40

1.8uH

L41

1.8uH R367

R233

6.8K

C339

220pF

GNDV GNDV

C341

220pF

GNDV GNDV

C343

220pF

GNDV GNDV

R295

6.8K

4

C314

330pF

C340

220pF

C342

220pF

C344

220pF

C316

220pF

GNDVGNDV GNDV

3

C2_IN

R426

75R

CVBS1_IN

GNDV

GNDV

GNDV

R427

75R

R472NC

R365

75R

R473NC

R366

75R

R474NC

75R

DTV_Pb_IN2

CVBS1_IN

C2_IN

AIN1L

AIN1R

DTV_Y_IN213

DVD_Y_IN 13

DTV_Pb_IN213

DVD_PB_IN 13

DTV_Pr_IN213

DVD_PR_IN 13

CVBS1_IN 7

C2_IN 7

AIN1L 4

AIN1R 4

+5V_SW1,3,4,12,13,15

GND1,2,3,4,6,7,8,9,10,11,12,13,14,15

+5V_SW

SUNPLUS

Title

Size Document Number

A

Date: Sheet of

2

Input-2 Video

SPTV05-13-V1

+5V_SW

Rev

1.0

5 15Thursday, May 01, 2008

1

Page 38

5

MD[0..15]7

MA[0..11]7

D D

C C

SDCLKP

BA07

BA17

WEN7

CASN7

RASN7

CKE7

SDCLKP7

SDCLKN7

DQS0L7

DQS0H7

DQM0L7

DQM0H7

R9310R

MD[0..15]

MA[0..11]

BA0

BA1

WEN

CASN

RASN

CKE

SDCLKP

SDCLKN

DQS0L

DQS0H

DQM0L

DQM0H

R86 10R

SDRAM Data Bus

R103 22K

R99 47R

MCLKP

4

+2V5

+2V5

+2V5

+2V5

+2V5

GNDM

+2V5

CKERCKE

+2V5

+1.25V

3

U5

1

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

DQS0H

DQM0H

WEN

CASN

RASN

CSN

BA0

BA1

MA10

MA0

MA1

MA2

MA3 MA4

GNDM GNDM

VDD

2

DQ0

3

VDDQ

4

DQ1

5

DQ2

6

VSSQ

7

DQ3

8

DQ4

9

VDDQ

10

DQ5

11

DQ6

12

VSSQ

13

DQ7

14

NC

15

VDDQ

16

LDQS

17

NC

18

VDD

19

NC

20

LDM

21

WE

22

CAS

23

RAS

24

CS

25

NC

26

BA0

27

BA1

28

AP/A10

29

A0

30

A1

31

A2

32

A3

33

VDD

8Mx16 DDR-SDRAM-TSOP

VSS

DQ15

VSSQ

DQ14

DQ13

VDDQ

DQ12

DQ11

VSSQ

DQ10

DQ9

VDDQ

DQ8

NC

VSSQ

UDQS

NC

VREF

VSS

UDM

CK

CK

CKE

NC

NC/A12

A11

A9

A8

A7

A6

A5

A4

VSS

2

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

DQS0L

DQM0L

MCLKN

MCLKP

CKER

MA11

MA9

MA8

MA7

MA6

MA5

+2V5

+2V5

+1.25V

*add

+2V5

GNDM

R70

4.7K

R87

4.7K

1

C35

0.1uF

These components close to DDR

All traces must have the same length

B B

SDCLKN

R9410R

R335

75R

CLOSE TO DDR

MCLKN

HY5DU281622ETP(128Mb/2Mx16x4B)

GNDM

R95 47R

+1.25V

*Short these ground planes on PCB

GNDM

CLOSE TO 7100

+2V5

A A

C21

C36

10uF/10V

GNDM

5

1000pF

4

C18

0.1uF

3

Title

Size Document Number

A

Date: Sheet of

2

SUNPLUS

DDR PART

SPTV05-13-V1

Rev

1.0

6 15Thursday, June 12, 2008

1

Page 39

5

Crystal Circuit

R150 22R

CEN_FLASH

SCK_FLASH

STB_AC_ON

CLKIN

CLKOUT

+5V_DDC

R299 10K

RXD

TXD

C49

C-0603

IR_DAT

CEN_FLASH9

SCK_FLASH9

STB_AC_ON1

C76

56pF

+DVDD

+CVDD

RESETN

22pF

BL_ADJ

SD1_FLASH

SD0_FLASH

CEN_FLASH

SCK_FLASH

HOLD_FLASH

MPU & SPI

PANEL_ONLED_C

LED_C

/WP

C63

56pF

+3V3_XTAL

+3V3_TMDS

HDMI Input

+3V3_ADCP

C117390pF+-5%

R170

C123

5.6K+-1%

8200pF+-5%

These components close to SPV7100

Close to 7100

GND_ADC

11/30 Note

VCM_AUI

C137

0.1uF

C-0603

5

C-0603

C61

56pF

C47

C-0603

56pF

R107 33R

R121 33R

R106 33R

+1V8_AUD

+CVDD

MIDSCV

C124

1uF

C242

10uF

C-0805

HPD_PC

MCU_IO

STB_AC_ON

HPD_HDMI

SDA_VGA

SCL_VGA

SCL_HDMI

FILT

C46

56pF

SDA_HDMI

CLKIN

CLKOUT

RXCM

RXCP

RXM0

RXP0

RXM1

RXP1

RXM2

RXP2

HPD_PC

HS_VGA

VS_VGA

MIDSCV

GND_TMDS

+1V8_ADCA

VCM_AUO

C-0603

GND_ADC

C-0603

GND_ADC

C157

1uF

C140

0.1uF

GND_AUO

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

209

210

211

212

213

214

215

216

217

218

219

220

221

222

223

224

225

226

227

228

229

230

231

232

233

234

235

236

237

238

239

240

241