Page 1

PSR-2000

SERVICE MANUAL

PK

001666

HAMAMATSU, JAPAN

1.421K-4071 Printed in Japan '01.09

CONTENTS

SPECIFICATIONS···································································· 2

PANEL LAYOUT······································································· 4

CIRCUIT BOARD LAYOUT······················································ 6

DISASSEMBLY PROCEDURE················································· 8

LSI PIN DESCRIPTION·························································· 13

IC BLOCK DIAGRAM ····························································· 20

CIRCUIT BOARDS································································· 21

TEST PROGRAM··································································· 39

SYSTEM RESET···································································· 42

MIDI IMPLEMENTATION CHART·········································· 43

MIDI DATA FORMAT······························································ 44

PARTS LIST

BLOCK DIAGRAM

OVERALL CIRCUIT DIAGRAM

This document is printed on chlorine free (ECF) paper with soy ink.

PSR-1000

Page 2

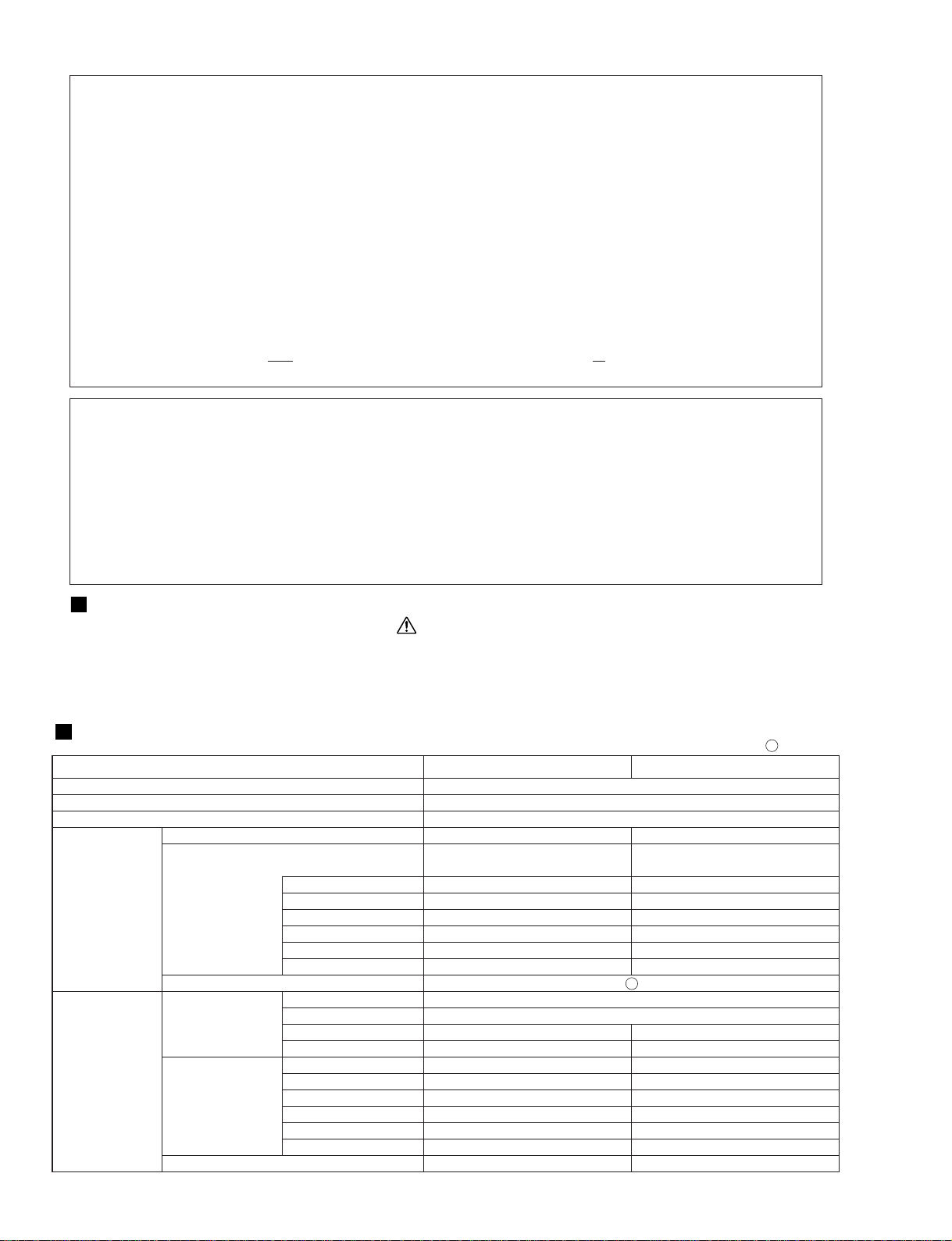

SPECIFICATIONS

PSR-1000/PSR-2000

2

WARNING: CHEMICAL CONTENT NOTICE!

The solder used in the production of this product contains LEAD. In addition, other electrical/electronic and/or plastic (where

applicable) components may also contain traces of chemicals found by the California Health and Welfare Agency (and possibly

other entities) to cause cancer and/or birth defects or other reproductive harm.

DO NOT PLACE SOLDER, ELECTRICAL/ELECTRONIC OR PLASTIC COMPONENTS IN YOUR MOUTH FOR ANY REASON

WHAT SO EVER!

Avoid prolonged, unprotected contact between solder and your skin! When soldering, do not inhale solder fumes or expose eyes

to solder/flux vapor!

If you come in contact with solder or components located inside the enclosure of this product, wash your hands before handling

food.

IMPORTANT NOTICE

This manual has been provided for the use of authorized Yamaha Retailers and their service personnel. It has been assumed that

basic service procedures inherent to the industry, and more specifically Yamaha Products, are already known and understood by

the users, and have therefore not been restated.

WARNING: Failure to follow appropriate service and safety procedures when servicing this product may result in personal

injury, destruction of expensive components and failure of the product to perform as specified. For these

reasons, we advise all Yamaha product owners that all service required should be performed by an authorized

Yamaha Retailer or the appointed service representative.

IMPORTANT: This presentation or sale of this manual to any individual or firm does not constitute authorization, certification,

recognition of any applicable technical capabilities, or establish a principal-agent relationship of any form.

The data provided is belived to be accurate and applicable to the unit(s) indicated on the cover. The research engineering, and

service departments of Yamaha are continually striving to improve Yamaha products. Modifications are, therefore, inevitable and

changes in specification are subject to change without notice or obligation to retrofit. Should any discrepancy appear to exist,

please contact the distributor's Service Division.

WARNING: Static discharges can destroy expensive components. Discharge any static electricity your body may have

accumulated by grounding yourself to the ground bus in the unit (heavy gauge black wires connect to this bus).

IMPORTANT: Turn the unit OFF during disassembly and parts replacement. Recheck all work before you apply power to the

unit.

WARNING

Components having special characteristics are marked and must be replaced with parts having specification equal to those

originally installed.

Model Name

Sound Source

Display

Keyboard

Voice Polyphony (max)

Voice Selection

Regular Voice

Sweet Voice

Cool Voice

Live Voice

Others

Organ Flute

Sound creator

Effects Reverb

Chorus

Effect Blocks

DSP

Microphone

REVERB

CHORUS

DSP1

Effect Types

DSP2, 3, 4

Master EQ

Part EQ

Vocal Harmony

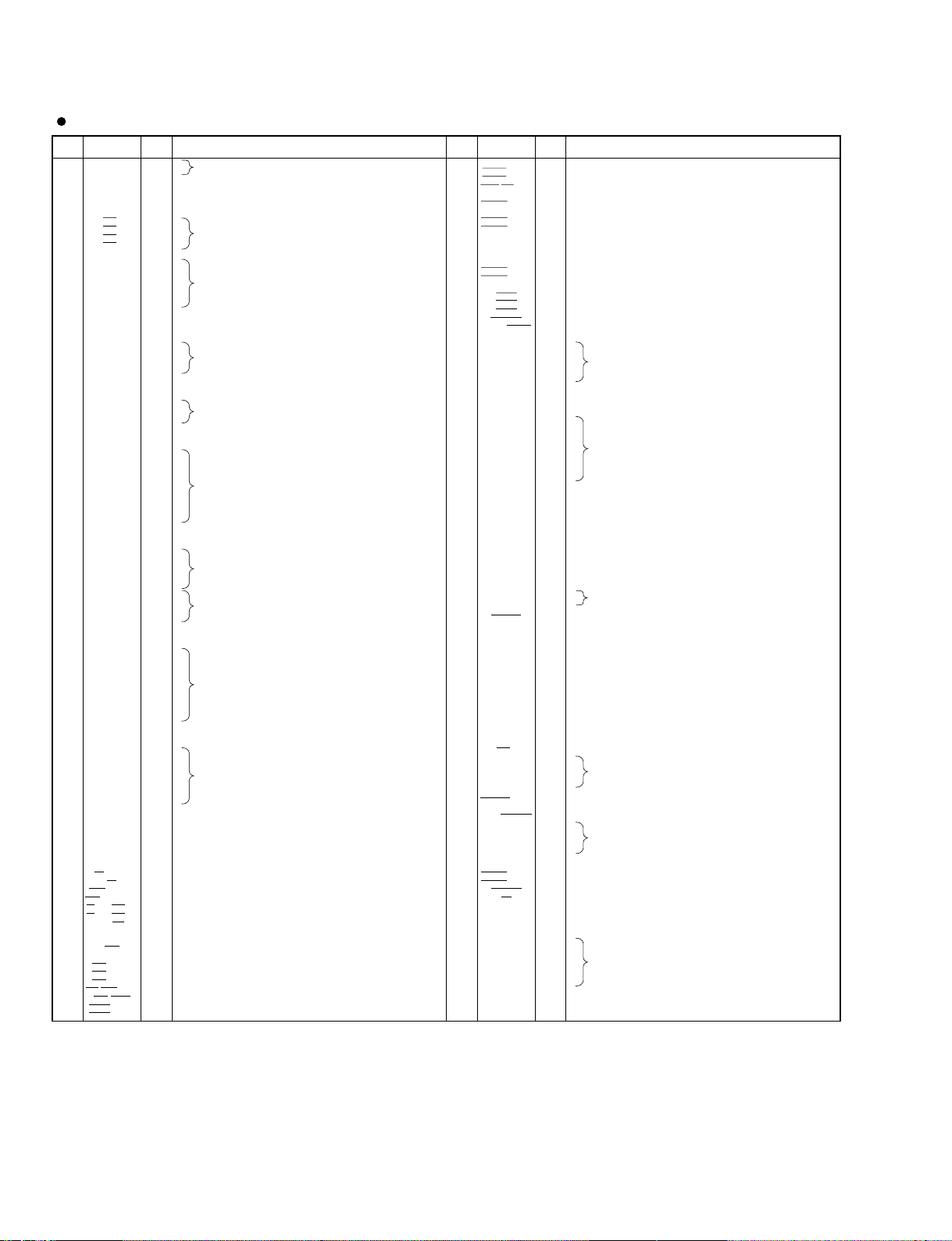

PSR-1000 PSR-2000

AWM Dynamic Stereo Sampling

320 x 240 dots backlit graphic LCD

61 keys (C1 - C6 with Initial Touch)

32 64

233 voices + 480 XG voices 313 voices + 480 XG voices

+ 15 Drum Kits + 16 Drum Kits

233 303

38

12

—3

229 290

— 10 (8 Footages)

1

1

14

—1

23 Preset+3 User 29 Preset+3 User

15 Preset+3 User 25 Preset+3 User

98 Preset+3 User 164 Preset+3 User

— 88 Preset +10 User

— 5 Preset + 2 User

— 27 Parts

— 49 Preset +10 User

: available

Page 3

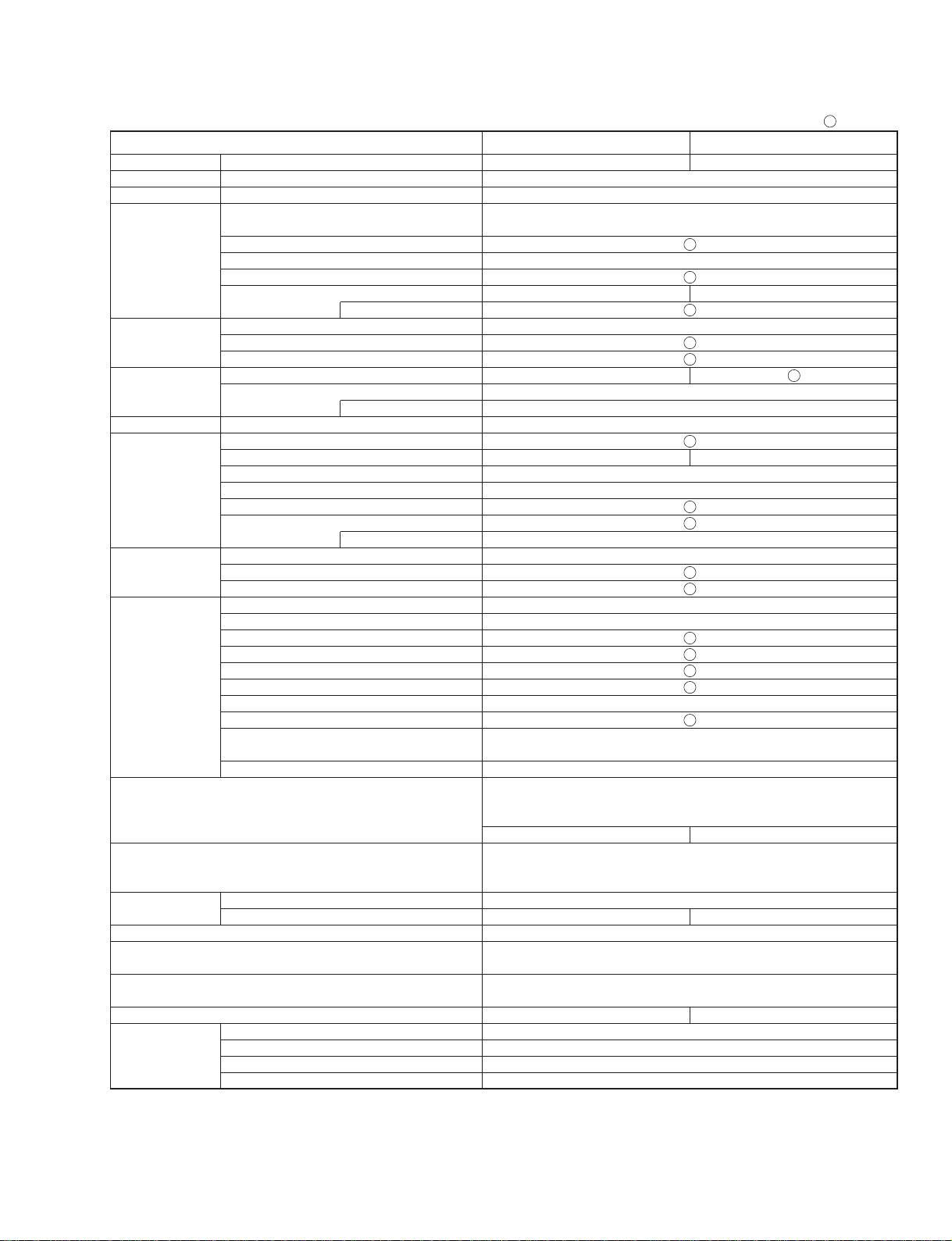

PSR-1000/PSR-2000

3

Model Name

Accompaniment Number of Accompaniment Styles

Style Number of Session Styles

Disk

Fingering

Style Creator

OTS (One Touch Setting)

OTS link

Music Finder

Edit

Song Format

Preset Songs

Lyrics

Score

Recording

Record Channels

Multi Pad Preset

Memory Floppy Disk (2HD,2DD)

Device Flash Memory (internal)

Flash Availability

Tempo Tempo Range

Tap Tempo

Metronome

Sound

Registration Buttons

Memory Regist Sequence

Freeze

Others Demo

Language

Help

Direct Access

Master Volume

Fade In/Out

Transpose

Tuning

Scale

Touch Response

Jacks/Connectors

Pedal Functions

Amplifiers/ Amplifiers

Speakers Speakers

Power Consumption

Power supply

Dimensions [W x D x H]

(without Music Stand)

Weight

Optional Headphones

accessories Foot Switch

Foot Controller

Keyboard Stand

PSR-1000 PSR-2000

169 181

4

28 styles (included in the accessory disk)

Single Finger, Fingered, Fingered On Bass, Multi Finger, AI Fingered,

Full Keyboard, AI Full Keyboard

4/Accompaniment Style

400 (max.) 500 (max.)

SMF (Format 0,1), ESEQ

—

Quick Recording, Multi Recording, Step Recording, Song Editing

16

4 Pads x 54 Banks

512KB 1MB

Song (SMF), Style (SFF), Registration, Voice, etc.

5 - 500

Bell on/off

8

Function, Voice, Style

6 languages (English, Japanese, German, French, Spanish, Italian)

Keyboard/Song/Master

Equal Temperament, Pure Major/Pure Minor, Pythagorean, Mean-Tone,

Werckmeister/Kirnberger, Arabic 1/2

5 level

DC IN, PHONES, MIDI (OUT, IN), TO HOST,

HOST SELECT SW, FOOT PEDAL1 (SWITCH), FOOT PEDAL2,

AUX OUT (LEVEL FIXED) (L/R), OUTPUT (L/L+R)

— MIC (INPUT VOLUME, MIC./ LINE)

VOLUME, SUSTAIN, SOSTENUTO, SOFT, GLIDE, PORTAMENTO,

PITCHBEND, MODULATION, DSP VARIATION, SONG START/STOP,

STYLE START/STOP, etc.

12 W x 2

(12 cm + 5 cm) x 2 [12 cm + 4 cm (dome)] x 2

31 W

Yamaha AC adaptor PA-300 (included)

*May not be in you area.Please check with your Yamaha dealer.

973 x 399 x 161 mm

[38-5/16" x 15-11/16" x 6-5/16"]

10.0 Kg (22 lbs., 1 oz) 10.5 Kg (23 lbs., 2 oz)

HPE-150

FC4 / FC5

FC7

L-6, L-7

: available

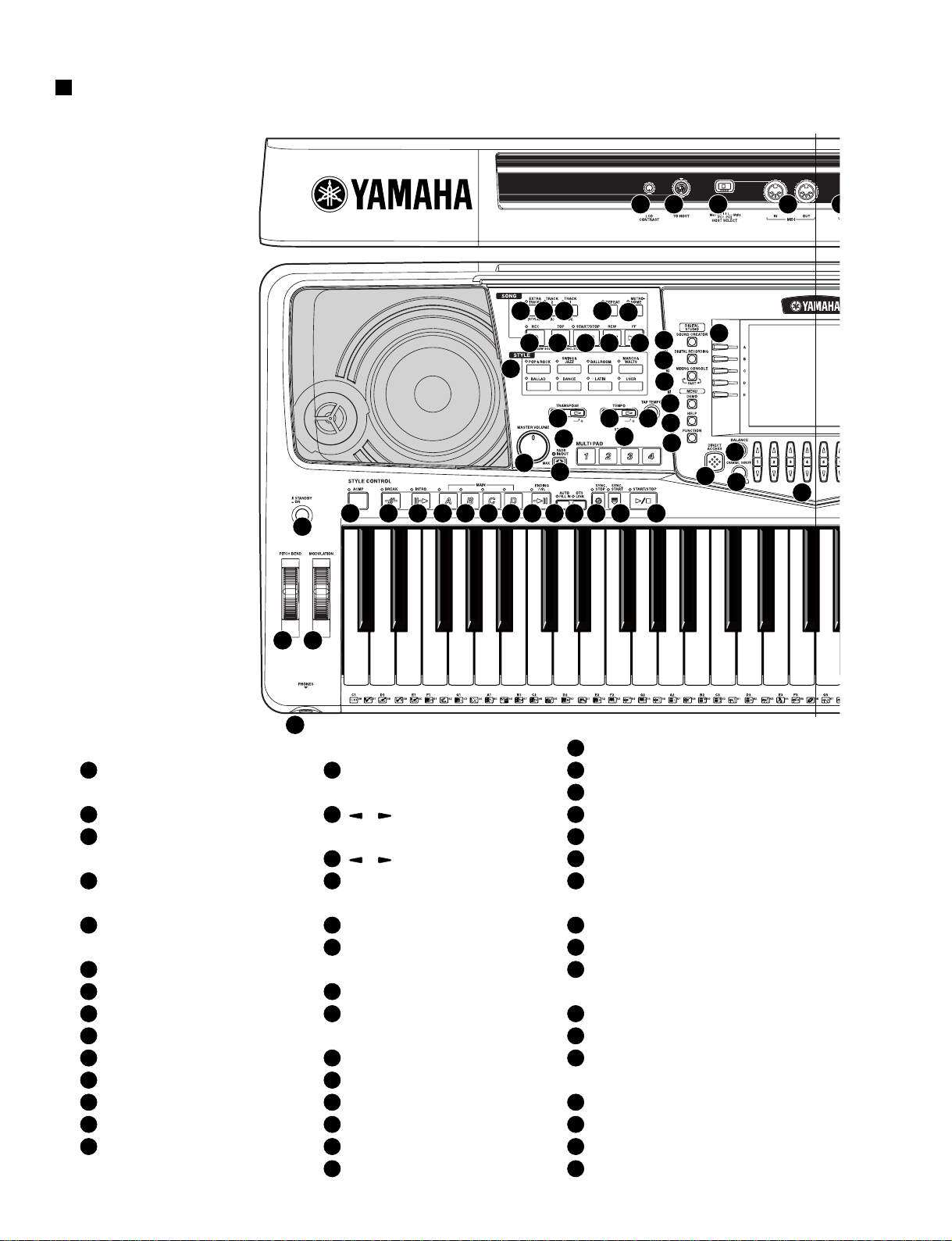

Page 4

PSR-1000/PSR-2000

4

PANEL LAYOUT

A'

A

5

6 7 8 9

10

15

16

19

20

23 24 25 26 27 28 29 30 31 32 33 34 35

21

22

17 18

11 12 13 14

36

42

43

44

45

46

55 74 75 76 7

37

38

39

40

41

2 3

4

1

1

[STANDBY/ON] switch

POWER

15

STYLE buttons

STYLE

36

[SOUND CREATOR] button

37

[DIGITAL RECORDING] button

38

[MIXING CONSOLE] button

DIGITAL STUDIO

39

[DEMO] button

40

[HELP] button

41

[FUNCTION] button

MENU

42

[A] - [J] buttons

43

[DIRECT ACCESS] button

44

[BALANCE] button

45

[CHANNEL ON / OFF] button

DISPLAY CONTROL

29

MAIN [D] button

30

[ENDING / rit.] button

31

[AUTO FILL IN] button

32

[OTS LINK] button

33

[SYNC.STOP] button

34

[SYNC.START] button

35

[START / STOP] button

TRANSPOSE

17

[ ] [ ] buttons

18

[TAP TEMPO] button

TEMPO

19

[MASTER VOLUME] dial

20

[FADE IN / OUT] button

MASTER VOLUME

21

[1] - [4] buttons

22

[STOP] button

MULTI PAD

23

[ACMP] button

24

[BREAK] button

25

[INTRO] button

26

MAIN [A] button

27

MAIN [B] button

28

MAIN [C] button

STYLE CONTROL

2

PITCH BEND

3

MODULATION (PSR-2000 only)

WHEEL

4

[PHONES] jack

PHONES

5

[METRONOME] button

METRONOME

6

[EXTRA TRACKS (STYLE)] button

7

[TRACK 2 (L)] button

8

[TRACK 1 (R)] button

9

[REPEAT] button

10

[REC] button

11

[TOP] button

12

[START / STOP] button

13

[REW] button

14

[FF] button

SONG

16

[ ] [ ] buttons

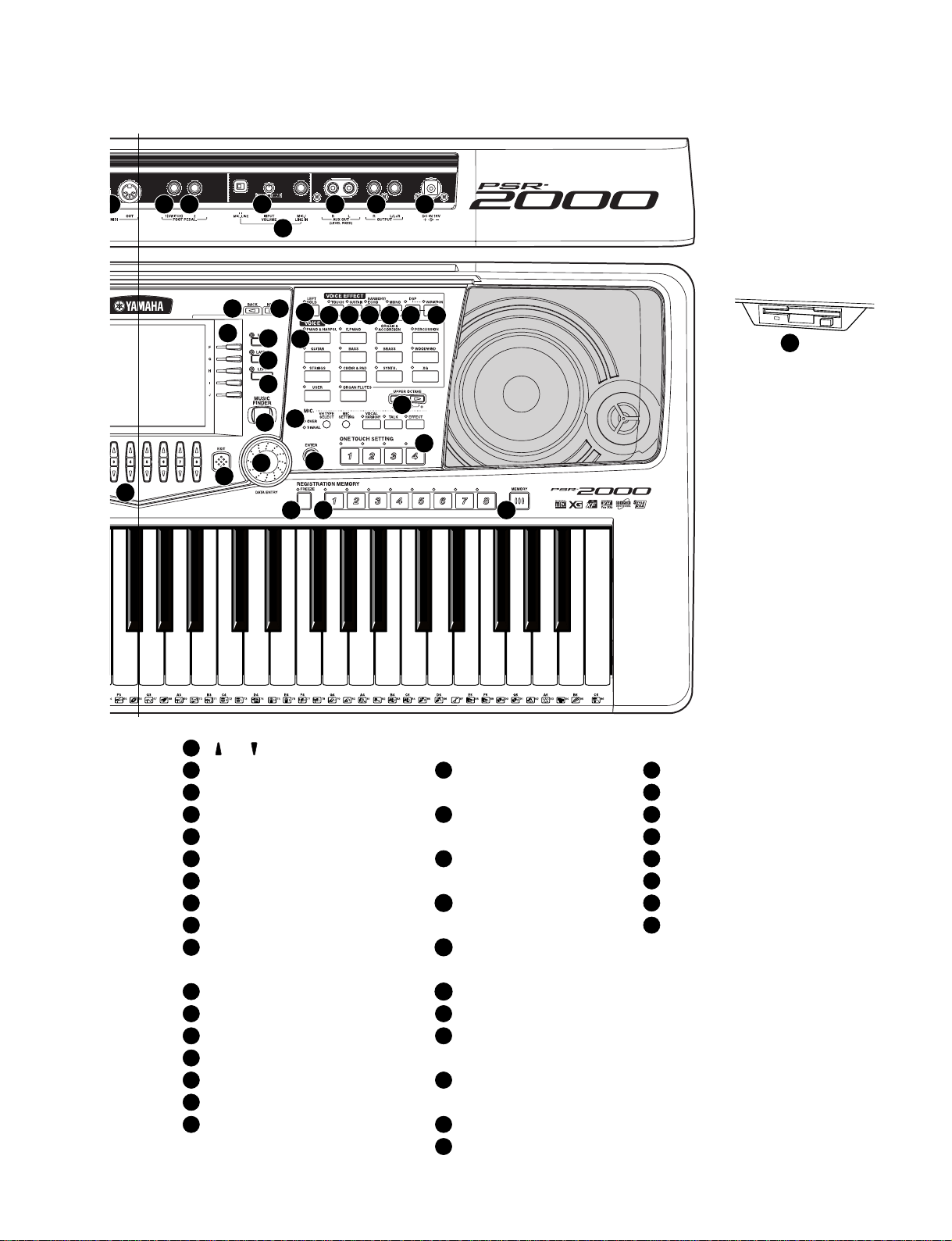

Page 5

PSR-1000/PSR-2000

5

A'

A

46

42

47

73

48

56

57 58 59 60 61 62

63

64

65

66

67

68 69 70

71

49

50

51

52

53

54

63

VOICE buttons

VOICE

74

[TO HOST] terminal

75

[HOST SELECT] switch

76

MIDI [OUT] [IN] terminals

77

[FOOT PEDAL 1 (SWITCH) ] jack

78

[FOOT PEDAL 2] jack

79

AUX OUT (LEVEL FIXED) [L] [R] jacks

80

OUTPUT [L / L+R] [R] jacks

81

DC IN terminal

Connectors

64

[UPPER OCTAVE] button

UPPER OCTAVE

65

MIC. buttons (PSR-2000 only)

MIC.

66

[MUSIC FINDER] button

MUSIC FINDER

67

[1] - [4] buttons

ONE TOUCH SETTING

68

[FREEZE] button

69

[1] – [8] buttons

70

[MEMORY] button

REGISTRATION MEMORY

71

Floppy disk drive (3.5”)

FLOPPY DISK

72

[INPUT VOLUME] knob

73

[MIC. / LINE IN] jack

Microphone (PSR-2000 only)

56

[LEFT HOLD] button

57

[TOUCH] button

58

[SUSUTAIN] button

59

[HARMONY / ECHO] button

60

[MONO] button

61

[DSP] button

62

[VARIATION] button

VOICE EFFECT

46

[1 ] - [8 ] buttons

47

[BACK] button

48

[NEXT] button

49

VOICE PART ON / OFF [MAIN] button

50

VOICE PART ON / OFF [LAYER] button

51

VOICE PART ON / OFF [LEFT] button

52

[ENTER] button

53

[DATA ENTRY] dial

54

[EXIT] button

55

[LCD CONTRAST] knob

Page 6

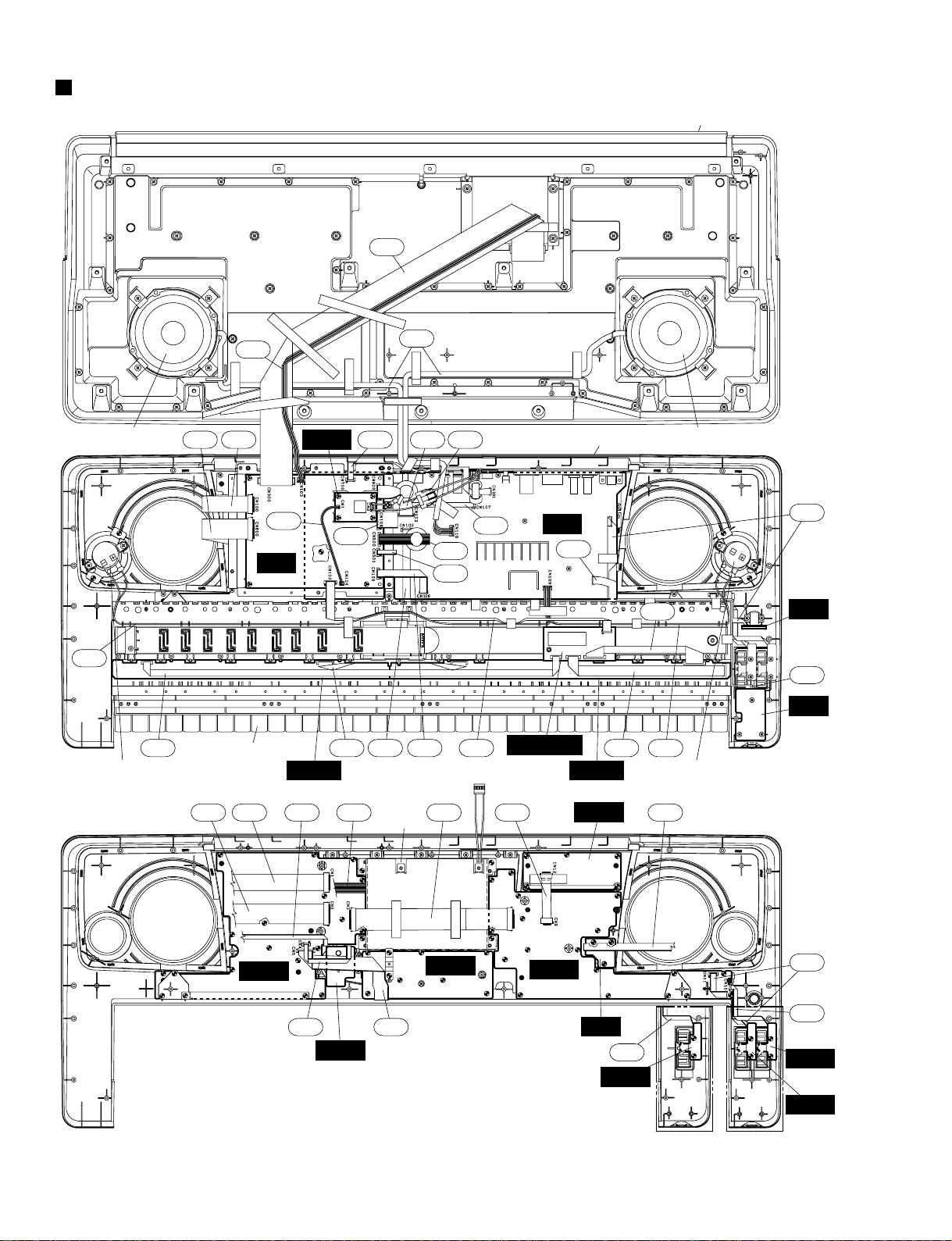

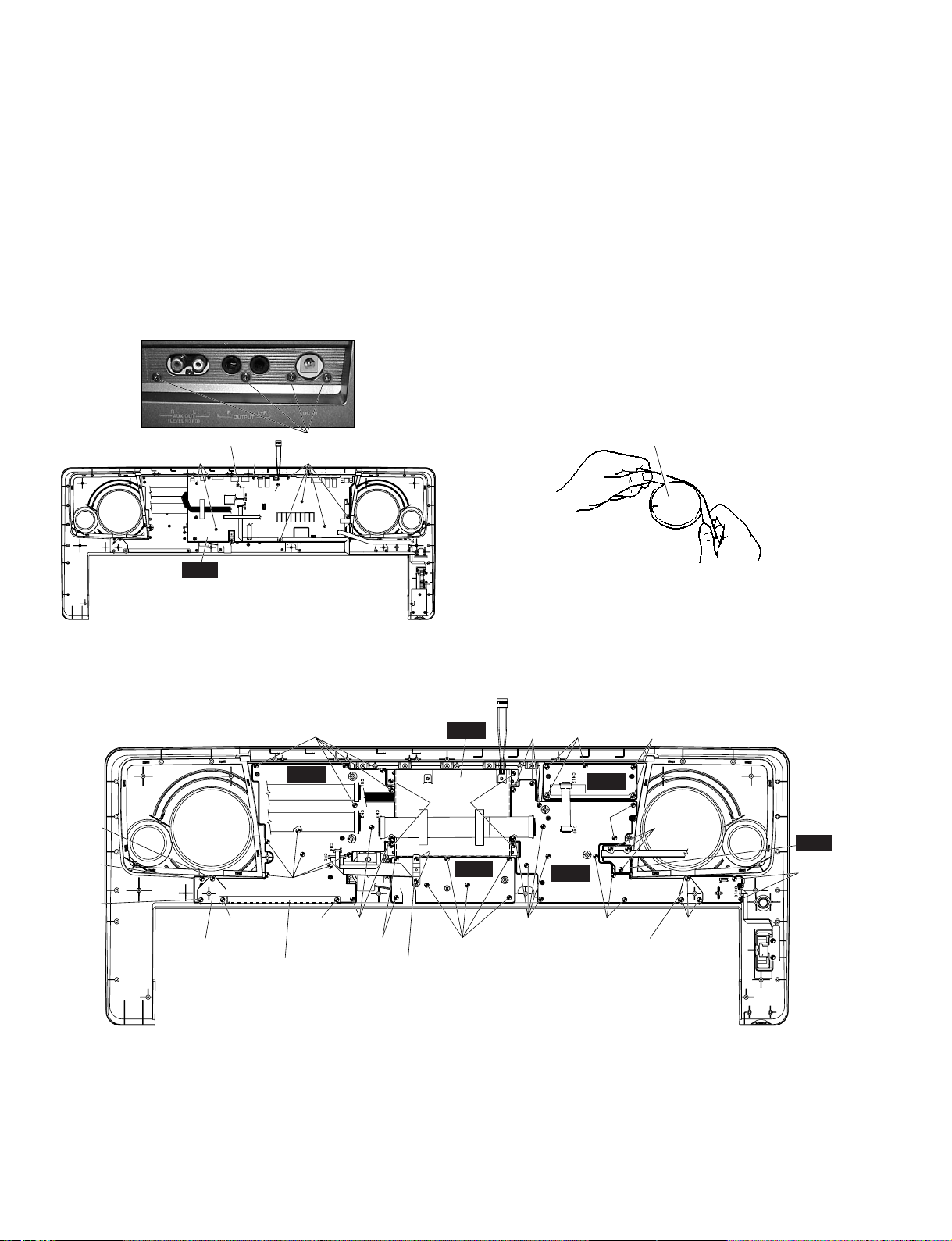

WH008

WH007

DM

VR

INV

AM

SW

HP

WH003

170

WH002

WH013

WH007

U410

LCD

Keyboard assembly

Speaker L (Tweeter)

PN1

PN2

ENC

PN3

PB1

PB2

MOD

PN4

MKS5F

MK-LMK-H

370

L110

180WH012U380U370

L160

L170

WH006WH005S5 150 160S6

S4

S7

160

U370 U380 WH013 U390U410

WH001

WH010

WH010

WH011

WH009

U400 WH005

<PSR-1000> <PSR-2000>

Speaker R (Tweeter)

Speaker R (Woofer)

Speaker L (Woofer)

Upper case assembly

Lower case assembly

PSR-1000/PSR-2000

6

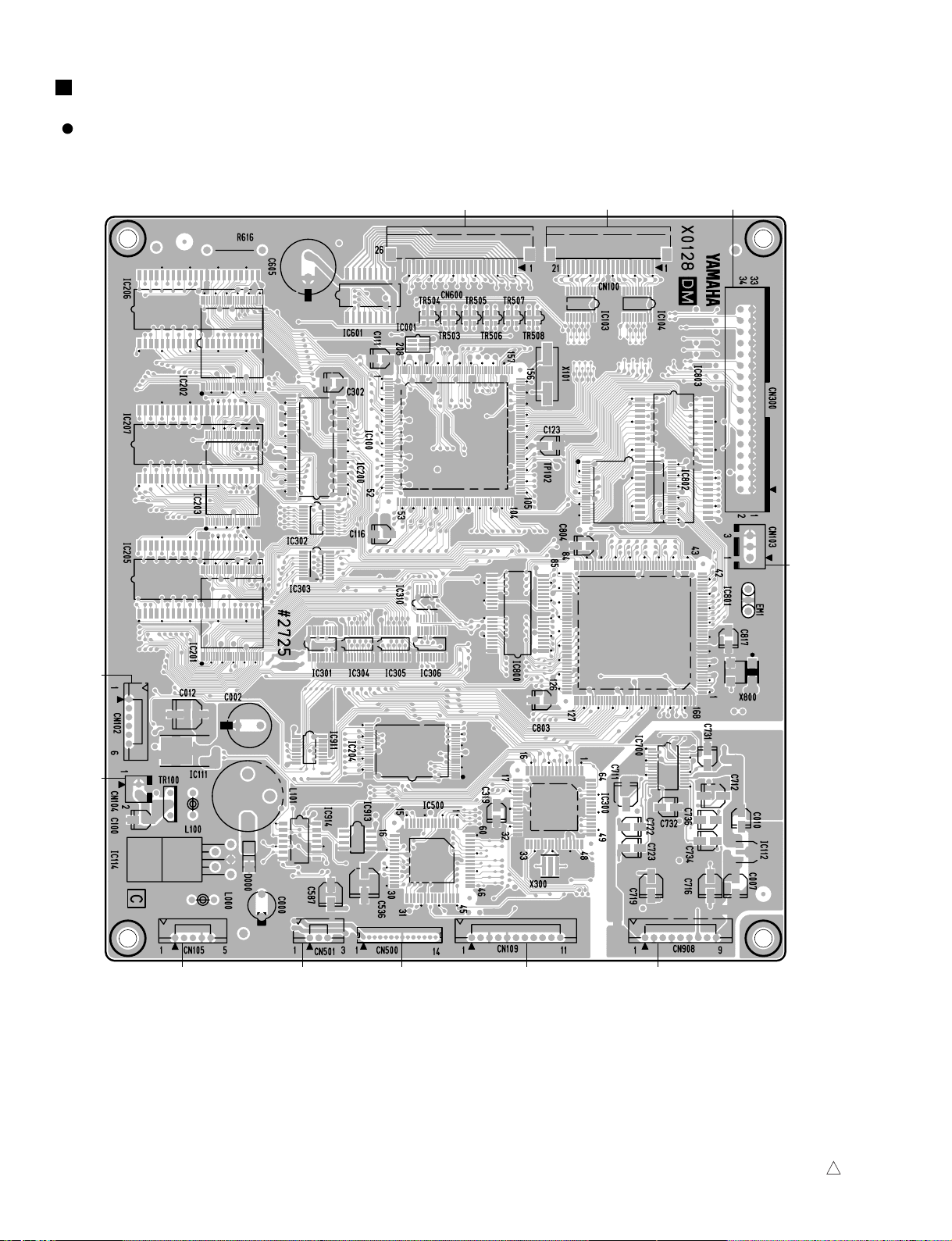

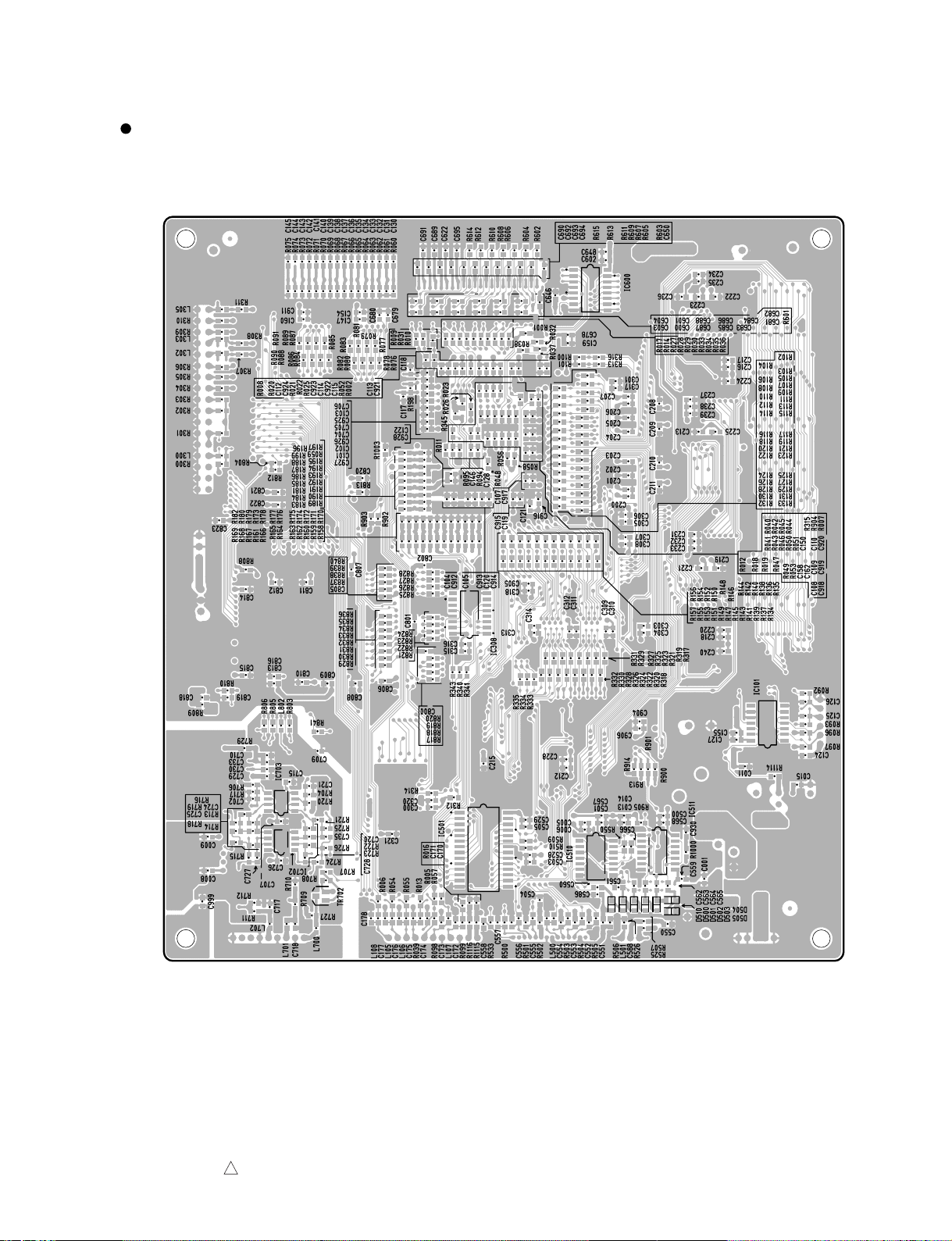

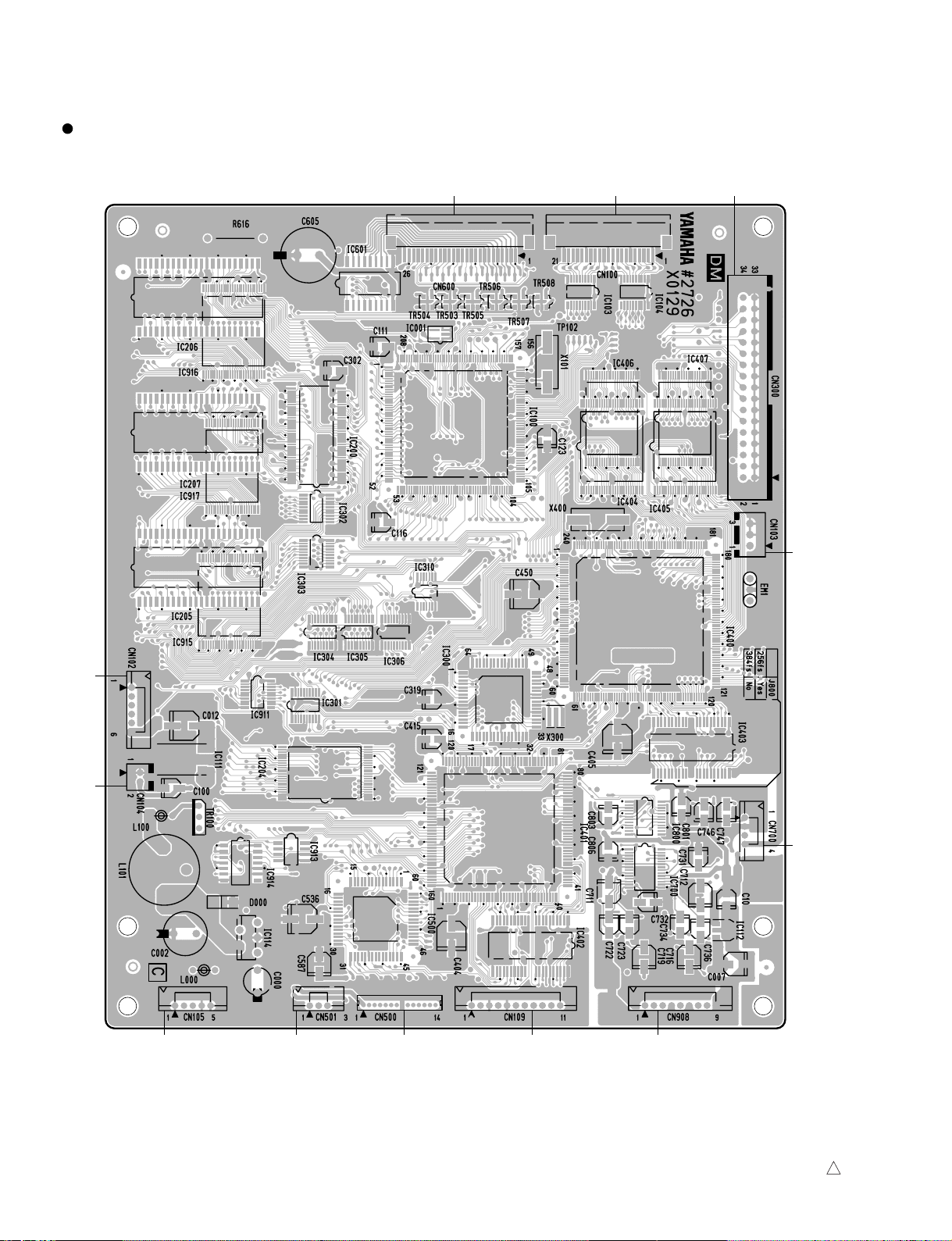

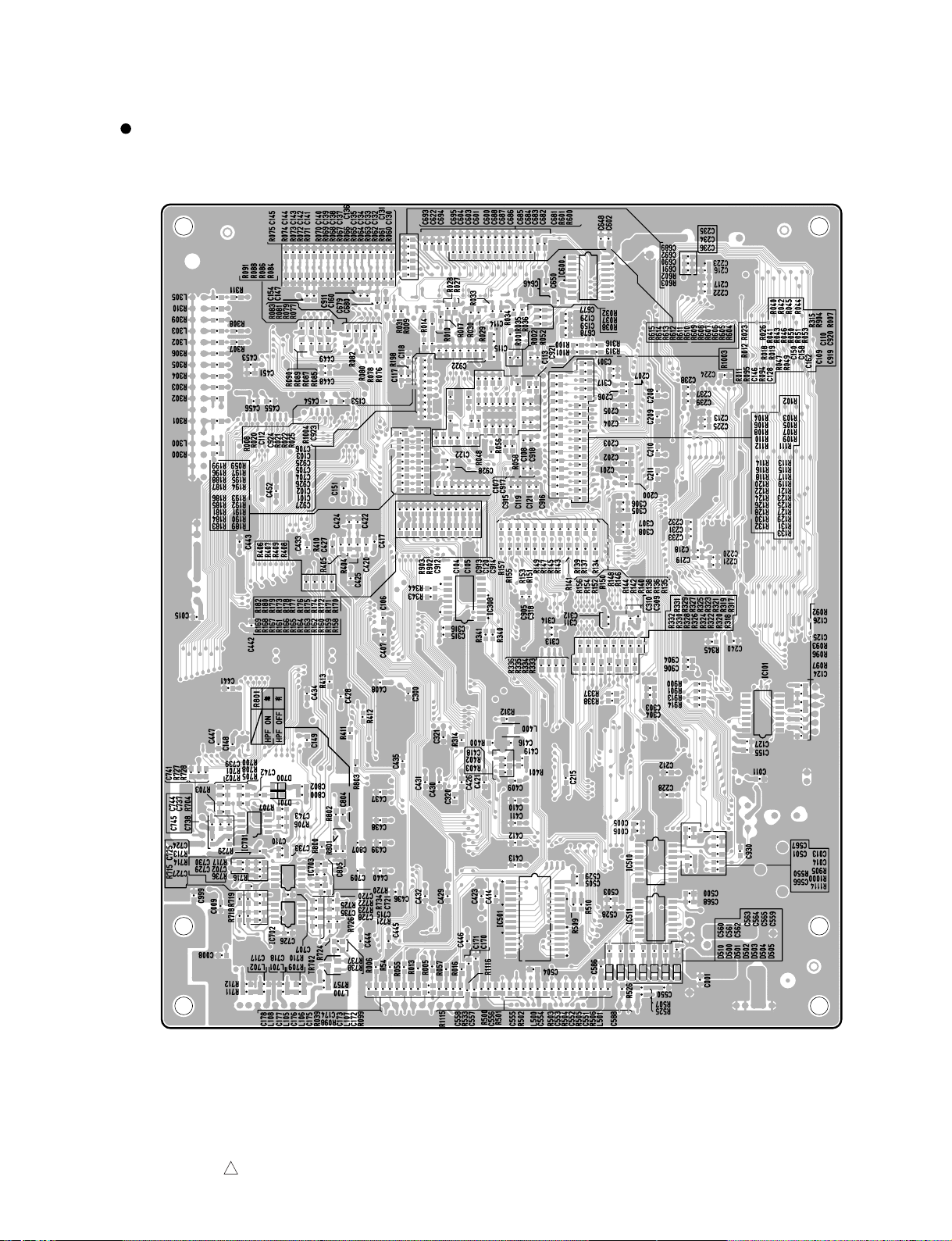

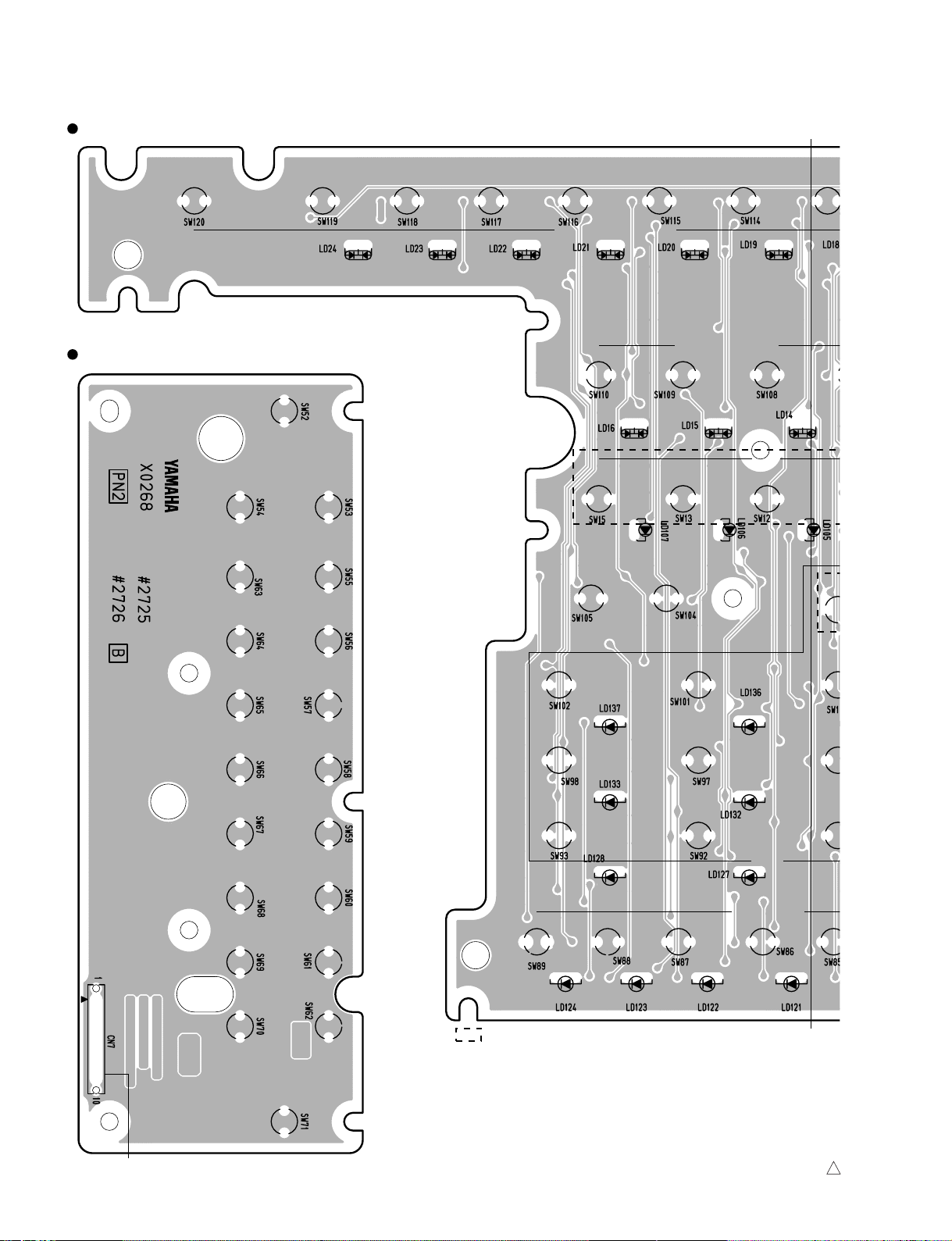

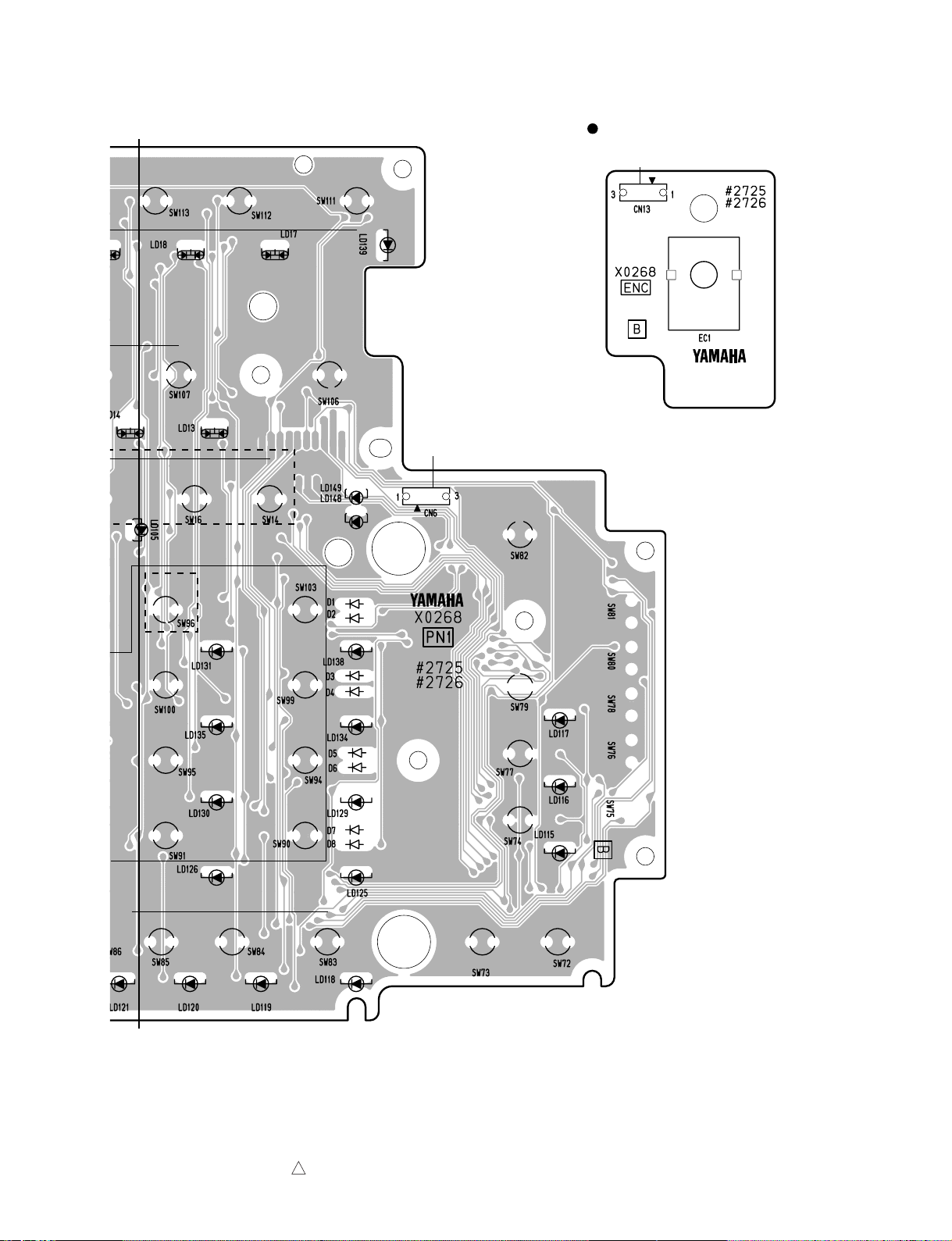

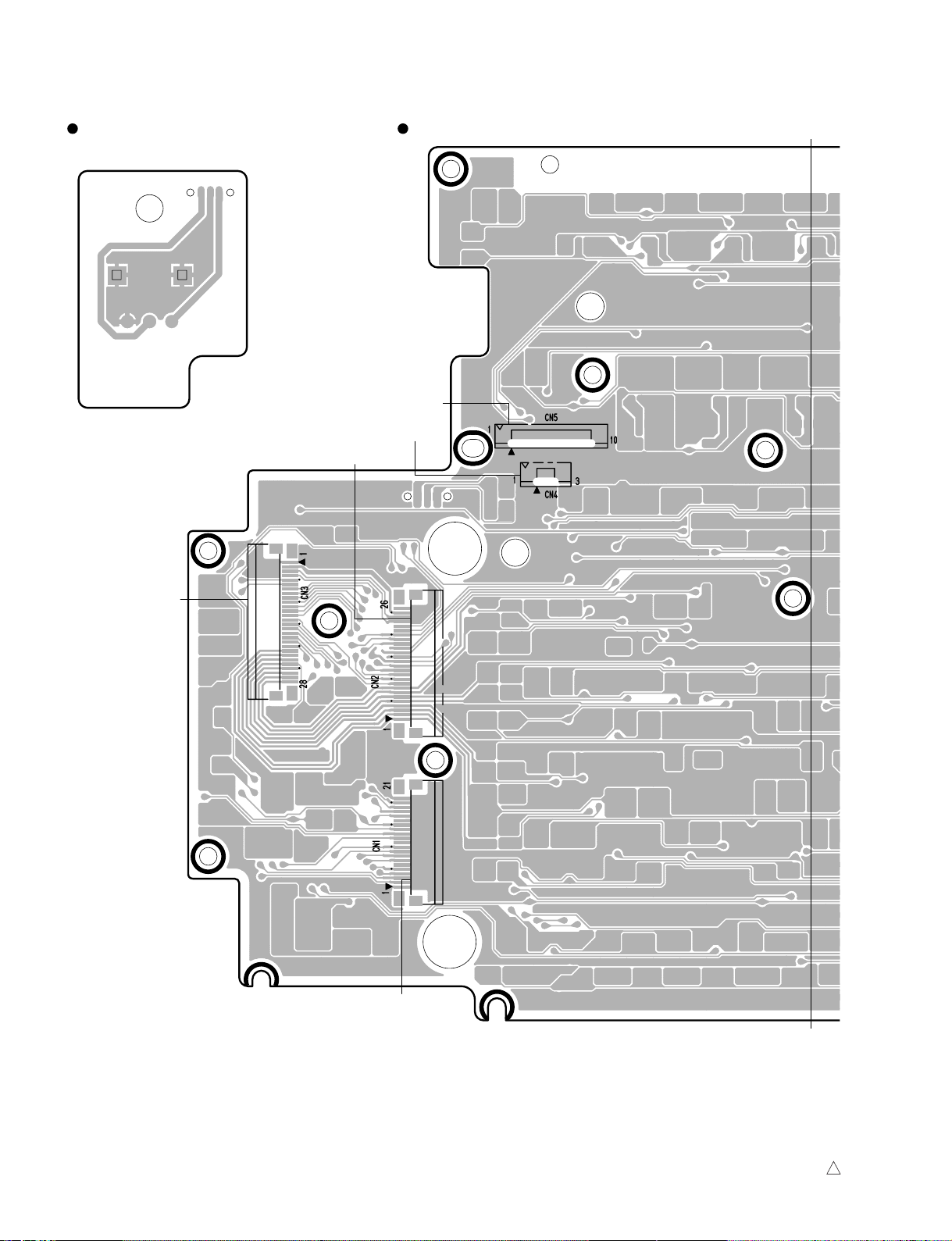

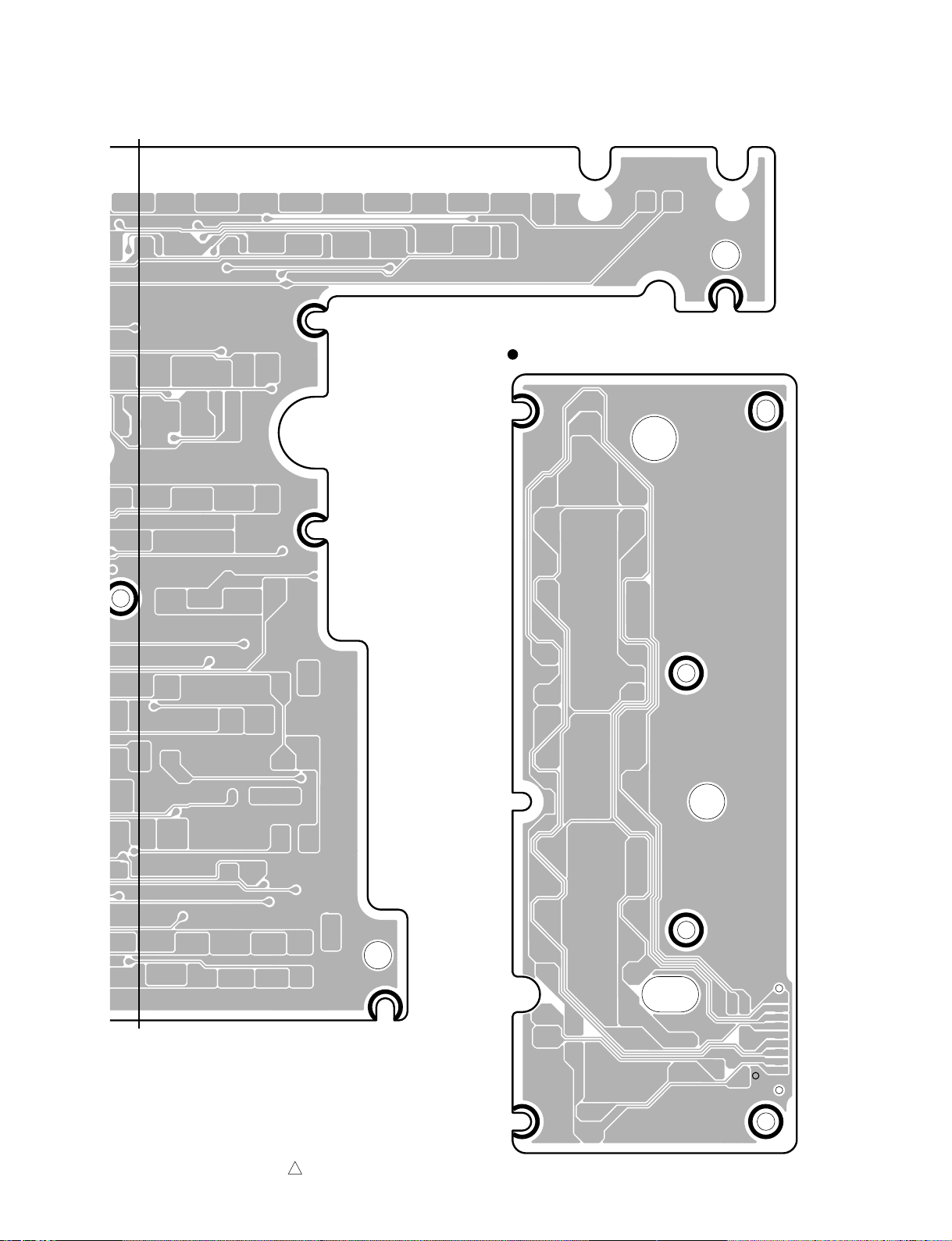

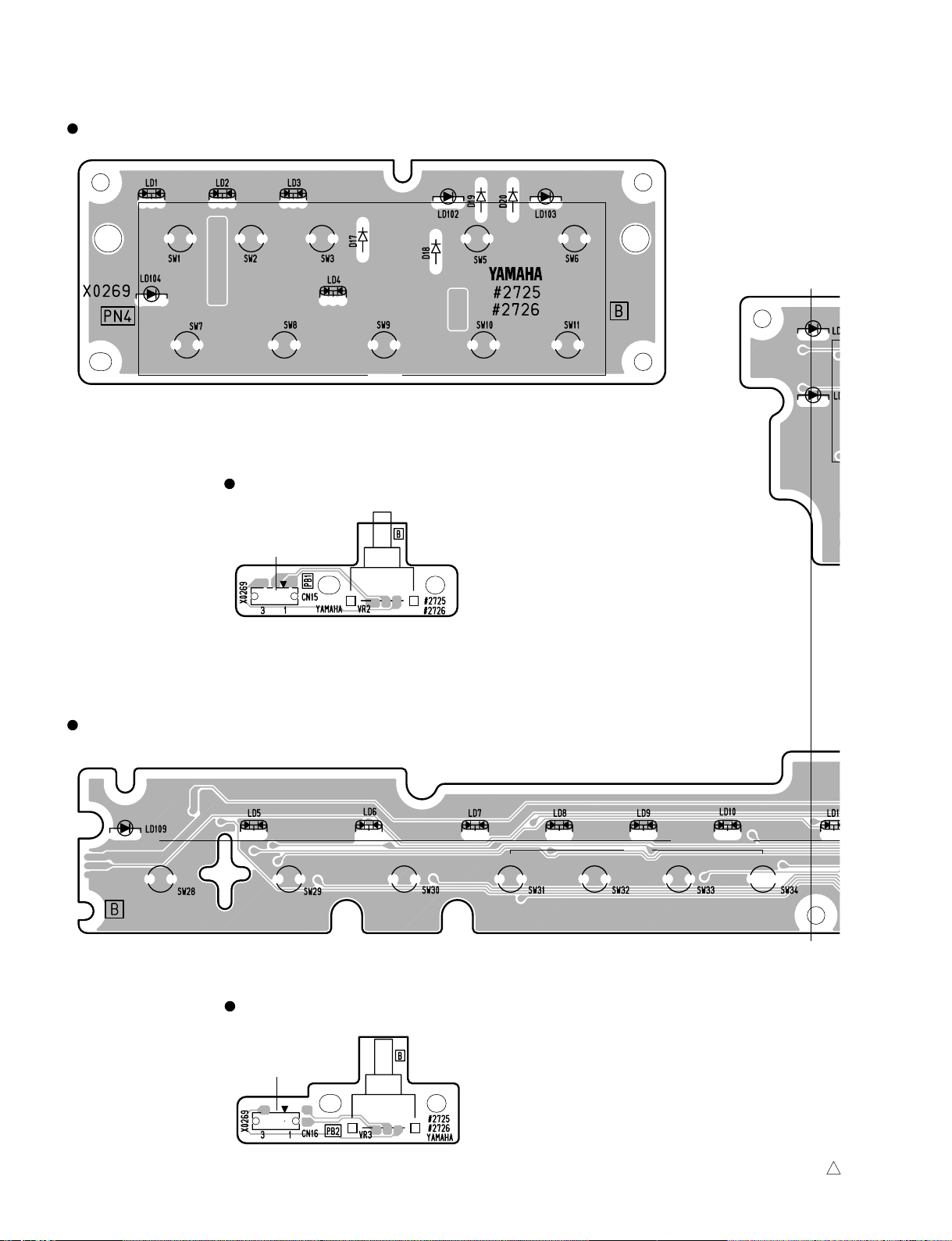

CIRCUIT BOARD LAYOUT

Page 7

U410

WH005

L160

L170

U370

U380

WH001

WH002

WH003

WH006

WH009

WH010

WH011

WH012

WH013

Speaker (Woofer)

MKS5F-CN1 *1 *1

*1 *2

*1

*1 *1

*2

*1

*1

*1

*1

*1

*1

*1

*1

*1

*1

*2

Speaker (Tweeter)

AM-CN110

DM-CN102

AM-CN109

5P L=800

6P

4P L=800

SP

KB

TW

Connector AssemblyPart No.

(V778250)

(V778240)

(V778260)

Location Destination Remarks

LCD

VR-CN100

FDD

FDD

PN1-CN2

PN1-CN1

PN2-CN7

AM-CN303

AM-CN300

DM-CN500 14P

AM-CN102 5P L=480

DM-CN300 34P

DM-CN103 3P L=700

DM-CN600 26P

DM-CN100 21P

PN1-CN5 10P L=200

DM-CN501 3P L=120

DM-CN109 11P L=120

LCD

VOL

FD

FDPS

PN1

PN2

PN5

CNT

DJ

(V815820)

S4

MK-L MKS5F-CN2 12PCableVU958900

S5

MK-L MK-H 12PCableVU659500

S6

MK-L MKS5F-CN3 7PCableVU659400

S7

MK-H MKS5F-CN4 5PCableVU659600

(V778150)

V7782900

V7780900

(V778070)

(V778080)

(V778110)

(V778120)

(V778130)

AM-CN106 DM-CN105 5P L=120PS(V778160)

ENC-CN13 PN1-CN4 3P L=100ENC(V778190)

PB1-CN15

PN3-CN10

PB2-CN16

3P L=130

3P L=130

(PSR-1000)

(PSR-2000)

(PSR-2000)

(PSR-2000)

(PSR-2000)

PB(V778200)

MOD-CN14 PN3-CN11 4P L=130MOD(V778210)

AM-CN101 DM-CN700 4P L=300MIC(V778220)

PN1-CN6 AM-CN107 3P L=480IND(V778230)

* The parts with “( )” in “Part No.” are not available as service parts.

*1:

*2:

Edge mark is adjusted to Pin 1 mark ( mark).

Red wire is adjusted to Pin 1 mark ( mark).

L110

150

160

INV-CN1 DM-CN104 2P L=200INVP(V778270)

170

INV-CN2 LCD 4P L=100INV(V778280)

180

AM-CN103

PN1-CN3

PN3-CN9

DM-CN908

PN3-CN8

PN4-CN12

9P

28P 300mm

11P 100mm

AN2

CARD

CARD

(V815810)

MFA28300

MFA11100

370

U390

U400

WH007

HP-CN111 AM-CN108 5P L=380HP(V778170)

WH008

SW-CN104 AM-CN105 6P L=320SW(V778180)

PSR-1000/PSR-2000

7

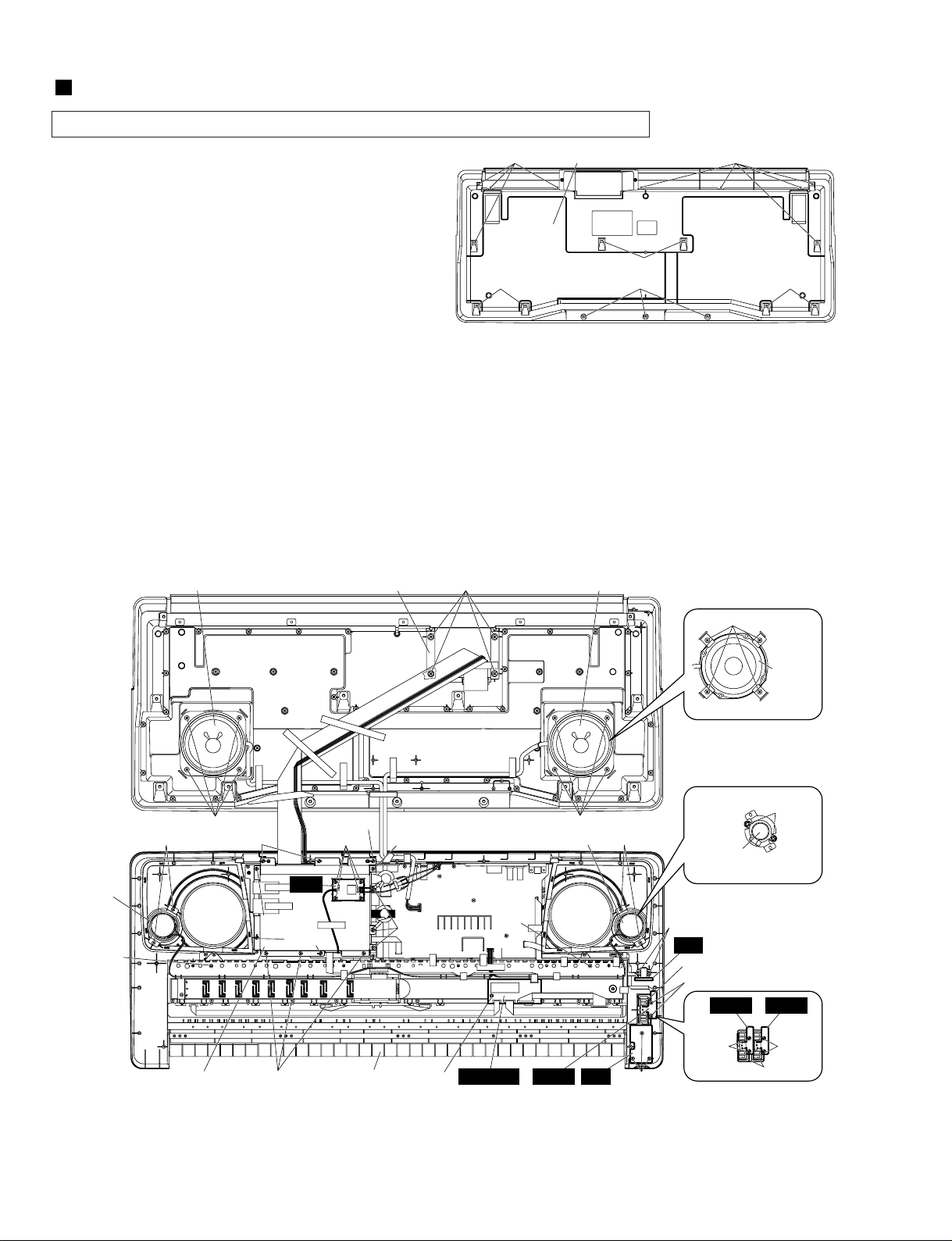

Page 8

[270A]

[250B]

[30]

[510A]

[340]

[270B][260A][270C]

[270C]

[270C]

[100A]

[50] Woofer LFloppy disk drive assembly

Keyboard assembly

Wheel assembly

Shield cover L

[270B]

[100A]

Woofer R

[250B]

[260B]

[260B]

[260B]

[260B]

* This figure shows the PSR-1000.

[100B]

* PSR-2000

Woofer

[30]: Bind Head Tapping Screw-P 3.0x16 MFZN2BL (EP630220)

[50]: Bind Head Tapping Screw-P 4.0x16 MFZN2Y (VM839600)

[100]: Bind Head Tapping Screw-P 4.0x10 MFZN2Y (EP640500)

[250B]: Bind Head Tapping Screw-P 3.0x25 MFZN2Y (VK228100)

[260]: Bind Head Tapping Screw-B 3.0x6 MFZN2Y (EP600130)

[270]: Bind Head Tapping Screw-P 3.0x8 MFZN2Y (EP600280)

[290]: Bind Head Tapping Screw-B 4.0x6 MFZN2BL (EP600370)

[340]: Flat Head Tapping Screw-B 3.0x8 MFZN2Y (EP600420)

[510]: Bind Head Tapping Screw-P 3.0x8 MFZN2Y (EP600280)

Tweeter R

Tweeter L

INV

HPMKS5F

[290]

Tweeter

* PSR-2000

SW

PB2

[510B] [510A]

Wheel

* PSR-2000

PB1MOD

(Fig. 2)

PSR-1000/PSR-2000

8

DISASSEMBLY PROCEDURE

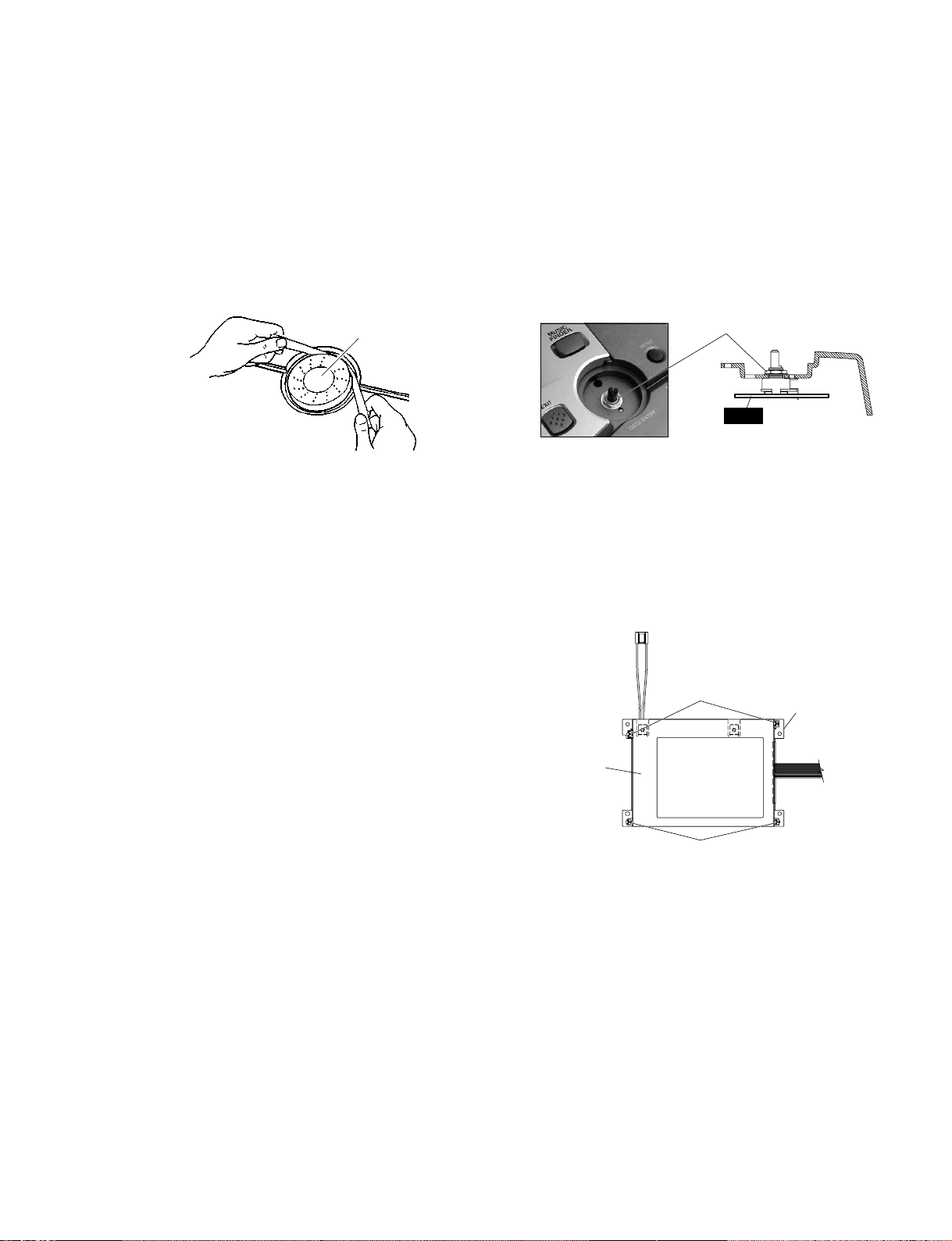

1. Lower Case Assembly (Time required: About

5 minutes)

1-1 Remove the sixteen (16) screws marked [240] and the two

(2) screws marked [250A]. The lower case assembly can

then be removed. (Fig. 1)

2. HP Circuit Board

(Time required: About 10 minutes)

2-1 Remove the lower case assembly. (See procedure 1.)

2-2 Remove the three (3) screws marked [270A]. The HP

circuit board can then be removed. (Fig. 2)

3. Wheel Assembly, PB2 Circuit Board (PSR-

1000), PB1 Circuit Board (PSR-2000)

(Time required: About 10 minutes)

3-1 Remove the lower case assembly. (See procedure 1.)

3-2 Remove the two (2) screws marked [510A]. The PB2 ( or

PB1) circuit board with the wheel assembly can then be

removed. (Fig. 2)

3-3 Remove the wheel assembly from the PB2 (or PB1)

circuit board. (Fig. 3)

4. MOD Circuit Board (PSR-2000 only)

(Time required: About 10 minutes)

4-1 Remove the lower case assembly. (See procedure 1.)

4-2 Remove the two (2) screws marked [510B]. The MOD

circuit board with the wheel can then be removed. (Fig. 2)

4-3 Remove the wheel from the MOD circuit board. (Fig. 3)

(Fig. 1)

[240]: Bind Head Tapping Screw-P 3.0x12 MFZN2Y (EP600300)

[250A]: Bind Head Tapping Screw-P 3.0x25 MFZN2Y (VK228100)

[240]

[240] [240] [240]

[250A]

[240]Lower case assembly

Caution: Be sure to attach the removed filament tape just as it was before removal.

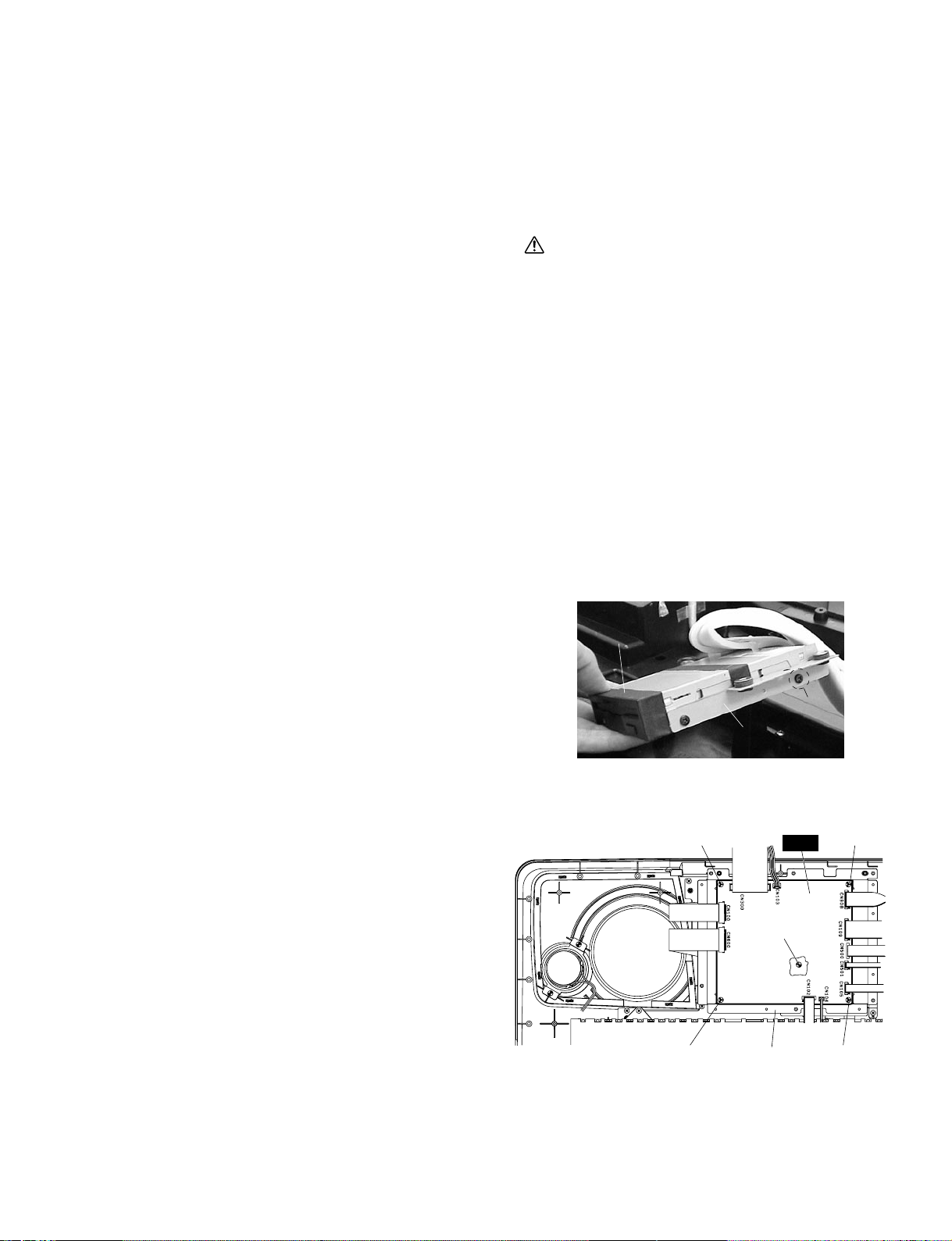

Page 9

5. SW Circuit Board

(Time required: About 10 minutes)

5-1 Remove the lower case assembly. (See procedure 1.)

5-2 Remove the two (2) screws marked [340]. The SW circuit

board can then be removed. (Fig. 2)

5-3 Remove the red knob from the SW circuit board.

6. Tweeter (PSR-1000)

(Time required: About 10 minutes)

6-1 Remove the lower case assembly. (See procedure 1.)

6-2 Remove the two (2) screws marked [270B]. The tweeter

can then be removed. (Fig. 2)

* The left and right tweeters can be removed in the respectively

same method.

7. Tweeter (PSR-2000)

(Time required: About 10 minutes)

7-1 Remove the lower case assembly. (See procedure 1.)

7-2 Remove the two (2) screws marked [290]. The tweeter can

then be removed. (Fig. 2)

* The left and right tweeters can be removed in the respectively

same method.

8. Woofer (PSR-1000)

(Time required: About 10 minutes)

8-1 Remove the lower case assembly. (See procedure 1.)

8-2 Remove the four (4) screws marked [100A]. The woofer

can then be removed. (Fig. 2)

* The left and right woofers can be removed in the respectively

same method.

9. Woofer (PSR-2000)

(Time required: About 10 minutes)

9-1 Remove the lower case assembly. (See procedure 1.)

9-2 Remove the four (4) screws marked [100B]. The woofer and

the four (4) speaker holders can then be removed. (Fig. 2)

* The left and right woofers can be removed in the respectively

same method.

10. Floppy Disk Drive

(Time required: About 10 minutes)

10-1 Remove the lower case assembly. (See procedure 1.)

10-2 Remove the four (4) screws marked [50]. The floppy disk

drive assembly can then be removed. (Fig. 2)

10-3 Remove the four (4) screws marked [F40]. The left and right

FDD holders can then be removed from the floppy disk

drive. (Fig. 3)

11. Keyboard Assembly

(Time required: About 10 minutes)

11-1 Remove the lower case assembly. (See procedure 1.)

11-2 Remove the two (2) screws marked [250B]. The keyboard

assembly can then be removed. (Fig. 2)

12. INV Circuit Board

(Time required: About 10 minutes)

ATTENTION: High Voltage

12-1 Remove the lower case assembly. (See procedure 1.)

12-2 Remove the four (4) screws marked [260A]. The INV

circuit board can then be removed. (Fig. 2)

13. DM Circuit Board, Shield Cover L and U

(Time required: About 15 minutes)

13-1 Remove the lower case assembly. (See procedure 1.)

13-2 Remove the INV circuit board. (See procedure 12.)

13-3 Remove the eight (8) screws marked [260B] and the five

(5) screws marked [270C]. The shield cover L can then be

removed. (Fig. 2)

13-4 Remove the four (4) screws marked [260C]. The DM

circuit board can then be removed. (Fig. 4)

13-5 Remove the screw marked [270D]. The shield cover U can

then be removed. (Fig. 4)

[F40]: Bind Head Tapping Screw 3.0x6 MFZN2BL (EG330360)

[F40]x4

(Fig. 3)

Floppy disk drive

FDD holder R

Shield cover U

[270D]

[260C]

[260C] [260C]

(Fig. 4)

[260C]: Bind Head Tapping Screw-B 3.0x6 MFZN2Y (EP600130)

[270D]: Bind Head Tapping Screw-P 3.0x8 MFZN2Y (EP600280)

DM

[260C]

PSR-1000/PSR-2000

9

Page 10

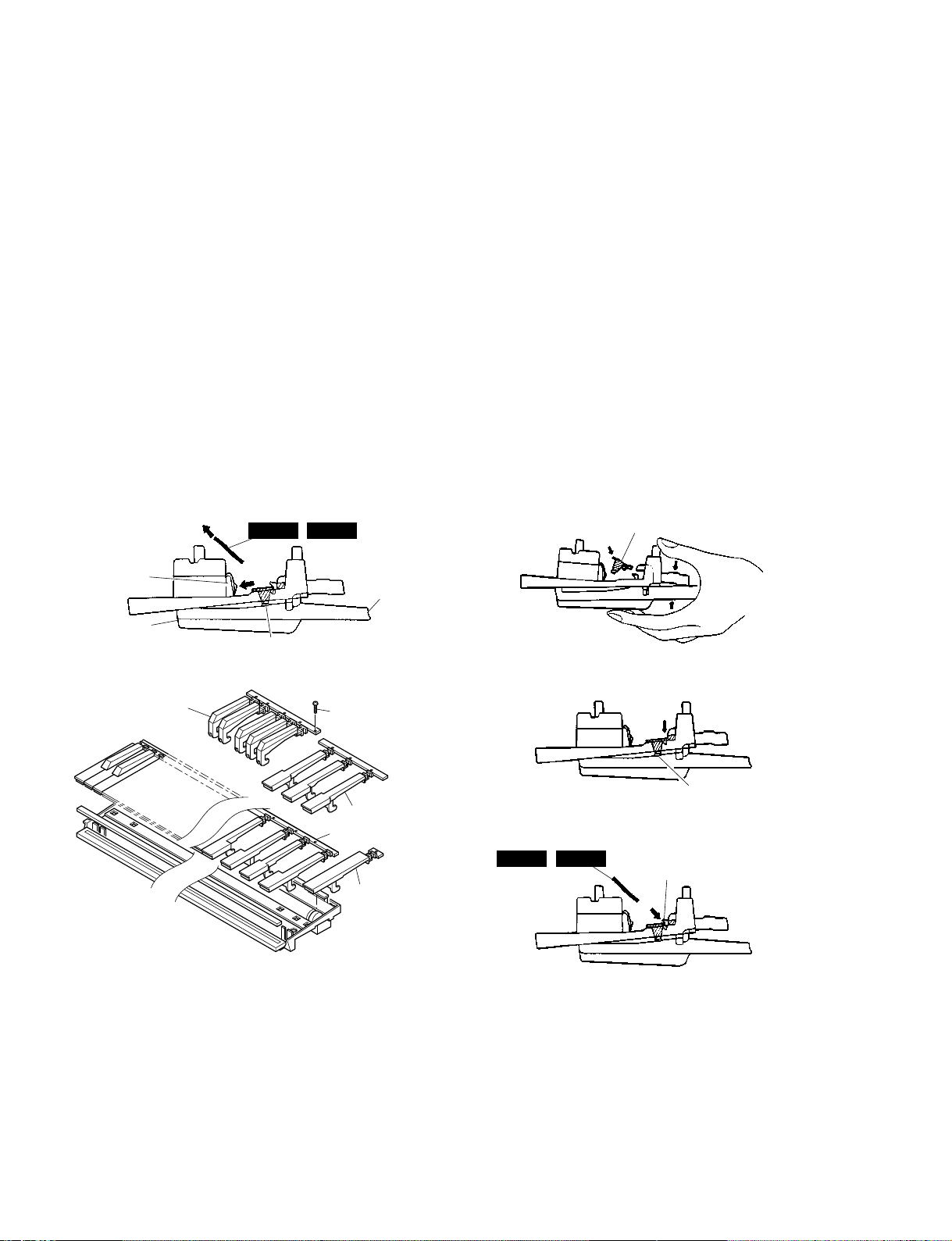

[510D]

[510D]

[510E]

[510C]

[510E]

[510E]

[510C] [510E] [510I] [510I]

[510G] [510G]

[510H]

[510I]

[270F]

[510I] [510J] [510J]

[510I]

[510F]

[510K]

Keyboard support (A) Keyboard support (B)

Panel angle bracket DM holder

[260D]: Bind Head Tapping Screw-B 3.0x6 MFZN2Y (EP600130)

[270E]: Bind Head Tapping Screw-P 3.0x8 MFZN2Y (EP600280)

[280]: Bind Head Tapping Screw-B 3.0x6 MFZN2BL (EP600230)

[260D]

[270E] [270E]

[260D]

[270E]

[280]

• Rear view

(Fig. 5)

[270F]: Bind Head Tapping Screw-P 3.0x8 MFZN2Y (EP600280)

[510]: Bind Head Tapping Screw-P 3.0x8 MFZN2Y (EP600280)

(Fig. 7)

(Fig. 6)

AM

PN1

PN2

PN4

PN3

Volume knob

VR

LCD

PSR-1000/PSR-2000

10

14. AM Circuit Board

(Time required: About 15 minutes)

14-1 Remove the lower case assembly. (See procedure 1.)

14-2 Remove the INV circuit board. (See procedure 12.)

14-3 Remove the shield cover L, the DM circuit board and the

shield cover U. (See procedure 13.)

14-4 Remove the two (2) screws marked [260D], the nine (9)

screws marked [270E] and the four (4) screws marked

[280]. The AM circuit board can then be removed. (Fig. 5)

15. VR, ENC, PN1, PN2, PN3, PN4 Circuit Boards and LCD

15-1 Remove the lower case assembly. (See procedure 1.)

15-2 Remove the INV circuit board. (See procedure 12.)

15-3 Remove the shield cover L, the DM circuit board and the

shield cover U. (See procedure 13.)

15-4 Remove the AM circuit board. (See procedure 14.)

15-5 VR Circuit Board

(Time required: About 20 minutes) :

15-5-1 Remove the volume knob from the control panel side.

(Fig. 6)

15-5-2 Remove the three (3) screws marked [270F]. The VR

circuit board can then be removed. (Fig. 7)

Page 11

15-6 ENC Circuit Board

(Time required: About 20 minutes) :

15-6-1 Remove the encoder knob from the control panel side.

(Fig. 8)

15-6-2 Remove the hexagonal nut marked [A]. The ENC circuit

board can then be removed. (Fig. 9)

15-7 PN1 Circuit Board

(Time required: About 25 minutes) :

15-7-1 Remove the keyboard assembly. (See procedure 11.)

15-7-2 Remove the two (2) screws marked [510C]. The panel

angle blacket can then be removed. (Fig. 7)

15-7-3 Remove the two (2) screws marked [510D]. The keyboard

support (A) can then be removed. (Fig. 7)

15-7-4 Remove the fifteen (15) screws marked [510E]. The PN1

circuit board can then be removed. (Fig. 7)

PSR-1000/PSR-2000

11

15-8 PN2 Circuit Board

(Time required: About 25 minutes) :

15-8-1 Remove the keyboard assembly. (See procedure 11.)

15-8-2 Remove the two (2) screws marked [510F]. The DM

holder can then be removed. (Fig. 7)

15-8-3 Remove the seven (7) screws marked [510G]. The PN2

circuit board can then be removed. (Fig. 7)

15-9 PN3 Circuit board

(Time required: About 25 minutes) :

15-9-1 Remove the keyboard assembly. (See procedure 11.)

15-9-2 Remove the three (3) screws marked [510H]. The

keyboard support (B) can then be removed. (Fig. 7)

15-9-3 Remove the fifteen (15) screws marked [510I]. The PN3

circuit board can then be removed. (Fig. 7)

15-10 PN4 Circuit board

(Time required: About 20 minutes) :

15-10-1

Remove the five (5) screws marked [510J]. The PN4

circuit board can then be removed. (Fig. 7)

15-11 LCD (Time required: About 20 minutes) :

15-11-1

Remove the four (4) screws marked [510K]. The LCD can

then be removed with the LCD holder. (Fig. 7)

15-11-2

Remove the four (4) screws marked [500]. The LCD

holder can then be removed from the LCD. (Fig. 10)

ENC

[A]

(Fig. 8) (Fig. 9)

Encoder knob

[500]: Bind Head Tapping Screw-B 3.0x6 MFZN2Y (EP600130)

(Fig. 10)

LCD holder

LCD

[500]

[500]

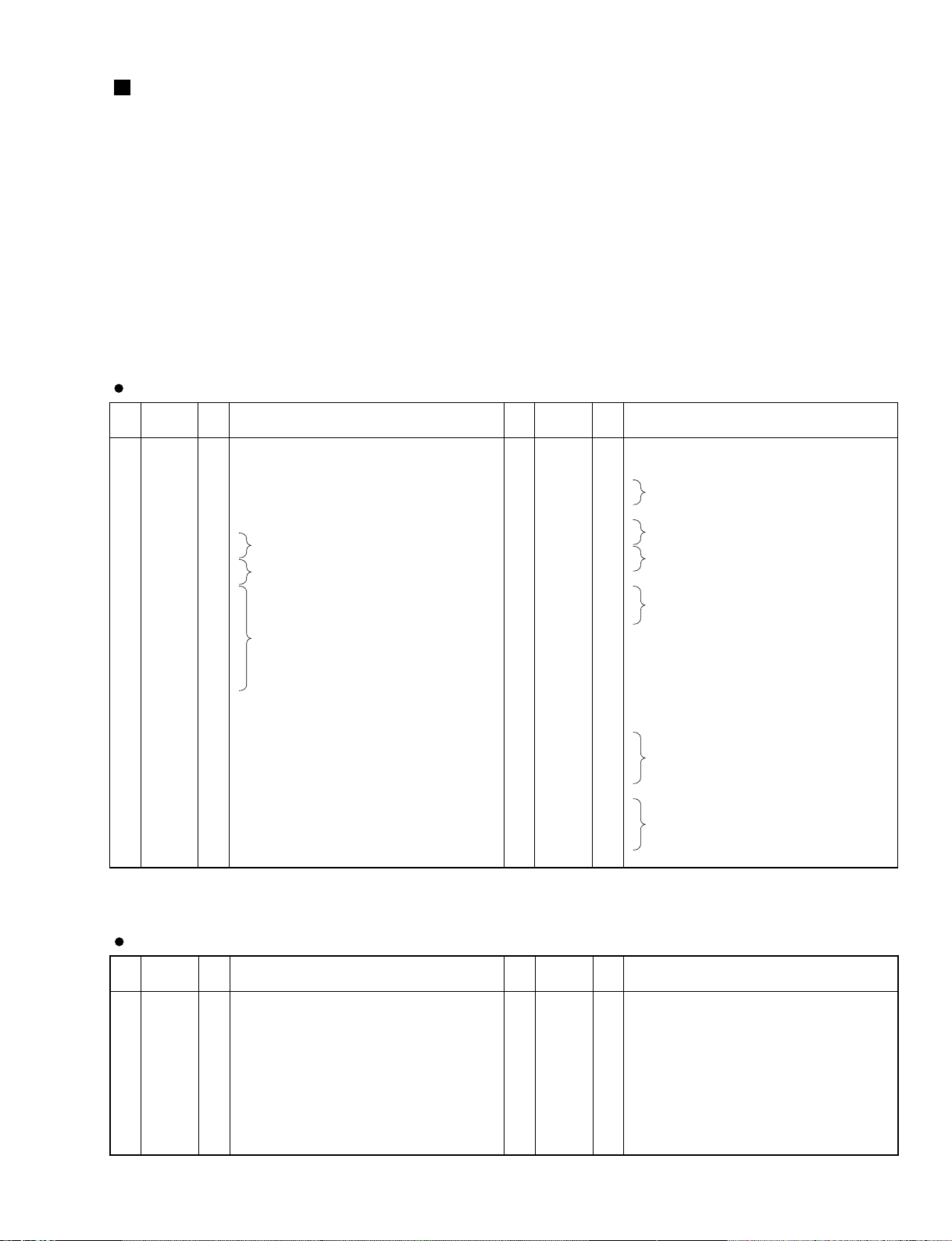

Page 12

PSR-1000/PSR-2000

12

[140]: Bind Head Tapping Screw-P 3.0x16 MFZN2BL (VB205200)

[140]: Bind Head Tapping Screw-P 3.0x16 MFZN2B (VS756700)

(Fig. 12) (Fig. 15)

MK-L MK-H,

MK-L MK-H,

Hooks A

Hooks B

Black key

Black key

Rubber contact

Rubber contact

Rubber contact

White key

White key C'

White key CEGB

White key DFA

(Fig. 11) (Fig. 13)

(Fig. 14)

[140]

16. Disassembling the Keyboard Assembly

16-1 Remove the Keyboard assembly. (See procedure 11.)

16-2 Remove the two (2) screws marked [30]. The MKS5F

circuit board can then be removed. (Fig. 2)

* Be sure to make a correct match when connecting

MKS5F (CN1) and DM (CN102).

Connecting the connectors in the wrong way

around may cause damage to the MKS5F circuit

board.

16-3 Remove the MK-L and MK-H circuit board while

pressing the fifteen (15)hooks A inward, and then remove

the rubber contact. (Fig. 11)

16-4 Remove the twenty-one (21) screws marked [140], then

removw the black keys from the lower notes. Afterwards,

remove the white keys DFA and C' and then remove the

white keys CEGB from the higer notes. At this time, lift

the keys from the front and slide them towards you. The

keys can then be removed from the assembly. (Fig. 12)

17. Assembling the Keyboard Assembly

17-1 Install the white keys CEGB from the lower notes, and

then install the DFA keys and C' key. Afterwards install

the black keys from the higher notes, and tighten the

twenty-one (21) screws marked [140]. (Fig. 12)

17-2 Install the rubber contacts in the assembly while pressing

the keys as shown in Figure13. Check that the rubber

contact has been firmly placed into position in the area

indicated by the arrow in Figure 14. When fitting the

rubber contacts, raise both ends of the frame so that keys

do not push the rubber contact up.

17-3 Install the MK-L and MK-H circuit boards in the assembly

so that the hooks B hold it as shown in Figure 15.

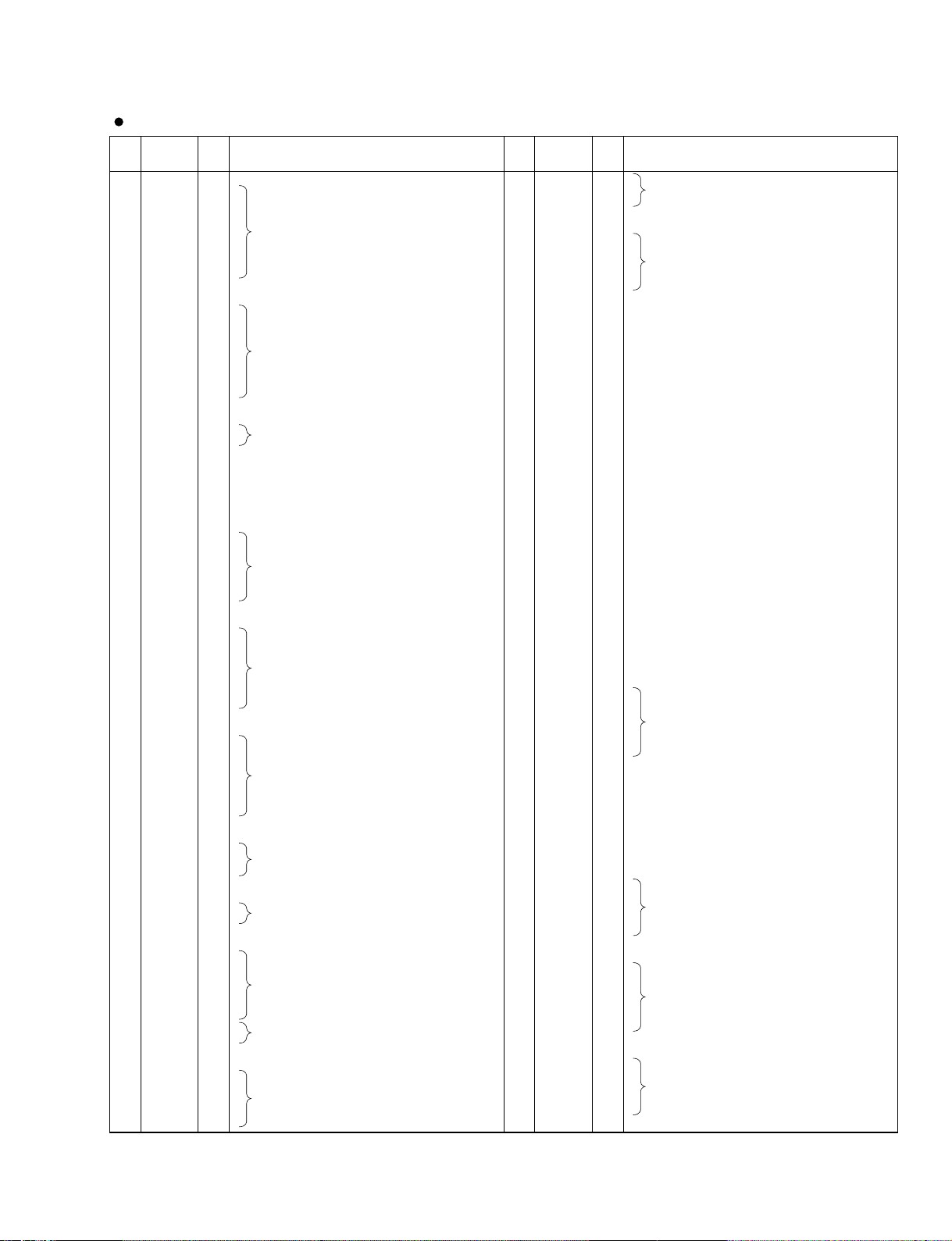

Page 13

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

AINR+

AINRVREF

VA

AGND

AINL+

AINLTST1

HPFE

TST2

TST3

VD

I

I

O

-

I

I

I/O

I/O

I/O

-

Analog signal input (R channel +)

Analog signal input (R channel -)

Reference voltage

Analog power supply

Analog ground

Analog signal input (L channel +)

Analog signal input (L channel -)

Test mode setting 1

HPF on/off

Test mode setting 2

Test mode setting 3

Digital power supply

13

14

15

16

17

18

19

20

21

22

23

24

DGND

TST4

AMODE2

/PD

MCLK

SCLK

LRCK

FSYNC

SDATA

CMODE

SMODE1

VB

-

I/O

I

I

I/O

I

I/O

O

I

I

-

Digital ground

Test mode setting 4

Interface clock select 2

Power-down mode

Master clock input

Serial data clock

Input/Output channel clock

Frame synch. clock

Serial data output

Master clock select

Interface clock select 1

Digital power supply

AK5351-VF-E2 (XV510A00) ADC (Analog to Digital Converter)

DM: IC800 (PSR-2000)

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

8"//5"

XTALSET

/RESET

E//RD

RW//WR

/CS

/DACK

RS0

RS1

VSS1

VSS2

D0

D1

D2

D3

D4

D5

D6

D7

/DREQ

/IRQ

/DEND

VSS3

1/2 EX1

VCC1

NUM1

NUM3

IFS

SFORM

/INP

/READY

/WPRT

I

I

I

I

I

I

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

I

I

I

I

I

I

I

I

Data transmission speed

Clock select

Rest

Enable/Read

Read/write/Write

Chip select

DMA acknowledge

Register select

Ground

Data bus

DMA request

Interrupt request

Data end

Ground

Power supply

Host interface select

Format data

Index pulse

Ready from FDD

Write control signal

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

/TRKO

/INDEX

/RDATA

XTAL2

EXTAL2

NC

XTAL1

EXTAL1

VSS4

VSS5

NC

VCC2

VCC3

VCC4

/WGATE

/WDATA

VSS6

/STEP

/HDIR

/HLOAD

/HSEL

VSS7

/DS0

/DS1

/DS2

/DS3

VSS8

/MON0

/MON1

/MON2

/MON3

VSS9

I

I

I

O

O

O

O

O

O

O

O

O

O

O

O

O

O

Track 00 signal

Index signal

Read data input from FDD

Clock

Clock

Ground

Power supply

Write control

Writ data to FDD

Ground

Step signal to control head of FDD

Direction

Head load

Head select

Ground

Drive select

Ground

Motor on

Ground

HD63266F (XI939A00) FDC (Floppy Disk Controller)

DM: IC300

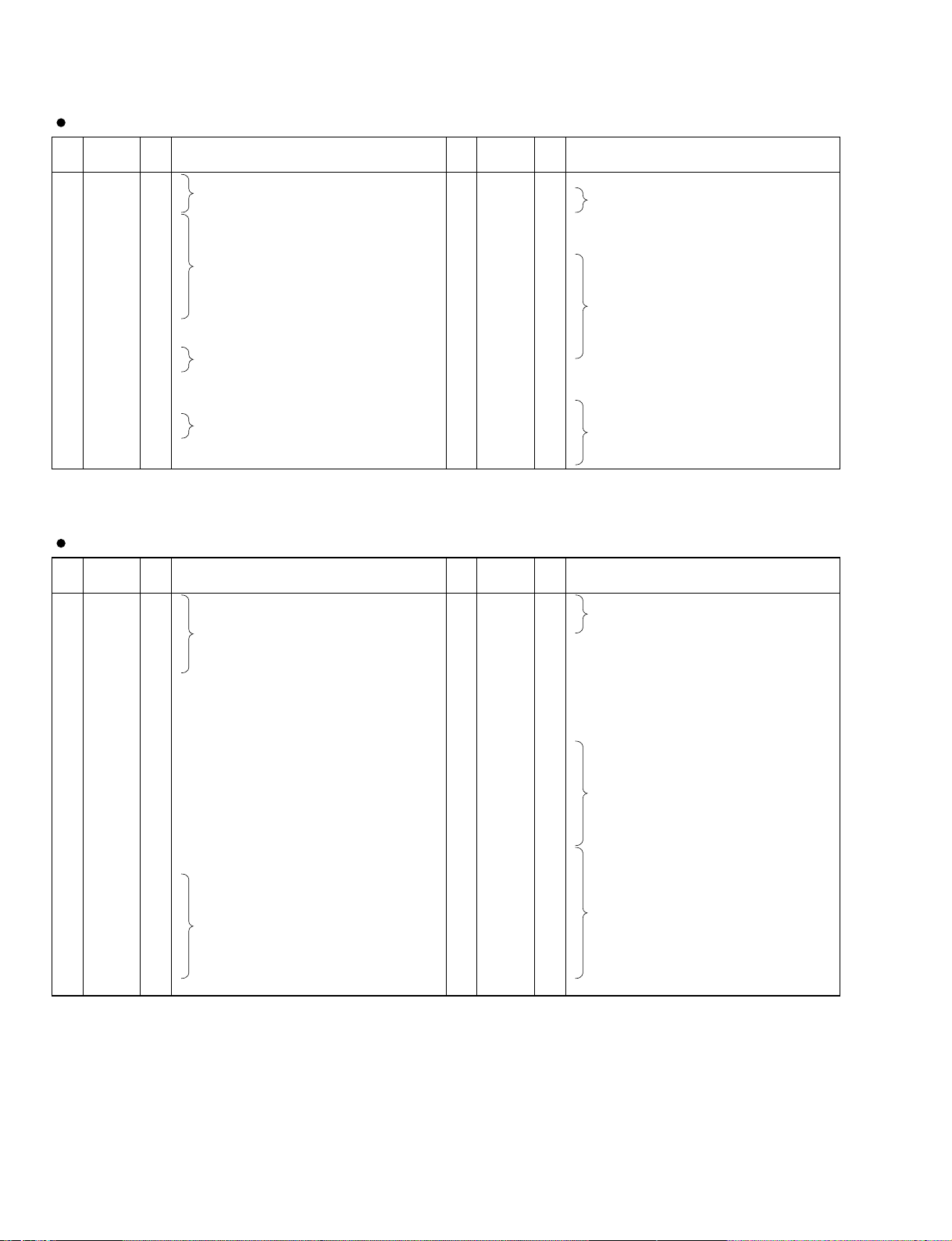

LSI PIN DESCRIPTION

PSR-1000/PSR-2000

13

HD63266F (XI939A00) FDC················································································································· 13

AK5351-VF-E2 (XV510A00) ADC ········································································································ 13

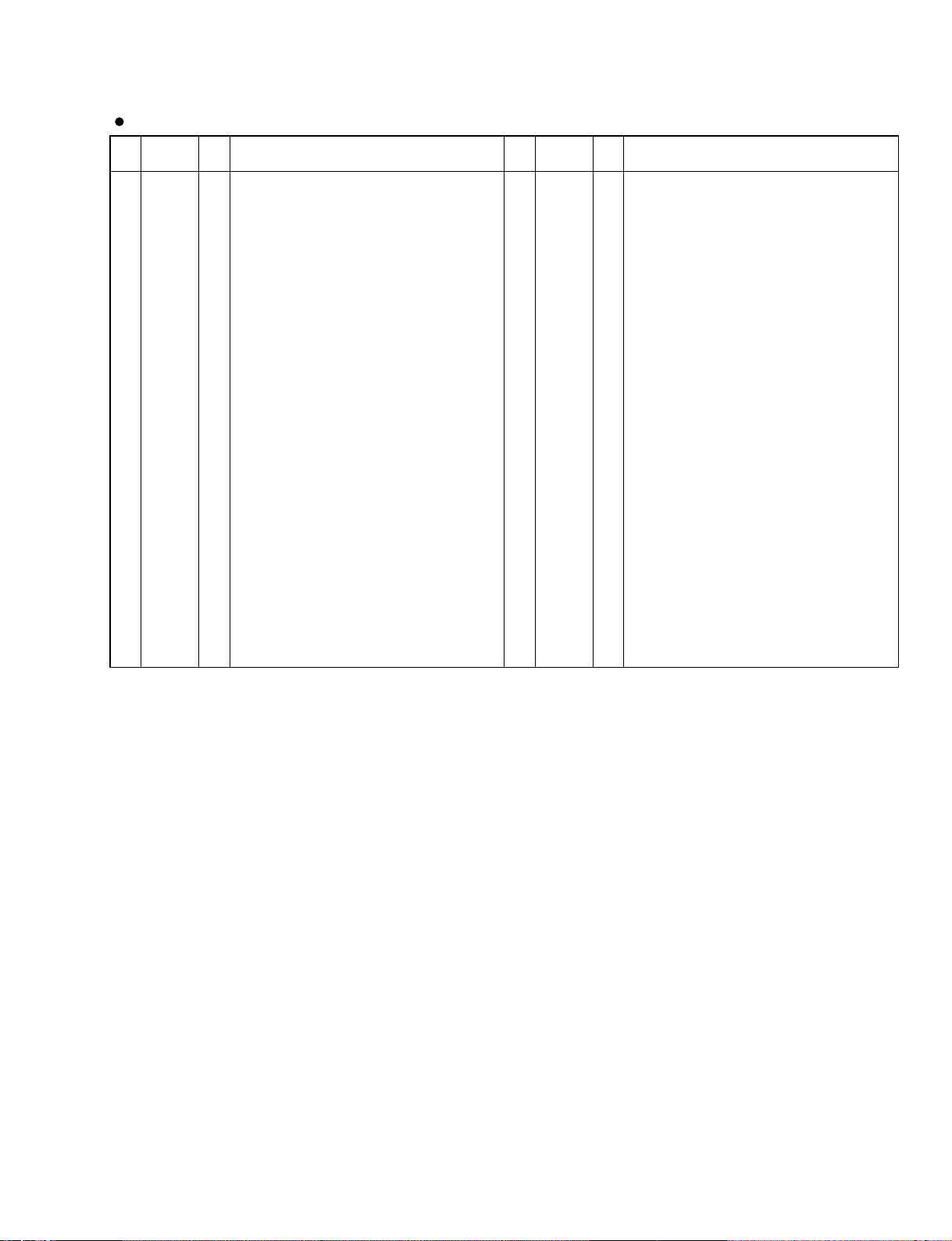

HD6417709F80B (XV250B00) CPU····································································································· 14

TC203C760HF-002 (XS725A00) SWP30B·························································································· 15

HG73C205AFD (XU947C00) SWX00B································································································ 16

YSS236-F (XT013A00) VOP3·············································································································· 17

µPD789022GB-A15-8E (XZ560100) CPU KBS···················································································· 18

S1D13305F00B100 (XQ595A00) LCDC ······························································································ 18

AD1854JRSRL (XY782A00) DAC········································································································ 19

Page 14

PSR-1000/PSR-2000

14

PIN

NO.

I/O

FUNCTION

NAME

PIN

NO.

I/O

FUNCTION

NAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

MD1

MD2

Vcc (RTC)

XTAL2

EXTAL2

Vss (RTC)

NMI

IRQ0/IRL0/PTH[0]

IRQ1/IRL1/PTH[1]

IRQ2/IRL2/PTH[2]

IRQ3/IRL3/PTH[3]

IRQ4/PTH[4]

D31/PTB[7]

D30/PTB[6]

D29/PTB[5]

D28/PTB[4]

D27/PTB[3]

D26/PTB[2]

Vss

D25/PTB[1]

Vcc

D24/PTB[0]

D23/PTA[7]

D22/PTA[6]

D21/PTA[5]

D20/PTA[4]

Vss

D19/PTA[3]

Vcc

D18/PTA[2]

D17/PTA[1]

D16/PTA[0]

Vss

D15

Vcc

D14

D13

D12

D11

D10

D9

D8

D7

D6

Vss

D5

Vcc

D4

D3

D2

D1

D0

A0

A1

A2

A3

Vss

A4

Vcc

A5

A6

A7

A8

A9

A10

A11

A12

A13

Vss

A14

Vcc

A15

A16

A17

A18

A19

A20

A21

Vss

A22

Vcc

A23

Vss

A24

Vcc

A25

BS/PTK[4]

RD

WE0/DQMLL

WE1/DQMLU/WE

WE2/DQMUL/ICIORD/PTK[6]

WE3/DQMUU/ICIOWR/PTK[7]

RD/WR

PTE[7]

Vss

CS0

Vcc

CS2/PTK[0]

CS3/PTK[1]

CS4/PTK[2]

CS5/CE1A/PTK[3]

CS6/CE1B

CE2A/PTE[4]

CE2B/PTE[5]

I

I

I

O

I

I

I

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

-

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

O

-

O

-

O

O

O

O

O

O

O

O

O

-

O

-

O

O

O

O

O

O

O

-

O

-

O

-

O

-

O

I/O

O

O

O

I/O

I/O

O

I/O

-

O

I/O

I/O

I/O

I/O

O

I/O

I/O

System clock

Power supply (3.3 V)

Clock

Clock

Ground (0 V)

Interrupt request

Interrupt request

Interrupt request

Data bus/ I/O port B

Ground (0 V)

Interrupt request

Power supply (3.3 V)

Data bus/ I/O port B

Data bus/ I/O port A

Ground (0 V)

Data bus/ I/O port A

Power supply (3.3 V)

Data bus/ I/O port A

Ground (0 V)

Data bus

Power supply (3.3 V)

Data bus

Ground (0 V)

Data bus

Power supply (3.3 V)

Data bus

Address bus

Ground (0 V)

Address bus

Power supply (3.3 V)

Address bus

Ground (0 V)

Address bus

Power supply (3.3 V)

Address bus

Ground (0 V)

Address bus

Power supply (3.3 V)

Address bus

Ground (0 V)

Address bus

Power supply (3.3 V)

Address bus

Bus control/ I/O port K

Read strobe

Select signal/DQM (SDRAM)

Select signal/DQM (SDRAM)/PCMCIA WE

Select signal/DQM (SDRAM)/PCMCIA I/O read/ I/O port K

Select signal/DQM (SDRAM)/PCMCIA I/O write/ I/O port K

Read/Write signal

I/O port E

Ground (0 V)

Chip select

Power supply (3.3 V)

Chip select/ I/O port K

Chip select/ I/O port K

Chip select/ I/O port K

Chip select/CE1/ I/O port K

Chip select/CE1

Chip enable/ I/O port E

Chip enable/ I/O port E

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

CKE/PTK[5]

RAS3L/PTJ[0]

RAS2L/PTJ[1]

CASLL/CAS/PTJ[2]

Vss

CASLH/PTJ[3]

Vcc

CASHL/PTJ[4]

CASHH/PTJ[5]

DACK0/PTD[5]

DACK1/PTD[7]

CAS2L/PTE[6]

CAS2H/PTE[3]

RAS3U/PTE[2]

RAS2U/PTE[1]

PTE[0]

BACK

BREQ

WAIT

RESETM

PTH[5]/ADTRG

IOIS16/PTG[7]

PTG[6]

PTG[5]

PTG[4]

PTG[3]

PTG[2]

Vss

PTG[1]

Vcc

PTG[0]

PTF[7]/PINT[15]

PTF[6]/PINT[14]

PTF[5]/PINT[13]

PTF[4]/PINT[12]

PTF[3]/PINT[11]

PTF[2]/PINT[10]

PTF[1]/PINT[9]

PTF[0]/PINT[8]

MD0

Vcc (PLL1)

CAP1

Vss (PLL1)

Vss (PLL2)

CAP2

Vcc (PLL2)

PTH[6]

Vss

Vss

Vcc

XTAL

EXTAL

STATUS[0]/PTJ[6]

STATUS[1]/PTJ[7]

TCLK/PTH[7]

IRQOUT

Vss

CKIO

Vcc

TxD0/SCPT[0]

SCK0/SCPT[1]

TxD1/SCPT[2]

SCK1/SCPT[3]

TxD2/SCPT[4]

SCK2/SCPT[5]

RTS2/SCPT[6]

RxD0/SCPT[0]

RxD1/SCPT[2]

Vss

RxD2/SCPT[4]

Vcc

CTS2/IRQ5/SCPT[7]

PTC[7]/PINT[7]

PTC[6]/PINT[6]

PTC[5]/PINT[5]

PTC[4]/PINT[4]

Vss

WAKEUP/PTD[3]

Vcc

PTD[2]/RESETOUT

PTC[3]/PINT[3]

PTC[2]/PINT[2]

PTC[1]/PINT[1]

PTC[0]/PINT[0]

DRAK0/PTD[1]

DRAK1/PTD[0]

DREQ0/PTD[4]

DREQ1/PTD[6]

RESETP

CA

MD3

MD4

MD5

AVss

AN[0]/PTL[0]

AN[1]/PTL[1]

AN[2]/PTL[2]

AN[3]/PTL[3]

AN[4]/PTL[4]

AN[5]/PTL[5]

AVcc

AN[6]/DA[1]/PTL[6]

AN[7]/DA[0]/PTL[7]

AVss

I/O

I/O

I/O

I/O

-

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

I

I

I

I

I

I

I

I

I

I

-

I

-

I

I

I

I

I

I

I

I

I

I

-

-

-

-

-

-

I

-

-

-

O

I

I/O

I/O

I/O

O

-

I/O

-

O

I/O

O

I/O

I/O

I

I

-

I

I/O

I/O

I/O

I/O

-

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I

I

I

I

I

-

I

I

I

I

I

I

I/O

I/O

-

CK enable (SDRAM)/ I/O port K

RAS/ I/O port J

RAS/ I/O port J

CAS (DRAM)/CAS (SDRAM)/ I/O port J

Ground (0 V)

CAS (DRAM)/ I/O port J

Power supply (3.3 V)

CAS (DRAM)/ I/O port J

CAS (DRAM)/ I/O port J

DMAC/ I/O port D

DMAC/ I/O port D

CAS (DRAM)/ I/O port E

CAS (DRAM)/ I/O port E

RAS/ I/O port E

RAS/ I/O port E

I/O port E

System clock

System clock

Bus control

Reset

I/O port H/Analog

Right protect/Input port G

I/O port G

Ground (0 V)

I/O port G

Power supply (3.3 V)

I/O port G

I/O port F/Port Interrupt request

System clock

Power supply (3.3 V)

Clock

Ground (0 V)

Ground (0 V)

Clock

Power supply (3.3 V)

I/O port H

Ground (0 V)

Ground (0 V)

Power supply (3.3 V)

Clock

Clock

System clock

Timer

Interrupt request

Ground (0 V)

Clock

Power supply (3.3 V)

Forward data/Output port for SCI

Serial clock/ I/O port for SCI

Forward data/Output port for SCI

Serial clock/ I/O port for SCI

Transmit request/ I/O port for SCI

Reception data/Input port for SCI

Ground (0 V)

Reception data/Input port for SCI

Power supply (3.3 V)

Transmit clear/Interrupt request/Input port for SCI

I/O port C/Interrupt request

Ground (0 V)

Interrupt request/ I/O port D

Power supply (3.3 V)

I/O port D/Reset

I/O port C/Interrupt request

DMA request/ I/O port D

DMA request/ I/O port D

DMA request/ I/O port D

DMA request/ I/O port D

System clock

System clock

System clock

System clock

System clock

Analog ground (0 V)

A/D change input/Input port L

Analog power supply (3.3 V)

A/D change input/D/A change output/Input port L

Analog ground (0 V)

HD6417709F80B (XV250B00) CPU

DM: IC100

Page 15

PSR-1000/PSR-2000

15

PIN

NO.

I/O

FUNCTION

NAME

PIN

NO.

I/O

FUNCTION

NAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

Vss

CA0

CA1

CA2

CA3

CA4

CA5

CA6

CA7

CA8

CA9

CA10

CA11

VSS

CD0

CD1

CD2

CD3

CD4

CD5

CD6

CD7

CD8

CD9

CD10

CD11

CD12

CD13

CD14

VDD

VSS

CD15

CSN

WRN

RDN

VDD

SYSH0

SYSH1

SYSH2

SYSH3

SYSH4

SYSH5

SYSH6

SYSH7

KONO0

KONO1

KONO2

KONO3

VSS

SYSL0

SYSL1

SYSL2

SYSL3

SYSL4

SYSL5

SYSL6

SYSL7

KONI0

KONI1

VDD

VSS

KONI2

KONI3

DAC0

DAC1

WCLK

MELO0

MELO1

MELO2

MELO3

MELO4

MELO5

MELO6

MELO7

VDD

ADLR

MELI0

MELI1

MELI2

MELI3

MELI4

MELI5

MELI6

MELI7

VSS

RCASN

RA8

RA7

RA6

VDD

VSS

RA5

RA4

RA3

RA2

RA1

RA0

RRASN

RWEN

VSS

RD7

RD6

RD5

RD4

RD3

RD2

RD1

RD0

VSS

RD17

RD16

RD15

RD14

RD13

RD12

RD11

RD10

RD9

RD8

VDD

I

I

I

I

I

I

I

I

I

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I

O

O

O

O

O

O

O

O

O

O

O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I

I

I

O

O

O

O

O

O

O

O

O

O

O

O

I

I

I

I

I

I

I

I

O

O

O

O

O

O

O

O

O

O

O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

(Ground)

Address bus of internal register

(Ground)

Data bus of internal register

(Power supply)

(Ground)

Chip select

Write strobe

Read strobe

(Power supply)

NSYS/LNSYS upper 16 bits

Key on data

(Ground)

NSYS input/LNSYS output lower 8 bits

(Power supply)

Key on data input

(Ground)

DAC output

DAC0/DAC1 word clock

MEL wave data output

(Power supply)

ADC word clock

MEL wave data input

(Ground)

DRAM column address strobe

(Power supply)

(Ground)

DRAM address bus

DRAM row address strobe

DARM write enable

(Ground)

(Ground)

DRAM data bus

(Power supply)

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

209

210

211

212

213

214

215

216

217

218

219

220

221

222

223

224

225

226

227

228

229

230

231

232

233

234

235

236

237

238

239

240

VSS

HMD0

HMD1

HMD2

HMD3

HMD4

HMD5

HMD6

HMD7

HMD8

HMD9

HMD10

HMD11

HMD12

HMD13

HMD14

HMD15

VSS

HMA0

HMA1

HMA2

HMA3

HMA4

HMA5

HMA6

HMA7

HMA8

HMA9

HMA10

VSS

VDD

HMA11

HMA12

HMA13

HMA14

HMA15

HMA16

HMA17

HMA18

HMA19

HMA20

HMA21

HMA22

HMA23

HMA24

VSS

MRASN

MCASN

MOEN

MWEN

VSS

LMD0

LMD1

LMD2

LMD3

LMD4

LMD5

LMD6

LMD7

VDD

VSS

LMD8

LMD9

LMD10

LMD11

LMD12

LMD13

LMD14

LMD15

VSS

LMA0

LMA1

LMA2

LMA3

LMA4

LMA5

LMA6

LMA7

LMA8

LMA9

LMA10

LMA11

VSS

LMA12

LMA13

LMA14

LMA15

LMA16

LMA17

VDD

VSS

LMA18

LMA19

LMA20

LMA21

LMA22

LMA23

LMA24

VSS

SYO

SYOD

QCLK

HCLK

CK256

SYSCLK

VDD

SYI

MCLKI

MCLKO

VDD

XIN

XOUT

VSS

ICN

CHIP2

SLAVE

TESTON

ACIN

DCTEST

VDD

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

I

I

O

I

O

I

I

I

I

I

I

(Ground)

Wave memory data bus (Upper data memory)

(Ground)

(Ground)

(Power supply)

Wave memory address bus (Upper 16 bits)

(Ground)

RAS when DRAM(s) is connected to wave memory

CAS when DRAM(s) is connected to wave memory

Wave memory output enable

Wave memory write enable

(Ground)

Wave memory data bus (Lower data memory)

(Power supply)

(Ground)

(Ground)

(Ground)

Wave memory address bus (Lower data memory)

(Power supply)

(Ground)

(Ground)

Sync. signal for master clock

Sync. signal for HCLK/QCLK

1/12 master clock (64 Fs)

1/6 master clock (128 Fs)

1/3 master clock (256 Fs)

1/2 master clock (384 Fs)

(Power supply)

Sync. clock

Master clock input

Master clock output

(Power supply)

Crystal osc. input

Crystal osc. output

(Ground)

Initial clear

2 chips mode enable

Master/Slave select when 2 chips mode

Test pin

(Power supply)

TC203C760HF-002 (XS725A00) SWP30B (AWM Tone Generator coped with MEG)

Standard Wave Processor

DM: IC400 (PSR-2000 only)

Page 16

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

ICN

RFCLKI

TM2

AVDD_PLL

AVSS_PLL

MODE0

VCC7

GND8

XIN

XOUT

MODE1

TEST0

TESTON

AN0-P40

AN1-P41

AN2-P42

AN3-P43

AVDD_AN

AVSS_AN

TXD0

TXD1

EXCLK

SMD11

SMD4

SMD3

SMD12

SMD10

SMD5

SMD2

SMD13

SMD9

SMD6

SMD1

SMD14

VCC35

GND36

SMD8

SMD7

SMD0

SMD15

SOE

SWE

SRAS

SCAS

REFRESH

CS0

SMA0

SMA16

VCC49

GND50

SMA1

SMA15

SMA2

SMA14

SMA3

SMA13

SMA4

SMA12

SMA5

GND60

VCC61

SMA11

SMA6

SMA10

SMA7

SMA9

SMA17

SMA8

SMA18

SMA19

SMA20

SMA21

SMA22

SMA23

CMA20

CMA19

VCC77

GND78

CMA18

CMA17

CMA5

CMA6

CMA4

CMA7

I

I

I

I

I

O

I

I

I

I

I

I

I

O

O

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

Initial clear

PLL Clock

PLL Control

Power supply

Ground

SWX dual mode

Power supply

Ground

crystal oscillator

crystal oscillator

SWX separate mode

TEST pin

TEST pin

A/D converter

A/D converter

A/D converter

A/D converter

Power supply

Ground

for MIDI or TO-HOST

for MIDI

Crystal oscillator

Wave memory data bus

Wave memory data bus

Wave memory data bus

Wave memory data bus

Wave memory data bus

Wave memory data bus

Wave memory data bus

Wave memory data bus

Wave memory data bus

Wave memory data bus

Wave memory data bus

Wave memory data bus

Power supply

Ground

Wave memory data bus

Wave memory data bus

Wave memory data bus

Wave memory data bus

read signal

write signal

RAS signal

CAS signal

REFRESH signal

CS signal

Memory address bus

Memory address bus

Power supply

Ground

Memory address bus

Memory address bus

Memory address bus

Memory address bus

Memory address bus

Memory address bus

Memory address bus

Memory address bus

Memory address bus

Ground

Power supply

Memory address bus

Memory address bus

Memory address bus

Memory address bus

Memory address bus

Memory address bus

Memory address bus

Memory address bus

Memory address bus

Memory address bus

Memory address bus

Memory address bus

Memory address bus

Program address bus

Program address bus

Power supply

Ground

Program address bus

Program address bus

Program address bus

Program address bus

Program address bus

Program address bus

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

CMA3

CMA8

CMA2

CRD

CMA1

CUB

VCC91

GHND92

CS1

CMA0

CLB

CMA12

CMA11

CMA10

CMA9

GND100

CWE

CMA16

CMA15

CMA14

CMA13

CMD8

CMD7

CMD9

CMD6

CMD10

CMD5

CMD11

CMD4

CMD12

CMD3

CMD13

CMD2

CMD14

VCC119

GND115

CMD1

CMD15

CMD0

CMA21

PDT15

PDT14

PDT13

PDT12

PDT11

PDT10

PDT9

PDT8

VCC133

GND134

PDT7

PDT6

PDT5

PDT4

PDT3

PDT2

PDT1

PDT0

VCA143

GND144

PAD2

PAD1

PAD0

VCC148

GND149

PCS

PWR

PRD

RXD0

RXD1

SCLKI

ADIN

ADLR

DO0

DO1

SYSCLK

VCC161

GND162

WCLK

QCLK

BCLK

SYI

IRQ0

NMI

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I

I

I

I

I

I

I

I

O

O

O

O

O

O

O

I

I

I

Program address bus

Program address bus

Program address bus

read signal

Program address bus

high byte effective signal

Power supply

Ground

CS signal

Program address bus

low byte effective signal

Program address bus

Program address bus

Program address bus

Program address bus

Ground

write signal

Program address bus

Program address bus

Program address bus

Program address bus

Program memory Data bus

Program memory Data bus

Program memory Data bus

Program memory Data bus

Program memory Data bus

Program memory Data bus

Program memory Data bus

Program memory Data bus

Program memory Data bus

Program memory Data bus

Program memory Data bus

Program memory Data bus

Program memory Data bus

Power supply

Ground

Program memory Data bus

Program memory Data bus

Program memory Data bus

Program address bus

SWX access data bus

SWX access data bus

SWX access data bus

SWX access data bus

SWX access data bus

SWX access data bus

SWX access data bus

SWX access data bus

Power supply

Ground

SWX access data bus

SWX access data bus

SWX access data bus

SWX access data bus

SWX access data bus

SWX access data bus

SWX access data bus

SWX access data bus

Power supply

Ground

SWX access address bus

SWX access address bus

SWX access address bus

Power supply

Ground

Chip select

write enable

read enable

for Midi or TO-HOST

for Midi or Key scan

EXT Clock

A/D converter

A/D converter LR clock

DAC

DAC

1/2 clock

Power supply

Ground

for DAC LR clock

1/12 clock

IIS-DAC clock

Synch signal

Interrupt request

Interrupt request

HG73C205AFD (XU947C00) SWX00B (Tone Generator)

DM: IC801 (PSR-1000)

PSR-1000/PSR-2000

16

Page 17

PSR-1000/PSR-2000

17

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

VSS

WA17

WA16

WA15

WA14

WA13

WA12

WA11

WA10

VDD

VSS

WA09

WA08

WA07

WA06

WA05

WA04

WA03

WA02

VDD

VSS

WA01

WA00

WEN

OEN

RASN

CASN

CEN

VDD

VSS

WD19

WD18

WD17

WD16

WD15

WD14

VDD

VSS

WD13

WD12

WD11

WD10

WD09

WD08

WD07

VDD

VSS

WD06

WD05

WD04

WD03

WD02

WD01

WD00

VDD

VSS

TST2

TST1

TST0

MS

LRCLK

SI7

SI6

VDD

VSS

SI5

SI4

SI3

SI2

SI1

SI0

DB1

DB0

VDD

VSS

ODFM

OFS3

OFS2

OFS1

OFS0

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

I

O

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

Power supply

External memory address bus

Ground

Power supply

External memory address bus

Ground

Power supply

External memory address bus

External memory control (WEN)

External memory control (OEN)

External memory control (RASN)

External memory control (CASN)

External memory control (CEN)

Ground

Power supply

External memory data bus

Ground

Power supply

External memory data bus

Ground

Power supply

External memory data bus

Ground

Power supply

Test output

Memory select

LR clock for ADC

Serial input

Ground

Power supply

Serial input

Output bit type select for DAC

Ground

Power supply

Output mode select for DAC

Serial output format select

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

SO7

SO6

SO5

VDD

VSS

SO4

SO3

SO2

SO1

SO0

WDCK

SWPKON

IRQN

VDD

VSS

XTAL_I

XTAL_O

MCLK

VDD

VSS

MICN

CLKIN

SYWIN

SYW

SYWD

VDD

VSS

CLKO

WCLK

HCLK

QCLK

TSTCI

VDD

VSS

(NC)

VDD(PLL)

CPO

CPIN

REF

VSS(PLL)

(NC)

VDD

VSS

TSTCS

CA6

CA5

CA4

CA3

CA2

VDD

VSS

CA1

CA0

CSN

RDN

WRN

BTYP

VDD

VSS

CD15

CD14

CD13

CD12

CD11

VDD

VSS

CD10

CD09

CD08

CD07

CD06

CD05

VDD

VSS

CD04

CD03

CD02

CD01

CD00

VDD

O

O

O

O

O

O

O

O

O

O

O

I

O

O

I

I

I

O

O

O

O

O

O

I

O

I

I

I

I

I

I

I

I

I

I

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Serial output

Ground

Power supply

Serial output

Data enable for DAC

SWP00 format key on output

EG interrupt

Ground

Power supply

Quartz crystal terminal

Quartz crystal terminal

Oscillate clock output

Ground

Power supply

Initial clear

Master clock input

Sync.signal input

Sync.signal output

Sync.signal output

Ground

Power supply

For test (512 fs output)

2 times sync.clock output (256 fs)

4 times sync.clock output (128 fs)

8 times sync.clock output (64 fs)

PLL test input

Ground

Power supply

PLL control output

PLL control input

PLL control input

Ground

Power supply

PLL test input

CPU address bus

Ground

Power supply

CPU address bus

Lo/Hi select in 8 bits write

Chip select

Register read

Register write

Data bus type select

Ground

Power supply

CPU data bus

Ground

Power supply

CPU data bus

Ground

Power supply

CPU data bus

Ground

YSS236-F (XT013A00) VOP3

DM: IC401 (PSR-2000 only)

Page 18

PSR-1000/PSR-2000

18

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

VA5

VA4

VA3

VA2

VA1

VA0

/VWR

/VCE

/VRD

/RES

NC

NC

/RD

/WR

SEL2

SEL1

OSC1

OSC2

/CS

A0

Vdd

D0

D1

D2

D3

D4

D5

D6

D7

XD3

O

O

O

O

O

O

O

O

I

-

I

I

I

I

I

O

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

VRAM address bus

VRAM read/write

Memory control

Not used

Initial clear

Not used

Not used

Read strobe

Write strobe

Bus select

Bus select

Clock

Clock

Chip select

Data mode select

Power supply

Data bus

Data bus output for 4 bit dot

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

XD2

XD1

XD0

XECL

XSCL

Vss

LP

WF

YDIS

YD

YSCL

VD7

VD6

VD5

VD4

VD3

VD2

VD1

VD0

VA15

VA14

VA13

VA12

VA11

VA10

VA9

VA8

VA7

VA6

NC

O

O

O

O

O

O

O

O

O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

O

O

O

O

O

O

O

-

Data bus output for 4 bit dot

S driver enable, chain clock

Data bus shift clock

Ground

X driver latch pulse

Frame signal for X/Y driver

Power down signal for displaying off mode

Scan start signal

Scan shift clock

VRAM data bus

VRAM address bus

Not used

S1D13305F00B100 (XQ595A00) LCDC (LCD Controller)

DM: IC500

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

P12

P11

P10

P47/KR7

P46/KR6

P45/KR5

P44/KR4

P43/KR3

P42/KR2

P41/KR1

P40/KR0

NC

IC

X2

X1

VSS0

VDD0

/RESET

P53

P52

P51/TO2

P50/TI0/TO0

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I/O

I/O

I/O

I/O

Port 1

Port 4/Key return signal detection input

Internally connected (N.C.)

Clock

Ground

Power supply

System reset

Port 5

Port 5/16-bit timer output

Port 5/External count clock input to 8-bit timer/8-bit timer output

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

P32/INTP2/CPT2

P31/INTP1

P30/INTP0

P22/RXD/SI0

P21/TXD/SO0

P20/ASCK//SCK0

P07

P06

P05

P04

P03

P02

P01

P00

NC

VDD1

VSS1

P17

P16

P15

P14

P13

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Port 3/External interrupt input/Capture edge input

Port 3/External interrupt input

Port 2/Asynchronous serial interface serial data input/Serial interface serial data input

Port 2/Asynchronous serial interface serial data output/Serial interface serial data output

Port 2/Asynchronous serial interface serial clock input/Serial interface serial clock

Port 0

Power supply

Ground

Port 1

µPD789022GB-A15-8E

(XZ560100) CPU

MKS5F: IC1

Page 19

PSR-1000/PSR-2000

19

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

DGND

MCLK

CLATCH

CCLK

CDATA

384//256

X2MCLK

ZEROR

DEEMP

96//48

AGND

OUTR+

OUTR-

FILTR

I

I

I

I

I

I

I

O

I

I

I

O

O

O

Digital Ground

Master Clock Input. Connect to an external

clock source at either 256, 384 or 512 Fs.

Latch input for control data. This input is

rising-edge sensitive.

Control clock input for control data. Control

input data must be valid on the rising edge of

CCLK. CCLK may be continuous or gated.

Serial control input, MSB first, containing 16 bits

of unsigned data per channel. Used for specifying

channel-specific attenuation and mute.

Selects the master clock mode as either 384

times the intended sample frequency (HI) or

256 times the intended sample frequency (LO).

The state of this input should be hardwired to

logic HI or logic LO, or may be changed while

the AD1854 is in power-down/reset. It must not

be changed while the AD1854 is operational.

Selects internal clock doubler (LO) or

internal clock = MCLK (HI).

Right Channel Zero Flag Output. This pin

goes HI when Right Channel has no signal

input for more than 1024 LR Clock Cycles.

De-Emphasis. Digital de-emphasis is

enabled when this input signal is HI. This is

used to impose a 50 µs/15 µs response

characteristic on the output audio spectrum

at an assumed 44.1 kHz sample rate.

Selects 48 kHz (LO) or 96 kHz Sample

Frequency Control.

Analog Ground

Right Channel Positive line level analog output.

Right Channel Negative line level analog output.

Voltage Reference Filter Capacitor Connection.

Bypass and decouple the voltage reference

with parallel 10 µF and 0.1 µF capacitors to the

AGND.

15

16

17

18

19

20

21

22

23

24

25

26

27

28

AGND

OUTL-

OUTL+

AVDD

FILTB

IDPM1

IDPM0

ZEROL

MUTE

/PD//RST

L//RCLK

BCLK

SDATA

DVDD

I

O

O

I

O

I

I

O

I

I

I

I

I

I

Analog Ground

Left Channel Negative line level analog

output.

Left Channel Positive line level analog

output.

Analog Power Supply. Connect to analog 5

V supply.

Filter Capacitor connection, connect 10 µF

capacitor to AGND.

Input serial data port mode control one.

With IDPM0, defines one of four serial

modes.

Input serial data port mode control zero.

With IDPM1, defines one of four serial

modes.

Left Channel Zero Flag Output. This pin

goes HI when Left Channel has no signal

input for more than 1024 LR Clock Cycles.

Mute. Assert HI to mute both stereo analog

outputs. Deassert LO for normal operation.

/Power-Down//Reset. The AD1854 is

placed in a low power consumption mode

when this pin is held LO. The AD1854 is

reset on the rising edge of this signal. The

serial control port registers are reset to the

default values. Connect HI for normal

operation.

Left//Right clock input for input data. Must

run continuously.

Bit clock input for input data. Need not run

continuously; may be gated or used in a

burst fashion.

Serial input, MSB first, containing two

channels of 16, 18, 20, and 24 bits of twos

complement data per channel.

Digital Power Supply Connect to digital 5 V

supply.

AD1854JRSRL (XY782A00) DAC (Digital to Analog Converter)

DM: IC700

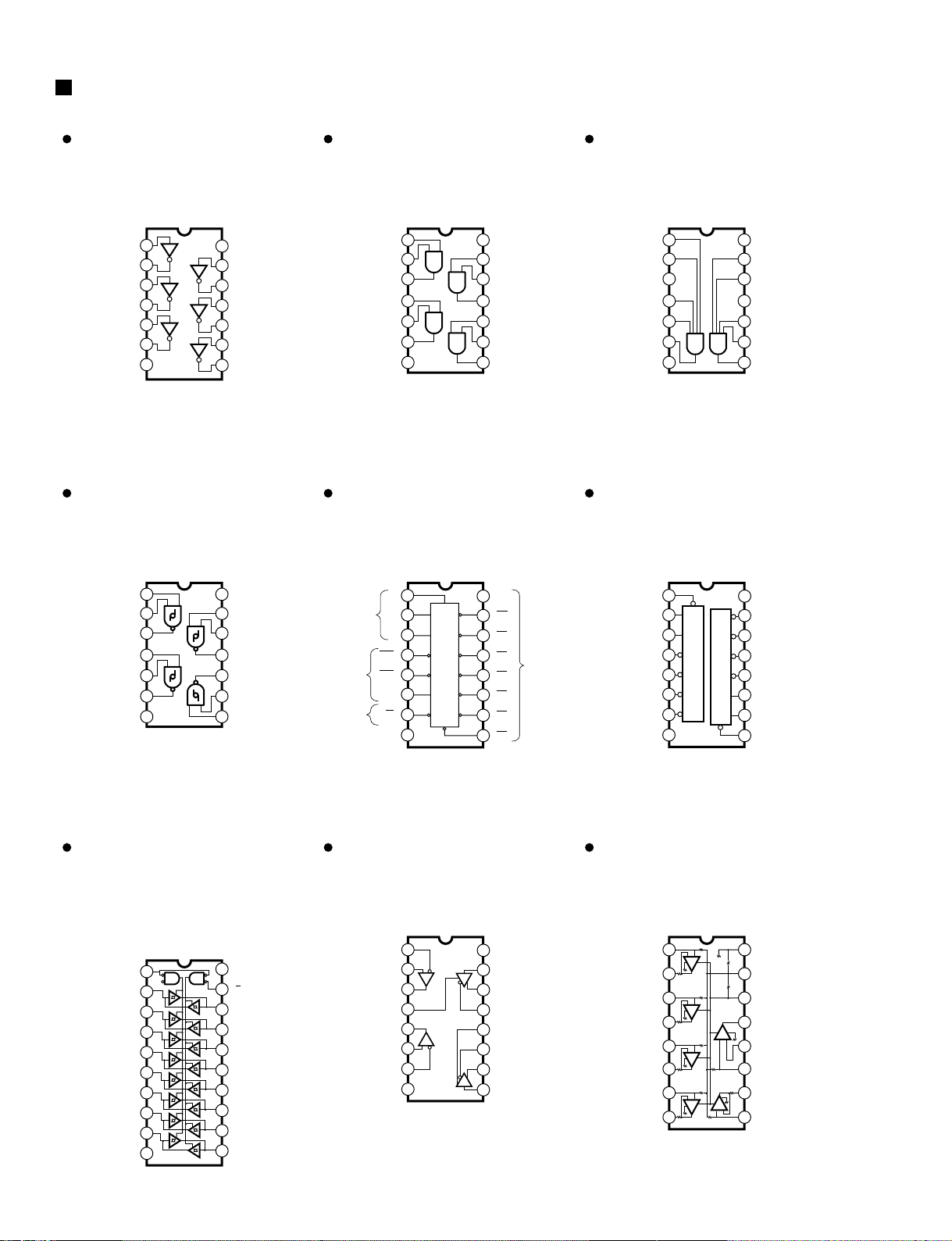

Page 20

1

2

3

4

5

6

7

1A

1Y

2A

2Y

3A

3Y

Vss

14

13

12

11

10

9

8

VDD

6A

6Y

5A

5Y

4A

4Y

SN74HCU04NSR (XW842A00)

SN74HCU04N (IG142250)