Yaesu FT-1000MP Service Manual

HF Transceiver

Technical Supplement

© 2002 VERTEX STANDARD CO., LTD. EH013H90A

VERTEX STANDARD CO., LTD.

4-8-8 Nakameguro, Meguro-Ku, Tokyo 153-8644, Japan

VERTEX STANDARD

US Headquarters

17210 Edwards Rd., Cerritos, CA 90703, U.S.A.

International Division

8350 N.W. 52nd Terrace, Suite 201, Miami, FL 33166, U.S.A.

YAESU EUROPE B.V.

P.O. Box 75525, 1118 ZN Schiphol, The Netherlands

YAESU UK LTD.

Unit 12, Sun Valley Business Park, Winnall Close

Winchester, Hampshire, SO23 0LB, U.K.

VERTEX STANDARD HK LTD.

Unit 5, 20/F., Seaview Centre, 139-141 Hoi Bun Road,

Kwun Tong, Kowloon, Hong Kong

This manual provides technical information necessary for servicing the Yaesu MARK-V

not include information on installation and operation, which are described in the MARK-V

vided with each transceiver, or on MARK-V

The MARK-V

FT-1000MP

Fi el d is carefully designed to allow the knowledgeable operator to make nearly all adjustments required

FT-1000MP

Fi el d accessories, which are described in manuals provided with each.

FT-1000MP

FT-1000MP

Fi el d HF transceiver. It does

Fi el d Operating Manual, pro-

for various station conditions, modes and operator preferences simply from the controls on the panels, without opening the case of the

transceiver. The MARK-V

FT-1000MP

Fi el d Operating Manual describes these adjustments, plus certain internal settings.

Servicing this equipment requires expertise in handling surface mount chip components. Attempts by non-qualified persons to service

this equipment may result in permanent damage not covered by warranty. For the major circuit boards, each side of the board is identified

by the type of the majority of components installed on that side. In most cases one side has only chip components, and the other has either

a mixture of both chip and lead components (trimmers, coils, electrolytic capacitors, packaged ICs, etc.), or lead components only.

While we believe the technical information in this manual is correct, Vertex Standard assumes no liability for damage that may occur

as a result of typographical or other errors that may be present. Your cooperation in pointing out any inconsistencies in the technical

information would be appreciated. Vertex Standard reserves the right to make changes in this transceiver and the alignment procedures, in

the interest of technological improvement, without notification of the owners.

Contents

Specifications...................................................................................................................................................... 1-1

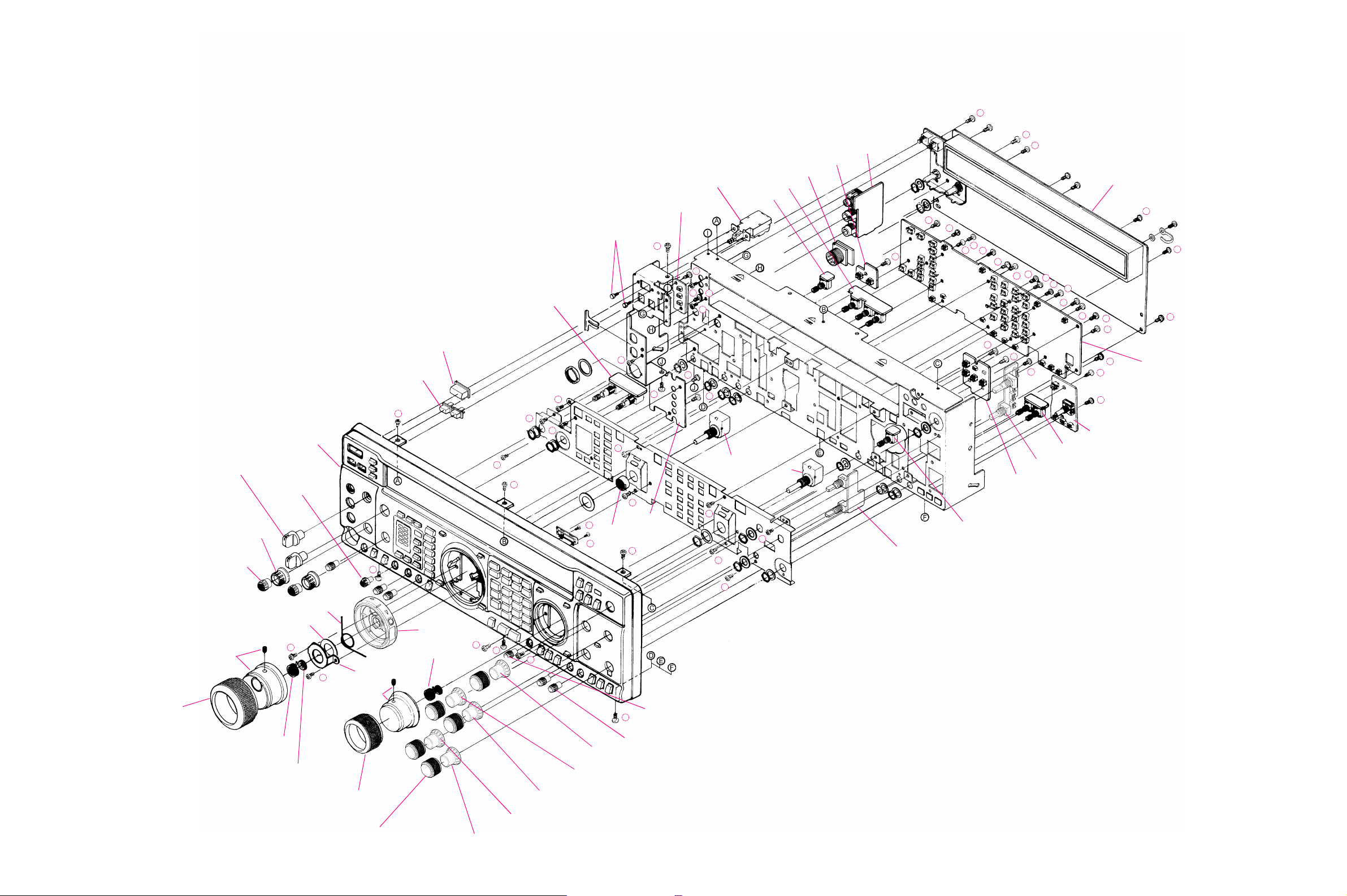

Exploded View & Miscellaneous Parts ............................................................................................................ 2-1

Alignment ........................................................................................................................................................... 3-1

Circuit Description ............................................................................................................................................ 4-1

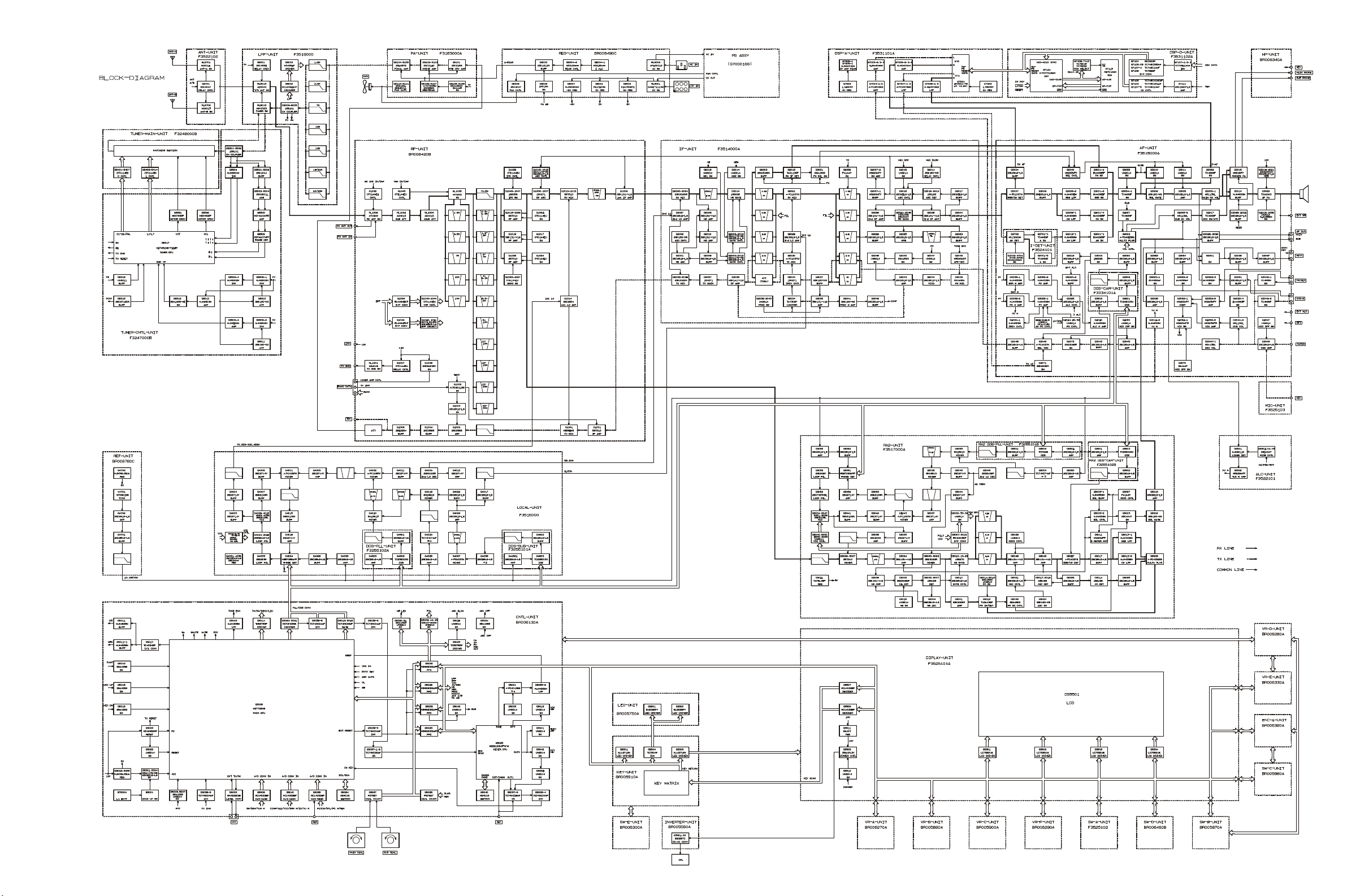

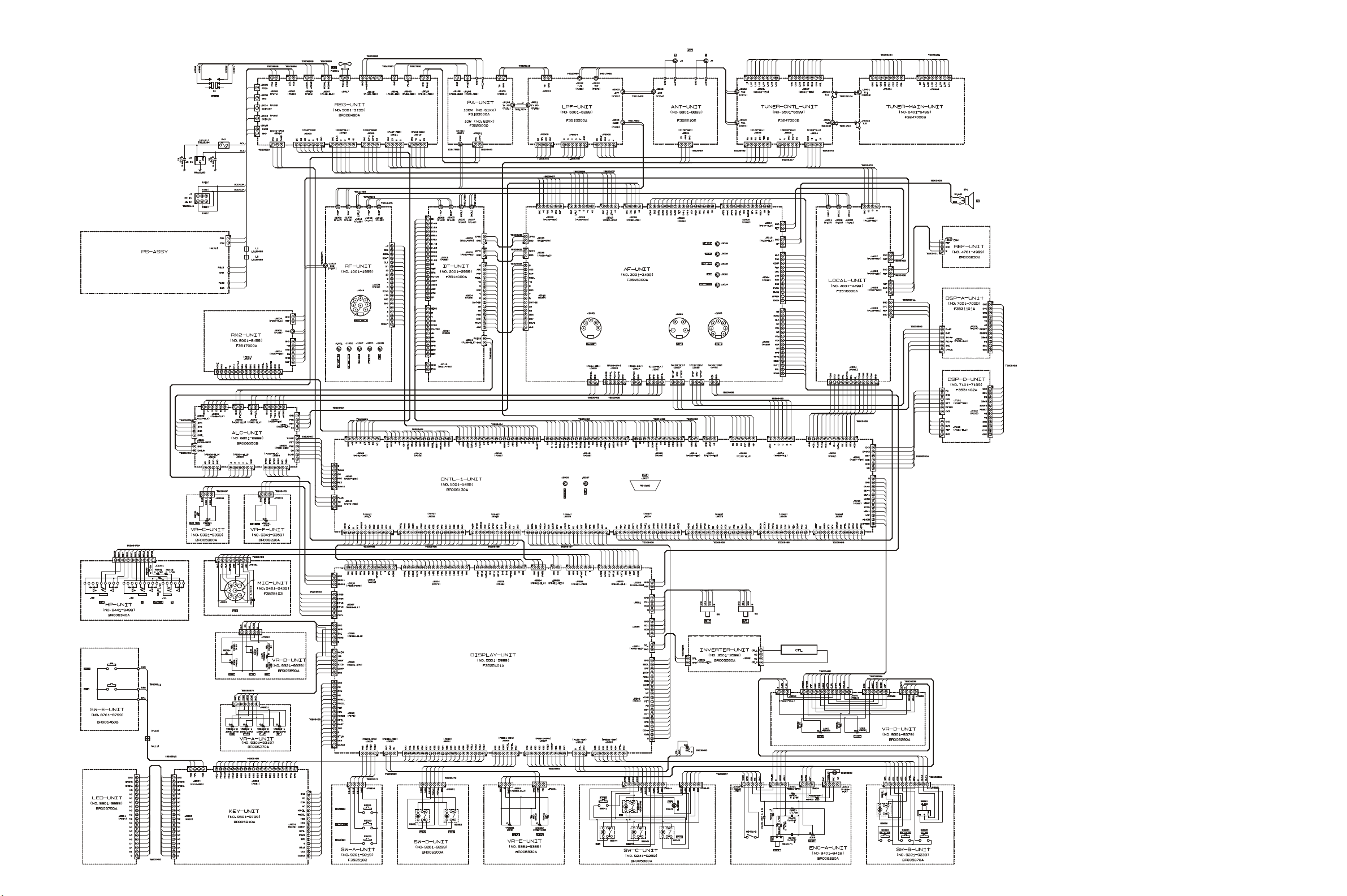

Block & Interconnection Diagram ................................................................................................................... 5-1

PCB Diagrams & Parts Lists

RF Unit ........................................................................................................................................................ 6A-1

IF Unit ...........................................................................................................................................................6B-1

AF Unit ......................................................................................................................................................... 6C-1

INVERTER Unit .......................................................................................................................................... 6D-1

DDS-CAR Unit ............................................................................................................................................. 6E-1

I-DET Unit .................................................................................................................................................... 6F-1

LOCAL Unit ................................................................................................................................................ 6G-1

DDS-SUB Unit ............................................................................................................................................ 6H-1

DDS-PLL Unit ............................................................................................................................................... 6I-1

REF Unit ........................................................................................................................................................6J-1

CNTL-1 Unit ................................................................................................................................................ 6K-1

DISPLAY Unit .............................................................................................................................................. 6L-1

LPF-1 Unit ................................................................................................................................................... 6M-1

PA Unit ......................................................................................................................................................... 6N-1

TUNER-MAIN Unit .................................................................................................................................... 6O-1

TUNER-CNTL Unit ..................................................................................................................................... 6P-1

ALC Unit ..................................................................................................................................................... 6Q-1

DSP-A Unit ...................................................................................................................................................6R-1

DSP-D Unit ................................................................................................................................................... 6S-1

RX-2 Unit ..................................................................................................................................................... 6T-1

RX2PLL-DDS Unit ..................................................................................................................................... 6U-1

RX2CAR-DDS Unit ..................................................................................................................................... 6V-1

ANT Unit ..................................................................................................................................................... 6W-1

REG Unit ..................................................................................................................................................... 6X-1

SW-A, B, C, D, E Unit .................................................................................................................................. 6Y-1

VR-A, B, C, D, E, F Unit .............................................................................................................................. 6Z-1

ENC-A, MIC, HP Unit ...................................................................................................................................6a-1

KEY Unit ...................................................................................................................................................... 6b-1

LED Unit ........................................................................................................................................................6c-1

PS Unit .......................................................................................................................................................... 6d-1

CAUTION

Danger of explosion if battery is incorrectry replaced.

Replace only with the same or equivalent type.

Specifications

General

Rx Frequency Range: 100 kHz - 30 MHz

Tx Frequency Ranges: 160 - 10m (Amateur bands only)

Frequency Stability: ±0.5 ppm (after 1 min. @ 25 °C [77 °F])

±0.25 ppm (after 1 min. @ 25 °C[77 °F], w/TCXO-6)

Operating Temperature Range: –10 °C ~ +50 °C [+14 °F ~ +122 °F]

Emission Modes: LSB, USB, CW, FSK, AFSK, AM, FM

Frequency Steps: 0.625/1.25/2.5/5/10 Hz for SSB,CW, RTTY & Packet;

100 Hz for AM and FM

Antenna Impedance: 50 Ohms, unbalanced

16.6 - 150 Ohms, unbalanced (Tuner ON, TX only)

Power Consumption: AC 117V AC 200V DC 13.8 V

Rx (no signal) 70 VA 80 VA 2.3 A

Rx (signal) 80 VA 90 VA 2.7 A

100 W (CLASS AB) 450 VA 480 VA 20 A

25 W (CLASS A) 300 VA 320 VA 13 A

Supply Voltage: 13.8 VDC/100-120 VAC 50-60 Hz/200-240 VAC 50-60 Hz

Dimensions (WHD): 410 x 135 x 347 mm ( 16 x 5.3 x 13.7 inch)

Weight (approx.): 15 kg. (33 lbs)

Transmitter

Power Output: Adjustable up to 100 watts (25 watts AM carrier),

Class A mode (SSB): 25 watts maximum

Duty Cycle: 100% @ 50 watts, 50% @ 100 watts (FM & RTTY, 3-minute Tx)

Modulation Types: SSB: J3E Balanced, AM: A3E Low-level (early stage),

FM: F3E Variable reactance, AFSK: J1D, J2D Audio frequency shift keying

Maximum FM Deviation: ± 2.5 kHz

FSK Shift Frequencies: 170, 425, and 850 Hz

Packet Shift Frequencies: 200 and 1000 Hz

Harmonic Radiation: Better than –60 dB (Typical)

SSB Carrier Suppression: At least 40 dB below peak output

Undesired Sideband Suppression: At least 55 dB below peak output

Audio Response (SSB): Not more than -6 dB from 400 to 2600 Hz

3rd-order IMD: –31 dB @ 100 watts PEP, or better

Class A mode: –40 dB @ 25 watts PEP (Typical)

Microphone Impedance: 500 to 600 Ohms

Receiver

Circuit Type: Quad-conversion superheterodyne (triple conversion for FM)

Intermediate Frequencies: Main Rx; 70.455 MHz/8.215 MHz/455 kHz, Sub Rx; 47.21 MHz/455 kHz

Sensitivity: Modes 0.5 - 1.8 MHz 1.8 - 30 MHz

SSB/CW (2.0 kHz) 2 µV 0.16 µV

AM (6 kHz) 13 µV 2 µV

FM – 0.5 µV

(with preamp on, IDBT on, SSB/CW/AM for 10 dB S/N, FM for 12 dB SINAD,

0 dBµ = 1 µV)

Selectivity (–6/–60 dB): Band Width Modes

2.4 kHz all except FM 2.2 kHz 4.2 kHz

2.0 kHz all except FM 1.8 kHz 3.6 kHz

500 Hz

250 Hz

IF Rejection (1.8 ~ 30 MHz): 80 dB or better (Main Rx), 60 dB or better (Sub Rx)

Image Rejection (1.8 ~ 30 MHz): 80 dB or better (Main), 50 dB or better (Sub)

Maximum Audio Output: 2.0 W into 4 Ohms with <10% THD

Audio Output Impedance: 4 to 8 Ohms

Specifications are subject to change, in the interest of technical improvement, without notice or obligation.

CW/RTTY/Packet

CW/RTTY/Packet

AM (Wide) 4 kHz 14 kHz

FM 8 kHz 19 kHz

Minimum –6 dB BW Maximum –60 dB BW

500 Hz 1.8 kHz

250 Hz 700 Hz

1-1

Notes

1-2

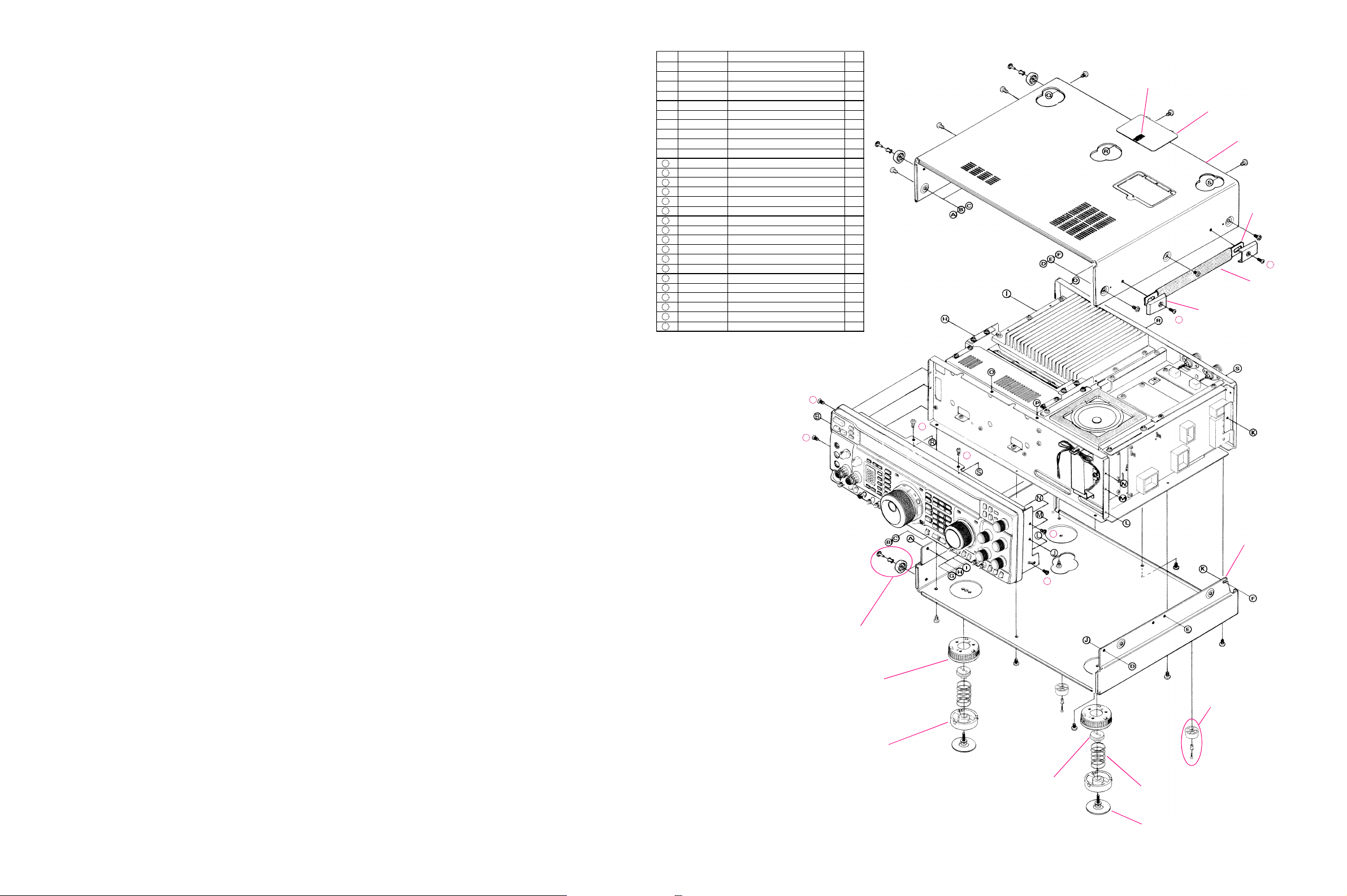

REF. VXSTD P/N Description Qty.

À

U00308001 PAN HEAD SCREW M3X8 1

Á

U00520002 PAN HEAD SCREW M5X20NI 1

Â

U03306001 SEMS SCREW ASM3X6 14

Ã

U04206001 SEMS SCREW HSM2.6X6 4

Ä

U20306001 BINDING HEAD M3X6 12

Å

U75703650

Æ

U20308001 BINDING HEAD M3X8 4

Ç

U20406007 BINDING HEAD M4X6B 16

È

U22416007 SEMS SCREW HM4X16B 2

É

U23306001 TAPTITE SCREW M3X6 4

11

U24305001 TAPTITE SCREW M3X5 41

12

U24306001 TAPTITE SCREW M3X6 137

13

U31415020

14

U24306007 TAPTITE SCREW M3X6B 14

15

U24308001 TAPTITE SCREW M3X8 10

16

U24310001 TAPTITE SCREW M3X10 6

17

U31306001 OVAL HEAD SCREW M3X6 6

18

U34306001 TAPTITE SCREW M3X6 5

19

U60300301 HEX NUT N3 1

20

U65500102 WING NUT N5NI 1

21

U65500002 FLANGE NUT N5NI 1

22

U70003001 PLANE WASHER FW3 4

23

U70005002 PLANE WASHER FW5NI 2

24

U73005002

25

U75703850

26

U9900062

27

Q6000115 TERMINAL B-5 (M3) 2

28

S5000102 TAPTITE SCREW M2X4 4

PLANE WASHER W3X8X0.5 FIBER

OVAL HEAD SCREW M4X15SUS

TOOTHED LOCK WASHER IW5NI

PLANE WASHER W3X8X1 FIBER

TAPTITE SCREW M1.6X3NI#3

Exploded View & Miscellaneous Parts

Ç

Ç

1

Ç

2

Ç

2

1

2

R3151730

HOOK

Ç

R0151720

Ç

CASE (COVER)

Ç

R4115020

13

HANDLE HOLDER

R0901050C

CASE (TOP)

Ç

R0115070

HANDLE CORE

Ç

13

R3084746

HANDLE

18

18

S4000025

FOOT FF-008 (X4pcs)

R3514220

LEG (X2pcs)

12

12

18

Ç

18

Ç

RA0391000

CASE (BOTTOM)

Ç

Ç

Ç

Ç

S4000042

CASE LEG FT-015 (X2pcs)

R3514230

LEG (X2pcs)

È

R3133080

COLLAR (X2pcs)

Ç

R0133740

COIL SPRING (X2pcs)

È

R7133800

WASHER (X2pcs)

2-1

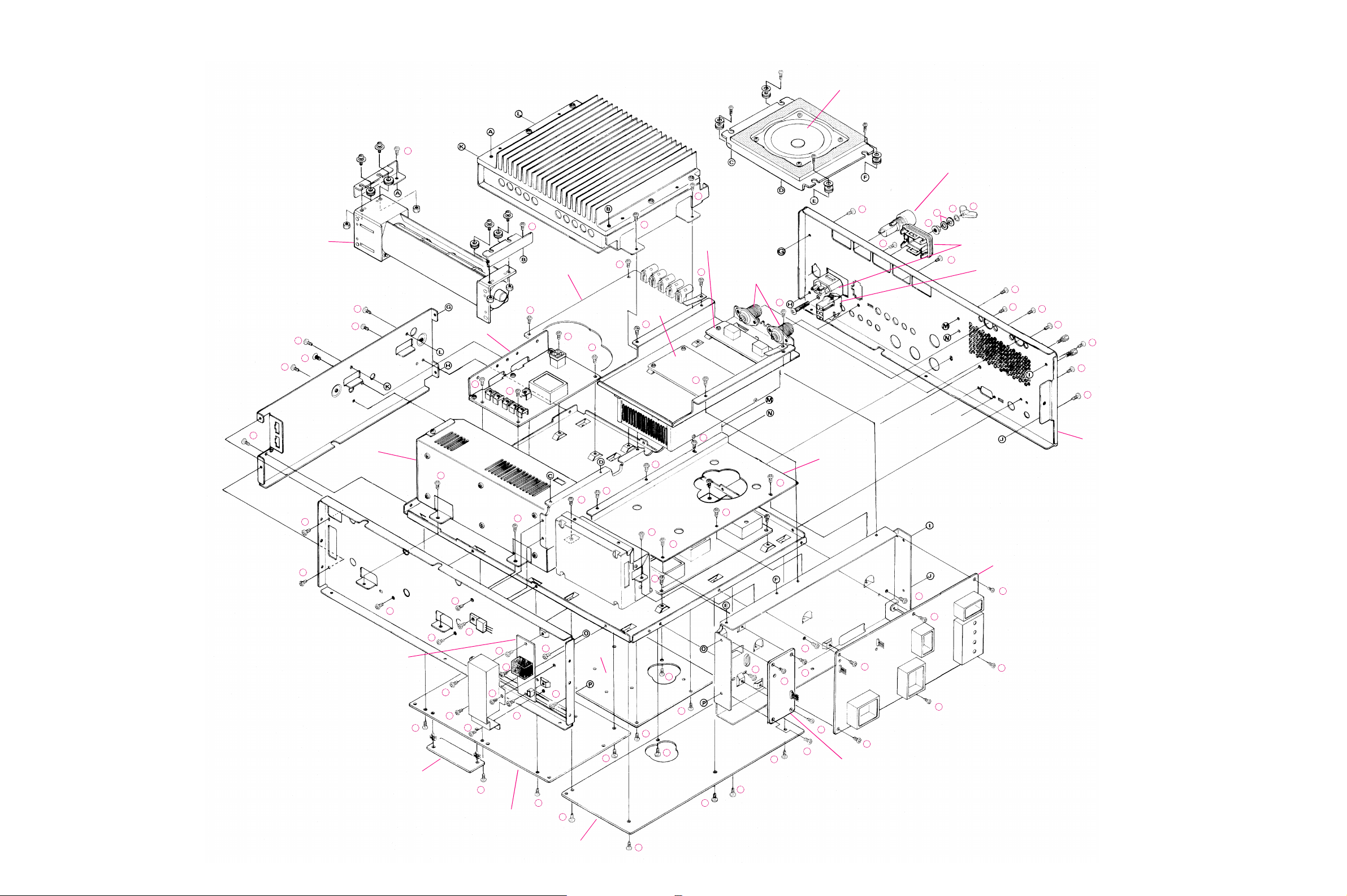

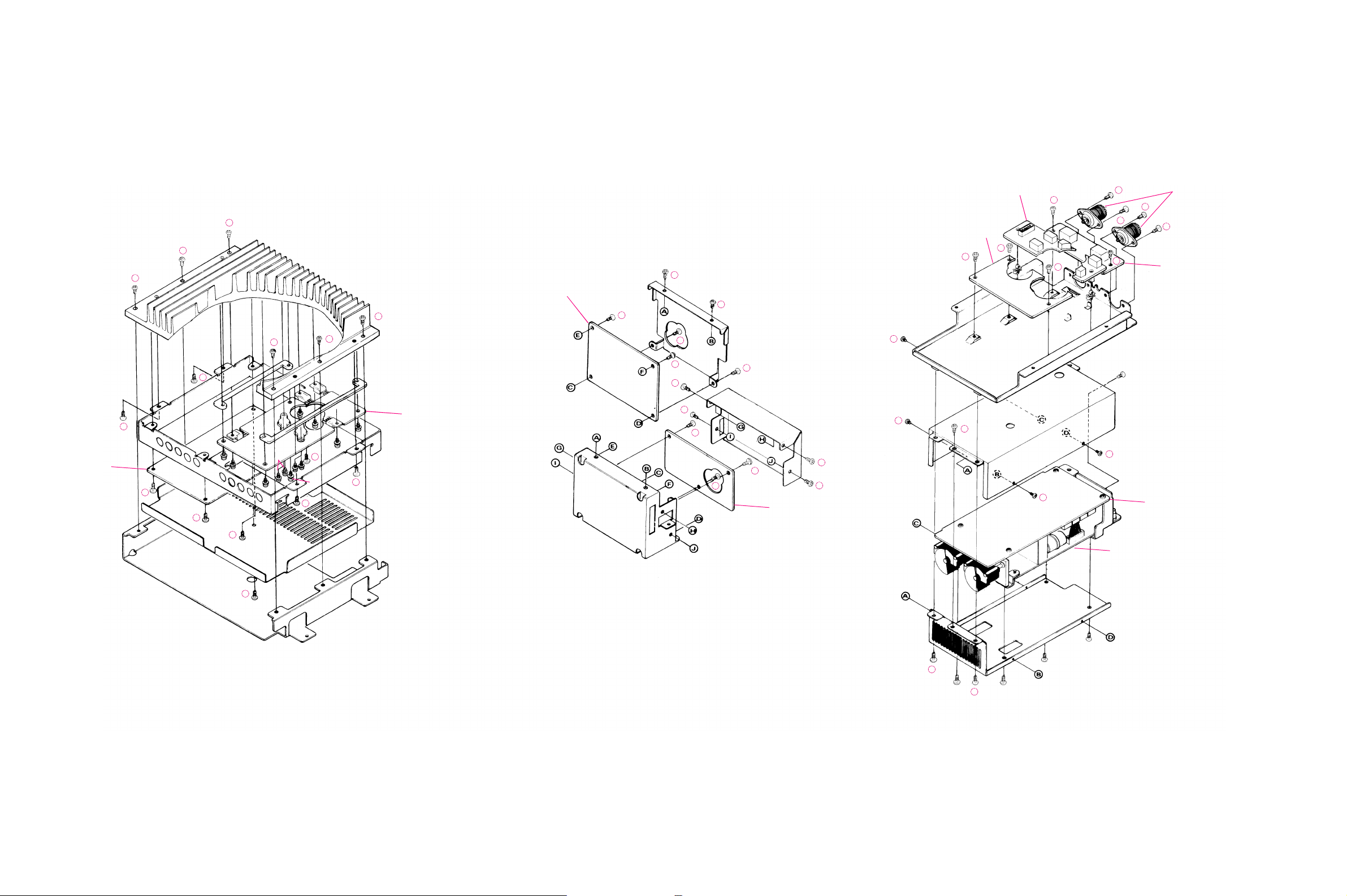

Exploded View & Miscellaneous Parts

M2090011A

FAN

12

18

12

Æ

M4090125

SPEAKER

Æ

Æ

Ã

Ã

16

Æ

P2000067

FUSE HOLDER

12

Ã

Ã

16

12

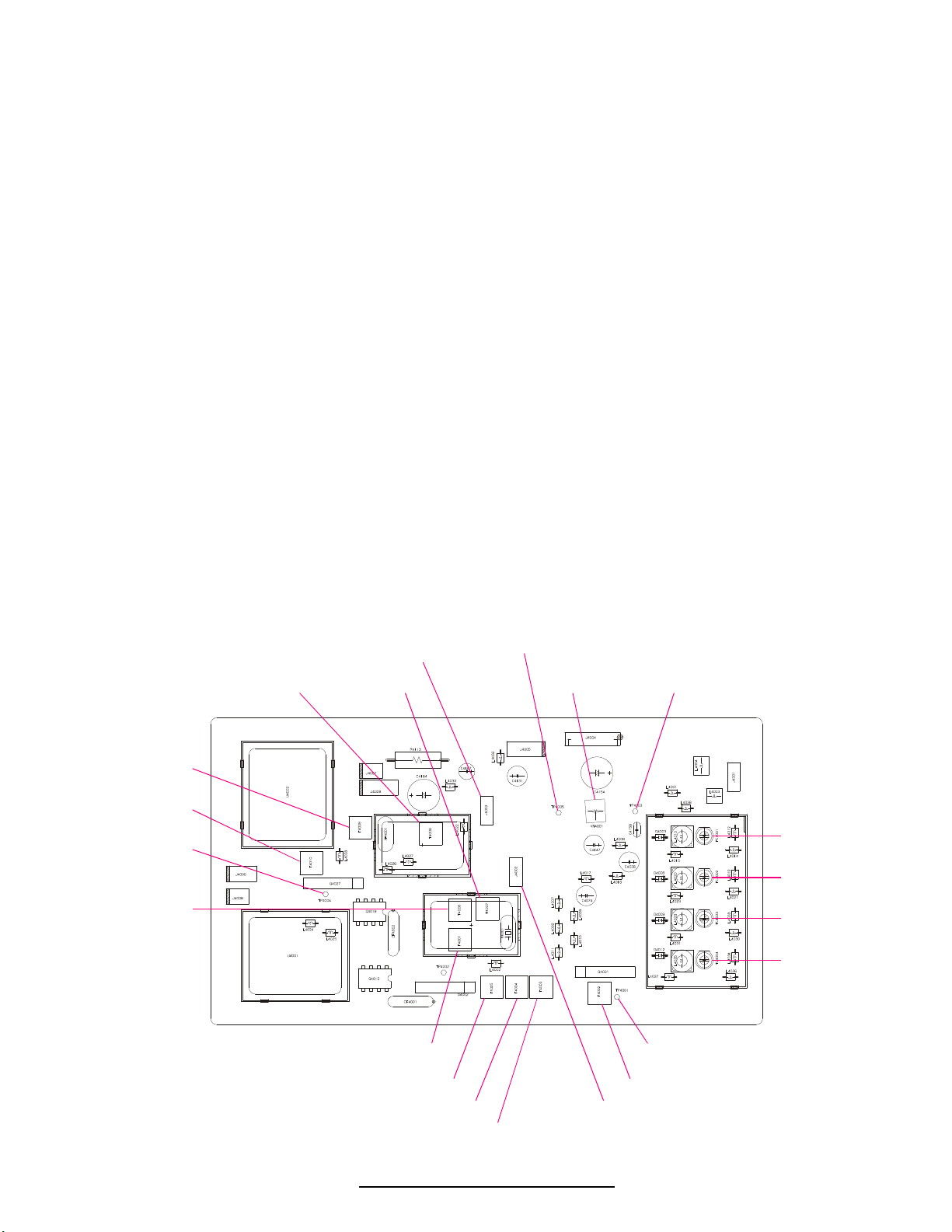

ANT Unit

RF Unit

12

P1090352

12

CONNECTOR

14

14

23

21

(2pcs)

12

12

REG Unit

12

12

12

12

12

ALC Unit

12

12

12

Á

20

24

P0090703

CONNECTOR

T9206441

14

WIRE ASS’Y

14

14

14

14

14

14

14

12

PS Unit

12

12

12

12

12

12

12

12

15

Q7000226

INV Unit

12

12

12

12

12

12

12

12

12

AF Unit

12

12

12

12

12

12

12

12

12

12

RA0387900

REAR FRAME

Local Unit

12

12

12

RX2 Unit

12

12

12

12

12

12

12

12

12

12

12

12

12

REF Unit

12

12

SSB-Filter Unit

12

IF Unit

12

12

12

12

2-2

CNTL Unit

12

R3151220A

KNOB (X2pcs)

R3151210A

KNOB

R6153330A

SPECIAL SCREW(X2 pcs)

VR-A Unit

Exploded View & Miscellaneous Parts

12

É

12

SW-D Unit

HP Unit

N4090148

PUSH SWITCH

MIC Unit

VR-B Unit

VR-B Unit

SW-A Unit

11

11

12

11

12

12

11

12

11

11

11

11

11

11

11

12

É

Display Unit

É

12

Å

11

11

11

11

11

11

11

11

11

11

11

11

11

Key Unit

É

12

12

R3521220A

KNOB MAIN ASS’Y

RA0256700

RUBBER RING

RA0388400

FRONT PANEL ASS’Y

R3521210A

KNOB (X2 pcs)

R3151500

KNOB (X2 pcs)

R3151490A

KNOB (X2 pcs)

R0134990A

COIL SPRING

R3152920A

KNOB

R0151140

U9900059

SPRING

POLY SLIDER

(X2 pcs)

15

R3521241

SUB MAIN ASS’Y

R3135000A

WASHER (X2 pcs)

12

12

R0151190A

15

HOLDER

RA0256800

RUBBER RING

RA0257000

RUBBER TOP (X5 pcs)

CP7273001

RING ASS’Y

R0136380

COIL SPRING

12

15

12

RA0253800

KNOB

12

12

15

RA02538B0

KNOB

RA02538A0

KNOB

12

12

12

26

R6151760

NUT

26

RA0253800

KNOB

RA02538A0

KNOB

12

12

LED Unit

12

RA0390900

KNOB

12

RA3151480A

KNOB (X5 pcs)

11

Q9000619

ROTARY ENCODER

12

12

12

12

11

SW-B Unit

VR-D Unit

ENC-A Unit

SW-C Unit

VR-C Unit

VR-E Unit

2-3

Exploded View & Miscellaneous Parts

LPF Unit

HPF Unit

12

16

16

16

12

ALC Unit

12

12

12

14

14

12

P1090352

CONNECTOR (2pcs)

14

14

ANT Unit

DSP-D Unit

16

16

11

11

Æ

11

11

11

Â

Æ

16

Â

Â

Â

11

Â

Â

Æ

11

Æ

11

PA Unit

12

12

12

12

12

12

28

12

28

12

12

12

12

12

11

28

DSP-A Unit

Ä

28

Tuner-Main Unit

Tuner-CNTL Unit

2-4

11

Ä

12

12

Ä

Ä

Ä

Alignment

Introduction and Precautions

The following procedures cover adjustments that are not normally required once the transceiver has left the factory. However,

if damage occurs and some parts subsequently be replaced, realignment may be required. If a sudden problem occurs during

normal operation, it is likely due to component failure; realignment should not be done until after the faulty component has been

replaced.

We recommend that servicing be performed by authorized Vertex Standard service technicians, experienced with the circuitry

and fully equipped for repair and alignment. If a fault is suspected,

contact the selling dealer for instructions regarding repair. Authorized Vertex Standard service technicians have the latest configuration information, and realign all circuits and make complete performance checks to ensure compliance with factory specifications

after repairs.

Those who do undertake any of the following alignments are

cautioned to proceed at their own risk. Problems caused by unauthorized attempts at realignment are not covered by the warranty

policy. Also, Vertex Standard must reserve the right to change circuits and alignment procedures in the interest of improved performance, without notifying owners.

Under no circumstances should any alignment be attempted

unless the normal function and operation of the transceiver are

clearly understood, the cause of the malfunction has been clearly

pinpointed and any faulty components replaced, and the need for

realignment determined to be absolutely necessary.

The following test equipment (and thorough familiarity with

its correct use) is necessary for complete realignment. Most steps

do not require all of the equipment listed, but the interactions of

some adjustments may require that more complex adjustments be

performed in a sequence. Do not attempt to perform only a single

step unless it is clearly isolated electrically from all other steps.

Rather, have all test equipment ready before beginning, and follow all of the steps in a section in the order they are presented.

Alignment Preparation & Precautions

A 50 Ω dummy load and in-line wattmeter must be connected

to the antenna jack in all procedures that call for transmission,

expect where specified otherwise. Correct alignment is not possible with an antenna. Except where specified otherwise, the transceiver should be tuned to 14.2000 MHz, USB mode, and these

controls set as indicated:

¦ MOX, VOX, AGC, PROC, IPO, ATT: OFF

¦ MIC & RF PWR: fully CCW (minimum)

¦ AF GAIN (Volume): As required

¦ SQL: fully CCW (minimum)

¦ NOTCH & SHIFT: to 12-o’clock

Read each step to determine if the same test equipment will be

required. If not, remove the test equipment (except dummy load

and wattmeter, if connected) before proceeding. Correct alignment

requires that the ambient temperature be the same as that of the

transceiver and test equipment, and that this temperature be held

constant between 20 ~ 30 °C (68 ~ 86 °F). If the transceiver is

brought into the shop from hot or cold air it should be allowed

time for thermal equalization with the environment before alignment. Alignments must only be made with oscillator shields and

circuit boards firmly affixed in place. Also, the test equipment must

be thoroughly warmed up before beginning.

Note: Signal levels in dB referred to in alignment are based on

0 dBµ = 0.5 µV.

Table Note: DC voltages should be within ±10 % of those listed

in the voltage tables.

REF Unit

Carrier Frequency

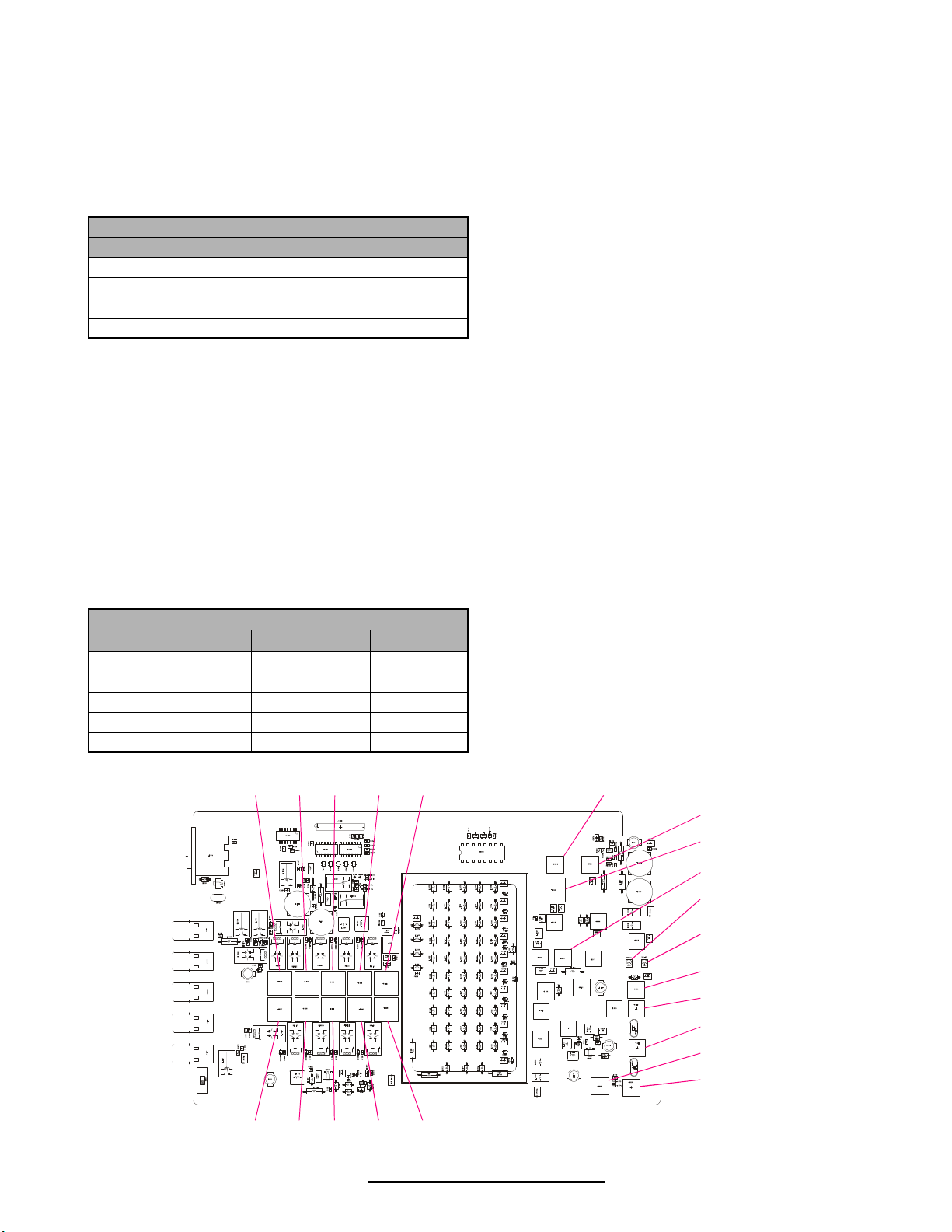

Refer to the drawing below for the REF Unit component locations and alignment points.

r Connect the frequency counter to pin 3 of J4703. Confirm the

frequency counter reading is 10.485760 MHz ±5 Hz.

Required Test Equipment

r Digital DC Voltmeter (high-Z, 1 MΩ/V)

r RF Millivoltmeter

r AC Voltmeter

r RF Standard Signal Generator w/calibrated output and dB scale,

0 dBµ = 0.5µV

r Signal Generator with calibrated output

r Spectrum Analyzer (60 MHz) or receiver (30 MHz)

r Frequency Counter

r 50 Ω Dummy Load (200 watts)

r 16.6 Ω Dummy load (200 watts)

r In-Line Wattmeter (200 watts, 50 Ω)

r Linear Detector

r RF Coupler

J4701 Pin-3

Carrier Frequency

Connect Frequency Counter (1.485760 MHz ± 5 Hz)

TCXO Unit Test & Alignment Points

3-1

Alignment

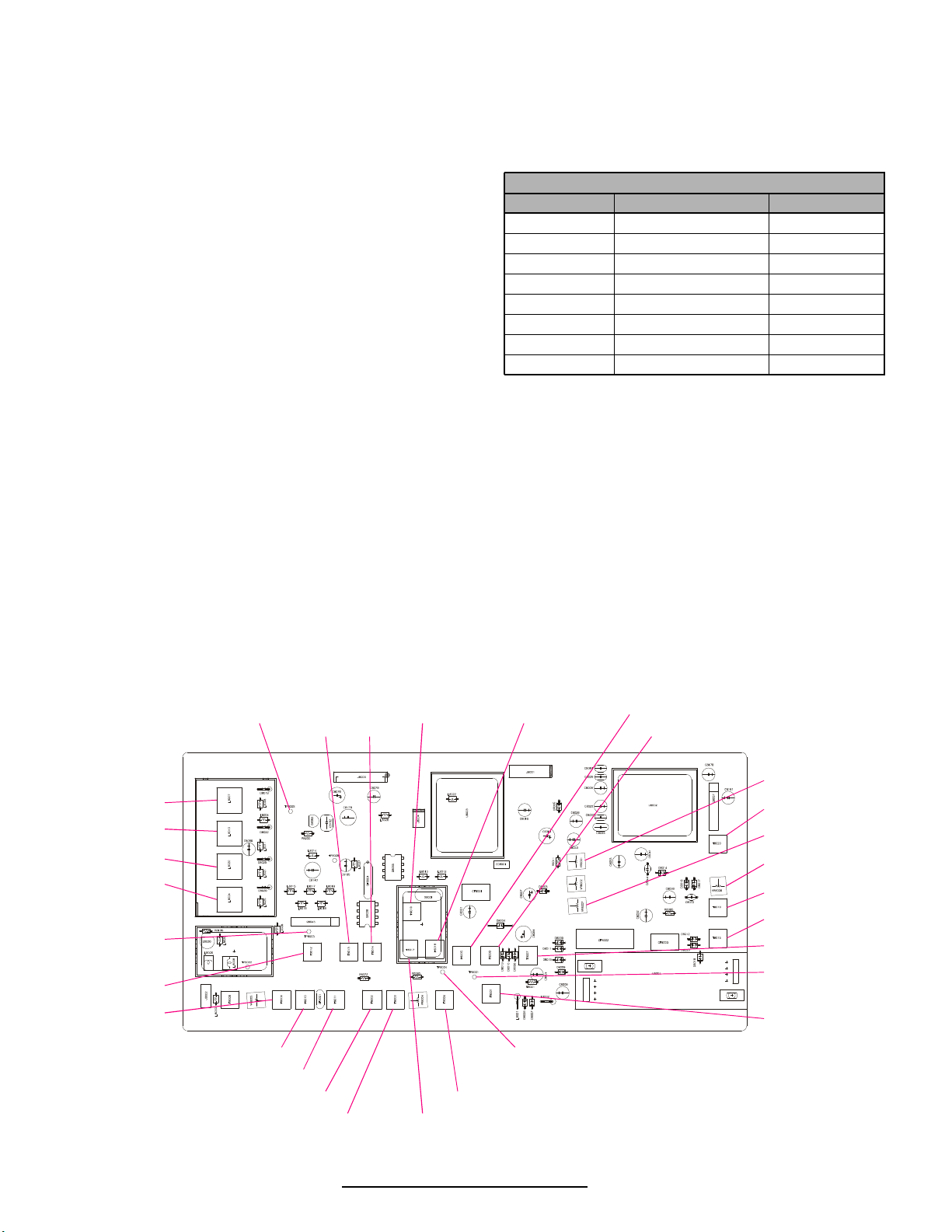

RX2 Unit

Local Section 2nd OSC

Refer to the drawing at the page bottom for the RX2 Unit com-

ponent locations and alignment points.

r Connect the RF millivoltmeter to TP8004, then adjust T8016,

T8017, and T8018 in succession several times for peak RF

millivoltmeter indication.

2nd Local Frequency

r Connect the frequency counter to TP8004, then adjust T8018

for 46.755 MHz (± 600 Hz) on the frequency counter.

2nd Local Amplifier

r Connect the RF millivoltmeter to TP8004, then adjust T8016

and T8017 in succession several times for peak RF

millivoltmeter indication (at least 500 mVrms).

PLL BPF

r Connect the RF millivoltmeter to TP8003, then adjust T8012,

T8013, and T8014 in succession several times for peak RF

millivoltmeter indication (at least 60 mVrms).

PLL Loop VCO

r Connect the DC voltmeter to TP8005. Tune the transceiver

display to the frequencies shown in the chart below, and adjust

the components listed for the corresponding voltage, or else

confirm required voltages.

PLL Loop VCO Alignment

Tune to:

7.499 MHz

0.100 MHz

14.499 MHz

7.500 MHz

21.999 MHz

14.500 MHz

30.000 MHz

22.000 MHz

Adjust/Confirm

Adjust L8007

Confirm

Adjust L8010

Confirm

Adjust L8020

Confirm

Adjust L8024

Confirm

for

7.0 ± 0.1 V

1.3 ~ 2.5 V

7.5 ± 0.1 V

1.3 ~ 2.5 V

7.5 ± 0.1 V

1.3 ~ 2.5 V

7.0 ± 0.1 V

1.3 ~ 2.5 V

RX Section Interstage Transformers

r Connect the RF signal generator to the antenna jack.

r Inject an RF signal (no modulation), and adjust T8002, T8004

~ T8007, T8009 ~ T8011, T8015, T8019, and T8020 in

succession several times for peak S-meter indication (adjust

the injection level as necessary to keep the meter around the

low side of the S-meter scale).

Connect DC Voltmeter (7.0 V ± 0.1 V)

L8007

PLL Loop VCO

L8010

PLL Loop VCO

L8020

PLL Loop VCO

L8024

PLL Loop VCO

TP8003

Connect RF Millivoltmeter

RX2 RX IF Transformer

PLL BPF

(>60 mVrms)

T8012

PLL BPF

T8009

TP8005

PLL Loop VCO

RX2 RX IF Transformer

RX2 RX IF Transformer

T8010

RX2 RX IF Transformer

RX2 RX IF Transformer

PLL BPF

T8011

T8013

T8002

PLL BPF

T8003

T8014

T8018

2nd Oscillator

2nd Local Amplifier

T8004

RX2 RX IF Transformer

T8017

2nd Oscillator

2nd Local Amplifier

T8016

2nd Oscillator

2nd Local Amplifier

TP8004

2nd Oscillator: Connect RF Millivoltmeter (peak)

2nd Local Frequency: Connect Frequency Counter (46.775 MHz ± 600 Hz)

2nd Local Amplifier: Connect RF Millivoltmeter (>500 mVrms)

T8005

RX2 RX IF Transformer

T8006

RX2 RX IF Transformer

VR8001

FM Squelch Threshold

T8020

RX2 RX IF Transformer

VR8007

S-Meter Full Scale

VR8006

IF Gain

T8019

RX2 RX IF Transformer

T8015

RX2 RX IF Transformer

T8007

RX2 RX IF Transformer

T8001

Noise Blanker

Connect DC Voltmeter

(minimum)

T8001

Noise Blanker

3-2

RX2 Unit Test & Alignment Points

Alignment

IF Gain

r Inject a +11 dBµ signal to the antenna jack, and tune the main

dial for peak indication on the S-meter.

r Now adjust VR8006 for 1-dot S-meter deflection.

S-Meter Full Scale

r Inject a +100 dBµ signal to the antenna jack, and tune the main

dial for peak indication on the S-meter.

r Adjust VR8007 for S9 +60 dB on the S-meter.

FM Squelch Threshold

r In FM mode, with no signal at the antenna jack, set the SQL

control to the 11-o’clock position.

r Now adjust VR8001 so that the squelch just closes.

SSB Squelch Threshold

r In the SSB mode, with no signal at the antenna jack.

r Confirm that the SQL control is in the 9- to 12-o’clock posi-

tion when the squelch is just closed.

Noise Blanker

r Connect the DC voltmeter to TP8001, press the NB button,

then inject a +40 dBµ signal to the antenna jack.

r Adjust T8001 for minimum indication in the DC voltmeter.

Reduce the injection level to +23 dBµ and confirm that the

voltage is now less than 3.4 V.

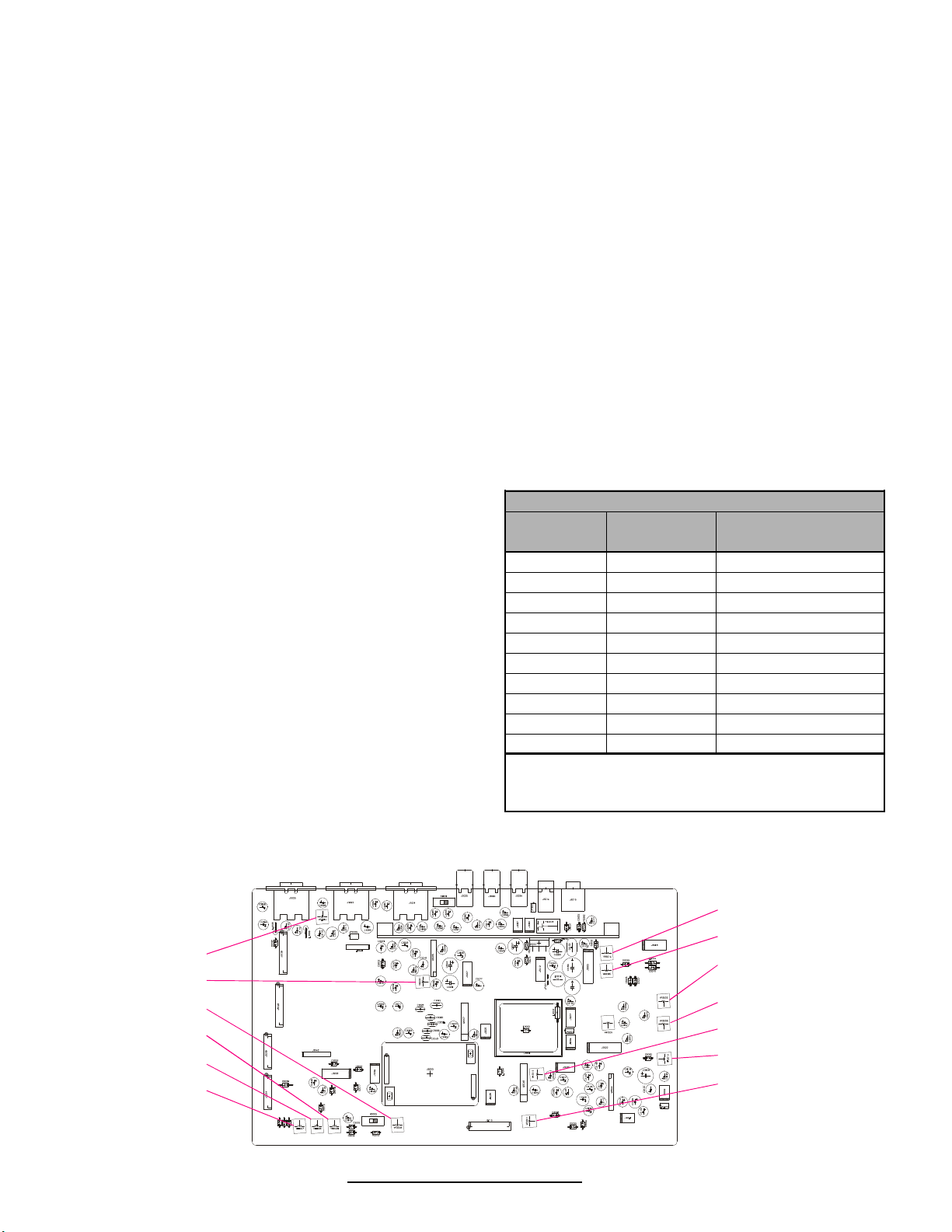

Local Unit

Refer to the drawing at the page bottom for LOCAL Unit component locations and alignment points.

2nd Local Oscillator

r Connect the RF millivoltmeter to TP4002, and adjust T4001

for maximum indication on the RF millivoltmeter (at least 400

mVrms), then turn T4001 1/4-clockwise futher more.

r Replace the RF millivoltmeter with a frequency counter at

TP4002, and confirm the frequency counter reading is 62.240

MHz (±600 Hz).

2nd Local Oscillator Amplifier

r Remove the coaxial plug from J4002, and connect a 50 Ω

resistor in parallel with the RF millivoltmeter across the socket.

r Adjust T4006 and T4007 in succession several times for peak

RF millivoltmeter indication (at least 170 mVrms).

r Remove the meter and resistor, and replace the plug into J4002.

WIDTH DDS Amplifier

r Connect the RF millivoltmeter to TP4004, and adjust T4010

for maximum indication on the RF millivoltmeter (at least 70

mVrms ).

3rd Local Amplifier

WIDTH DDS Amplifier

WIDTH DDS Amplifier

Connect RF Millivoltmeter

2nd Local Amplifier

T4009

T4010

TP4004

(>70 mVrms)

T4006

3rd Local Amplifier: Connect 50 Ω Dummy

in parallel with RF Millivoltmeter (>100 mVrms)

2nd Local Amplifier

2nd Oscillator:Connect RF Millivoltmeter (>400 mVrms)

T4008

Frequency Counter (62.24 MHz ± 200 Hz)

2nd Local Amplifier

J4003

T4007

TP4002

PLL BPF (67.98 MHz)

PLL BPF (67.98 MHz)

PLL BPF (67.98 MHz)

T4005

T4004

TP4005

PLL Main Loop VCO: Connect DC Voltmeter (1.65 V ± 0.01 V)

T4003

VR4001

PLL Main Loop VCO

J4002

2nd Local Amplifier: Connect 50 Ω Dummy

TP4003

PLL Main Loop VCO: Connect DC Voltmeter (8.5 V ± 0.1 V)

TP4001

PLL BPF (67.98 MHz): Connect RF Millivoltmeter (>100 mVrms)

T4002

PLL BPF (67.98 MHz)

in parallel with RF Millivoltmeter (>170 mVrms)

TC4001

PLL Main Loop VCO

TC4002

PLL Main Loop VCO

TC4003

PLL Main Loop VCO

TC4001

PLL Main Loop VCO

Local Unit Test & Alignment Points

3-3

Alignment

3rd Local Amp

r Remove the coaxial plug from J4003 and connect a 50 Ω re-

sistor in parallel with the RF millivoltmeter across the socket.

r Adjust T4008 and T4009 in succession several times for peak

RF millivoltmeter indication (at least 100 mVrms).

r Replace the RF millivoltmeter with a frequency counter at

J4003, and confirm that the frequency is 8.670 MHz (±30 Hz).

r Remove the frequency counter and resistor, and replace the

plug in J4003.

PLL BPF (67.98 MHz)

r Connect the RF millivoltmeter to TP4001, and adjust T4002

~ T4005 in succession several times for peak RF millivoltmeter

indication (at least 100 mV).

PLL Main Loop VCO

r Connect the DC voltmeter to TP4003.

r Referring to the table below, tune the transceiver to each fre-

quency, then confirm or adjust the listed component for the

required voltage.

r Tune the transceiver display to 14.200 MHz. Connect the DC

voltmeter to TP4005, and adjust VR4001 for 1.65V (±0.05

V) on the DC voltmeter.

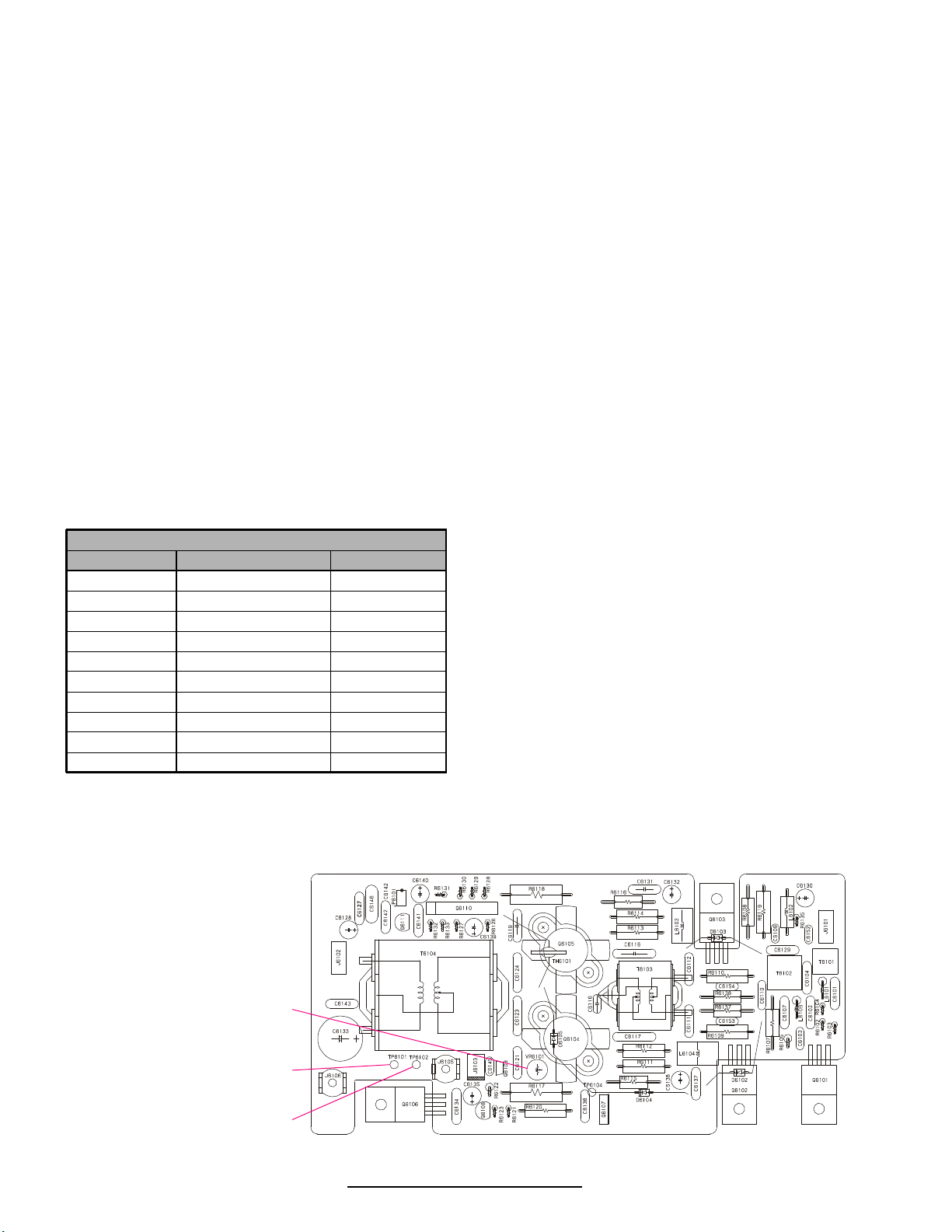

PA Unit

Refer to the drawing below for PA Unit component locations

and alignment points.

Idling Current (Class “AB”)

r Temporarily disconnect the jumper wire which connected be-

tween TP6101 and TP6102, and connect an ammeter in place

of the jumper.

r Key the transmitter in either USB or LSB with no microphone

input, and adjust VR6101 for 400 mA (±50 mA).

r Reinstall the jumper.

Idling Current (Class “A”)

r Temporarily disconnect the jumper wire which connected be-

tween TP6101 and TP6102, and connect an ammeter in place

of the jumper.

r Press the CLASS-A switch. Key the transmitter in either USB

or LSB with no microphone input, and adjust VR9001 on the

REG Unit for 9.0 A (±0.2 A).

r Depress the CLASS-A switch, then reinstall the jumper.

PLL Main Loop VCO Alignment

Tune to:

7.499 MHz

4.000 MHz

3.999 MHz

0.100 MHz

14.499 MHz

7.500 MHz

21.999 MHz

14.500 MHz

30.000 MHz

22.000 MHz

Adjust/Confirm

Adjust TC4001

Confirm

Confirm

Confirm

Adjust TC4002

Confirm

Adjust TC4003

Confirm

Adjust TC4004

Confirm

for

8.5 ± 0.1 V

1.3 ~ 3.5 V

6.5 ~ 8.5 V

1.5 ~ 2.5 V

8.5 ± 0.1 V

1.3 ~ 2.3 V

8.5 ± 0.1 V

1.3 ~ 2.3 V

8.5 ± 0.1 V

1.3 ~ 2.3 V

Idling Current (Class-AB)

Idling Current (Class-AB): Connect DC Ammeter

Idling Current (Class-AB): Connect DC Ammeter

3-4

VR6101

TP6101

(400 mA ± 50 mA)

TP6102

(400 mA ± 50 mA)

PA Unit Test & Alignment Points

Alignment

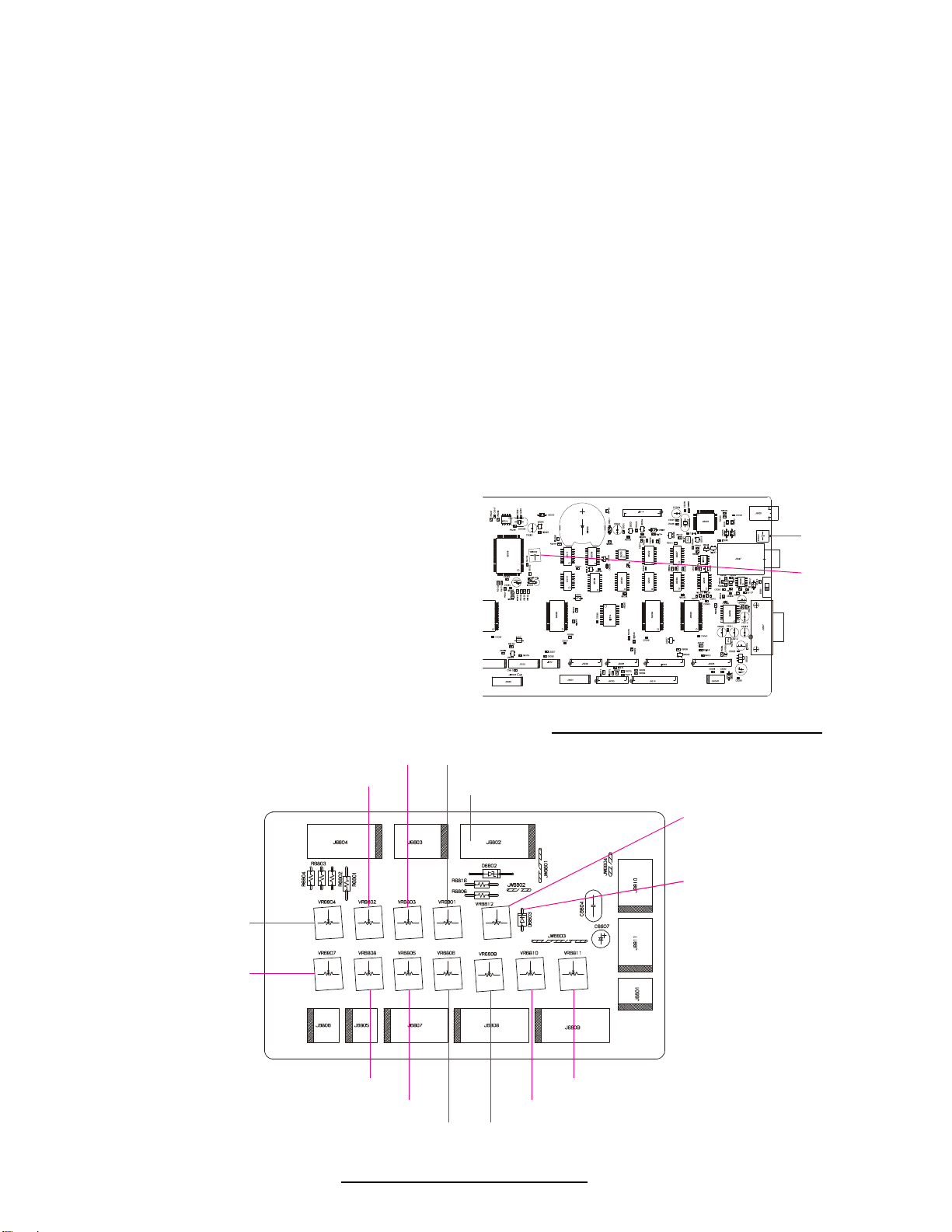

LPF Unit

Refer to the drawing below for LPF Unit component locations

and alignment points.

CM Coupler Balance

r Connect the DC voltmeter to pin 3 of JP6002, connect a 50 Ω

dummy load to the antenna jack, and select the CW mode.

r Key the transmitter, and adjust TC6001 for minimum indica-

tion on the DC voltmeter.

TC6001

CM Coupler Balance

JP6002

CM Coupler Balance: Connect DC Voltmeter (minimum)

LPF Unit Test & Alignment Points

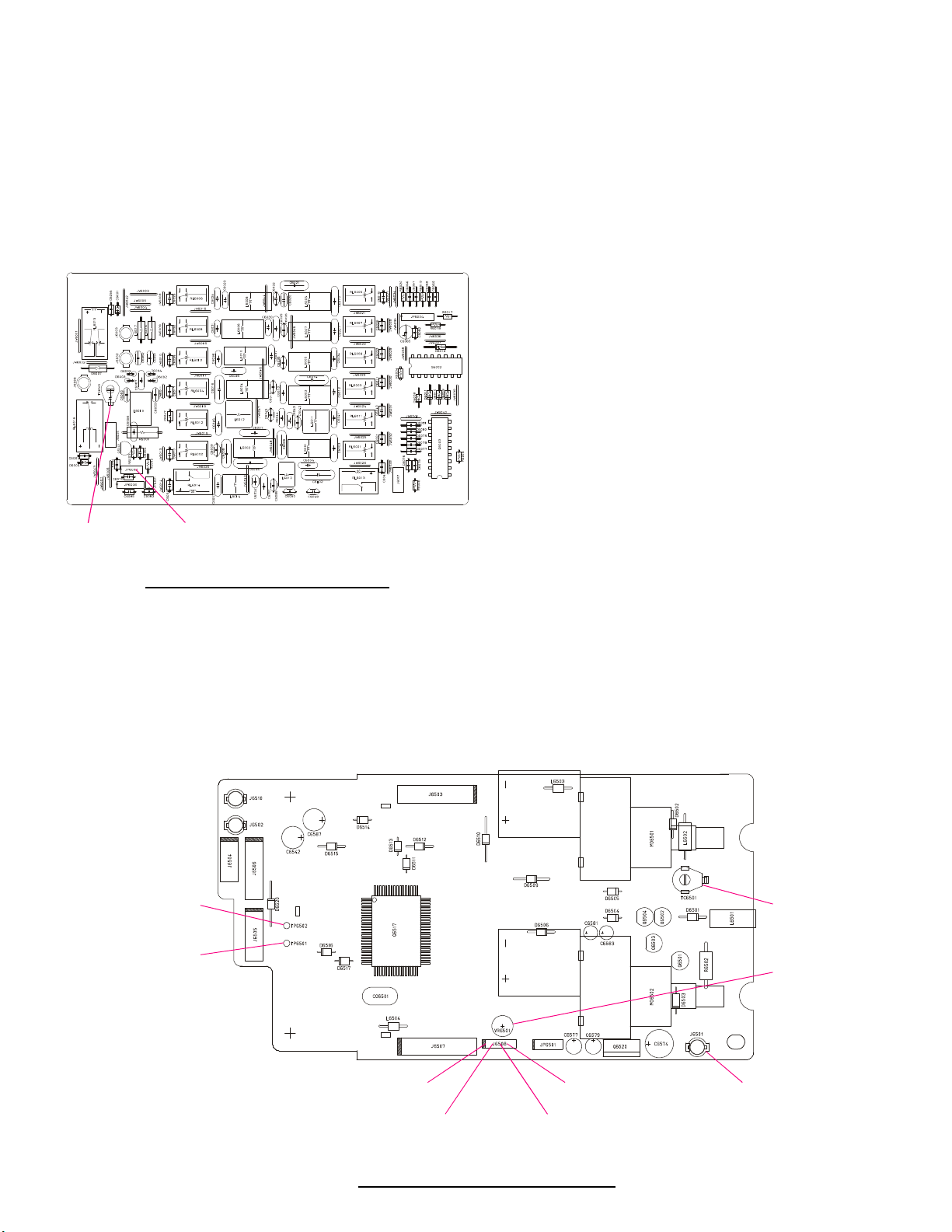

TUNER-CNTL Unit

Refer to the drawing at the page bottom for TUNER-CNTL

Unit component locations and alignment points.

Tuning Capacitor/Motor

(Mechanical check, setting & adjustment)

r Loosen all set screws in the shaft coupler, and turn the coupler

by hand to confirm it moves freely (the motor and capacitor

should not move).

r If the coupler binds, check the motor mounting position (it is

soldered in place) and the capacitor mounting screw.

r Turn the power switch off, and jumper TP6501 to chassis

ground. Turn the power switch on. The motor should rotate,

and then stop.

r Set the capacitor to its maximum capacitance position (plates

fully meshed) by hand, and tighten all shaft coupler set screw,

using care not to disturb the capacitor or motor positions.

r Turn the power off, and jumper TP6502 to chassis ground

(along with TP6501). Turn the power back on. The motor

should move 180°, and the capacitor should be then at mini-

mum capacitance (fully unmeshed). Remove the grounding

jumpers from TP6501 and TP6502.

Tuner Impedance & Phase Detection

r Connect the 50 Ω dummy load and wattmeter to J6501 (the

output of the Tuner-Control Unit), and select the CW mode.

r Connect the DC voltmeter between pin-1 (IZIi) and pin-2 (IZIV)

of J6508 (either polarity).

r Press the TUNER and MOX buttons, adjust the RF PWR con-

trol for 50 watts output, and then adjust TC6501, if necessary,

for meter indication within ±0.08 V of 0 V.

r While still transmitting, move the DC voltmeter to pin-3 (fC)

and pin-4 (f L) of J6508 (either polarity), and adjust VR6501,

if necessary, for meter indication within ±0.02 V of 0 V.

TP6502

Tuning Capacitor:

Jumper to GND

TP6501

Tuning Capacitor:

Jumper to GND

J6508 Pin-1

Connect DC Voltmeter (0 V ± 0.08 V)

Connect DC Voltmeter (0 V ± 0.08 V)

Phase Detection:

J6508 Pin-2

Phase Detection:

Tuner Unit Test & Alignment Points

J6508 Pin-4

Phase Detection:

Connect DC Voltmeter (0 V ± 0.02 V)

J6508 Pin-3

Phase Detection:

Connect DC Voltmeter (0 V ± 0.02 V)

TC6501

Tuning Impedance &

Phase Detection

VR6501

Phase Detection

J6501

Tuning Impedance &

Phase Detection:

Connect 50 Ω Dummey with Wattmeter

3-5

Alignment

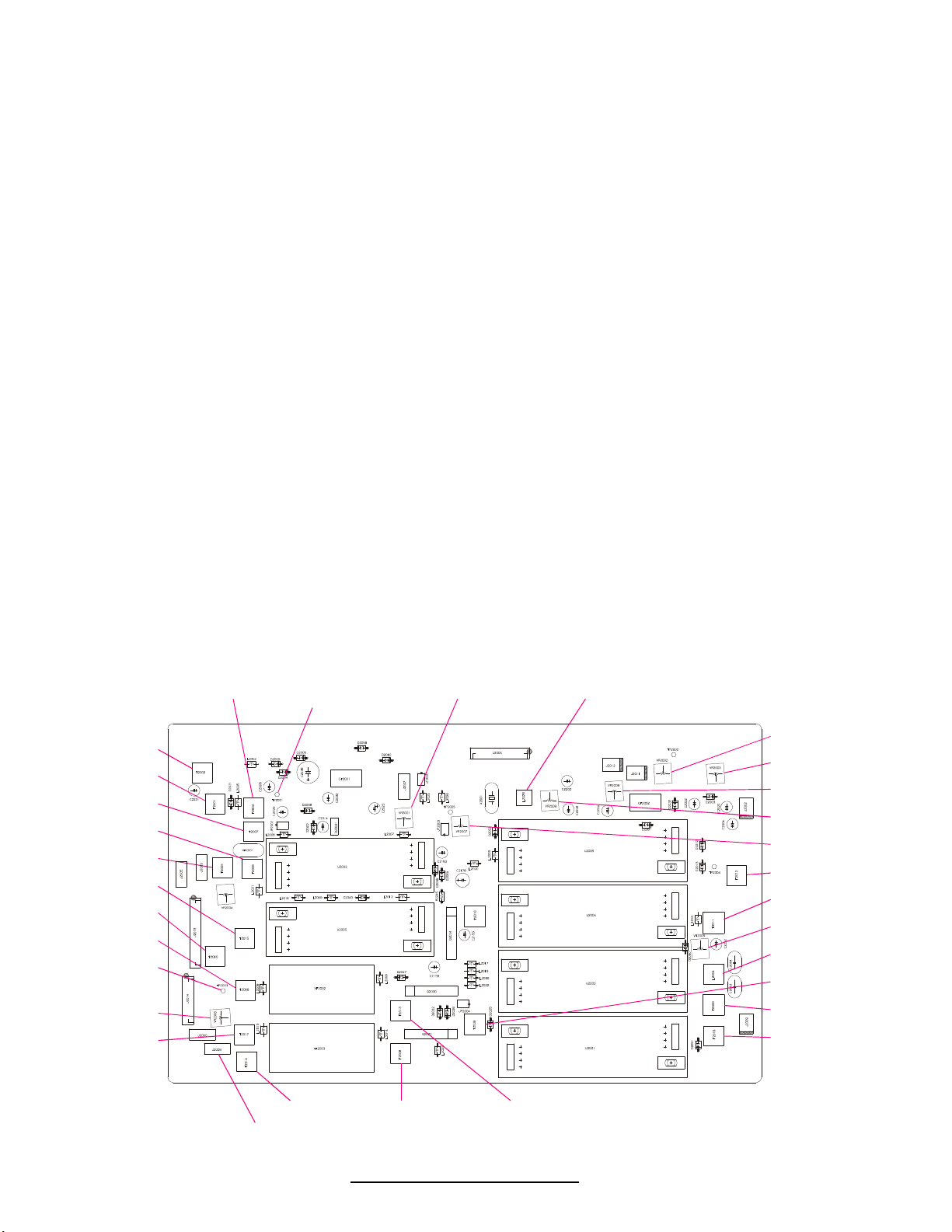

IF Unit

Refer to the drawing at the page bottom for IF Unit component

locations and alignment points.

2nd & 3rd Local Amplifiers

r Connect the RF millivoltmeter to TP2003, and adjust T2010

for maximum indication on the RF millivoltmeter (at least 450

mVrms ).

r Next, connect the RF millivoltmeter to TP2005, and confirm

at least 100 mVrms.

Rx IF Interstage Transformer (I) (Coarse Alignment)

r Connect the RF signal generator to J2003, and inject a +100

dBu signal at 70.455 MHz. Connect the AC voltmeter across

and an 4 Ω dummy load to the EXT SP jack on the rear panel.

r Adjust T2003 ~ T2009, T2011, and T2012 in succession sev-

eral times for peak indication on the AC voltmeter.

Receiver Section

RF Interstage Transformers (Coarse Alignment)

r Preset VR1001 and VR1002 to their 12-o’clock positions, and

select either USB or LSB mode. Adjust T1005 ~ T1009 on

the RF Unit in succession several times for peak noise from the

speaker.

S-Meter (Coarse Alignment)

r Preset VR2003 fully counter-clockwise, and adjust VR2003

so that all S-meter segments are just turned off. Preset the RF

GAIN control fully counter-clockwise, and adjust VR2002 for

S9+60 dB on the S-meter.

1st Mixer Balance

r Tune the transceiver to 1.800 MHz, then adjust VR1001 and

VR1002 for minimum noise from the speaker.

IF Interstage Transformers (II)

r Connect the RF signal generator to the antenna jack, and inject

a +80 dBµ signal at 14.2000 MHz.

r Select the USB mode, and tune the transceiver to 14.20220

MHz (so that a 2200 Hz tone is heard); adjust T1005 ~ T1009,

T2003 ~ T2009, T2011, and T2012 in succession several

times for peak S-meter indication (adjust the injection level as

necessary to keep the meter around mid scale).

T2002

Noise Blanker

T2001

Noise Blanker

RX IF Transformer

RX IF Transformer

RX IF Transformer

TX IF Transformer

2nd & 3rd Local Amplifier

TX IF Transformer

2nd & 3rd Local Amplifier:

Connect RF Millivoltmeter

TX IF Transformer

T2007

T2006

T2005

T2015

T2010

T2018

TP2003

(> 500 mVrms)

VR2006

TX 2nd Mixer

T2017

RX IF Transformer

T2004

TP2001

Noise Blanker:

Connect DC Voltmeter (minimum)

T2014

TX IF Transformer

J2008

TX 2nd Mixer: Connect Spectrum Analyzer (minimize 2nd local spurious)

T2008

RX IF Transformer

VR2001

FM Squelch Threshold

T2013

TX IF Transformer

L2026

FM Carrier Frequency

VR2002

S-Meter Full Scale

VR2003

S-Meter

VR2008

CTCSS Tone Deviation

VR2009

FM Deviation

VR2007

COMP Meter Calibration

T2012

RX IF Transformer

T2011

RX IF Transformer

VR2005

IF Notch

L2004

IF Notch

T2009

RX IF Transformer

T2003

RX IF Transformer

T2019

TX IF Transformer

3-6

IF Unit Test & Alignment Points

Alignment

RF Amplifiers

r Confirm that menu function 8-4 is set to “Tuned,” then connect

the RF signal generator to the antenna jack, and inject a +20

dBµ signal.

r Referring to the table below, tune the transceiver and RF signal

generator to the listed frequencies, and adjust the corresponding components for the levels shown.

RF Amp Alignment

Tune SG & Radio to

1.910 MHz

3.725 MHz

7.110 MHz

28.200 MHz

Adjust

T1020

T1021

T1022

T1016

for

Max S-meter

Max S-meter

Max S-meter

Max S-meter

VRF

r Turn the transceiver off, then press and hold the [SUB] and

[

ENT] keys of the keypad, and turn the transceiver on again.

r Connect the RF signal generator to the antenna jack, and inject

a +20 dBµ signal.

r Press the VRF button on the shuttle Jog, then adjust the VRF/

MEM CH knob to illuminate the “center” segment of the Ex-

panded Tuning Scale (above the main VFO-A frequency display).

r Referring to the table below, tune the transceiver and RF signal

generator to the listed frequencies, and adjust the corresponding components for the levels shown.

VRF Alignment

Tune SG & Radio to

1.910 MHz

3.775 MHz

7.260 MHz

10.100 MHz

14.100 MHz

Adjust

T1026 & T1027

T1028 & T1029

T1030 & T1031

T1032 & T1033

T1034 & T1035

for

Max S-meter

Max S-meter

Max S-meter

Max S-meter

Max S-meter

IF Gain

r Turn the transceiver off, then press and hold in the FAST and

LOCK buttons (near the main VFO knob), and turn the trans-

ceiver on again.

r Connect the RF signal generator to the antenna jack, and inject

a +11 dBµ signal. Select menu function 9-1, and adjust the

main VFO knob for a 1-segment S-meter deflection.

S-meter Full Scale

r Connect the RF signal generator to the antenna jack, and inject

a +100 dBµ signal.

r Tune for peak indication on the S-meter. Now adjust VR2002

for S9+60 dB on the S-meter.

Noise Blanker

r Set menu function 2-8 to “A15,” then press the NB switch on,

and connect the DC voltmeter to TP2001.

r Connect the RF signal generator to the antenna jack and inject

a +40 dBµ signal, then adjust T2001 and T2002 in succession

several times for minimum DC voltmeter indication.

r Reduce the RF signal level to +20 dBµ, and confirm at least

2.8 V on the DC voltmeter.

IF Notch

r Preset the NOTCH control to 12-o’clock, then inject a +30

dBµ signal at 14.2000 MHz to the antenna jack. Select USB,

then tune the transceiver to 14.20150 MHz (so that a 1500 Hz

tone is heard).

r Press the NOTCH button, then adjust VR2005 and L2004 for

minimum S-meter indication.

FM Squelch Threshold

r With the FM mode selected, and no signal present, set the SQL

control to the 11-o’clock position, then adjust VR2001 so that

the squelch just closes.

T1026

VRF

T1027

VRF

T1028

VRF

T1029

VRF

T1030

VRF

T1031

VRF

VRF

T1033

VRF

VRF

T1035

VRF

T1034

T1032

RF Unit Test & Alignment Points

T1021

Transmitter IF Interstage Transformer

T1022

Transmitter IF Interstage Transformer

T1020

Transmitter IF Interstage Transformer

T1016

Transmitter IF Interstage Transformer

VR1001

RF Interstage Transformers Coarse Alignment

1st Mixer Balance

VR1002

RF Interstage Transformers Coarse Alignment

1st Mixer Balance

T1009

IF Interstage Transformers (II)

T1008

IF Interstage Transformers (II)

T1007

IF Interstage Transformers (II)

T1005

IF Interstage Transformers (II)

T1006

IF Interstage Transformers (II)

3-7

Alignment

Transmitter Section

Tx 2nd Mixer

r Select the CW mode, and connect the spectrum analyzer

(FCENTER = 70.455 MHz) to J2008.

r Key the transmitter, and adjust VR2006 to minimize the 2nd

local spurious (±8.2 MHz from the 2nd local frequency).

Transmitter IF Interstage Transformers

r Connect the 50 Ω dummy load to the antenna jack. Preset the

RF PWR control fully clockwise, and MIC gain control fully

counter-clockwise. Select CW mode.

r Key the transmitter, and adjust T1001, T1002, T2013 ~

T2015, and T2017 ~ T2019 in succession several times for

maximum indication on the ALC meter.

Overcurrent ALC

r With the inline wattmeter and 50 Ω dummy load connected to

the antenna jack and the RF PWR control fully clockwise. Set

S3002 on the AF Unit to the “100W” position.

r Tune the transceiver to 3.500 MHz, and select the CW mode.

Key the transmitter, and adjust VR3008 for 140 watts on the

wattmeter.

Maximum RF Power Output

r Preset the RF PWR control fully clockwise, and tune the trans-

ceiver to 14.2000 MHz. Select the CW mode, key the transmitter, and adjust VR3003 for 100 watts on the meter.

25 W and 10 W RF Power Output

r Connect the in-line wattmeter and 50 Ω dummy load to the

antenna jack, select the CW mode, and tune to 14.2000 MHz.

r Set the menu function 4-0 to “Lo-2.”

Set the RF PWR control fully clockwise.

r Key the transmitter, and adjust VR3007 for 25 watts (±2 watts)

on the power meter.

r Recall menu function 4-0, and select “Lo-1.” Key the trans-

mitter, and adjust VR3006 for 10 watts (±1 watt) on the power

meter.

r After adjustment, recall menu function 4-0., then select “HI.”

TX Drive Control

r Set the RF PWR control fully counter-clockwise, and select

the CW mode. Key the transmitter, and adjust VR3013 so that

one segment is displayed on the PO meter.

ALC Meter Sensitivity

r Set the meter function to ALC, then inject a 1 kHz tone at 4 mV

level to the microphone jack. Key the transmitter, and adjust

the MIC gain control so the meter just begins to deflect.

r Increase the injection level to 10 mV, and adjust VR3005 so

that the meter deflects to the top edge of the ALC zone.

TX IF Gain

r Turn the transceiver off. Next, press and hold the FAST and

LOCK keys (near the main VFO knob), then turn the trans-

ceiver on.

r For the frequencies listed in the table below, set the transceiver

to LSB mode, and inject a 1 kHz tone at 0.5 mV level to the

microphone jack. Set the MIC gain control fully clockwise. Be

sure to check the Menu display for the correct alignment item.

TX IF Gain Alignment

TX IF Gain Alignment

Tune to:

1.800 MHz

3.750 MHz

7.150 MHz

10.125 MHz

14.175 MHz

18.100 MHz

21.200 MHz

24.900 MHz

28.500 MHz

29.500 MHz

Menu

Function 9-2

T IF-018

T IF-035

T IF-070

T IF-100

T IF-140

T IF-180

T IF-210

T IF-245

T IF-280

T IF-290

Note: For all adjustments below, set the transceiver to LSB,

and inject a 0.5 mV, 1-kHz to the MIC jack. Set the MIC

gain control fully clockwise.

Key Tx and adjust

Main VFO Dial for

Mininum ALC Indication

Mininum ALC Indication

Mininum ALC Indication

Mininum ALC Indication

Mininum ALC Indication

Mininum ALC Indication

Mininum ALC Indication

Mininum ALC Indication

Mininum ALC Indication

Mininum ALC Indication

PKT RX AF Level Preset

Key Beeper Level Preset

SSB Squelch Threshold

Maximum RF Power Output

25 W and 10 W RF Power Output

25 W and 10 W RF Power Output

3-8

VR3010

VR3001

VR3009

VR3003

VR3006

VR3007

AF Unit Test & Alignment Points

VR3014

PO Meter Calibration

VR3015

SWR Meter Calibration

VR3002

Overcurrent ALC

REV ALC

VR3005

ALC Meter Secsitivity

VR3012

SSB Modulation Balance

VR3013

TX Drive Control

VR3011

AM Carrier Level

Alignment

PO Meter Calibration

r With the wattmeter and 50 Ω dummy load connected to the

antenna jack, select the CW mode and set the meter to read

power output.

r Key the transmitter, and adjust the RF PWR control for 100

watts on the external wattmeter. Then adjust VR3014 so the

transceiver’s PO meter also indicates 100 watts.

Reverse ALC

r Connect the 16.6 Ω dummy load (or three 50 Ω loads in paral-

lel) to the antenna jack, preset the RF PWR control fully-clock-

wise, and select the CW mode. Key the transmitter, and adjust

VR3002 for 50 watts on the transceiver’s PO meter.

SWR Meter Calibration

r Connect the 16.6 Ω dummy load (or three 50 Ω loads in paral-

lel) to the antenna jack, then preset the RF PWR control fully

clockwise. Select the CW mode, and set the meter to read SWR.

r Key the transmitter, and adjust VR3015 so the meter indicates

3.0:1 SWR (within 1 bargraph segment).

IC Meter Calibration Check

r With the wattmeter and 50 Ω dummy load connected to the

antenna jack, select the CW mode, and set the meter to read

IC. Preset the RF PWR control fully clockwise.

r Key the transmitter, and confirm 12A ~ 21A IC meter indica-

tion.

FM Carrier Frequency

r With the 50 dB attenuator and frequency counter (or 50 Ω

dummy load and sampling coupler) connected to the antenna

jack, preset the FM mic gain control fully counter-clockwise,

select the FM mode, and tune to 29.0000 MHz. Key the transmitter, and adjust L2026 for 29.0000 MHz (±50 Hz) on the

frequency counter.

FM & CTCSS Tone Deviation

r With the 50 dB attenuator and linear detector (or 50 Ω dummy

load and sampling coupler) connected to the antenna jack, select the FM mode, and tune to 29.2000 MHz.

r Set the FM mic gain control fully clockwise, and inject a 1 kHz

tone at 10 mV level to the mic jack. Key the transmitter, and

adjust VR2009 for ±2.3 kHz (±0.1 kHz) on the linear detector.

r Select the 88.5 Hz (default) subaudible tone, and press the RPT

button to activate CTCSS operation. Key the transmitter and

with no microphone input, and adjust VR2008 for 0.5 kHz

±0.1 kHz on the liner detector.

FM Mic Gain

r With the 50 dB attenuator and linear detector (or 50 Ω dummy

load and sampling coupler) connected to the antenna jack, tune

to 29.200 MHz, and select FM mode.

r Inject a 1.8 mV signal at 1 kHz to the MIC jack. Key the trans-

mitter, and adjust VR6807 for 1.75 kHz ±0.1 kHz on the linear detector.

SSB Modulator Balance

r With the 50 dB attenuator and spectrum analyzer (or 50 Ω

dummy load and sampling coupler) connected to the antenna

jack, and the MIC gain control preset fully counterclockwise,

select either SSB mode. Alternatively, a separate receiver can

be used, with the transceiver connected to the dummy load.

r Set the menu function 8-9 to “-200.”

r Key the transmitter, and adjust VR3012 for minimum power

output (carrier leakage, which should be lower than -50 dB) as

indicated on the spectrum analyzer or external receiver.

AM Carrier Level

r With the wattmeter and 50 Ω dummy load connected to the

antenna jack, select the AM mode, and set the meter to read

ALC. With no microphone input, preset the RF PWR control

to the fully clockwise position. Key the transmitter, and adjust

VR3011 for ALC meter deflection to the top edge of the ALC

zone.

COMP Meter Calibration

r Set the PROC and RF PWR controls fully clockwise, and

press the PROC button to activate the speech processor.

r Set the meter to read COMP, and preset the MIC gain control

to the 1-o’clock position. Inject a 1 kHz tone at 2 mV level to

the mic jack, and adjust VR2007 so that the transceiver’s

COMP meter deflects to the 10 dB mark on the COMP scale.

Transmitter Carrier Point

r Turn the transmitter off, then press and hold in the FAST and

LOCK buttons (near main VFO knob), then turn the transceiver

on.

r Recall menu function 9-0 and select “t-LsbcAr” using the

SUB VFO-B dial.

r Select the LSB mode and then inject a 1 kHz tone to the mic

jack. Adjust the injection level to the point where the ALC meter

no longer deflects.

r Adjust the injection frequency (within 800 ~ 2000 Hz) for peak

RF output, then adjust the injection level for 80 W RF output.

r Set the injection frequency to 350 Hz, and adjust the MAIN

VFO-A knob for 20 W RF output.

r Select “t-uSbcAr” using the SUB VFO-B knob, and select the

USB mode. Inject a 1-kHz tone to the mic jack, and adjust the

injection level to the point where the ALC meter no longer

deflects.

r Adjust the injection frequency (from 800 ~ 2000 Hz) for peak

RF output, then adjust the injection level for 80 W RF output.

r Set the injection frequency to 350 Hz, and adjust the MAIN

VFO-A knob for 20 W RF output.

3-9

Alignment

Tuning Meter Center Preset

r Select the CW mode, and turn the SPOT function on.

r Connect the DC voltmeter to the cathode of D6803, and adjust

the PITCH control for at least 4.0 V on the DC voltmeter.

r Connect the DC voltmeter to the “common” lead of VR6812,

and adjust VR6812 for 2.7 V (±0.1 V) on the DC voltmeter.

r Connect the DC voltmeter to pin 5 of J6802, and adjust

VR6802 for 3.4 V (±0.1 V) on the DC voltmeter.

r Finally, adjust VR6812 for a centered tuning meter indication.

Tuning Meter Preset (CW, RTTY and PKT Modes)

r Recall menu function 3-5, and select “A1-PitcH” using the

MAIN VFO-A knob. Tune to 700 Hz using the PITCH knob

(“C-700” displayed).

r Select the CW mode, press the SPOT key, and adjust VR6811

for a centered tuning meter indication.

r Select menu function 4-2, select the RTTY mode, and tune to

2210 Hz using the MAIN VFO-A knob.

r Select “bEEP-tun” using the SUB VFO-B knob, and adjust

VR6810 for a centered tuning meter indication.

r Tune a 2125 Hz beep frequency using the MAIN VFO-A knob,

and select the PKT mode.

r Select “bEEP-tun” using the SUB VFO-B knob, and adjust

VR6809 for a centered tuning meter indication.

PKT Receiver AF Level Preset

r Preset VR3010 fully clockwise. The level should be adjusted

by the owner, if necessary.

Key Beeper Level Preset

r Preset VR3001 fully counter-clockwise. The “beep” level may

be reduced by the owner, if desired.

Headphone Output Level Preset

r Preset VR6804 ~ VR6807 to their 12-o’clock positions. The

level may be adjusted by the owner, if desired.

VOX Gain, ANTI TRIP and Delay Presets

r Preset VR6812 (DELAY), VR6813 (A-VOX) and VR6812

(VOX) to their 12-o’clock positions. These controls will be

adjusted by the owner during setup of the transceiver.

BEEP and SIDETONE Preset

r Preset VR5001 (SIDETONE) and VR5002 (BEEP) to their

10-o’clock positions. These controls may be adjusted by the

owner, if desired.

VR5001

Side Tone Preset

Headphone Output Level Preset

VOX Gain, ANTI TRIP and Delay Presets

VR6804

VR6807

Headphone Output Level Preset

Headphone Output Level Preset

VR6802

VR6803

VR6801

Headphone Output Level Preset

J6802 Pin-5

Tuning Meter Center Preset

Connect DC Voltmeter (3.4 V ± 0.1 V)

VR5002

BEEP Preset

CNTL-1 Unit Test & Alignment Points

VR6812

Tuning Meter Center Preset

Connect DC Voltmeter (2.7 V ± 0.1 V)

D6803 (Cathode

Tuning Meter Center Preset

Connect DC Voltmeter (4.0 V)

)

3-10

VOX Gain, ANTI TRIP and Delay Presets

VOX Gain, ANTI TRIP and Delay Presets

VOX Gain, ANTI TRIP and Delay Presets

VR6808

ALC Unit Test & Alignment Points

VR6805

VR6806

VR6810

Tuning Meter Preset

VR6809

Tuning Meter Preset

VR6811

Tuning Meter Preset

Circuit Description

Main Receive Signal Circuitry

High-Frequency Circuit

The receive signal enters from ANT connector A or B, selected

by relays RL6452/RL6453 on the TUNER-MAIN Unit, and it then

passes through t/r relay RL6451 and is fed to connector J1003 on

the RF Unit from connector J6454.

The receive signal then passes through the “RX Antenna” antenna switching relay RL1003 and an attenuator (-6 dB, -12 dB; 18 dB when combined) which consists of resistors R1051-R1054

and relays RL1003 and RL1004.

If the VRF feature is engaged (available on 160-20 meters),

the signal then enters a narrow band-pass “preselector” filter which

consists of relays RL1006-RL1015, coils T1026-T1036, and capacitors C1253-C1264 and C1282-C1285. The preselector, which

provides high-Q filtering ahead of any active devices in the receiver circuitry, protects the components in the front end from strong

out-of-band energy.

The receive signal then enters a 5th-order Chebyshev low-pass

filter (LPF) which consists of coils L1087 and L1088 and capacitors C1035-C1039. After the signal is removed of frequency components of 30 MHz and above, it is fed to one of the band-pass

filter (BPF) networks.

The BPF is a 5th-order Chebyshev type filter; a total of 11

different bandpass filters are provided, covering the frequency range

100 kHz ~ 30 MHz in segments of different widths. Depending on

the receiver frequency, the appropriate band is selected by diodes

D1008-D1017 (all 1SV271), D1018-D1026 (all 1SS356), D1027-

D1031 (all 1SV271), and D1032-D1036 (all 1SS356). After re-

moval of unwanted frequency components, the incoming RF energy is applied to the high-frequency amplifier circuit.

The RF amplifier consists of a low-band amplifier circuit FET

Q1018 (3SK131), a mid-band amplifier circuit FETs Q1019Q1022 (all SST310), and a high-band amplifier circuit Q1028

(SST310). The appropriate amplifier circuit is selected* by D1037D1041 and D1045 (all 1SS356). After amplification, the signal is

applied to the 1st mixer circuit and/or the sub-receive circuit (RX2

Unit).

* Note - If “Flat” is selected in Menu Program 8-4, RF signal

input is sent to the mid- band amplifier circuit.

Diodes D1046 and D1047 (both 1SS356), which are connected

to the RF amplifier input and output, turn on (off) the amplifier

circuit via the front-panel IPO switch.

1st Mixer Circuit/1st IF Circuit

The 1st mixer of the RF Unit consists of junction FETs Q1010Q1013 (all SST310). The 1st local signal (70.555 ~ 100.455 MHz)

from the LOCAL Unit is amplified by Q1014 (2SC2053) and

applied to the gates of each FET in the 1st mixer.

the 1st IF signal having a center frequency of 70.455 MHz. The

signal is fed to the 2nd mixer circuit of the IF Unit after it is amplified by FET Q1009 (2SK131).

2nd Mixer Circuit/2nd IF Circuit

The 2nd mixer consists of FETs Q2020 and Q2024 (both

2SK302GR) on the IF Unit. The 2nd local signal (62.24 MHz)

from the LOCAL Unit is amplified by Q2027 (2SC2812) and is

applied to each FET’s gate in the 2nd mixer.

The output from the 2nd mixer passes through monolithic crystal

filter XF2001, where it is stripped of unwanted signal components

to become the 2nd IF signal (8.215 MHz). A portion of the 2nd IF

signal from the mixer output is fed to the FM IF circuit through a

noise blanker circuit and buffer-amplifier FET Q2003

(2SK302GR).

The 2nd IF signal that has passed through the MCF enters the

noise blanker gate, D2014 (1SS226). It is then routed through

either a crystal filter (XF2002, XF2003, U2002, U2005) or an

attenuator (R2174, R2175, R2183), according to the receiving

mode (CW, SSB, or AM), and then it passes onward to the 3rd

mixer circuit.

Noise Blanker Circuit

A sample of the 2nd IF circuit is amplified by FETs Q2009 and

Q2010 (both 3SK131) on the IF Unit, and then undergoes detec-

tion by D2006 (1SS226). This output passes through R2017 and

R2027, C2006, and Q2001 (2SC2812) to yield an average AGC

voltage for controlling the degree of amplification of the above

FETs. Noise pulses contained in the output from D2026 are detected by D2009 (1SS270) and Q2012 (2SC2812) and are used

to control the NB Gate.

3rd Mixer Circuit/3rd IF Circuit (IF Notch Circuit)

The 3rd mixer uses double-balanced mixer (DBM) IC Q2021

(µPC1037H) on the IF Unit. The 3rd local signal (8.67 MHz)

from the LOCAL Unit is applied to the DBM IC local port after it

is buffer-amplified by Q2028 (2SC2812). The signal output from

the 3rd mixer passes through a ceramic filter, crystal filter, or mechanical filter (U2001, U2003, U2004, U2006, CF2002), to become the 455-kHz 3rd IF signal.

The 3rd IF signal, buffer-amplified by Q2022 (2SC2812),

passes through a notch frequency control circuit which consists of

L2004, C2063, C2064, and D2020 (HVU306A). Attenuation in

the IF notch circuit is controlled by VR2005. The 3rd IF is then

buffer-amplified by Q2023 (2SC2812) and further amplified in

two stages by FETs Q2026 and Q2029 (both 3SK131).

The IF signal is then buffer-amplified by Q2004 and Q2017

(both 2SC2812), respectively. The output of Q2004 is applied to

the AF Unit through connector J2002, and the output from Q2017

is sent to the AGC circuit.

The resulting output signal (the difference between the local

signal and receive signal) passes through dual monolithic crystal

filters (MCF) XF1001/1002 (70R12BUF, BW: ±6 kHz) to obtain

AGC Circuit

The AGC circuit consists of D2012 and D2013 (both 1SS198),

transistor Q2018 (2SC2812), etc. on the IF Unit. Output from the

4-1

Circuit Description

AGC circuit is fed back to the RF AGC circuit that consists of

FETs and PIN diodes of the IF amplifier stages, by which the output is controlled.

FM IF Circuit/FM Demodulator Circuit

The 2nd IF signal that has passed through buffer-amplifier FET

Q2003 on the IF Unit, and the 3rd local signal (8.67 MHz) that has

been buffer-amplified by Q2028, are fed to IC Q2015

(MC3372ML) for FM demodulation.

The FM demodulator IC contains a mixer, limiter amplifier,

filter amplifier, squelch trigger, and demodulator. The IF input signal is mixed with the 3rd local signal, band-limited by ceramic

filter CF2001 (CFWS455G, BW: ±4 kHz), amplified by the limiter amplifier, and demodulated into an audio signal by the demodulator. It then passes through a filter (R2028, C2021) and connector J2004 en route to the AF Unit. The signal then enters analog switch IC Q3001-3 (BU4066BF) through a de-emphasis circuit which consists of R3060 and C3052.

The squelch circuit selectively amplifies the noise component

of the demodulator output by the filter amplifier inside the FM IC

and the active band-pass filter consisting of an externally attached

resistor and capacitor. This circuit uses a signal detected by D2001

(1SS270).

SSB/CW Demodulator Circuit

The 3rd IF signal from the IF Unit is applied to the SSB de-

modulator of Q3007 (µPC1037H) on the AF Unit, which produces audio by applying the carrier signal from the DDS-CAR

Unit to Q3007 after buffering by Q3020 (2SC2812). Similarly,

the CW signal is demodulated by a carrier signal which is offset by

the “Pitch” frequency.

The demodulated SSB and CW signals are each stripped of

high-frequency components by an active low-pass filter consisting

of op-amp IC Q3008-2 and IC Q3008-1 (M5218AFP). Then, they

enter analog switch IC Q3001-2 and IC Q3001-4 (BU4066BF).

AM Demodulator Circuit

The 3rd IF signal from the IF Unit is applied to I-DET Unit

U3003 on the AF Unit, from which it enters IC Q3703

(MC13020M) for AM demodulation.

The IC for AM demodulation consists mainly of an envelope

detector, VCO, phase shifter, synchronous detector, and DC/AC

detector. From the IF signal that is fed to the IC, the envelope

detector output and synchronous detector output are picked up.

The output from the demodulator circuit passes through ana-

log switches Q3701-1 and Q3701-2 for switching between the syn-

chronous detector output and envelope detector output. It then

enters analog switch IC Q3001-1 (BU4066BF) after removal of

the high-frequency components by an active low-pass filter which

consists of op-amp IC Q3013-1 (M5218AFP) on the AF Unit.

Low-Frequency Amplifier Circuit

The demodulated signal that is selected by one of analog

switches IC Q3001-1 to IC Q3001-4 on the AF Unit (according to

the receiving mode) passes through the squelch switch, audio muting FET Q3002 (2SK160), low-frequency amplifier transistor

Q3006 (2SC2812), electronic volume IC Q3005 (M51131L), op-

amp IC Q3014-1 (M5218AFP) for buffer-amplification, and IC

Q3022 (TDA2003V) for low-frequency power to drive the inter-

nal or external speaker with a maximum output of approximately

1.5 W. The signal that passes through electronic volume IC Q3005

is also sent to the headphone terminals after it is amplified by headphone amplifier IC Q3015-1 (M5218AFP).

Transmit Signal Circuitry

Microphone Amplifier Circuit

The audio signal from microphone jack J9421 on the MIC Unit

is passed through connector JP9421 and the DISPLAY Unit’s connectors (J5528 and J5529), is amplified by transistor Q3048

(2SC2812) on the AF Unit, and then is applied to electronic volume IC Q3044 (M51131L), which is controlled by the MIC knob

on the panel.

The output (audio signal) from the electronic volume control

is amplified by Q3045 (2SC2812) and fed to balanced modulator

IC Q3046 (µPC1037H) through the buffer-amplifier transistor

Q3043 (2SC2812).

During FM transmission, the audio signal is routed to connector J2011 inside the IF Unit after its volume is adjusted by VR6814

on the ALC Unit. The audio signal that has passed through the preemphasis circuit consisting of C2201 and R2228 on the IF Unit is

mixed with a tone signal from the CNTL Unit, and is amplified

and limited by op-amp IC Q2049-2 (M5223AFP) of the IDC circuit. The audio then passes through the splatter filter (secondary

active low-pass filter) formed by op-amp IC Q2049-1, R2229, and

R2230, plus C2119 and C2206, and is then fed to the frequencymodulator circuit inside the IF Unit through VR2008 and VR2009

for setting of the frequency deviation.

SSB Modulator Circuit

The carrier signal appropriate to the transmitting mode (LSB

or USB) is applied from the CAR-DDS Unit to balanced modulator IC Q3046 on the AF Unit, and is modulated by microphone

audio.

The balanced modulator produces the upper and lower side

bands and carrier signal. The carrier and audio signal are suppressed

and the carrier balance is adjusted by VR3012. As a result, the

output signal obtained is a DSB signal with a carrier suppression

ratio of 35 dB or more.

The DSB modulated signal (1st IF signal: 455 kHz) then passes

through mechanical filter XF9801 inside the SSB-FIL Unit on the

IF Unit, stripping residual carrier and the undesired sideband; the

signal then passes as an SSB signal through buffer-amplifier Q3049

(2SC2812), connector J3026, and the IF Unit’s connector J2009.

4-2

Circuit Description

AM Modulator Circuit

As in the SSB modulator circuit, a carrier signal appropriate to

the transmitting mode (AM) from the CAR-DDS Unit and an audio signal from the microphone are applied to balanced modulator

IC Q3046 on the AF Unit.

The control signal from CPU IC Q5008 (M37702M) in the

CNTL Unit causes a voltage of AM 9 V to be sent from transistor

array IC Q5025 (TD62793F). This voltage is applied via VR3011

and D3018 (DAN202K) to IC Q3046, causing the balanced modulator to lose balance. The restored carrier signal and modulated

signal are then fed to the Tx mixer via ceramic filter CF2002

(CFWS455HT) inside the IF Unit.

Frequency Modulation Circuit

The FM circuit uses a voltage controlled crystal oscillator

(VCXO) consisting mainly of IF Unit oscillator Q2044

(2SC2812), X2001, varactor D2049 (HVU306A), and L2026.

The VCXO has a center frequency of 8.215 MHz.

The FM signal is produced by applying a signal from the FM

microphone amplifier circuit to varactor D2049 and varying the

crystal oscillator load capacity in proportion to the signal voltage.

The FM signal is fed to gate 1 of 2nd IF circuit FET Q2036

(3SK131) via Q2043 (2SC2812) for buffer amplification.

CW (A1) Signal Generator Circuit

When the transmitting mode is CW (A1), the control signal

from CPU IC Q5008 in the CNTL Unit causes a CW 9 V voltage

to be sent from transistor array IC Q5025. While microphone audio is cut off by Q3050 (2SC4047), the voltage is applied to balanced modulator IC Q3046 via D3018, providing a carrier from

the balanced modulator for input to the transmit signal circuit of

the IF Unit.

1st IF Circuit/1st Mixer Circuit

The 455 kHz 1st IF signal from the modulator circuit is bandlimited by the IF Unit’s ceramic or mechanical filter CF2002,

U2001 (XF9801) according to the selected mode (CW, SSB, or

AM). It is then buffer-amplified by FET Q2037 (2SK160) and

fed to 1st mixer IC Q2030 (µPC1037H).

The IF Unit’s double balanced mixer IC Q2030 (DBM) is used

as the 1st mixer. A local signal (8.67 MHz) from the LOCAL Unit

which is buffer-amplified by transistor Q2028 (3SK131) and fed

to the local port of DBM IC is mixed with the 455 kHz 1st IF

signal to produce an 8.215 MHz 2nd IF signal.

2nd IF Circuit/2nd Mixer Circuit

The 2nd IF signal passes through either the IF Unit’s crystal

filter XF2002 or attenuator (R2174, R2175, R2183), whichever is

appropriate to the selected mode (CW, SSB, or AM). It is then

amplified by FET Q2036 (3SK131) and fed to the 2nd mixer circuit.

gate. The signal that is produced by the 2nd mixer is removed of

unwanted signal components as it passes through a filter, formed by

T2014/T2017 and C2227, to obtain a 70.455 MHz 3rd IF signal.

3rd IF Circuit/3rd Mixer Circuit

The 3rd IF signal passes through T1001, is amplified by FET

Q1001 (SST310), then is fed to the 3rd mixer circuit D1001

(HSB88WSTR) via T1002. There it mixes with a local signal

(72.255 ~100.455 MHz) generated by the LOCAL Unit to produce a transmit signal (1.8 MHz to 30 MHz) at the desired operating frequency.

High-Frequency Transmit Preamplifier Circuit

The transmit signal is passed through a low-pass filter which

consists of L1002/L1003 and C1008-C1012, is amplified by Q1002

(2SC3356), and is passed onward to the PA Unit via buffer amplifiers Q1022 (2SC3356) and Q1023 (2SC2954), exiting via

connector J1005.

Power Amplifier Circuit

The transmit signal from the RF Unit arrives at connector J6101

of the PA Unit.

The transmit signal (1.8 MHz to 30 MHz) delivered to the PA

Unit is amplified by pre-driver Q6101 (2SC2166), driver Q6102/

Q6103 (2SC3133) and final amplifiers Q6104/Q6105

(2SC2879), and exits from connector J6102 then route to the LPF1 Unit.

Low-Pass Filter (LPF) Circuit

The transmit signal from the power amplifier circuit is sent to

connector J6001 of the LPF-1 Unit and passed through a low-pass

filter consisting mainly of RL6001-RL6014, L6001-L6014, and

various capacitors. The LPF is a 5th-order Chebyshev type filter,

utilizing seven different sections for the various amateur bands at

1.8 ~ 30 MHz.

The low-pass filtered transmit signal is fed to the ANT Unit

through directional coupler L6015 and connector J6005.

The directional coupler, which consists mainly of L6015,

TC6001, and C6061, samples a part of the transmission power to

detect forward power and reflected power. A DC voltage corresponding to the relative forward/reflected power is produced by

D6001-D6004 (all HRF32), and is used for automatic level con-

trol (ALC).

ALC Circuit

The output from the directional coupler is routed from connector J6003 through connectors J6810/J6814 in the ALC Unit and

applied to the ALC circuit via connector J3018 in the AF Unit.

The ALC circuit consists of an op-amplifier circuit for amplifying the forward and reflected voltage, a time-constant ALC amplifier, and a transmit signal control circuit on the IF Unit.

The 2nd mixer consists of the IF Unit’s FETs Q2033 and Q2038

(both 2SK302GR). A 2nd local signal (62.24 MHz) from the LOCAL Unit is amplified by Q2027 (2SC2812) and fed to each FET’s

The forward voltage from connector J3018 in the AF Unit is

added with a DC control voltage which passes through the output

4-3

Circuit Description

power control, VR3003 (for setting transmission output, etc., on

the panel), and is then applied to op-amp IC Q3026-1

(M5218AFP).

The reflected voltage is added with a DC control voltage which

passes through VR3008, and is then applied to op-amp IC Q3026-

2. During high SWR conditions (SWR 3:1 or more), transmitter

output is reduced and a “High SWR” warning appears, thus protecting the PA Unit for potential damage.

The op-amp output passes through D3009 (1SS184) where

the forward and reflected output from the op-amp are mixed and

fed to the ALC amplifier, which contains a time-constant circuit.

The ALC amplifier amplifies the forward and reflected-wave

output via transistor Q3025 (2SC2812). This output then passes

through a fast-attack, slow-delay RC time-constant circuit consisting of R3083/R3087 and C3069/C3157 for input to the Tx signal

control circuit via connector J3015 and J2004 on the IF Unit.

The TX control circuit adjusts the IF amplifier gain via gate 2

of FET Q2036 of the 8.215 MHz IF amplifier circuit to prevent

the Tx output from exceeding the preset level.

Keying Circuit

When the onboard electronic keyer is used in the CW mode,

the bias of Q1001, 2nd mixer FETs Q2033/Q2038, and 3rd mixer

D1001 is controlled via NAND gate IC Q1006 (µPD4011BG) to

generate CW.

To limit key clicks, the waveform is optimized by time-con-

stant circuits, such as D1002 (BAS316), R1016, and C1018 of

the bias control circuit.

The DDS outputs contain digital amplitude data correspond-

ing to serial frequency data from CPU IC Q5008 of the CNTL

Unit. The digital amplitude data is D/A-converted by ladder resistors RB3601/RB4501/RB4601 and passes through buffer amplifier Q3602, Q4501, Q4602 (all 2SC2812) and a Chebychev LPF

to generate a sine wave. The DDS frequency range is 453.5 ~ 466.74

kHz (cf = 455.0 kHz) for the CAR-DDS, 373.08 ~ 291.16 kHz for

the DDS-PLL, and 907.88 kHz ±620 Hz for the DDS-SUB.

3rd Local Oscillator Circuit

The 3rd L.O. circuit generates a 1.81576 MHz signal by dou-

bling the 907.88 kHz output from the SUB-DDS Unit on the LOCAL Unit using a circuit composed of Q4036 (2SC2812), T4010,

capacitors C4163, C4164, C4170, and coil L4038. The doubled

signal is sent to mixer Q4027 (µPC1037).

At the mixer, the 1.81576 MHz input signal is mixed with the

10.48576 MHz reference oscillation signal. The mixer output is

stripped of unwanted frequency components by T4009 and monolithic filter XF4001 to generate the 8.67 MHz 3rd L.O. signal.

This signal is amplified by Q4029 (2SC2812) and T4008 and

passes through buffer amplifier Q4017 (2SC2812) and a LPF composed of capacitors C4098, C4099, C4172, and coil L4022 for

input to the IF Unit via connector J4003.

2nd Local Oscillator Circuit

The 2nd L.O. circuit is a Hartley-type overtone oscillator cir-

cuit (frequency: 62.24 MHz) composed of FET Q4003

(2SK210GR), T4001, and X4001 on the LOCAL Unit. The signal then passes through amplifier Q4012 (2SC2714Y), T4006,

T4007, and C4043, for input to the IF Unit via connector J4002.

PLL Frequency Synthesizer (Main)

The PLL Frequency Synthesizer consists mainly of a master

reference oscillator circuit, 2nd local oscillator circuit, 3rd local

oscillator circuit, DDS-PLL/DDS-SUB/DDS-CAR units which

digitally synthesize carrier outputs, and a PLL circuit which contains a voltage controlled oscillator (VCO).

Master Reference Oscillator Circuit

The master reference oscillator uses a TCXO (oscillation frequency: 10.48576 MHz) on the REF Unit.

The reference oscillator signal passes through a low-pass filter

composed of C4715/C4716, and L4702. It is then fedto the LOCAL Unit via J4703, and also to the RX2, AF, and DSP-D Unit as

the reference oscillation signal.

DDS-CAR Unit/DDS-PLL Unit/DDS-SUB Unit

DDS ICs Q3601 (TC23SC030AF), Q4502 (FQ7928), and

Q4603 (TC23SC030AF) of the DDS (Direct Digital Synthesizer)

Units each contain a shift register, selector, phase accumulator,

and ROM.

The reference oscillation frequency (10.48576 MHz) that is delivered to each of the DDS Units is applied to each DDS IC after

amplification by transistors Q3603/Q4503/Q4601 (all 2SC2812).

4-4

1st Local Oscillator Circuit

VCO output is buffer-amplified by Q4004 and Q4005 (both

2SC2714Y) and passes through a LPF composed of coils L4003/

L4004 and capacitors C4028, C4029, and C4033-C4035. It is then

fed to the Tx/Rx frequency mixer circuitry of the RF Unit via connector J4001.

PLL Circuit

The PLL circuit is a frequency mixing type composed of a VCO,

mixer, PLL IC, and loop filter.

The VCO consists of four circuits (VCO1, VCO2, VCO3, and

VCO4), with a frequency range of 70.555 ~ 100.455 MHz divided

into four bands, allocated to the four VCO circuits. The range of

VCO1 is further divided by a circuit which shifts the oscillation

frequency. VCO1-VCO4 consist mainly of FETs Q4009, Q4016,

Q4023, and Q4032 (all 2SK210BL), diodes D4001, D4002,

D4004, D4005, D4007, D4008, D4010, and D4011 (all

HVU306A), trimmer capacitors TC4001-TC4004, and coils

L4013, L4020, L4029, and L4035.

The VCO switching signal from connector J4004 is used to

drive switching transistors Q4013, Q4021, Q4026, and Q4037

(all 2SC4047) to switch the source terminal of the oscillator FET.

Circuit Description

VCO1 uses the VCO0 control signal to drive switching tran-

sistors Q4039 (2SA1563) and Q4040 (2SC4047), applying a forward bias to D4013 (1SV271), and switching C4173 into the oscillator circuit, producing a frequency shift.

The 70.555 ~ 100.455 MHz VCO signal is fed to mixer Q4001

(µPC1037) via buffer amplifier FET Q4007 (2SK210GR) and

buffer amplifier Q4006 (2SC2714Y).

The 3rd local signal (8.67 MHz) is buffer-amplified by Q4022