White Electronic Designs EDI8L32512C20AI, EDI8L32512C20AC, EDI8L32512C17AI, EDI8L32512C17AC, EDI8L32512C15AI Datasheet

...

EDI8L32512C

512K x 32 CMOS High Speed Static RAM

FEATURES

n DSP Memory Solution

n Random Access Memory Array

n Surface Mount Package

n Single +5V (±5%) Supply Operation

* Advance Information.

NOT RECOMMENDED FOR NEW DESIGN

DESCRIPTION

The EDI8L32512C is a high speed, 5V, 16 megabit

Motorola DSP96002

Analog SHARC DSP

Texas Instruments TMS320C3x, TMS320C4x

Fast Access Times: 12*, 15, 17, and 20ns

TTL Compatible Inputs and Outputs

Fully Static, No Clocks

68 Lead PLCC, No. 99 JEDEC M0-47AE

Small Footprint, 0.990 Sq. In.

Multiple Ground Pins for Maximum

Noise Immunity

SRAM. The device is available with access times of

12, 15, 17 and 20ns allowing the creation of a no wait

state DSP memory solution. The high speed, 5V

supply voltage and control lines make the device ideal

for creating floating point DSP memory solutions.

The device can be configured as a 512K x 32 and used

to create a single chip external data memory solution for

TI's TMS320C30/C31 (Figure 8), TMS320C32 (Figure 9)

or TMS320C4x (Figure 10), Motorola's DSP96002 and

Analog's SHARC DSP (Figure 11). Alternatively, the

device's chip enables can be used to configure it as a 1M

x 16. A 1M x 48 program memory array for Analog's

SHARC DSP is created using three devices (Figure 12).

If this memory is too deep, two 512K x 24s (EDI8L24512C)

can be used to create a 512K x 48 array or two 128K x 24s

(EDI8L24128C) can be used to create a 128K x 48 array.

The device provides a 56% space savings when

compared to four 512K x 8, 36 pin SOJs. In addition

the EDI8L32512C has only a 10pF load on the data

lines vs. 32pF for four plastic SOJs.

The device provides a memory upgrade of the

EDI8L32256C (256K x 32) or the EDI8L32128C (128K x

32). For additional upgrade information see Figure 13.

Note: Solder Reflow Temperature should not exceed 230°C for 10 seconds.

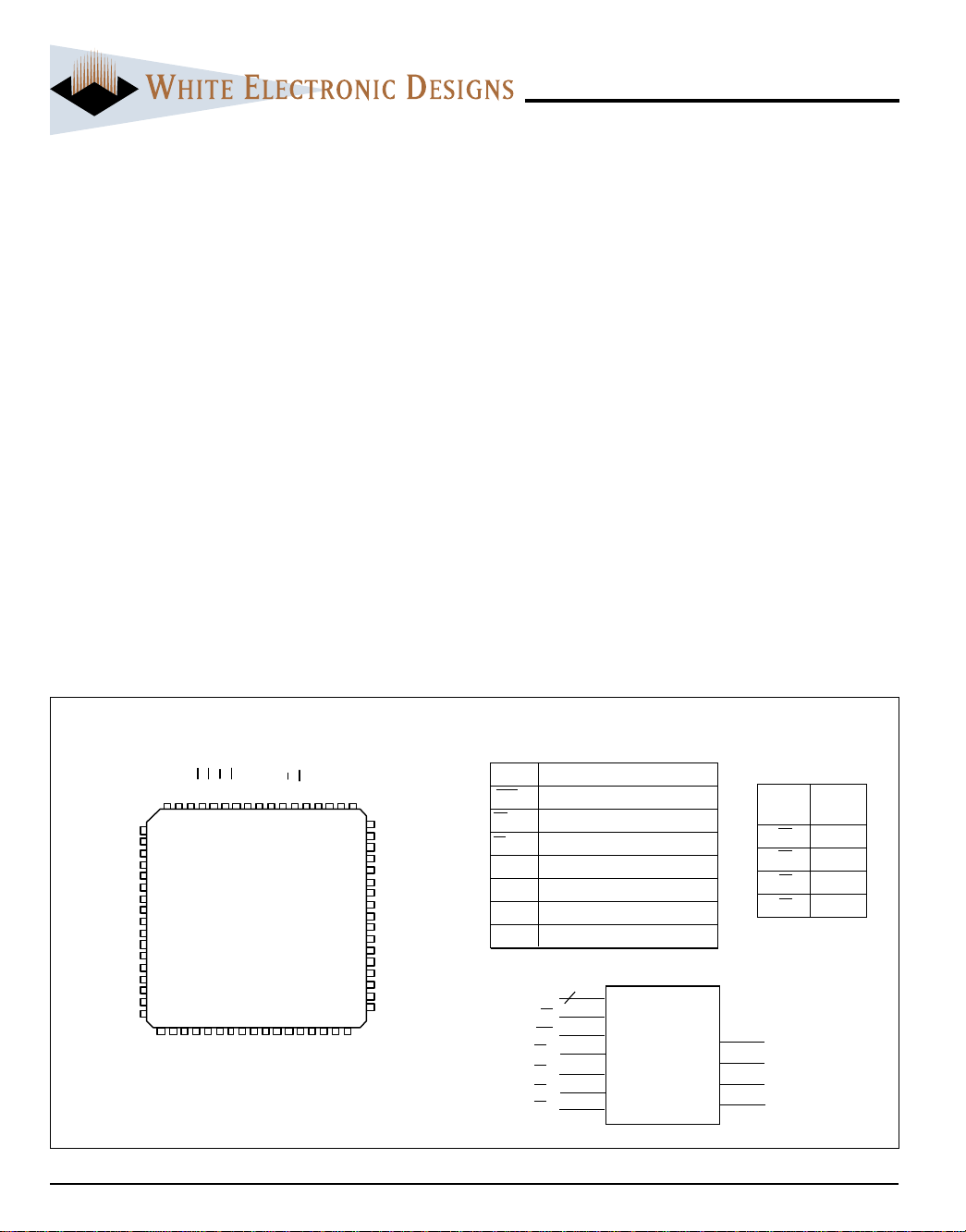

FIG. 1

PIN CONFIGURATIONS AND BLOCK DIAGRAM

CC

68 NC

67 NC

66 G

65 W

64 A16

63 A15

62 A14

A9A8A7

A10

61 DQ15

DQ0

DQ17

DQ18

DQ19

V

DQ20

DQ21

DQ22

DQ23

V

DQ24

DQ25

DQ26

DQ27

V

DQ28

DQ29

DQ30

9 DQ16

8 A18

7 A17

6E3

5E2

4E1

3E0

2NC

1V

10

11

12

13

SS

14

15

16

17

18

CC

19

20

21

22

23

SS

24

25

26

2728293031323334353637383940414243

A6A5A4A3A2

DQ31

A1

A0

CC

A11

A13

A12

V

60

DQ14

59

DQ13

58

DQ12

SS

57

V

DQ11

56

DQ10

55

DQ9

54

DQ8

53

CC

V

52

DQ7

51

DQ6

50

DQ5

49

DQ4

48

V

SS

47

DQ3

46

DQ2

45

DQ1

44

Note: For memory upgrade information, refer to Page 8, Figure 13

"EDI MCM-L Upgrade Path."

August 2000 Rev. 7

ECO #13097

PIN NAMES

A0-18 Address Inputs

E0-3 Chip Enables (One per Byte)

W Master Write Enable

G Master Output Enable

DQ0-31 Common Data Input/Output

VCC Power (+5V ±5%)

VSS Ground

BYTE CONTROL

TABLE

Chip Byte

Enable Control

E0 DQ0-7

E1 DQ8-15

E2 DQ16-23

E3 DQ24-31

NC No Connection

A0-

18

19

G

W

0

E

E

1

E

2

E

3

1

White Electronic Designs Corporation (508) 366-5151 www.whiteedc.com

512K x 32

Memory

Array

DQ

DQ

DQ

DQ

0-7

8-15

16-23

24-31

EDI8L32512C

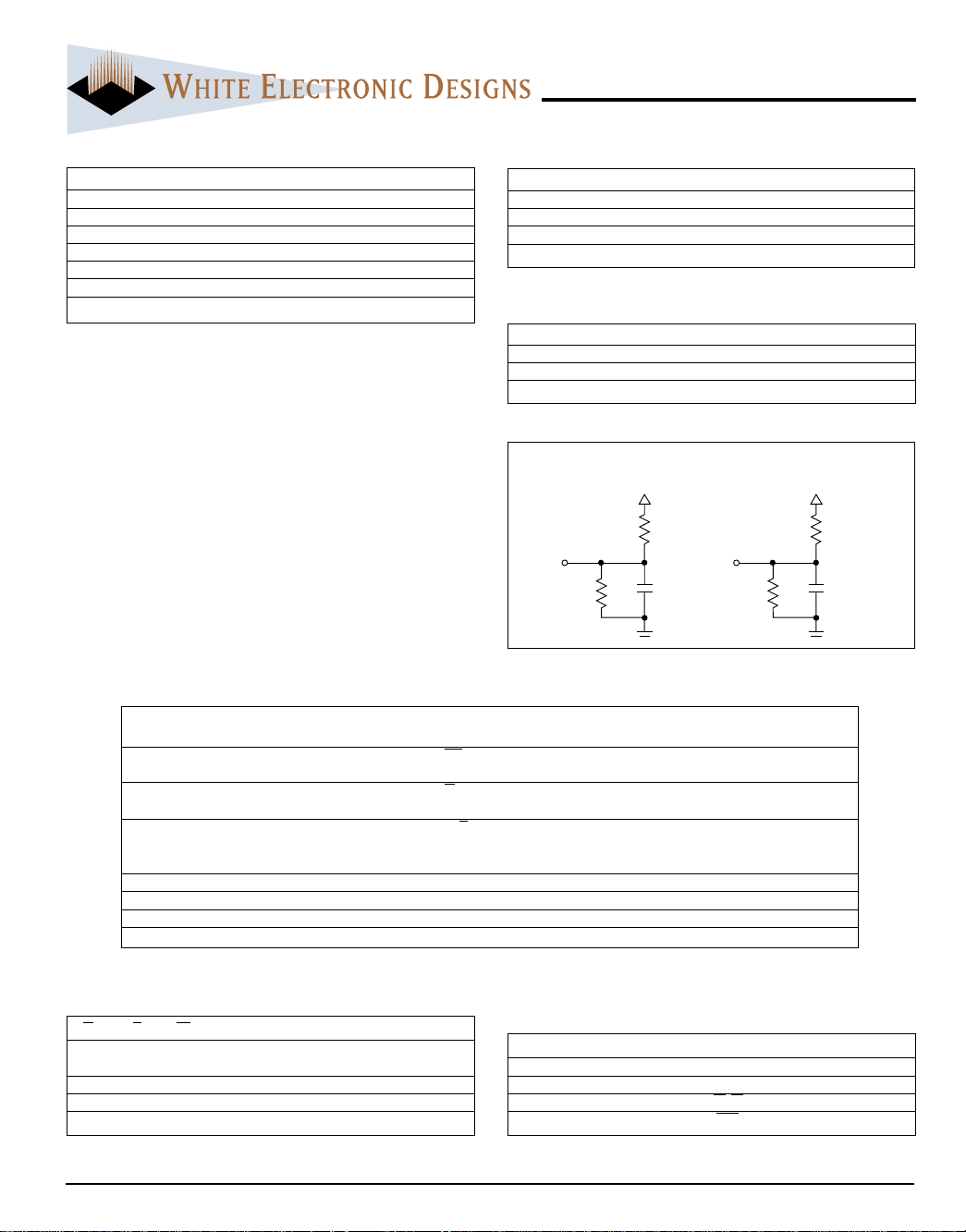

ABSOLUTE MAXIMUM RATINGS* RECOMMENDED DC OPERATING CONDITIONS

Voltage on any pin relative to VSS -0.5V to 7.0V

Operating Temperature TA (Ambient)

Commercial 0°C to + 70°C

Industrial -40°C to +85°C

Storage Temperature -55°C to +125°C

Power Dissipation 5.0 Watts

Output Current. 20 mA

Junction Temperature, TJ 175°C

*Stress greater than those listed under "Absolute Maximum Ratings"

may cause permanent damage to the device. This is a stress rating

only and functional operation of the device at these or any other

conditions greater than those indicated in the operational sections of

this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

DC ELECTRICAL CHARACTERISTICS

Parameter Sym Min Typ Max Units

Supply Voltage VCC 4.75 5.0 5.25 V

Supply Voltage VSS 00 0V

Input High Voltage VIH 2.2 -- VCC+0.5 V

Input Low Voltage VIL -0.3 -- 0.8 V

AC TEST CONDITIONS

Input Pulse Levels VSS to 3.0V

Input Rise and Fall Times 5ns

Input and Output Timing Levels 1.5V

Output Load Figure 2

(Note: For TEHQZ,TGHQZ and TWLQZ, CL = 5pF)

FIG. 2 FIG. 3

Vcc

480Ω

Q

255Ω

30pF

Q

255Ω

Vcc

480Ω

5pF

Parameter Sym Conditions Min Max Units

Operating Power Supply Current ICC1 W = VIL, II/O = 0mA, 800 720 mA

Standby (TTL) Supply Current ICC2 E ³ VIH, VIN £ VIL or 200 200 mA

Full Standby CMOS ICC3 E ³ VCC - 0.2V 40 40 mA

Supply Current VIN ³ VCC - 0.2V or

Input Leakage Current ILI VIN = 0V to VCC ±10 µA

Output Leakage Current ILO V I/O = 0V to VCC ±10 µA

Output High Volltage VOH IOH = -4.0mA 2.4 V

Output Low Voltage VOL IOL = 8 .0m A 0 .4 V

TRUTH TABLE CAPACITANCE

G E W Mode Output Power

X H X Standby High Z ICC2

ICC3

H L H Output Deselect High Z ICC1

L L H Read DOUT ICC1

X L L Write DIN ICC1

White Electronic Designs Corporation (508) 366-5151 www.whiteedc.com

12/15 17/20 m A

Min Cycle

VIN ³ VIH, f = ØMHz

VIN £ 0.2V

(f=1.0MHz, VIN=VCC OR VSS)

Parameter Sym Max Unit

Address Lines CI 30 pF

Data Lines CD/Q 10 pF

Write & Output Enable Lines W, G 30 pF

Chip Enable Lines E0-3 8pF

2

AC CHARACTERISTICS READ CYCLE

EDI8L32512C

Parameter JEDEC Alt. Min Max Min Max Min Max Min Max Units

Read Cycle Time TAVAV TRC 12 15 17 20 ns

Address Access Time TAVQV TAA 12 15 17 20 ns

Chip Enable Access Time TELQV TACS 12 15 17 20 ns

Chip Enable to Output in Low Z (1) TELQX TCLZ 3 3 3 3 ns

Chip Disable to Output in High Z (1) TEHQZ TCHZ 6 7 9 9 ns

Output Hold from Address Change TAVQX TOH 3 3 3 3 ns

Output Enable to Output Valid TGLQV TOE 6 7 9 9 ns

Output Enable to Output in Low Z (1) TGLQX TOLZ 0 0 0 0 ns

Output Disable to Output in High Z(1) TGHQZ TOHZ 6 7 9 9 ns

*Advanced Information

Note 1: Parameter guaranteed, but not tested.

FIG. 4

READ CYCLE 1 - W HIGH, G, E LOW

Symbol 12ns* 15ns 17ns 20ns

TAVAV

A

ADDRESS 1

ADDRESS 2

TAVQXTAVQV

Q

DATA 1

DATA 2

FIG. 5 READ CYCLE 2 - W HIGH

A

E

G

Q

TAVQV

TELQV

TELQX

TGLQV

TGLQX

TAVAV

TEHQZ

TGHQZ

3

White Electronic Designs Corporation (508) 366-5151 www.whiteedc.com

Loading...

Loading...