TEXAS INSTRUMENTS TLC320AD50C, TLC320AD50I Technical data

TLC320AD50C/I

TLC320AD52C

SigmaĆDelta Analog Interface Circuits With

MasterĆSlave Function

Data Manual

2000 Mixed Signal Products

SLAS131E

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty . Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 2000, Texas Instruments Incorporated

Contents

Section Title Page

1 Introduction 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 Features 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Functional Block Diagram 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Terminal Assignments 1–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Ordering Information 1–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 Terminal Functions 1–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.6 Definitions and Terminology 1–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.7 Register Functional Summary 1–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 Detailed Description 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1 Device Functions 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.1 Operating Frequencies and Filter Control 2–1. . . . . . . . . . . . . .

2.1.2 ADC Signal Channel 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.3 DAC Signal Channel 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.4 Serial Interface 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.5 Register Programming 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.6 Sigma-Delta ADC 2–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.7 Decimation Filter 2–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.8 Sigma-Delta DAC 2–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.9 Interpolation Filter 2–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.10 Analog and Digital Loopback 2–5. . . . . . . . . . . . . . . . . . . . . . . . .

2.1.11 FIR Overflow Flag 2–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Reset and Power-Down Functions 2–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.1 Software and Hardware Reset 2–6. . . . . . . . . . . . . . . . . . . . . . . .

2.2.2 Software and Hardware Power Down 2–6. . . . . . . . . . . . . . . . . .

2.3 Master Clock Circuit 2–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Data Out (DOUT) 2–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4.1 Data Out, Master Mode 2–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4.2 Data Out, Slave Mode 2–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 Data In (DIN) 2–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 FC (Hardware Secondary Communication Request) 2–7. . . . . . . . . . . . .

2.7 Frame-Sync Function for TLC320AD50C 2–7. . . . . . . . . . . . . . . . . . . . . . .

2.7.1 Frame Sync (FS

2.7.2 Frame Sync (FS

2.7.3 Frame-Sync Delayed (FSD

2.7.4 Frame-Sync Delayed (FSD

2.8 Frame-Sync Function for TLC320AD52C 2–11. . . . . . . . . . . . . . . . . . . . . . .

2.9 Multiplexed Analog Input and Output 2–11. . . . . . . . . . . . . . . . . . . . . . . . . . .

) Function, Master Mode 2–8. . . . . . . . . . . . . .

) Function,Slave Mode 2–8. . . . . . . . . . . . . . . .

) Function, Master Mode 2–9. . . . .

), Slave Mode 2–9. . . . . . . . . . . . . .

iii

2.9.1 Analog Output 2–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 Serial Communications 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 Primary Serial Communication 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Secondary Serial Communication 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.1 Hardware Secondary Serial Communication Request 3–3. . . .

3.2.2 Software Secondary Serial Communication Request 3–3. . . .

3.3 Conversion Rate Versus Serial Port 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 Phone Mode Control 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5 DIN and DOUT Data Format 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.1 Primary Serial Communication DIN and DOUT

Data Format 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.2 Secondary Serial Communication DIN and DOUT

Data Format 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 Specifications 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1 Absolute Maximum Ratings Over Operating Free-Air

Temperature Range 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 Recommended Operating Conditions 4–1. . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.1 Recommended Operating Conditions, DV

4.2.2 Recommended Operating Conditions, DV

= 5 V 4–1. . . . . .

DD

= 3 V 4–1. . . . . .

DD

4.3 Electrical Characteristics Over Recommended Operating

Free-Air Temperature Range, DV

= 5 V, RL = 600 Ω 4–2. . . . . . . . . . .

DD

4.3.1 Digital Inputs and Outputs, MCLK = 8.192 MHz,

f

= 8 kHz, DVDD = 5 V 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

s

4.3.2 Digital Inputs and Outputs, MCLK = 8.192 MHz,

= 8 kHz, DVDD = 3 V 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

f

s

4.3.3 ADC Channel, MCLK = 8.192 MHz, f

= 8 kHz 4–2. . . . . . . . . .

s

4.3.4 ADC Dynamic Performance, MCLK = 8.192 MHz,

f

= 8 kHz 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

s

4.3.5 ADC Channel Characteristics 4–3. . . . . . . . . . . . . . . . . . . . . . . .

4.3.6 DAC Path Filter, MCLK = 8.192 MHz, f

= 8 kHz 4–3. . . . . . . .

s

4.3.7 DAC Dynamic Performance 4–4. . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.8 DAC Channel Characteristics 4–5. . . . . . . . . . . . . . . . . . . . . . . .

4.3.9 Power Supply, AV

4.3.10 Power-Supply Rejection, AV

= DVDD = 5 V, No Load 4–5. . . . . . . . . . .

DD

= DVDD = 5 V 4–5. . . . . . . . . .

DD

4.4 Timing Characteristics 4–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.1 Master Mode Timing Requirements 4–5. . . . . . . . . . . . . . . . . . .

4.4.2 Slave Mode Timing Requirements 4–6. . . . . . . . . . . . . . . . . . . .

4.4.3 Master Mode Switching Characteristics 4–6. . . . . . . . . . . . . . . .

4.4.4 Slave Mode Switching Characteristics 4–6. . . . . . . . . . . . . . . . .

4.4.5 Reset Timing 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.6 Other 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5 Parameter Measurement Information 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6 Register Set 6–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1 Control Register 1 6–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2 Control Register 2 6–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iv

6.3 Control Register 3 6–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4 Control Register 4 6–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7 Application Information 7–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Appendix A – Mechanical Data A–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

v

List of Illustrations

Figure Title Page

2–1 Timing Sequence of ADC Channel (Primary Communication Only) 2–2. . . . . .

2–2 Timing Sequence of ADC Channel (Primary and Secondary

Communication) 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–3 Timing Sequence of DAC Channel (Primary Communication Only) 2–3. . . . . .

2–4 Timing Sequence of DAC Channel (Primary and Secondary

Communication) 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–5 Register 1 Read Operation Timing Diagram 2–4. . . . . . . . . . . . . . . . . . . . . . . . . .

2–6 Register 1 Write Operation Timing Diagram 2–5. . . . . . . . . . . . . . . . . . . . . . . . . .

2–7 Internal Power-Down Logic 2–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–8 Master Device Frame-Sync Signal With Primary and Secondary

Communications (No Slaves) 2–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–9 Master Device Frame-Sync Signal With Primary and Secondary

Communications (With 1 Slave Device) 2–8. . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–10 Master Device FS

Control 3 Register) is 0 2–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–11 Master Device FS

Programmed (One Slave Device) 2–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–12 Master With Slaves (To DSP Interface) 2–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–13 Master-Slave Frame-Sync Timing After A Delay Has Been

Programmed Into The FSD Register (D0–D5 of Control 3 Register) 2–10. . .

2–14 Master Device FS

Is Programmed With 49H 2–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–15 RC Antialias Filter 2–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–16 INP and INM Internal Self-Biased (2.5 V) Circuit 2–12. . . . . . . . . . . . . . . . . . . . .

2–17 Differential Output Drive (Ground Referenced) 2–12. . . . . . . . . . . . . . . . . . . . . . .

2–18 Digital Input Code vs Analog Output Voltage 2–12. . . . . . . . . . . . . . . . . . . . . . . .

3–1 Primary Serial Communication Timing 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 Hardware and Software Methods to Make a Secondary Request 3–2. . . . . . . . .

3–3 FS

3–4 FS

3–5 FS

3–6 Phone Mode Timing When Phone Mode Is Enabled 3–4. . . . . . . . . . . . . . . . . . .

Output When Hardware Secondary Serial Communication Is Requested

Only Once (No Slave) 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output When Hardware Secondary Serial Communication Is Requested

Only Once (Three Slaves) 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output During Software Secondary Serial Communication Request

(No Slave) 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

and FSD Output When FSD Register (D0–D5,

and FSD Output After Control 3 Register Is

and FSD Output After Control 3 Register

vi

3–7 Primary Communication DIN and DOUT Data Format 3–4. . . . . . . . . . . . . . . . .

3–8 Secondary Communication DIN and DOUT Data Format 3–5. . . . . . . . . . . . . . .

5–1 Master FS

5–2 Slave FS

5–3 Master/Slave SCLK to FSD

5–4 Serial Communication Timing (Master Mode) 5–2. . . . . . . . . . . . . . . . . . . . . . . . .

5–5 Serial Communication Timing (Slave Mode) 5–2. . . . . . . . . . . . . . . . . . . . . . . . . .

5–6 ADC Channel Filter Response (MCLK = 8.192 MHz, f

5–7 ADC Channel Filter Passband Ripple (MCLK = 8.192 MHz, f

5–8 DAC Channel Filter Response (MCLK = 8.192 MHz, f

5–9 DAC Channel Filter Passband Ripple (MCLK = 8.192 MHz, f

7–1 Master Device and Slave Device Connections (to DSP Interface) 7–1. . . . . . .

7–2 Power Supply Decoupling 7–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

and FSD Timing 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

to FSD Timing 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timing 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

= 8 kHz) 5–3. . . . . . . .

s

= 8 kHz) 5–3. .

s

= 8 kHz) 5–4. . . . . . . .

s

= 8 kHz) 5–4. .

s

List of Tables

Table Title Page

3–1 Least Significant Bit Control Function 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–1 Register Map 6–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–2 Control Register 1 6–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–3 Control Register 2 6–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–4 Control Register 3 6–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–5 Control Register 4 6–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vii

viii

1 Introduction

The TLC320AD50C, TLC320AD50I, and TLC320AD52C provide high-resolution signal conversion from

digital-to-analog (D/A) and from analog-to-digital (A/D) using oversampling sigma- delta technology. This device

consists of a pair of 16-bit synchronous serial conversion paths (one for each direction) and includes an interpolation

filter before the DAC and a decimation filter after the ADC. Other overhead functions on the chip include timing

(sample rate, FSD

sigma-delta architecture produces high resolution A/D and D/A conversion at a low system cost.

Programmable functions of this device can be selected through the serial interface. Options include reset, power

down, communications protocol, signal sampling rate, gain control, and system test modes (see section 6). The

TLC320AD50C and TLC320AD52C are characterized for operation from 0°C to 70°C, and the TLC320AD50I is

characterized for operation from –40°C to 85°C.

1.1 Features

• General-purpose analog interface circuit for V.34+ modem and business audio applications

• 16-bit oversampling sigma-delta ADC and DAC

• Serial port interface

• Typical 89-dB SNR (signal-to-noise ratio) for ADC and DAC

• Typical 90-dB THD (signal to total harmonic distortion) for ADC and DAC

• Typical 88-dB dynamic range

• Test mode that includes a digital loopback test and analog loopback test

• Programmable A/D and D/A conversion rate

• Programmable input and output gain control

• Maximum conversion rate: 22.05 kHz

• Single 5-V power supply voltage or 5-V analog and 3-V digital power supply voltage

• Power dissipation (PD) of 120 mW rms typical in the operating mode

• Hardware power-down mode to 7.5 mW

• Internal reference voltage (V

• Differential architecture throughout device

• TLC320AD50C/I can support up to three slave devices; TLC320AD52C can support one slave

• 2s complement data format

• ALTDATA terminal provides data monitoring

• Monitor amplifier to monitor input signals

• On-chip phase locked loop (PLL)

delay) and control (programmable gain amplifier, PLL, communication protocol, etc.). The

)

ref

1–1

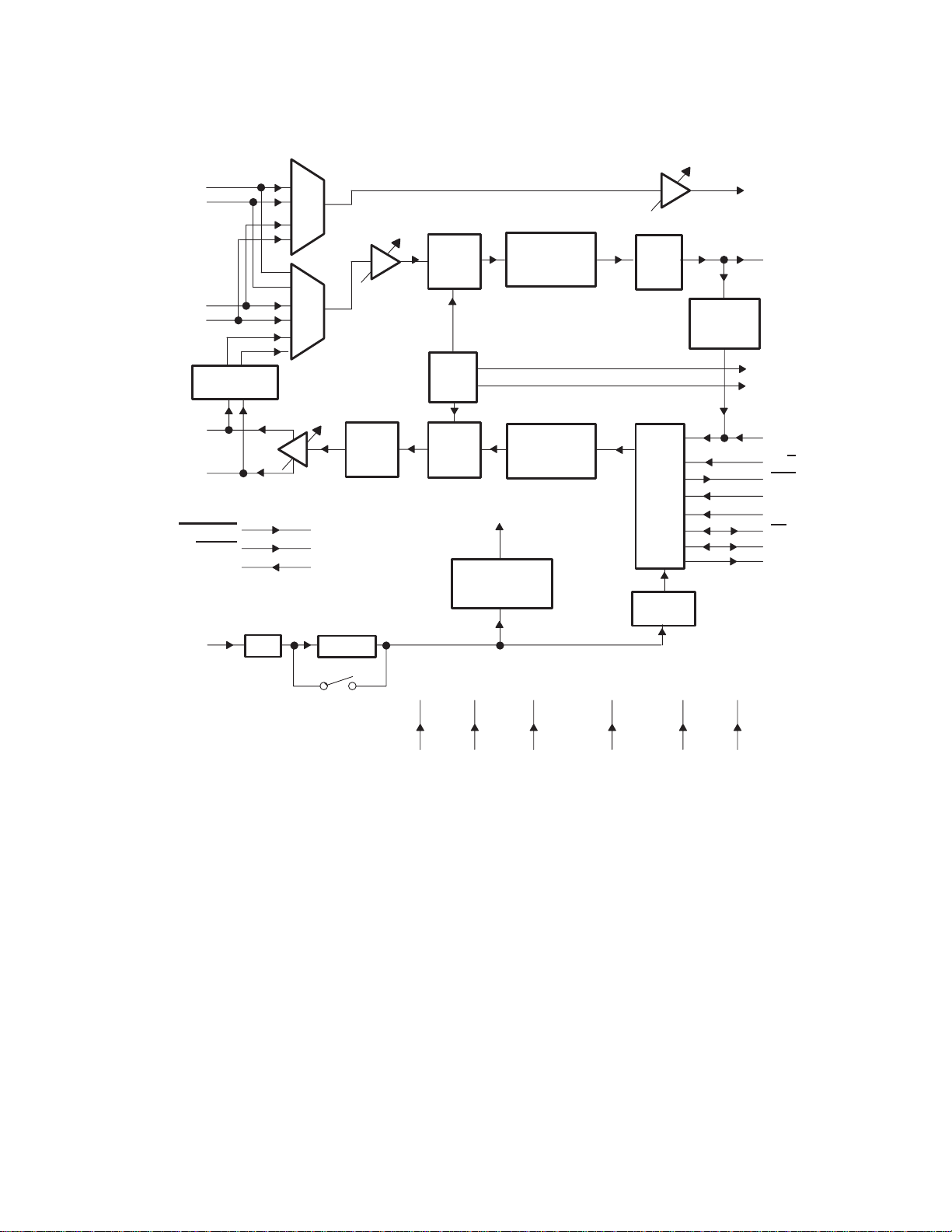

1.2 Functional Block Diagram

INP

INM

AUXP

AUXM

OUTP

OUTM

PWRDWN

RESET

MCLK

5

6

3

4

Analog

Loopback

23

24

16

15

28

FILT

18

÷N

MUX

MUX

PGA

Low

Pass

Filter

PLL (x4)

PGA

Sigma

-Delta

ADC

V

ref

Sigma

-Delta

DAC

Clock Circuit

Decimation

Interpolation

Internal

Filter

Filter

Buffer

Buffer

I/O

Control

PGA

Digital

Loopback

27

11

1

2

12

22

21

14

17

20

19

13

MONOUT

DOUT

REFP

REFM

DIN

M/S

FSD

ALTDATA

FC

FS

SCLK

FLAG

1–2

10 9 7 8

DV

SS

NOTE: Pin numbers shown are for the DW package.

DV

DD

AV

DD(PLL)AVSS(PLL)

26 25

AV

SS

AV

DD

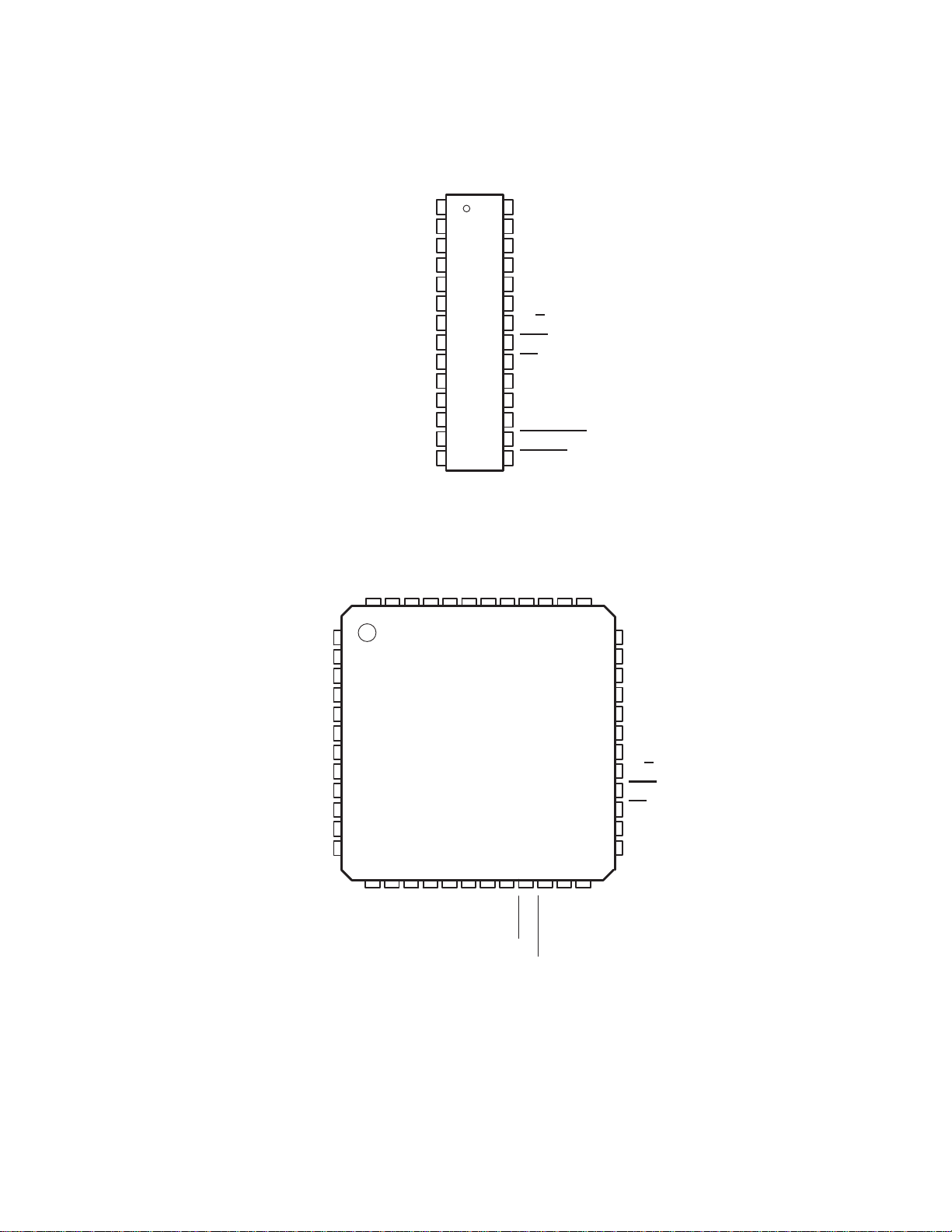

1.3 Terminal Assignments

REFP

REFM

AUXP

AUXM

INM

AV

DD(PLL)

AV

SS(PLL)

DV

DV

DOUT

FLAG

ALTDATA

AUXM

AUXP

DW PACKAGE

(TOP VIEW)

1

2

3

4

5

INP

6

7

8

9

DD

10

SS

11

12

DIN

13

14

PT PACKAGE

(TOP VIEW)

REFP

REFM

NC

FIL T

28

27

26

25

24

23

22

21

20

19

18

17

16

15

NC

FILT

MONOUT

AV

SS

AV

DD

OUTM

OUTP

M/S

FSD

FS

SCLK

MCLK

FC

PWRDWN

RESET

AV

NC

MONOUT

SS

NC

DD

AV

47 46 45 44 4348 42

1

INP

2

INM

3

NC

4

NC

NC

NC

NC

NC

DD

SS

5

6

7

8

9

10

11

12

13

14 15

AV

DD(PLL)

AV

SS(PLL)

DV

DV

NC

DOUT

NC – No internal connection

17 18 19 20

16

DIN

FLAG

NC

NC

40 39 3841

21

NC

37

22 23 24

FC

36

35

34

33

32

31

30

29

28

27

26

25

NC

OUTM

OUTP

NC

NC

NC

NC

NC

M/S

FSD

FS

SCLK

MCLK

RESET

AL TDATA

PWRDWN

1–3

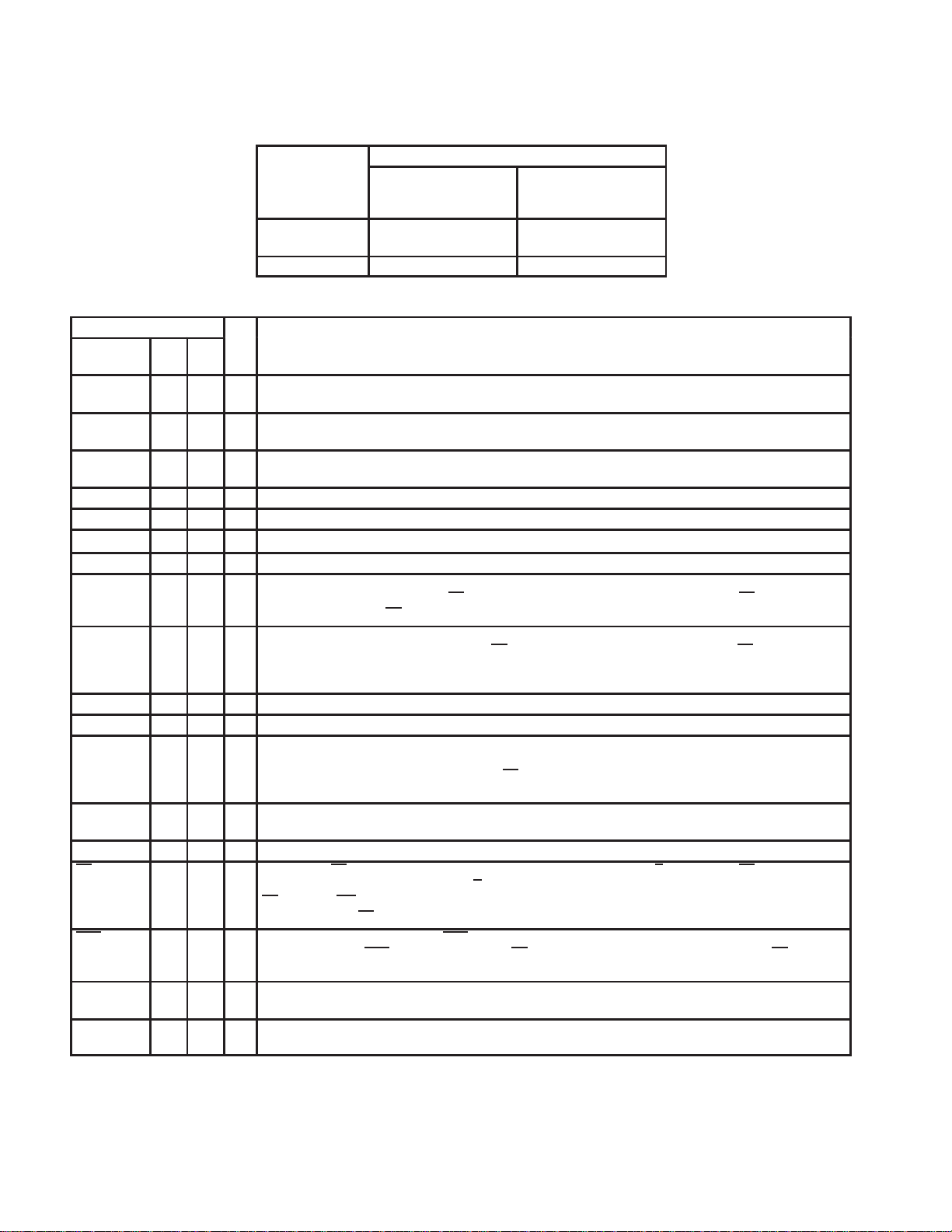

1.4 Ordering Information

PACKAGE

T

A

0°C to 70°C

–40°C to 85°C TLC320AD50IDW

SMALL OUTLINE

PLASTIC DIP

(DW)

TLC320AD50CDW

TLC320AD52CDW

QUAD FLAT PACK

(PT)

TLC320AD50CPT

TLC320AD52CPT

1.5 Terminal Functions

TERMINAL

NAME

ALTDATA 17 14 I Alternate data. ALTDATA signals are routed to DOUT during secondary communication if the phone mode

AUXM 48 4 I Inverting input to auxiliary analog input. AUXM requires an external single-pole antialias filter with a low output

AUXP 47 3 I Noninverting input to auxiliary analog input. AUXP requires an external single-pole antialias filter with a low

AV

DD

AV

DD(PLL)

AV

SS

AV

SS(PLL)

DIN 15 12 I Data input. DIN receives the DAC input data and register data from the external DSP (digital signal processor)

DOUT 14 11 O Data output. DOUT transmits the ADC output bits and register data, and is synchronized to SCLK. Data is

DV

DD

DV

SS

FC 23 17 I Hardware secondary communication request. When FC is set to high, a secondary communication, followed

FILT 43 28 O Bandgap filter. FILT is provided for decoupling of the bandgap reference, and provides 3.2 V. The optimal

FLAG 16 13 O Output flag. During phone mode, FLAG contains the value set in control 2 register.

FS 27 20 I/O Frame sync. FS is an output when the device is configured as a master (M/S pin tied high). FS is an input when

FSD 28 21 O Frame sync delayed output. The FSD (active-low) output synchronizes a slave device to the frame sync of

INM 2 6 I Inverting input to analog modulator. INM requires an external single-pole antialias filter with a low output

INP 1 5 I Noninverting input to analog modulator. INP requires an external single-pole antialias filter with a low output

NOTES: 1. Separate analog and digital power and ground pins are supplied on this device. For best operation and results, the PC board designer

NO.PTNO.

37 25 I Analog ADC power supply (5 V only) (see Note 1)

5 7 I Analog power supply for the internal PLL (5 V only) (see Note 1)

39 26 I Analog ground (see Note 1)

7 8 I Analog ground for the internal PLL (see Note 1)

11 9 I Digital power supply (5 V or 3 V) (see Note 1)

12 10 I Digital ground (see Note 1)

should utilize separate analog and digital power supplies as well as separate analog and digital ground planes.

2. All digital inputs and outputs are TTL compatible, unless otherwise noted (for DVDD = 5 V).

I/O DESCRIPTION

DW

is enabled using control 2 register.

impedance and should be tied to AVSS if not used.

output impedance and should be tied to A VSS if not used.

and is synchronized to SCLK and FS

high impedance when FS

sent out at the rising edge of SCLK when FS

When configured as a master, DOUT is active only during the appropriate time slot. DOUT is in high

impedance during the frame syncs for the slaves.

by the primary communication, will occur to transfer data between this device and the external controller. FC

is sampled and latched on the rising edge of FS

3 for details.

capacitor value is 0.1 µF (ceramic). This voltage node should be loaded only with a high-impedance dc load.

the device is configured as a slave (M/S

FS

goes low. FS is internally generated in the master mode for the master device and all slave devices. In

the master mode FS

the master device. FSD

is delayed in time by the number of shift clocks programmed in the control 3 register.

impedance.

impedance.

is not active.

is low during data transfer.

is applied to the slave FS input and is the same duration as the master FS signal but

. Data is latched at the falling edge of SCLK when FS is low. DIN is at

pin tied low). When configured as a slave, data will transfer when

is low. DOUT is at high impedance when FS is not activated.

at the end of the primary serial communication. See section

1–4

1.5 Terminal Functions (Continued)

TERMINAL

NAME

M/S 29 22 I Master/slave select input. When M/S is high, the device is the master. When M/S is low, the device is a slave.

MCLK 25 18 I Master clock. MCLK derives the internal clocks of the sigma-delta analog interface circuit.

MONOUT 40 27 O Monitor output. MONOUT allows for monitoring of the analog input and is a high-impedance output. The gain

OUTM 36 24 O Inverting output of the DAC. The OUTM output can be loaded with 600 Ω. OUTM is functionally identical with

OUTP 35 23 O Noninverting output of the DAC. The OUTP output can be loaded with 600 Ω. OUTP can also be used alone

PWRDWN 22 16 I Power down. When PWRDWN is pulled low, the device goes into a power-down mode, the serial interface

REFM 46 2 O Voltage reference filter output. REFM is provided for low-pass filtering of the internal bandgap reference. The

REFP 45 1 O Voltage reference filter positive output. REFP is provided for low-pass filtering of the internal bandgap

RESET 21 15 I Reset. RESET initializes all of the internal registers to their default values. The serial port can be configured

SCLK 26 19 I/O Shift clock. The SCLK signal clocks serial data in through DIN and out through DOUT during the frame-sync

NOTES: 1. Separate analog and digital power and ground pins are supplied on this device. For best operation and results, the PC board designer

NO.PTNO.

should utilize separate analog and digital power supplies as well as separate analog and digital ground planes.

2. All digital inputs and outputs are TTL compatible, unless otherwise noted (for DVDD = 5 V).

I/O DESCRIPTION

DW

or mute is selected using control 1 register.

and complementary to OUTP. OUTM can also be used alone for single-ended operation.

for single-ended operation.

is disabled. However, all the register values are sustained and the device resumes full power operation without

reinitialization when PWRDWN

programmed register contents (see paragraph 2.2.2 for more information).

optimal ceramic capacitor value is 0.1 µF and should be connected between REFM and REFP. DC voltage

at REFM is 0 V.

reference. The optimal ceramic capacitor value is 0.1 µF and should be connected between REFP and REFM.

DC voltage at REFP is 3.2 V.

to the default state accordingly. See section 6 and paragraph 2.2.1 for more information.

interval. When configured as an output (M/S

signal frequency by 256. When configured as an input (M/S

synchronous with the master clock and frame sync.

is pulled high again. PWRDWN resets the counters only and preserves the

high), SCLK is generated internally by multiplying the frame-sync

low), SCLK is generated externally and must be

1–5

1.6 Definitions and Terminology

ADC Channel The ADC channel refers to all signal processing circuits between the analog input and the digital

conversion results at DOUT.

Channel Delay The delay for the analog signal at the ADC input to appear on the digital output. The delay for

the digital value at the DAC input to appear on the analog output.

d

d The alpha character

(see Section 3.2) when discussing other data bit portions of the register.

Dxx Dxx is the bit position in the primary data word (xx is the bit number).

DSxx DSxx is the bit position in the secondary data word (xx is the bit number).

DAC Channel DAC channel refers to all signal processing circuits between the digital data word applied to DIN

and the differential output analog signal available at OUTP and OUTM.

represents valid programmed or default data in the control register format

Data Transfer

Interval

The time during which data is transferred from DOUT and to DIN. The interval is 16 shift clocks

and the data transfer is initiated by the falling edge of the frame-sync signal.

FIR Finite duration impulse response

f

s

Frame Sync and

Sampling Period

The sampling frequency

Frame sync and sampling period is the time between falling edges of successive primary

frame-sync signals. It is always equal to 256 SCLK.

Frame Sync Frame sync refers only to the falling edge of the signal that initiates the data transfer interval.

The primary frame sync starts the primary communications, and the secondary frame sync

starts the secondary communications.

Frame-Sync

Interval

Host A host is any processing system that interfaces to DIN, DOUT, SCLK, FS

The frame-sync interval is the time period occupied by 16 shift clocks. The frame-sync signal

goes high on the seventeenth rising edge of SCLK.

, and/or MCLK.

PGA Programmable gain amplifier

Primary

Communications

Primary communications refers to the digital data transfer interval. Since the device is

synchronous, the signal data words from the ADC channel and to the DAC channel occur

simultaneously.

Secondary

Communications

Secondary communications refers to the digital control and configuration data transfer interval

into DIN and the register read data cycle from DOUT. The data transfer interval occurs when

requested by hardware or software.

Signal Data This refers to the input signal and all of the converted representations through the ADC channel

and the signal through the DAC channel to the analog output. This is contrasted with the purely

digital software control data.

X The alpha character X represents a

1–6

don’t care

bit-position within the control register format.

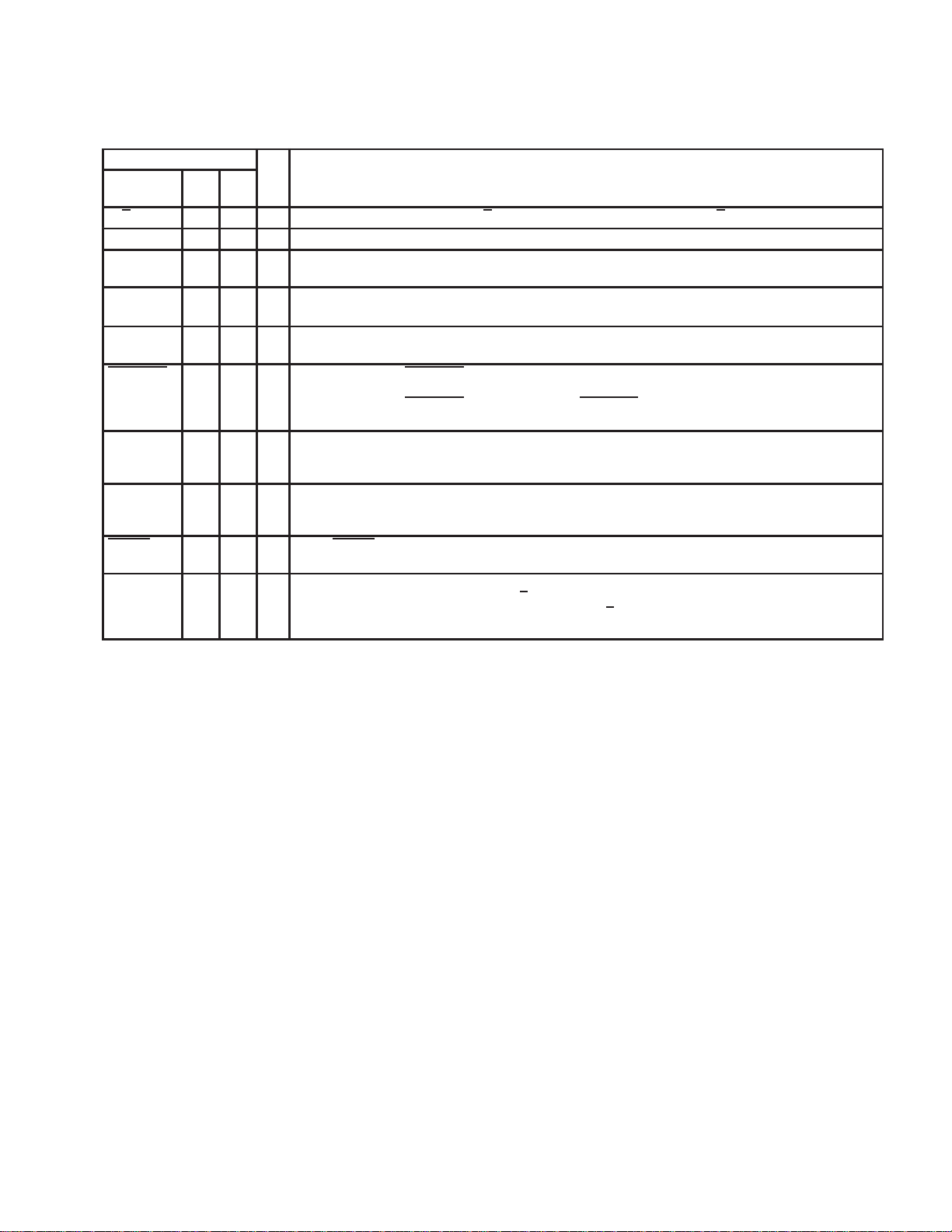

1.7 Register Functional Summary

There are seven control registers that are used as follows:

Register 0 The No-Op register. Addressing register 0 allows secondary communications requests without altering

any other register.

Register 1 Control register 1. The data in this register controls:

• Software reset

• Software power down

• Normal or auxiliary analog inputs enabling

• Normal or auxiliary analog inputs monitoring

• Selection of monitor amplifier output gain

• Selection of digital loopback

• Selection of16-bit or (15+1)-bit mode of DAC operation

Register 2 Control register 2. The data in this register:

• Contains the output value of FLAG

• Selects phone mode

• Contains the output flag indicating a decimator FIR filter overflow

• Selects either 16-bit mode or (15+1)-bit mode of ADC operation

• Enables analog loopback

Register 3 Control register 3. The data in this register:

• Sets the number of SCLK delays between FS

• Informs the master device of how many slaves are connected in the chain

and FSD

Register 4 Control register 4. The data in this register:

• Selects the amplifier gain for the input and output amplifiers

N

• Sets the sample rate by choosing the value of

MCLK/(512

• Selects the PLL. If the PLL is selected, the sampling rate is set to MCLK/(128

bypassed, the sampling rate can be set to MCLK/(512

Register 5 Reserved for factory test. Do not write to this register.

Register 6 Reserved for factory test. Do not write to this register.

N

)

from 1 to 8 where fs = MCLK/(128 N) or

N

). If the PLL is

N

).

1–7

1–8

2 Detailed Description

2.1 Device Functions

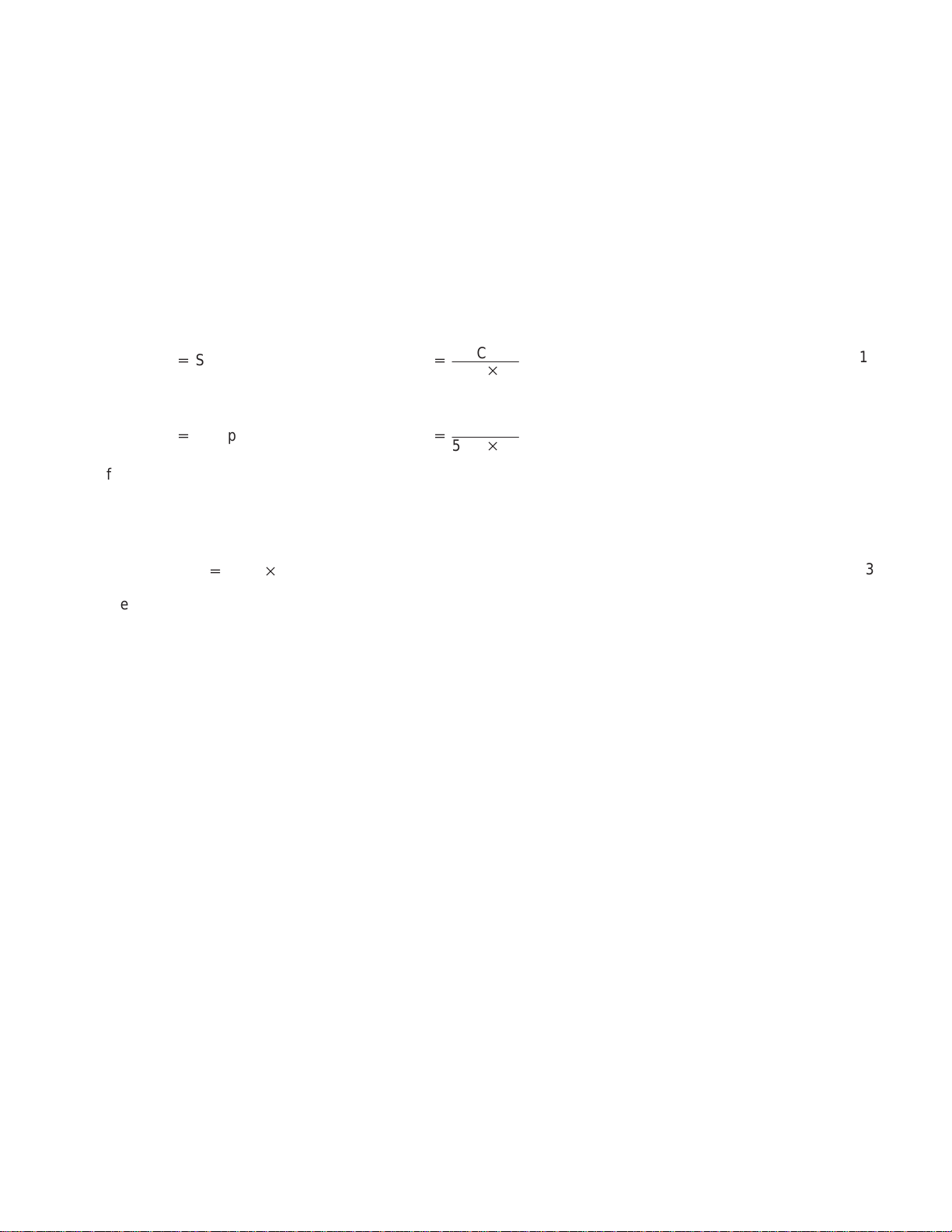

2.1.1 Operating Frequencies and Filter Control

The sampling frequency is controlled by control register 4. When the internal PLL is enabled (D7=0), the sampling

frequency is derived from the following equation:

fs+

Sampling (conversion) frequency

When the internal PLL is disabled (D7=1), the sampling frequency is derived from the following equation:

fs+

Sampling (conversion) frequency

If the sampling frequency is lower than 7 kHz, the sampling frequency is derived from the master clock (MCLK) using

equation 2. The internal PLL must be bypassed. The PLL input clock for sampling frequencies lower than 7 kHz is

outside the working range for the PLL input clock.

The frequency of SCLK is derived from sampling frequency (fs) instead of MCLK. The equation is as follows:

SCLK

The cutoff frequency of the filter can not be controlled by register programming. The filter response is shown in the

specification for an 8 kHz sample rate. This pass band scales linearly with the sample rate.

+

256 f

s

MCLK

+

128 N

MCLK

+

512 N

(1)

(2)

(3)

2.1.2 ADC Signal Channel

The input signal is amplified and applied to the ADC input. The ADC converts the signal into discrete output digital

words in 2s-complement data format, corresponding to the instantaneous analog-signal value at the sampling time.

These 16-bit (or 15-bit) digital words, representing sampled values of the analog input signal after the PGA, are

clocked out of the serial port (DOUT) at the positive edge of SCLK during the frame-sync interval, one bit for each

SCLK and one word for each primary communication interval (256 SCLKs). The 16-bit or (15 + 1)-bit ADC mode is

programmed into the device using control register 2. The default setting is the (15 + 1)-bit mode after power-up.

During secondary communication, the data previously programmed into the registers can be read out. This read

operation is accomplished by sending the appropriate register address (DS12 – DS8) with the read bit (DS13) set

to 1 in through DIN during present secondary communication. If a register read is not requested, all 16 bits are cleared

to 0 in the secondary communication. The timing sequence is shown in Figure 2–1 and Figure 2–2.

2–1

Loading...

Loading...